# Clemson University TigerPrints

All Theses

Theses

5-2007

# Software Development for Mechatronics Systems: Simulation of Multiple UAV Navigation and Device Driver Interface for the Q4 Data Acquisition Card

Ninad Pradhan Clemson University, npradha@clemson.edu

Follow this and additional works at: https://tigerprints.clemson.edu/all\_theses Part of the <u>Electrical and Computer Engineering Commons</u>

## **Recommended** Citation

Pradhan, Ninad, "Software Development for Mechatronics Systems: Simulation of Multiple UAV Navigation and Device Driver Interface for the Q4 Data Acquisition Card" (2007). *All Theses*. 60. https://tigerprints.clemson.edu/all\_theses/60

This Thesis is brought to you for free and open access by the Theses at TigerPrints. It has been accepted for inclusion in All Theses by an authorized administrator of TigerPrints. For more information, please contact kokeefe@clemson.edu.

## SOFTWARE DEVELOPMENT FOR MECHATRONICS SYSTEMS: SIMULATION OF MULTIPLE UAV NAVIGATION AND DEVICE DRIVER INTERFACE FOR THE Q4 DATA ACQUISITION CARD

A Thesis Presented to the Graduate School of Clemson University

In Partial Fulfillment of the Requirements for the Degree Master of Science Electrical Engineering

> by Ninad Pradhan May 2007

Accepted by: Dr. Darren Dawson, Committee Chair Dr. Ian Walker Dr. Timothy Burg

## ABSTRACT

Mechatronics systems are often a close interleaving of different aspects of hardware, software, control and mechanical design. Two such aspects are delved into in greater detail for this thesis, both related to software development.

Simulations are used to know the practical conditions under which a control design is effective. The system simulated in this case was a multiple vehicle system, where the vehicles navigated from source to a destination configuration avoiding two different kinds of obstacles.

Post simulation, a system is implemented using hardware and tested using an experimental setup. Data Acquisition Boards such as the Quanser Q4 are used to read the system state. A device driver interface containing a wide variety of functions was developed and extensively tested for the Q4 PCI bus card.

Both these projects were software development efforts towards contributing to different aspects of Robotics and Mechatronics projects in the Controls and Robotics Group.

# DEDICATION

I dedicate this work to my parents, Nilkanth and Aparna Pradhan, for it was their patience, belief and encouragement that made it possible.

#### ACKNOWLEDGMENTS

I would like to thank my advisor, Dr. Darren Dawson, for his guidance and emphasis on persistence and independence with work. I would also like to thank Dr. Timothy Burg for serving on my committee. I would like to thank Dr. Ian Walker for his good counsel and empathy, whenever it was sought.

I would like to thank Vilas for his help and guidance with the device driver project, and Jian, whose research Erhun and I simulated during our first year.

I would like to acknowledge and thank my lab partner, Erhun Iyasere. I learnt a lot from his technical insight and creativity at work, all laced with diligence and good humor. I would also like to thank Vikram Iyengar, for his support and his infectious enthusiasm for all things, including research and engineering. I would also like to thank another group mate and friend, Nitendra Nath, for his candid and constructive opinions whenever I was looking for them. I would like to thank my friend Rahul Saxena, for being there as always and bearing the brunt of my questions during my learning curve on the device driver project.

I would like to offer special thanks to Kaveri for her motivation and presence at all times, which made much of this possible. I would also like to thank all my friends from VG 110 and 127, especially Radhika, Neha and Utpal, who have been my support system for the past two years, and more.

Finally, I would like to thank my parents, my sister Meeta and aunt Kunda for their love and unconditional support and guidance. None of my endeavors would have fructified without it.

# TABLE OF CONTENTS

|                                                                                                                        | Page                    |  |

|------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

| TITLE PAGE                                                                                                             | i                       |  |

| ABSTRACT                                                                                                               | ïi                      |  |

| DEDICATION                                                                                                             |                         |  |

| ACKNOWLEDGEMENTS                                                                                                       | iv                      |  |

| LIST OF FIGURES                                                                                                        | vii                     |  |

| CHAPTER                                                                                                                |                         |  |

| 1. INTRODUCTION                                                                                                        | 1                       |  |

| Thesis Organization                                                                                                    | 3                       |  |

| 2. COOPERATIVE CONTROL OF MULTIPLE VEHICLES WITH<br>LIMITED SENSING                                                    | 4                       |  |

| Introduction<br>Problem Formulation<br>Model Development<br>Multiple UAV Cooperative Control<br>Moving EA Extension    | 4<br>7<br>8<br>14<br>19 |  |

| 3. SIMULATION OF MULTIPLE UAV SYSTEM                                                                                   | 22                      |  |

| Overview of Simulation Model<br>Layout of Simulation Model<br>Simulation Results<br>Generating a Simulation Movie File | 22<br>23<br>24<br>28    |  |

| 4. DEVELOPMENT OF DEVICE DRIVER INTERFACE FOR Q4<br>DATA ACQUISITION CARD                                              | 29                      |  |

| Project Summary<br>PCI Communication in QNX<br>Interrupt Servicing using QNX<br>Q4 Registers                           | 29<br>34<br>41<br>48    |  |

| 5. IMPLEMENTATION AND TESTING OF          |     |

|-------------------------------------------|-----|

| THE INTERFACE                             | 61  |

|                                           |     |

| Outline of Driver Class QuanserQ4         | 61  |

| Introduction to Class QuanserQ4 Functions | 61  |

| Installation and Documentation            | 71  |

| Software Testing                          | 72  |

| Testing using QMotor                      | 79  |

|                                           |     |

| APPENDICES                                | 83  |

| A: Q4 Functions : Summary                 | 84  |

|                                           | 110 |

| B: Class QuanserQ4 Example Program        |     |

| C: DAC Channel Output Calculation Formula | 113 |

| D: Simulation Layout                      | 115 |

| N P P P N I O P O                         | 110 |

| REFERENCES                                | 116 |

## LIST OF FIGURES

| Figu | re                                                                | Page |

|------|-------------------------------------------------------------------|------|

| 2.1  | Multiple UAVs in Combat Zone                                      | 7    |

| 2.2  | Smooth Bump Function                                              | 10   |

| 3.1  | UAV Navigation - First Stage                                      | 25   |

| 3.2  | UAV Navigation – Second Stage                                     | 26   |

| 3.3  | UAV Navigation - Third Stage                                      | 26   |

| 3.4  | UAV Navigation - Fourth Stage                                     | 27   |

| 3.5  | UAV Navigation – Final Configuration                              | 27   |

| 4.1  | Device Driver Project – Implementation Flowchart                  | 33   |

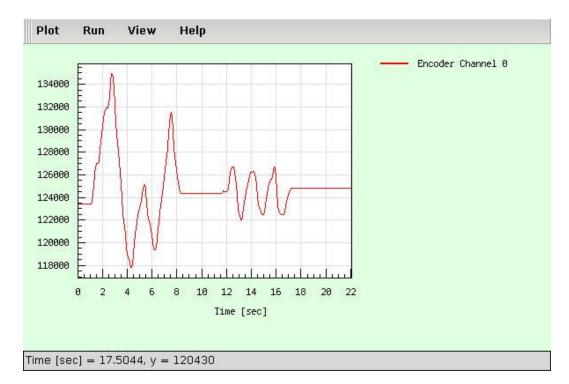

| 5.1  | Plot of Encoder Channel Count                                     | 81   |

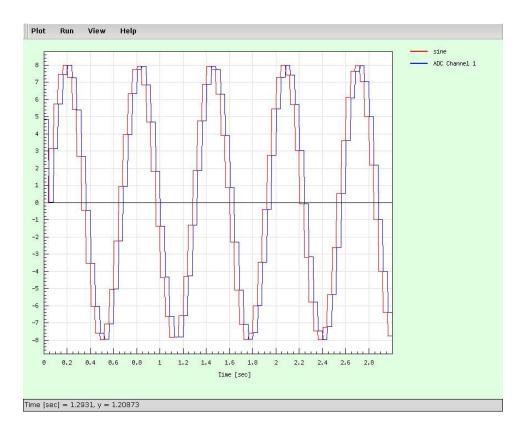

| 5.2  | Plot of DAC Output and ADC Readout of DAC Output                  | 82   |

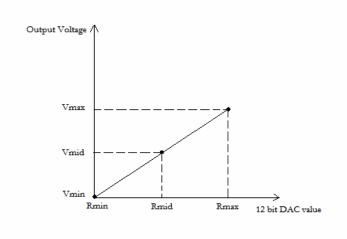

| C.1  | Linear Relationship between Register Input and DAC Channel Output | 114  |

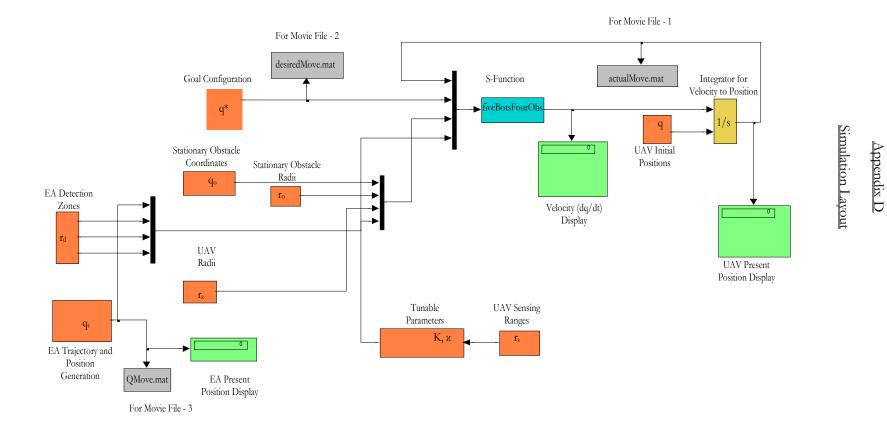

| D.1  | Multiple UAV Simulation – Simulink Model Layout                   | 116  |

#### CHAPTER ONE

## INTRODUCTION

The field of Mechatronics brings together, under its umbrella, diverse areas of engineering theory and practice. The projects in this thesis provided an opportunity to explore problems in two such areas.

The first was a simulation of a cooperative control algorithm which used a navigation function to guide a group of mobile robots from a source position to a goal configuration. The navigation function built on the theory of potential fields, which repel robots from known obstacle locations while attracting them towards the goal position. This navigation function has been designed to avoid getting stuck at local minima when realizing the goal configuration. The robots were assumed to be unmanned aerial vehicles (UAVs) and their region of operation a combat zone. The task for the UAVs was to move to the target configuration in the combat zone while avoiding collision with stationary obstacles, and avoiding being detected by enemy assets (EAs). The EAs were each assumed to have a detection zone, and problem was formulated with certain assumptions regarding the detection range and capabilities of the mobile agents in question.

Simulations were carried out for cases where the EAs were assumed to be stationary, and mobile. Conditions for the simulation were varied, such as the area of the stationary obstacles, the sensing and detection zones of mobile agents (both UAVs and EAs), and the initial and final configuration of the UAV group. For each change in the system configuration, system gains were tuned to achieve desired performance. The sensitivity of the system to these variations provided feedback on the performance of the centralized navigation algorithm proposed in the publication.

In contrast to the theoretical background to the first project, and its subsequent simulation, is the second project, which is the design and implementation of a device driver for a Data Acquisition and Control Card. The device driver made it possible for the PCI based Q4 Data Acquisition and Control Card, developed by Quanser Consulting Inc., to be used on a QNX system. The Q4 is a versatile system which contains a number of ADC, DAC and Encoder Channels, Digital Input/Output Pins, and External Signal and Interrupt Lines. Prior to the development of this software, the Q4 could only be run on the Windows platform.

Migration to the QNX platform would be beneficial to the Control and Robotics Group, since QNX based motor control software has been extensively used in and developed for experiments. The Q4 would provide the Data Acquisition functionality to compliment this control software; this functionality being currently supplied by the ServoToGo Board. The Q4 not only provides all the functionalities of the ServoToGo, and more, but also uses the PCI bus, unlike the ServoToGo's use of the increasingly obsolete ISA architecture.

There were numerous challenging sub-problems which needed addressing before the Q4 Device Driver Interface could be implemented. Initial hurdles were faced in communicating with the card. QNX system commands were adapted for Interrupt processing, to deal with 'events' which would be the means for the card to satisfy requirements for speed in performance, vital to most control based applications. Once interrupts could be serviced, it was necessary to set the card up in a way that the user application would be able to write to and read from card Registers, which were the means of configuring a mode of operation for the Q4.

The next stage was the development of a user friendly interface to the functions that the card had to offer. A number of functions were written so that the user could exercise the maximum possible degree of control over card configuration, and make changes to the configuration using intuitive function calls and arguments. At each stage during the software development process, numerous test programs were written, and all code was carefully commented so as to simplify future modifications to the software. The final driver interface was also exhaustively commented and documentation was generated so that a user manual was available to supplement the software.

It has been an endeavor to produce a thesis manuscript that provides adequate information on both projects, with a view towards not only outlining what has been done during the execution of these by the author, but also assist, in whatever way possible, future simulations and software development in this research group.

## Thesis Organization

This thesis discusses two software development projects for the Controls and Robotics Group. Chapter One introduces both projects and discusses significant aspects of their objectives and implementation.

Chapter Two delves into the development of a control law for the Cooperative Control of Multiple Vehicles with Finite Sensor Range. The navigation algorithm is developed for a case where the vehicles or UAVs encounter stationary obstacles and enemy assets, and is extended for a case where the enemy assets themselves are mobile. Chapter Three discusses the simulation of the system for the staionary Enemy Assets case, and provides figures for the UAV trajectories from source to their convergence to the destination configuration.

Chapter Four gives the design objectives for the device driver interface, and introduces QNX and Q4 features which form the basis of the implementation. The actual implementation of the driver Class, and testing of the software using standalone programs and QMotor is detailed in Chapter Five.

A detailed listing for the driver interface, an example program and derivation of a formula used in the Class are included in the Appendices, as is the layout for the multiple UAV simulation.

### CHAPTER TWO

## COOPERATIVE CONTROL OF MULTIPLE VEHICLES WITH LIMITED SENSING

A navigation function based cooperative control is developed in this paper for the navigation of multiple Unmanned Aerial Vehicles (UAVs) in the presence of known stationary obstacles and unknown enemy assets (EAs). Specifically, the motion of UAVs are planned in a centralized fashion. The standard navigation function approach is extended to a multiple navigation strategy with an analytical switch among different cases due to the limited sensing zone of the UAVs. A differentiable controller is proposed based on this navigation function that yields asymptotic convergence. A discussion for avoiding moving EAs is presented. Simulation results are provided to illustrate the performance of the proposed control strategy.

## Introduction

Numerous researchers have proposed algorithms to address the motion control problem associated with robotic task execution in an obstacle cluttered environment. A comprehensive summary of techniques that address the classic geometric problem of constructing a collision-free path and traditional path planning algorithms is provided in Section 9, ``Literature Landmarks", of Chapter 1 of [16]. Since the pioneering work by Khatib in [11], it is clear that the construction and use of potential functions has continued to be one of the mainstream approaches to robotic task execution in the presence of obstacles. In short, potential functions produce a repulsive potential field around the robot workspace boundary and obstacles and an attractive potential field at the goal configuration. A comprehensive overview of research directed at potential functions is provided in [16]. One of the criticisms of the potential function approach is that local minima can occur that can cause the robot to ``get stuck" without reaching the goal position. Several researchers have proposed approaches to address the local minima issue (e.g., see [1], [2], [6], [12], [27]). One approach toaddress the local minima issue was provided by Koditschek in [13] for holonomic systems (see also [14] and [20]) that is based on a special kind of potential function, coined a navigation function, that has a refined mathematical structure which guarantees a unique minimum exists. For other related work that has focused on the development of potential function-based approaches, the reader is referred to [3], [9], [10], [15], [17], [20], [25], and [26].

By leveraging previous results directed at classic (single robot) systems, more recent research has focused on the development of potential function-based approaches for the more challenging multiple agent system. For example, Loizou et al. [18] extended the navigation function methodology, established for single robot navigation, to the case of multiple robots. [19] presented an extension to the navigation function methodology to the case where unmodelled obstacles are introduced in the workspace. The approach of [19] constructs a potential field that models all known environment features and combines it with an efficient control scheme that handles additional unknown features. In [4], gyroscopic forces and scalar potentials were utilized to create swarming behaviors for multiple agent systems. As stated in [4], two main assumptions, the kinetic energy of the vehicle is bounded and only one obstacle is present in the detection shell, limit the application of the approach. A decentralized motion control approach was proposed in [8] in which the agent reacts with the agents in its neighborhood. No obstacles were considered in [8]. In [24], the flocking motion remains stable as long as the graph that describes the neighboring relations among the agents in the group is always connected. For local agent interaction, a nonsmooth potential function was applied between two agents under a local interaction regime. Additionally, demonstration of the nonsmooth control law in [23] showed the use of local sensing (limited sensing distance) to affect motion but not affect the stability properties of the group. This type of system falls into the category of differential equations with discontinuous right hand sides, and hence, the stability tools are generally based on nonsmooth analysis. More recently, Olfati-Saber et al. presented a theoretical framework for the design and analysis of distributed flocking algorithms in the presence of multiple obstacles [21].

The goal of this paper is to develop a cooperative control algorithm for the multiple UAV

problem to ensure that all of the UAVs will: i) remain in the combat zone, ii) avoid collisions with other UAVs, iii) avoid collisions with predetermined stationary objects, iv) avoid being detected by EAs, and v) ensure each UAV moves to its desired location in the combat zone. The unique aspect of this approach is that the UAVs only act with respect to the EAs within its sensing zone. That is, the navigation function is analytically switched when EAs enter the sensing zone of UAVs without corrupting the stability and convergence properties of the navigation function. The proposed approach can be applied to numerous applications<sup>1</sup> such as mobile sensor network deployment, pre-flocking (gathering the UAVs to a specific formation in a certain location), and suppression of enemy air defense using a cooperative group of UAVs.

This paper is organized in the following manner. In Section 2.1, the problem is formulated for the multiple UAVs navigation. In Section 2.2, a smooth bump function, a boundary function, obstacle functions, EA detection zone functions, and UAV collision functions are developed. In Section 2.3, a multiple UAV navigation function is designed, and a cooperative control algorithm is developed. A discussion for avoiding moving EAs is presented in Section 2.4. Simulation results illustrating the performance of the cooperative control algorithm are given in Chapter 3, and concluding remarks are given following the simulation results.

<sup>&</sup>lt;sup>1</sup>Although the vehicle model in this manuscript is the UAV, it can be applied to any multiple agent system which has various applications and has attracted significant attention as stated in [24].

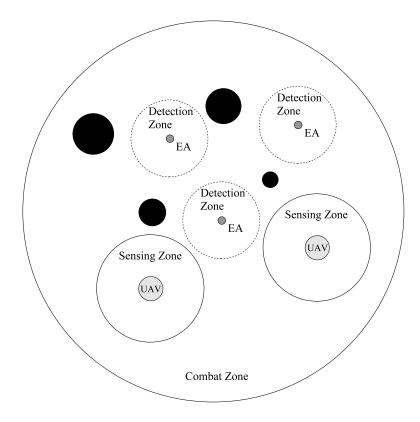

Figure 2.1 Multiple UAVs in Combat Zone

## Problem Formulation

As illustrated by Figure (2.1), all UAVs are assumed to be initially in the combat zone (i.e., the large circle), which is a configuration space with a boundary. In the combat zone, there are some stationary obstacles and EAs. All UAVs have an onboard sensor, which can only sense objects in its neighborhood denoted as the sensing zone (i.e., due to the physical limitation of the onboard sensing capability of each UAV). With a limited detection range, the EAs can also only detect objects in its neighborhood denoted as the detection zone. The cooperative control objectives for the multiple UAVs are to ensure that all of the UAVs will:

- Objective 1: Remain in the combat zone.

- Objective 2: Avoid collisions with other UAVs.

- Objective 3: Avoid collisions with the predetermined stationary objects.

- Objective 4: Avoid being detected by EAs.

- Objective 5: Ensure that each UAV moves to its desired location in the combat zone.

To address the multiple UAV cooperative control problem in this paper, we use the following assumptions:

- Assumption 1: The physical dimensions of the combat zone are assumed to be known by all of the UAVs.

- Assumption 2: The location and the physical dimensions of the stationary obstacles are known within the combat zone by all of UAVs.

- Assumption 3: The UAV sensing zone and the EA detection zone are much greater than the size of the EA; therefore, the EAs can be treated as points.

- Assumption 4: The detection zone of the EA is known by all of UAVs.

- Assumption 5: The sensing zone of the UAVs is greater than the detection zone of the EAs (otherwise it is impossible for the UAVs to avoid being detected by the EAs).

- Assumption 6: Within the finite combat zone, all UAVs have access to all of the other UAVs' position.

- Assumption 7: Initially, all of the UAVs are in a non-contact configuration in the combat zone and do not contact the EAs, stationary obstacles, and the boundary of the combat zone.

## Model Development

To explain the approach, we first transform the physical geometry of each UAV into a sphere with  $q_i(t) \in \mathbb{R}^3$  and  $r_{zi} \in \mathbb{R}, i = 1, 2, \dots, n$ , denoting the time-varying center and the constant radius of the *i* th UAV sphere, respectively, and *n* denotes the number of the UAVs. The composite configuration for the UAV  $q(t) \in \mathbb{R}^{3n}$  is defined as

$$q(t) = \begin{bmatrix} q_1^T(t) & q_2^T(t) & \cdots & q_n^T(t) \end{bmatrix}^T.$$

(1)

We will assume the multiple UAV system can be described by the following kinematic model:

$$\dot{q} = u \tag{1}$$

where  $u(t) \in \mathbb{R}^{3n}$  is the cooperative control input. The goal configuration of the UAVs is denoted as  $q^* \in \mathbb{R}^{3n}$  and defined by

$$q^* = \begin{bmatrix} q_1^{*T} & q_2^{*T} & \cdots & q_n^{*T} \end{bmatrix}^T$$

(2)

where  $q_i^* \in \mathbb{R}^3$ ,  $i = 1, 2, \dots, n$ , denotes the desired constant location of the *i* th UAV.

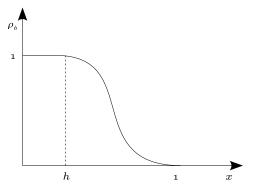

#### Smooth Bump Function

The multiple UAV navigation problem is complicated by the fact that the sensing zone of the UAVs is finite. To deal with this problem, a smooth bump function is introduced to analytically switch the repulsive force generated by the EAs and the boundary of the combat zone from zero to one. Indeed, it is this type of analytical smoothing approach that allows the boundary functions and EA detection functions developed subsequently to be appropriately smoothed out to facilitate the gradient-like differentiation that is utilized to construct the cooperative control algorithm.

Definition 1 The smooth bump function, denoted by  $\rho_h(\cdot): \mathbb{R}_+ \to [0,1]$ , is a scalar function satisfying [22]

$$\rho_h(x) = \begin{cases} 1 & 0 \leq x \leq h \\ 0 & x \geq 1 \\ \in (0,1) & h < x < 1 \end{cases}$$

(3)

where  $\mathbb{R}_+$  denotes non-negative real number, and  $h \in (0,1)$  is a positive constant parameter of the bump function.

The smooth property of the bump function defined in ((3)) is illustrated in Figure (2.2).

Figure 2.2 Smooth Bump Function

Based on the definition of the bump function in ((3)), one possible choice is the following bump function introduced in [22]

$$\rho_h(x) = \begin{cases} 1 & x \in [0,h] \\ \frac{1}{2} \left[ 1 + \cos\left(\pi \frac{x-h}{1-h}\right) \right] & x \in (h,1) \\ 0 & \text{otherwise.} \end{cases}$$

(4)

## Boundary Function

To ensure that the UAVs remain within the predefined combat zone, a scalar boundary function is introduced to determine the relationship between the boundary of the combat zone and the position of the UAVs. The objective in selecting a boundary function is to prevent any UAV from contacting any part of the combat zone boundary.

$$\beta_{0} = \begin{cases} 0 & \text{At least one UAV contacts the} \\ \text{boundary of the combat zone} \\ & \text{All UAV are inside the combat zone} \\ 1 & \text{and the boundary of the combat zone} \\ \text{is outside the sensing zone of UAVs} \\ \in (0,1) & \text{Otherwise.} \end{cases}$$

(5)

As indicated by ((5)), the function  $\beta_0(\cdot)$  approaches zero if any of the UAVs approach the boundary of the combat zone, and hence, this type of design for  $\beta_0(\cdot)$  spawns a gradient-like term to ensure that the UAV moves away from the boundary of the combat zone. Based on ((3)) and ((5)), the boundary function can be designed as follows

$$\beta_{0} = \prod_{i=1}^{n} \rho_{h_{0i}} \left( \frac{1}{r_{o0} - r_{zi}} \| q_{i} - q_{o0} \| \right)$$

(6)

where  $q_{o0} \in \mathbb{R}^3$  denotes the position of the center of the combat zone, and  $r_{o0} \in \mathbb{R}$  denotes the radius of the combat zone. From ((5)) and ((6)), it is clear that: i)  $\beta_0 = 0$  when for any i,  $\|q_i - q_{o0}\| \ge r_{o0} - r_{zi}$ , and ii)  $\beta_0 = 1$  only when for all i,  $\|q_i - q_{o0}\| \le h_{0i} (r_{o0} - r_{zi})$ . Based on ((3)), ((5)), and ((6)), the bump function parameter  $h_{0i}$  in ((6)) can be designed as follows

$$h_{0i} = \frac{r_{o0} - r_{si}}{r_{o0} - r_{zi}} \tag{7}$$

where  $r_{si} \in \mathbb{R}$  denotes the radius of the UAV sensing zone.

#### Obstacle Function

To ensure that no UAV contacts the stationary obstacles that have been predetected in the combat zone, a scalar obstacle function is introduced to determine the relationship between the UAVs and the obstacles.

Definition 3 The *i* th obstacle function  $\beta_i(\cdot) \in \mathbb{R}$ ,  $i = 1, 2, \dots, n_o$ , is a function satisfying

$$\beta_{i} = \begin{cases} 0 & \text{At least one UAV contacts} \\ & \text{the ith obstacle} \\ > 0 & \text{Otherwise} \end{cases}$$

(8)

where  $n_o \in \mathbb{R}$  is the number of the obstacles.

As indicated by ((8)), if any of the UAVs approach the boundary of the *i* th obstacle, the *i* th obstacle function  $\beta_i(\cdot)$  approaches zero, and hence, this type of design for  $\beta_i(\cdot)$  spawns a gradient-like term to ensure that the UAV moves away from the *i* th obstacle. Based on ((8)), the *i* th obstacle function  $\beta_i(\cdot)$  can be designed as follows

$$\beta_{i} = \prod_{j=1}^{n} \left[ \left\| q_{j} - q_{oi} \right\|^{2} - \left( r_{zj} + r_{oi} \right)^{2} \right]$$

(9)

where  $q_{oi} \in \mathbb{R}^3$ ,  $i = 1, 2, \dots, n_o$ , denotes the position of *i* th obstacle, and  $r_{oi} \in \mathbb{R}$ ,  $i = 1, 2, \dots, n_o$ , denotes the radius of the *i* th obstacle.

## EA Detection Zone Function

To avoid being detected by the EAs, a scalar EA detection zone function is introduced to determine the relationship between the UAVs and the EAs.

Definition 4 The EA detection zone function  $g_i(\cdot) \in \mathbb{R}$ ,  $i = 1, 2, \dots, n_e$ , is a function satisfying

$$g_{i} = \begin{cases} At least one UAV reaches \\ 0 & the detection zone boundary \\ of the ith EA \\ 1 & The ith EA is outside of the sensing zone of all UAV s \\ \in (0,1) & O therwise \end{cases}$$

(10)

where  $n_e \in \mathbb{R}$  is the number of the EAs.

As the boundary of the sensing zone of any of the UAVs approaches the boundary of the detection zone of any of the EAs, the value of the EA detection zone function  $g_i(\cdot)$  approaches zero. Based on the definition of the bump function in ((3)) and the EA detection zone function in ((10)), a specific EA detection zone function  $g_i(\cdot)$  can be designed as follows

$$g_{i} = \prod_{j=1}^{n} \left[ 1 - \rho_{h_{ij}} \left( \frac{h_{ij}}{r_{di} + r_{zj}} \| q_{j} - q_{ei} \| \right) \right]$$

(11)

where  $q_{ei} \in \mathbb{R}^3$ ,  $i = 1, 2, \dots, n_e$ , denotes the position of i th EA, and  $r_{di} \in \mathbb{R}^3$ ,  $i = 1, 2, \dots, n_e$ , denotes the radius of the i th EA detection zone. From ((10)) and ((11)), it is clear that: i)  $g_i = 0$ when for any  $j = 1, 2, \dots, n$ ,  $||q_j - q_{ei}|| \leq r_{di} + r_{zj}$ , and ii)  $g_i = 1$  when for all  $j = 1, 2, \dots, n$ ,  $||q_j - q_{ei}|| \geq r_{sj}$ . Based on ((3)), ((10)), and ((11)), the bump function parameter  $h_{ij}, i = 1, 2, \dots, n_e, j = 1, 2, \dots, n$ , in ((11)) can be designed as follows

$$h_{ij} = \left(r_{di} + r_{zj}\right)/r_{sj}.$$

(12)

Because  $g_i(\cdot)$  is a user-defined function, and  $r_{di}$  may be somewhat uncertain, a best guess for  $r_{di}$  can be used instead of the actual size of the EA detection zone as long as the best guest of  $r_{di}$  is greater than the actual values.

Remark 1

## UAV Collision Function

To avoid collisions between UAVs, we quantify the distance between the i th UAV and the *j* th UAV by introducing the UAV collision function.

Definition 5 The UAV collision function  $b_{ij}(\cdot) \in \mathbb{R}$ ,  $i, j = 1, 2, \dots, n$  and  $i \neq j$ , is a function satisfying

$$b_{ij} = \begin{cases} 0 & \text{The } i\text{th UAV contacts the } j\text{th UAV} \\ > 0 & \text{Otherwise.} \end{cases}$$

(13)

From ((13)), it is clear that when the i th UAV and the j th UAV do not contact each other,  $b_{ij}(q_i(t), q_j(t)) > 0$ . As indicated by ((13)), the function  $b_{ij}(\cdot)$  approaches zero if the *i* the UAV approaches the j th UAV, and hence, this type of design for  $b_{ij}(\cdot)$  spawns a gradient-like term to ensure that there is no contact between the i th UAV and the j th UAV. Based on the definition of UAV relationship function in ((13)), a specific UAV collision function can be designed as follows [28]

$$b_{ij} = \left\| q_j - q_i \right\|^2 - \left( r_{zi} + r_{zj} \right)^2.$$

(14)

#### Multiple UAV Cooperative Control

#### Multiple UAV Navigation Function

The primary objective is to navigate the multiple UAVs from an initial configuration to a constant goal configuration while remaining in the combat zone and avoiding stationary obstacles and EAs. To avoid collision with obstacles and EAs, the UAV configuration q(t) should remain in a free configuration space denoted by  $\mathcal{D} \subset \mathbb{R}^{3n}$  which is a subset of the whole combat zone with all configurations removed that involve collision with obstacles and EAs. The constant initial and goal configuration are assumed to be in the interior of  $\mathcal{D}$ . To generate  $q(t) \in \mathcal{D}$ , the special artificial potential function coined a navigation function in [13], can be used. Specifically, the navigation function used in this paper is defined as follows [20].

Definition 6 Let  $\mathcal{D}$  be a compact connected analytic manifold with a boundary, and let  $q^*$  be a goal point in the interior of  $\mathcal{D}$ . A mapping  $\varphi(q): \mathcal{D} \to [0, 1]$ , is a navigation function if:

- It is analytic on  $\mathcal{D}$  (at least the first and second partial derivatives exist and are bounded on  $\mathcal{D}$ );

- It has a unique minimum at  $q^*$ ;

- It obtains a maximum value on the boundary of  $\mathcal{D}$  (i.e., admissible on  $\mathcal{D}$ );

- It is a Morse function (i.e., the matrix of second partial derivatives, the Hessian, evaluated at its critical points is non-singular).

After defining the obstacle functions, the UAV collision functions, the boundary functions, and the EA detection zone function, we now introduce the navigation function that is utilized to derive the cooperative control algorithm. The navigation function  $\varphi(q) \in \mathbb{R}$  for multiple UAVs is constructed as follows

$$\varphi(q) = \frac{\|q - q^*\|^2}{\left[\|q - q^*\|^{2\kappa} + G(q)\right]^{1/\kappa}}$$

(15)

where  $\kappa \in \mathbb{R}_+$  is a positive constant parameter,  $G(q) \triangleq G_1 G_2 G_3 \in \mathbb{R}$ , and the scalar functions  $G_1(\cdot), G_2(\cdot), G_3(\cdot) \in \mathbb{R}$  are defined as follows

$$G_{1} = \prod_{i=0}^{n_{0}} \beta_{i}(q) \quad G_{2} = \prod_{i=1}^{n_{e}} g_{i}(q)$$

$$G_{3} = \sqrt{\prod_{i=1}^{n} \prod_{j \neq i} b_{ij}(q)}$$

(16)

where  $\beta_i(\cdot)$ ,  $g_i(\cdot)$ , and  $b_{ij}(\cdot)$  were defined in ((6)), ((9)), ((11)), and ((14)). Based on ((16))

) and the definition of  $G(\cdot)$ , we can easily show that G = 0 will occur:

- if  $G_1 = 0$  (when any UAV contacts the boundary of the combat zone or the obstacles)

- if  $G_2 = 0$  (when any UAV contacts the detection zone boundary of a EA)

- if  $G_3 = 0$  (when two or more UAVs contact).

Remark 2 Indeed, for a typical obstacle avoidance problem, it does not seem possible to construct

$$\varphi(q(t))$$

, coined a navigation function, such that  $\frac{\partial}{\partial q}\varphi(q(t)) = 0$  only at  $q(t) = q^*$ . Koditschek [14] has

shown that strict global navigation is not possible. That is, as discussed in [20], the appearance of interior saddle points (i.e., unstable equilibria) seems to be unavoidable; however, these unstable equilibria do not really cause any difficulty in practice. As proved in [14], the function  $\varphi(\cdot)$  is a navigation function, so long as the parameter  $\kappa$  exceeds a certain function of the geometric data. That is,  $\varphi(q(t))$  can be constructed such that the attraction domain of the unstable equilibria is a set of measure zero.

Remark 3 The boundary of  $\mathcal{D}$  includes the boundary of the combat zone, the boundary of the stationary obstacles, and the detection zone boundary of the EAs.

Remark 4 The main difference between the navigation function in ((15)) and the standard navigation function in [20] is that for the navigation function in ((15)), the boundary of the combat zone and the EAs have only local interaction with the UAVs. When the boundary of the combat zone and EAs are out of the sensing zone of the UAVs, the corresponding boundary function and EA detection zone function become unity. When the boundary of the combat zone contacts at least one UAV and the detection zone boundary of the EA contacts at least one UAV, the boundary function and corresponding EA detection zone function become zero. It is the analytical smoothing bump function that allows the functions given by ((6)) and ((11)) to be appropriately smoothed out among all cases to facilitate the gradient-like differentiation for multiple UAV navigation. With a similar structure as compared to the standard navigation function given in [14], it is not difficult to follow the proof in [14] to show the multiple UAV navigation function defined in ((15)) satisfies the navigation function properties defined in [14], [20].

### Cooperative Control Design

The cooperative control in this paper is specified as all UAVs act based on all other UAVs' position to avoid collision with other UAVs, obstacles, and EAs. Based on the above definitions, the input u(t) in ((1)) is designed as follows

$$u = -K \left(\frac{\partial \varphi}{\partial q}\right)^T \tag{17}$$

where  $K \in \mathbb{R}^{3n \times 3n}$  is a constant positive definite symmetric control gain matrix and  $\frac{\partial \varphi}{\partial q}(q) \in \mathbb{R}^{1 \times 3n}$  is the partial derivative of  $\varphi(\cdot)$  from ((15)), along q(t). The control algorithm designed in ((17)) illustrates this cooperative control concept since the multiple UAV navigation function  $\varphi(q)$  is a function of all of the UAVs' position.

Remark 5 The control u(t) in ((17)) has been based on the kinematic model in ((1)). This control can be extended using standard backstepping techniques to include second-order dynamic robot models.

Remark 6 With the definition of the EA zone detection function, the navigation function  $\varphi(q)$  is a function of i th EA position only when the i th EA is within the sensing zone of UAVs. Therefore, the control designed in ((17)) depends on the position of the i th EA only when the i th EA is within the sensing zone of UAVs in which case the position of the i th EA is known. This is one of the novelties of the proposed control algorithm.

## Stability Analysis

Theorem 1 Provided  $q(0) \in \mathcal{D}$ , the cooperative control designed in ((17)) along with the navigation

function  $\varphi(q)$  designed in ((15)) ensures that  $q(t) \in \mathcal{D}$  and asymptotic navigation in the sense that

$$q(t) \to q^* \text{as } t \to \infty.$$

(18)

Proof: Let  $V(q): \mathcal{D} \to \mathbb{R}$  denote the following non-negative function

$$V(q) = \varphi(q). \tag{19}$$

After taking the time derivative of ((19)), the following expression can be obtained

$$\dot{V} = \frac{\partial \varphi}{\partial q} \dot{q}.$$

(20)

After substituting ((17)) into ((20)), the following expression is obtained

$$\dot{V} = -f(t) \tag{21}$$

where  $f(t) \in \mathbb{R}$  denotes the following non-negative function

$$f(t) \triangleq \frac{\partial \varphi}{\partial q} K \left( \frac{\partial \varphi}{\partial q} \right)^{T}.$$

(22)

Based on ((21)) and ((22)), it is clear that V(q(t)) is a non-increasing function in the sense that

$$V(q(t)) \le V(q(0)). \tag{23}$$

From ((23)), it is clear that for any initial condition  $q(0) \in \mathcal{D}$ , that  $q(t) \in \mathcal{D} \quad \forall t > 0$ ; therefore,

$\frac{\partial \varphi}{\partial q}, \frac{\partial^2 \varphi}{\partial q^2} \in \mathcal{L}_{\infty}$  based on the Property 1 of Definition 6. Then, it is clear from ((1)) and ((22)) that

$\dot{f}(t) \in \mathcal{L}_{\infty}$ . Based on ((19)), ((21)), ((22)), and the fact that  $\dot{f}(t) \in \mathcal{L}_{\infty}$  on  $\mathcal{D}$ , then Lemma A.6 of

[7] can be invoked to prove that

$$\left\|\frac{\partial\varphi}{\partial q}\right\| \to 0 \tag{24}$$

in the region  $\mathcal{D}$ . Based on Definition 6 and Remark 2, it can be determined that if  $\frac{\partial \varphi}{\partial q}(q(t)) \rightarrow 0$

then  $q(t) \rightarrow q^*$ .

Remark 7 Based on Assumption 7 and ((9)), ((11)), ((14)), and ((16)),  $G_1(q(0))$ ,  $G_2(q(0))$ ,  $G_3(q(0)) > 0$ . Therefore G(q(0)) > 0. Since G(q(0)) > 0 and  $V(q(t)) \le V(q(0))$  for all time, then it is clear from ((15)) that G(q(t)) > 0. Then  $G_1(q(t)) \ne 0, G_2(q(t)) \ne 0, G_3(q(t)) \ne 0$ . Therefore  $G_1(q(t)), G_2(q(t)), G_3(q(t)) > 0$ . We can now see that if G(q(t)) > 0 for all time and  $q(t) \rightarrow q^*$  as  $t \rightarrow \infty$ , then all the objectives given in the Problem Formulation Section will be achieved.

## Moving EA Extension

As explained in the previous sections, the above navigation problem involves moving multiple UAVs from an initial configuration to a constant goal configuration while avoiding stationary obstacles and EAs. To address the moving EA problem, we now discuss, in a heuristic manner, how the approach can still be expected to provide reasonable performance with regard to cooperative control.

A composite configuration of the moving EAs, denoted by  $q_e(t) \in \mathbb{R}^{3n_e}$ , is defined as follows

$$q_{e}(t) = \begin{bmatrix} q_{e1}^{T}(t) & q_{e2}^{T}(t) & \cdots & q_{en_{e}}^{T}(t) \end{bmatrix}^{T}$$

(25)

Similar to the navigation function  $\varphi(q)$  designed in ((15)), a navigation-like function  $\varphi_1(q,q_e): \mathcal{D} \times \mathcal{D} \to [0,1]$  is constructed as follows

$$\varphi_{1}(q,q_{e}) = \frac{\left\|q-q^{*}\right\|^{2}}{\left[\left\|q-q^{*}\right\|^{2\kappa} + G(q,q_{e})\right]^{1/\kappa}}$$

(26)

where  $G(q, q_e) \triangleq G_1 G_2 G_3 \in \mathbb{R}$ , and the scalar functions  $G_1(\cdot), G_3(\cdot) \in \mathbb{R}$  were defined in ((16)), and  $G_2(\cdot) \in \mathbb{R}$  are defined as follows

$$G_2 = \prod_{i=1}^{n_e} g_i(q, q_e) \tag{27}$$

In ((27)),  $g_i(\cdot)$  were defined in ((11)). To facilitate the subsequent discussion, the following assumption must be satisfied:

Assumption 8 The velocity of the EA must satisfy  $\left\|\frac{\partial \varphi_1}{\partial q_e}\dot{q}_e\right\| \leq \varepsilon$  where  $\varepsilon \in \mathbb{R}$  is a

positive constant.

Similar to the input u(t) designed in ((17)) for stationary EA case, the input u(t) in ((1)) for moving EA case is designed as follows

$$u = -K_1 \left(\frac{\partial \varphi_1}{\partial q}\right)^T \tag{28}$$

where  $K_1 \in \mathbb{R}^{3n \times 3n}$  is a constant positive definite symmetric control gain matrix.

To discuss the stability and convergence of multiple UAVs system for the moving EA case, a non-negative function  $V_1(q, q_e): \mathcal{D} \times \mathcal{D} \rightarrow [0, 1]$  is defined as follows

$$V_1(q,q_e) = \varphi_1(q,q_e). \tag{29}$$

After taking the time derivative of ((29)), the following expression can be obtained

$$\dot{V}_1 = \frac{\partial \varphi_1}{\partial q} \dot{q} + \frac{\partial \varphi_1}{\partial q_e} \dot{q}_e.$$

(30)

Based on ((1)), ((28)), and Assumption 8,  $\dot{V}_1(t)$  in ((30)) can be upper bounded as follows

$$\dot{V}_{1} \leqslant -k \left\| \frac{\partial \varphi_{1}}{\partial q} \right\|^{2} + \varepsilon.$$

(31)

where  $k \triangleq \lambda_{\min}(K_1)$ , and  $\lambda_{\min}(\cdot)$  denotes the minimum eigenvalue. We now discuss two cases.

Case 1 q(t) is near the boundary of  $\mathcal{D}$ .

Since we are near the boundary, it seems reasonable to assume that  $\left\| \frac{\partial \varphi_1}{\partial q} \right\| \ge \varepsilon$ , where  $\varepsilon \in \mathbb{R}$  is a

positive constant. Hence, based on ((31)), k can be selected to ensure that  $\dot{V}_1(t)$  be non-positive when q(t) is near the boundary of  $\mathcal{D}$ . Similar to Property 3 in Definition 6, it is clear from ((26)) that the navigation-like function  $\varphi_1(q, q_e)$  obtains the maximum value on the boundary of  $\mathcal{D}$ . Since  $\varphi_1(t)$  is a non-increasing function, and  $\varphi_1(t) < 1$  for all time when q(t) is near the boundary of  $\mathcal{D}$ , the UAVs will never contact the boundary of  $\mathcal{D}$ . It is also clear that  $G_i(t) > 0$ , for i = 1, 2, 3 when q(t) is near the boundary of  $\mathcal{D}$ . Hence, Objective 1 - Objective 4 will be achieved for this case.

Case 2: q(t) is far away from the boundary of  $\mathcal{D}$ .

For this case, the second term in ((30)) will vanish based on the property of the bump function in ((5)). Hence, an argument identical to the proof of Theorem 1 can now be applied to show that Objective 1 - Objective 5 will be achieved.

#### CHAPTER THREE

## SIMULATION OF MULTIPLE UAV SYSTEM

Simulations were carried out on both the stationary EA system and the moving EA extension. The UAVs were configured in an arbitrary initial configuration from where they navigated to the final configuration while fulfiling all objectives of the navigation function. None of the UAVs touched the others, stationary obstacles were avoided, the UAVs stayed out of the detection zones of the EAs, and the UAVs stayed within the combat zone at all times.

The system was found to be sensitive to the values of the tunable parameters, namely  $\kappa$  (from (16)) and K (from (18)). Successful convergence to the goal configuration was highly dependant on the gains assigned to the system using tunable parameters. The gains required re-tuning when EAs or stationary obstacles were added to the combat zone, and when their properties such as physical radius or radius of motion were changed.

## Overview of Simulation Model

The system was simulated using MATLAB Simulink. Simulations were in the Simulink 6 format. For the final version of the simulations, the moving EA extension simulation template was modified to create the stationary EA simulation. The reason for this is apparent when the moving EA simulation is examined.

A circle was used as the trajectory for EA motion. The radius of the circle was varied for each EA. A S-Function was written to incorporate EA motion into the program. The S-Function generated position values for each of the EAs and they were passed to the S-Function responsible for calculating UAV positions based on the navigation function. For the stationary EA case, the EAs were set to retain their original position by setting their trajectory to a circle of radius zero.

### Layout of the Simulation model

The main model template can be seen in Figure (D.1). In the model, four kinds of blocks can be seen : Subsystems, S-Functions, Data Files and Displays. They have been represented by orange, blue, gray and green blocks respectively, in the figure.

There are three multiplexers in the model. The multiplexers may be viewed as demarcation points, which divide the simulation can be divided into three major subsystems. EA Subsystems define the location, motion and properties of the EAs in the combat zone. Obstacle Subsystems combine the EA Subsystem with stationary, non-EA obstacles from the environment. Navigation Subsystems use information from Obstacle Subsystems, current position of the UAVs and desired Goal Configuration in the Navigation Function.

Each of the major subsystems mentioned above comprises of smaller subsystem blocks, which are seen in the model. Their nomenclature in the model explains their relevance to the algorithm or the nature of the data provided by them.

Desired Goal Configuration, Current EA Position and Current UAV position are written to separate data files. These data files log these positions in a matrix for each time instant in the simulation. This data can be used to create a movie file which animates the simulation. It is also possible to view the position values being logged by attaching a Displays to appropriate points. Displays were otherwise used as a diagnostic tool, for observing the variation in certain values which reflected the performance of the system.

All the algorithmic input was used by a single S-Function, called fiveBotsFourObs.m. This function performed all the mathematical calculations necessary to obtain the control input *u*, which was the derivative of the UAV position. This was integrated and fed back to the same function. The control loop also included other, non-feedback inputs such as Goal Configuration, EA Position and value of gains from the Tunable Parameters. There were a number of long differentiation operations required for the math in the simulation. All of these operations were performed using Maple and these Maple outputs were used in the S-function .

## Simulation Results

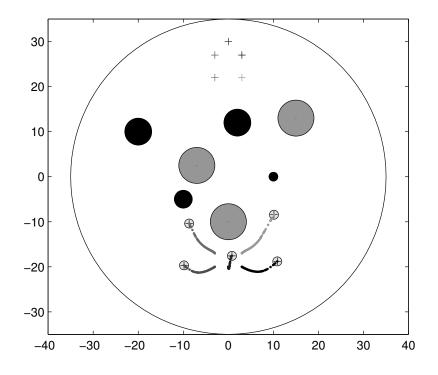

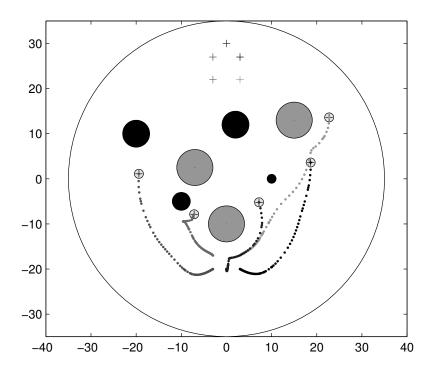

To illustrate the performance of the proposed cooperative control algorithm, we set up a 2dimensional simulation to navigate five UAVs from an initial configuration to the goal configuration while avoiding four obstacles and avoiding being detected by three EAs. Whenever there are multiple obstacles along the trajectory between the initial and final points, which in this case consists of stationary EAs and obstacles, the UAVs cannot pass through the obstacles. The chosen initial configurations constitute non-trivial setups since the straight paths connecting the initial and final positions are obstructed by the stationary EAs and obstacles. As a result, the UAVs might split along the straight line connecting the two points in two or smaller groups while avoiding the stationary EAs and obstacles.

The initial configuration of the five UAVs was selected as follows:

$$q_{1}(0) \triangleq \begin{bmatrix} 0 & -20 \end{bmatrix}^{T} \qquad q_{2}(0) \triangleq \begin{bmatrix} 3 & -20 \end{bmatrix}^{T} \qquad q_{3}(0) \triangleq \begin{bmatrix} -3 & -20 \end{bmatrix}^{T} q_{4}(0) \triangleq \begin{bmatrix} -3 & -17 \end{bmatrix}^{T} \qquad q_{5}(0) \triangleq \begin{bmatrix} 3 & -17 \end{bmatrix}^{T}.$$

Their destination configuration was selected as follows:

$$q_1^* \triangleq \begin{bmatrix} 0 & 30 \end{bmatrix}^T$$

$q_2^* \triangleq \begin{bmatrix} 3 & 27 \end{bmatrix}^T$   $q_3^* \triangleq \begin{bmatrix} -3 & 27 \end{bmatrix}^T$

$q_4^* \triangleq \begin{bmatrix} -3 & 22 \end{bmatrix}^T$   $q_5^* \triangleq \begin{bmatrix} 3 & 22 \end{bmatrix}^T$ .

The stationary obstacles were positioned in the combat zone at

$$q_{o1} \triangleq \begin{bmatrix} -10 & -5 \end{bmatrix}^{T} \quad q_{o2} \triangleq \begin{bmatrix} 2 & 12 \end{bmatrix}^{T}$$

$$q_{o3} \triangleq \begin{bmatrix} -20 & 10 \end{bmatrix}^{T} \quad q_{o4} \triangleq \begin{bmatrix} 10 & 0 \end{bmatrix}^{T}$$

Three stationary EAs were located at

$$q_{e1} \triangleq \begin{bmatrix} -7 & 2.5 \end{bmatrix}^T$$

$q_{e2} \triangleq \begin{bmatrix} 15 & 13 \end{bmatrix}^T$   $q_{e3} \triangleq \begin{bmatrix} 0 & -10 \end{bmatrix}^T$ .

The radii of the UAVs were selected as follows

$$r_{z1} = 1$$

$r_{z2} = 1$   $r_{z3} = 1$   $r_{z4} = 1$   $r_{z5} = 1$ .

The radii of the combat zone and the obstacles were selected as follows

$$r_{o0} = 35$$

$r_{o1} = 2$   $r_{o2} = 3$   $r_{o3} = 3$   $r_{o4} = 1$ .

The radii of the UAV sensing zones were selected as follows

$$r_{s1} = 8$$

$r_{s2} = 8$   $r_{s3} = 8$   $r_{s4} = 8$   $r_{s5} = 8$ .

The radii of the EA detection zone were selected as follows

$$r_{d1} = 4 \quad r_{d2} = 4 \quad r_{d3} = 4.$$

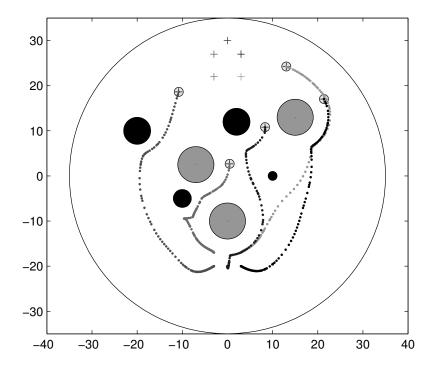

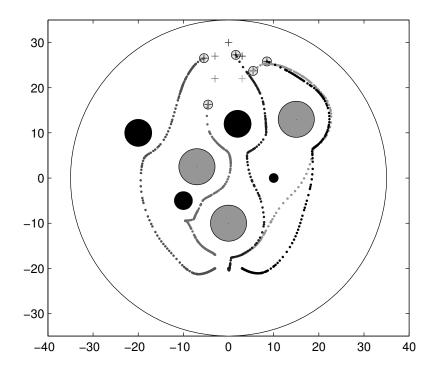

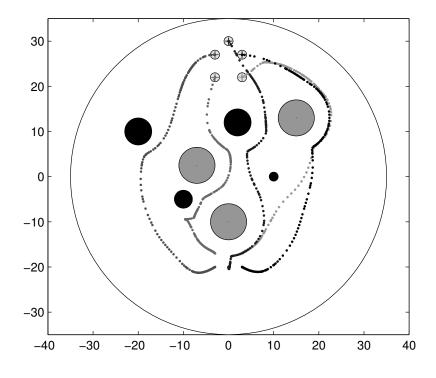

Figure (3.1) - Figure (3.5) show several stages of multiple UAVs from the initial configuration to the goal configuration. The gray circles illustrate the detection zone of the EAs, the black circles illustrate the obstacles, and the UAVs are denoted by the circles with the cross in the center. The five crosses at the top part of the figure illustrate the goal configuration of the UAVs. From the figures, it is clear that the UAVs moved to their destination while avoiding the stationary obstacles and avoiding being detected by the EAs along their paths.

Figure 3.1 UAV Navigation - First Stage

Figure 3.2 UAV Navigation - Second Stage

Figure 3.3 UAV Navigation - Third Stage

Figure 3.4 UAV Navigation - Fourth Stage

Figure 3.5 UAV Navigation - Final Configuration

## Generating a Simulation Movie File

The simulation data collected by .mat files was used in generation of .avi files which animated the simulation results. Movie generation in MATLAB is essentially a plot generating program which includes additional movie conversion commands. While the UAVs and EAs were drawn using standard MATLAB plot commands, their positions were taken from the data files from the simulation. The plot program, and hence the movie, left a trace of the path of each UAV as it moved from source to destination. MATLAB provides a combination of movie generation functions which create an animation based on information from data files.

The downloadable video clips for multiple UAV navigation for both stationary EAs and moving EAs are provided in [5].

#### Conclusion

A navigation function based cooperative control is developed in this paper to navigate multiple UAVs in an obstacle and enemy asset cluttered environment. The standard navigation function approach was extended to a multiple navigation strategy with analytical switching among different cases due to the limited sensing zone of the UAVs. A differentiable cooperative control law is proposed based on this navigation function that yields asymptotic convergence. The navigation strategy of avoiding the moving EAs is also discussed. Simulation results are provided to demonstrate the performance of the proposed control strategy.

# CHAPTER FOUR DEVELOPMENT OF DEVICE DRIVER INTERFACE FOR Q4 DATA ACQUISITION CARD

# Project Summary

#### **Development Objectives**

The objective of this project was the development of a device driver for the Quanser Q4 Measurement and Control Board for the QNX Operating System. The Quanser Q4 offers an interface to a wide variety of devices such as Analog and Digital sensors and Encoders. The development of this low level software was necessitated by two primary motivators

- The need to migrate to a PCI device for measurement and data acquisition. The data acquisition card currently in use is the ServoToGo Board, which is an ISA Board. This required even recently purchased motherboards to come equipped with ISA slots. The ISA architecture being increasingly obsolete, a switch to a measurement and control system running on the commonly used PCI bus was desired. The Q4 is such a device.

- The need for a QNX driver for the Q4, QNX being the operating system of choice in the Control and Robotics Group. The Quanser Q4 had been successfully tested on the Windows platform using standard drivers and software developed by Quanser Consulting Inc<sup>®</sup>.

## Design Considerations

It was desired to have a driver which

- Provided access to all features of the Quanser Q4.

- Was economical in its use of system resources

- Provided an easy interface for user to configure the operating mode of the Quanser Q4.

Support for achieving the above objectives would be provided by

• The functionalities provided by the operating system for a software developer. These would determine the fluidity possible during the development process.

• The technical support provided in the Q4 Manual in terms of device details necessary for implementing a driver.

It was observed that QNX offers a wide range of functions related to PCI Device communication and programming [31]. Further, the microkernel architecture of QNX allows the programmer to work at the user level even when developing low level software such as a device driver. This made it possible to debug and test the functioning of the device while still employing high level debugging techniques such as printing out information on the Terminal window. QNX Help provided exhaustive information on each of the QNX system calls and other relevant functions.

The Q4 itself has been well documented in the Q4 Manual. A section on the Quanser Q4 Registers has been included in the manual for the benefit of programmers working towards device driver development. All of the interaction with the Q4 internal to the computer can be defined in terms of operations on Q4 Registers, and Interrupt Servicing.

Working successfully with the card depended on being able to perform operations on card registers, and servicing interrupt requests coming from the card. Register level operations were assisted by provisions in QNX for device memory mapping. Interrupt Servicing was made possible by a number of interrupt related commands and system calls provided by the QNX OS.

Decisions on the software development process were made depending on matching the design objectives with the available tools for fulfilling those objectives. C was used as the preferred programming language for software testing in the initial phase. Later, it became possible to modularize the code using C++. The Class implemented using C++ was the culmination of the programming effort.

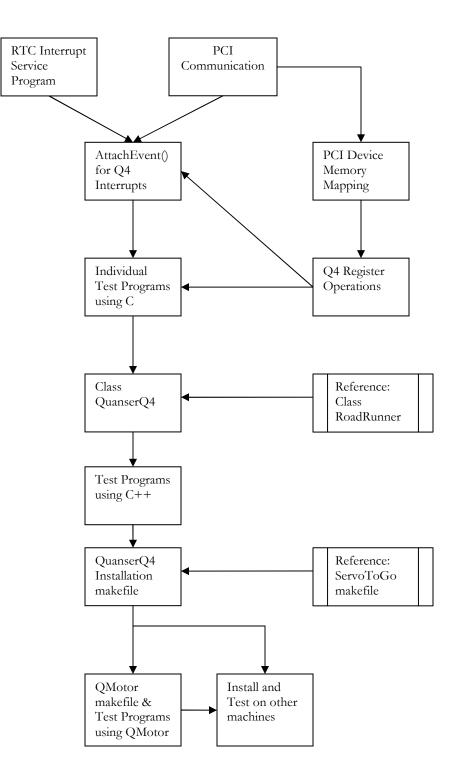

#### Overview of the Project Implementation

The project could be considered to have three significant phases of development

- Achieving Interrupt Service and PCI Communication

- Testing Card Features using standalone C Programs

- Implementation and Testing of the Driver Class

In the first phase lay the testing of operations related to communicating with the card, which was to form the basis of all future development.

Real Time Clock Interrupt programs were used for understanding how interrupt driven software is written for QNX. The importance of the Real Time Clock interrupt was that it was a system interrupt assigned to a fixed interrupt line for x86 systems, and that the RTC was a periodic interrupt source. Failure to acknowledge or service the RTC Interrupt was thus a sure indicator of a flaw in either the logic or the implementation of the interrupt service mechanism. PCI commands in QNX were used to talk to the device and memory map the device to provide access to Registers. Memory mapping is used to provide user programs with direct access to device memory. The result of the mapping is an access to the Read/Write Registers of the Q4. The completion of Phase I meant that the card could be communicated with, successfully. Card Features were tested in the next phase following methods validated by Phase I.

Given the versatility of the Q4, testing each feature meant writing values to a different set of Registers, or writing different values to the same set of Registers. There were a number of such features to be tested, and they demanded slightly or vastly different testing methods. To simplify this process, each significant feature was tested using a different program. Register configurations were hard-coded into the program, and results were checked using either software methods or by using digital multimeters and wires.

Once the card features had been tested in Phase II, it was necessary to modularize the software to allow the user to define the configuration of the card. This was the phase in which the Driver Class was implemented.

A look at the Quanser Q4 Register Map [30] reveals that the operations that can be employed on the card can be divided into six major categories; Interrupt Service, ADC, DAC, Counter/Timer, Digital IO and Encoder functions. To complete the interface, one adds the Constructor and Destructor which set up the Card and renders it ready for use for one of the above set of functions. In addition, it was observed that some of the functions in a category needed to be called in a particular sequence to correctly set up the system. Moreover, functions across categories could be used in combination to realize a feature of the Q4. Finally, it was essential to let the user customize the setup and keep very little hard-coded control over the state of the system.

All of these factors were considered in the final implementation for this project, which was the class QuanserQ4. The outline of this project implementation is given in Figure (4.1).

Figure 4.1 Device Driver Project - Implementation Flowchart

## PCI Communication in QNX

#### About Device Initialization and Memory Mapping

QNX provides a set of functions which simplify communicating with a PCI device. They can broadly be classified into Device Initialization and Memory Mapping functions.

A card on the PCI bus needs to be initialized before any operations are performed on it. The following is done during Device Initialization

- Check the presence and operation of the PCI Bus,

- Locate the Card on the PCI Bus, and

- Associate a QNX structure called pci\_dev\_info, which stores PCI device information, with the card.

Associating the software structure with the device allocates an Interrupt Request line to the Card, and Interrupt Servicing methods can be used from that point onwards. Interrupt Servicing is necessary for complete testing for Card Features. To setup the device for Interrupt Servicing and memory read/write operations, device memory needs to be mapped to the system. The procedure for memory mapping is

- Obtain the device Base Address from the initialized pci\_dev\_info structure

- Verify that the Address is a Memory Address

- Use the Base Address to map device memory to system memory

All features of the Q4 can be used in the Q4 Driver Class by reading from, and writing to, the Q4 Card Registers. Once the device has been initialized and memory mapping has taken place, the features of the Q4 are accessible to the application. The following sequence of steps are taken to communicate with the Q4 PCI device on the system

• Attach the PCI server

pci\_attach( )

• Check for the presence of the PCI BIOS

pci\_present( )

• Find the PCI device

pci-v

pci\_find\_device( )

• Attach a driver to the PCI device

pci\_attach\_device( )

pci\_dev\_info

• Map PCI device memory

Extract CPU Base Address

```

Q4info.CpuBaseAddress[ ]

```

PCI\_IS\_MEM( )

Map device memory

mmap\_device\_memory( )

Use of memory map to address registers (Memory map + offsets)

Details of the Algorithm

Attach the PCI server

The pci\_attach() function connects to the Peripheral Component Interconnect (PCI) server.

pci\_attach() has to be called before calling any of the other PCI functions.

pci\_attach() is used in the programs as follows

if (pci\_attach(0) != -1 ) ... // If no error, program

continues

#### Check for the presence of the PCI BIOS

The pci\_present() function has been used to determine whether or not the PCI BIOS interface function set is present.

When no flags are defined, the function checks only for the presence of the PCI BIOS. This function has been used in Q4 Programs as follows

if(pci\_present(NULL,NULL,NULL)==PCI\_SUCCESS) ...

// Program continues

# Find the PCI device

The QNX System can search for a PCI device when given identification numbers, called Device ID and Vendor ID. The function used for this search is pci\_find\_device(). It returns the location of the nth PCI device that has the specified Device ID and Vendor ID.

Device and Vendor ID information for the Q4 are necessary for this and other commands. These may be obtained by either using the Q4 Manual or the QNX Terminal window listing of all PCI devices (using pci -v) on the system's PCI bus. The Q4 Manual lists device information. Using the Manual, the Device and Vendor ID obtained is as follows

Q4\_DEVICE\_ID 0x0010

## Q4\_VENDOR\_ID 0x11e3

The pci\_find\_device() command can be excluded from test programs for a single Q4 Card system without a loss of functionality. However, it can be used as a diagnostic to confirm the presence of a PCI Card when pci\_attach\_device() has not been not fully tested. Also, it can be used find multiple PCI Cards of the same Device and Vendor ID. This is done by making successive calls to this function, starting with an index of 0, and incrementing it until PCI\_DEVICE\_NOT\_FOUND is returned.

Attach a driver to the PCI device

pci\_attach\_device( )

pci\_dev\_info

memset( )

At this point, the pci server has been attached, the presence of the PCI BIOS has been verified, and the device has been found on the PCI system. The next major step is to attach a driver to the device.

The command pci\_attach\_device() is used for attaching a driver to the card. The command uses information from some user-definable members of the structure pci\_dev\_info to initialize other members of the same structure. This device information struct is called pci\_dev\_info.

pci\_dev\_info : The pci\_dev\_info structure has input and output members. Input Member values can be assigned to the structure by the user. One can call pci\_attach\_device() and specify which of the Output Members are to be initialized by the command. pci\_attach\_device() uses specified Input Members to identify the device and carry out this assignment.

Input members of the structure are Device ID (DeviceID), Vendor ID (VendorID) and Class Code (Class). Output members of interest are Interrupt Number (Irq), CPU Base Address (a six member array called CpuBaseAddress[]), and PCI ROM Address (PciRom).

pci\_attach\_device() : Typically drivers use this function to attach themselves to a PCI device, so that other drivers can't attach to the same device. If the PCI\_SHARE flag is specified, then multiple drivers can attach to the same device.

The PCI server can scan based on a class code, vendor/device ID, or bus number and device/function number. To control the server scanning, appropriate fields of the info structure are initialized and appropriate flags are set.

When first attached to a non-initialized device, the PCI server assigns all the I/O ports, memory and IRQs required for the device. IRQ routing is also done. Once this has completed successfully, these values are filled to the pci\_dev\_info structure for use by the application.

The device can be detached by passing its handle to pci\_detach\_device(). This frees any resources used by pci\_attach\_device(). Usage of pci\_dev\_info and pci\_attach\_device() in test programs is as follows

attachDevice = pci\_attach\_device(NULL, PCI\_SHARE |

PCI\_SEARCH\_VENDEV | PCI\_INIT\_IRQ | PCI\_INIT\_BASE0 |

PCI\_INIT\_BASE1 | PCI\_INIT\_BASE2, 0, &Q4info);

// PCI\_SEARCH\_VENDEV : Scan device based on Vendor ID and Device ID

// PCI\_INIT\_IRQ, PCI\_BASEx : Initialize IRQ, Base Address

// &Q4info : Pointer to the device pci\_dev\_info structure

Following the assignment of the Base Address values in the pci\_dev\_info structure, the device memory can be mapped, as detailed in the following section. The user software can then directly access and manipulate the PCI Card.

# Map PCI device memory

CPU Base Address

Q4info.CpuBaseAddress[ ]

PCI\_IS\_MEM( )

PCI\_IS\_IO( )

Map device memory

mmap\_device\_memory( )

Use of memory map to address registers (Memory map + offsets)

Memory mapping is used to provide application programs with direct access to device memory [33]. The result of the mapping is access to the Read/Write Registers of the Q4, which give the user control over the Data Acquisition and Control features. This access, for a PCI Device, can be provided either by I/O commands, such as in() and out(), or by regular memory operations employing pointers to gain access to device memory [34]. I/O access is achieved by mapping the device memory using a mmap\_device\_io() command, whereas, if the device lends itself to regular memory memory operations, mmap\_device\_memory() is used.

The application does not need to know, in advance, how a PCI device may be mapped. The pci\_dev\_info structure is used for extracting this information.

CPU Base Address: pci\_attach\_device() writes to the struct pci\_dev\_info, a member known as the CpuBaseAddress[]. A CPU Base Addresses is the first physical memory address for the device. The struct member CpuBaseAddress[] is a six element array of type uint64\_t (64 bit unsigned integer). Since PCI Cards such as the Q4 have just one CPU Base Address, only CpuBaseAddress[0] is written to, the rest of the array elements retain their initialization value of zero. Other devices such as graphics cards and multi-head ethernet cards may use more than one Base Address.

To know whether IO or Memory mapping of device is to be carried out, the initialized, non zero Base Address (CpuBaseAddress[0]) is considered. It is used in macros called PCI\_IS\_MEM() and PCI\_IS\_IO(). The PCI\_IS\_MEM() macro returns a TRUE value if the address given to it is a memory address. If this is the case, then mmap\_device\_memory() is used to map the device memory. PCI\_IS\_IO() returns TRUE if the address given to it is an IO address. mmap\_device\_io() is used in this case. For the Q4, PCI\_IS\_MEM(CpuBaseAddress[0]) holds true, and mmap\_device\_memory() is used.

mmap\_device\_memory(): mmap\_device\_memory() maps user defined n bytes of a device's

physical memory address into the caller's address space at the location returned by

mmap\_device\_memory(). When pci\_dev\_info is updated using the pci\_attach\_device() function, a

member called BaseAddressSize[] is initialized for every valid CPU Base Address found by the

function. BaseAddressSize is the size of the Base Address aperture into the board. Since the Q4 contains one CPU Base Address, hence one BaseAddressSize, this Base Address Size is used as the mapping length.

The PROT\_NOCACHE flag is specified for programs in this project. This ensures that the CPU won't defer or omit read/write cycles to the device's registers, nor will it deliver the reads or writes to the registers in a different order than in which they were issued by the driver [34].

Memory mapping is implemented in programs as follows

// Ascertain if this is a memory mappable device if (PCI\_IS\_MEM(baseAddValue)) { // Map device memory memoryMap = mmap\_device\_memory(NULL, Q4info.BaseAddressSize[0], PROT\_READ | PROT\_WRITE | PROT\_NOCACHE, 0, Q4info.CpuBaseAddress[0]); }

The device's memory can now be accessed using the memoryMap pointer. By giving the pointer offsets into the memory, Register Address variables can be created and assigned. Another programming feature is then incorporated so that test programs can use the mapped memory and test card features using Register Read/Write operations.

This feature is the ability to deal with interrupts generated by the PCI device.

# Interrupt Servicing in QNX

As seen earlier, the pci\_attach\_device() function writes to members of the pci\_dev\_info structure, initialising them to values relevant for the Q4. One of the members of the structure is PciIrq, which the interrupt request number assigned to the device. Interrupts are used extensively in the test applications since they provide an efficient means of communicating with the device. Interrupt related functions are also written for the driver Class.

A large number of Q4 Card features have interrupts associated with them. External interrupts such as the Ext\_Int and Fuse, can act as Master-Slave and Emergency interrupts respectively. Analog to Digital Conversion completion is notified using the ADC03\_RDY interrupt line, and the Counter, Watchdog and Encoder Channels have interrupts associated with them.

This leads to an investigation of the available interrupt setup, signalling and processing methods on the QNX platform. Both the standalone test programs and driver Class use the InterruptAttachEvent() method in conjunction with the sigevent structure. The Real Time Clock interrupt was used to test both Interrupt Service methods, InterruptAttach() as well as InterruptAttachEvent().

#### Use of the Real Time Clock Interrupt

The RTC is associated with the hardware interrupt line IRQ8. As a test interrupt source, the IRQ8 is both reliable and periodic. Also, the interrupt frequency of the IRQ8 interrupt can be controlled by writing to its Address and Data Registers. Moreover, since the IRQ8 is a commonly used interrupt source for designing system clock displays, literature related to it is easily accessible. All of this makes the RTC an ideal interrupt source for experimenting with interrupt servicing in QNX.

The Real Time Clock interrupt was used to test the use of Interrupt Attach methods and Interrupt Wait and Service mechanisms. The code for this was adapted from [35] and modified to suit application requirements. Programs which processed interrupts coming from the Q4 Card were initially based on the inferences drawn from the experience with the RTC Interrupt programs. The use of the sigevent structure and use of both the InterruptAttachEvent() and InterruptAttach() methods was suggested by tests on the RTC.

#### The sigevent Structure

The Q4 Card is assigned an interrupt ID when pci\_attach\_device() is called. Interrupt requests from the Q4 are routed through this interrupt ID to the system. The question of how these interrupt requests can be delivered to the application is addressed by the use of Event Notification in QNX.

An interrupt request is an example of an Event. A structure called sigevent allows the user to define what is to be done when an event occurs. Examples of reactions to events are: raise an interrupt (SIGEV\_INTR), send a pulse to the process (SIGEV\_PULSE), send a signal to the process (SIGEV\_SIGNAL) and do nothing (SIGEV\_NONE)

A sigevent structure is associated with a function such as InterruptAttachEvent(). Prior to this, the event structure is initialized to define the reaction to an event. For an event to cause an interrupt, the SIGEV\_INTR response is defined, using the appropriate initialization macro

// Define the sigevent structure variable

struct sigevent event;

// Initialize it to raise interrupt on events

SIGEV\_INTR\_INIT ( &event )

// Associate with command like InterruptAttachEvent( )

As noted earlier, the sigevent structure can be delivered to the process after associating it with an interrupt service method.

## Requesting IO Privity

The thread using Interrupt related system calls needs to have I/O Privity, which gives it the ability to manipulate hardware interrupt sources and affect the processor Interrupt Enable Flag. IO Privity is given using the instruction

## ThreadCtl(\_NTO\_TCTL\_IO, 0)

Root permissions are needed to use this command. If a thread attempts to use these opcodes without successfully executing this call, the thread faults with a SIGSEGV when the opcode is attempted.

#### InterruptAttach() and InterruptAttachEvent()

#### InterruptAttach() and its Limitations

Interrupts in QNX can be serviced using either the InterruptAttach(), or InterruptAttachEvent() function. Threads inherited by the calling thread retain IO privity, as provided by the \_NTO\_TCTL\_IO status. This feature is useful when Interrupt Service Routines (ISR), which are separate interrupt processing threads, are used to service Interrupts. ISR usage is made possible by the use of the InterruptAttach() method.

The software needs to tell the OS [Print Ref 5] that it needs to associate the ISR with an interrupt source. InterruptAttach() is used to specify which interrupt source is to be associated with the ISR.

The ISR operates at a higher priority than any other thread. This makes operations done using the ISR effective almost immediately after the interrupt is called. However, very few kernel calls are available inside the ISR. There is a clear tradeoff between the very low interrupt latency provided by the ISR, and the severe limit on its functionality at that fast access.

#### Choice between InterruptAttach() and InterruptAttachEvent()

The choice between InterruptAttach() or InterruptAttachEvent() is made on the basis of the work that needs to be done in the ISR [36]. If there is some time critical functionality which needs to be dealt with in an ISR, then the InterruptAttach() function call is used. If the ISR needs to do nothing other than schedule a thread which later does all the work at user priority, then InterruptAttachEvent() can be used.

Though there is the consideration of the time delay between an interrupt request and process in InterruptAttachEvent( ), it has been preferred over InterruptAttach( ) in the Test Programs for the following reasons

• It has no ISR, hence nothing running in kernel space, hence there is no danger of crashing the system [Krten pg 231]

• Process level debugging can be used on the Interrupt Handler code [36]. The most commonly used debugging method in this project is the use of fprintf() statements.

Latency in accessing and servicing the interrupt was deemed to be allowable for the application at hand. Test programs did not present a case for the faster servicing route of the InterruptAttach() call.

## Interrupt Servicing

InterruptWait( )

InterruptDisable( )

InterruptUnmask( )

The combination of InterruptAttachEvent() and sigevent allows processing of the interrupt at the thread level. The desired interrupts are enabled using the Q4 Interrupt Enable Register, which leads to the next stage; waiting for an Interrupt and post-interrupt Processing.

Waiting for an Interrupt is done using InterruptWait(). This system call waits for a hardware interrupt. The call to InterruptWait() blocks waiting for an interrupt handler to return an event with

notification type SIGEV\_INTR (i.e. a hardware interrupt). If the notification event occurs before InterruptWait() is called, a pending flag is set. When InterruptWait() is called, the flag is checked; if set, it's cleared and the call immediately returns with success.

To avoid early or spurious interrupt notifications, all Q4 interrupts are disabled before Interrupt Processing function calls like the InterruptAttachEvent() are employed. The interrupt wait function is called as

#### InterruptWait(0, NULL)

Once an event notification in the form of a SIGEV\_INTR has occurred, other necessary function calls are used, to ensure that the interrupt is handled as expected. These are InterruptDisable() and InterruptUnmask().