Clemson University TigerPrints

All Theses

Theses

8-2009

# A DUAL INPUT BIDIRECTIONAL POWER CONVERTER FOR CHARGING AND DISCHARGING A PHEV BATTERY

Daniel Fain Clemson University, dfain@clemson.edu

Follow this and additional works at: https://tigerprints.clemson.edu/all\_theses Part of the <u>Electrical and Computer Engineering Commons</u>

**Recommended** Citation

Fain, Daniel, "A DUAL INPUT BIDIRECTIONAL POWER CONVERTER FOR CHARGING AND DISCHARGING A PHEV BATTERY" (2009). *All Theses.* 631. https://tigerprints.clemson.edu/all\_theses/631

This Thesis is brought to you for free and open access by the Theses at TigerPrints. It has been accepted for inclusion in All Theses by an authorized administrator of TigerPrints. For more information, please contact kokeefe@clemson.edu.

### A DUAL INPUT BIDIRECTIONAL POWER CONVERTER FOR CHARGING AND DISCHARGING A PHEV BATTERY

A Thesis Presented to the Graduate School of Clemson University

In Partial Fulfillment of the Requirements for the Degree Master of Science Electrical Engineering

> by Daniel Ian Fain June 2009

Accepted by: Dr. Randy Collins, Committee Chair Dr. Pierluigi Pisu Dr. Michael Bridgwood

#### ABSTRACT

This thesis looks at a new design for a dual input bidirectional power converter (DIBPC) for charging and discharging a PHEV battery. The design incorporates a power factor correcting rectifier aimed at optimizing the battery charging efficiency from either a 120  $V_{AC}$  or 240  $V_{AC}$  source or discharging the battery to a usable AC voltage at 120  $V_{AC}$ . For simplicity and cost-effectiveness, the DIBPC is constructed using a standard IGBT 6-pack intended for motor control. The DIBPC is designed specifically to provide efficient operation with 120  $V_{AC}$  and 240  $V_{AC}$  inputs while achieving a very low THD<sub>1</sub>. The DIBPC also needs to be able to provide AC output power at 120  $V_{AC}$  with the flexibility to output at 240  $V_{AC}$  in the future.

The DIBPC was tested first in simulation, and then in experimentation. The DIBPC consists of two portions, an AC/DC converter and a DC/DC converter. Although both were simulated, only the AC/DC converter was constructed. Testing under various load values and in each mode of operation provided ample data to show the DIBPC can meet all design goals.

When operating as a rectifier, the DIBPC produces between 7.4% and 13.35% THD<sub>I</sub> and a DC voltage ripple of 8  $V_{P-P}$  or less at 400  $V_{DC}$ . At 120  $V_{AC}$  and 240  $V_{AC}$  an efficiency of 84.5% and 94.6% was achieved, respectively. When operating as an inverter, the DIBPC produces less than 6% THD<sub>V</sub> and 7% THD<sub>I</sub>, while outputting a voltage between 114 and 128  $V_{RMS}$ . Overall, the THD<sub>I</sub> in the charging mode easily meets and exceeds all standards and design constraints set forth, including IEC 61000-3-4. The efficiency with a 120  $V_{AC}$  input, however, is less than expected – about 84%.

#### ACKNOWLEDGMENTS

I would like to thank everyone who has supported me throughout my time here at Clemson (and before). I want to thank my family; my parents have always supported me and encouraged me to meet my full potential. My siblings, Sarah and Aaron, have been sources of good advice, strength and great friendships. To my beautiful fiancée, Amy, who has been patient with me and encouraged me, always knowing when I needed it most. I can't thank you enough for everything you've done for me, such as bringing dinner and that ridiculous dog by the lab when I stayed late. I love you all.

I would like to thank Dr. Collins and Curtiss Fox for their endless technical (and nontechnical) support these last two years. Without their assistance, this project would have been completely overwhelming.

I would also like to acknowledge the donations that were made for my thesis project. I would like to thank Magnetics, Inc. for the donation of the inductor cores. I want to thank Powerex and Mike Barger at Southeast Power Components for the donation of the Powerex IGBT 6-pack. Finally, I would like to thank Ford for the donation of the Ford Escape Hybrid battery. While it has not yet been integrated, it has still provided an end goal and a direction for future research for this project.

### TABLE OF CONTENTS

| TITLE PAGE                                                                                             | i     |

|--------------------------------------------------------------------------------------------------------|-------|

| ABSTRACT                                                                                               | ii    |

| DEDICATION                                                                                             | iii   |

| ACKNOWLEDGMENTS                                                                                        | iv    |

| LIST OF TABLES                                                                                         | vii   |

| LIST OF FIGURES                                                                                        | ix    |

| CHAPTER                                                                                                |       |

| I. BACKGROUND                                                                                          | 1     |

| Motivation<br>Problem Statement<br>Power Factor Correction<br>Existing Technology<br>Summary           | 5<br> |

| II. DESIGN OF THE DUAL INPUT BIDIRECTIONAL<br>POWER CONVERTER                                          | 22    |

| Design Concept<br>AC/DC Stage Design<br>DC/DC Stage Design<br>Component Sizing and Rating<br>Summary   |       |

| III. SIMULATION                                                                                        | 42    |

| Simulation Design<br>Design Topology Model<br>Simulation Controls<br>DC/DC Stage Simulation<br>Summary |       |

| Table of Contents (Continued) |  |

|-------------------------------|--|

|                               |  |

|        |                                        | Page |

|--------|----------------------------------------|------|

| IV.    | EXPERIMENTAL HARDWARE SETUP            | 64   |

|        | Critical Equipment                     | 64   |

|        | Support Equipment                      |      |

|        | Measurements and Feedback              |      |

|        | Fault Protection                       |      |

|        | Hardware Issues and Troubleshooting    | 86   |

|        | Summary                                |      |

| V.     | EXPERIMENTAL SOFTWARE SETUP            | 97   |

|        | DSPIC30F2020 PIC <sup>®</sup> Overview |      |

|        | Microcontroller Module Setup           |      |

|        | Charging Mode Controller               |      |

|        | Discharging Mode Controller            |      |

|        | Microcontroller Ancillary Functions    |      |

|        | Summary                                | 107  |

| VI.    | RESULTS AND DISCUSSION                 | 110  |

|        | Charging Mode Results                  | 110  |

|        | Discharging Mode Results               |      |

|        | Summary                                |      |

| VII.   | CONCLUSIONS AND CONTINUING STUDY       |      |

|        | Conclusions                            |      |

|        | Recommendations for Continuing Study   |      |

| APPENI | DICES                                  |      |

|        |                                        | 104  |

| A:     | Microcontroller Code                   |      |

| B:     | Experimental Setup Pictures            | 145  |

| REFERE | NCES                                   |      |

### LIST OF TABLES

| Table |                                                     | Page |

|-------|-----------------------------------------------------|------|

| 2.1   | IEC 61000-3-4 Current Harmonic Limitations          | 27   |

| 5.1   | Microcontroller Digital I/O Functions               | 100  |

| 6.1   | Charging Mode True Power Factor and THD             | 118  |

| 6.2   | Charging Mode Simulated and Experimental Efficiency | 119  |

| 6.3   | Charging Mode with DC/DC Stage Simulation Results   | 122  |

| 6.4   | Discharging Mode THD and V <sub>AC</sub> Magnitude  | 126  |

### LIST OF FIGURES

| Figure | Page                                                                           |

|--------|--------------------------------------------------------------------------------|

| 1.1    | Typical US Residential Electric Service                                        |

| 1.2    | Simulated Rectifier Voltage and Current10                                      |

| 1.3    | Typical PFC Boost Rectifier                                                    |

| 1.4    | Tyco Dual Boost PFC Rectifier                                                  |

| 1.5    | Zero Voltage Transition PFC Boost Rectifier16                                  |

| 1.6    | Interleaved Full Bridge Rectifier with Voltage Doubler17                       |

| 1.7    | Combination AC to DC Converter and Motor Inverter                              |

| 1.8    | Bidirectional PFC Boost Rectifier with Capacitor<br>Midpoint Ripple Mitigation |

| 1.9    | Bidirectional PFC Boost Rectifier with Third Leg<br>Inductor Ripple Mitigation |

| 1.10   | Simple Bidirectional PFC Boost Rectifier                                       |

| 2.1    | Charging Mode Block Diagram                                                    |

| 2.2    | Discharging Mode Block Diagram25                                               |

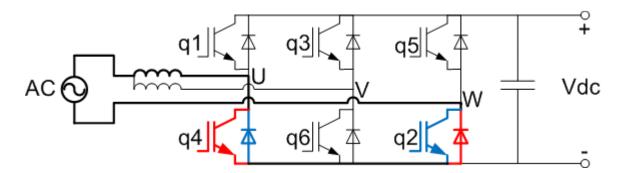

| 2.3    | Dual Channel PFC Boost Rectifier and Inverter                                  |

| 2.4    | PFC Rectifier Spooling Paths                                                   |

| 2.5    | PFC Rectifier Current Path during Capacitor Charging                           |

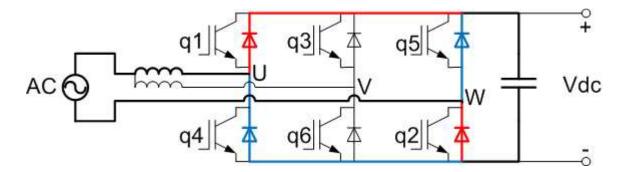

| 2.6    | Discharging Mode Operation                                                     |

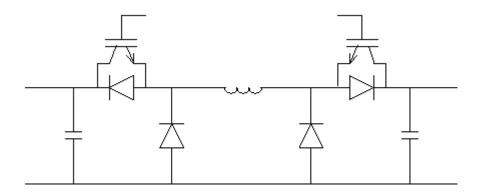

| 2.7    | DC/DC Stage Topology                                                           |

| 3.1    | IGBT 6-pack Model                                                              |

| 3.2    | Electrical Circuit Model                                                       |

# List of Figures (Continued)

| Figure | Page                                                          |

|--------|---------------------------------------------------------------|

| 3.3    | Charging Mode Model                                           |

| 3.4    | Discharging Mode Model                                        |

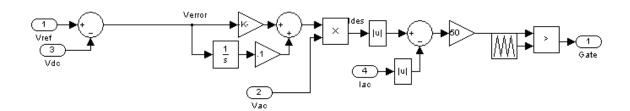

| 3.5    | SPWM Current Control Block Diagram                            |

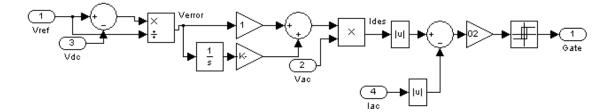

| 3.6    | Hysteresis Current Control Block Diagram                      |

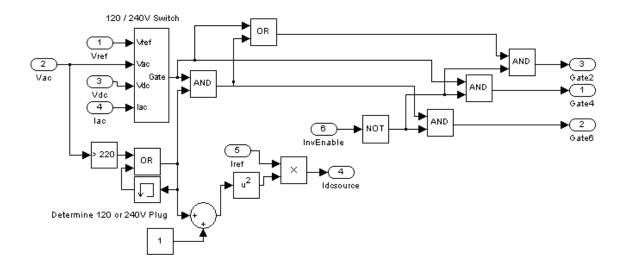

| 3.7    | Gate Selection Logic                                          |

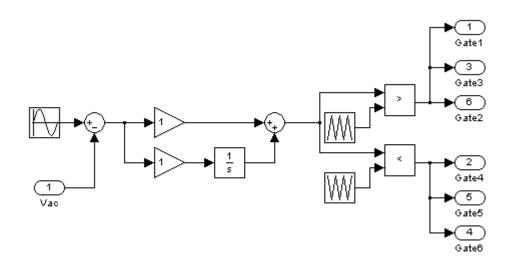

| 3.8    | Inverter Control Block Diagram                                |

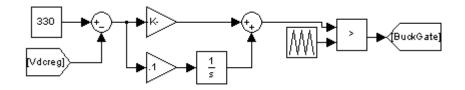

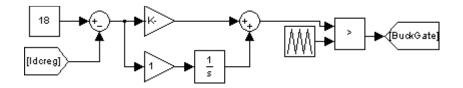

| 3.9    | DC/DC Stage Model                                             |

| 3.10   | DC/DC Stage Voltage Control Block Diagram                     |

| 3.11   | DC/DC Stage Current Control Block Diagram                     |

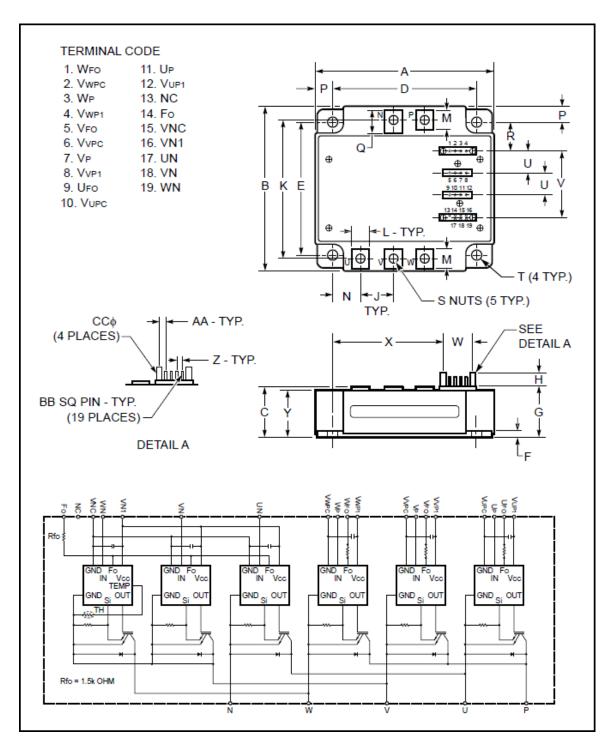

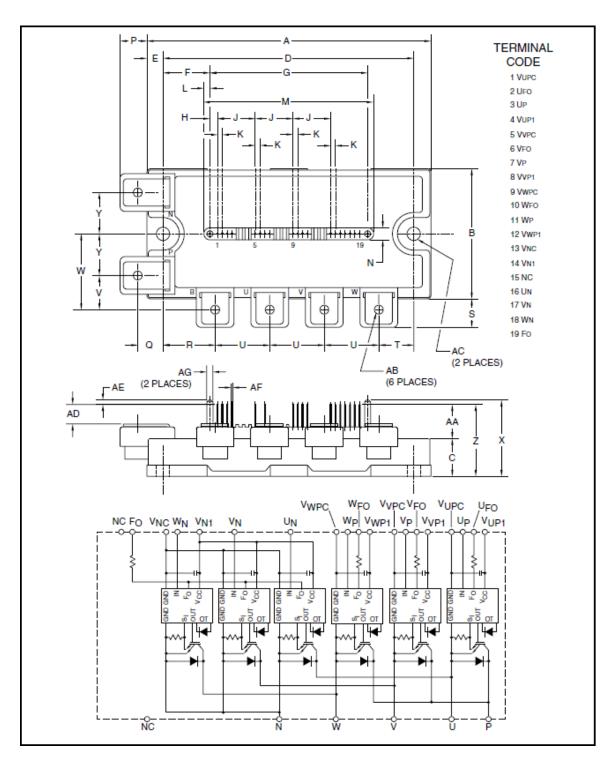

| 4.1    | Mitsubishi <sup>®</sup> Intelligent Power Module PM75CVA12065 |

| 4.2    | Powerex <sup>®</sup> Intellimod <sup>®</sup> PM50CLA060       |

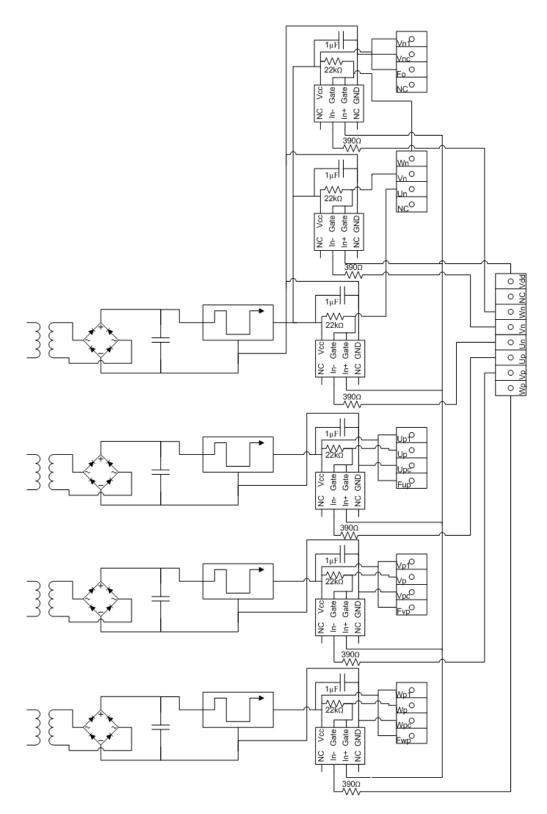

| 4.3    | Gate Driver Circuit Diagram74                                 |

| 4.4    | Digital Switching Circuit Diagram75                           |

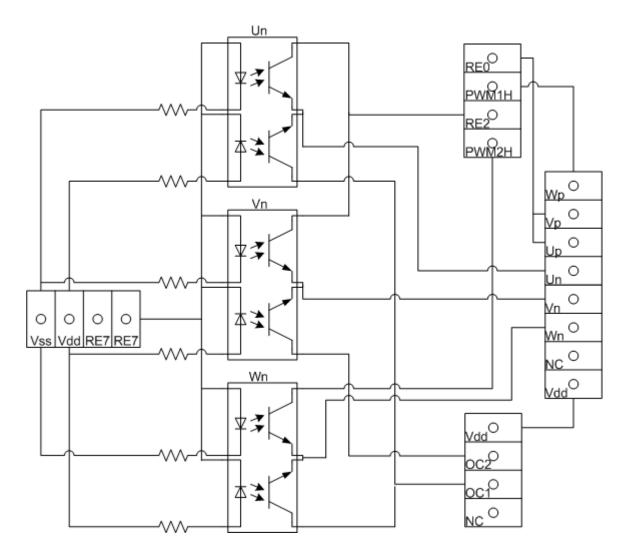

| 4.5    | Optocoupler Gate Switching Circuit Diagram                    |

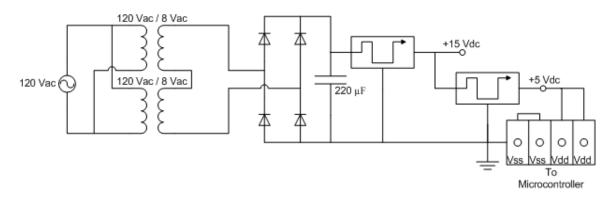

| 4.6    | Power Supply Circuit Diagram                                  |

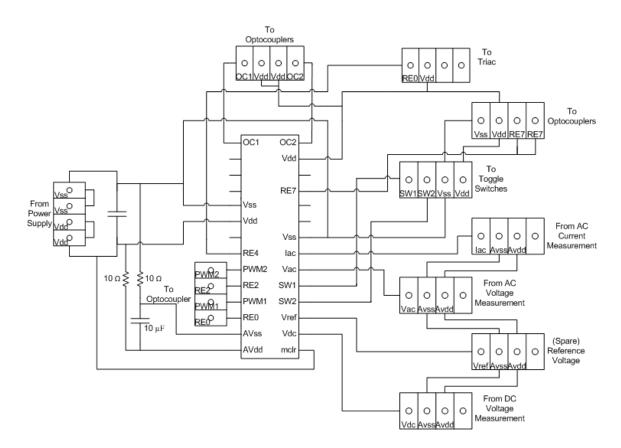

| 4.7    | Microcontroller Board Layout                                  |

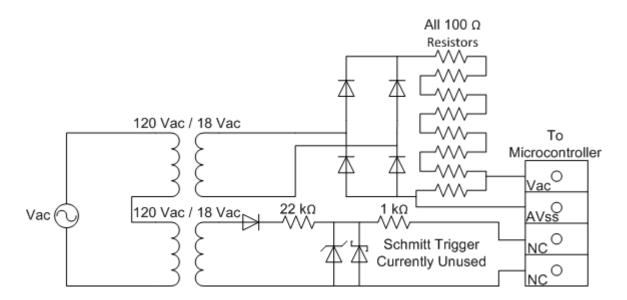

| 4.8    | AC Voltage Measurement Circuit                                |

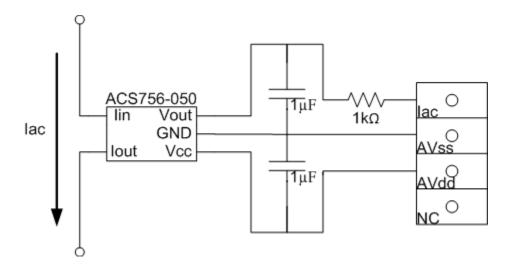

| 4.9    | AC Current Measurement Circuit                                |

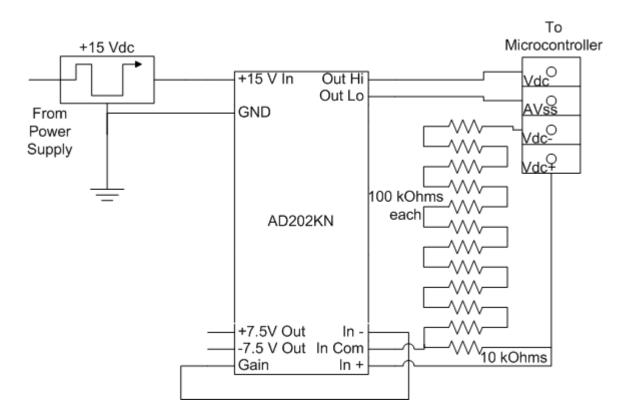

| 4.10   | DC Voltage Measurement Circuit                                |

| 4.11   | IGBT 6-pack Diode Failure Simulation Results                  |

# List of Figures (Continued)

| Figure | Page                                                     |

|--------|----------------------------------------------------------|

| 4.12   | Damaged IGBT 6-pack                                      |

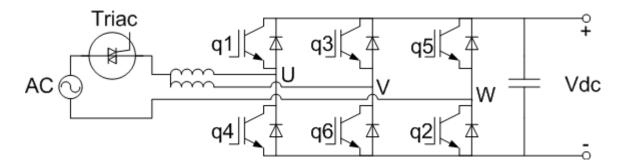

| 4.13   | Modified 240 V <sub>AC</sub> Charging Mode Configuration |

| 4.14   | Modified Discharging Mode Configuration                  |

| 4.15   | Slow Capacitor Charge Triac                              |

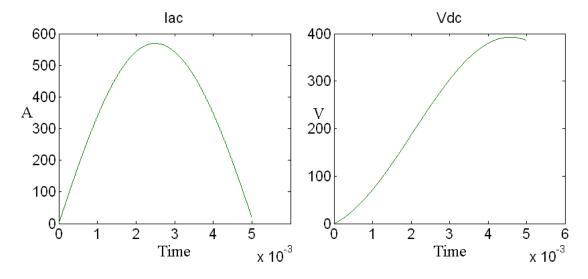

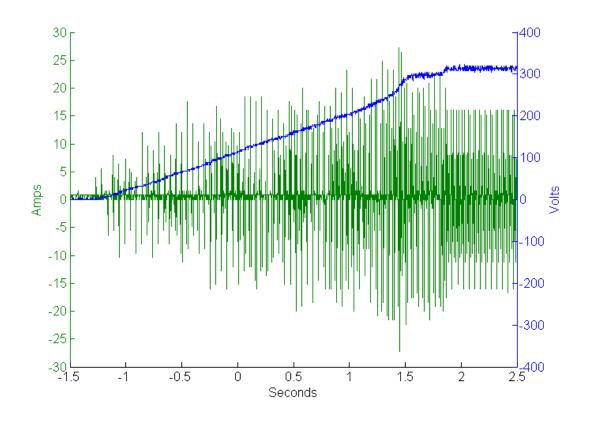

| 4.16   | Slow Startup Capacitor Voltage and Input Current         |

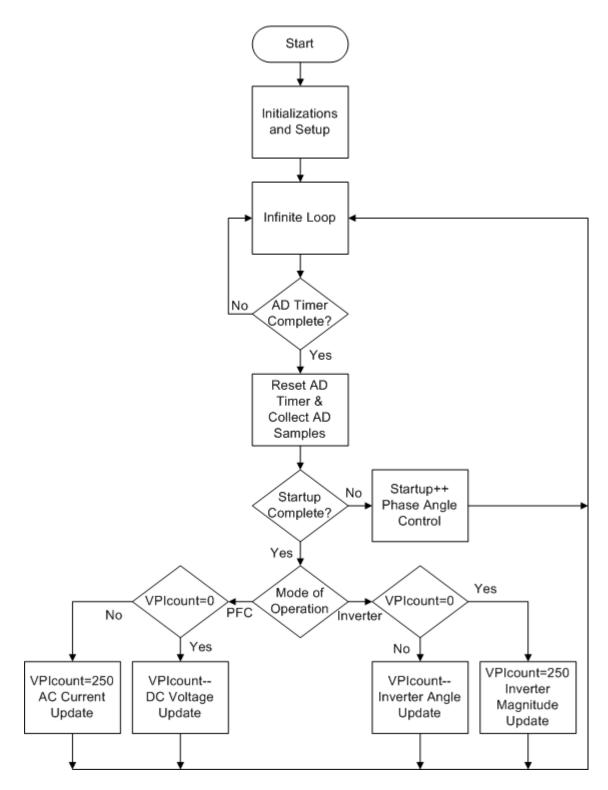

| 5.1    | Microcontroller Program Flowchart                        |

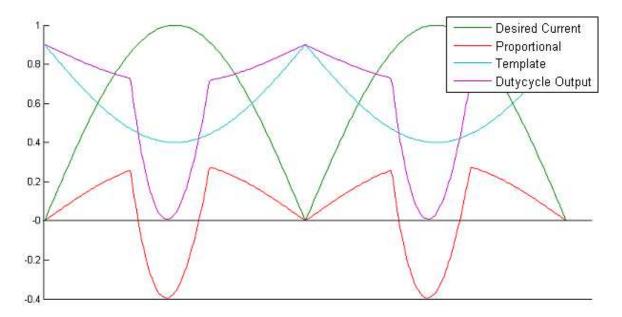

| 5.2    | Duty Cycle Creation Components                           |

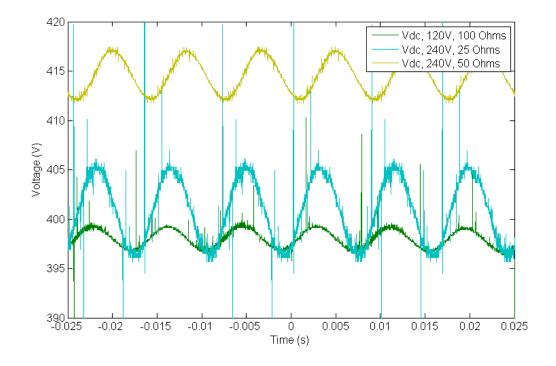

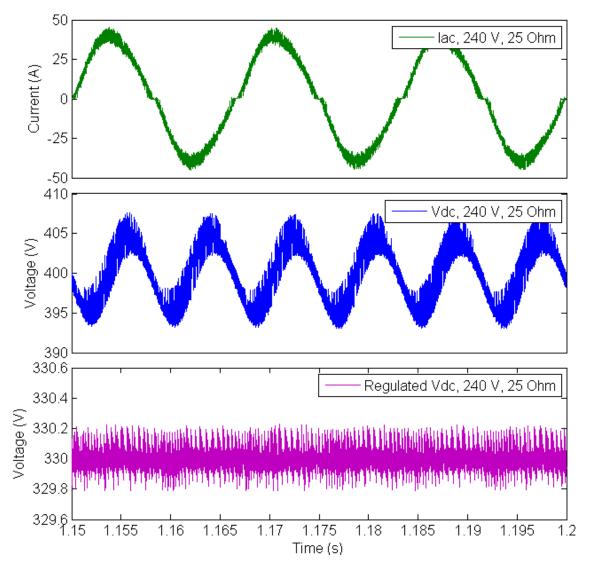

| 6.1    | Charging Mode Simulated DC Bus Voltages                  |

| 6.2    | Charging Mode Experimental DC Bus Voltages               |

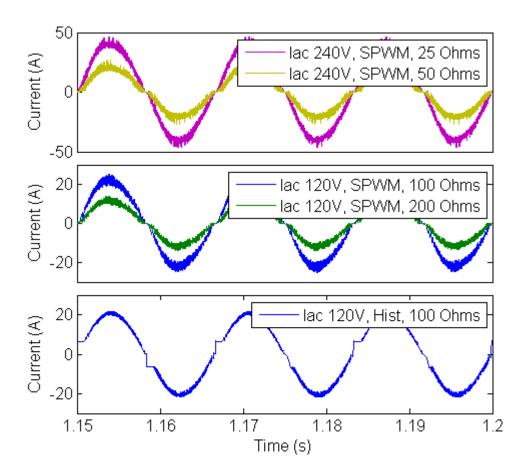

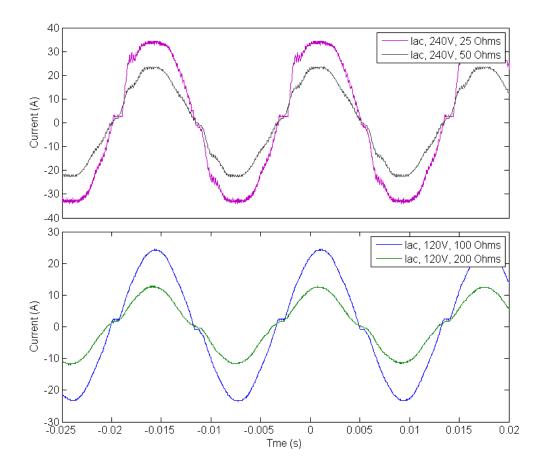

| 6.3    | Charging Mode Simulation AC Currents114                  |

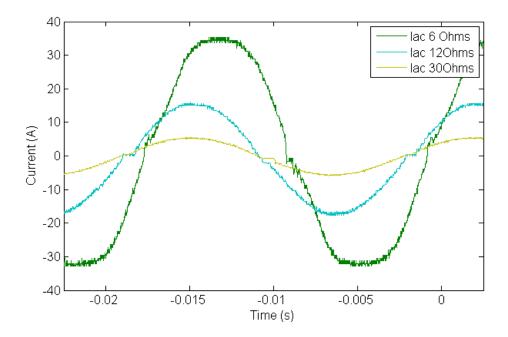

| 6.4    | Charging Mode Experimental AC Currents115                |

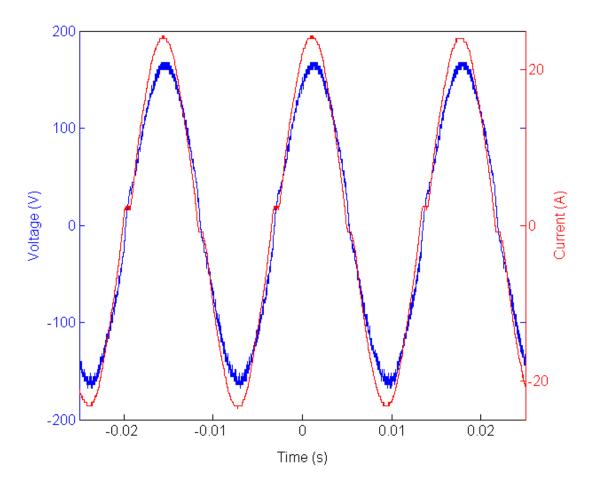

| 6.5    | Charging Mode Experimental AC Current and Voltage117     |

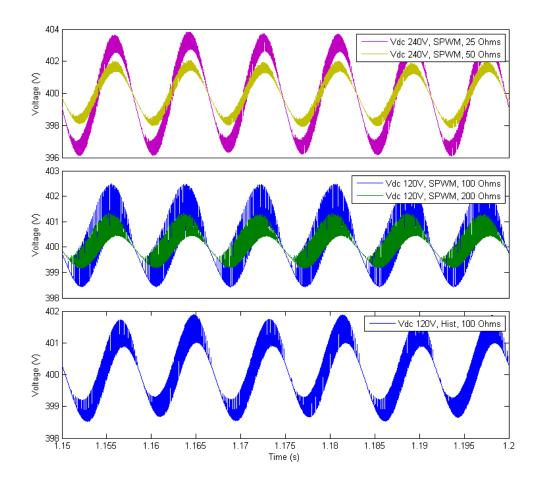

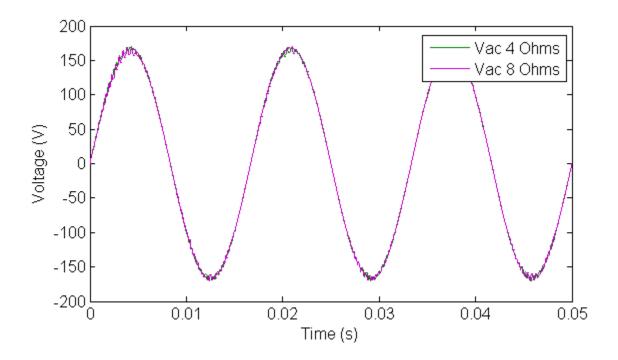

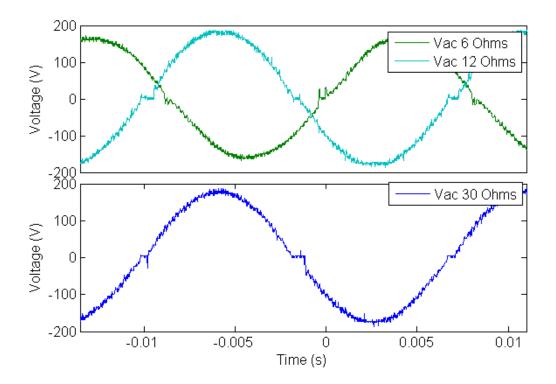

| 6.6    | Discharging Mode Simulated AC Voltages                   |

| 6.7    | Discharging Mode Simulated AC Voltages                   |

| 6.8    | Discharging Mode Experimental AC voltages124             |

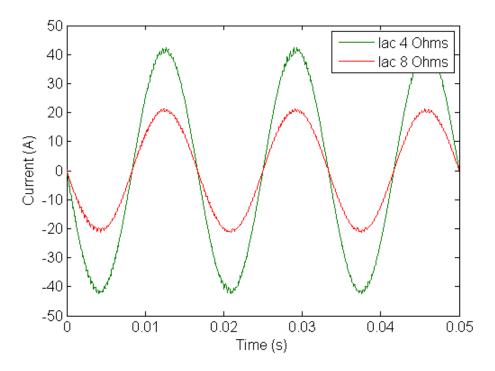

| 6.9    | Discharging Mode Simulated AC Currents                   |

| 6.10   | Discharging Mode Experimental AC Currents                |

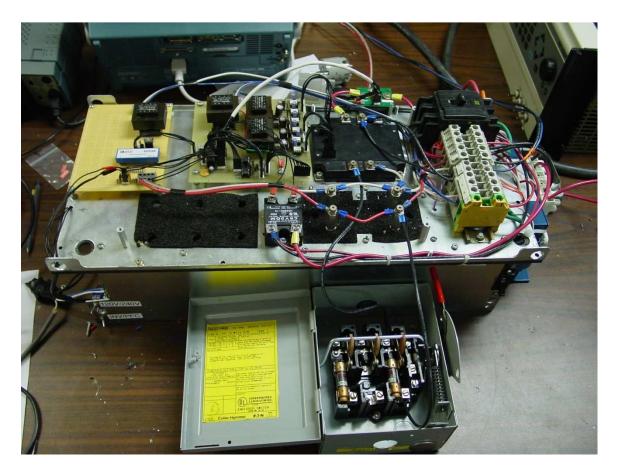

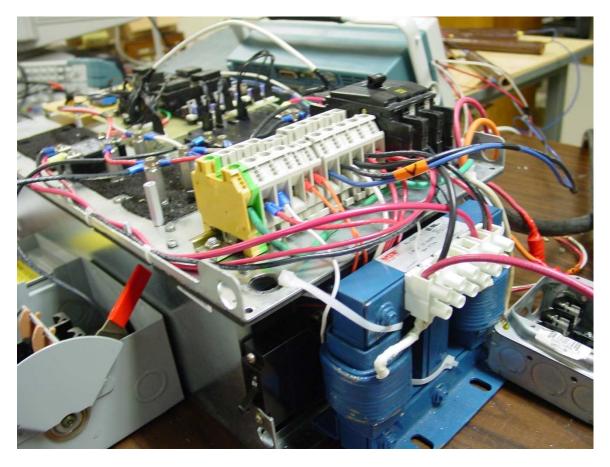

| B.1    | Overview                                                 |

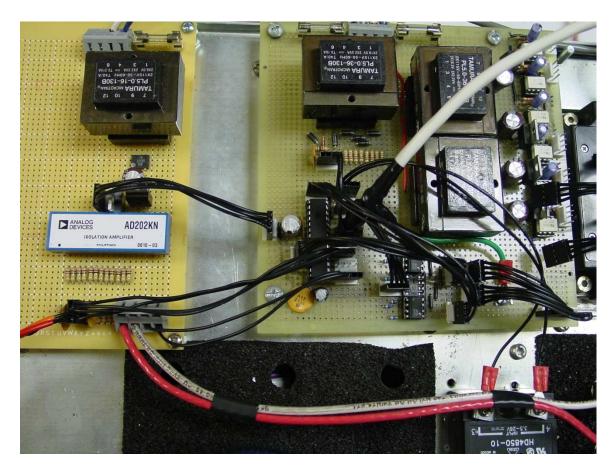

| B.2    | Microcontroller, AC and DC Measurements                  |

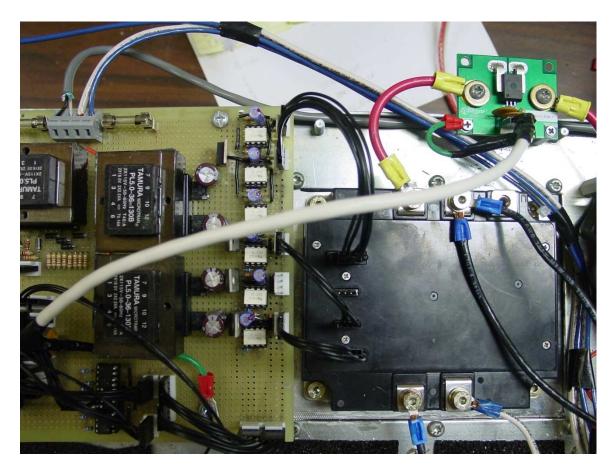

| B.3    | Hall Effect Sensor, Gate Drivers and IGBT 6-pack147      |

# List of Figures (Continued)

| Figure |                                    | Page |

|--------|------------------------------------|------|

| B.4    | Toggle Switches and Fan            | 148  |

| B.5    | Filter, Terminal Block and Breaker | 149  |

#### CHAPTER ONE

#### BACKGROUND

This thesis presents a modification of existing technology for a power converter designed specifically for the charging and discharging of a PHEV battery, herein called the Dual Input Bidirectional Power Converter (DIBPC). This chapter first provides the motivation driving need for this technology. Next, the many aspects of the problem are discussed. Once the problem is laid out, the power factor correcting rectifier is introduced as a solution. Finally, the existing technologies used to address these issues and accomplish these goals are considered and the pros and cons for each technology are weighed.

#### **Motivation**

Recent improvements in key technologies, including batteries and power electronics, have provided the technological means to the construction of hybrid electric vehicles. However, the technical superiority of hybrid electric vehicles has not solely moved them into the mainstream automotive market. Social and political trends have played a vital role in creating a popular niche for the hybrid electric vehicle.

For a long time now, the US has relied on large amounts of petroleum imports to supply gasoline and diesel to the transportation sector. As a result of this, many people are looking for ways to reduce their petroleum consumption. Hybrid electric vehicles have helped to provide a way for many people to do this. Reliance on an imported petroleum is not the only sociopolitical factor which has proven to be favorable for the advancement of the hybrid electric vehicle. As more people are becoming aware of their environmental impact, they are looking for many ways to reduce their environmental footprint. One of the most obvious solutions available to most people is to reduce the use of internal combustion engines, a primary consumer of petroleum. The burning of gasoline or diesel produces various toxic and greenhouse gases which have been attributed to global climate change.

The success of the hybrid electric vehicle in both domestic and foreign markets has assured its continued place in the automotive industry. The hybrid electric vehicle incorporates an electric motor and generator along with some power electronics and a large battery to provide a more efficient alternative to a vehicle with only a combustion engine.

The hybrid electric vehicle comes in two forms. The first, and most common, is the parallel hybrid electric vehicle. The parallel hybrid electric vehicle is the most common because it is the most similar to a traditional combustion engine powered vehicle, and it is typically the cheapest. The parallel hybrid vehicle uses both an electric motor and the combustion engine to provide power directly to the wheels. Because the combustion engine provides power directly to the wheels, a transmission is still needed in this configuration. The battery is charged from an electric motor during regenerative braking and from power provided by the combustion engine when needed.

The second form of the hybrid electric vehicle is the series hybrid. The series hybrid electric vehicle is more closely related to a purely electric vehicle than a

2

combustion engine vehicle. The series hybrid electric vehicle, while being simpler in concept, is more expensive to construct. The series hybrid uses an electric motor only to provide power to the wheels. The combustion engine is only used to provide power to charge the batteries. One of the advantages of this configuration is that there is no need for a transmission. Series hybrid electric vehicles are currently in use in heavy equipment. Locomotives and large ships already use the series hybrid layout where they use a diesel generator to power electric motors. Because the engine is only used to generate electricity, it can be designed to work in a very small power band, increasing the operating efficiency of the combustion engine.

Hybrid electric vehicles provide a more efficient alternative to a pure combustion engine. They do not, however, release the dependence upon petroleum. If hybrid electric vehicles can be viewed as the first step towards achieving that aim, plug-in hybrid electric vehicles (PHEVs) can be viewed as the second step towards that same goal. A PHEV is, in its most basic form, a hybrid electric vehicle with the ability to recharge the battery from utility supplied AC power. A PHEV generally follows the same configuration as a series hybrid, with a couple of important differences. A PHEV generally contains a significantly larger battery along with power electronics that allow the battery to be charged from an external electrical power source, the power grid.

While PHEVs are not yet in full-scale production from a major automotive manufacturer, conversions and custom made PHEVs by small specialized companies can be obtained. A PHEV has all the advantages of a series hybrid electric vehicle with the additional advantage of having an "electric-only" range that is subsidized from the power

3

grid. Based on tests with existing conversion vehicles, PHEVs have easily achieved over 100 mpg by utilizing the battery charge from the power grid [1].

As the first PHEVs are mass produced and marketed, they are expected to have an electric only driving range that is sufficient to encompass the daily commute of most drivers. This will allow a typical commuter to drive to and from work with little need to use the combustion engine. If the driver then charges the PHEV each night before work, theoretically the majority of the driving will use just the energy from the grid. While PHEVs still rely on another form of energy (typically gasoline), they enable future technologies to supplant that as they become available.

As the power grid becomes cleaner from the use of renewable energy and alternative forms of energy, this means the electric charge on the PHEV will further reduce the production of pollutions and greenhouse gases associated with burning fossil fuels. As battery and power electronic technology improves, this will also increase the length of the electric driving range and further reduce the use of the combustion engine in the vehicle. The current state of PHEV technology and the predicted road of future progress in this field have made the prospects of PHEVs as a prominent holder of the market share a very real likelihood in the near future.

Because so many PHEVs may soon be in production, details surrounding the charging and discharging of these PHEV batteries have given rise to many questions and possibilities. The Chevy Volt, one of the first PHEVs slated to go into production, will contain a battery with approximately 16 kWh of energy storage [2]. This is a significant amount of energy, which will require a significant amount of power and time to charge it.

Many concerns regarding the capacity of the existing power grid have been raised in light of this possible increased load. If many PHEVs are adopted, it could result in a significant boost in power consumption.

PHEVs are uniquely flexible – they can be charged at any time and then have the battery energy available for use when needed. If a charger was provided with feedback from the utility grid, it could govern the charger to operate at optimal off-peak times, limiting the additional peak power that must be supplied by the grid. If a charger is made sufficiently adaptable, it could use supplied feedback from the grid along with a user programmable schedule to determine the best charging time during the day, making it "smart grid" enabled.

#### Problem Statement

There are several design issues surrounding the PHEV battery charger discussed in this section. On a high level, the constraints that most greatly affect the design of a PHEV battery charger are: the minimization of input current harmonics, the ability to accept 120  $V_{AC}$  and 240  $V_{AC}$  and the ability to transfer high power bidirectionally.

As more and more devices, including PHEVs, require a substantial amount of DC power, the need to control harmonic distortion arises. A typical "dumb" single phase AC – DC converter consists of a half-bridge or full-bridge set of diodes, which rectify AC to DC and charge a capacitor. The charging of a capacitor through diodes creates a large amount of input current harmonics. In sufficient quantity, harmonics can be detrimental

to almost every aspect of the power grid, including transformer derating, voltage drops and power losses in the distribution system.

In the US, IEEE develops the standards which govern things such as harmonic distortion; in Europe and elsewhere, IEC performs the same task. IEEE currently has no standards for harmonic content on end use devices; however IEC standards are in place which limit current harmonics. Total harmonic distortion (THD) is the standard measurement used to rate the amount of harmonic distortion present in a waveform. These standards impose limits on the amount of total harmonic distortion in the current (THD<sub>1</sub>). The details of these standards will be discussed in the next chapter.

In order to be flexible enough to operate internationally, adhering to harmonic standards is not the only requirement. A PHEV charger would also need to have a wide range of input voltages. Because most PHEVs would, assumedly, be charged in residences, residential voltage sources must be used. For the US, 120  $V_{AC}$  and 240  $V_{AC}$ , 60 Hz are the typical values and in Europe, 220  $V_{AC}$  50 Hz is the norm. Therefore this wide range of operating input voltages would be desirable. Because the PHEV charger would be charged in a residential application, typical residential electrical power limitations apply. In the US, a typical circuit breaker on a 240  $V_{AC}$  system would be 30 A. Using this as a limitation for the power that can be converter by the PHEV charger, 7.2kW of input power would be the power limitation at 240  $V_{AC}$ .

If the development of PHEV technology continues to mature, a unique opportunity for PHEVs exists to benefit the stability of the power grid. If a complete and uniform set of standards are developed for safety and compatibility, PHEVs could also

provide a means for distributed energy storage through the power grid. If a large number of vehicles with partially or fully charged batteries are available on the grid during peak hour loading, utility companies could use those batteries to improve grid stability and reduce the need for low-efficiency peak-time generators.

In order for the utility company to use these batteries as distributed energy storage, the power converters between the vehicle and the utility grid would have to be bidirectional. Bidirectional power flow between the utility and the vehicle creates several issues that have to be addressed. One of the most important issues is safety. A house with a vehicle discharging power to the grid appears as a distributed energy source that is not known to the utility company. Among other issues, not always knowing the direction of the power flow in a distribution line can leave doubt as to whether or not a circuit breaker or switch can actually protect the system it intends to protect or disconnect.

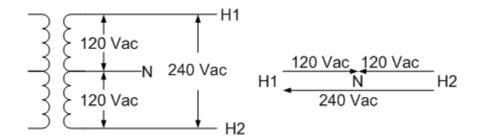

In the US, residential 240  $V_{AC}$  is provided from a transformer with a center tapped neutral. Therefore two voltage magnitudes are available from the same transformer, 120  $V_{AC}$  and 240  $V_{AC}$ . Two 120  $V_{AC}$  lines are available, each with opposite polarity relative to the neutral. A transformer diagram and a phasor diagram of this can be seen in Figure 1.1. For the PHEV charger to operate bidirectionally, it needs to provide support for this installation.

7

Figure 1.1: Typical US Residential Electrical Service

A power converter which can meet all of these tasks needs to be considered. A power converter needs to be able to charge a very high storage battery, perhaps 16 kWh or more. The power converter needs to be able to charge it quickly and without exceeding any current or future harmonic standards. Because the design is aimed at a typical residential application, the converter needs to operate within the bounds of a typical installation for 120  $V_{AC}$  or 240  $V_{AC}$  in the US or 220  $V_{AC}$  in Europe. Finally, the converter needs to be able to discharge the battery and invert it for use as backup power or auxiliary power when the power grid is disconnected. The next section discusses how existing technology would meet these goals and the shortcomings they may have.

#### Power Factor Correcting Technology

PHEV battery chargers are not anything completely unique. The concept of a high power AC to DC rectifier is not new. Existing rectifiers are currently used in many applications where batteries are needed to be charged or where a DC motor or variable frequency drive is operated. Due to the limitations placed on harmonic content and the side effects created by harmonic content, most large power rectifiers incorporate some means of power factor correction.

The term power factor correcting or power factor correction (PFC) technology refers to a device whose function is to improve the true power factor. True power factor, as opposed to displacement power factor, is defined as  $\frac{P}{|S|}$  or  $\frac{Real Power}{Apparent Power}$ . Displacement power factor is defined as  $cos(\theta_{v1} - \theta_{i1})$ , where  $\theta_{v1}$  and  $\theta_{i1}$  are the phase angles of the fundamental frequency of the voltage and the current, respectively. For a perfectly sinusoidal waveform, the displacement power factor and true power factor are the same. When harmonic content is present, however, these two values can vary greatly. The true power factor can be greatly reduced by the presence of harmonic content in either the voltage or the current.

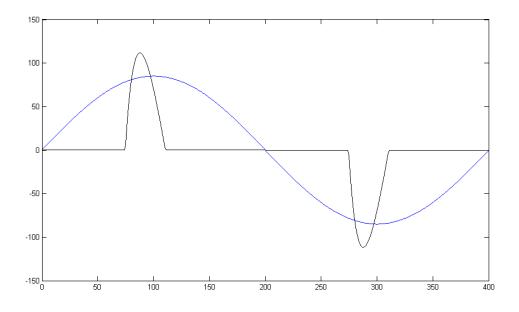

The difference between the true power factor and the displacement power factor is illustrated with two simulated waveforms in Figure 1.2. The blue waveform is a true sinusoidal waveform which represents the input voltage to a diode rectifier. The black waveform is a distorted waveform which represents the input current to a diode rectifier.

Figure 1.2: Simulated Rectifier Voltage and Current

The phase angles of the fundamental frequency for both of these waveforms are close to the same, only varying by about 8.5°; therefore the displacement power factor is 0.989. The true power factor, shown in Equation 1.1, is calculated by dividing the real power by the apparent power, which contains the harmonic content.

$$pf = \frac{P}{|S|} = \frac{V_{RMS(1)} * I_{RMS(1)} * \cos(\theta)}{V_{RMS} * I_{RMS}} = 0.54$$

(1.1)

The harmonic content present in the distorted current waveform has created a true power factor that is much lower than the displacement power factor. As the true power factor gets closer to 1, the harmonic content present in both the voltage and the current is reduced. Therefore when a device has power factor correction, it not only improves the phase shift between the voltage and current, but also reduces the harmonic content.

Power factor correcting (PFC) rectifiers are designed to convert AC to DC without producing the large amount of harmonics associated with a typical diode rectifier and DC filter capacitor. A PFC rectifier can be constructed as a passive device or an active device. Passive PFC rectifiers contain a low pass or a band pass filter to improve the true power factor by filtering out some of the undesirable harmonics. These produce very limited results, however, due to the hard to filter low frequency harmonics typically created by a diode rectifier. Because active PFC rectifiers typically result in much better power factor correction than passive PFC rectifiers, they are favored in applications requiring a significant power factor improvement.

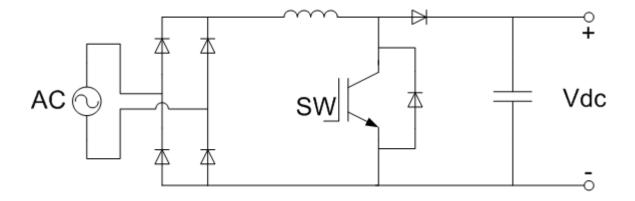

An active PFC rectifier is typically designed by taking a rectifier and attaching a DC to DC converter. In order to illustrate the operation of a PFC rectifier, one of the most basic PFC rectifier designs is considered. This basic PFC rectifier design consists of a diode rectifier followed by a DC to DC boost converter. The boost converter is made up of an inductor, a diode, a switch (such as an IGBT or MOSFET) and a capacitor. The circuit can be seen in Figure 1.3.

Figure 1.3: Typical PFC Boost Rectifier

A typical rectifier only charges the capacitor when the input voltage is greater than the capacitor voltage, near the peak of the voltage waveform. This only allows current to flow near that peak. In order to improve the power factor, current needs to flow at all points in the waveform, mimicking the voltage. In order to do this, the inductor is switched on and off very quickly. This allows current to spool in the inductor when the switch is closed. When the switch is closed, the voltage quickly rises across the inductor ( $V_L = L * \frac{di_L}{dt}$ ). This rise in voltage forward-biases the diodes and allows current to flow into the capacitor. By modulating the switch, the input current can be made to follow the input voltage.

One undesirable effect of improving the input current waveform this way, is the DC voltage ripple present at twice the line frequency. The DC voltage ripple for a 60 Hz input voltage would be 120 Hz. This voltage ripple can be explained by considered the power balance. Because the current waveform now looks like the voltage waveform, the instantaneous power is greatest at the peak of these waveforms. This input power

decreases the closer you get to the zero crossing, and eventually reaches zero before increasing again. This varying input power results in a fluctuation of the voltage of the DC bus capacitor because the output power should remain essentially constant.

To mitigate this dc voltage ripple at twice the line frequency, some PFC rectifiers incorporate another DC / DC converter as a second stage. This DC / DC converter operates at a switching frequency fast enough to respond to the changes of the DC bus voltage resulting from the voltage ripple. The second stage DC / DC converter can easily provide a DC voltage output with very low ripple. Some PFC rectifier topologies are specifically designed to reduce the DC voltage ripple that is present without the addition of another DC / DC stage. These and other PFC rectifier technologies will be discussed in the following section.

#### Existing Technology

The present state of existing technology is a somewhat open ended question, in this field. Because PHEVs are not yet readily available in the current market, much of the PHEV charger designs are proprietary and/or contracted from other suppliers, . Because so many of the designs used for these applications are trade secrets, very little documentation regarding them is available. For this reason, the list of existing technology contains only the designs that are available through corporate or academic publications. Some of the relevant designs can be seen below. Existing converters that could be used for PHEV battery charging applications can be broken down into two distinct groups. They can be distinguished based on their ability to discharge the battery back to a AC voltage. Therefore the following list will be broken down into two groups as well. First, the PFC rectifiers which can only operate unidirectionally to charge the battery are considered. While Unidirectional PFC rectifiers will not work for this application, two are discussed to demonstrate some of the techniques used to correct the power factor of a rectifier circuit. Next, the converters which can be operated bidirectionally (PFC rectifiers and inverters) are discussed.

The most common unidirectional PFC rectifier circuit can be seen above in Figure 1.3. This PFC rectifier is the most basic, containing the fewest components, and is therefore the cheapest and easiest to control. The drawbacks of this design, however, are the inefficiency, the inability to perform bidirectionally and the limited power factor correcting ability. This design operates with a lower efficiency because more semiconductor junctions are crossed. This design is generally used for low power, low cost applications. Because of these limitations, it is not suited for this application.

Now, one other, more specific application oriented PFC rectifier is examined. Figure 1.4 shows a PFC rectifier designed by Tyco Electronics [3]. This is a production system that can be bought as a PFC rectifier assembly. This is an excellent unidirectional PFC rectifier with a simple, cost effective and efficient design.

This topology is designed to minimize the number of semiconductor junctions that are crossed. It is designed to operate at up to 6kW, 160kHz switching frequency, 400V DC output. Experimentation has shown a 97.4% efficiency with an input voltage

of 230V AC and a 94.8% efficiency with 120V AC input. For unidirectional PFC rectifier applications, this design would be the most suited for the power levels, cost and efficiency requirements for the power converter. This design, however, does not allow for the flow of power in the opposite direction, thus is cannot be used for this application.

Figure 1.4: Tyco Dual Boost PFC Rectifier

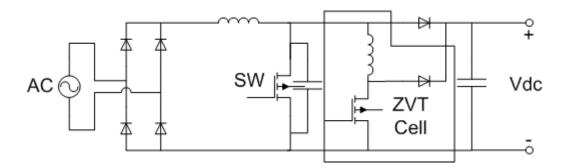

The next design is very similar to the first PFC boost rectifier. It simply contains a couple more components. This topology was of interest because of the zero voltage transition cell, highlighted in Figure 1.5. Because this topology uses resonance to drive the voltage across the switch nearly to zero before switching, it has better switching characteristics and improved efficiency [4]. However, this ended up not being applicable due to its inability to operate bidirectionally.

Figure 1.5: Zero Voltage Transition PFC Boost Rectifier

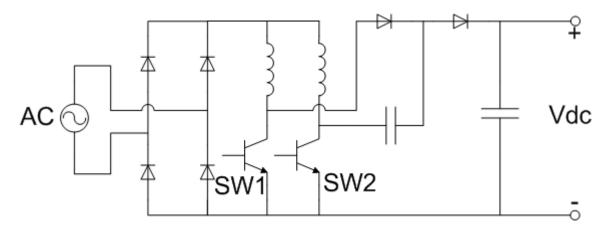

The interleaved full bridge rectifier with voltage doubler, seen in Figure 1.6, is an interesting solution. With this scheme, the converter can provide additional capability to double the voltage when rectifying 120V versus 240V AC by introducing a second capacitor, the boost capacitor. This increases efficiency with 120V AC input. However, there are a couple of serious drawbacks. To make this scheme operable bidirectionally, a non-trivial amount of semiconductor switches would have to be added and the bridge rectifier would have to be a fully controlled bridge with IGBTs. This would prove to be overly complicated and cost-prohibitive.

Figure 1.6: Interleaved Full Bridge Rectifier with Voltage Doubler

There are a wide array of unidirectional PFC rectifiers currently utilized, however, not nearly as many bidirectional PFC rectifiers. Next, some of the existing bidirectional PFC rectifiers are examined. A comprehensive review of all the significant PFC rectifiers, including bidirectional rectifiers, was performed in 2003 [5]. This review included several bidirectional PFC boost rectifiers, and those are discussed below. Most of the bidirectional designs are referenced from this comprehensive review.

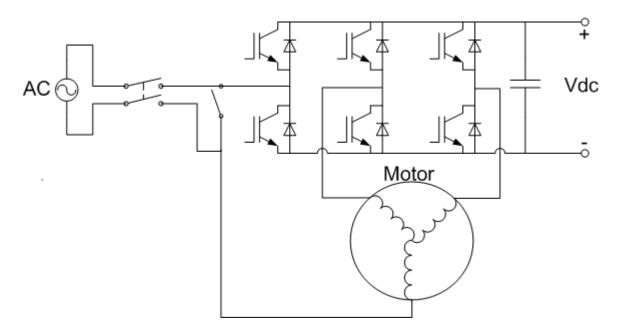

For PHEV specific applications, some implementations have shown a combined AC to DC bidirectional converter and motor inverter [6]. This is an interesting design because it uses the motor windings as the spooling inductors for the PFC rectifier circuit. Seen below in Figure 1.6, the converter can be used for multiple purposes. When the vehicle is in operation, the converter is used as a DC to AC inverter for motor control. However, when the vehicle is being charged, the converter acts as an AC to DC PFC rectifier.

The contactors shown in K1, K2 and K3 allow the converter to utilize the windings of the motor as a PFC rectifier choke (inductor) for spooling current. Because this topology is designed to be used as a DC to AC inverter for motor control, it could also operate bidirectionally to discharge the battery back to the residential AC. This topology provides a unique method to reuse existing components, however at this point the design is simply a concept that depends on unknown components inside of the PHEV.

Figure 1.7: Combination AC to DC Converter and Motor Inverter

Figures 1.8 and 1.9 show similar bidirectional PFC boost rectifiers. The rectifier seen in Figure 1.8 has the addition of a third IGBT leg. This third IGBT leg allows the addition of the capacitor midpoint. This third leg can be switched in such a way as to provide mitigation for the DC voltage ripple seen at twice the line frequency [5]. The topology seen in Figure 1.9 has an inductor connected between two of the line IGBT legs.

This inductor serves the same purpose as the capacitors seen in Figure 1.8 by spooling current through the third IGBT leg to supply current which cancels out the current ripple in the capacitor. These designs would not require a second stage DC to DC converter. These designs are also not optimized for multiple input voltages, however, concentrating instead on filtering the dc output voltage.

Figure 1.8: Bidirectional PFC Boost Rectifier with Capacitor Midpoint Ripple Mitigation

Figure 1.9: Bidirectional PFC Boost Rectifier with Third Leg Inductor Ripple Mitigation

The most basic bidirectional PFC rectifier is shown below in Figure 1.10. This simple design effectively provides the AC to DC or DC to AC conversion, but is not the

most efficient design. It does not provide any filtering for the DC voltage ripple which is present at twice the line frequency. It also does not operate as efficiently at varying input line voltages as it does at its designed line voltage. This design would require a DC to DC converter to filter the ripple at twice the line frequency.

Figure 1.10: Simple Bidirectional PFC Boost Rectifier

While there are certainly other existing PHEV battery charger topologies, these are the most relevant and comparable topologies available in publications. Because of the specific design constraints of this PHEV battery charger, none of these optimally meet the design criteria. The basic bidirectional PFC boost rectifier seen in Figure 1.10 is the most closely suited to the needs of this application.

The design found in Figure 1.10 does not provide adequate flexibility for operation with multiple input voltages. The components for this topology would have to be designed to operate ideally at 240  $V_{AC}$ . For this reason, the efficiency at 120  $V_{AC}$

would be significantly lower than at 240  $V_{AC.}$  Also, when inverting, this topology could only invert to 120  $V_{AC}$  or 240 $V_{AC}$ .

#### <u>Summary</u>

This chapter discussed the background behind PHEVs and their relevance in today's world. The technology associated with the charging and discharging of the batteries and the technological problems that inherently need solutions were then considered. Finally, the existing technology that meets these goals was listed, along with the pros and cons of each.

Because none of these known existing technologies satisfactorily meets all the listed design constraints, a new bidirectional PHEV battery charger is proposed. The details of the constraints that govern the design along with the details of the design can be found in Chapter Two.

#### CHAPTER TWO

#### DESIGN OF THE DUAL INPUT BIDIRECTIONAL POWER CONVERTER

The existing technology offers several solutions to meet the goals of the PHEV battery charger and discharger. Through the study of the existing technology and comparisons of how it suits the existing need, a modified PFC rectifier design has been designed, simulated and constructed. This operation of the modified PFC rectifier design, herein called the Dual Input Bidirectional Power Converter (DIBPC) is discussed in detail in this chapter. First, the different stages and overall top down control scheme is discussed. Next, the constraints which govern the design are individually discussed followed by a detailed explanation of the design topology and operation. Finally, the method used for sizing and rating components is discussed.

#### Design Concept

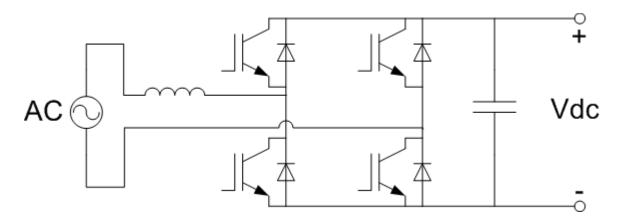

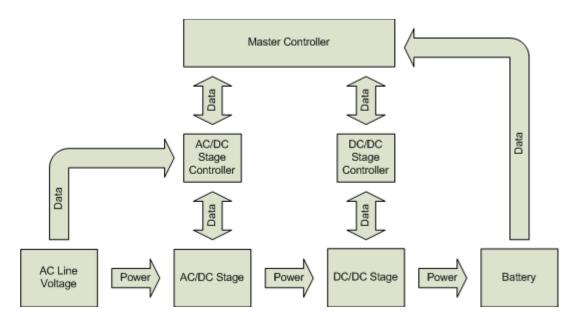

The DIBPC is designed in two stages that can be broken up according to their general function, an important concept to note when considering the design. One stage, the AC/DC stage, takes an AC voltage and provides a constant DC output voltage or takes a constant DC voltage and inverts to a 120  $V_{AC}$  output. The other stage, the DC/DC stage, takes a constant DC voltage and outputs a varying DC voltage to the battery or takes a varying DC voltage from the battery and outputs a constant DC voltage to the DC bus.

These two stages are both controlled by a single master controller. This master controller communicates directly with the battery, the AC/DC stage and the DC/DC stage of the DIBPC. Because the DIBPC is designed to operate with multiple battery types, the master controller must dictate the charging profile to both stages of the DIBPC. This controller must oversee the controllers for the two stages and ensure that they are providing the correct output to the battery in the charging mode,

Most batteries have two modes of operating during their charging. First, during the lower state of charges, they operate in a current limit mode. The voltage is varied so that the maximum current is reached and maintained. The other mode of operation is voltage limit mode. Once the battery nears its full state of charge, it will usually need to operate in the voltage limit mode, where the voltage is set to the peak value and the current will be variable below the maximum value to maintain voltage. These voltage and current limits are incorporated in the charging profile of the battery, which is stored in and controlled by the master controller.

The master controller would most likely be a controller that has a graphical user interface (GUI), such as Labview<sup>TM</sup>. This would allow the user to configure the charging profile easily based on the battery being used. If this was built for a production operation, then a microcontroller could be used to control it with a preset battery charging profile or multiple battery charging profiles that could be chosen between.

The DIBPC is capable of operating in two different modes. The mode of operation is either the charging mode or the discharging mode, depending on the flow of energy to or from the battery. In the charging mode, the master controller will control the DC/DC stage and set it to the correct voltage output. It will also ensure that the current in the AC/DC stage is not over the limit (this protection will also be redundantly provided in the AC/DC stage controller for faster operation). In the discharging mode, the master controller will ensure that the DC/DC stage is not operating the battery out of its state of charge limitation.

In the charging mode, the AC/DC stage is rectifying from AC to DC to constant DC voltage on the DC bus. The DC/DC stage is converting the constant DC bus voltage to the required battery DC voltage supplied from the master controller, as discussed later in this chapter. For a graphical explanation of the charging mode, see Figure 2.1.

Figure 2.1: Charging Mode Block Diagram

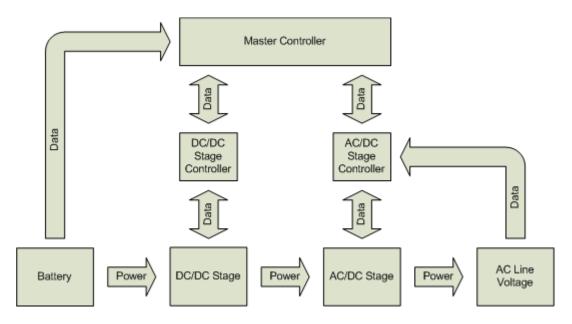

In the discharging mode, the DC/DC stage of the DIBPC is outputting constant DC voltage to the DC bus. The input to the DC/DC stage is the varying DC battery

voltage. In the discharging mode, the AC/DC stage is inverting the DC bus voltage to AC line voltage. The discharging mode block diagram can be seen below in Figure 2.2.

Figure 2.2: Discharging Mode Block Diagram

To make the DIBPC as flexible as possible, it is ideal to choose a DC bus voltage that is capable of charging many different types and styles of batteries. The battery with which the DIBPC is specifically designed to operate is a NiMH battery with a nominal voltage of 330 V<sub>DC</sub>. Many other batteries operate in the same nominal voltage region. In the charging mode the AC/DC stage of the DIBPC is designed to have an output voltage of 400 V<sub>DC</sub> to ensure the voltage remains high enough after the DC/DC stage to meet the maximum voltage limit for the battery. This voltage is chosen as a good median value which will allow lower voltage components to be used, yet still be capable of charging any battery with a required charging voltage up to about 380 V<sub>DC</sub>. The individual constraints of the charging mode are now considered. The system as a whole, including both stages, will have a variable DC output with a very low voltage ripple (ideally less than one volt) to nominally charge the battery. As discussed in the last chapter, the AC/DC stage has a large voltage ripple at a frequency equal to twice the line frequency. The DIBPC is designed to operate at 50 Hz or 60 Hz, so the ripple would be either 100 Hz or 120 Hz. The ripple magnitude is dependent upon the value of the filter capacitor, the input voltage and the load current. The DC/DC stage of the converter is designed to filter this ripple out, much like an active filter, while also providing a variable DC output voltage determined by the charging profile of the battery.

The second major constraint in the charging mode is the input current harmonic restrictions. In the US, there are currently no required limitations imposed on consumer device current harmonics, however, this may change in the future. There are international standards that do impose requirements on current harmonics and power factor which may eventually be applied in the US. Because products in the automotive industry such as this PHEV battery charger are usually designed and marketed for worldwide implementation, they generally meet the international standards everywhere they are implemented. Below, a couple of the most applicable standards are listed and described.

IEEE 519-1992 is an IEEE standard entitled "Recommended Practices and Requirements for Harmonic Control in Electrical Power Systems." This standard is directed at utility distribution systems and distribution systems within industrial plants. Although this standard does not directly relate to consumer devices, it still provides some insight into the expected limitations. IEEE 519, recommends limiting total voltage distortion to 3% of the fundamental and limiting total current distortion to 5% of the fundamental [7].

IEC 61000-3-4 (also the Euronorm (EN 61000-3-4) standard with the same number), entitled "Limitation of Emission of Harmonic Currents in Low-Voltage Power Supply Systems for Equipment with Rated Current Greater than 16 A," provides THD limitations for the input current [8]. This standard applies to the PHEV battery charger assuming the system is used within the jurisdiction of the IEC standards. The standards per harmonic are listed below in Table 2.1.

| Harmonic<br>Number | Admissible<br>Harmonic Current  | Harmonic<br>Number | Admissible<br>Harmonic Current  |

|--------------------|---------------------------------|--------------------|---------------------------------|

| n                  | %I <sub>n</sub> /I <sub>1</sub> | n                  | %I <sub>n</sub> /I <sub>1</sub> |

| 3                  | 21.6                            | 21                 | ≤0.6                            |

| 5                  | 10.7                            | 23                 | 0.9                             |

| 7                  | 7.2                             | 25                 | 0.8                             |

| 9                  | 3.8                             | 27                 | ≤0.6                            |

| 11                 | 3.1                             | 29                 | 0.7                             |

| 13                 | 2                               | 31                 | 0.7                             |

| 15                 | 0.7                             | <u>≥</u> 33        | ≤0.6                            |

| 17                 | 1.2                             |                    |                                 |

| 19                 | 1.1                             | Even               | $\leq 8/n \text{ or } \leq 0.6$ |

Table 2.1: IEC 61000-3-4 Current Harmonic Limitations

Because IEEE Std 519 is directed at utility and industrial distribution systems which would typically require the use of a transformer (low pass filter) before their end use, the harmonic limitations are much more stringent than IEC 61000-3-4. For this

application, IEC 61000-3-4 provides more realistic current limitations; so for this charger, it is important for the harmonic limitations seen in IEC 61000-3-4 to be met.

One important variation that was considered for this design is the input voltage. In the US, two options are available, 120  $V_{AC}$  or 240  $V_{AC}$  at 60hz. Outside the US, varying voltages and frequencies are used, from 100  $V_{AC}$  – 240  $V_{AC}$  and 50 Hz – 60 Hz. To make the system as flexible as possible, it is designed to work from 120  $V_{AC}$  – 240  $V_{AC}$  and at either 50 Hz or 60 Hz. To maximize the rate at which the battery can be charged, the power of the DIBPC is limited only by the amount of current that can safely flow in typical residential wiring, and therefore by the circuit breaker size. A typical 120  $V_{AC}$  breaker is 15 A and a typical 240  $V_{AC}$  breaker that may be available in a residence is 30 A. Therefore the input power limitations for 120  $V_{AC}$  and 240  $V_{AC}$  are 1.8kW and 7.2kW, respectively.

In the discharging mode, there are several constraints that must also be considered in the design. Because of the safety issues discussed in Chapter One, the DIBPC is designed to only operate in the discharging mode when the main residential breaker is open. This will avoid any safety issues that arise from connecting to the utility grid. Because typical residential connections in the US have a center tapped 240  $V_{AC}$  supply, inverting to both 120  $V_{AC}$  lines relative to the neutral point would be required to emulate this connection and supply power to both residential circuits

To avoid this, the decision to only invert to 120  $V_{AC}$  was made – however, the topology needs to be capable of outputting 240  $V_{AC}$  with an available neutral if this is deemed necessary in the future. This decision makes the discharging mode and the

DC/DC converter much simpler. Because two 120  $V_{AC}$  lines exist in a typical residential environment, they must both be powered individually. To do this, the DIBPC will supply the same 120  $V_{AC}$  phasing to each line. This will result in a line to line voltage of zero between the two 120  $V_{AC}$  and make all 240  $V_{AC}$  appliances unable to operate. Therefore in the discharging mode, the DC bus voltage is set to 200  $V_{DC}$ . This 200  $V_{DC}$  voltage is converted from the battery voltage in the DC/DC stage. The AC/DC stage takes that 200  $V_{DC}$  and then inverts it to produce 120  $V_{AC}$ .

On the practical side of things, the design needs to be simple and cost-effective. This includes minimizing the component count, correctly sizing the components and requiring the minimal amount of system feedback for optimum operation. Simplifying the design minimizes opportunities for unexpected problems and component failures, increasing reliability. Simplifying the control will minimize the chances of software glitches and require less processing power.

Finally, the system needs to be efficient. Power losses in a battery charger would be analogous to gasoline being spilled while filling a tank. The efficiency of charging the battery therefore directly affects the amount of energy from the grid that is required per mile of driving, similar to a loss in the miles per gallon (mpg) of a combustion engine vehicle.

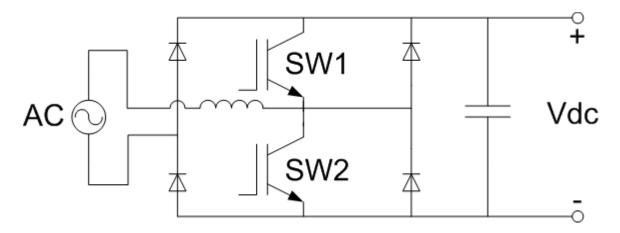

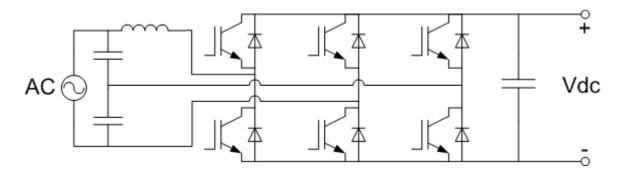

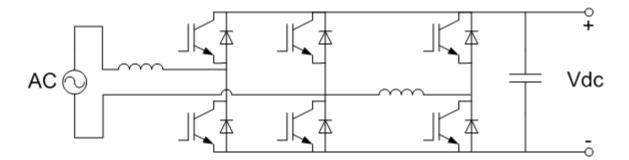

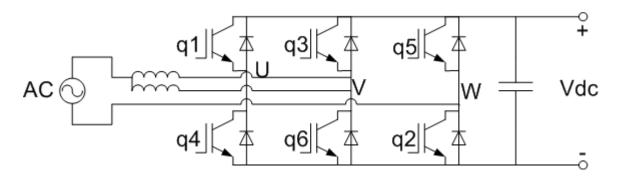

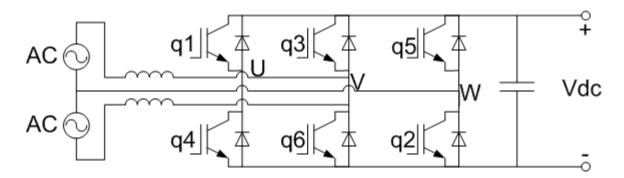

## AC/DC Stage Design

The topology chosen for the AC/DC stage of the DIBPC design can be seen below in Figure 2.3. This topology was chosen for its simplicity, flexibility, and efficiency. The design meets all the design constraints, including the ability to effectively operate at 120  $V_{AC}$  or 240  $V_{AC}$  and to operate bidirectionally. This design can be implemented with the use of an IGBT 6-pack, which is typically used in three phase motor control applications. Because IGBT 6-packs with anti-parallel diodes are used so commonly in this configuration, these packs are readily available and cost-effective.

Figure 2.3: Dual Channel PFC Boost Rectifier and Inverter

The basic operation of this topology is relatively simple. It essentially consists of a diode rectifier intermingled with a DC – DC boost converter, much like the PFC rectifier described above. First, consider the charging mode. In the charging mode, either two or all three legs of the Rectifier will be modulated. When the input voltage is  $120 V_{AC}$ , only the first leg, containing q1 and q4, and the third leg, containing q5 and q2, are operated, leaving q3 and q6 gated off. However, when the input voltage is 240  $V_{AC}$ , all three legs are operated. This third leg allows the addition of a second inductor to be used in conjunction with the first inductor. This allows more current to be used without increasing the current seen by each inductor. Inductor saturation, sizing and heat dissipation is a major concern, and this topology takes that into consideration.

Consider the case of the 120  $V_{AC}$  input, knowing it can easily be extended to the 240  $V_{AC}$  case. In this mode, q2 and q6 are modulated using pulse width modulation (PWM) generated with the aim of controlling the input current waveform and boosting the output voltage. When q2 and q4 (and q6 for 240  $V_{AC}$ ) are gated on, there is a path for the current to spool through the inductor, seen below in Figure 2.4. The path the current takes is bolded. The path that is unique to the positive half-cycle is shown bolded in red and the alternative path it takes during the negative half-cycle is shown bolded in blue. If the DIBPC was operating for 240  $V_{AC}$ , q6 would perform the same function as q4, therefore using both inductors for spooling.

Figure 2.4: PFC Rectifier Spooling Paths

No distinction is made between the negative and positive half-cycles during the spooling mode. No distinction is necessary because both q2 and q6 can be operated together such that whichever half-cycle the input voltage is in, the spooling path will still be available. Once the current has spooled a sufficient amount (decided by the controller, described later in this chapter), q2 and q6 gated off, eliminating the path for the current to spool. Because the current in an inductor cannot change instantaneously, and the voltage across that inductor is proportional to the rate of change of the current through the inductor, the voltage of the inductor will rise enough to forward bias the anti-parallel diodes at q1 and q5 (and q3 in 240 V<sub>AC</sub> mode) such that current can flow through the diodes and into the filter capacitor. This path can be seen below in Figure 2.5.

Figure 2.5: PFC Rectifier Current Path during Capacitor Charging

The discharging mode is operated much like a typical H-bridge inverter. Two possible discharging mode operations are discussed. First, a discussion of the potential operation versus the modified operation of the discharging mode is needed. In the potential operation of the discharging mode, the AC/DC stage would output two separate

120  $V_{AC}$  sinusoidal voltages 180° apart. This would allow the discharging mode to output to each line in a typical US residence, powering any 120  $V_{AC}$  and 240  $V_{AC}$  circuits. First, this potential operation is discussed, and then the modified operation is discussed.

The potential operation of the DIBPC in discharging mode actually has two different states of operation per switching period during each half-cycle. Each switching period is broken into two parts where the first part is dedicated to modulating the first AC line and the second part is dedicated to modulating the second AC line. During the first half-cycle the first state of operation per switching period modulates q1 and q2 to produce a sinusoidal positive half-cycle in the first state of operation modulates q5 and q6 to produce a sinusoidal negative half-cycle in the second AC line. During the second half-cycle, the first state of operation modulates q5 and q4 to produce a sinusoidal negative half-cycle in the first AC line and the second state of operation modulates q3 and q2 to produce a sinusoidal positive half-cycle in the first AC line and the second state of operation modulates q3 and q2 to produce a sinusoidal positive half-cycle in the first AC line and the second state of operation modulates q3 and q2 to produce a sinusoidal positive half-cycle in the second AC line.

Figure 2.6 is helpful in understanding the end result and the modes of operation for the potential operation. The red paths and waveform corresponds to the first AC line and the blue paths and waveform corresponds to the second AC line. One of the disadvantages of using this scheme is that the DC bus voltage must be equal to at least twice the maximum AC line to neutral voltage. This is because having two states of operation per switching period means that the maximum duty cycle for either AC line is 50% for a given switching period.

Figure 2.6: Discharging Mode Operation

The actual modified operation is a little different. This mode of operation was implemented as a simpler operation simply to demonstrate the ability of this topology to work in the discharging mode. In the modified operation, both the first and second AC lines output 120  $V_{AC}$  with no phase shift between them. The result of this is that the line to line voltage is 0  $V_{AC}$ , rather than 240  $V_{AC}$ , but both 120  $V_{AC}$  circuits are powered. During this operation, only one state exists for each half-cycle switching period. In the positive half-cycle, q1, q2 and q6 are modulated to produce the sinusoidal positive half-cycle in both AC lines. In the negative half-cycle, q5, q3 and q4 are modulated to produce the sinusoidal negative half-cycle in both AC lines.

The simulated and experimental control methods and the derivation of the output to input voltage ratio and the duty cycle can be seen in the controls sections of Chapter Three and Chapter Five. One of the cons of this topology is the fact that the rated current for q1, q2, q3 and q4 is only half that of q5 and q6. The IGBT legs containing q1 and q4 and q3 and q6 both use the IGBT leg containing q5 and q2 as a return path. Because both IGBT legs use q5 and q2 as a return path, those IGBTs will have twice as much current as the remaining IGBTs. This is an issue considering typical IGBT 6-packs have identically rated IGBTs. However, the current rating required in each inductor is only half that it of what it would be if only two IGBT legs were present.

## DC/DC Stage Design

The battery charger needs the addition of the DC/DC stage to successfully complete its operation. In the charging mode, the DC/DC stage is added at the end to buck the DC bus voltage down and to a variable voltage to charge the battery with the desired voltage. This DC/DC stage also operates as a buck converter in the discharging mode, decreasing the battery voltage to a steady 200  $V_{DC}$ .

The DC/DC stage has two major functions in the charging mode. The first function is to provide a variable DC output which will be suitable for the needs of the battery following the charging profile. The second function is to eliminate the ripple voltage present at twice the line frequency. Because the ripple voltage is so low in frequency, it can easily be eliminated by a DC/DC stage.

The DC/DC stage is very simple, consisting of a typical implementation of a DC to DC buck converter. The DC to DC buck converter must operate bidirectionally, however. To achieve this, two IGBTs would need to be used, both with anti-parallel diodes. These are each in series with an inductor. Then another diode is placed between the negative and positive DC bus lines with the cathode at the positive side. The DC/DC stage begins with the DC bus capacitor at the left side. It ends with the battery connected to the DC capacitor at the right side. The topology can be seen below in Figure 2.7.

Figure 2.7: DC/DC Stage Topology

In either operating mode, the DC/DC stage can be treated like a normal DC to DC buck converter. In the charging mode, the right IGBT is inconsequential because the anti-parallel diode will always be forward biased and will provide the current path. The left IGBT is pulsed to provide a duty cycle which is proportional to the ratio of the output voltage to the input voltage. The relationship between the input and output voltage and duty cycle for a DC to DC buck converter in continuous conduction mode can be seen below in Equation 2.1 [9].

$$\frac{V_{out}}{V_{in}} = \frac{I_{in}}{I_{out}} = D$$

(2.1)

In the discharging mode, the left IGBT is not considered because its anti-parallel diode is forward biased. The right IGBT is pulsed in the same fashion as the charging mode to provide the desired constant DC bus voltage of  $200 V_{DC}$ .

The DC/DC stage is designed, but it will not be implemented experimentally for the DIBPC. The DC/DC stage consists of two basic and commonly used DC to DC converters arranged such that one can act in either operating mode. Because DC to DC buck converters are used, the DC/DC stage's construction and control are somewhat trivial. The DC/DC stage is, however, simulated. This will be discussed in the next chapter on simulation.

#### Component Sizing and Rating

To optimize the DIBPC AC/DC stage design, the components need to be ideally sized. To do this, several pieces of information must be known. First, the maximum size of the load must be determined. The limiting factor for this design has been the typical size of a residential 240  $V_{AC}$  circuit breaker, 30  $A_{AC}$ . Therefore it can be assumed that the maximum input current must be 30 A – this also sets the limit for the output current. The next piece of information that must be known is the switching frequency, which has been designated at 20 kHz due to IGBT switching frequency limitations and to minimize

the number of switches that occur, and therefore the switching losses. The desired DC link voltage is also needed to determine the relationship between the input current and the output current, this is set to 400  $V_{DC}$ . The final piece of information that is required is the maximum acceptable ripple current and ripple voltage.

The worst case scenario must be considered for sizing each component. First, the capacitor must be sized. The worst case scenario for the capacitor would be the 30  $A_{AC}$ , 240  $V_{AC}$  case, with an efficiency of 100%. This produces a maximum amount of current which will deplete the charge on the capacitor, creating a ripple voltage. Because the second stage of the converter will be a DC to DC converter which will filter the ripple voltage present at twice the line frequency, the ripple tolerance is quite high. As much as a 40  $V_{p-p}$  ripple is an acceptable amount that could easily be filtered by the second stage of the converter. Because DC capacitors have limitations on voltage ripple and current, 40  $V_{p-p}$  ripple limitation is chosen. Because the ripple voltage at twice the line frequency will be so much greater than the ripple voltage at the switching frequency, only the lower frequency ripple voltage is considered for capacitor sizing. Equation 2.2 shows the derivation of the desired capacitance.

$$P_{dc} = P_{ac} * \eta = I_{ac} * V_{ac} * 1.00$$

$$I_{cap} = I_{dc} = \frac{P_{dc}}{V_{dc}} = 18A$$

$$I_{cap} = C * \frac{dV_{cap}}{dt}$$

$$C = \frac{I_{cap}}{\frac{dV_{cap}}{dt}} = \frac{18A}{\frac{40V}{8.3333ms}} = 3750\mu F$$

(2.2)

The inductor value for a given inductor ripple current is not quite as easily calculated. The ripple current is only a function of the switching frequency, there is no relevant ripple voltage at twice the line frequency because the fundamental inductor current is AC, oscillating at the line frequency. The derivation of the inductor ripple current for a DC to DC boost converter can be seen in [10].

This inductor current ripple calculation can be applied to a PFC boost rectifier by assuming the line frequency is so much lower than the switching frequency that it can be viewed as a DC voltage in the reference timeframe. This line frequency voltage can then be converted similarly to a DC to DC boost converter. To assume a worst case scenario, the source voltage,  $V_s$  that produces a maximum ripple current is used. To limit electromagnetic interference (EMI), minimize THD and maximize the PF and the efficiency, the inductor current ripple is limited to  $3A_{p-p}$ . This value is selected by optimizing efficiency (balancing filter losses with harmonic losses).

IEC 61000-3-4 limits any harmonic greater than the  $33^{rd}$  to .6% of the fundamental, or about  $500mA_{p-p}$  at maximum load. To meet this limit for the switching frequency ( $333^{rd}$  harmonic), an AC line filter must be installed with an attenuation of at least 8 dB at the switching frequency of 20 kHz. [10] gives the derivation for the inductor ripple current and the relationship between the duty cycle, k, and the input and output voltages, seen in Equations 2.3 and 2.4.

$$k = \frac{V_{dc} - V_s}{V_{dc}} \tag{2.3}$$

$$\Delta I = \frac{V_s * k}{f * L} = \frac{V_s * \frac{V_{dc} - V_s}{V_{dc}}}{f * L}$$

$$\Delta I_{max}: \frac{d\Delta I}{dV_s} = 0 = \frac{V_{dc} - 2V_s}{f * L * V_{dc}} \Rightarrow V_s = \frac{V_{dc}}{2}$$

$$\Delta I = \frac{\frac{V_{dc}}{2} * \frac{V_{dc} - \frac{V_{dc}}{2}}{f * L}}{L = 1.414mH}$$

$$(2.4)$$

The other components do not have to be sized, only rated for their operation. The IGBTs and diodes in the neutral path (q5 and q2), need to be rated for 30  $A_{RMS}$  and 400  $V_{DC}$  continuous. The IGBTs and diodes in the other two legs need only be rated for 15 $A_{RMS}$  and 400  $V_{DC}$ . However, because the duty cycle of this device could potentially be so high during charging and because inductive load switching could occur in discharging mode, a generous safety margin has been incorporated. The filter capacitor needs to be rated for at least 450  $V_{DC}$  – this will include any maximum ripple or charging overshoot that may be present. The inductors need to be rated for at least 15  $A_{RMS}$ .

## <u>Summary</u>

The DIBPC design is broken down to better separate the functions of each individual stage. Once the design was chosen, simulations were constructed. These simulations, detailed in the next chapter, were used during the design process to concrete some of the details of the design. Once the simulations were completed, the experimental process began. In the experimental implementation, the master controller was not constructed. The overall design focuses primarily on the AC/DC stage of the DIBPC, because the DC/DC stage consists of a common design with very little changes. The DIBPC AC/DC design takes into consideration the design of the DC/DC stage, ideally minimizing its complexity and cost.

# CHAPTER THREE

# SIMULATION

To better understand and design the PHEV battery charger, some simulations were constructed. The simulation process was employed to test different designs and to examine the effects changes have on the system. Simulations were also useful to explore and troubleshoot the hardware during the construction and experimentation phases.

## Simulation Design

Two software programs were utilized for simulation purposes. The first software used was PSCAD<sup>TM</sup>. PSCAD is a graphical based program designed for modeling and simulating power systems. PSCAD is mainly aimed at the utility industry for steady state and transient studies, including fault analyses, transient and harmonic effects and load flows. The second software employed was Matlab<sup>TM</sup>. Matlab is a mathematical program designed to be flexible and applicable to almost any mathematical problem. Matlab has a graphical modeling and simulation interface called Simulink<sup>TM</sup>.

Simulink comes equipped for typical mathematical systems, and capable of expansion through the use of toolboxes. Toolboxes for Simulink incorporate new blocks that can be used for a specific function. One of these toolboxes is the Simulink Power Systems Toolbox. This toolbox contains many useful blocks for this application, including various transistors, diodes, multimeters, motor drives and controllers, passive elements, etc.

Basic models were constructed in each of these software packages. After initial simulations and some simple analyses were completed, it was decided to move forward using only Matlab/Simulink. Simulink has a more user friendly interface, but more importantly, it has more useful existing blocks. Simulink comes well equipped for many control problems, making it much more flexible than PSCAD for designing a controller. This was the major deciding factor in choosing between PSCAD and Simulink.

The Simulink Power Systems Toolbox operates in a somewhat unique manner from typical Simulink applications. The Power Systems Toolbox contains the PowerGUI interface which operates as a layer between the Matlab solver and the Simulink models. The PowerGUI layer discretizes the model system. This is done to improve performance of the simulation, and so that the model will converge in a realistic amount of time. PowerGUI also allows for many different analyses to be performed that are unique to Power Systems, including frequency sweeps, load flows, FFTs and steady state versus transient values.

One of the considerations that must be taken into account is solver step size. This determines how many iterations are calculated. Knowing the switching frequency would be around 20 kHz – 25 kHz, a step size of 1  $\mu$ s was chosen. This step size allowed for plenty of resolution for the duty cycle. Tests were done at 10  $\mu$ s steps, but the simulations contained a large ripple that was not present at 1  $\mu$ s step size. Another important factor is the length of the simulation. The simulation must be long enough to

get past all the transient behavior so that only the steady state behavior is evident. This is typically not an issue, and a simulation run time of 250 ms was adequate. The only problematic situation is when the state of charge of the battery needs to be changed. To get an appreciable change in the state of charge, it would take thousands of seconds, much too long to run a simulation. Therefore some interpolation must be used.

One area of difficulty which often arises in simulation is how to model the load. In this case, the system was modeled and simulated in three different modes, including: the charging mode, the discharging mode and the charging mode with the DC/DC stage. Therefore several different load models had to be used. For the first mode, the charging mode, the load model was simply a resistive load. This was used to ensure that the basic operation of the AC/DC stage was effective when converting to a constant DC voltage. When considering how the AC/DC converter should operate, it was thought that it would be desirable to operate the system with a constant DC current. This was modeled with a simple ideal current source model. After some testing and comparison, however, it was determined that the constant DC current load and a simple resistive load had nearly identical results. Because the constant DC current load took significantly longer to solve in simulation time, the resistor was used.

The second mode of operation was the discharging mode. This mode required the use of a source on the AC side of the converter. When in this mode, the voltage source was modeled with a simple DC voltage source to emulate the output from the DC/DC stage that is fed from the battery. The load on the AC side was modeled as a resistor and

also as a resistive an inductive load. These should provide for some variation in loads that one might expect to see in a typical residential application.

When the DC/DC stage was added in, two loads were modeled. The first modeled load was also a resistor. This provided a simple way to determine if the overall system would act as expected when subjected to a constant impedance load. The second load model, though, was a NiMH battery model. This is a generic battery model contained within the Simulink<sup>™</sup> Power Systems Toolbox.

The battery model allows certain parameters to be changed for the battery. These parameters include the DC voltage rating, the energy rating in amp-hours, the initial state of charge, the internal resistance and the discharge characteristics. Because the characteristics of the battery are not known at this time, the default values for a NiMH battery with a voltage rating of 330  $V_{DC}$  and about 15 A-hrs were used. Unfortunately, due to computing restrictions, the simulation could not be run for a long enough period of time to accurately show what was happening as a result of the charge being applied. Because of this limitation, the battery essentially always looked and acted like a constant DC voltage source, creating essentially meaningless results. For this reason, only the resistive load results were considered.

## Design Topology Model

The simulation is broken down into two major parts. The first part, discussed in this section, is the system model. The second part is the control structure. This is discussed later in this chapter. The simulation model is organized using several subsystems. The operation of the simulation model will be discussed by subsystem.

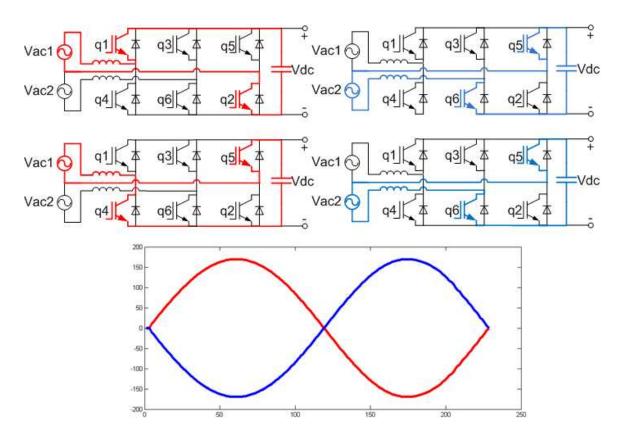

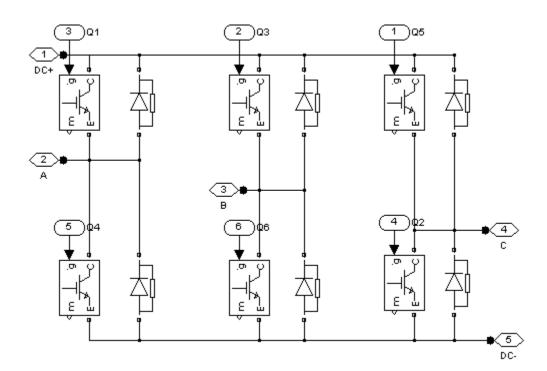

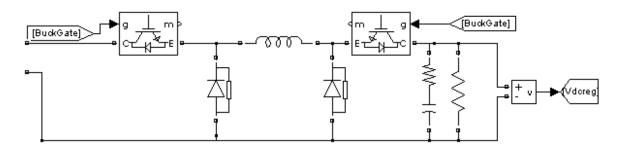

The simulation implementation is broken into three subsystem layers. The inner most layer contains the component makeup of the IGBT 6-pack with anti-parallel diodes. This can be seen below in Figure 3.1. The inputs and outputs for this block are the same as you would expect from an IGBT 6-pack, one connection for each of the IGBT legs between the upper and lower IGBTs (A, B and C), a negative DC connection and a positive DC connection. The control connections consist of one gate connection for each IGBT.

Figure 3.1: IGBT 6-pack Model

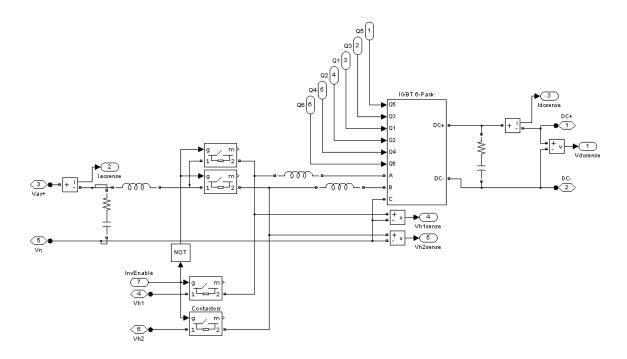

The middle layer of the controller consists of the external electronic components such as inductors, capacitors and filters, along with measurement blocks and ideal switches. This layer can be seen below in Figure 3.2. The two spooling inductors can be seen leading into the IGBT 6-pack subsystem. The capacitor with its modeled equivalent series resistance (ESR) is connected to the output from the IGBT 6-pack subsystem. The AC line filter, consisting of an AC capacitor and a series inductor can be seen on the left. Finally, four ideal switches are used to make any connection changes for use in all modes of operation. The connections from this layer go directly to the AC and DC input and output (load and source).

Figure 3.2: Electrical Circuit Model

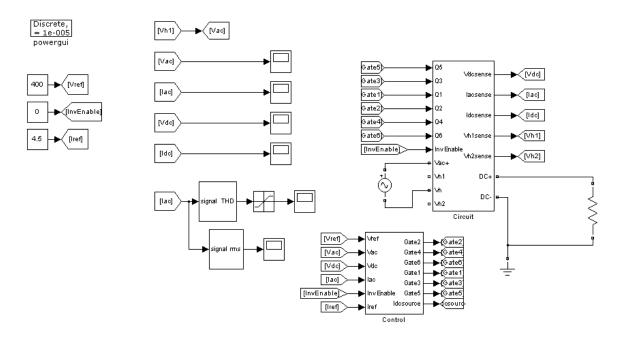

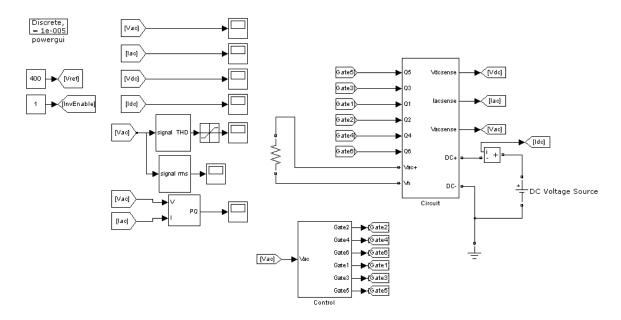

Finally, the last layer of the simulation model is the outer layer containing the source and the load. This layer will vary depending whether the simulation is in the charging mode or the discharging mode. The charging mode will have a voltage source on the AC side and a load on the DC side. Conversely in the discharging mode this layer will have a voltage source connected on the DC side and a load connected on the AC side. In the charging mode, the model can be seen below in Figure 3.3 and the discharging mode model can be seen below in Figure 3.4.

Figure 3.3: Charging Mode Model

Figure 3.4: Discharging Mode Model

In the outside layer is where the measurements are plotted and calculations such as THD, RMS, and power are made. The control subsystem can be seen, and the measurements needed to make that operate are ported into the subsystem. Likewise the resulting control outputs for each gate are ported out of the subsystem and into the electrical circuit model subsystem. To properly emulate the control, only the measurements that would be absolutely necessary to the controller will be fed back into the controller. Enough measurements are taken otherwise to provide adequate feedback about the operation, efficiency, and effectiveness of the simulated converter.