### Clemson University TigerPrints

#### All Dissertations

Dissertations

8-2007

# Manufacturable process and tool for high performance metal/high-k gate dielectric stacks for sub-45 nm CMOS & related devices

Aarthi Venkateshan *Clemson University,* avenkateshan@gmail.com

Follow this and additional works at: https://tigerprints.clemson.edu/all\_dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Venkateshan, Aarthi, "Manufacturable process and tool for high performance metal/high-k gate dielectric stacks for sub-45 nm CMOS & related devices" (2007). *All Dissertations*. 113. https://tigerprints.clemson.edu/all\_dissertations/113

This Dissertation is brought to you for free and open access by the Dissertations at TigerPrints. It has been accepted for inclusion in All Dissertations by an authorized administrator of TigerPrints. For more information, please contact kokeefe@clemson.edu.

### MANUFACTURABLE PROCESS AND TOOL FOR HIGH PERFORMANCE METAL/HIGH-K GATE DIELECTRIC STACKS FOR SUB-45 NM CMOS & RELATED DEVICES

A Dissertation Presented to the Graduate School of Clemson University

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy Electrical and Computer Engineering

> by Aarthi Venkateshan August 2007

Accepted by: Dr.Rajendra Singh, Committee Chair Dr. Kelvin F. Poole Dr. William R. Harrell Dr. Mica Grujicic

#### ABSTRACT

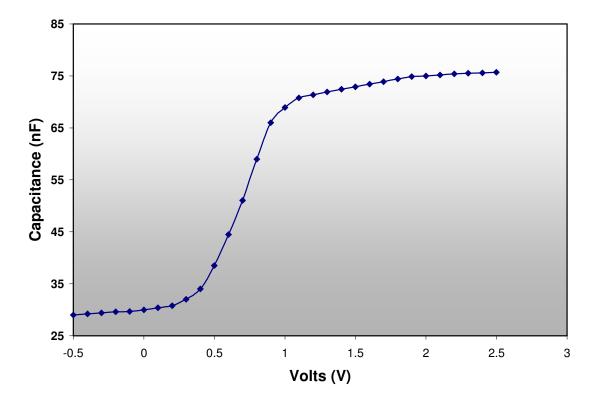

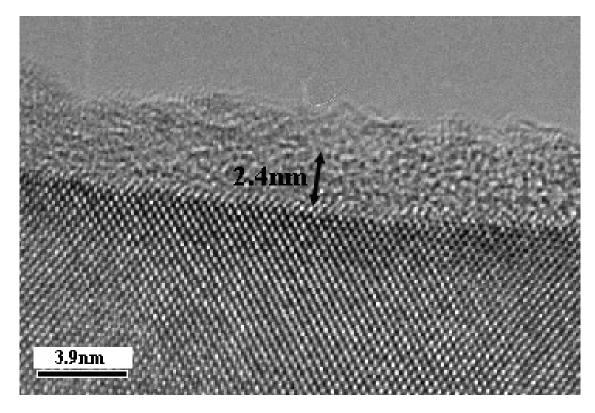

Off state leakage current related power dominates the CMOS heat dissipation problem of state of the art silicon integrated circuits. In this study, this issue has been addressed in terms of a low-cost single wafer processing (SWP) technique using a single tool for the fabrication of high- $\kappa$  dielectric gate stacks for sub-45 nm CMOS. A system for monolayer photoassisted deposition was modified to deposit high-quality HfO<sub>2</sub> films with in-situ clean, in-situ oxide film deposition, and in-situ anneal capability. The system was automated with Labview 8.2 for gas/precursor delivery, substrate temperature and UV lamp. The gold-hafnium oxide-aluminum (Au-HfO<sub>2</sub>-Al) stacks processed in this system had superior quality oxide characteristics with gate leakage current density on the order of 1 x 10<sup>-12</sup> A/cm<sup>2</sup> @ 1V and maximum capacitance on the order of 75 nF for EOT=0.39 nm. Achieving low leakage current density along with high capacitance demonstrated the excellent performance of the process developed. Detailed study of the deposition characteristics such as linearity, saturation behavior, film thickness and temperature dependence was performed for tight control on process parameters. Using Box-Behnken design of experiments, process optimization was performed for an optimal recipe for HfO<sub>2</sub> films. UV treatment with in-situ processing of metal/high-κ dielectric stacks was studied to provide reduced variation in gate leakage current and capacitance. High-resolution transmission electron microscopy (TEM) was performed to calculate the equivalent oxide thickness (EOT) and dielectric constant of the films. Overall, this study shows that the in-situ fabrication of MIS gate stacks allows for lower processing costs, high throughput, and superior device performance.

#### ACKNOWLEDGEMENTS

I express my gratitude to my advisor Dr. Rajendra Singh for his sincere guidance and support throughout my studies at Clemson University. He not only helped me to comprehend this project but also provided valuable insights on issues relevant to semiconductor technology. I thank Dr. Kelvin F. Poole, who lent valuable support and advice on various technical issues and for serving on my committee. I also thank Dr. Mica Grujicic who served on my committee for his valuable input.

I thank Dr. William R. Harrell for letting me use his laboratory for C-V, J-V measurements of my samples and for serving on my committee. I thank Dr. Herman F. Senter for his advice and kind assistance with the statistical design of experiments. I thank Mr. Robert Teague for his help with Labview during the automation of the system. I owe a debt of gratitude to Dr. James E. Harriss for training me in the cleanroom and assisting with the more intricate parts of my project. My sincere thanks to Dr. Robert A. Latour and his graduate student Kenan Fears from the Bioengineering department for the ellipsometry study. I thank Dr. J. Narayan, and his graduate student Punam Pant, from the NSF Center for Advanced Materials and Smart Structures at North Carolina State University, for providing TEM micrographs of my samples. This work was supported by the Applied Materials graduate fellowship award from September 2004 – August 2007.

Finally, I express my deep felt gratitude to my husband Sudhir for his constant encouragement and patience, as well as my parents and brother, who provided me with an immense amount of moral support during the completion of this work.

### TABLE OF CONTENTS

| Page |

|------|

|------|

| TITLE PAGE                                                                                                                     | . i                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| ABSTRACT                                                                                                                       | ii                                                                                                                     |

| ACKNOWLEDGEMENTS                                                                                                               | iii                                                                                                                    |

| LIST OF TABLES                                                                                                                 | /ii                                                                                                                    |

| LIST OF FIGURES                                                                                                                | iii                                                                                                                    |

| CHAPTER                                                                                                                        |                                                                                                                        |

| I. INTRODUCTION                                                                                                                | . 1                                                                                                                    |

| II. HIGH-K GATE DIELECTRIC ISSUES                                                                                              | 4                                                                                                                      |

| Introduction<br>Need for a High-κ Gate Material<br>Required Properties of a Suitable Material<br>Analysis of Published Results | 5<br>7<br>20<br>21<br>22                                                                                               |

| III. MONOLAYER PHOTOASSISTED DEPOSITION<br>SYSTEM                                                                              | 32                                                                                                                     |

| Introduction                                                                                                                   | <ul> <li>33</li> <li>34</li> <li>36</li> <li>41</li> <li>44</li> <li>45</li> <li>51</li> <li>51</li> <li>52</li> </ul> |

| References                                                                                                                     | 53                                                                                                                     |

Table of Contents (Continued)

| IV.   | OFF STATE GATE CURRENT LEAKAGE POWER             |     |

|-------|--------------------------------------------------|-----|

|       | REDUCTION BY HFO <sub>2</sub>                    |     |

|       |                                                  | 70  |

|       | Introduction                                     |     |

|       | Impact of Zero Gate Dielectric Current On Future |     |

|       | Generations Of CMOS                              |     |

|       | Experimental Procedure                           |     |

|       | Experimental Results                             |     |

|       | Manufacturability                                |     |

|       | Discussion                                       |     |

|       | Conclusion                                       |     |

|       | References                                       |     |

| V     | NEW PROCESS AND TOOL FOR METAL/HIGH-K            |     |

| •••   | GATE DIELECTRIC STACK                            | 107 |

|       |                                                  | 107 |

|       | Introduction                                     |     |

|       | Our Manufacturing Mantra                         |     |

|       | Statistical Design Of Experiments                |     |

|       | In-Situ Cleaning DOE                             |     |

|       | Box Behnken design of experiments for annealing  |     |

|       | Optimized Process Recipe                         |     |

|       | Process Variation Analysis                       |     |

|       | Conclusion                                       |     |

|       | References                                       |     |

| VI.   | CONCLUSION                                       | 150 |

| APPEN | IDICES                                           | 154 |

| A.    | Labview Automation                               |     |

| B.    | Statistical design of experiments                |     |

Page

### LIST OF TABLES

| Table | Page                                                                                            |

|-------|-------------------------------------------------------------------------------------------------|

| 1.    | Sample numbers and processing conditions of<br>few samples processed                            |

| 2.    | Samples and their respective leakage current<br>densities (J) at different voltages             |

| 3.    | Gate current related power consumption data<br>from ITRS roadmap for future generations of CMOS |

| 4.    | Comparison of three factor designs                                                              |

| 5.    | Box-Behnken in-situ cleaning DOE                                                                |

| 6.    | Experimental runs for in-situ cleaning DOE 121                                                  |

| 7.    | Results for in-situ DOE leakage current density for 8 points<br>on each sample                  |

| 8.    | Box Behnken Annealing DOE with 3 levels chosen                                                  |

| 9.    | Experimental runs for Box Behnken annealing DOE                                                 |

| 10.   | Box Behnken annealing DOE with 8 points<br>measured on each sample                              |

| 11.   | Final optimized process recipe for deposition<br>of hafnium oxide films                         |

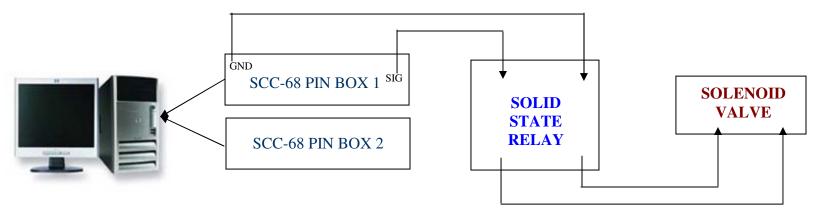

| 12.   | NI-DAQ MX Virtual channels and corresponding<br>SCC-68 pinouts                                  |

| 13.   | SCC-68 pinouts and corresponding solid state<br>relays and valves                               |

| 14.   | Analog inputs and corresponding SCC-68 pinouts                                                  |

### LIST OF FIGURES

| Figure | Pa Pa                                                                                                                                                             | ge |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

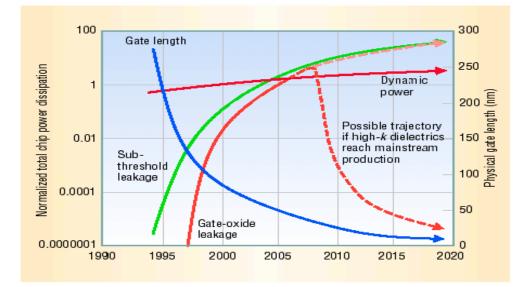

| 1.     | Chip power dissipation versus gate length                                                                                                                         | 29 |

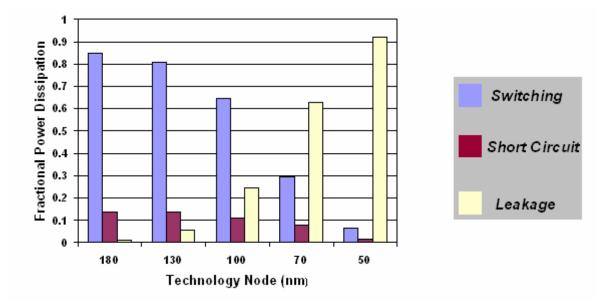

| 2.     | Power dissipation distribution for various technology nodes                                                                                                       | 30 |

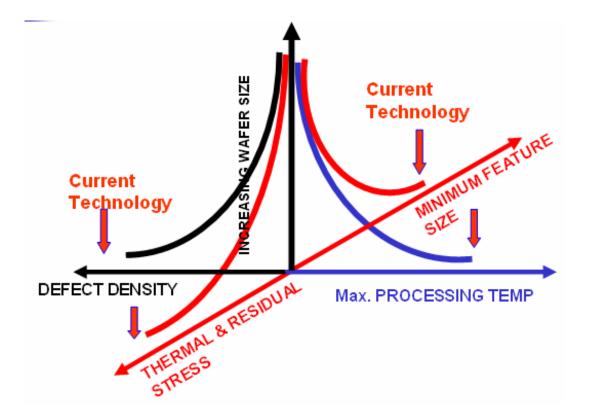

| 3.     | Process integration issues                                                                                                                                        | 31 |

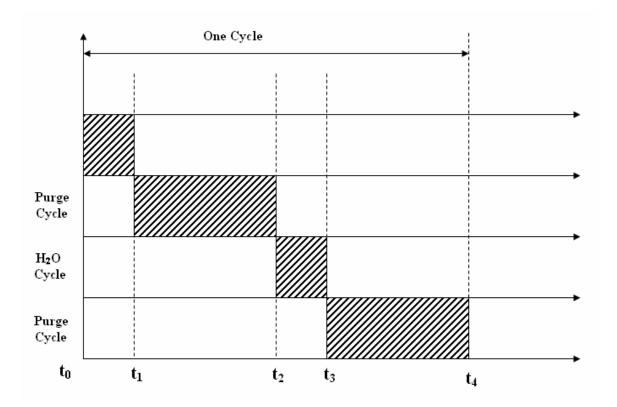

| 4.     | Cycling steps showing time profiles                                                                                                                               | 58 |

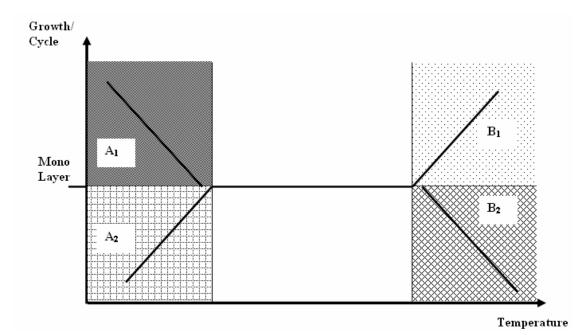

| 5.     | Processing window of the monolayer photoassisted<br>CVD process                                                                                                   | 59 |

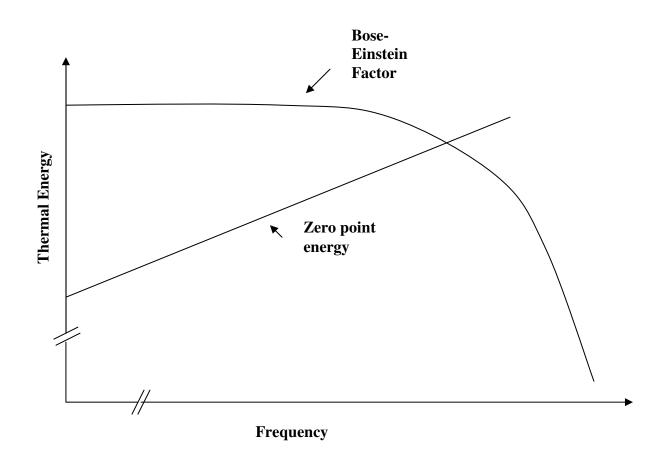

| 6.     | Representation of Bose Einstein factor in thermal<br>energy dependence with frequency                                                                             | 60 |

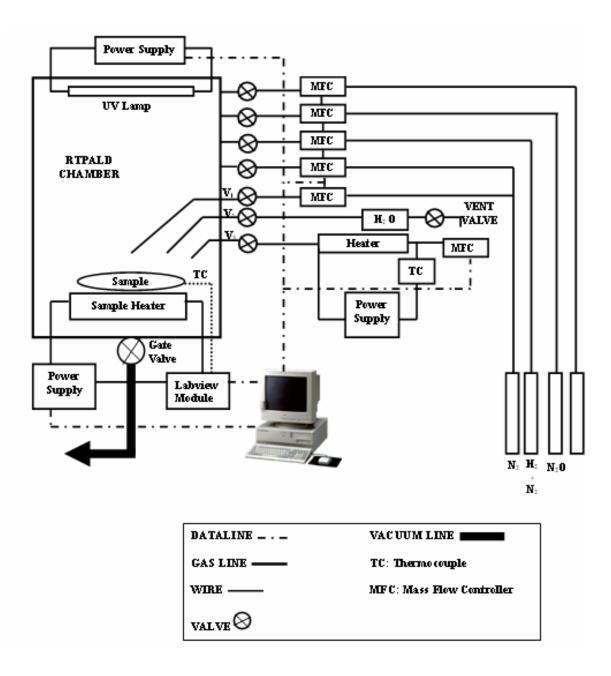

| 7.     | Schematic diagram of the monolayer photoassisted CVD system                                                                                                       | 61 |

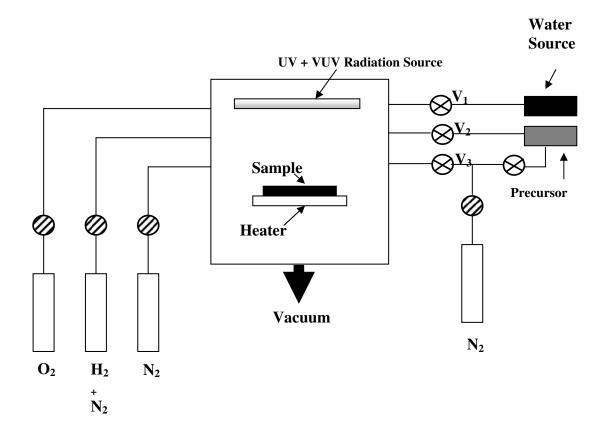

| 8.     | Simplified diagram of the monolayer photoassisted CVD system                                                                                                      | 62 |

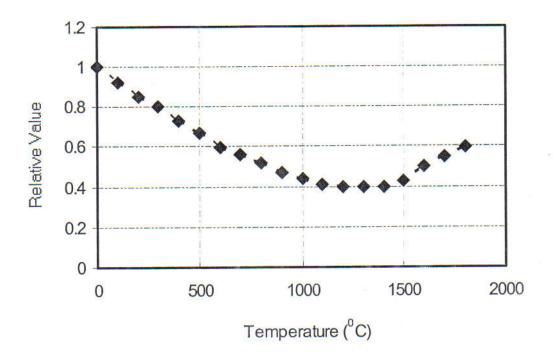

| 9.     | Resistivity of the PG conductive film<br>in a Boraelectric <sup>®</sup> heater                                                                                    | 63 |

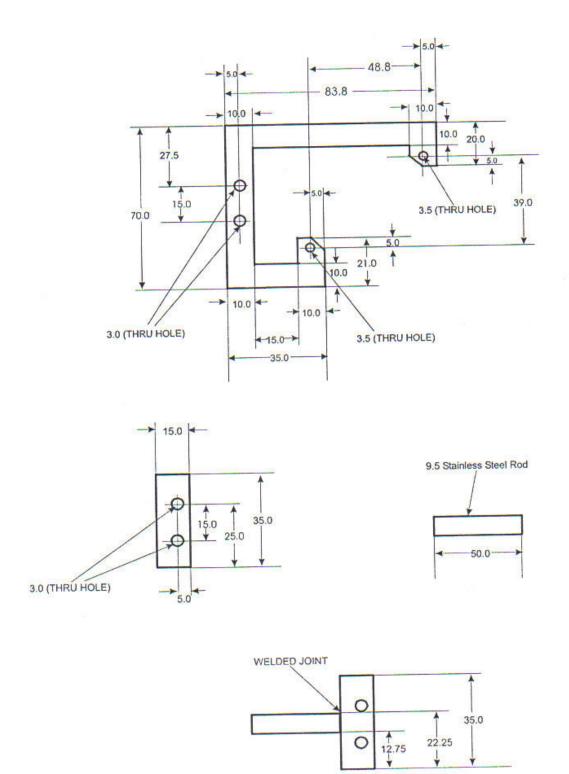

| 10.    | Heater Mounting Plate                                                                                                                                             | 64 |

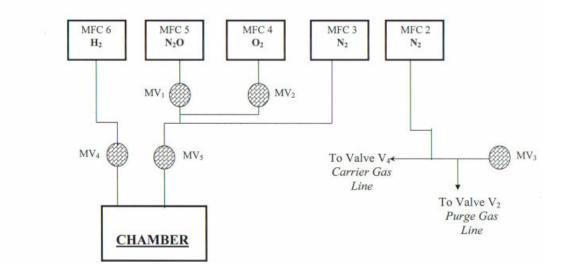

| 11.    | Detailed Gas Flow connections                                                                                                                                     | 65 |

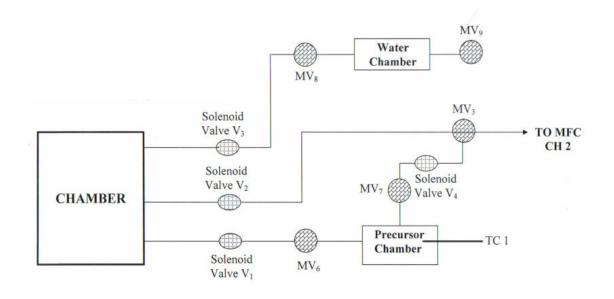

| 12.    | Precursor Delivery Line connections                                                                                                                               | 66 |

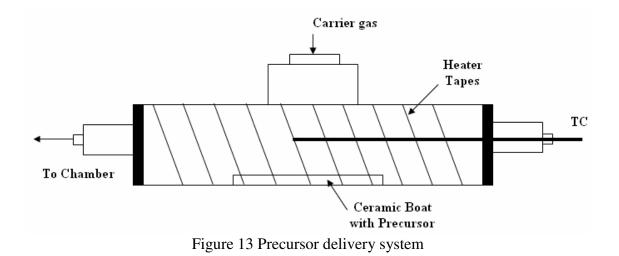

| 13.    | Precursor Delivery System                                                                                                                                         | 67 |

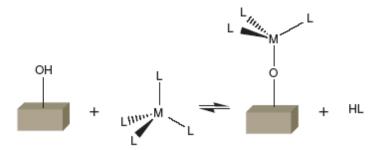

| 14.    | Schematic of a ligand exchange reaction<br>for a ML <sub>4</sub> /H <sub>2</sub> O ALD                                                                            | 68 |

| 15.    | Precursor types – R's represent alkyl<br>groups consisting of carbon and hydrogen,<br>such as methyl (CH <sub>3</sub> ) or ethyl (C <sub>2</sub> H <sub>5</sub> ) | 69 |

| Figures                                                                                                                        | Page    |

|--------------------------------------------------------------------------------------------------------------------------------|---------|

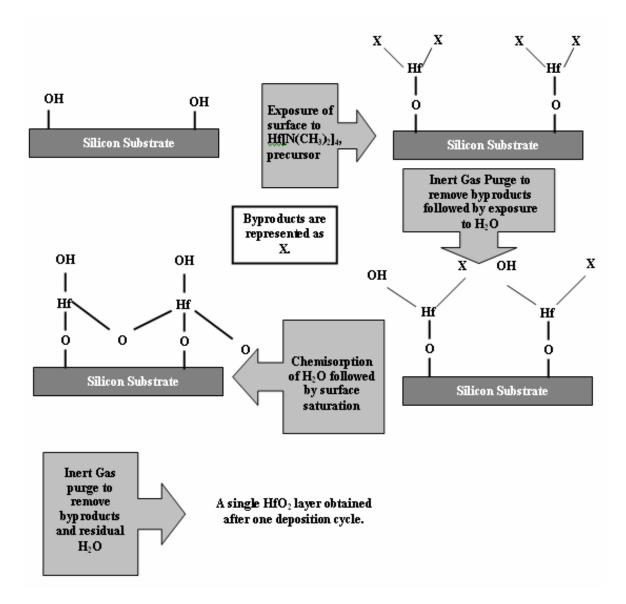

| 16. Formation of a single HfO <sub>2</sub> layer for one deposition cycle                                                      |         |

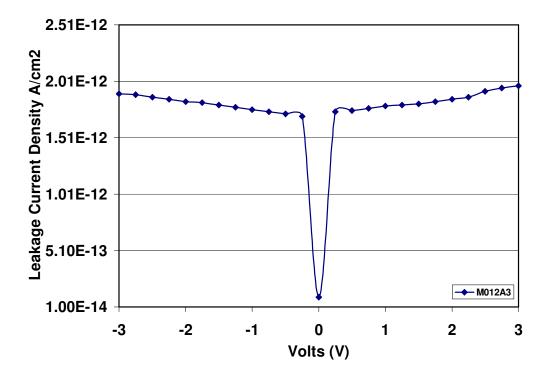

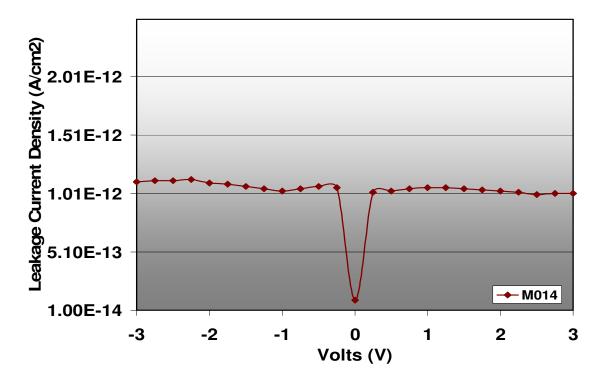

| 17. Leakage Current Density vs voltage characteristi<br>of sample M012A3 measured at both positive<br>and negative gate biases | e       |

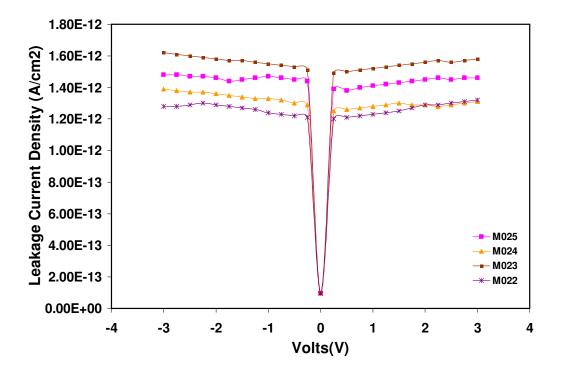

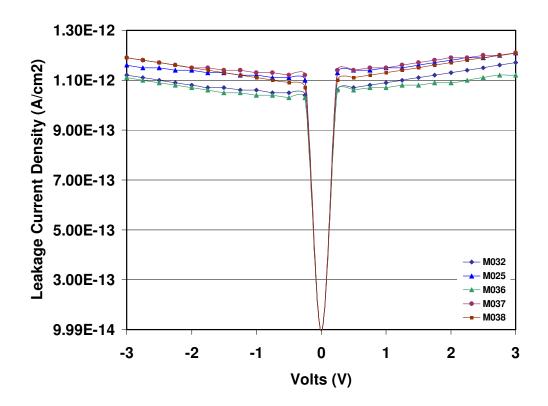

| <ol> <li>Leakage current densities of different samples pr<br/>differently by using the RTPMLD system</li> </ol>               |         |

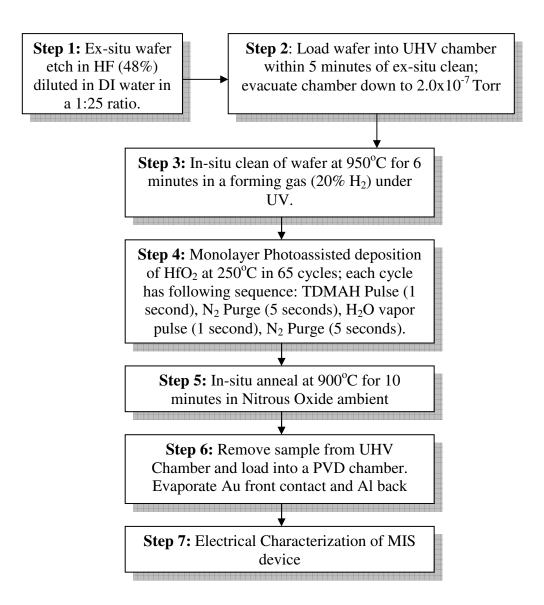

| 19. Experimental process flow for deposition of hafnium oxide                                                                  |         |

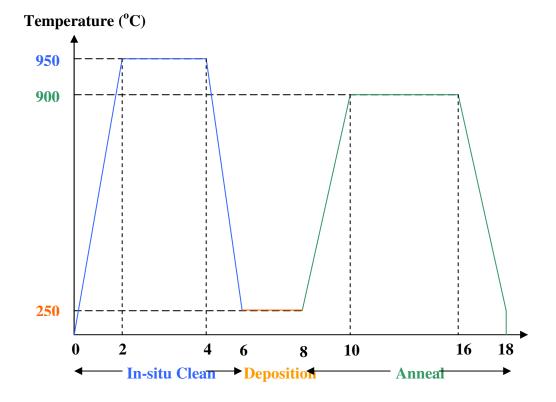

| 20. Temperature profile during monolayer photoassisted deposition process                                                      |         |

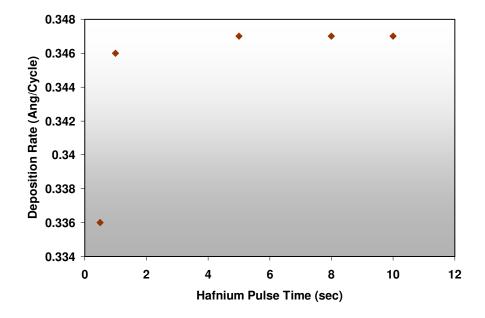

| 21. Deposition rate as a function of Hafnium precurs pulse time                                                                |         |

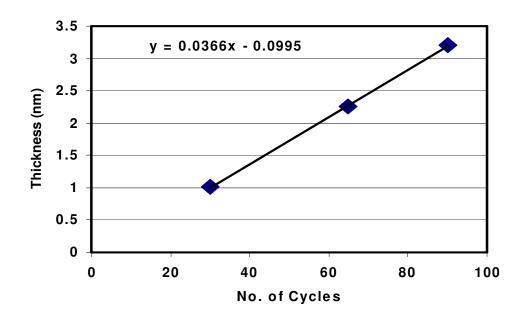

| 22. Film Thickness as a function of number of cycle used in the deposition process                                             |         |

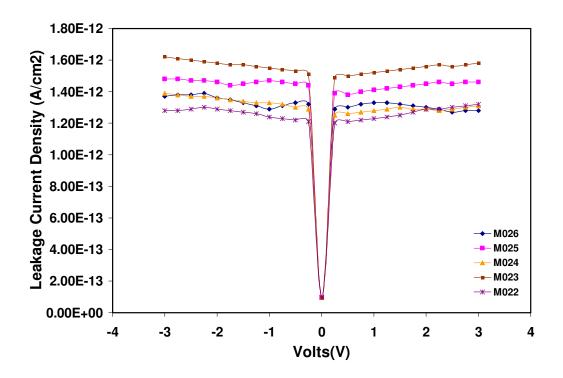

| 23. Leakage current density for various samples during deposition parameters optimization                                      |         |

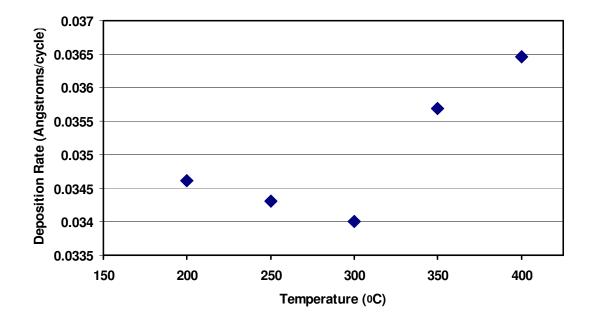

| 24. Temperature dependence on deposition rate                                                                                  |         |

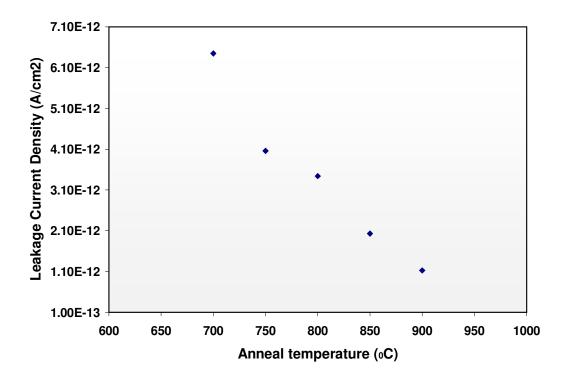

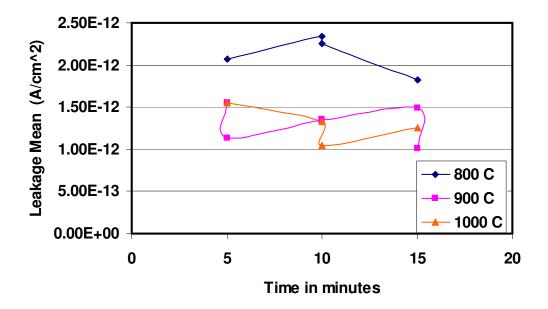

| 25. Anneal temperature dependence on leakage curre                                                                             | ent     |

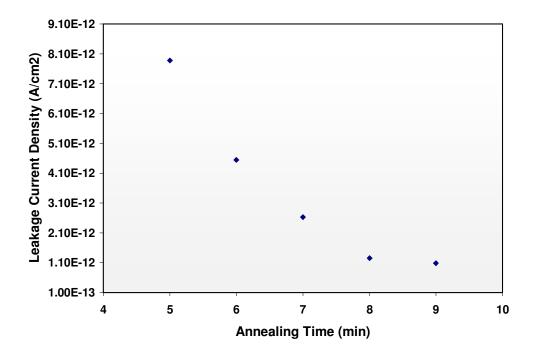

| 26. Anneal time dependence on leakage current                                                                                  |         |

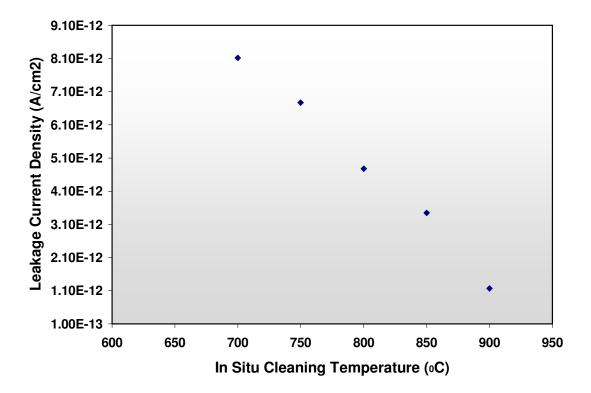

| 27. In-Situ cleaning temperature dependence on leak current                                                                    | -       |

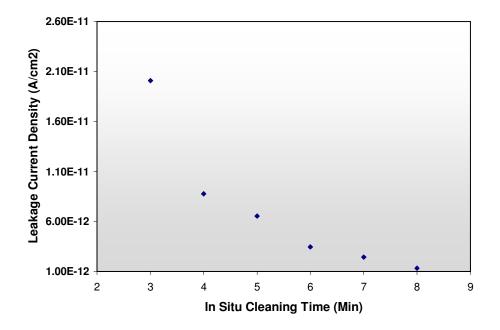

| 28. In-Situ cleaning time dependence on leakage cur                                                                            | rent 96 |

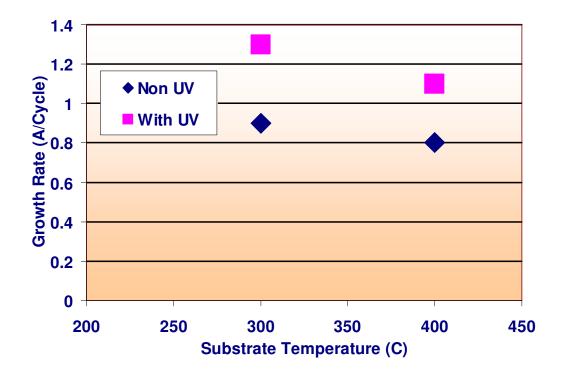

| 29. Dependence of UV on growth rate                                                                                            |         |

| 30. C-V measurements at 1 MHz                                                                                                  |         |

| Figures                                                                                                                                                                       | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <ol> <li>High-resolution cross-section TEM results in</li> <li>&lt;110&gt; direction of the HfO<sub>2</sub>/ Si (001) specimen showing the oxide and the interface</li> </ol> |      |

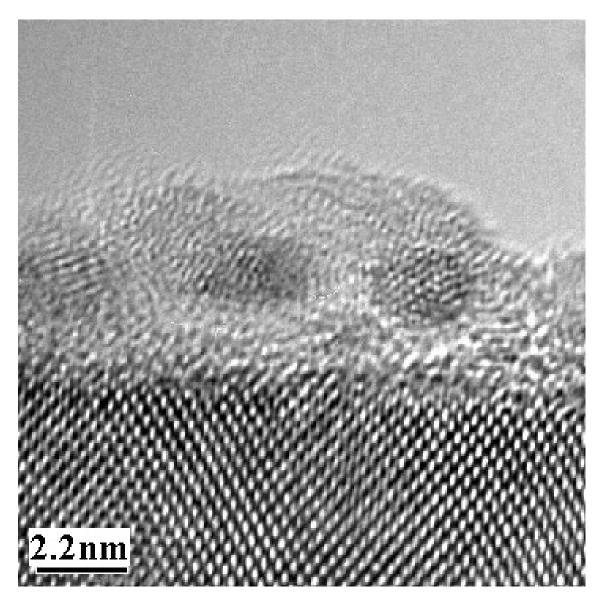

| 32. Atomic structure of oxide-silicon interface                                                                                                                               | 100  |

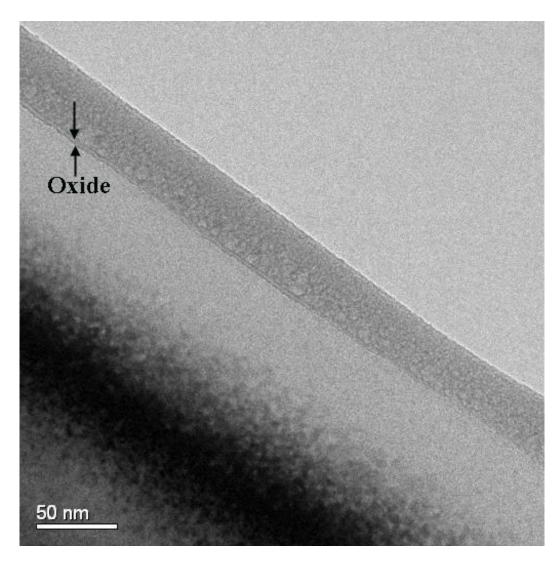

| 33. Cross-section transmission electron microscopy<br>micrograph showing the presence of HfO2 layer                                                                           | 101  |

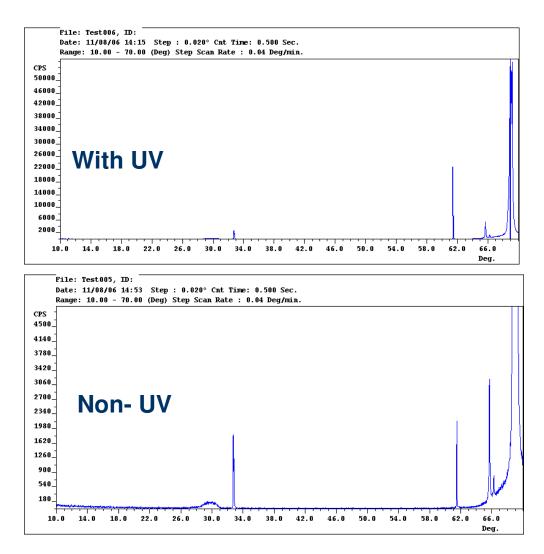

| 34. XRD Measurements for UV and Non-UV samples                                                                                                                                | 102  |

| 35. Leakage current density mean for optimized process recipe at various                                                                                                      | 103  |

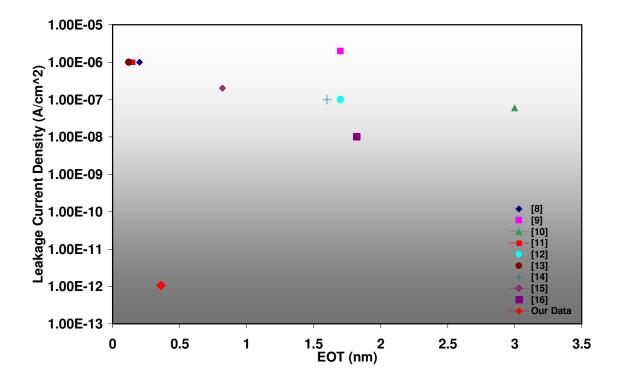

| 36. Comparison of published leakage current density data versus EOT                                                                                                           | 104  |

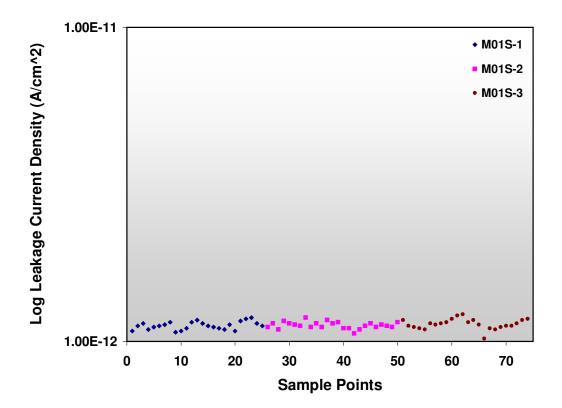

| 37. Repeatability of leakage current density for 3 samples                                                                                                                    | 105  |

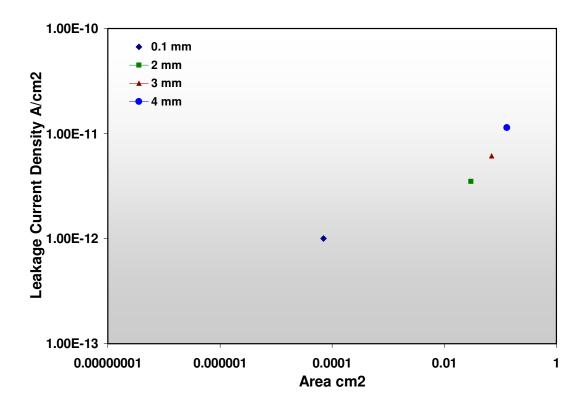

| 38. Area effect on leakage current density                                                                                                                                    | 106  |

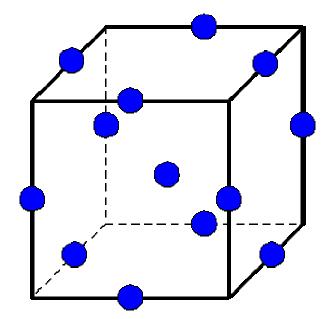

| 39. Illustration of a 3-factor Box Behnken design                                                                                                                             | 118  |

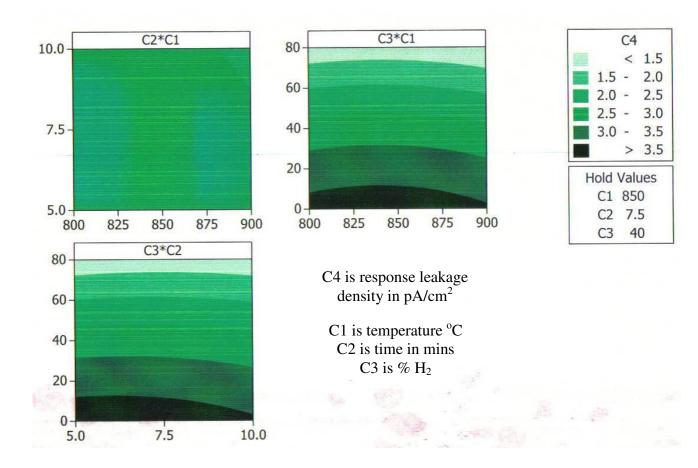

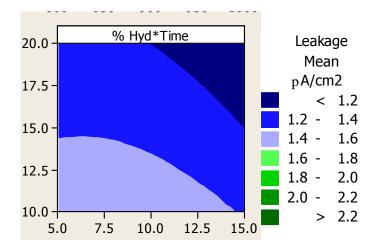

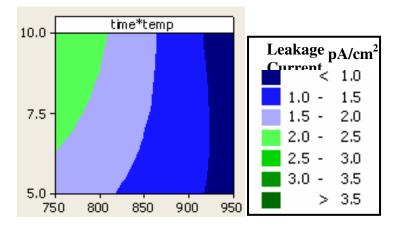

| 40. Contour plot for in-situ cleaning DOE                                                                                                                                     | 123  |

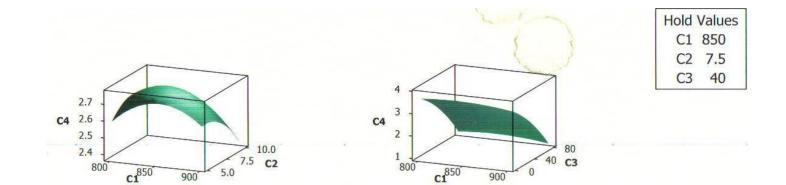

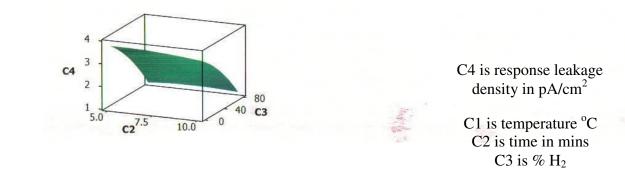

| 41. Surface plots for in-situ cleaning                                                                                                                                        | 124  |

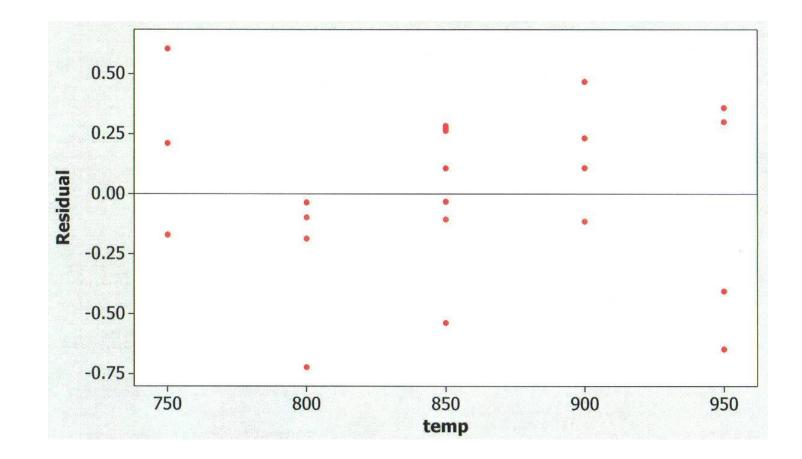

| 42. Residual plot for temperature                                                                                                                                             | 125  |

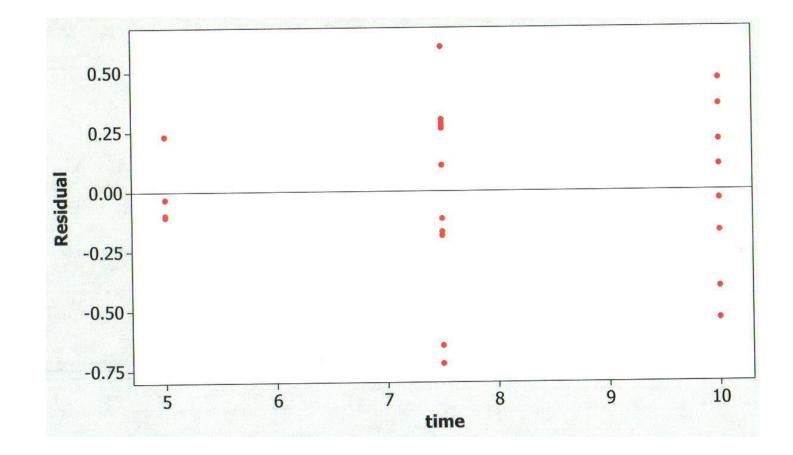

| 43. Residual plot for time                                                                                                                                                    | 126  |

| 44. Response surface and contour plots for optimization of in-situ cleaning time and temperature                                                                              | 127  |

| 45. Contour plots for optimizing in-situ time and hydrogen concentration                                                                                                      | 128  |

| 46. Contour plots for optimizing in-situ temperature and hydrogen concentration                                                                                               | 129  |

| Figures Page                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------|

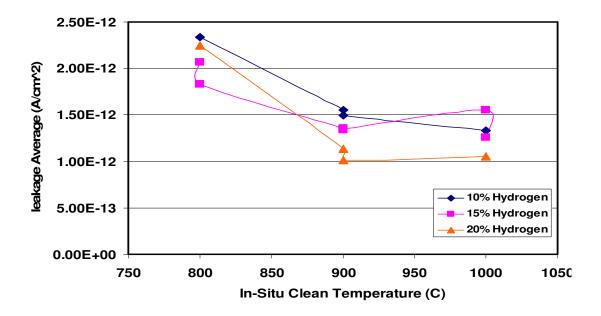

| 47. Leakage average vs. in-situ clean temperature                                                                                        |

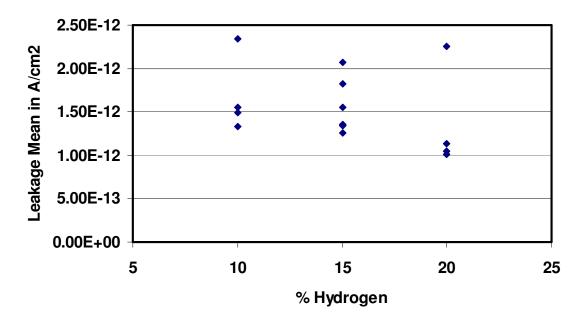

| 48. In-situ cleaning leakage mean vs. % hydrogen                                                                                         |

| 49. In situ cleaning leakage density vs. time in minutes                                                                                 |

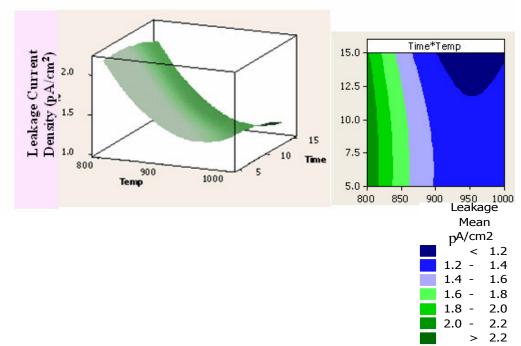

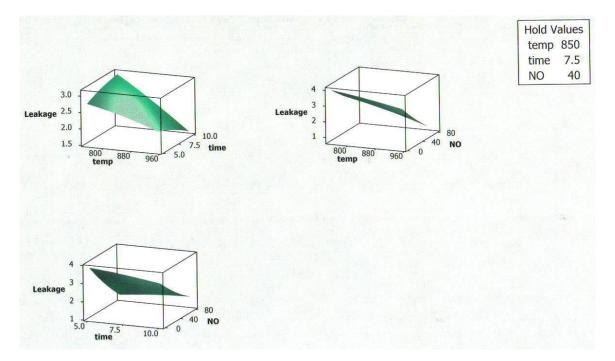

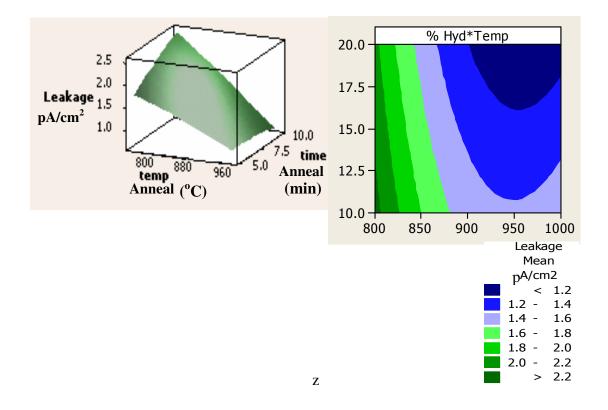

| 50. Surface response plot for annealing DOE                                                                                              |

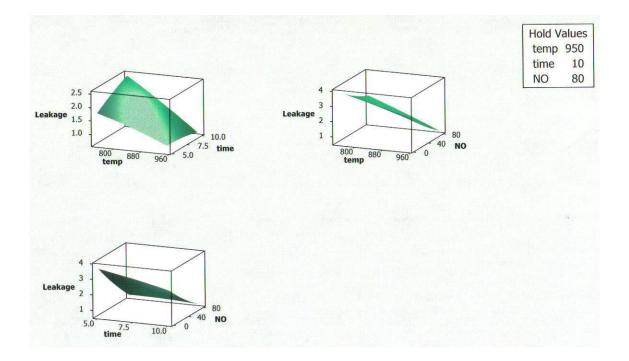

| 51. Surface response plot for annealing DOE with different hold values                                                                   |

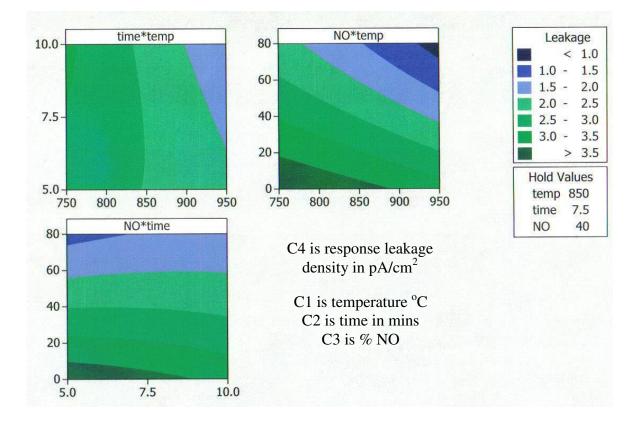

| 52. Contour plot for leakage current density for annealing DOE                                                                           |

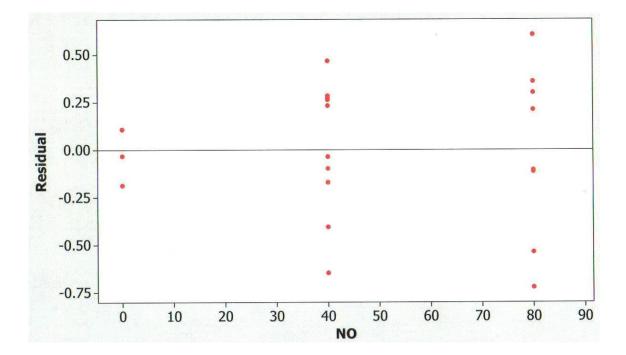

| 53. Residual plot for leakage versus % nitrous oxide                                                                                     |

| 54. Response surface and contour plots for optimizing annealing time and temperature                                                     |

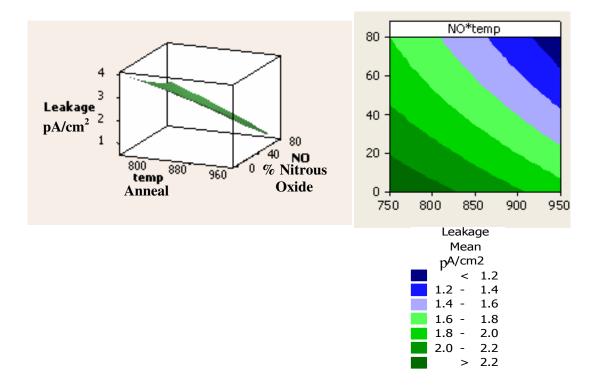

| 55. Response surface and contour plots for optimizing annealing temperature and nitrous oxide concentration                              |

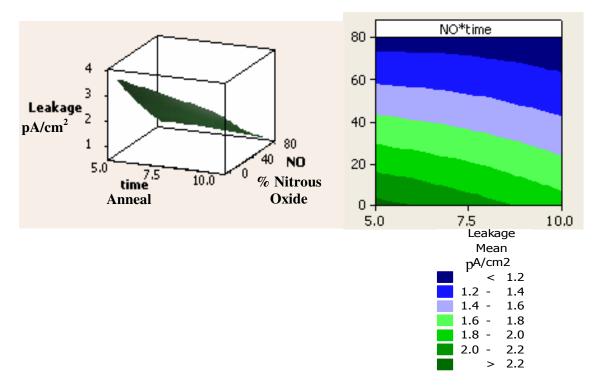

| 56. Response surface and contour plots for optimizing annealing time and nitrous oxide concentration                                     |

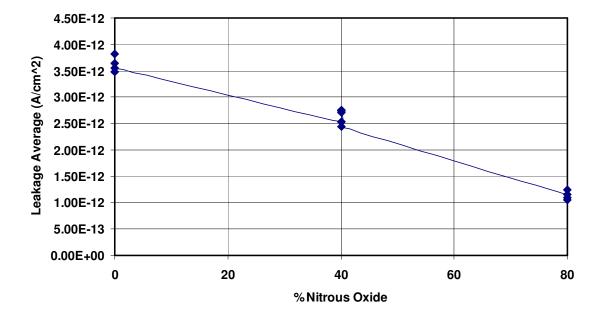

| 57. Leakage average for annealing vs. % nitrous oxide                                                                                    |

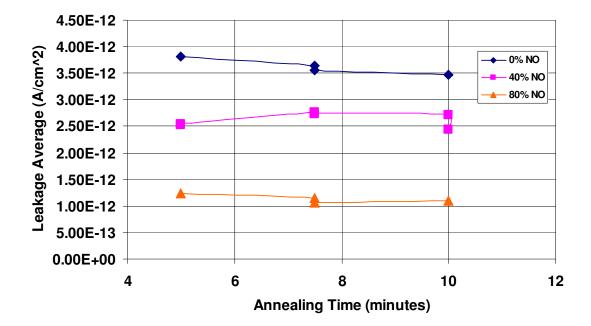

| 58. Leakage average vs. annealing time                                                                                                   |

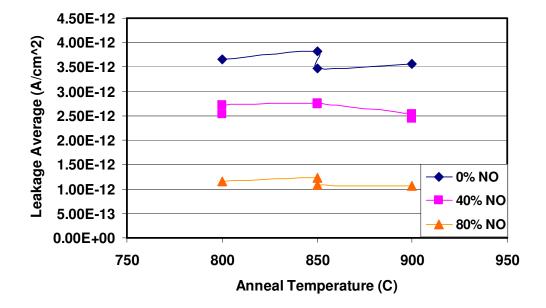

| 59. Leakage average vs. anneal temperature 145                                                                                           |

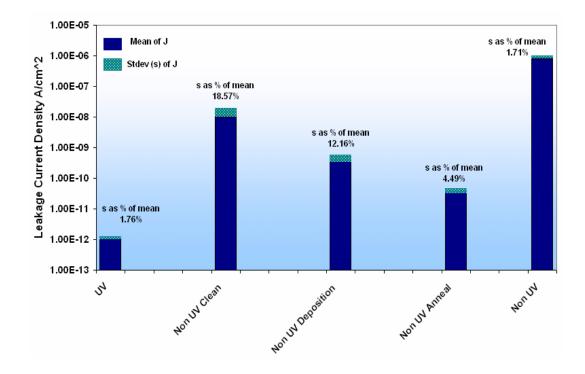

| <ol> <li>Effect of UV photons on process variation of leakage<br/>current for various steps used in<br/>the deposition process</li></ol> |

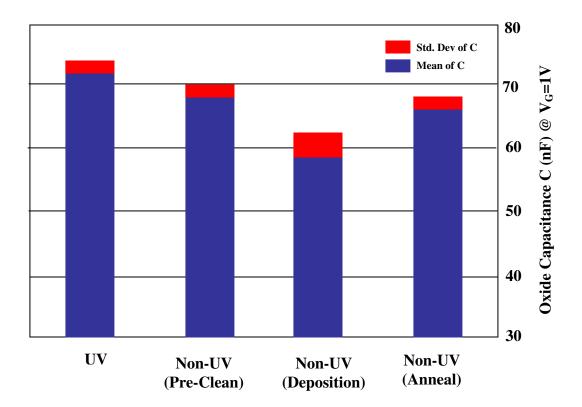

| 61. Mean capacitance values (@ VG = 1V)<br>and their standard deviations for gate<br>stacks processed using different UV treatments      |

| Figures                                                                                                  |       |

|----------------------------------------------------------------------------------------------------------|-------|

| 62. Mean leakage current densities for 6 samples after process optimization through design of experiment | s 149 |

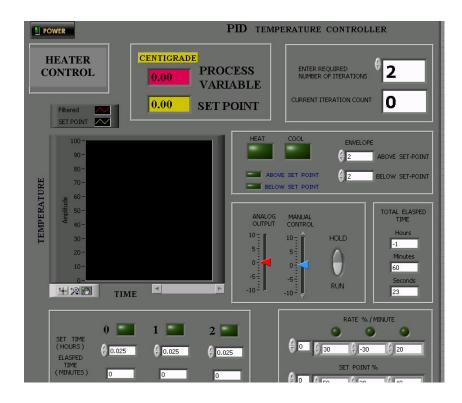

| 63. General Overview of Labview interface                                                                |       |

| Figures                                                                                                                 | Page |

|-------------------------------------------------------------------------------------------------------------------------|------|

| 64. SCC-68 Pinouts                                                                                                      | 164  |

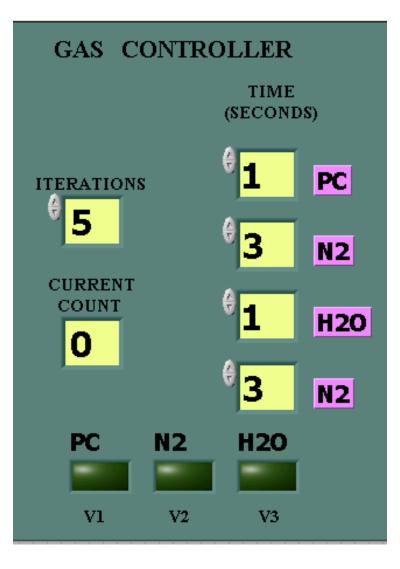

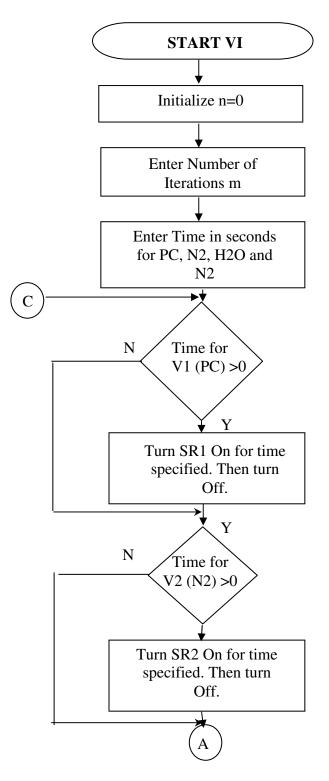

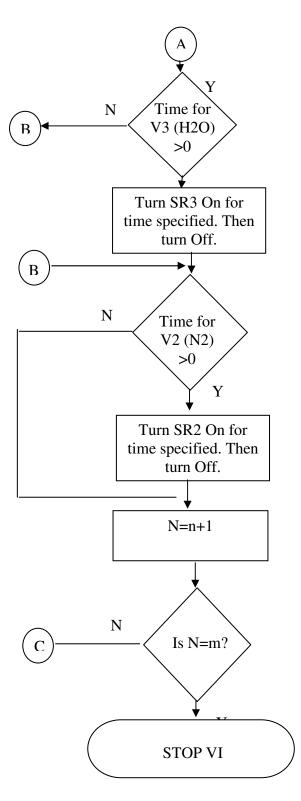

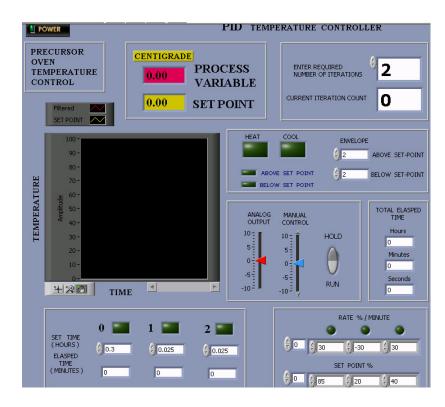

| 65. Gas Controller VI User interface                                                                                    | 167  |

| 66. Flowchart for gas controller VI                                                                                     | 168  |

| 67. Gas controller VI Code                                                                                              | 170  |

| 68. PID toolkit for precursor oven temperature control                                                                  | 171  |

| 69. PID toolkit for heater control                                                                                      | 172  |

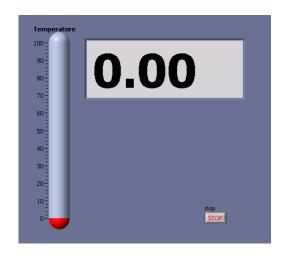

| 70. User interface for wafer temperature readout                                                                        | 173  |

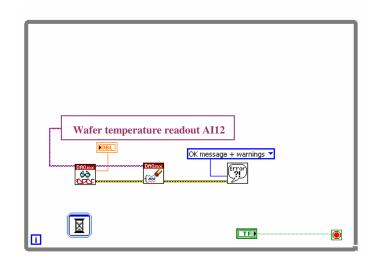

| 71. Labview VI for wafer temperature readout                                                                            | 174  |

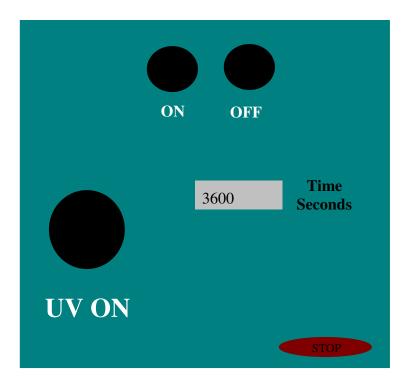

| 72. User interface for UV lamp control                                                                                  | 175  |

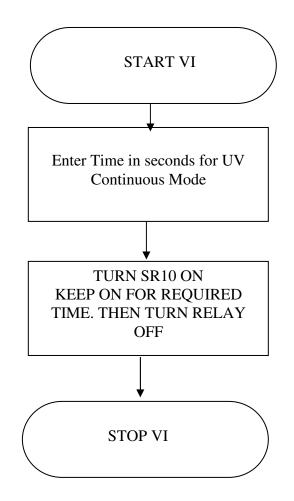

| 73. Flowchart for UV lamp control Labview code                                                                          | 176  |

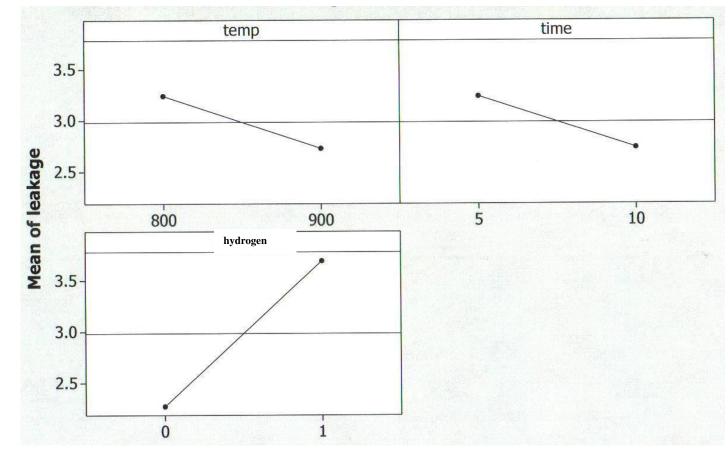

| 74. Main interactions plot for leakage response                                                                         | 178  |

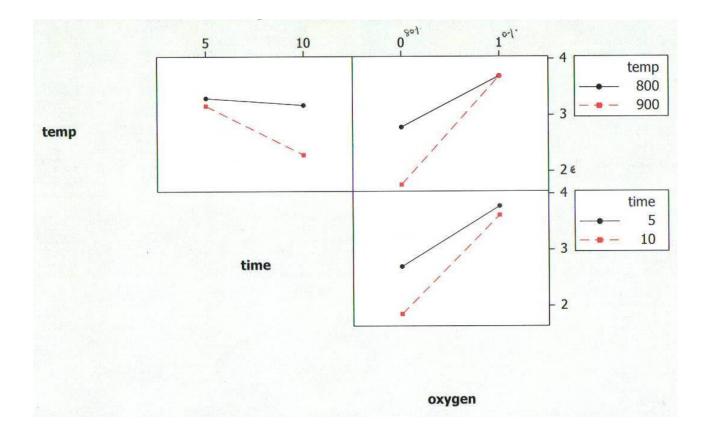

| 75. Main level interactions plot for annealing DOE                                                                      | 179  |

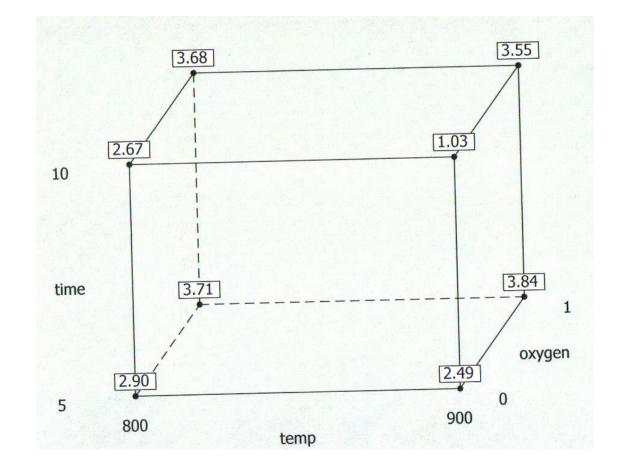

| 76. Cube plot for leakage (fitted means)                                                                                | 180  |

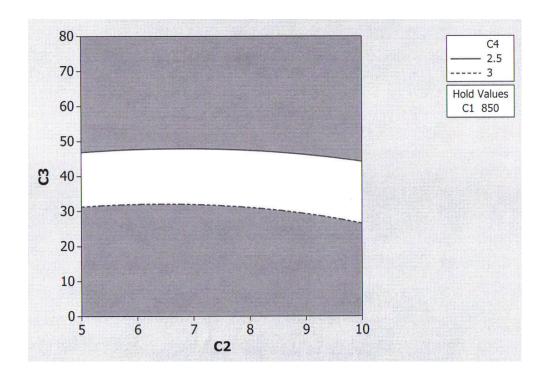

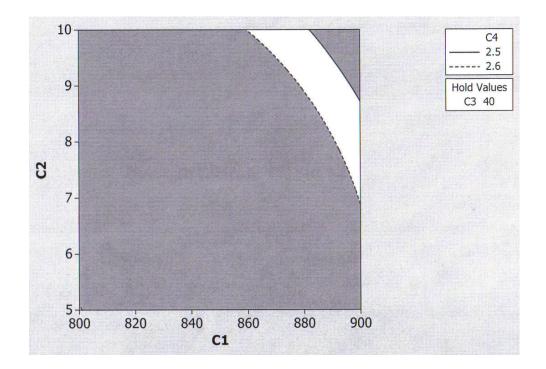

| <ul><li>77. Overlaid contour plot for annealing DOE</li><li>(C1 time, C2 temperature, C4 is leakage response)</li></ul> | 181  |

| <ul><li>78. Overlaid contour plot for annealing DOE<br/>(C1 time, C2 temperature, C3 % Hyd)</li></ul>                   | 182  |

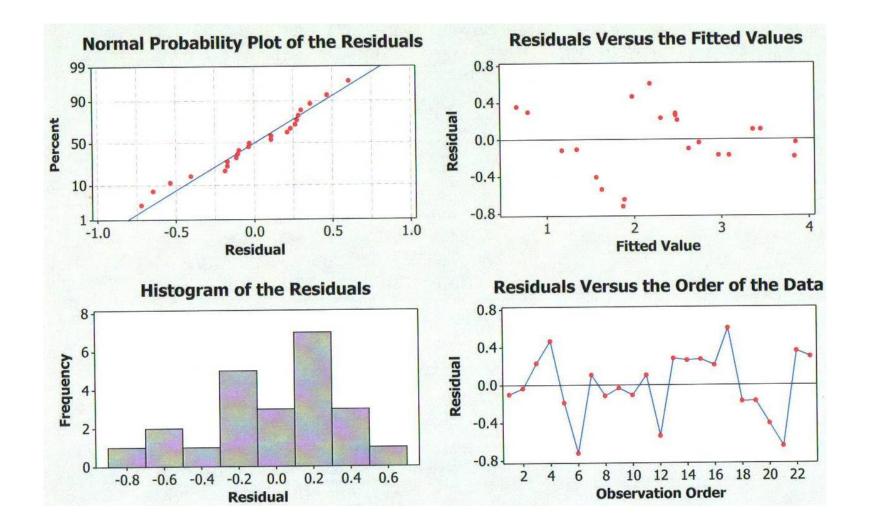

| 79. Descriptive statistics residual plot for annealing DOE                                                              |      |

| 80. SAS results for annealing DOE                                                                                       |      |

#### CHAPTER 1

#### INTRODUCTION

The introduction of high- $\kappa$  gate dielectrics in place of currently used silicon based gate dielectrics has the potential to push silicon complimentary metal-oxide-silicon (CMOS) technology to the fundamental limit of <10 nm feature size circuits. The ability of the semiconductor industry to continue scaling microelectronic devices to smaller dimensions is limited by quantum mechanical effects. As the thickness of conventional silicon dioxide (SiO<sub>2</sub>) gate insulators is reduced to just a few atomic layers, electrons can tunnel directly through the dielectric films. Continued device scaling will therefore require the replacement of the insulator with high-dielectric-constant (high- $\kappa$ ) oxides, to increase its thickness, thus preventing tunneling currents while retaining the electronic properties of an ultra thin SiO<sub>2</sub> film.

In Chapter 2, published results of high dielectric constant gate dielectrics have been analyzed with process integration and manufacturing criterions. Required materials, performance, process and manufacturing requirements of high-k dielectrics are outlined. A careful study of published results shows that from the materials point of view, the MOSFET data does indicate significant advantages of using hafnium-based compounds as the gate material compared to any other material reported so far. Research is underway in the semiconductor industry to meet the manufacturing needs for process integration requirements to implement high- $\kappa$  gate dielectrics. Based on the work reported in this dissertation, I propose a new tool/process for the integration of the metal/high- $\kappa$  gate dielectric stack in the currently used CMOS fabrication sequence. In Chapter 3, discussion on the development of rapid photothermal based mono layer deposition (RTPMLD) system is presented. Also, discussion on the basics of mono layer photoassisted deposition and UV based RTP or rapid photothermal process (RPP) is presented. Description of the system is detailed and some key features are discussed. It is shown that the RTPMLD processed gate dielectric has the potential to solve some of the manufacturing and process integration issues currently faced by the semiconductor industry. RTPMLD deposition of  $HfO_2$  films showed a significant reduction in leakage current density as well as an increase in capacitance per unit area. Automation of the RTPMLD system was carefully designed using Labview 8.2 software from National Instruments for precise delivery of the MLD reactants and substrate heater control and this is described in Chapter 3. This automation enables the RTPMLD system to be robust, reliable and extremely precise for repeatable performance.

In Chapter 4, the impact of zero gate leakage current density on future CMOS technology nodes is discussed. The MLD process is characterized in great detail using the precursor tetrakis dimethyl amido hafnium (TDMAH) outlining critical and noncritical processes for growth rate, deposition cycles, temperature dependence and dielectric thickness. Results are reported for optimized process parameters. For effective oxide thickness of 0.39 nm, we have achieved a leakage current density as low as  $1 \times 10^{-12}$  A/cm<sup>2</sup> at a gate voltage of +3 to -3 V. The leakage current density of 1.06 x  $10^{-12}$  A/cm<sup>2</sup> for an EOT of 0.39 nm at 1 V represents the lowest value of leakage current reported by any one to date. The comparison in terms of leakage current density vs. EOT between our results and other reported results in the literature is shown. It shows that our leakage

current density with an EOT of 0.39 nm is four orders of magnitude lower than the best published results at higher EOT values. Detailed high resolution transmission electron microscopy (HRTEM) studies are also reported here. In the TEM micrographs, the interface between  $HfO_2$  and Si(001) is atomically sharp and shows that the hafnium oxide layer appears conformal to the (100) silicon substrate having a uniform thickness. These two features along with the thin interfacial oxide layer hold the key to the excellent electrical properties for RTPMLD processed  $HfO_2$ . Finally, a brief discussion on repeatability and the effect of the front contact area are discussed.

In Chapter 5, the statistical optimization of process parameters is outlined for exsitu/in-situ cleaning, deposition and annealing steps. A number of experiments were designed to achieve the lowest leakage current density through Box-Behnken multivariate design techniques. Statistical software, MINITAB, was used to outline surface and contour plots for optimizing the various parameters. Several samples were generated at the same optimal processing conditions to determine the descriptive statistics for leakage current density and capacitance and the results are reported here. Thermal processing of dielectrics is an integral part of advanced semiconductor manufacturing. The advantages of using UV assisted RTP were exploited to process thin dielectric films and is also reported in Chapter 5. The electrical data, after optimizing for all the parameters, is analyzed by statistical methods and the results are compared with 1% level of significance.

Finally, a summary of the significance of the work presented in this study is given in the conclusion chapter.

#### **CHAPTER 2**

#### HIGH-K GATE DIELECTRIC ISSUES

#### Introduction

Silicon dioxide has served for more than three decades as the gate dielectric material in CMOS devices. The reason for the nearly exclusive use of silicon dioxide in this application is that silicon dioxide uniquely possesses the required combination of several properties: good mobility of holes and electrons flowing in silicon at the silicon dioxide interface, ability to keep electronic states (surface states) at this interface low, relatively low trapping rates of holes and electrons, and excellent compatibility with CMOS processing. CMOS processes in current production feature oxides as thin as 1.2 nm, and device physics requires that this thickness must be further reduced to enable continued scaling improvements in density, performance, and power in very large-scale integrated (VLSI) circuits. Thus, understanding of the reliability of such thin oxides is critical [1-5]. Tunnel current limitations and newer dielectric reliability projections of the gate insulator continue to threaten an end to CMOS scaling unless a suitable replacement for silicon dioxide is soon developed [3-5].

Integrating new materials into a standard CMOS device flow raises many challenges in regard to compatibility with the currently used gate electrode materials, particularly the silicon surface itself [6]. Although several new high-k materials have been researched for several years now, there have been several roadblocks to integrating these materials to the 65 nm node [7]. This study attempts to look at these issues and suggest solutions for the successful integration of high-k dielectrics.

#### <u>Need for a High-κ Gate Material</u>

In a recent publication we have outlined the needs of the semiconductor manufacturing industry in the 21<sup>st</sup> century [8]. In order to meet the needs of the 45 nm technology node, high- $\kappa$  material has to be introduced. The challenges of integrating high-k into the existing CMOS process flow is discussed in great detail here [9]. Figure 1 shows the normalized total chip power dissipation versus the physical gate length and corresponding years of possible production of high- $\kappa$  [10]. The possible trajectory with the inclusion of high- $\kappa$  dielectrics shows a clear reduction of the total chip power dissipation.

Theoretically, the improved performance that is obtained when scaling logic device dimensions is seen clearly when you consider a simple model for the drive current associated with a FET [11]. The drive current can be written using the gradual channel approximation as:

$$I_{D} = \frac{W}{L} \mu C_{ox} (V_{G} - V_{T} - \frac{V_{D}}{2}) V_{D}$$

(1)

where W is the width of the transistor channel, L is the channel length,  $\mu$  is the channel carrier mobility (assumed constant here), C<sub>ox</sub> is the capacitance density associated with the gate dielectric when the underlying channel is in the inverted state, V<sub>G</sub> and V<sub>D</sub> are the voltages applied to the transistor gate and drain respectively, and the threshold voltage is given by V<sub>T</sub>. Here the drain current is proportional to the average charge across the channel (potential is V<sub>D</sub>/2) and the average electric field (V<sub>D</sub>/L) along the channel direction. Initially,  $I_D$  increases linearly with  $V_D$  and then eventually saturates to a maximum when  $V_{D,sat} = V_G - V_T$  to yield

$$I_{D,sat} = \frac{W}{L} \mu C_{inv} \frac{\left(V_G - V_T\right)^2}{2}$$

(2)

The term ( $V_G - V_T$ ) is limited in range due to reliability and room temperature operation constraints, since a very large  $V_G$  would create an undesirably high electric field across the oxide. Further,  $V_T$  cannot be easily reduced below 200 mV, because kT ~ 25mV at room temperature. Typical specification temperatures ( $\leq 100^{\circ}$ C) could therefore cause statistical fluctuations in thermal energy, which would adversely affect the desired  $V_T$ value. Thus, even in this simplified approximation, a reduction in the channel length or an increase in the gate dielectric capacitance will result in an increased I<sub>Dsat</sub>.

In the case of increasing the gate capacitance, consider a parallel plate capacitor (ignoring quantum mechanical and depletion effects from a Si substrate and gate) [11]

$$C = \frac{\kappa \varepsilon_0 A}{t} \tag{3}$$

where  $\kappa$  is the dielectric constant or the relative permittivity of the material [12].  $\varepsilon_0$  is the permittivity of free space (8.85X10<sup>-3</sup> fF/µm), A is the area of the capacitor, and t is the thickness of the dielectric. This expression for C of the capacitor can be rewritten in terms of t<sub>eq</sub> which is equivalent oxide thickness, and  $\kappa_{ox}$ , which is the dielectric constant of Si, 3.9. The term t<sub>eq</sub> represents the theoretical thickness of SiO<sub>2</sub> that would be required to achieve the same capacitance density as the dielectric (ignoring issues such as leakage current and reliability). For example, if the capacitor dielectric is SiO<sub>2</sub>,

$$t_{eq} = 3.9\varepsilon_0 \left(\frac{A}{C}\right),\tag{4}$$

and a capacitance density of

$$\frac{C}{A} = 34.5 fF / \mu m^2 \tag{5}$$

corresponds to  $t_{eq}=10$  Å. Thus the physical thickness of an alternative dielectric employed to achieve the equivalent capacitance density of  $t_{eq}=10$  A<sup>o</sup> can be obtained from the expression

$$\frac{t_{eq}}{\kappa_{ox}} = \frac{t_{high-\kappa}}{\kappa_{high-\kappa}}$$

(6)

or simply,

$$t_{high-\kappa} = \frac{\kappa_{high-\kappa}}{\kappa_{ox}} t_{eq} = \frac{\kappa_{high-\kappa}}{3.9} t_{eq}$$

(7)

A dielectric with a relative permittivity of 16 therefore affords a physical thickness of ~40 A<sup>o</sup> to obtain  $t_{eq}$ =10 A<sup>o</sup>. In reality, actual performance of a CMOS gate stack does not scale directly with the dielectric due to possible quantum mechanical and depletion effects [10].

#### Required Properties of a Suitable Material

The new dielectric must satisfy a number of requirements based on material, properties, device performance and reliability. A complete understanding and control of these requirements can lead to the successful integration of high- $\kappa$  dielectrics into the manufacturing sequence. In the following subsections, some critical properties of high- $\kappa$  materials that are relevant for low power and ultra fast electronics are discussed.

#### a. Crystal Structure

The high- $\kappa$  dielectrics can be either crystalline or amorphous in nature. In general, high dielectric constant materials do not remain amorphous at the temperature (about 900°C or more) used in processing silicon CMOS. Therefore, the crystal structure and the lattice constant of a material may be important parameters in deciding the quality of the silicon-dielectric interface. It is known that the crystalline structure should be identical to that of Si. The amount of deviation from that of the silicon structure will determine the defect density and the lattice strain at the interface, and those may also determine whether the presence of an interfacial SiO<sub>2</sub> layer is desirable or not [13].

#### b. Band Offset and Electron Affinity

The tunneling current depends on the carrier effective mass, m, in the dielectric, the barrier height between the silicon and the conduction or the valence band of the insulator,  $\Phi_{\rm B}$ , and the barrier thickness t<sub>di</sub>. The tunneling probability for a rectangular barrier can be expressed as [10]:

$$T \equiv \exp\left(-2\frac{\sqrt{2mq}}{h}\right)\sqrt{\phi_B t_{di}}$$

(8)

The issue of the bandgap and electron affinity of high- $\kappa$  dielectric materials was discussed in [14]. In recent years, improved methods of calculations of band alignments of different oxides with respect to silicon have been reported [15]. However, in calculating the values of barrier height, the effect of image force barrier lowering should be considered, which is given by [10, 16]:

$$\Delta\phi_B = \sqrt{\frac{qE}{4\pi\kappa\varepsilon_o}} \tag{9}$$

where, E is the electric field at the interface, and  $\varepsilon_0$  is the free space permittivity. For SiO<sub>2</sub> at E=1.5x10<sup>7</sup> V/cm, the barrier lowering is 0.75 V, while for a value of  $\kappa$ =25, the value of  $\Delta \Phi_B$  is about 0.3 V.

#### c. Melting Point

Melting point of a material is very crucial [17]. High bandgap materials should have high a melting point. Lack of high melting point indicates inherent imperfection of the material (like weak bonds: contrast the melting point of diamond with that of graphite). Another important point is that deposition of a film much below the melting temperature tends to produce defects in the material. Addition of different types of energy sources (e.g. visible and ultra violet photons) along with thermal energy may be needed to increase ionization energy as well as atomic mobility, in order to obtain a defect free dielectric.

#### d. Device Requirements

The success of the silicon CMOS transistor as a high speed, low power, and low cost device is attributed to a large extent to the excellent quality of  $SiO_2$  as the gate dielectric, as well as the excellent properties of the Si-SiO<sub>2</sub> interface. Any new gate dielectric material must satisfy a number of device requirements described in the following sections.

#### 1 .Leakage Current Density

The leakage current of current high- $\kappa$  based metal-insulator-semiconductor (MIS) structure should be atleast two or three orders of magnitude lower than the leakage current of the corresponding MOS (metal-SiO<sub>2</sub>-silicon) structure with the same equivalent oxide thickness. Only under these conditions, the gate current will be negligible as compared to the drain current. Thus, from both the device performance and reliability point of view, and also from the power dissipation consideration, the leakage current criterion is critical for the use of high- $\kappa$  dielectrics in the future generations of CMOS.

#### 2. Bulk and Interface Defects

The interface between the insulator and silicon is extremely important for optimum device performance. Any particular mechanism that is responsible for the creation of defects and the manner in which they are responsible for dielectric degradation are still under debate. Most researchers believe that the creation of defects is related to the passage of electrons (and/or holes) through the dielectric. It is also well accepted that the energy of the electrons has a direct effect upon the generation of such defects and specifically the rate at which such defects are produced. An understanding of the carrier transport mechanisms is therefore a key to identifying the nature of defect generation. For example, if we consider the Si-SiO<sub>2</sub> system, the interface is atomically abrupt and electrically perfect to first order [18, 19]. Although the Si-SiO<sub>2</sub> system produces a virtually perfect electrical interface with trap and fixed charge densities corresponding to less than

one surface defect in  $10^5$  surface silicon atoms [19]. Thus, high- $\kappa$  dielectric based transistors will require control of nanoscale atomic roughness at the Si-dielectric interface, and structural homogeneity is crucial for obtaining the desired performance and reliability.

#### 3. Mobility

The drain current of a CMOS device is directly proportional to mobility. It has been shown recently [20] that even for a nanoscale MOSFET, mobility is an important factor in determining the on current, as long as the device does not approach the ballistic limit. A low value of the midgap interface state density does not guarantee that mobility will not be degraded under device operating conditions [20]. Therefore one of the major issues in the development of high- $\kappa$  materials is to achieve low defect density for the Sihigh- $\kappa$  system, so that the mobility does not degrade. Perfectly controlled ultrathin (1-2 monolayer) high quality silicon-oxide (SiO<sub>2</sub>) layer may be required to obtain mobility comparable to the Si-SiO<sub>2</sub> system.

#### 4. Power Dissipation

The leakage current has become a very important issue and will present the most important obstacle for sub 45 nm designs. As can be seen from Figure 2 [21], while the active power remains approximately the same with the decreasing technology nodes, the leakage power is increasing. Hence, controlling this sensitive nature of leakage current will be the toughest challenge for both designers and manufacturers. A waste of more power in leakage current would imply more energy to do the basic operation of moving the carriers from source to drain which means more of battery power will be drained. Leakage power is the dominant component of future nodes of technology. As Figure 2 points out, at the 50 nm node, the significant power problem is induced by the leakage component as opposed to the short circuit or switching power though they dominated in previous nodes of technology.

Sub threshold leakage power increases exponentially and accounts for about 42% of the total power in the 90nm technology [22]. The goal is to maximize the drive current, that is, the ratio between  $I_{ON}$  and  $I_{OFF}$ , but at the same time reduce the leakage current to minimize power utilized by the chip. Techniques such as strained silicon [18, 22], stack effect [23], and reverse body bias [24] are being investigated for reduction of leakage power. Leakage power reduction being the main focus of low-power design, sleep transistors is one such solution where the majority of the functional blocks are only active for a small fraction of time. The use of the sleep transistors lowers leakage by the stack effect, where when functional block enters standby mode, sleep transistor isolates the supply from the block [22, 24]. Although this may be a solution to reducing leakage, the side effects include functional blocks incurring performance degradation during active operation and increase in area on the chip [25] among others; however, it is the most effective technology as technology scales.

#### e. Metal Gate Considerations

For the future generations of CMOS, metals have to be used as gate electrodes because of the problems related to polysilicon. Thus it has been shown that the entire gate stack has to be changed [23, 25]. In the case of metals, the gate electrode formation should occur during the final part of the process to avoid high temperatures and acids [10, 25]. The

damascene process will make it more complicated. Another problem concerning metal gate is that the work function of the gate electrode has to be selected in such a way that these are different for NMOS and PMOS, in order to adjust the threshold voltage to the optimum values. The combination of the high- $\kappa$  gate dielectric with the metal gate enables a drastic reduction in current leakage while maintaining very high transistor performance, making it possible to drive and technology innovation well into the next decade. In order to achieve optimum device performance, work functions close to the band edges of silicon are desired. Materials with nearly the correct work function can be selected from the periodic table, but the integration of any two metals in a CMOS flow is very challenging.

#### f. Reliability Requirements

Early failures will become more important for the future generations of circuits [28]. The breakdown voltage of high- $\kappa$  dielectrics is reasonably high enough for low voltage operation of the future generation devices. Defect generation both at the interface and in the bulk of the dielectric is directly related to the microstructure of the high- $\kappa$  dielectric material [29]. Structural homogeneity will assure minimal defects in the starting material as well as defects generated during the lifetime of the device [26]. Particular attention needs to be paid to the trap generation and the impurities in the dielectric material. This will require the introduction of new concepts such as built-in reliability material. In other words, the process has to provide a perfect microstructure to assure the desired reliability [27]. The following steps, that were suggested to improve the reliability of the thin gate oxides, will also be applicable to high- $\kappa$  dielectrics.

- a. Careful monitoring of the intrinsic structural wearout will need to be carried out, as these are reliable indicators of dielectric quality [31, 32].

- b. Statistical tools developed for the silicon-based dielectrics will be equally applicable to high- $\kappa$  dielectrics.

In reality, integrated circuits operate in ac mode. The stress on the dielectric film caused by the ac operating mode is considered to be less destructive compared to the dc stress, and the ac lifetime might be considerably longer than the dc lifetime [30]. If we consider the stress due to ac operating conditions as a restoring mechanism, then under the normal operating conditions, the reliability of the device will increase [31]. These results will need to be included, since the fast switching field may affect the high- $\kappa$  dielectric degradation in opposing ways.

A number of fundamental questions are still being resolved for the reliability requirements of the sub-45 nm technology node [28, 29]. These include:

1. Whether the mechanism of defect generation, at the semiconductor-dielectric interface and in the dielectric bulk, is basically different, for very low supply voltages and ultra-small gate areas, from the current models [28, 29]. In the case of ultra-small area and leaky gates, the stored energy in the capacitor may not suffice for an electrostatic discharge. In which case, dielectric and interface degradation would be more important and relevant than dielectric breakdown. In a tunnel gate dielectric, how relevant is the concept of hot electron injection into the dielectric [28]? The electron, tunneling through the gate dielectric, cannot be expected to expend any energy in the dielectric bulk. And, even if some electrons

are injected into the dielectric, would they have the energy for the generation of bulk defects, when the supply voltage is very low? In such a situation, would not the interface defects be more important than the bulk defects [30]?

2. In the case of very low supply voltages, ultra-small gate areas and high operation temperatures, how reliable are the current reliability evaluation procedures, particularly the voltage and area scaling procedures [28, 29]? For example, even now, all the voltage stressing is done above 2.0 V, often above 3.0 V, while the future circuits will operate at 0.7 – 1.0 V. Are the extrapolations from 2.0 – 3.0 to 0.7 – 1.0 V not too far fetched, in the light of the questions above?

#### g. Yield and Defect Management

Detection of ever shrinking yield-critical defects, high aspect ratio defects, nonvisual defects, and timely elimination of yield detracting systematic mechanisms top the list of challenges for yield enhancement for 45 nm and beyond. Moreover, the yield enhancement community is constantly challenged to achieve acceptable yield ramp and mature yields due to increasing process complexity and fewer yield learning cycles with each subsequent technology node [31]. The design for yield should basically incorporate the two most important ideologies of design for test and design for manufacturing.

(a) Cost-effective high throughput, high aspect ratio inspection tools are needed urgently to achieve acceptable yields for current and future process technology nodes [32].

- (b) With increasing process complexity and longer cycle times, tools and methods are needed to increase the number of yield learning cycles for each technology node.

- (c) With a move to smaller features, longer processes, 300 mm wafers, and new materials (low k, high k, etc.), numerous tools and methods are required to understand all yield detracting interactions. Use of SOI, new gate dielectrics and compound semiconductors will further challenge yield learning [26].

- (d) Signal-to-noise improvements are required for defect metrology tools to detect ever shrinking critical defects of interest [33].

Defects enter the cost function at many levels. Firstly, minimizing the process related defects reduces costs of monitoring defects plus the cost related to excluding defected products. Minimizing process-generated defects improves yields and hence die costs. SWP has significant advantages over BP in keeping process related defects to a minimum. Secondly, defected components will fail early in service so this ends up as a cost function to the user. Current practice puts a lot of emphasis on defect monitoring, defect classification, and defect control after processing. The number of process steps that can be completed in-situ clearly reduces the defect density, leading to increased yield and ultimately lower costs.

Although scaling of CMOS technology [the design/process] is being pushed, it doesn't translate to system-level performance because of the leakage and yield issues. The yield enhancement challenges continue to grow with each subsequent technology node. Given the demanding requirements and the above issues, it will be highly unlikely to achieve historical yield levels in the future unless the drastic approach is changed. The only realistic solution to achieve high-yield levels is to have the signature of the tool as early as the design stage.

#### h. Throughput and Cost of Ownership Issues

With continuous increase in the cost of modern IC fabrication facilities, issues such as throughput, equipment utilization, cost of ownership, etc., have become more important than ever. However, due to the importance of high- $\kappa$  dielectrics in the development of sub-45 nm CMOS, these factors may be more tolerable than for other processing steps. Thus, even the low throughput processes (e.g. atomic layer chemical vapor deposition) may be acceptable provided they offer the desired performance, reliability and yield.

#### i. Low Temperature and Short Time Processing

Enhancement of product yield by controlling different parameters responsible for process fluctuation is going to be more important than ever for nanometer scale gate manufacturing. The surface and related interface nano-roughness of the deposited or a grown material is very important for sub-45 nm feature size geometries. Lower roughness can result in better electrical properties, such as high mobility, low leakage current and better reliability. In any deposition process, one of the major reasons for the formation of surface roughness and defects is the statistical roughening, which arises because of statistical fluctuation in the arrival of the vapor flux. The fluctuation in flux increases with processing temperature. During the deposition, statistical roughening and surface diffusion compete with each other, the first increasing the film roughness and the second smoothing it out. It is well known that at lower processing temperatures, the quality of dielectrics and throughputs are inferior compared to dielectrics processed at higher temperatures. Thus, at a lower processing temperatures, activation energy reduction for a thermal process can be achieved by using plasmas, photons with wavelength less than infrared, ions, electrons or sonic energy sources. Out of these additional sources of energy, the use of ultra violet (UV) photons for in-situ substrate cleaning, growth or deposition, and in-situ cleaning is very attractive, since these photons provide beneficial effects in reducing microscopic defects, processing temperature and processing time. Combined with rapid thermal processing (RTP), UV photons can be used in developing better thermal processing for sub-45 nm IC manufacturing [37-39].

#### j. Metrology Related Issues

In order to control the microstructure of the dielectric film, in-situ process control may become a necessity. It has been observed that there is a one to one correspondence between the defects and stress of the dielectric film [40]. Thus, by in-situ monitoring of stress, the homogeneity of the microstructure may be accomplished. Recently, several issues related to metrology need for high- $\kappa$  dielectrics was discussed in great detail [41].

#### k. Manufacturing Requirements

As we look forward to the 45 nm technology nodes, technical challenges arise in virtually every aspect of manufacturing. The challenges the industry faces involve more new materials and technologies, including new gate materials and designs, wider use of engineered substrates such as SoI, and the need for more powerful inspection and metrology tools, among many other issues [41]. Besides introducing these new materials and processes, we need to solve the integration issues in CMOS processing. The push for

new materials to increased frequencies creates challenges with deposition, patterning, integration and inspection, as well as packaging. Fab automation continues to be important, not only in terms of optimizing yield and fab efficiency, but also in terms of supply chain management. Equipment and materials suppliers, and their own suppliers of components and subsystems, are developing tools to meet these challenges. Without a doubt, process control, yield, defect management and process variation are major obstacles facing those considering technology requirements for work at the 45 nm node.

Key points that will provide the paradigm shift for integrating high-k dielectrics at 45 nm node and beyond:

- (i) Manufacturing at 45 nm node & beyond is no more a game of evolution of existing processes and materials. Only the top integrated device manufacturers (IDM's) and most advanced foundries will be the key future players.

- (ii) Most of the advanced 300 mm fabs employ about 80 % of the wafer manufacturing steps by single wafer processing and other 20 % by batch processing [43]. The cycle time for such fabs is about 90 days. On the other hand for single wafer processing fabs the cycle time is about 30 days. Packaging has become more important than ever. For advanced semiconductor products, wafer level packaging is gaining grounds. System on chip is a long term universal solution, and system in package is a near term profitable solution. The use of single wafer manufacturing in both

wafer processing and the wafer level packaging has the potential to reduce the volatility of the semiconductor industry (through better supply chain management). These issues are discussed at length in recent publications [25, 44-45].

- (iii) The industry is moving from design for manufacturing (DFM) [management of technology constraint (rules, lithography) applied to a design] to design for yield (DFY) [management of design's sensitivity to the manufacturing process]. Both designers and manufacturers have to interact more closely than in the past. This favors location of foundry and fabless design house in close proximity.

- (iv) With the fab tool signature existing right from the design stage combined with the benefits of single wafer manufacturing, high yield levels, and throughput and cost considerations can be incorporated into the tool. This will benefit Optical Proximity corrections (OPC), Automation Process control (APC) and manufacturing variations to be worked into the tool very early, benefiting the overall profitability and performance

#### Analysis of Published Results

There have been legitimate debates in terms of developing and processing a high- $\kappa$  gate dielectric material for several years. Recently, in January 2007, Intel Corporation announced that it will incorporate the use of high- $\kappa$  dielectrics (hafnium based compounds) for the 45nm technology node. Although a number of materials have been

proposed as a potential high dielectric constant gate material, hafnium based compounds have emerged as the current material of choice. The published results shown here were compared based on the leakage current density J ( $A/cm^2$ ) and EOT figures of merit. The lowest reported leakage current density in the open literature, to the best of our knowledge to date, is presented by Mikelashvili et al [46] to be 1.6 x 10<sup>-8</sup> A/cm<sup>2</sup>. It will be shown in Chapter 4 that our leakage current density with an EOT of 0.39 nm is four orders of magnitude lower than the best published results at higher EOT values [47].

#### Process Integration Considerations

Variations due to the process have to be taken seriously now, even though in the past, the industry could make a profit with serious variations caused by different processes. Tighter design rules have been successfully implemented to keep process variation issues at bay from the critical manufacturing issues [48]. However, as the critical dimensions are moving towards a few nanometers, process control at the atomic level is becoming a significant issue [49]. As future circuits will be capable of handling fewer process variations, both designers and process engineers have to coordinate in such a way that the process is optimized for the design or vice versa. Otherwise, yield will be affected and the profit will decline. This situation can be eased by developing a process that has the inherent property of introducing fewer defects during processing. Single wafer manufacturing has the advantage of precision and accuracy for each wafer, which increases performance and yield while reducing defects. Figure 3 shows the process integration challenged faced by the semiconductor industry today.

#### **Conclusion**

In this chapter, the key issues involved in the process integration and manufacturing of high-k gate dielectrics for the next generation of silicon MOSFETs have been reviewed. An examination of the published results shows that from the materials point of view, even though there is a clear cut winner in hafnium-based compounds at this moment, the leakage current density is not low enough to scale to the fundamental limits of Silicon technology. Due to the fundamental limitations of the materials, currently used hightemperature processing techniques are inadequate to meet the process integration and manufacturing requirements. By innovations in process integration schemes, it will be possible to integrate high- $\kappa$  dielectrics by using currently available low-temperature processing techniques. However, due to the cost of ownership, lack of high performance, and reliability issues, currently available low-temperature processing techniques may not be suitable for manufacturing. Based on published results, it appears that UV assisted rapid thermal processing based chemical vapor deposition tools are capable of meeting the process integration and manufacturing needs. The new tool should also have the insitu cleaning, in-situ deposition and in-situ annealing capability for the entire gate stack for integration into the currently used CMOS fabrication sequence.

#### References

- [1] Y. Taur and E. Nowak, "CMOS Devices below 0.1 m How High Will Performance Go?", *IEDM Tech. Digest*, pp. 215–218 (1997).

- [2] D. A. Muller, T. Sorsch, S. Moccio, F. H. Baumann, K. Lutterodt, and G. Timp, "The Electronic Structure at the Atomic Scale of Ultrathin Gate Oxides," *Nature* 399, pp. 758–761 (1999).

- [3] C. Hu, "Gate Oxide Scaling Limits and Projections," *IEDM Tech. Digest*, vol 18, pp. 96–99 (1996).

- [4] J.H. Stathis and D.J. DiMaria, "Reliability projection for Ultra-Thin Oxides at Low Voltage," *IEDM Tech. Digest*, vol 25, pp 167-170 (1998).

- [5] R. Degraeve, B. Kaczer and G. Groesseneken, "Reliability: A Possible Showstopper for Oxide Thickness Scaling?," *Semicond sci. technol*, vol 15, pp 436-444 (2000).

- [6] International technology Roadmap for Semiconductors, 1999 Edition, Semiconductor Industry Association, 4300 Stevens Boulevard, San Jose, CA 95129

- [7] A.Venkateshan, R.Singh, K.F.Poole, P.Pant and J.Narayan, "Off state gate leakage power reduction by using Hafnium Oxide as Gate dielectric for sub-45 nm CMOS", *IEEE Trans on Elect Dev* (submitted).

- [8] R.Singh, A.Venkateshan, K.F.Poole and P.Chaterjee, "Semiconductor Manufacturing in the 21<sup>st</sup> Century", *GESTS Inter Trans on Comp Sci and Engg*, vol.30, No.1, (2006).

- [9] A.Venkateshan, R.Singh, K.F. Poole, J. Harriss, H. Senter and R. Teague, "High-k Gate dielectrics with ultra-low leakage current for sub-45 nm CMOS ", *IEEE Elec Dev lett* (submitted).

- [10] N.S. Kim, T. Austin, T. Blaauw, T. Mudge, "Leakage Current: Moore's Law meets Static Power", *IEEE Comp Soc* (Cover article), vol 21, pp 68 – 75, (2003).

- [11] T. Hori, "Gate dielectrics and MOS ULSIs Principles, Technologies and Applications", Springer 1<sup>st</sup> edition, ISBN-10: 3540631828, New York, (1997).

- [12] The relative permittivity of a material is often given by E or  $E_r$  such as with the expression C= E.E<sub>o</sub>a/t. The relation between k and E varies depending on the choice of units (e.g. when  $E_o=1$ ), but since it is always the case that k is proportional to E, here we use the definition k=E

- [13] R. Singh and J. Shewchun, "A Possible Explanation for the Photovoltaic Effect in Indium Tin Oxide on InP Solar Cells", J. Appl. Phys., vol. 49, pp. 4588-4591, (1978).

- [14] J. Robertson, "Band offsets of wide-band-gap oxides and implications for future electronic devices", *J. Vac Sci and Technol B*, vol 18, pp 1785-1791, (2000).

- [15] J.D. Plummer and P.B. Griffin, "Material and process limits in silicon VLSI technology", Proc. of the IEEE, vol 89, 240-258, (2001).

- [16] Y. Kawamoto, K. Kimura, J. Nakazato and M. Nagao, "The outlook for semiconductor processes and manufacturing technologies in the 0.1 μm age", *Hitachi Review*, vol 48, pp 334-339, (2001).

- [17] M.S. Lundstrom, "On the mobility versus drain current relation for a nanoscale MOSFET", *IEEE Electron Dev Lett.*, vol 22, pp 293-295, (2001).

- [18] Intel shifts to next generation strained silicon, http://www.extremetech.com/article2/0,1558,1640647,00.asp

- [19] S. Narendra, S. Borkar, V. De, D. Antoniadis, and A. Chandrakasan, Scaling of stack effect and its application for leakage reduction, *Proc. Int. Symp. Low Power Electronic Design*, pp. 195-200, (2001).

- [20] J. Tschanz, S. Narendra, Y, Ye, B. Bloechel, S. Borkar, V. De, Dynamic Sleep transistor and Body Bias for Active Leakage Power Control of Microprocessors, *IEEE J. Solid-State Circuits*, vol. 38, pp. 1838-1845, (2003)

- [21] R.Singh, A.Venkateshan, M.Fakhruddin, K.F.Poole, N.Balakrishnan & L.D. Fredendall, "Dominant role of single-wafer manufacturing in providing sustained growth of semiconductor Industry", *Semi Fabtech*, 19<sup>th</sup> Edition, pp. 85-93, (2003).

- [22] S. J. Hood, S. Bermon and F. Barahona," Capacity Planning Under Demand Uncertainty for Semiconductor Manufacturing", *IEEE Trans on semi Manuf*, vol. 16, pp. 273-280 (2003).

- [23] J. Benkoski, "A Humbler, wiser Valley", EE Times, Issue, June 30, 2003

- [24] S.V. Hattangady, R.Kraft, D.T. Grider, M.A Douglas, G.A Brown, P.A Tiner, J.W Kuehne, P.E Micollian and M.F.Pas, *Tech Dig Int Electron Devices meet*, pp 465 – 469, (1997)

- [25] H. Iwai, and S. Ohmi, "ULSI process integration for 2005 and beyond", ULSI Process Integration II, *Electrochem Soc Proc*, vol 2001-2002, pp 3-32, (2002).

- [26] R.Singh, V. Parihar, K.F. Poole and R. Rajkannan, "Semiconductor manufacturing in the 21<sup>st</sup> Century", *Semi Fabtech*, 9<sup>th</sup> Edition, pp 223-232, (1999).

- [27] R. Singh and R.K. Ulrich, "High and Low dielectric Constant Materials", The *Electrochem Soc Interf*, vol 8(2), pp 26-29, (1999).

- [28] J.C Jackson, D.J. Dumin, C. Messick and R.E. Rendall, "Practical triggering of early breakdowns in thin oxides", *IEEE Int. Rel. Workshop Final Report*, pp 27-32, (1998).

- [29] E.Rosenbaum, Z.Liu and C. Hu, "Silicon dioxide breakdown lifetime enhancement under bipolar bias conditions", *IEEE Trans. Elec Dev*, vol 40, pp 2287-2295, (1993).

- [30] R. Degraeve, B. Kaczer and G. Groeseneken, "Reliability: a possible showstopper for oxide thickness Scaling?", *Semi Sci and Tech*, vol 15, pp 436-444, (2001).

- [31] G.Fishman, "New Tech: stick to the core", EE times, Issue 1276, June 30, 2001

- [32] G. P. Morrison, V.Yamunan, and A.G. Lewis, "Co-design or Bust: SOC FBGA", EE Times, May 23, 2003. http://www.eetimes.com/story/OEG20030521S0071

- [33] F. N. Mokhoff and M. LaPedus, "IC Forecasts for '03 See Bears Beating a Retreat," EE Times, Issue 1235, September 9, p. 1, 2002.

- [34] S. Kar, "Linkage between interface im<sub>ref</sub> pinning and the reliability of ultrathin gate dielectrics", *IEEE Semi Intl Sci*, vol.3, pp 34-37 (2001)

- [35] S.Kar, "Two limiting thinnesses of the ultra thin gate oxides in Silicon Nitride and Silicon Dioxide thin Insulating films", *Electrochem. Soc. Proc.* vol 7 pp 201-207, (2001).

- [36] S.Kar, "Ultimate gate oxide thinness set by recombination tunneling of electrons via Si-SiO<sub>2</sub> interface traps", *J. Appl Phys*, vol 88, pp 2693-2695, (2001).

- [37] R.Singh, S.V. Nimmagadda, V. Parihar, Y. Chen and K.F. Poole, "Role of rapid photothermal processing in process integration", *IEEE Trans. Electron Devices*, vol 45, pp 643-654, (1998)

- [38] R.Singh, V. Parihar, Y. Chen, K.F. Poole, S.V. Nimmagadda and L. Vedula, "Importance of rapid photothermal processing in defect reduction and process integration", *IEEE Trans. Semi Manuf*, vol 12, pp 36-43, (1999)

- [39] R.Singh and V. Parihar, "Rapid photothermal processing of dielectrics", Handbook of Low and High Dielectric Constant Materials and Their Applications, ch.1, vol. 2, Edited by H.S. Nalwa, Academic Press, pp 1-59, (1999).

- [40] J.C. Yu, B.C. Lai, and J.Y. Lee, "Fabrication and characterization of metal-oxidesemiconductor field-effect transistors and gated diodes using Ta<sub>2</sub>O<sub>5</sub> gate oxide", *IEEE Electron Device Lett*, vol 21, pp 537-539, (2004).

- [41] Solid State Technology Webcast, March 13, 2007, "Metrology for High-κ Dielectrics and Metal Gates" sponsored by Jordan Valley Semiconductors, Inc., Olympus Integrated Technologies America, Inc.

- [42] D. A. Muller, T. Sorsch, S. Moccio, F. H. Baumann, K. Evans-Lutterodt, and G. Timp, *Nature London*, vol. 399, pp 758 761, (1999).

- [43] T. Hattori, "Implementing a Single Wafer Cleaning Technology suitable for Minifab Operations", "http://www.micromagazine.com/archive/03/01/hattori.htm

- [44] R. Singh, M. Fakhruddin, and K. F. Poole," The Impact of Single Wafer Processing on Semiconductor Manufacturing", *IEEE Trans on Semi Manuf*, Vol. 16, pp. 96– 101, (2003).

- [45] H. Bolla, D. Damjanovic, M. Fakhruddin, R. Singh, K.F. Poole and A. Venkateshan, "A new approach in Thermal processing and new CVD tools to reduce cost of APC", *ISMI AEC/APC Symposium XVI*, September 18-23, (2004), Denver, Colorado

- [46] V. Mikelashvili and G. Eisenstein, "High-k Al<sub>2</sub>O<sub>3</sub>-HfTiO Nanolaminates with less than 0.8 nm EOT", *IEEE Electron Device Letters*, vol. 27, pp 24-26, (2007).

- [47] A.Venkateshan, R.Singh, K.F.Poole, H.Senter, "A New Process and Tool for Metal/High-κ Gate Dielectric Stack for sub-45 nm CMOS Manufacturing", International Symposium on Semiconductor Manufacturing (submitted).

- [48] R.Singh, A.Venkateshan & K.F.Poole, "Rapid Thermal processing of Cu/low-k interconnections for 65-nm technology node and beyond", *Semiconductor Fabtech*, 20<sup>th</sup> Edition, pp 120-124, (2003).

- [49] F. Vahid and T. Givargis, "Embedded System Design: A unified Hardware/Software Introduction", John Wiley & Sons Inc, pp.61, (2002).

Figure 1 Chip power dissipation versus gate length [10]

Figure 2 Power dissipation distribution for various technology nodes [21]

Figure 3 Process integration issues [26]

#### CHAPTER 3

### MONOLAYER PHOTOASSISTED DEPOSITION SYSTEM

#### Introduction

As discussed in the previous chapter, successful use of a new high- $\kappa$  material in the real manufacturing environment will depend on developing a new process that can be easily integrated with the existing CMOS process sequence. There is a need to develop a new tool that offers low temperature, short time process and has the built-in quality of minimizing statistical fluctuation as well as providing atomic level control of the film growth. The new tool should also offer in-situ cleaning, in-situ annealing and in-situ gate processing capability. Having all these characteristics in mind, a system was designed at Clemson University previously to deposit zirconium oxide films [1], and that system was modified for the deposition of hafnium oxide films. The tool was automated with Labview to control the UV source and provide pulsing for the precursor delivery, purge gas delivery, and water vapor delivery, in addition to accurate substrate temperature control. A process was developed to process reliable ultra-thin HfO<sub>2</sub> high-κ films by combining all the salient features of traditional monolayer deposition and UV assisted rapid thermal processing (RTP). Because of the high vacuum capability, the system also has the advantage of low pressure chemical vapor deposition (CVD). A low pressure system also offers the advantage of adding in-situ characterization techniques, otherwise not compatible with a high or atmospheric pressure system.

#### Monolayer Photoassisted Deposition

Monolayer deposition is a process to grow thin films of either crystalline or polycrystalline materials one layer at a time. During the process, a sequential reactant interaction is combined with a substrate at a specific temperature that prevents condensation of individual reactants on the growing surface. Temperature of the substrate is a key parameter to control the growth of the film. The temperature of the substrate should be low enough to allow the monolayer to react with the reactant but high enough to reevaporate any subsequent layers or add-on molecules on top of the monolayer. The control of monolayer growth can be better if there are additional sources of energy (i.e., ultraviolet or vacuum ultraviolet light), so that there is a greater difference between the bond energy of the monolayer and the bond energies of the subsequent layers.

During the process, both elemental and compound reactants can be used. As compound precursors were used in this study, the discussion will be limited to compound reactants. Using compound reactants solves the problem of low vapor pressure of elemental metal reactants. To process a compound; i.e., compound AB, the elements A and B are supplied on the substrate as an alternate exposure of compounds AX and BY. During a typical monolayer photoassisted CVD cycle, compound AX is supplied to the surface of the substrate for time  $t_1$ . Then the substrate is purged for time  $t_2$  to ensure that no two reactants are simultaneously present at the substrate surface. Also, if there has been a condensation of the compound AX, it will re-evaporate during the purge time. Usually inert gases are used for the purging process. Figure 4 shows the profile of the cycling steps. For this study, TDMAH (Tetrakis Dimethylamino Hafnium) 99.95% Hf from Strem Chemicals was used as the first compound, and the second compound BY (Y referring to 1 to n hydrogen atoms), water vapor was used. The compound BY is applied to the substrate for a time  $t_3$ , followed by another purge step of duration  $t_4$ . Therefore the total time t, needed for one complete process cycle is equal to the sum of  $t_1$ ,  $t_2$ ,  $t_3$  and  $t_4$ . The vapor pressure of BY is usually high and condensation of BY does not occur during the normal monolayer CVD process [2]. During the purge steps, there is a certain amount of possibility of re-evaporation of a formed monolayer A(s) bonded to B. But under favorable process conditions, the re-evaporation probability of an atom A from a B surface is much less than the re-evaporation probability of an atom A from an A surface [2,3]. Also the bond energy of an atom B on surface A is generally higher than that of atom A on surface atoms B (non metal surface atoms generally form a more stable surface than metal atoms). This also prevents the re-evaporation of the B(s) surface [4]. The processing window of the monolayer photoassisted CVD process is shown in Figure 5. In that figure  $A_1$  is the area where condensation of the reactants occurs,  $A_2$  is the area where activation of the necessary reaction is not exceeded,  $B_1$  is the area where decomposition of a reactant results in a non-evaporating surface layer on a monolayer, and  $B_2$  is the area where re-evaporation of a formed monolayer occurs.

### UV Radiation and Rapid Thermal Processing (RTP)

It is well known that as the temperature of a black body is increased, the color emitted by it becomes richer in shorter wavelengths. The thermal power of the radiation can be expressed as [5]:

$$P = hf\Delta f \left\{ \frac{1}{e^{hf/kT} - 1} + \frac{1}{2} \right\}$$

(1)

where  $\Delta f$  is the frequency band occupied by the radiation mode, h is Planck's constant, k is boltzman constant and T is absolute temperature. The factor  $\frac{1}{2}$  in the above equation is due to the contribution of zero point energy, which is a quantum phenomenon. The other factor inside the curly bracket is the Bose Einstein factor [4], which is the thermal part of radiation. It is evident from Figure 6, that in the lower frequency (higher wavelength) range, the thermal part is dominant but as the frequency goes up, the quantum part of the energy dominates. Therefore, when photons interact with matter there will be quantum effects in addition to thermal effect. It has been shown that photons with wavelength more than about 800 nm contribute to thermal effects [5]. Photons with wavelength between about 400 and 800 nm contribute to both thermal and quantum effects. Only quantum effects are observed with photons less than about 400 nm. The quantum energy of photons that can be used during UV and VUV assisted RTP without any adverse effects (e.g. ionic displacement leading to the formation of defects) is about 10-12 eV [6]. In this case, the use of ultra violet (UV) and vacuum ultra violet (VUV) photons exploits the quantum phenomena. The quantum effects have the following implications for UV assisted rapid thermal processing [6, 7]: