# Clemson University **TigerPrints**

All Theses Theses

12-2014

# Scientific Application Acceleration Utilizing Heterogeneous Architectures

Edwin Weill Clemson University, eweill@g.clemson.edu

Follow this and additional works at: <a href="https://tigerprints.clemson.edu/all\_theses">https://tigerprints.clemson.edu/all\_theses</a>

Part of the <a href="Computer Engineering Commons">Computer Engineering Commons</a>, and the <a href="Computer Sciences Commons">Computer Sciences Commons</a>

#### Recommended Citation

Weill, Edwin, "Scientific Application Acceleration Utilizing Heterogeneous Architectures" (2014). *All Theses.* 2046. https://tigerprints.clemson.edu/all\_theses/2046

This Thesis is brought to you for free and open access by the Theses at TigerPrints. It has been accepted for inclusion in All Theses by an authorized administrator of TigerPrints. For more information, please contact <a href="kokeefe@clemson.edu">kokeefe@clemson.edu</a>.

# SCIENTIFIC APPLICATION ACCELERATION UTILIZING HETEROGENEOUS ARCHITECTURES

A Thesis

Presented to

the Graduate School of

Clemson University

In Partial Fulfillment

of the Requirements for the Degree

Master of Science

Computer Engineering

by

Edwin Weill

December 2014

Accepted by:

Dr. Melissa C. Smith, Committee Chair

Dr. Amy Apon

Dr. Walter Ligon

#### **Abstract**

Within the past decade, there have been substantial leaps in computer architectures to exploit the parallelism that is inherently present in many applications. The scientific community has benefited from the emergence of not only multi-core processors, but also other, less traditional architectures including general purpose graphical processing units (GPGPUs), field programmable gate arrays (FPGAs), and Intel's many integrated cores (MICs) architecture (i.e. Xeon Phi). The popularity of the GPGPU has increased rapidly because of their ability to perform massive amounts of parallel computation quickly and at low cost with an ease of programmability. Also, with the addition of high-level programming interfaces for these devices, technical and non-technical individuals can interface with the device and rapidly obtain improved performance for many algorithms. Many applications can take advantage of the parallelism present in distributed computing and multithreading to achieve higher levels of performance for the computationally intensive parts of the application.

The work presented in this thesis implements three applications for use in a performance study of the GPGPU architecture and multi-GPGPU systems. The first application study in this research is a K-Means clustering algorithm that categorizes each data point into the closest cluster. The second algorithm implemented is a spiking neural network algorithm that is used as a computational model for machine learning. The third, and final,

study is the longest common subsequences problem, which attempts to enumerate comparisons between sequences (namely, DNA sequences).

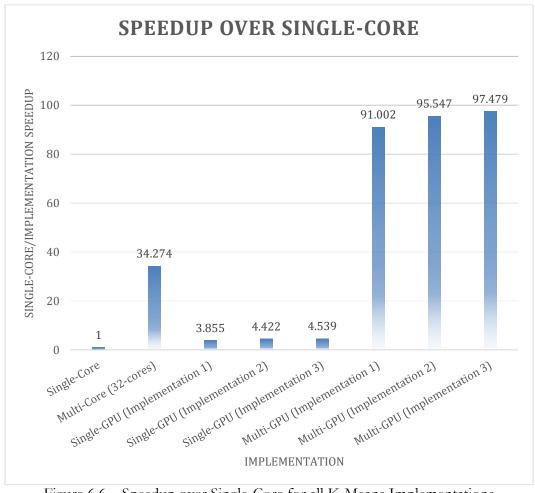

The results for the aforementioned applications with varying problem sizes and architectural configurations are presented and discussed in this thesis. The K-Means clustering algorithm achieved approximately 97x speedup when utilizing an architecture consisting of 32 CPU/GPGPU pairs. To achieve this substantial speedup, up to 750,000 data points were used with up 30,000 centroids (means). The spiking neural network algorithm resulted in speedups of about 33x for the entire algorithm and 160x for each iteration with a two-level network with 1000 total neurons (800 excitatory and 200 inhibitory neurons). The longest common subsequences problem achieved speedup of greater than 10x with 100 random sequences up to 500 characters in length. The maximum speedup values for each application were achieved by utilizing the GPGPU as well as multi-core devices simultaneously. The computations were scattered over multiple CPU/GPGPU pairs with the computationally intensive pieces of the algorithms offloaded onto the GPGPU device.

The research in this thesis illustrates the ability to scale a heterogeneous cluster (i.e. CPUs and GPUs working collaboratively) for large-scale scientific application performance improvements. Each algorithm demonstrates slightly different types of computations and communications, which can be compared to other algorithms to predict how they would perform on an accelerator. The results show that substantial speedups can be achieved for scientific applications when utilizing the GPGPU and multi-core architectures.

# **Dedication**

I dedicate this thesis to my parents and my academic advisor without whose constant support and guidance this thesis would not have been possible. I also dedicate this thesis to my wife and my younger sister, who have always stood by my side and been an inspiration.

## Acknowledgements

This thesis was made possible by the help and support of the following faculty members, family members, and colleagues.

I begin by thanking my academic advisor Dr. Melissa Smith, who graciously accepted me as her pupil. Dr. Smith's words of wisdom, immense experience, constant encouragement, and insightful suggestions allowed for the completion of this research and thesis.

I would also like to thank Dr. Amy Apon and Dr. Walt Ligon for serving on my committee and instructing me in various aspects of computer architecture.

I am also thankful for my parents, Edwin and Jeanine, my Sister, Shannon, and my wife, Hiliary, who provided constant support during my research and writing this manuscript.

I also owe a debt of gratitude to my fellow colleagues from the Future Computing Technologies Lab at Clemson University: Ashraf, Vivek, Karan, Nimisha and many others whom I fail to mention for providing me a stimulating work environment during this process.

I would also like to acknowledge the National Science Foundation MRI Grant Award No. 1228312 for making this research possible (PI Amy Apon; Co-PIs Melissa C Smith, Walter Ligon, Jill Gemmill, and Steven Stuart).

# **Table of Contents**

|              |                                                   | Page |

|--------------|---------------------------------------------------|------|

| Title Page.  |                                                   | i    |

| Abstract     |                                                   | ii   |

| Dedication   |                                                   | iv   |

| Acknowled    | gements                                           | v    |

| List of Tabl | les                                               | ix   |

| List of Figu | ires                                              | xi   |

| Chapter      |                                                   |      |

| 1 Introdu    | ction                                             | 1    |

| 2 Related    | l Work                                            | 6    |

| 2.1          | K-Means                                           | 6    |

| 2.2          | Izhikevich SNN                                    | 8    |

| 2.3          | Longest Common Subsequences                       | 11   |

| 2.4          | Summary                                           |      |

| 3 Backgr     | ound                                              | 13   |

| 3.1          | K-Means Clustering                                | 13   |

|              | 3.1.1. K-Means Algorithm                          | 14   |

|              | 3.1.2. K-Means Clustering Real-world Applications | 16   |

| 3.2          | Spiking Neural Networks                           | 17   |

|              | 3.2.1 Izhikevich SNN Model                        | 19   |

|              | 3.2.2 SNN Real-world Applications                 | 21   |

| 3.3          | Longest Common Subsequences Problem               |      |

|              | 3.3.1 LCS Real-world Applications                 | 24   |

#### Table of Contents (Continued)

|   |         |                                             | Page |

|---|---------|---------------------------------------------|------|

|   | 3.4     | Summary                                     | 24   |

| 4 | Comput  | ting Architectures and Programming Models   | 26   |

|   | 4.1     | Computing Architectures                     | 27   |

|   |         | 4.1.1 Multi-Core Architecture               | 27   |

|   |         | 4.1.1.1 Intel Xeon E5-2665                  | 28   |

|   |         | 4.1.2 GPGPU Architecture                    |      |

|   |         | 4.1.2.1 NVIDIA Tesla K20 (Kepler GK110)     |      |

|   | 4.2     | Programming Models                          |      |

|   |         | 4.2.1 MPI                                   |      |

|   |         | 4.2.2 CUDA                                  | 36   |

|   | 4.3     | Palmetto Cluster                            | 39   |

|   | 4.4     | Summary                                     | 40   |

| 5 | Experin | nental Setup and Implementation             | 41   |

|   | 5.1     | Experimental Setup                          | 41   |

|   |         | 5.1.1 Heterogeneous System Setup            | 42   |

|   |         | 5.1.2 Compiler                              |      |

|   | 5.2     | Implementations                             |      |

|   |         | 5.2.1 K-Means                               |      |

|   |         | 5.2.2 Spiking Neural Networks               |      |

|   |         | 5.2.3 Longest Common Subsequences           |      |

|   | 5.3     | GPU Implementations                         |      |

|   |         | 5.3.1 Implementation 1 (Global Memory)      |      |

|   |         | 5.3.2 Implementation 2 (Constant Memory)    |      |

|   |         | 5.3.3 Implementation 3 (GPGPU Math Library) |      |

|   |         | 5.3.4 Multi-GPU Implementations             |      |

|   | 5.4     | Summary                                     | 53   |

| 6 | Results | and Analysis                                | 54   |

|   | 6.1     | K-Means                                     | 55   |

|   |         | 6.1.1 Single-Core Implementation            |      |

|   |         | 6.1.2 Multi-Core Implementation             |      |

|   |         | 6.1.3 Single-GPU Implementation             |      |

|   |         | 6.1.4 Multi-GPU Implementation              |      |

|   |         | 6.1.5 Speedup                               |      |

|   | 6.2     | Spiking Neural Networks (SNN)               |      |

|   |         | 6.2.1 Single-Core Implementation            | 64   |

#### Table of Contents (Continued)

|            |          |                               | Page |

|------------|----------|-------------------------------|------|

|            | 6.2.2    | Multi-Core Implementation     | 64   |

|            | 6.2.3    | Single-GPU Implementation     | 68   |

|            | 6.2.4    | Multi-GPU Implementation      | 70   |

|            | 6.2.5    | Speedup                       |      |

| 6.3        | Longe    | est Common Subsequences (LCS) |      |

|            | 6.3.1    | Single-Core Implementation    |      |

|            | 6.3.2    | Multi-Core Implementation     |      |

|            | 6.3.3    | Single-GPU Implementation     |      |

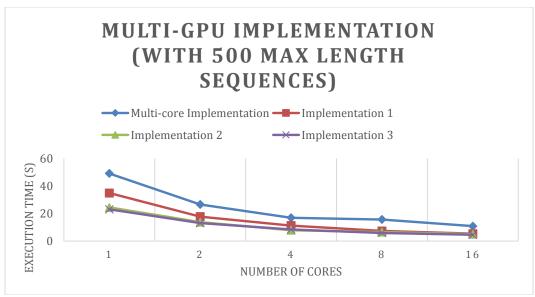

|            | 6.3.4    | Multi-GPU Implementation      |      |

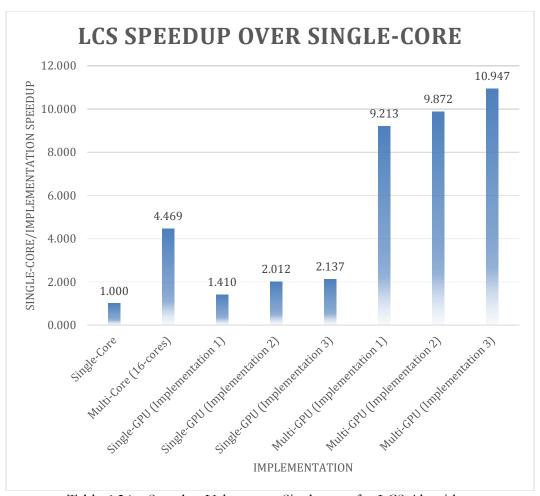

|            | 6.3.5    | Speedup                       |      |

| 6.4        | Summ     | nary                          |      |

| 7 Conclus  | sions an | d Future Work                 | 90   |

| 7.1        |          | usions                        |      |

| 7.2        | Future   | e Works                       | 93   |

| References |          |                               | 98   |

# List of Tables

| Table | I                                                        | Page |

|-------|----------------------------------------------------------|------|

| 4.1   | Intel Xeon E5-2665 ("Romley") Statistics                 | 28   |

| 4.2   | Kepler GK110 (Tesla K20) Statistics                      | 34   |

| 4.3   | Commonly used MPI Functions                              | 36   |

| 5.1   | Features available on the NVIDIA Tesla K20m device       | 43   |

| 5.2   | Data Configurations for K-Means Clustering               | 44   |

| 5.3   | Data Configurations for Izhikevich SNN Algorithm         | 45   |

| 5.4   | Data Configurations for LCS Algorithm                    | 46   |

| 6.1   | Execution Times for Single-Core K-Means Algorithm        | 56   |

| 6.2   | Execution Times for Multi-Core K-Means Algorithm         | 57   |

| 6.3   | Execution Times for Single-GPU K-Means Algorithm         | 59   |

| 6.4   | Execution Times for Multi-GPU K-Means Algorithm          | 60   |

| 6.5   | Speedup over Single-Core for all K-Means Implementations | 63   |

| 6.6   | Execution Times for Single-Core Izhikevich SNN           | 64   |

| 6.7   | Execution Times for Multi-Core Izhikevich SNN            | 65   |

| 6.8   | Execution Times for Single-GPU Izhikevich SNN            | 68   |

| 6.9   | Total Execution Times for Multi-GPU Izhikevich SNN       | 71   |

| 6.10  | Iteration 1 Execution Times for Multi-GPU Izhikevich SNN | 72   |

#### List of Tables (Continued)

| Table | Page                                                      |

|-------|-----------------------------------------------------------|

| 6.11  | Iteration 2 Execution Times for Multi-GPU Izhikevich SNN  |

| 6.12  | Speedup of Total Execution Times for Izhikevich SNN       |

| 6.13  | Speedup of Iteration 1 Execution Times for Izhikevich SNN |

| 6.14  | Speedup of Iteration 2 Execution Times for Izhikevich SNN |

| 6.15  | Execution Times for Single-Core LCS Algorithm             |

| 6.16  | Execution Times for Multi-Core LCS Algorithm              |

| 6.17  | Execution Times for Single-GPU LCS Algorithm              |

| 6.18  | Execution Times for Multi-GPU LCS Algorithm               |

| 6.19  | Speedup Values over Single-Core LCS Algorithm             |

# List of Figures

| Figure | Page                                                                |

|--------|---------------------------------------------------------------------|

| 3.1    | Example of LCS Algorithm                                            |

| 4.1    | NVIDIA GeForce 8800 GTX Architecture [Reference]30                  |

| 4.2    | NVIDIA Fermi Architecture [Reference]                               |

| 4.3    | NVIDIA Kepler GK110 Architecture [Reference]                        |

| 4.4    | GK110 SMX Architecture [Reference]                                  |

| 4.5    | Thread block layout in CUDA [Reference]                             |

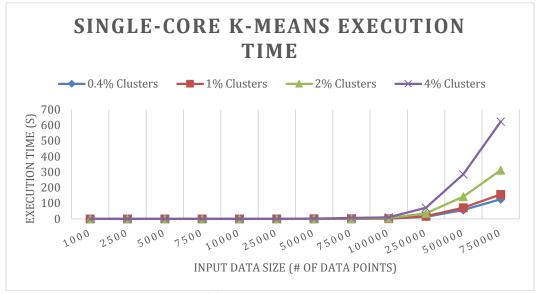

| 6.1    | Execution Times for Single-Core K-Means Algorithm                   |

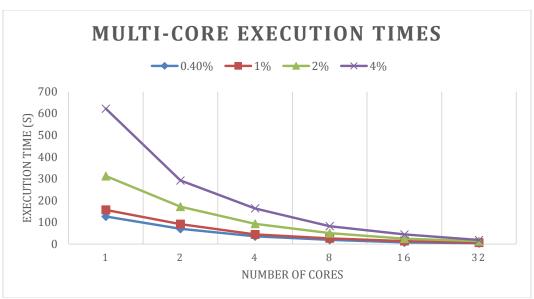

| 6.2    | Execution Times for Multi-Core K-Means Algorithm                    |

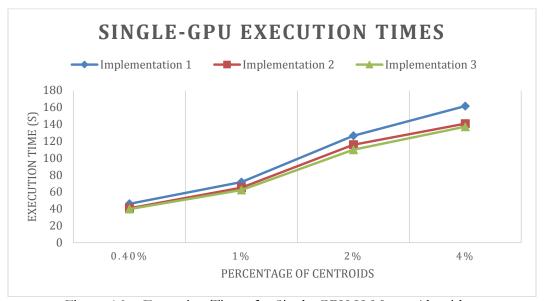

| 6.3    | Execution Times for Single-GPU K-Means Algorithm                    |

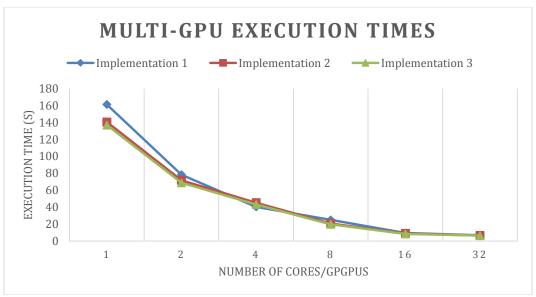

| 6.4    | Execution Times for Multi-GPU K-Means Algorithm                     |

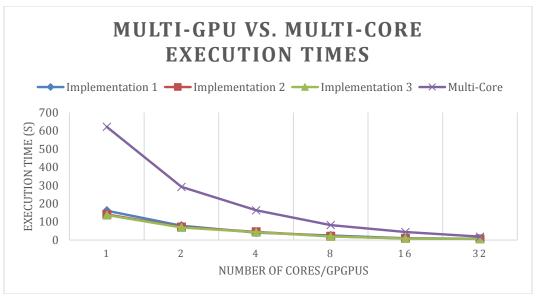

| 6.5    | Execution Times for Multi-GPU Comparison with Multi-Core K-Means 62 |

| 6.6    | Speedup over Single-Core for all K-Means Implementations            |

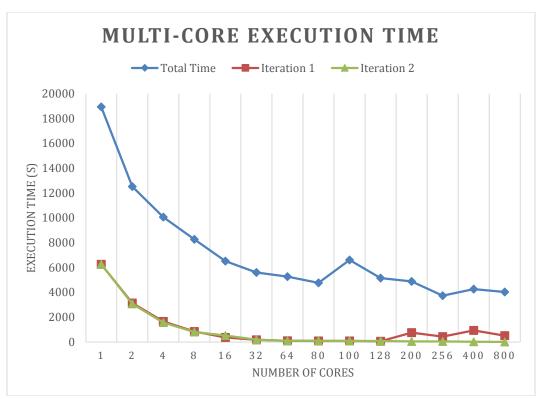

| 6.7    | Execution Times for Multi-Core Izhikevich SNN                       |

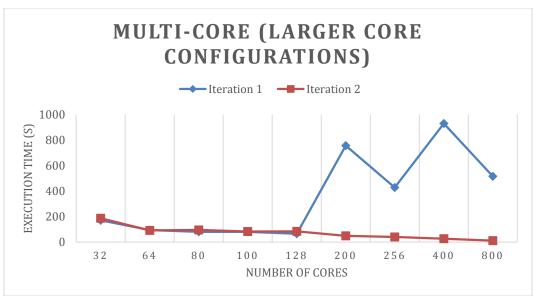

| 6.8    | Execution Times for Multi-Core (Large # of Cores) Izhikevich SNN68  |

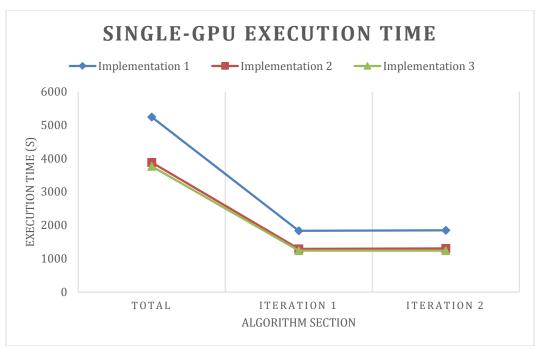

| 6.9    | Execution Times for Single-GPU Izhikevich SNN                       |

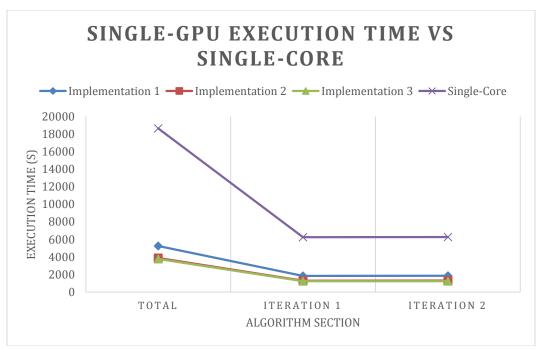

| 6.10   | Execution Times for Single-GPU vs. Single-Core Izhikevich SNN70     |

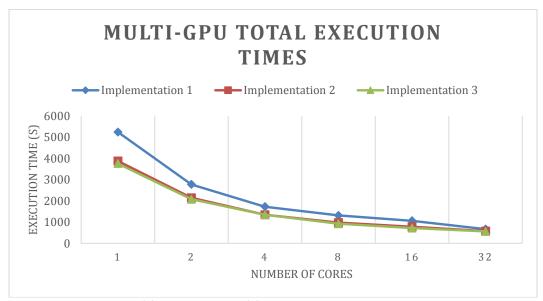

| 6.11   | Total Execution Times for Multi-GPU Izhikevich SNN71                |

#### List of Figures (Continued)

| Figure | Page                                                                    |

|--------|-------------------------------------------------------------------------|

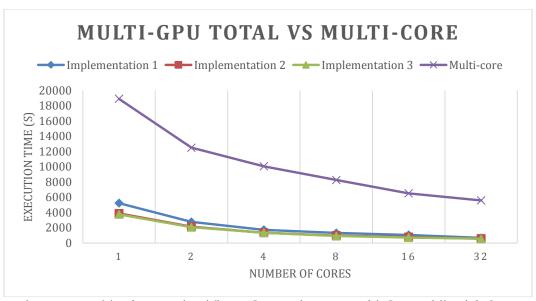

| 6.12   | Total Execution Times Comparison to Multi-Core Izhikevich SNN72         |

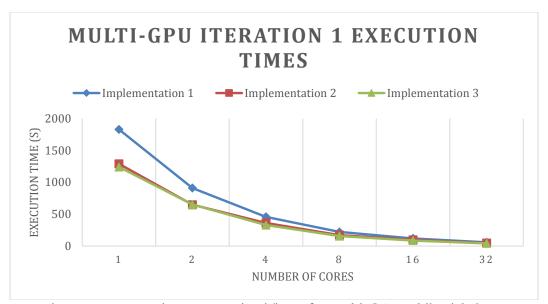

| 6.13   | Iteration 1 Execution Times for Multi-GPU Izhikevich SNN                |

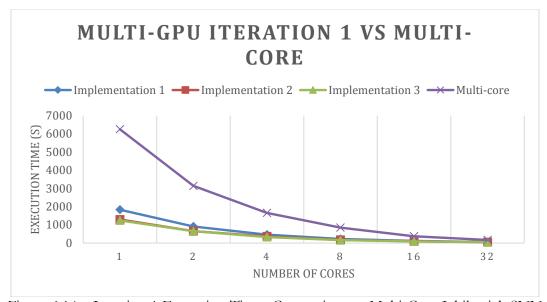

| 6.14   | Iteration 1 Execution Times Comparison to Multi-Core Izhikevich SNN73   |

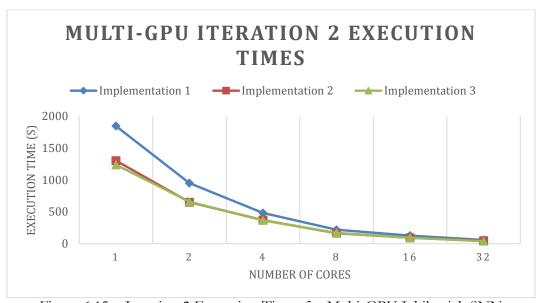

| 6.15   | Iteration 2 Execution Times for Multi-GPU Izhikevich SNN                |

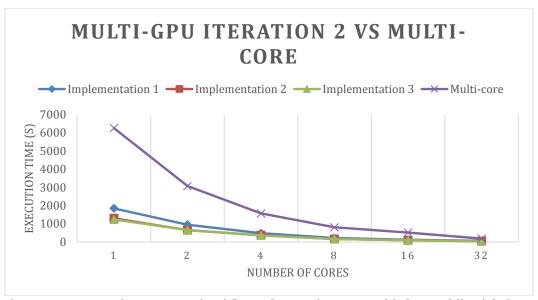

| 6.16   | Iteration 2 Execution Times Comparison to Multi-Core Izhikevich SNN75   |

| 6.17   | Speedup of Total Execution Times vs. Single-Core Izhikevich SNN76       |

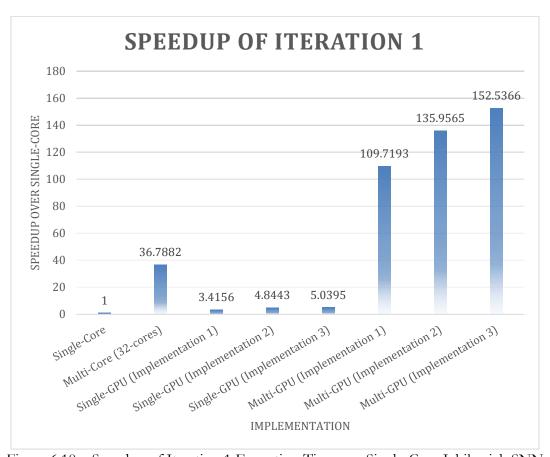

| 6.18   | Speedup of Iteration 1 Execution Times vs. Single-Core Izhikevich SNN77 |

| 6.19   | Speedup of Iteration 2 Execution Times vs. Single-Core Izhikevich SNN78 |

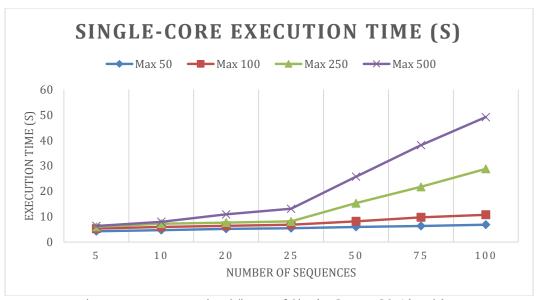

| 6.20   | Execution Times of Single-Core LCS Algorithm                            |

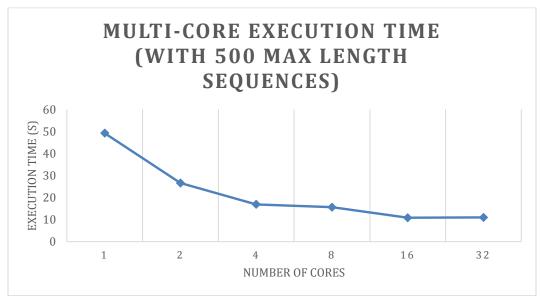

| 6.21   | Execution Times of Multi-Core LCS Algorithm                             |

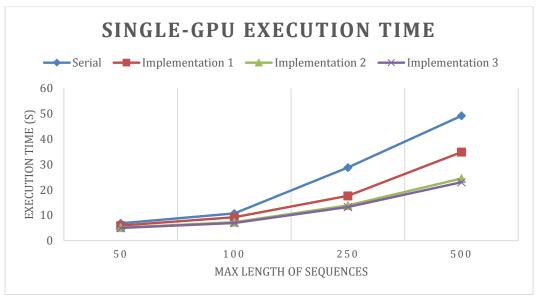

| 6.22   | Execution Times for Single-GPU LCS Algorithm                            |

| 6.23   | Execution Times for Multi-GPU LCS Algorithm                             |

| 6.24   | Speedup over Single-Core for LCS Algorithm                              |

# Chapter 1

#### Introduction

For a significant time in the past, scientific researchers relied on the advancement of computer architectures, in terms of higher clock speeds and other low-level optimizations, to increase the performance of their applications. However, due to hardware limitations including memory, clock speed, and physical processor size, parallel computing architectures are necessary to bridge the gap between the need for performance improvements in applications and the lack of significant advancements in the low-level architecture design (i.e. lithography limits, clock wall, power density, etc.). The trends have moved toward parallel computing architectures, leading vendors to increase the number of cores per device and increase the number of processors per machine.

However, computationally intensive applications need more than just multi-core architectures to perform well. Therefore, along with the advances that have emerged with multi-core architectures, advances in the field of heterogeneous computing have developed simultaneously to comply with the computational needs. Heterogeneous computing can be described as the combination of a CPU host and one or more special-purpose computing devices or accelerators such as general-purpose graphical processing units (GPGPUs), field programmable gate arrays (FPGAs), and Intel's many- integrated cores (MICs) architecture

(i.e. Xeon Phi [1]). From the list of special-purpose computing devices, GPGPUs have gained significant leverage in the parallel computing niche due to the ability to perform massively parallel tasks at a relatively low cost and easy programming interface through open source languages such as OpenCL [2] and architecture specific languages such as NVIDIA's Compute Unified Device Architecture (CUDA) [3]. With the growing need for increased performance in computationally intensive applications, GPGPUs provide a means for more efficient execution exploiting many-core resources. The release of NVIDIA's CUDA allowed researchers to explore the parallelism of GPGPUs with their applications. With the growing popularity of NVIDIA's CUDA, GPGPUs became the mainstream accelerator in high-performance computing (HPC) and therefore forced vendors to continually evolve them to include advanced features and increase the number of compute cores.

Even with the emergence of GPGPUs in the scientific community, there are still needs for more, faster parallel computations. Therefore, heterogeneity is achieved through the combination of the multi-core and many-core architectures. These systems allow the developer to optimally parallelize code sections, while the remaining code is executed on a sequential processor or core. In heterogeneous systems, the CPU host executes sequential computations such as the data management and file I/O, while the accelerator(s) perform the computationally intensive parts of the application or algorithm, thereby improving the overall application performance. The CPU host and accelerators are connected via special interconnect technologies such as Infiniband [4] or PCI express [5].

Many scientific applications use complex calculations on very large data sets. To perform these calculations, CPUs serialize each computation, which can cause very long execution times if the algorithm is complex or the data set is large. For this reason, it is

preferred to exploit the parallelism of GPGPUs. The algorithms used in this research study (clustering, neural networks, and longest common subsequences) create a diverse algorithm set specifically selected to prove that multiple types of algorithms can utilize GPGPU parallelism. The research in this thesis illustrates the efficacy of attempting to parallelize an application if the execution time is large or there is a large percentage of computation that can be parallelized.

With the emergence of heterogeneous systems, researchers are concerned about how well these computing systems fit in their research paradigm and improve performance of their applications. This research study conducts a performance analysis of a variety of scientific applications using heterogeneous systems including GPGPUs to understand how well different types of applications scale with the system. There are two programming models used in this study including CUDA and MPI. The use of these models allows for a comparison between multi-core and heterogeneous systems as well as an analysis of the algorithms that later will be described in Chapter 3.

The first algorithm discussed as part of this research study in Chapter 3 is the K-Means clustering algorithm [6] where *n* observations are clustered into *k* clusters. K-Means is an iterative process where each of the *n* observations is moved into a group (one of the *k* clusters) such that each observation is clustered to the closest cluster centroid. An implementation of this algorithm utilizing a heterogeneous GPGPU architecture is developed and is described in Chapter 5.

The second algorithm discussed as part of this research study in Chapter 3 is the Izhikevich Spiking Neural Network algorithm [7], which is a computational model used for machine learning algorithms such as speech or facial recognition and computer vision. The

Izhikevich algorithm is highly biologically accurate and computationally efficient allowing for more computation in a given time period compared to other neural network algorithms. An implementation of this algorithm is developed utilizing a heterogeneous GPGPU architecture and will be described in Chapter 5.

The final algorithm discussed as part of this research study in Chapter 3 is the Longest Common Subsequences (LCS) [8] problem that finds the longest common subsequence in a given set of sequences. The solution to the LCS problem uses dynamic programming (i.e. breaking the problem into smaller sub-problems) to obtain the optimal longest common subsequence for the given set of sequences. Not only can the LCS problem be applied to simple problems such as comparing two text files, but can also be used for more complex tasks such as DNA sequence matching [9]. An implementation of this algorithm is developed utilizing a heterogeneous GPGPU architecture and is described in Chapter 5.

Each of the algorithms described above are implemented using the CUDA and MPI models which are discussed in Chapter 4. The implementations that will be discussed include a CPU-only implementation, an MPI (multi-core) implementation, a CUDA (single CPU-GPU pair) implementation, and a CUDA-MPI (multiple CPU-GPU pair) implementation. Chapter 6 presents a comparative study of the algorithm implementations using the aforementioned programming paradigms.

The completion of this thesis is structured as follows. Chapter 2 reviews the work that has been completed on the clustering, bioinformatics, and neural network algorithms mentioned above. Chapter 3 provides background on the scientific algorithms used in this research study. Chapter 4 explores the GPGPU architecture and provides an overview of the programming paradigms used in this research study. Chapter 5 provides an overview of the

details of the experimental setup and implementation for each of the algorithm studies. This chapter also includes optimization strategies explored in this research study. Chapter 6 presents the results and analysis for each of the algorithms. Chapter 7 provides conclusions and discusses suggestions for future work.

### Chapter 2

#### **Related Work**

This chapter introduces the work that motivates and supports this research. Each section gives an overview of the work that has been completed for each of the applications discussed in this work as well as the results that were achieved. Section 2.1 discusses implementations of the K-Means algorithm including other multi-core and single-GPU implementations, section 2.2 discusses previous implementations completed using a Spiking Neural Network, and section 2.3 gives an overview of the work that has been done with the Longest Common Subsequences problem in the past.

#### 2.1 K-Means

In [10], Farivar et al. present a GPU-based parallel implementation of the K-Means clustering algorithm on an NVIDIA G80 (the NVIDIA 8600GT). When compared to a 3 GHz Intel Pentium(R) processor running the same algorithm, the CUDA implementation is shown to improve 13x over the single processor implementation. The proposed implementation randomly generates the data points as well as the original k clusters and then in each step re-computes the new cluster centers. The CUDA implementation for this algorithm includes having each thread process single data points, computing the distance

between the point and each centroid. An important aspect of this implementation is the use of constant memory for the centroids. The use of constant memory allows for a faster access through the cacheable part of the device memory. Farivar et al. also make a prediction of a 68x performance increase using the NVIDIA GeForce 8800GT with the same algorithm, but the hardware was not available at the time of publication to verify the assumptions.

In [11], Zechner and Granitzer present an optimized CUDA implementation of the K-Means algorithm on NVIDIA's G80 GPU. To observe how the algorithm performs with differing number of data points, data sets of 500, 5,000, 50,000, and 500,000 were generated with 2, 20, and 200 dimensions. The CPU takes the role of the master thread in this implementation and prepares all of the data points to send to the GPU. The data points are uploaded to the GPU once and then each iteration of the algorithm labels each point as belonging to a specific centroid. Each iteration, the GPU performs the labeling of each point with the nearest centroid and then the results are sent back to the CPU to calculate the new centroid for each cluster. For the GPU-based implementation performance values range from 23 GB/s to 44 GB/s computational performance based on the cluster count and dimensionality.

Hong-tao et al. demonstrate a GPU-based k-means implementation on the NVIDIA G80 architecture, which performs as high as 40x better than the CPU-base k-means implementation in [12]. This paper presents a novel approach to the algorithm (compared to previous implementation), where both the data objects assignment and the centroid recalculation are done on the GPU. Li, Zhao, Chu, and Liu in [13] also present a novel approach for parallelizing k-means on GPUs with two different strategies: one for low-dimensional data sets and one for high-dimensional data sets to achieve best performance.

For low-dimensional data sets, on-chip registers are used on the GPU to decrease latency to access data. For high-dimensional data sets, on-chip shared memory is used to gain a better compute-to-data-access ratio. The algorithm presented is shown to be three to eight times faster than the other GPU-based implementations it was compared to.

The motivation for this thesis can be seen by the results of this literary review. All of the work done previously has shown that the k-means algorithm is a great candidate for accelerations using the GPU. All of the work has been done on a single-GPU; therefore, the research in this thesis continues utilizing the GPU and extends the k-means algorithm to utilize multiple CPU/GPU pairs. The implementation presented in this thesis also utilizes constant memory as well as device functions to further optimize the algorithm.

#### 2.2 Izhikevich SNN

In his well-known paper [14], Izhikevich described the "biological plausibility and computational efficiency" of spiking and bursting neurons and provides models that mimc these properties. Some of these spiking models include "Integrate & Fire" (I&F), I&F with Adaptation, Integrate-and-Fire-or-Burst, Resonate-and-Fire, Spiking Model by Izhikevich, Morris-Lecar [15], Wilson [16], and Hodgkin-Huxley [17]. The rest of the works detailed in this section use one of the aforementioned models to perform neural network simulations.

In [18], Fidjeland and Shanahan make use of the Izhikevich neuron model to perform real-time large-scale simulations of biological brain structures. The GPU implementation in [18] can deliver up to 550 million spikes per second with a single device, which is approximately 55,000 neurons with 1000 synapses per neuron while portraying biologically

accurate conditions in the simulation. Through the use of a GPU kernel a throughput of up to 22 times the original was achieved.

Gupta and Long in [19] use a slightly different approach than previous papers. Instead of using the neural network to perform biological simulations, the spiking neural network model in their research is used to identify characters in a character set. The GPU is not used in their research, however, it is a great example of how SNNs can be used to solve real-world problems. Similar to the research done in this thesis, both excitatory and inhibitory connections are made within the network to train using a known data set.

Han and Taha also present a similar pattern recognition software based on both Izhikevich and Hodgkin-Huxley models in [20]. Three GPU platforms are examined including the GeForce 9800 GX2, the Tesla C1060, and the Tesla S1070. The research presented attempts to prove the efficacy of using the GPU to accelerate a SNN based character recognition networks for large scale systems. The results show accelerations of up to 5.6x (for Izhikevich) and 84.4x (for Hodgkin-Huxley) over the fastest tested CPU (a quadcore 2.67 GHz Xeon processor).

Bhuiyan, Pallipuram, and Smith in [21] investigate optimization techniques as well as performance improvements for SNNs utilizing GPUs and compare the results to a 2.66 GHz Intel Core 2 Quad for the Izhikevich and Hodgkin-Huxley models. These two models are chosen for their study because of the significant differences in computational intensity: the Hodgkin-Huxley model is very computationally intensive whereas the Izhikevich model is much more compute efficient. It is shown that for a small flops/bytes ratio, it is not desirable to offload the computation to the accelerator, however, benefits can be seen when the application has a larger flops/bytes ratio. The Izhikevich model results in about 0.65

flops/byte while the Hodgkin-Huxley model stand at 6.02 flops/byte. Speedups of approximately 9x are achieved by the Izhikevich model where speedups of about 115x are achieved using the Hodgkin Huxley model. The conclusions show that the best speedup over all test cases for the Izhikevich model is the optimized Intel Xeon implementation while the GPU implementation with coalesced global memory accesses and texture lookup proved better for the Hodgkin-Huxley model. Pallipuram, Bhuiyan, and Smith also present a performance analysis comparing NVIDIA's Fermi architecture with AMD's Radeon 5870 using OpenCL in [22]. The four SNN models used for the performance analysis include [15], [16], [17], and [18] with optimization techniques for each algorithm. Speedups of 857x and 658x were achieved on the Fermi and Radeon respectively for the Hodgkin Huxley model with 9.72 million neurons.

All previous work done with SNNs has led to the research completed in this thesis. The research in this thesis provides a simulation of spiking neural networks performed on GPUs with one caveat, the neural network can polychronize. A network that can polychronize "exhibits reproducible time-locked but not synchronous firing patterns with millisecond precision" [23]. The neural network simulation presented in this thesis has this property and is therefore slightly different than previously completed research. It provides a computationally efficient method for simulation as well as reproducibility of biological characteristics found in realistic simulations.

#### 2.3 Longest Common Subequences (LCS)

In [24], Khajeh-Saeed et al. explore the problem of sequences alignment by developing a GPU implementation of the Smith-Waterman algorithm. As mentioned in this research, sequence matching (or sequence alignment) is well-known for its use in testing DNA and protein sequences with large databases. The implementation presented demonstrates the used of up to four GPUs executing the Smith-Waterman algorithm in parallel. The results show that for large enough problems the single-GPU can accelerate the CPU version up to 45x and the speedup linearly scales as the number of GPUs increases (up to 4 GPUs).

McGuiness et al. present a performance study for four very different applications in [25] including the STREAM Benchmark, Smith-Waterman, Graph Analysis, and the Unbalanced Tree Search. Each of these applications is evaluated using single and multiple GPUs and have much different memory needs illustrating the types of scientific applications that could make use of the GPU architecture and its parallelism. For the Smith-Waterman algorithm (a.k.a. the LCS problem), when compared to a single core CPU the speedup is 100x for a single GPU while speedups of 5,335x are achieved when utilizing 120 GPUs.

In [26], Steinbrecher et al. also present a case study that includes the LCS but does not utilize an accelerator, only multi-core systems. The two machines used in the research presented by Steinbrecher include a 12-core and a 4-core machine. The use of techniques such as altering the sequential loops and skewing the loop by changing the linear schedule achieves speedups of approximately 42x. Further optimization such as computing entire rows in one thread led to speedups of approximately 60x.

The concepts described in each of these papers were taken into account when studying the LCS algorithm for this research. In this research both multi-core and multi-GPU implementations are studied compared to the previous works that only include multi-core or single-GPU.

#### 2.4 Summary

In this chapter, an overview of the related work that motivates the use of these algorithms is given. This chapter also provides a brief explanation of the contribution of this research relative to the previously completed work (mentioned at the end of Sections 2.1, 2.2, and 2.3. The next chapter provides a detailed description of the algorithms that were used in this research along with the governing equations used to implement each of the algorithms.

### Chapter 3

# Background

This chapter presents background information on the algorithms used in this research, specifically, k-means clustering, Izhikevich spiking neural networks, and the longest common subsequences problem. The underlying equations for all three algorithms are presented and explained. This chapter is concluded with a discussion of how each of these applications can be used in real-world circumstances.

### 3.1 K-Means Clustering

The k-means clustering algorithm [6] is a method for analyzing clusters of data, typically in data mining applications. The goal of the algorithm is to categorize each data point in a cluster to belong to the cluster with the closest centroid, or mean, to achieve the minimal sum of distances between each point and centroid. More generally, the k-means algorithm attempts to make k clusters out of the n observations, or data points, where each observation is a member of the cluster with the nearest mean. The initial centroids can be chosen to be any values within the bounds of the dataset, but there are available methods that lead to better performance of the algorithm. These methods however are not the aim of this research study.

In this study, the initial centroids are defined by choosing pseudo-random data points in the data set.

#### 3.1.1 K-Means Algorithm

The k-means algorithm can be described using the following steps:

- 1. Initialize the points that will be categorized as the initial means.

- Assign each observation (data point) in the data set to belong to the cluster with the closest centroid.

- Recalculate the positions of the new centroids based on the new clusters that have been created.

- 4. Continue steps 2 and 3 until the centroids for each cluster are no longer changing or they are oscillating between a set of points with similar function values.

The k-means algorithm categorizes data points into clusters to minimize the mean distance between all the points; therefore, the main computation in this algorithms involves the distance formula between two points. The main goal of the algorithm can be expressed as an objective function, **Z**, utilizing the equation for Euclidean distance (Eq. 3.1):

$$\min Z = \sum_{i=1}^{k} \sum_{j=1}^{n} ||x_{j} - c_{i}||^{2}$$

(3.1)

where  $\|x_j - c_i\|^2$  is the Euclidean distance between the point in question,  $x_i$ , and the centroid of the cluster,  $c_i$ , k is the number of clusters, and n is the number of data observations within the set.

The first step of the algorithm involves initializing the centroids for the first computation. There are numerous ways to initialize these values, some more efficient than others. Some of these methods include:

- 1. Locate the minimum and maximum data points in the set and initialize the centroids in a way that they are evenly spaced across the domain of the set. This method works well if all data points are somewhat evenly distributed within the domain. However, without doing preprocessing to determine the distribution (which uses computation time), there is not a reasonable method to determine if the points fit this distribution.

- 2. Use completely random data points (either points inclusive in the data set or just random points located within the domain). This method allows for quick initialization of centroids as well as semi-distributed centroids because of the random number generator. However, randomization could lead to inconsistent performance caused by the distribution of the random values and the choice of initial means. If every execution chooses different initial means, there is no guarantee the algorithm will execute in the same number of clock cycles as it would with a different set of means.

- 3. Choose initial centroids based on the size of the data set and the number of clusters that are needed. For example, the means of a given set S with size n would have initial means k given by the equation  $m_i = \left\{0 \quad \frac{n}{k} \cdots \left(n \frac{2*n}{k}\right) \quad (n \frac{n}{k})\right\}$ , where each  $m_i$  is an initial mean. This method is used in the study because of its quick computation.

After the initial centroids are determined the next step is to attribute each of the points within the set to the nearest centroid. This is completed by using the Euclidean distance formula to find the distance between every point and each centroid as shown in Eq. 3.2.

$$c_i = \{x_c: ||x_c - m_i||^2 \le ||x_c - m_j||^2 \forall j, 1 \le j \le k\}$$

(3.2)

Based on Euclidean distance formulas the k-means algorithm determines which points belong to each cluster, also known as the "assignment step"

After each point has been assigned to a cluster, new cluster means should be calculated, also called the "update step". In this step, the new members of the cluster are taken into account when calculating the new cluster centroid. To calculate the new mean,  $m_i$ , the observations in each cluster,  $x_c$ , are summed together and then the total is normalized by the cardinality of the cluster  $|c_i|$ , given by Eq. 3.3.

$$m_i^{(t+1)} = \frac{1}{|c_i|} \sum_{x_c \in c_i} x_c \tag{3.3}$$

Once the new means have been determined, the algorithm can continue. The process of assigning all points to the closest mean and then recalculating each mean is repeated until the centroids in two adjacent iterations of the algorithm are the same. This means that the algorithm has converged to a local optimum solution; however it is not guaranteed by this algorithm that the global optimum solution will be found.

#### 3.1.2 K-Means Clustering Real-world Applications

K-means clustering is a somewhat general algorithm; therefore, there are many uses where the algorithm can be utilized to solve real-world problems. In [27], Ray and Turi illustrate that a major disadvantage of the k-means algorithm is that the user must specify the number of clusters, k, that should be used in the calculation. In this study, segmented images are produced for 2 clusters up to  $k_{max}$  clusters, which is followed by calculations that determine which number of clusters finds the minimum value for the given parameter being measured. This concept could be used to further the research in this thesis by studying a given data set and determining what is the optimal number of clusters to achieve a minimum optimal value.

In [28], Huang derives an extension of the k-means algorithm (called k-modes) that allows for the use of categorical data rather than purely numerical data. In the paper, soybean

disease and credit approval data sets are used to demonstrate the clustering performance of the k-modes algorithm, but many other types of categorical data could be used with the same result. For instance, in automotive manufacturing, there have been strides to predict when faults or warranty claims will occur for vehicles. Models have been constructed based on very large sets of data on each of the cars being produced as well as each car that was returned for a warranty claim. Based on the different types of cars and car parts, categorical data can be constructed and then clustered to detect faulty parts or even faulty manufacturers.

In [29], Oyelade et al. describe a method to utilize k-means clustering to monitor students' academic performance in a higher education academic environment. Oyelade et al. used the created models to predict students' academic performance in English and Mathematics studies. This study provides a method for instructors and institutions to monitor performance of students as well as use the models to improve on future performance of the academic results provided by the institution.

There are numerous applications that can utilize clustering algorithms such as the k-means algorithm. Along with the three uses mentioned, there are still a broad range of applications that benefit from clustering algorithms.

#### 3.2 Spiking Neural Networks

Neural networks or artificial neural networks (ANNs) is a paradigm of processing techniques that strive to perform pattern recognition and machine learning types of algorithms, to model the functionality of the biological nervous system, namely the human brain. Simon Haykin described neural networks as "a massively parallel distributed processor made

up of simple processing units, which has a natural propensity for storing experiential knowledge and making it available for use. It resembles the brain in two respects:

- 1. Knowledge is acquired by the network from its environment through a learning process.

- 2. Interneuron connection strengths, known as synaptic weights, are used to store the acquired knowledge." in his book [30].

Neural networks model the smallest fundamental component present in the human brain, the *neuron*. Neurons simply use signals from other neurons to determine if they will "fire" or not, meaning that they are active in a given layer of the neural network. Propagation of these signals through multiple layers of the network produces the output, which is how the human brain functions at a high level. In order to accurately represent the human brain and mimic functionality, millions of neurons per network are required, which sometimes is not feasible. Therefore, there are not many models that can accurately represent the human brain activity, but simply mimic the functionality to perform other tasks.

Spiking Neural Networks (SNNs) are the third generation artificial neural networks that attempt to make the modeling more biologically accurate and have a realistic simulation of the human brain. The difference in ANNs and SNNs is that the neurons in an ANN typically "fire" during each propagation cycle while neurons in SNNs only "spike" or "fire" at certain points in time. The properties of the spike including time of the spike are determined solely by the input to the network, which is where information is propagated and processed. Because SNNs have neurons that "spike" only at certain time steps they work very well with applications that incorporate a time component, such as signal processing or image/video recognition.

There are many models that have been developed for SNNs, ranging in computation intensity, complexity, and efficiency. Some of these models include the Izhikevich Model [7], the Wilson Model [16], the Morris-Lecar Model [15], and the Hodgkin Huxley Model [17]. Each of these four models has different properties and complexities and, therefore, each perform differently when implemented. In previous research [31], these models are evaluated and implemented. However in this research, a variation of the Izhikevich model is studied. The overall model, described in the next section, is identical to the original Izhikevich model, however there is one slight difference. The implementation studied in this research allows the spiking neural network to polychronize, which means that the model exhibits reproducible time-locked firing patterns that are not necessarily synchronous. In the following section, the Izhikevich SNN Model is described and the governing equations are defined and explained.

#### 3.2.1 Izhikevich SNN Model

Eugene M. Izhikevich, in [Simple Model of Spiking Neurons], presents a model that is able to replicate the spiking behavior of certain types of cortical neurons. To develop this model, Izhikevich "combined the biological plausibility of [the] Hodgkin-Huxley-type dynamic model and the computationally efficient models [such as the Morris-Lecar and Wilson models]". By reducing the complexity of the Hodgkin-Huxley model and using computations similar to those of the more efficient models, the computations for the Izhikevich model are able to be completed quicker and therefore used for real-time simulations. The Izhikevich model can be described using the following ordinary equations:

$$v' = 0.04 * v^2 + 5 * v + 140 - u + I$$

(3.4)

$$u' = a * (b * v - u) \tag{3.5}$$

if

$$v \ge +30 \text{ mV}$$

, then  $\begin{cases} v \leftarrow c \\ u \leftarrow_+ d \end{cases}$  (3.6)

"The variable v represents the membrane potential of the neuron and u represents a membrane recovery variable, which accounts for the activation of  $K^+$  ionic currents and inactivation of  $Na^+$  ionic currents, and it provides negative feedback to v. After the spike reaches its apex (+30 mV), the membrane voltage and the recovery variable are reset according to Eq. 10 [Simple Model of Spiking Neurons]." By selecting the model variables a, b, c, and d the model is able to accurately mimic firing patterns for neurons as well as compute each stage of neurons very quickly. The parameters of the Izhikevich models which govern its behavior are as follows:

- a describes the time scale of recovery for the variable u (if smaller values of this parameter, the variable u "recovers" slower)

- b describes the sensitivity of the recovery for the variable u

- c describes the reset value of the membrane potential v after a spike occurs

- d describes the reset value of the recovery variable u after a spike occurs

Selecting these parameters can be described as a large research area to optimize the efficiency of the model, but this is not the aim of this research. The set of parameters chosen for this work is based on the typical values mentioned in [Simple Model of Spiking Neurons].

#### 3.2.2 SNN Real-world Applications

Neural Networks have numerous applications that are used every day in the real-world. From speech/audio/video recognition to machine learning, neural networks can be used for a variety of problems. In [32], Ghosh-Dastidar and Adeli present a model using supervised learning with SNNs to classify EEF readings. There are three applications that are used and tested with this model including the XOR problem, the Fisher iris classification problem, and the epilepsy and seizure detection (EEG classification). Using the single-spiking SNN and 82% classification accuracy was achieved for the EEG classification problem while a 90.7%-94.8% accuracy was achieved by the multi-spiking neural network (MuSpiNN).

#### 3.3 Longest Common Subsequences Problem

The longest common subsequences (LCS) [8] problem analyzes two sequences and performs comparisons between the two to compute the longest subsequence that is common to both of the sequences. The idea behind this algorithm is to use dynamic programming methods to break the problem into smaller sub-problems to obtain the optimal solution. A mathematical definition of the LCS algorithm can be given by the equation (Eq. 3.7):

$$LCS(S_{i}^{(1)}, S_{j}^{(2)}) = \begin{cases} \emptyset & if \ i = 0 \ or \ j = 0 \\ LCS(S_{i-1}^{(1)}, S_{j-1}^{(2)}) + 1 & if \ s_{i}^{(1)} = s_{j}^{(2)} \\ max(LCS(S_{i}^{(1)}, S_{j-1}^{(2)}), LCS(S_{i-1}^{(1)}, S_{j}^{(2)})) & if \ s_{i}^{(1)} \neq s_{j}^{(2)} \end{cases}$$

(3.7)

where  $S^{(1)}$  and  $S^{(2)}$  are the two subsequences and can be defined as the following:

$$S^{(1|2)} = \left\{ s_1^{(1|2)} \quad s_2^{(1|2)} \cdots s_{(m-1|n-1)}^{(1|2)} \quad s_{(m|n)}^{(1|2)} \right\} \tag{3.8}$$

and  $LCS(S_i^{(1)}, S_j^{(2)})$  represents the entire set of longest common subsequences which have prefixes  $S_i^{(1)}$  and  $S_j^{(2)}$ . To find the longest common subsequence, the algorithm simply compares all of the elements  $s_i^{(1)}$  and  $s_j^{(2)}$ . If the two elements are equal (second line in the above equation) then the entire subsequence is extended by that common element. If the two elements are not equal (third line in the above equation), then the longest of the two subsequences  $LCS(S_i^{(1)}, S_{j-1}^{(2)})$  and  $LCS(S_{i-1}^{(1)}, S_j^{(2)})$  is kept.

The longest common subsequences problem uses "traceback" matrices as its main form of displaying the answer. Within these traceback matrices, the length of the longest subsequence can be found as well as the subsequence itself. Without the matrix, only the length would be available at the end of the algorithm. There are often very large problems that use this method to find the solution to a subsequencing problem, but the main drawback is matrices must be stored in memory, which can be costly. Dynamic programming helps in this aspect of the problem. Since the problem is already constructed in a way that it is broken up into subproblems, these very large systems (matrices) can be partitioned into subproblems and the solutions can be constructed from the combination of the results. During the process of computing the LCS score for the set of sequences, additional information can be added to the matrix for the backtracking step of the algorithm. The chosen method for representing the "traceback" elements uses directional arrows which can be determined using the equation (Eq. 8):

$$b(S_{i}^{(1)}, S_{j}^{(2)}) = \begin{cases} if \ s_{i}^{(1)} = s_{j}^{(2)} \\ " \uparrow " & if \ s_{i}^{(1)} \neq s_{j}^{(2)} \ and \ LCS(S_{i-1}^{(1)}, S_{j}^{(2)}) \geq LCS(S_{i}^{(1)}, S_{j-1}^{(2)}) \\ " \leftarrow " & if \ s_{i}^{(1)} \neq s_{j}^{(2)} \ and \ LCS(S_{i-1}^{(1)}, S_{j}^{(2)}) < LCS(S_{i}^{(1)}, S_{j-1}^{(2)}) \end{cases}$$

(3.9)

If the two elements  $s_i^{(1)}$  and  $s_j^{(2)}$  are the same, the arrow simply points to the upper left corner of the matrix. If the two elements  $s_i^{(1)}$  and  $s_j^{(2)}$  are different, the arrow points toward the value either above or to the left with the higher value. After the entire matrix has been filled with traceback elements, the arrows illustrate how to construct the subsequence that was found using the LCS algorithm.

This method of calculation is frequently used with bio-informatics type algorithms; therefore, there are many examples that use "AGCT" (Adenine, Guanine, Cytosine, and Thymine) combinations, which appear in DNA. The following is a simple example that illustrates the traceback matrix concept.

Example: Given the two sequences GTCAG and AGCGA, use the LCS algorithm and a traceback matrix to compute the longest common subsequence for the two given sequences. For each element  $s_i^{(1)}$  in the sequence, compare it to the corresponding element  $s_j^{(2)}$  in the other sequence. The following table illustrates the completed table for the LCS algorithm including backtracking, which gives the solution GCG as the longest common subsequence of GTCAG and AGCGA.

|   | 0 | G          | Т          | С           | Α          | G          |

|---|---|------------|------------|-------------|------------|------------|

| 0 | 0 | 0          | 0          | 0           | 0          | 0          |

| Α | 0 | <b>↑</b> 0 | <b>↑</b> 0 | <b>↑</b> 0  | <b>∇</b> 1 | ←1         |

| G | 0 | <b>∇</b> 1 | ←1         | ←1          | <b>↑</b> 1 | <b>∇</b> 2 |

| С | 0 | <b>↑</b> 1 | <b>↑</b> 1 | <b></b> ∇ 2 | ← 2        | <b>↑</b> 2 |

| G | 0 | <b>∇</b> 1 | <b>↑</b> 1 | <b>↑</b> 2  | <b>↑</b> 2 | <b>₹</b> 3 |

| Α | 0 | <b>↑</b> 1 | <b>↑</b> 1 | <b>↑</b> 2  | ₹3         | <b>↑</b> 3 |

Figure 3.1 – Example of LCS Algorithm

## 3.3.1 LCS Real-world Applications

The longest common subsequences problem is a general mathematical algorithm, but is most widely used in the field of genetics and biology because it works very well with DNA and RNA sequences. In [33], Bereg et al. develop a model for RNA multiple sequence structural alignment, which is based on the longest common subsequences algorithm. The model presents a polynomial  $O(n^2)$  time algorithm as well as a Maximum Loop Chain algorithm with  $O(n^5)$  time, which investigates many sequences simultaneously using the dynamic programming paradigm found in the LCS algorithm. In [34], Iyer and Saxena investigate the flowshop scheduling problem, which is an algorithm that schedules jobs on an assembly line while minimizing the completion time of the process. The two methods in [34] include using standard implementation of the flowshop scheduling problem and a problem that is tailored using specific information. The LCS algorithm was used in [34] to solve the minimization problem used on an assembly line.

Aside from these, there are many other problems and algorithms that make use of the LCS algorithm. Any time subsequencing is performed in the context of genetics or biological information, most likely the LCS algorithm will be used at some point during the process to compute subsequences.

## 3.4 Summary

In this chapter, an in-depth description of the three algorithms that are used in this research is provided. These algorithms include k-means clustering, Izhikevich spiking neural networks, and the longest common subsequences problem. Each of these algorithms represents a different type of computation and illustrate why the performance study using

heterogeneous systems is relevant. The k-means algorithm involves computation with double precision values including the data points and centroids. The spiking neural network involves computing the next stage spikes and firing patterns for the network. The LCS algorithm involves comparisons between sequences of characters that are represented differently in hardware compared to double precision values. The next chapter provides a detailed description of the computing architecture and programming models use in this research.

# Chapter 4

# Computing Architectures and

# **Programming Models**

Over the past few years, multi-core and many-core architectures have become popular technologies used in numerous areas of computational research. Multi-core architectures can be described as systems that contain more than 2 cores and are typically used for general purpose processing rather than parallel processing. Many-core architecture can be described as systems that contain hundreds or thousands of cores and are built specifically to perform parallel tasks. With the advent of multi-core and many-core architectures, programming models such as MPI [35] and CUDA [3] were developed to aid developers in efficiently utilizing the resources available.

This chapter reviews the two different programming models that are used in this research as well as introduces the GPGPU and multi-core architectures as well as mentions the Xeon Phi [1] coprocessor architecture. Clemson University's Palmetto Cluster [36] is also described. (The heterogeneous system used in this research.) Although the Xeon Phi coprocessor was not used for results in this research, it can be used in future work to perform the same types of parallel tasks as the GPGPU.

## 4.1 Computing Architectures

In this research, multi-core and many-core architectures are evaluated in the context of the scientific algorithms described in Chapter 3. In this chapter, the multi-core and many-core architectures will be described along with the corresponding programming models. The Palmetto Cluster will also be detailed as the heterogeneous system used for this research.

#### 4.1.1 Multi-Core Architecture

Processors have been around for several decades, but not until the early 2000s did the major processor vendors (Intel, AMD, etc.) begin to realize the need for multi-core processors. Multi-core architectures began with simple two-core (dual-core) designs present in the AMD Phenom II X2 [37] and the Intel Core Duo [38] and have evolved today to incorporate up to ten or more cores. Multi-core processors provide multiprocessing capabilities that allow the user to parallelize applications while only utilizing a single device. Not every application can benefit from the multi-core architectures, however. If the application can be run in parallel (i.e. simultaneously, not sequentially), then the application has a good chance to perform well on these architectures. Today's CPUs comprise numerous advancements over their predecessors that allow for performance improvements including caching, pipelining, wider data paths, superscalar execution, increased transistor density, and increased transistor performance.

In this study, Intel's Xeon E5-2665 [39] will be used as the primary CPU device when performing serial computations and as well as utilizing pairs of them for highly parallel computations without accelerators. This CPU is one of the primary CPUs present in the

Palmetto Cluster, which is used for most of the results. The following section discusses the architecture details of the Xeon E5-2665.

#### 4.1.1.1 Intel Xeon E5-2665

The Xeon E5 [39] series architecture (codenamed Romley) is a 32nm octo-core device with each core based on Intel's Sandy Bridge-E architecture and runs at 2.4 GHz with a max turbo frequency of 3.1 GHz with overclocking. Each Romley core includes two 32KB, 8-way L1 caches (one for instructions and one for data), a 256KB, 8-way L2 cache, and a 20MB L3 cache. Each socket (LGA2011) allows for up to 2 processors for multiprocessing capabilities. Table 4.1 gives a more concise overview of the important properties of the Xeon E5-2665 architecture. In this study, the Palmetto Cluster [36] will be used with the Intel Xeon E5-2665 in a dual socket configuration creating 16 cores per node with 32 threads.

Table 4.1: Intel Xeon E5-2665 ("Romley") Statistics

|                       | , , ,                   |

|-----------------------|-------------------------|

|                       | Intel Xeon              |

| Processor Name        | E5-2665                 |

| Clock Speed           | 2.4 GHz                 |

| Max Turbo Frequency   | 3.1 GHz                 |

| # of Cores            | 8                       |

| # of Threads          | 16                      |

| Max CPU Configuration | 2                       |

| L3 Cache              | 20 MB                   |

| Instruction Set       | 64-bit                  |

| Lithography           | 32 nm                   |

| Max Memory Size       | 384 GB                  |

| Memory Types          | DDR3-800/1066/1333/1600 |

| # of Memory Channels  | 4                       |

#### 4.1.2 **GPGPU** Architecture

The advent of fully programmable graphical devices has changed the face of parallel programming. The previous generation of parallel programming involved multi-core processors only, which are capable of parallel computations but lack the inherent parallel nature of today's General Purpose Graphical Processing Units (GPGPUs). Software applications are growing ever larger and more complex; hence there is a need to utilize concurrency (such as that present on a GPGPU) to achieve dramatically increased speed and execution efficiency.

The past decades have seen impressive leaps in GPGPU technology beginning with devices specifically designed for graphical processing to current devices with thousands of cores designed for parallel computations, not limited to graphical processing and image rendering [40]. At its inception, the GPU was used for graphics rendering on personal computers, gaming consoles, and mobile devices. The highly parallel nature of the GPGPU has allowed for a paradigm shift, making the devices much more useful for developing complex software and applications by utilizing the quantity of processor cores compared to a typical CPU.

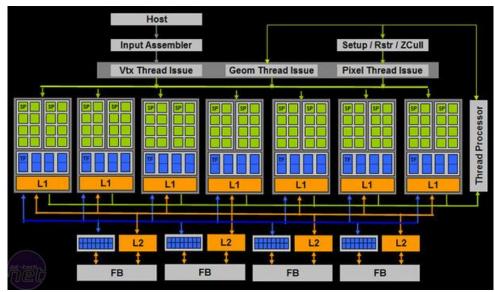

In 2006, NVIDIA introduced the GeForce 8 series revolutionizing the GPU market bringing to light the massively parallel nature of the GPU and exposing the device as a frontrunner in general-purpose computing. NVIDIA's G80 [41] based GeForce 8800 GTX GPGPU (2006) shown in Figure 4.1 was the first GPGPU architecture to introduce a unified pipeline, which replaced all vertex and pixel pipelines present in older model GPUs. This

generation of GPUs was also the first to utilize Streaming Processors (SPs), simple compute units grouped together within a small area on the device.

Figure 4.1: NVIDIA GeForce 8800 GTX Architecture [41]

Each SP can produce a result that can either be utilized by other SPs or stored in local memory for later calculations. The advantage of an SP is that similar simultaneous computations can be performed on different SPs on different elements in a data set utilizing the high-speed decode and execute logic present on each SP. A group of SPs is used in the device to execute single instruction multiple data (SIMD) type instructions providing tremendous parallel processing capabilities. Also introduced in the G80 series GPU was the concept of shared memory. Located inside each SP, this fast on-chip memory allows for barrier synchronization and cache-like storage of data for fast retrieval for threads active on a given SP.

Many GPGPUs used in HPC clusters today are still modeled after many of the same features as the G80 (GeForce 8800 GTX) architecture. After the G80 architecture, the next

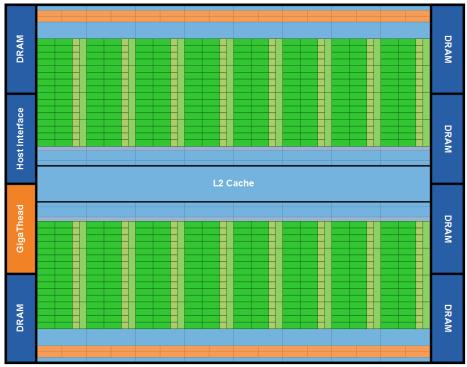

substantial development for NVIDIA was in 2009 with the introduction of the Fermi [42] architecture shown in Figure 4.2.

Figure 4.2: NVIDIA Fermi Architecture [42]

The Fermi architecture was an extension of the G80 architecture that included the advent of steaming multiprocessors (SMPs), which incorporates a group of SPs, a double-precision compute unit, and shared memory within the SMP. With the introduction of the Fermi architecture, new terms were coined to explain the GPGPU and how it functioned at a low level. A *thread* is the basic unit of execution in a GPGPU and is executed on a SP within a SMP. Within a SMP, groups of threads, *thread blocks*, are executed on the multiprocessors. The *thread blocks* are further divided into SIMD groups of 32 threads called *warps*, which can also be divided into groups of 16 threads called half-warps.

The first Fermi based GPU contained 16 SMPs, each containing a total of 32 cores creating a device total of 512 CUDA cores. Each SMP is equipped with both an integer

arithmetic logic unit (ALU) and a floating point unit; therefore, in each clock cycle, each SMP can execute either a floating point or integer instruction. The Fermi architecture also included a dual warp scheduler allowing for two warps to be scheduled on the device simultaneously.

The most recent development in the GPU architecture made by NVIDIA is the Kepler [Reference: Kepler Architecture] architecture. This architecture was used in this research and will be explained in the subsequent section along with details about the specific device used.

#### 4.1.2.1 NVIDIA Tesla K20 (Kepler GK110)

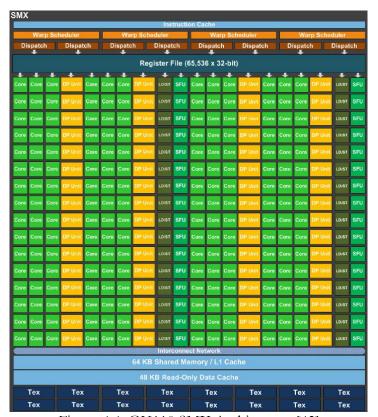

In 2012, NVIDIA introduced the Kepler GK110 [43] architecture offering the GPU market a significant improvement over the previous Fermi architecture including improvements in compute capabilities and performance and reduced power consumption. Of the GK110 architecture (Figure 4.3) devices, the K20 and K20X GPUs are two of the most popular devices being used in machines and clusters today.

Figure 4.3: NVIDIA Kepler GK110 Architecture [43]

The GK110 Kepler GPUs typically have 5GB of GDDR5 memory, with a GPU clock speed of 706 MHz and a memory clock speed of 1300 MHz. Each GK110 GPU supports CUDA compute capability 3.5. The Kepler GK110 contains *Next Generation Streaming Multiprocessors* (SMX), which provide astounding performance improvements while lowering the necessary power consumption compared to earlier generations of the GPU containing SMPs. Each SMX (Figure 4.4) inside a Kepler GK110 contains 192 single-precision CUDA cores, while the SMX still holds the ability for single and double-precision arithmetic computations. The Kepler family of GPUs can support a total of 16 SMX units per block, but all GK110 devices do not contain the maximum number of SMX units. For example, the NVIDIA Tesla K20 (the device used in this research) contains 13 SMX units, meaning the device contains a total of 2496 CUDA cores instead of the maximum 3072 CUDA cores.

Figure 4.4: GK110 SMX Architecture [43]

The Kepler GK110 GPU has a warp size of 32 threads and supports up to 64 warps per SMX. This architecture also includes a quad warp scheduler (compared to the dual warp scheduler of the Fermi), which allows for a total of four warps to be executed concurrently. Other important information about the GK110 architecture (in particular, the NVIDIA Tesla K20) can be found in Table 4.2.

The Kepler GK110 also has a few features that are altogether new to the realm of GPU programming including Hyper Q and dynamic parallelism. Hyper Q [44] enables multiple CPU threads to offload tasks to the GPU simultaneously, which creates less idle time for the CPU while increasing the utilization of the GPU. Dynamic parallelism allows the developer to have an application directly launched by the GPU instead of going through the CPU as a middle-man. This allows for more effective load balancing on the GPU as well as lower communication times between the host and device.

Table 4.2: Kepler GK110 (Tesla K20) Statistics

|                              | 1110 (1esia 1920) Statistics       |

|------------------------------|------------------------------------|

|                              | NVIDIA Tesla K20                   |

| GPU Name                     | GK110                              |

| Processor Size               | 28 nm                              |

| GPU Clock Speed              | 706 MHz                            |

| Memory Clock Speed           | 1300 MHz                           |

| Memory Size                  | 5120 MB (GDDR5)                    |

| Memory Width                 | 320-bits                           |

| Threads/Warp                 | 32                                 |

| Max Warps/SMX                | 64                                 |

| Max Threads/SMX              | 16                                 |

| Max Thread Blocks/SMX        | 2048                               |

| Max Registers/Thread         | 255                                |

|                              | 64 KB (48 KB shared/16 KB L1 cache |

|                              | or                                 |

| SMX Memory (Local)           | 16 KB shared/48 KB L1 cache        |

| # of CUDA Cores              | 2496                               |

| Single Precision Performance | 3.52 teraflops                     |

| Double Precision Performance | 1.17 teraflops                     |

# 4.2 Programming Models

This section introduces the programming models used in this study: MPI [35] and CUDA [3]. Message Passing Interface (MPI) is a standardized "message-passing" system design that allows programmers to utilize the parallel nature of modern processors and processor cores. This provides programmers with the ability to parallelize applications and algorithms when only multi-core processors are available. Compute Unified Device Architecture (CUDA) is a widely used programming platform and framework for parallel computing on GPGPUs. CUDA is designed for use with NVIDIA GPGPUS, and furthermore only supports NVIDIA GPGPUs. For a more generic solution, a programmer could use a model such as OpenCL [2], which supports a wide variety of HPC architectures such as GPGPUs and FPGAs while not being vendor specific. CUDA was used in this research study instead of OpenCL or another generic models because of the availability of NVIDIA GPGPUs.

#### 4.2.1 MPI

One of the more popular techniques for utilizing multi-core processors is to "scatter" the data and computations to multiple processor cores to achieve a faster result. Message Passing Interface (MPI) [35] is a standardized system designed by collaborators in academia and industry to allow "message-passing" in a parallel environment. MPI provides system calls and functions for users to easily parallelize computations and spread data across a multi-core system. MPI allows users of a wide variety of programming languages including Fortran, C, C++, and Java to utilize the parallel functionality of message passing. Table 4.3 gives a few

of the commonly used functions and their descriptions to explain the premise of the programming language.

Table 4.3: Commonly used MPI Functions

| Function      | Description                              |

|---------------|------------------------------------------|

| MPI_Send      | Send a buffer of data to another process |

|               | Receives a buffer of data from another   |

| MPI_Recv      | process                                  |

|               | Send a buffer of data to every process   |

| MPI_Bcast     | from "root" process                      |

|               | Send a buffer from one process to all    |

| MPI_Scatter   | other processes (dissemination)          |

|               | Gather together values from a group of   |

| MPI_Gather    | processes                                |

| MPI_Init      | Initialize MPI execution environment     |

| MPI_Finalize  | Terminate MPI execution environment      |

|               | Performs a specified operation on each   |

| MPI_Allreduce | processes set of data (i.e. addition)    |

#### 4.2.2 **CUDA**

The Compute Unified Device Architecture (CUDA) [3] showcases the power of GPGPUs by providing the programmer a C-like experience when developing. CUDA was introduced in 2007 by NVIDIA to be a single programming language for use with NVIDIA GPUs. CUDA is vendor specific (meaning that it is only possible to utilize CUDA on NVIDIA GPUs) however most details in the CUDA programming language have been optimized to work well with its family of GPUs. OpenCL is another language that can be used to program any type of GPU, but there are limited optimizations performed for architectures because it is designed for being open source and working on a multitude of devices.

The CUDA architecture, being architecture specific, is able to exploit all specialties of the NVIDIA GPU including shared and textured memory and utilizing all of the processing (CUDA) cores. In CUDA, the code that is executed on the device is known as a *kernel*. Kernels are C-like functions (with CUDA specific directives) that are executed in parallel by utilizing every CUDA core on the device. In most situations, one kernel is executed on the device followed by another in a sequential fashion. In newer models of NVIDIA GPUs, it is possible to launch multiple kernels simultaneously, but this is not studied in this research.

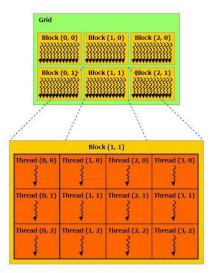

Each thread that is created for a given application executes the kernel in parallel. CUDA executes threads in groups called thread blocks as a grid in either one-, two-, or three-dimensions. Each thread block is executed on a separate SMX, which are grouped into 32 thread groups called warps. The threads inside each thread block can be accessed through device parameters threadIdx, blockIdx, and blockDim, which give the programmer the ability to access any thread by using its global index. The threadIdx variable specifies the thread index within a given block, blockIdx gives the number of the current block, and the number of threads per dimension is given by the variable blockDim. When a CUDA kernel is launched, the information about number of blocks and number of threads per block is defined and setup on the device. Figure 4.5 shows the CUDA thread hierarchy and how the threads and blocks inside a kernel interact.

Figure 4.5: Thread block layout in CUDA [3]

The CUDA programming model provides a wide range of memory types for which each thread has the opportunity to access throughout the kernel execution. At the per-thread level, there is local memory and registers that each thread can access for a private memory location separate from other threads. Even though the local memory is only accessible to a single thread it actually resides in the external device memory (global memory) and is therefore slower than other types of memory. All threads in a thread block share a bank of memory, coincidentally named *shared memory*, in which each thread in the block can access and modify. Thread synchronization is needed for shared memory as well because multiple threads could possibly change the same memory location. In addition to the shared and local memory, there is also *global memory* and *constant memory*. Global memory is the largest of the memory banks on the GPU device (off-chip memory) and is accessible to any thread in the kernel. The constant memory is also accessible to all threads active in a kernel however it is read-only memory so it cannot be modified. To make constant memory accesses faster, because the memory locations are read-only and it resides in the global memory, the values in memory are cached and

therefore only take a few clock cycles to retrieve rather than a few hundred retrieving data from the global memory.

There are many optimization techniques that can be used when performing GPU programming using CUDA including memory optimization, varying execution configurations, and instruction optimizations. Rather than mentioning all optimization techniques for CUDA, the particular optimization techniques and implementation strategies that are used for the applications mentioned in Chapter 3 will be described in detail in Chapter 5.

### 4.3 Palmetto Cluster

For the purposes of this research, the Palmetto Cluster [36] is used as the heterogeneous computing platform. This cluster allows the user to specify whether a CPU-only implementation is sufficient or whether a homogeneous system utilizing CPU-GPU pairs is necessary. Each node (that was utilized) in the cluster is an HP SL250s containing two Intel Xeon E5-2665 (see Section 4.1.1.1) processors with 16 cores and 64GB of RAM together on the machine. To utilize all cores on a given node, MPI is used to handle all communications and transfers. Along with the pair of processors on each node, they are also equipped with 2 NVIDIA Tesla K20 GPU devices. For applications that will utilize the GPU, it is possible to use open source languages such as OpenCL to program the GPU, but for the purposes of this study, CUDA is the only programming language used.

For applications that can utilize multiple GPUs to perform the computations, other strategies can be employed. The CUDA-MPI programming model can be applied to distribute the data to each of the GPUs to perform a larger scale parallel computation. The same idea is applied for programming on a single CPU-GPU pair except the data that will be computed

will be divided onto different nodes so the processing can be performed in parallel. The communication between the CPU and GPU is done over the PCI-Ex bus while the communication between nodes uses 56g Infiniband [4].