## Clemson University TigerPrints

#### All Theses

Theses

8-2013

# Thermo-Mechanical Effects Of Thermal Cycled Copper Through Silicon Vias

James Marro Clemson University, JMarro@g.clemson.edu

Follow this and additional works at: https://tigerprints.clemson.edu/all\_theses Part of the <u>Materials Science and Engineering Commons</u>

#### **Recommended** Citation

Marro, James, "Thermo-Mechanical Effects Of Thermal Cycled Copper Through Silicon Vias" (2013). *All Theses*. 1688. https://tigerprints.clemson.edu/all\_theses/1688

This Thesis is brought to you for free and open access by the Theses at TigerPrints. It has been accepted for inclusion in All Theses by an authorized administrator of TigerPrints. For more information, please contact kokeefe@clemson.edu.

### THERMO-MECHANICAL EFFECTS OF THERMAL CYCLED COPPER THROUGH-SILICON VIAS

A Thesis Presented to the Graduate School of Clemson University

In Partial Fulfillment of the Requirements for the Degree Master of Science Materials Science and Engineering

> by James Marro August 2013

Accepted by: Dr. Kathleen Richardson, Committee Co-Chair Dr. Yaw Obeng, Committee Co-Chair Dr. Igor Luzinov Dr. Marian Kennedy Dr. Fei Peng

# ABSTRACT

The semiconductor industry is currently facing transistor scaling issues due to fabrication thresholds and quantum effects. In this "More-Than-Moore" era, the industry is developing new ways to increase device performance, such as stacking chips for three-dimensional integrated circuits (3D-IC). The 3D-IC's superior performance over their 2D counterparts can be attributed to the use of vertical interconnects, or through silicon vias (TSV). These interconnects are much shorter, reducing signal delay. However TSVs are susceptible to various thermo-mechanical reliability concerns. Heating during fabrication and use, in conjunction with coefficient of thermal expansion mismatch between the copper TSVs and silicon substrate, create harmful stresses in the system. The purpose of this work is to evaluate the signal integrity of Cu-TSVs and determine the major contributing factors of the signal degradation upon in-use conditions. Two series of samples containing blind Cu-TSVs embedded in a Si substrate were studied, each having different types and amounts of voids from manufacturing. The samples were thermally cycled up to 2000 times using three maximum temperatures to simulate three unique in-use conditions. S<sub>11</sub> parameter measurements were then conducted to determine the signal integrity of the TSVs. To investigate the internal response from cycling, a protocol was developed for cross-sectioning the copper TSVs. Voids were measured using scanning electron microscope and focused ion beam imaging of the cross-sections, while the

ii

microstructural evolution of the copper was monitored with electron backscattering diffraction. An increase in void area was found to occur after cycling. This is thought to be the major contributing factor in the signal degradation of the TSVs, since no microstructural changes were observed in the copper.

# ACKNOWLEDGMENTS

I am grateful to the many people who aided me in this thesis work. First, I would like to thank my advisors, Dr. Kathleen Richardson from Clemson University, and Dr. Yaw Obeng from the National Institute of Standards and Technology, for their guidance and support, without whom, none of this work would have been possible. I would also like to thank my committee members, Dr. Igor Luzinov, Dr. Marian Kennedy, and Dr. Fei Peng of Clemson University. Dr. Chukwudi Okoro's immense knowledge of this area was also of major help as was Binayak Kandel's assistance in recording measurements during my absence. Thanks to NIST for the funding and the Semiconductor and Dimensional Metrology Division for supplying labs for some of my research. Dr. Daniel Josell and Sandy Claggett also facilitated and extended their knowledge in grinding and polishing of these specimens. I would like to thank them alongside Dr. Taghi Darroudi, of the Advanced Materials Research Laboratory's EM lab, for his FIB Furthermore, my gratitude goes out to those that assisted in my expertise. training of the electron microscopes, especially Dr. JoAn Hudson and Donald Mulwee, at AMRL's EM lab. To my GPCL group members, especially Dave Musgraves and Pete Wachtel, thanks for helping me learn the ins and outs of our lab equipment. Lastly, I would like to thank my future wife, Emma Westlund, and the rest of my family for their encouragement and support.

# TABLE OF CONTENTS

| Pag                                              | je |

|--------------------------------------------------|----|

| TITLE PAGE                                       | i  |

| ABSTRACT                                         | ii |

| ACKNOWLEDGMENTS in                               | v  |

| LIST OF TABLES                                   | ii |

| LIST OF FIGURESiz                                | х  |

| LIST OF ACRONYMS                                 | v  |

| CHAPTER ONE: MOTIVATION AND OBJECTIVES           | 1  |

| 1.1 Motivation                                   | 1  |

| 1.2 Objectives                                   | 4  |

| 1.3 Thesis Scope                                 | 7  |

| 1.4 References                                   | 8  |

| CHAPTER TWO: INTRODUCTION10                      | 0  |

| 2.1 3D Stacking of Chips10                       | 0  |

| 2.2 Benefits of 3D IC13                          | 3  |

| 2.3 Challenges of 3D Integrated Circuits (ICs)14 | 4  |

| 2.4 TSV Structure                                | 5  |

| 2.5 Integrated Circuit (IC) Materials18          | 8  |

Table of Contents (Continued)

| Pa                                                        | ge |

|-----------------------------------------------------------|----|

| 2.6 TSV Processing1                                       | 9  |

| 2.7 Thermo-Mechanical Reliability of TSVs2                | 1  |

| 2.8 Real World Conditions and Potential Impact on TSVs    | 1  |

| 2.9 TSV analysis – Common Analytical Techniques           | 2  |

| 2.10 Focus of This Work                                   | 3  |

| 2.11 References                                           | 5  |

| CHAPTER THREE: EXPERIMENTAL PROCEDURE4                    | .1 |

| 3.1 Preparation of The TSVs Used In This Study4           | .1 |

| 3.2 Pre- and Post-Fabrication Materials Characterization4 | .4 |

| 3.3 References6                                           | 0  |

| CHAPTER FOUR: RESULTS                                     | ;1 |

| 4.1 As-Received Sample TSV Characterization6              | 1  |

| 4.2 Cross-Sectioning Protocol – Repeatability of Process  | 3  |

| 4.3 RF Signal Measurements6                               | 6  |

| 4.4 Void and Other Defect Measurements6                   | 9  |

| 4.5 Microstructure7                                       | 3  |

| CHAPTER FIVE: DISCUSSION OF RESULTS8                      | 2  |

| 5.1 As-Received Sample Characterization8                  | 2  |

| 5.2 Cross-Sectioning Methodology8                         | 3  |

Table of Contents (Continued)

| Page                                                  |

|-------------------------------------------------------|

| 5.3 RF Measurements - Signal Integrity of the Cu-TSVs |

| 5.4 Void and Other Defect Evolution in Cu-TSVs        |

| 5.5 Microstructural Evolution of Cu-TSVs89            |

| 5.6 References                                        |

| CHAPTER SIX: CONCLUSIONS AND FUTURE WORK              |

| 6.1 Conclusion95                                      |

| 6.2 Future Work98                                     |

| APPENDICES                                            |

| Appendix A: Sample Organization100                    |

| Appendix B: S <sub>11</sub> Parameter Measurements101 |

| Appendix C: Grain Size Distribution by Sample104      |

# LIST OF TABLES

| ble Pa                                                                                                                                                    | ge |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 Material properties of Si and Cu, data taken from reference [25]2                                                                                     | 22 |

| 4.1 Average grain aspect ratio of the as-received , 2000 cycled non-voide and voided samples                                                              |    |

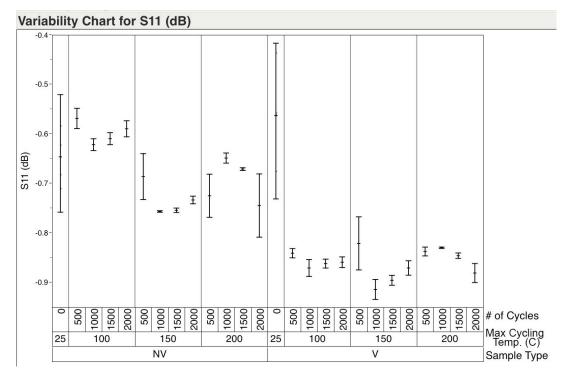

| 5.1 Variance component chart, which shows the amount of influence each component has on the S <sub>11</sub> parameter                                     |    |

| A1 The number of samples used for the different procedures conducted in<br>this study separated by sample type and maximum thermal cycling<br>temperature |    |

# LIST OF FIGURES

| Figure Page                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 Graph showing the accuracy of Moore's law up to 2011, taken from reference [6]3                                                                                                                                                                                                                                                                                                       |

| 2.1 A SiP which utilizes wire bonding, taken from reference [2]11                                                                                                                                                                                                                                                                                                                         |

| 2.2 Illustration of an Imec WLP, which uses microbumps, taken from reference [4]12                                                                                                                                                                                                                                                                                                        |

| 2.3 Breakdown of a 3D IC, taken from reference [5]                                                                                                                                                                                                                                                                                                                                        |

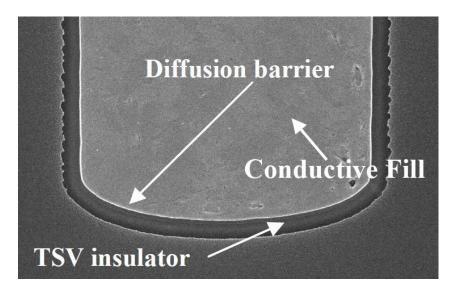

| 2.4 Illustration of the three layers of typical TSV, insulator, diffusion barrier,<br>and conductive layer, taken from reference [14]17                                                                                                                                                                                                                                                   |

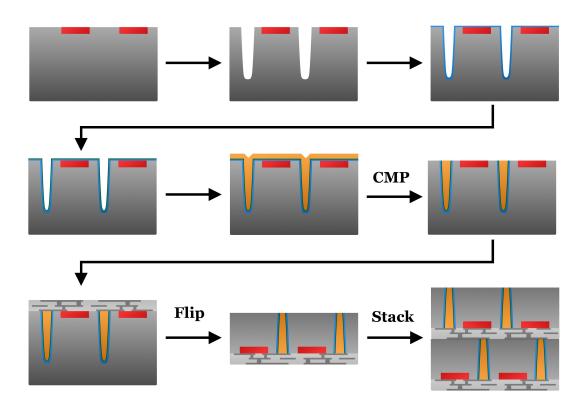

| 2.5 Process flow of via middle filling. a.) FEOL is placed on chip; b.)DRIE cuts via holes in the Si chip; c.) CVD of isolation layer; d.) PVD of barrier layer; e.) deposition of Cu seed layer and fill using PVD and ECD respectively; f.) CMP of surface; g.) addition of BEOL; h.) flipping of the chip in preparation for final steps; i.) alignment and stacking of multiple chips |

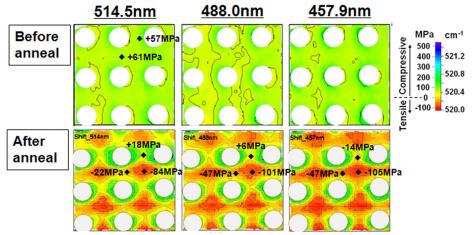

| 2.6 Stress map of Silicon substrate, measured by micro-raman, taken from reference [23]23                                                                                                                                                                                                                                                                                                 |

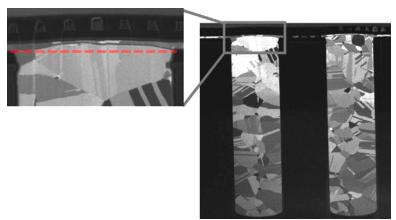

| 2.7 Cross-section of a TSV, which has undergone out-of-plane expansion,<br>leading to deformation of the BEOL. A dashed line has been<br>added for planar reference, taken from reference [29]24                                                                                                                                                                                          |

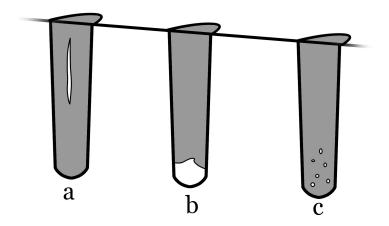

| 2.8 Different void types found from flawed processing. A.) seam void; b.) void at bottom of a incompletely filled TSV; c.) microvoids25                                                                                                                                                                                                                                                   |

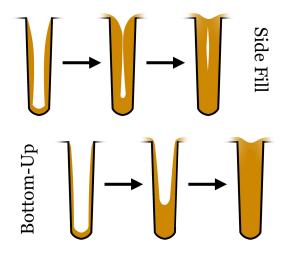

| 2.9 The process flow for filling TSVs, revealing how bottom up filling creates void-free TSVs while sidewall filling can produce seams                                                                                                                                                                                                                                                    |

| Figure                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

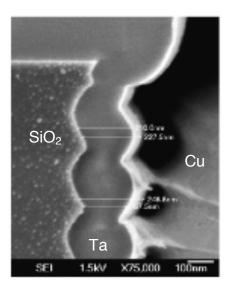

| 2.10 Scalloped Ta barrier layer, taken from reference [20]                                                                                                                                                                            |

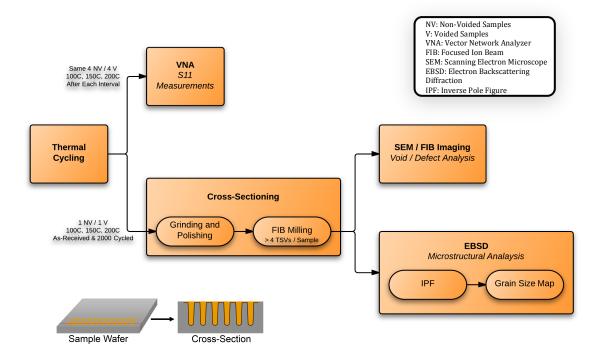

| 3.1 Diagram showing the experiment sequence of this study43                                                                                                                                                                           |

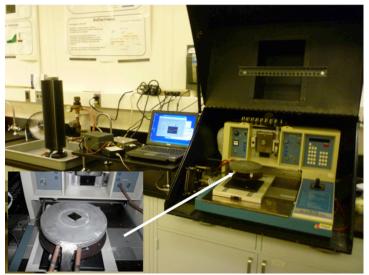

| 3.2 The thermal cycling instrument used for heat-treating samples. The sample chamber, on the right, contains a hot plate, which exposes the samples to heat and allows fast cooling                                                  |

| 3.3 A typical thermal cycle temperature profile for a maximum cycling temperature of 150°C45                                                                                                                                          |

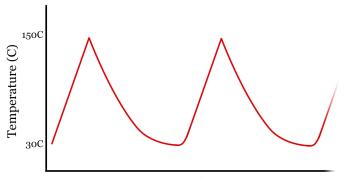

| 3.4 Diagram showing the thermal cycling conditions, including the three maximum cycling temperatures and cycle numbers at which measurements were made                                                                                |

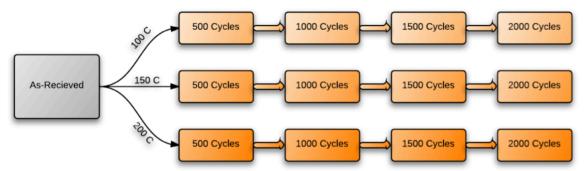

| 3.5 The polishing arm and sample holder for cross-sectioning samples.<br>The two micrometers on the arm are used to align the sample, for<br>accurate cross-sectioning and the sample is mounted to the glass<br>on the sample holder |

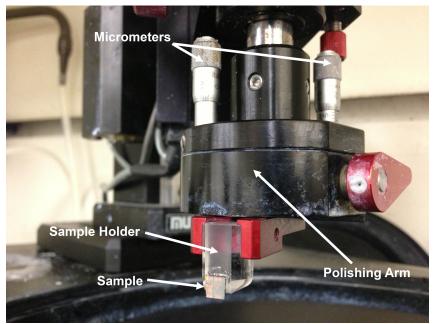

| 3.6 Ion beam image of TSV after milling, where diamond is embedded into the Cu, causing uneven FIB milling49                                                                                                                          |

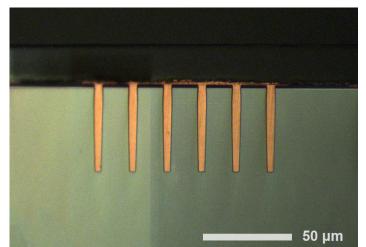

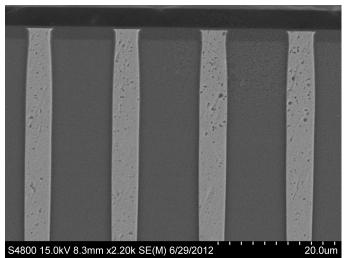

| 3.7 A successfully polished cross section of a sample. The cover glass remains on top of the sample and six Cu-TSVs are shown49                                                                                                       |

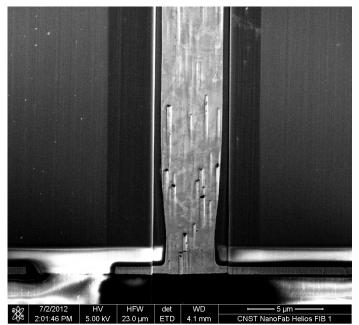

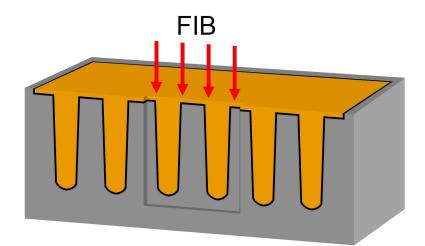

| 3.8 Illustration of the FIB milling direction, parallel to the cross section51                                                                                                                                                        |

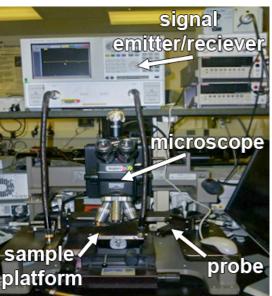

| 3.9 The components of the VNA used to measure $S_{11}$ parameter                                                                                                                                                                      |

| Figure | Page                                                                                                                                                                                                                                                                                       |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

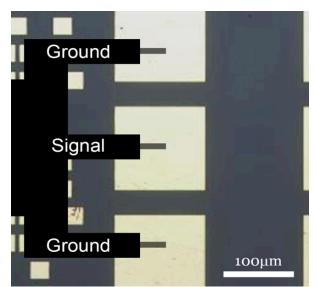

| 3.10   | Illustration of the three-pronged probe used by the VNA to measure the $S_{11}$ parameter                                                                                                                                                                                                  |

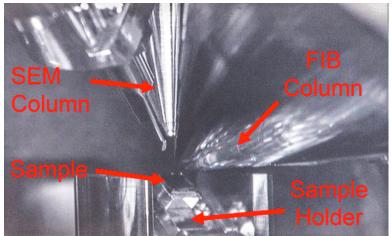

| 3.11   | Infrared image of the Hitachi NB5000 dual beam chamber55                                                                                                                                                                                                                                   |

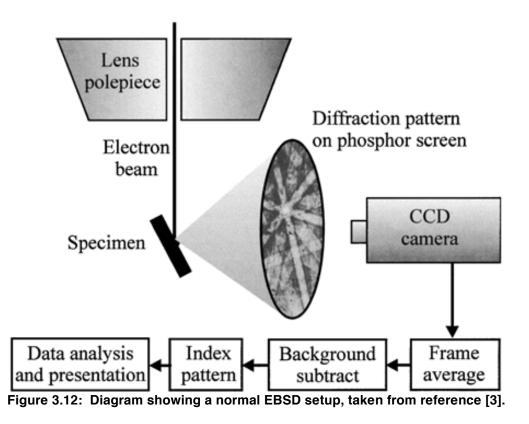

| 3.12   | Diagram showing a normal EBSD setup, taken from reference [3]57                                                                                                                                                                                                                            |

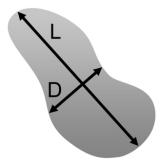

| 3.13   | An illustration of the measurements needed for grain size calculations.<br>L is the longest length of the grain and D is the width perpendicular<br>to L                                                                                                                                   |

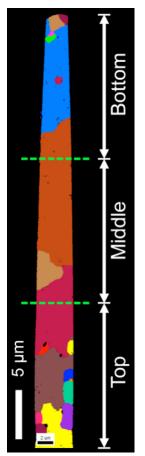

| 3.14   | A grain size map of a TSV, showing the regions used for regional grain size measurements                                                                                                                                                                                                   |

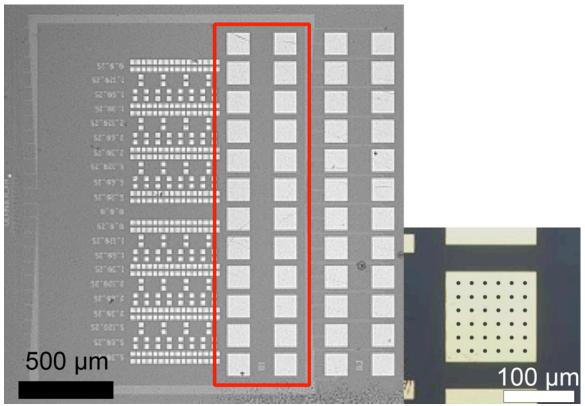

| 4.1    | Optical images of an as-received sample. The left shows the two<br>rows of twelve bond pads of interest highlighted in red. On the<br>right is a close up optical image of a single bond pad, where the<br>black dots represent the 6 by 6 TSV matrix that lies underneath the<br>bond pad |

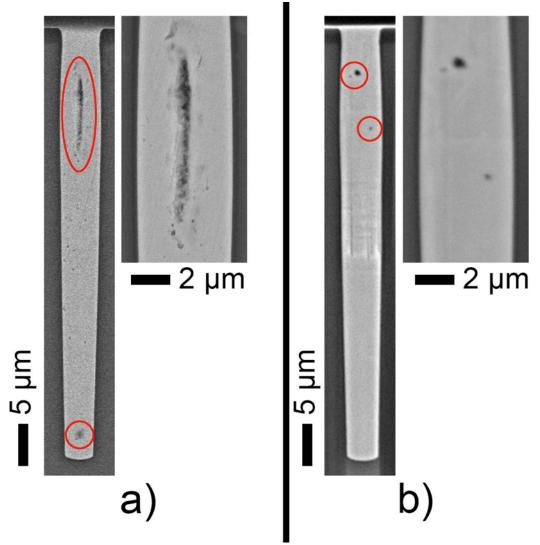

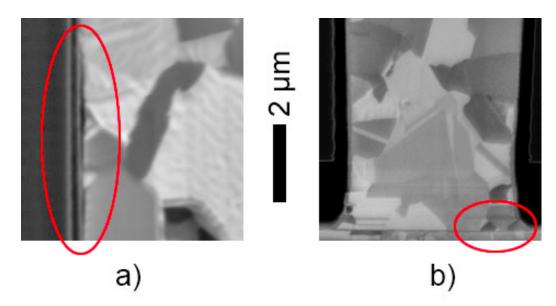

| 4.2    | SEM images of the as-received sample cross-sections with the voids circled in red and a zoomed in image of each sample for the a) voided sample and b) non-voided sample63                                                                                                                 |

| 4.3    | Diamond particles from the diamond lapping paper embedded in Cu-<br>TSVs                                                                                                                                                                                                                   |

| 4.4    | FIB images and IPF maps from the EBSD. a) FIB image of voided sample, b) IPF map of TSV shown in a), c) FIB image of non-voided sample, d) IPF map of TSV shown in c)65                                                                                                                    |

| Figure | Page                                                                                                                                                                                                                                                 |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

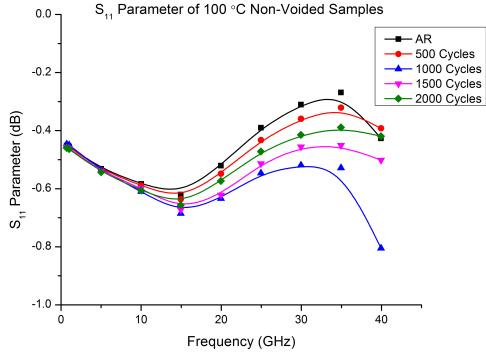

| 4.5    | The S <sub>11</sub> parameter as a function of frequency for the non-voided samples cycled to a maximum temperature of 100 °C68                                                                                                                      |

| 4.6    | Graph of the S <sub>11</sub> parameter at 10 GHz and 20 GHz for all samples,<br>showing how the non-voided samples have less loss than the<br>voided samples                                                                                         |

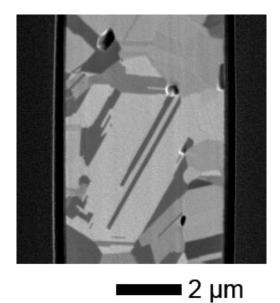

| 4.7    | FIB image of typical void location in the Cu grain boundaries70                                                                                                                                                                                      |

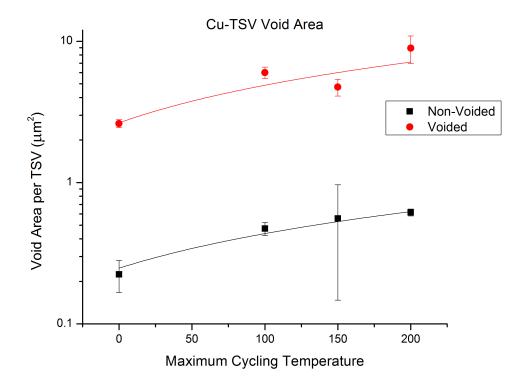

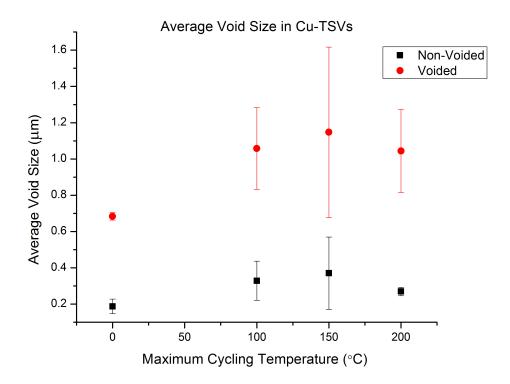

| 4.8    | The average void area within in the TSVs before and after cycling for<br>both sample types, which shows a linear correlation to maximum<br>cycling temperature71                                                                                     |

| 4.9    | The average void size for both sample types before and after 2000 thermal cycles. No significant change in average void size is seen from thermal cycling                                                                                            |

| 4.10   | Ion beam images of a) delamination between the Cu and the barrier<br>layer after 2000 cycles with a max cycling temperature of 200 °C<br>and b) voids at the Cu-TSV/bond pad interface before thermal<br>cycling                                     |

| 4.11   | Examples of the EBSD maps used to study TSVs: a) FIB image, b) IPF map, c) grain size map after twin refining. The small scale bars at the bottom of each map are 2 $\mu$ m, but a more legible scale bar is shown on the right side of the figure74 |

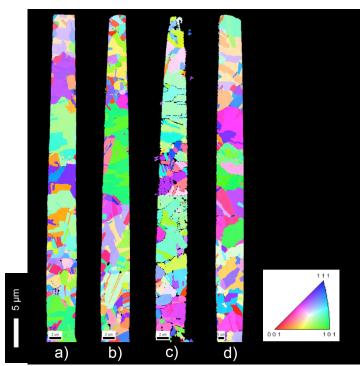

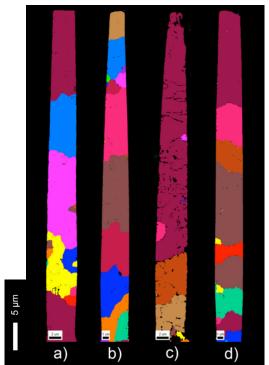

| 4.12   | Normal direction inverse pole figure maps of the non-voided 2000 cycled, a) as-received, b) 100 °C, c) 150 °C, d) 200 °C, TSVs. No preferential grain orientation is apparent                                                                        |

| Figure | Page                                                                                                                                                                          |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.13   | Normal direction inverse pole figure maps of the voided 2000 cycled,<br>a) as-received, b) 100 °C, c) 150 °C, d) 200 °C, TSVs. The Cu-<br>TSVs are randomly oriented75        |

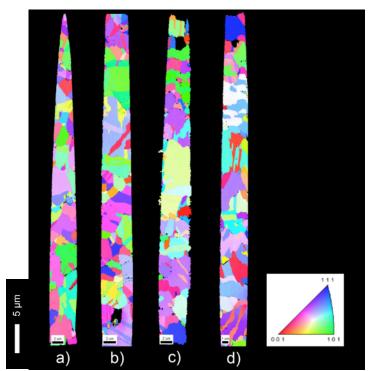

| 4.14   | Grain size maps of the non-voided 2000 cycled, a) as-received, b) 100 °C, c) 150 °C, d) 200 °C, TSVs after twin refining. No significant changes in grain size or shape       |

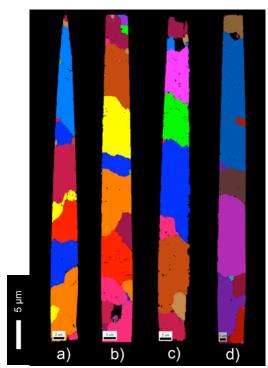

| 4.15   | Grain size maps of the voided 2000 cycled, a) as-received, b) 100 °C,<br>c) 150 °C, d) 200 °C, TSVs after twin refining. No significant<br>changes in grain size or shape77   |

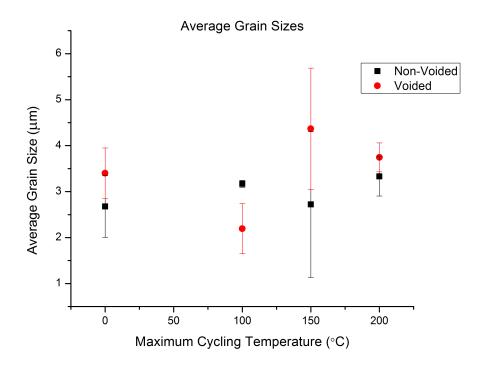

| 4.16   | Graph of the average grain size changes due to the maximum cycling temperature for the 2000 cycled samples. The grain size does not appear to change with cycling temperature |

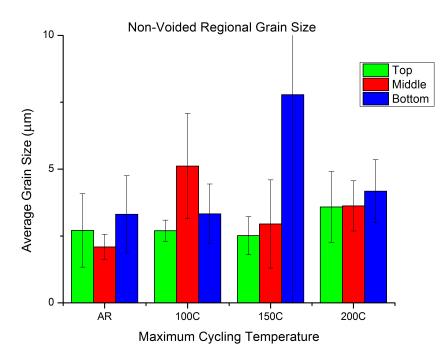

| 4.17   | Average regional grain sizes of the non-voided samples, where there<br>is no discernable difference between regions                                                           |

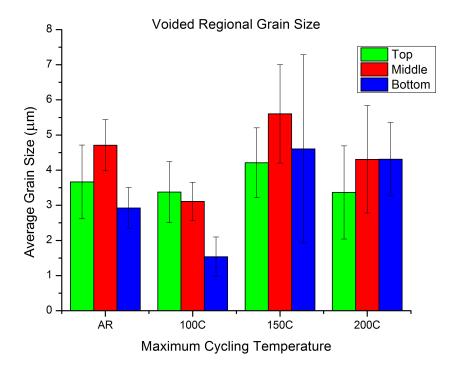

| 4.18   | The average regional grain sizes of the voided samples, where the grain size of the bottom region is shown to be smaller than the middle region some samples                  |

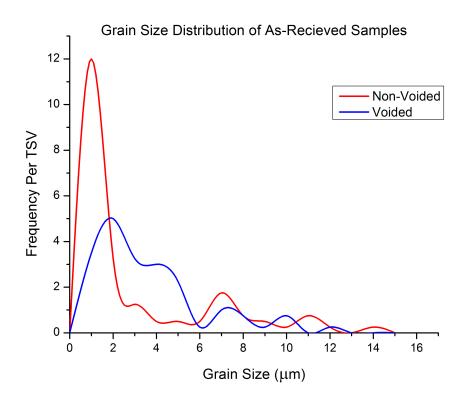

| 4.19   | Grain size distribution of the Cu-TSVs for the as-received samples,<br>which shows the voided samples have a broader distribution than<br>the non-voided samples              |

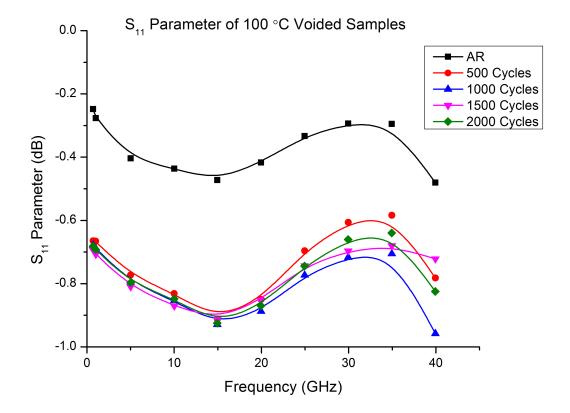

| B1     | S <sub>11</sub> parameter as a function of frequency for the voided samples as<br>they underwent cycling with a maximum temperature of<br>100 °C                              |

| ure Pa                                                                                                                                                            | age |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

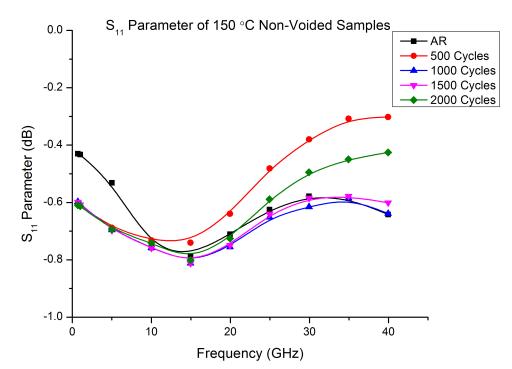

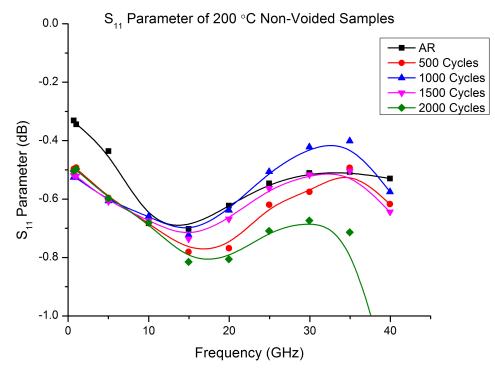

| B2 S <sub>11</sub> parameter as a function of frequency for the non-voided samples<br>as they underwent cycling with a maximum temperature of<br>150 °C10         |     |

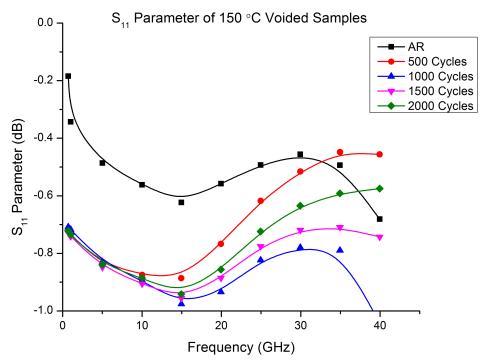

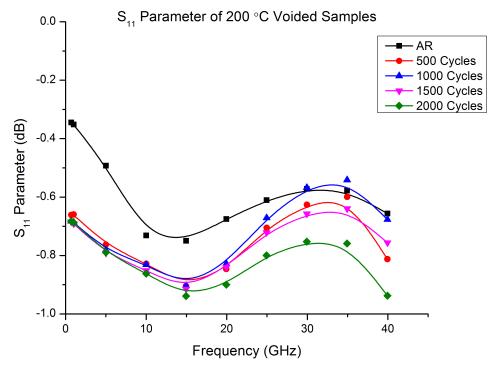

| <ul> <li>B3 S<sub>11</sub> parameter as a function of frequency for the voided samples as they underwent cycling with a maximum temperature of 150 °C.</li> </ul> | 02  |

| B4 S <sub>11</sub> parameter as a function of frequency for the non-voided samples<br>as they underwent cycling with a maximum temperature of<br>200 °C10         |     |

| <ul> <li>B5 S<sub>11</sub> parameter as a function of frequency for the voided samples as they underwent cycling with a maximum temperature of 200 °C.</li> </ul> | 03  |

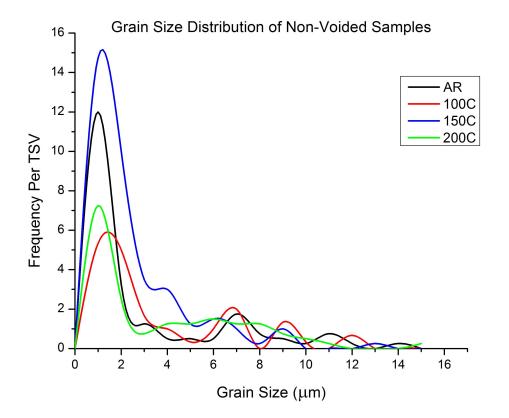

| C1 Grain size distribution of non-voided samples cycled with different<br>maximum cycling temperatures                                                            | 04  |

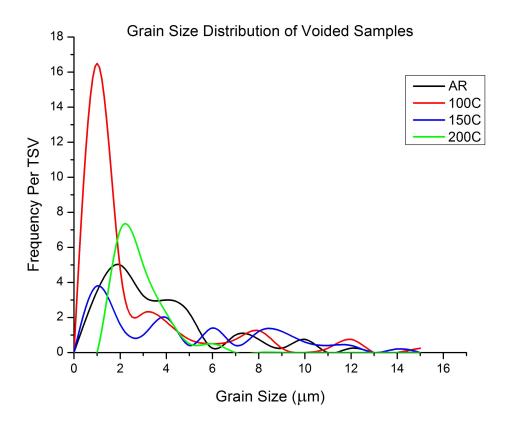

| C2 Grain size distribution of voided samples cycled with different<br>maximum cycling temperatures                                                                | 05  |

# LIST OF ACRONYMS

- 2D: Two-Dimensional

- 3D: Three-Dimensional

- AC: Alternating Current

- AFM: Atomic Force Microscopy

- Al: Aluminum

- AR: As-Received

- BEOL: Back End Of The Line

- **BSE: Backscattered Electrons**

- **CD: Critical Dimension**

- CMP: Chemical Mechanical Polishing

- CTE: Coefficient of Thermal Expansion

- Cu: Copper

- CVD: Chemical Vapor Deposition

- DRIE: Deep Reactive Ion Etching

- EBSD: Electron Backscattering Diffraction

- ECD: Electro-Chemical Deposition

- FCC: Face Centered Cubic

- FEA: Finite Element Analysis

- FEM: Finite Element Modeling

- FEOL: Front End Of The Line

- FIB: Focused Ion Beam

- GaAs: Gallium Arsenide

- Ge: Germanium

- IC: Integrated Circuit

- IPF: Inverse Pole Figure

- ISE: Ion Induced Secondary Electrons

- LMIS: Liquid Metal Ion Source

- NV: Non-Voided Samples

- Poly-Si: Polycrystalline Si

- PVD: Physical Vapor Deposition

- RF: Radio Frequency

- SE: Secondary Electrons

- SEM: Scanning Electron Microscope

- Si: Silicon

- SiO<sub>x</sub>: Silicon Oxide

- SiP: System-in-Package

- SoC: System-on-Chip

- Ta: Tantalum

- TEOS: Tetraethyl Orthosilicate

- Ti: Titanium

TSV: Through Silicon Via

V: Voided Samples

VNA: Vector Network Analyzer

W: Tungsten

WLI: White Light Interferometer

WLP: Wafer Level Packaging

## CHAPTER ONE

## MOTIVATION AND OBJECTIVES

#### 1.1 Motivation

Traditional integrated circuits (IC) have been available since the mid 1900's, replacing the vacuum tube with the invention of integrated based solid state, fabricated on thin semiconductor substrates (i.e., wafers) [1]. The segmented devices (i.e., chips) have provided the basis for which electronics are built, and has propelled higher performance and other needs to meet the demand of the end-user.

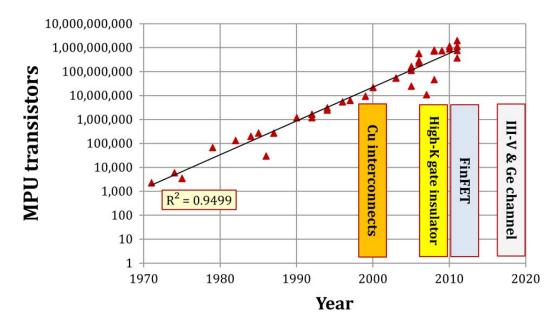

Traditionally, higher performance generally means cramming more devices into a unit area of semiconductor substrate; this is accomplished by geometrically shrinking the device features such as reduction of the feature size of fabricated transistors. This shrinkage, also described as feature scaling, lead to an increased density of devices on a single chip. The scaling trend has motivated an empirical relationship between performance and chip complexity is known as Moore's Law, which states that the amount of transistors on a chip increases two fold about every two years as seen in Figure 1.1 [2]. Over the past 40 years, scientists and engineers have relentlessly followed this law. This has led to current devices with critical dimensions (CD) of 22 nm, as illustrated by the production of Intel's smallest platform (Ivy Bridge) transistors [3]. However, the

size of transistors is quickly approaching the size of an atom, a few angstroms, and this presents numerous challenges. First, the tools and the lithographybased fabrication technology needed for the continued geometric scaling down of transistor feature size is not scaling with Moore's law. Furthermore, continued scaling of the transistor will also lead to a change in device physics, as quantum mechanics sets in. As transistors shrink, so must interconnects. Unlike transistors, decreasing cross-sectional area of an interconnect decreases its performance. The resistance of a wire can be calculated using equation 1,

$$R = \rho \frac{L}{WH} \tag{1}$$

where R is the resistance,  $\rho$  is the resistivity, and the length, width, and height of the interconnect are denoted by L,W, and H respectively; hence, the resistance is inversely proportional to the interconnect's cross-section (WH) [1]. The smaller distances between interconnects and other devices on the chips as well as longer interconnect lengths, increase the parasitic capacitance [4] and cross-talk between adjacent devices. Thus, as scaling down continues, interconnects become the performance-limiting component as opposed to transistors. This situation is known as "the interconnect bottleneck" within the semiconductor industry.

Figure 1.1: Graph showing the accuracy of Moore's law up to 2011, taken from reference [6].

Three-dimensional (3D) devices are emerging as a potential solution to this bottleneck. Interestingly, the 3D stacking of ICs enables the co-integration of devices that perform different functions into a single system. This co-integration of devices has ushered in the so-called 'More-than-Moore' era [5]. The Morethan-Moore approach focuses on system integration as opposed to transistor down-scaling (Moore's law). The stacking of chips allows for more transistors on a device, benefiting from increased performance, form factor, and integration. 3D interconnects are necessary for communication across multiple chips. While there are many different interconnect technologies for achieving 3D-stacked dies, the use of through-silicon vias (TSV) has emerged as the most efficient and preferred technique. These interconnects are achieved by vertically drilling through the active silicon chip and subsequently filling it with a conductive material, such as copper to realize electrical connectivity, between stacked layers.

While TSVs are just one part of the 3D electronic system, their effectiveness in providing 'connectivity' will ultimately limit the device's overall performance. The temperature of chips in electronic devices fluctuates during fabrication, and during use. Thus, thermo-mechanical reliability concerns have risen due to mismatch between the thermal characteristics of the materials used in the TSV. Typically, the electrically conducting pathways in the interconnect expand differently than the surrounding semiconductor material resulting in stress build-up during use. Thus, a detailed understanding of the inter-material interactions and potential failure mechanisms are needed to understand the reliability limits of such devices. Such multi- and inter-material interactions are of utmost importance to design, fabrication and implementation of TSVs in future semiconductor device systems.

#### 1.2 Objectives

TSVs provide an interconnect basis for the 3D stacking of chips, which make up 3D integrated circuits (3D-IC). This study strives to investigate the thermo-mechanical reliability of through-silicon vias (TSV) when subjected to thermal cycling. This investigation aims to define possible causes of

degradation/failure through pre- and post-cycling evaluation of TSV morphology and microstructure to draw a correlation between radio-frequency (RF) signal integrity and the material changes seen in the via structure. The thermal cycling in the present effort serves to simulate the typical lifetime conditions or long-term use of the device.

This study was carried out on non-stacked wafers, containing blind Cu-TSVs. Two wafer types were studied, where the processing conditions were slightly different. Due to this variation in initial via processing methods, different amounts and types of pre-existing voids have been observed in each wafer type. Thus, this variation has allowed a side-by-side basis by which initial defect formation and in-service evolution with thermal cycling conditions can be observed. As discussed in detail in subsequent chapters, samples containing TSVs underwent thermal cycling from room temperature to an established varied maximum temperature and the TSVs were studied to examine the following factors to realize the thesis' target goals:

- Evaluate the RF reflection coefficient (S<sub>11</sub>) parameter to determine the signal integrity of commercially-prepared Cu-TSVs from simulated use conditions.

- 2. Develop a method for examining the microstructure and defects within the Cu-TSVs.

- Identify the pre-existing defects in the TSVs of the two commercially manufactured wafers and how these defects form and evolve with thermal cycling.

- Quantify the difference in Cu microstructure of the two wafer type TSVs as well as how this microstructure evolves due to thermal cycling.

- 5. Correlate the performance variation of the Cu-TSVs to the internal aspects of the TSVs, such as defect and microstructure changes.

Thermo-mechanical effects on TSVs, typically found in 3D ICs, were studied in conjunction with thermal cycling. Thermal cycling simulates what transpires in electronic chips during their lifetime. As an electronic device is used, it experiences temperature fluctuations due to energy dissipation. When electrical current flows through the interconnect to devices on a chip, it meets resistance from the material, which converts the current into heat from Joule heating. In general, not all of the electrons' energy is used to carry information in the interconnects. Instead, the energy is dissipated as different energy forms, such as light or heat. When the device is put to sleep or is not in use, it cools down, because the circuits are not pushing current. Over time these temperature fluctuations may cause the chips to fail. 3D ICs sport a higher level of density than traditional 2D ICs and thus are exposed to heat for longer intervals of time. Hence, thermo-mechanical reliability becomes an essential factor in these systems. Limited research has been conducted on thermally cycled Cu-TSVs, however, the cycling conditions used typically simulate the heating profiles utilized during the processing of these chips, with slow ramp rates and higher maximum temperatures, rather than in-use conditions [7, 8].

Thermal cycling is expected to induce more defects from the stress created by the mismatch in the coefficient of thermal expansion (CTE) between the Cu of the TSVs and the Si wafer. The voids may congregate, forming larger voids and resulting in larger amounts of signal loss, since voids act as scattering centers. Although some microstructural changes are expected in the Cu, such as grain coarsening, from the elevated temperature of thermal cycling, these changes may be minimal due to the fast cycling times. Furthermore, preferential grain orientation has not been found in Cu-TSVs [8, 9, 10, 11]. The lack of texture, or random granular orientation, impedes performance of these interconnects and creates local stresses within the copper from inter-granular anisotropy, causing void formation and, subsequently, signal loss.

#### **1.3 Thesis Scope**

The organization of this thesis is as follows. Chapter two gives an introduction by including the state-of-the-art research in this field. Chapter three describes the experimental procedure employed to complete this investigation. Chapters four and five highlight the results and discussion, respectively, of the

electrical loss, defect, and microstructure measurements. Lastly, the conclusions

and future work are enclosed in Chapter six.

## **1.4 References**

1. J. D. Meindl, 'Beyond Moore's Law: the interconnect era,' *Computing in Science & Engineering*, 5 [1] 20-24 (2003).

2. G. E. Moore, 'Cramming More Components Onto Integrated Circuits,' *Proceedings of the IEEE*, 86 [1] 82-85 (1998).

3. M. Bohr and K. Mistry, 'Intel's Revolutionary 22 nm Transistor Technology,' (2011).

4. J. A. Davis, R. Venkatesan, A. Kaloyeros, M. Beylansky, S. J. Souri, K. Banerjee, K. C. Saraswat, A. Rahman, R. Reif and J. D. Meindl, 'Interconnect limits on gigascale integration (GSI) in the 21st century,' *Proceedings of the IEEE*, 89 [3] 305-324 (2001).

5. G. Q. Zhang, M. Graef and F. van Roosmalen, 'The rationale and paradigm of "more than Moore",' *Electronic Components and Technology Conference, 2006. Proceedings. 56<sup>th</sup>* 7 (2006).

6. R. K. Cavin, P. Lugli and V. V. Zhirnov, 'Science and Engineering Beyond Moore's Law,' *Proceedings of the IEEE*, 100 [Special Centennial Issue] 1720-1749 (2012).

7. P. Kumar, I. Dutta and M. S. Bakir, 'Interfacial Effects During Thermal Cycling of Cu-Filled Through-Silicon Vias (TSV),' *Journal of Electronic Materials*, 41 [2] 322-335 (2012).

8. C. Okoro, R. Labie, K. Vanstreels, A. Franquet, M. Gonzalez, B. Vandevelde, E. Beyne, D. Vandepitte and B. Verlinden, 'Impact of the electrodeposition chemistry used for TSV filling on the microstructural and thermo-mechanical response of Cu,' *Journal of Materials Science*, 46 [11] 3868-3882 (2011).

9. A. Heryanto, W. N. Putra, A. Trigg, S. Gao, W. S. Kwon, F. X. Che, X. F. Ang, J. Wei, R. I Made, C. L. Gan and K. L. Pey, 'Effect of Copper TSV Annealing on Via Protrusion for TSV Wafer Fabrication,' *Journal of Electronic Materials*, 41 [9] 2533-2542 (2012).

10. H. Kadota, R. Kanno, M. Ito and J. Onuki, 'Texture and Grain Size Investigation in the Copper Plated Through-Silicon via for Three-Dimensional Chip Stacking Using Electron Backscattering Diffraction,' *Electrochemical and Solid-State Letters*, 14 [5] D48-D51 (2011).

11. C. Okoro, K. Vanstreels, R. Labie, O. Lühn, B. Vandevelde, B. Verlinden, and D.Vandepitte, 'Influence of annealing conditions on the mechanical and microstructural behavior of electroplated Cu-TSV,' *J Micromech Microengineering*, 20 [4] 045032 (2010).

# CHAPTER TWO

# INTRODUCTION

This chapter provides an introduction to the research presented in this thesis. The current state of art for 3D-IC devices and up-to-date studies of TSVs and their reliability issues, are discussed. Furthermore, the instruments used to characterize these reliability concerns and questions this work will answer, are included.

### 2.1 3D Stacking of Chips

The effort to maintain Moore's law has led to the development of other 3D technologies, each showcasing the progress of the semiconductor industry toward 3D ICs. Each are discussed here with contrast shown as to technology attributes. These include 3D system-in-packages, 3D wafer-level-packaging, and 3D integrated circuits.

#### 2.1.1 3D System-in-Packages

3D System-in-Package (SiP) designs consist of several devices stacked in one package. SiPs usually utilize a silicon interposer to connect multiple chips. These connections are generally made using wirebonds. Wirebonds are long interconnects as shown in Figure 2.1. The use of wirebonds is the limiting factor in SiPs due to their length and amount of space taken up. There is still a large increase in density for these systems compared to systems-on-chips (SoC), however the wirebonding still occupies a large area compared to other 3D systems. Furthermore, this technology is currently the most well developed amongst 3D stacked chips [1].

Figure 2.1: A SiP which utilizes wire bonding, taken from reference [2].

#### 2.1.2 3D Wafer-Level-Packaging

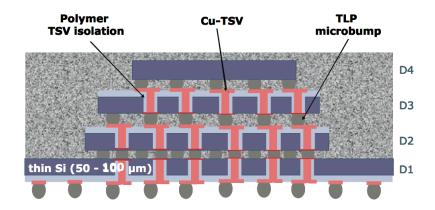

3D Wafer-Level-Packaging (WLP) is a more dense package than the SiP, because of their interconnecting methods. Some WLPs contain through-silicon vias (TSV), or vertical interconnects that are perpendicular to the surfaces of the chip. TSVs need less space to operate and provide a shorter pathway for current, increasing the performance of the chips. At the end of these TSVs are bondpads that are used for flip chip bumping. Flip chip bumping is the application of solder bumps on the bottom of a chip to allow them to communicate when stacked. Bumps and microbumps, like TSVs, make the WLP more densely packed then SiPs [1]. Figure 2.2 shows a cross section of a WLP with TSVs and microbumps. While SiPs are constructed after dicing, the stacking of chips in WLPs precedes the dicing of the wafers [3].

Figure 2.2: Illustration of an Imec WLP, which uses microbumps, taken from reference [4].

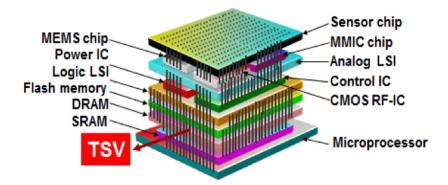

#### 2.1.3 3D Integrated Circuits

3D Integrated Circuits (IC) presents superior density to SiP and WLP stacked chip technologies. In these systems, the use of wirebonds has been abandoned and replaced fully with TSVs. While all the advantages of 3D ICs will be presented in the next section, the use of TSVs brings the chips closer together and makes the stacked chips more highly integrated. Design is crucial for these ICs because everything must be integrated together. 3D ICs allow one chip to do the function of many, all the while, reducing the form for the system. It also shortens the interconnect path length and minimizes power losses via Joule heating. An example of a 3D IC is found in Figure 2.3.

Figure 2.3: Breakdown of a 3D IC, taken from reference [5].

#### 2.2 Benefits of 3D IC

The semiconductor industry is always striving to reduce chip volume. 3D stacking of chips allows for increases in density of the system and thus a smaller form factor. Such designs take full advantage of the silicon wafer, having a silicon efficiency, defined as the ratio of the available area on the silicon over the total area of the substrate, of over 100% compared to 2D systems [6]. Thinning of the wafers allows these systems to further achieve a greater density. These compact chips easily fit into mobile devices, such as cell phones and tablets, without reducing the number of components on the chips. Also, since interconnects can be utilized in another dimension, more transistors and other devices can be added to the chips because less surface area is occupied.

Performance is shown to increase in these 3D ICs compared to their 2D counterparts [6-11]. This is due to the reduced length of interconnects. With single chip systems, the interconnects are only limited to two dimensions and

thus the signal must travel further to reach its destination. 3D ICs have much shorter vertical interconnects, reducing the time it takes for the signal to be transmitted. Davis *et.al.* have suggested that about a 65% delay drop could be seen in 3D ICs over their 2D equivalencies [7], while Al-Sarawi *et. al.* suggests a 30% decrease in delay due to lower parasitic capacitance [6]. This also leads to a decrease in signal scattering, which in turn means up to 30% less power is required to drive the system [6]. Furthermore, interconnect density is increased and thus the signal throughput is much greater.

Heterogeneous integration allows for a variety of chips to be stacked, as illustrated by Figure 2.3. Incompatibility is no longer an issue as different wafers and materials can be stacked to form 3D ICs. The most advanced chips and devices can all be packaged into one seamless system, using this 3D technology [11].

#### 2.3 Challenges of 3D Integrated Circuits (ICs)

Complexity is a major issue for chip designers and architects [6]. Vertical integration of chips means that professionals need to rethink the layouts of these chips for optimal performance. This adds more opportunity for flaws in the design and structures. Since most components rely on each other, given the increase in integration, one component failure could lead to a decrease in overall

chip performance or entire chip breakdown. Reparability is limited when everything is that tightly integrated.

The increased density of these chips makes heat dissipation a major concern [11]. Temperature excursions can affect the system greatly and has the potential to change many material properties, as the involved multi-materials create thermal expansion mismatches. This results in added stress to the system which as will be discussed in subsequent chapters, can cause many different types of failure, from delamination of the substrate to via cracking.

Since 3D ICs are a relatively new technology, many unknowns are still being tested. The manufacturability and optimization of the design and materials of these 3D structures are in question. Stacking these chips will require precise wafer thinning and accurate alignment methods. It is expected that perfecting the structure, reliability, and manufacturability of these circuits will take many more years.

#### 2.4 TSV Structure

While the shape of TSVs has been studied extensively, this thesis will only focus on tapered cylindrically shaped TSVs. The semiconductor industry is always looking to minimize the surface area of these structures. Electrical properties have been shown to degrade with increasing TSV height to diameter aspect ratios [12]. Larger aspect ratios show increased probability of void and

other defect formation during fabrication. However, larger aspect ratios are becoming reality due to advanced filling techniques, which will be discussed later in this chapter. It is speculated that by the year 2015 the maximum aspect ratio will double from the current 10:1 to 20:1 and the minimum global TSV diameters will be cut in half from 4  $\mu$ m to 2  $\mu$ m, while height remains unchanged. Due to the size changes, the maximum pitch is also predicted to reach 4  $\mu$ m from its present 8  $\mu$ m by 2015 [13]. Smaller pitch means more densely packed arrays of TSVs that occupy less chip area.

TSVs are made up of several layers, each serving its own purpose. Figure 2.4 shows an optical micrograph of the structure for a blind TSV such as that examined in the present study. A typical TSV is conceptually similar in structure to an electrical transmission line; it contains three different layers, the isolation liner, barrier layer, and a conduction layer. The outermost layer, the isolation liner, is in contact with the silicon substrate and prevents cross talk between adjacent vias as well as loss of current through sneak paths into the substrate. Sandwiched between the isolation liner and conduction layer is the barrier layer. There are two critical requirements of such a barrier layer: (1) it must be a good adhesive to the isolation layer and the innermost conductive layer, and (2) the barrier layer must prevent diffusion between the conduction and Si substrate. The adhesive attributes of the barrier layer aids in the filling process, allowing the TSV to be filled while maintaining its shape. The

conduction layer is the inner most layer of TSVs. It consists of a conductive material, which provides a path for electric current to flow. Diffusion from the conduction layer into the isolation layer must be prevented, as such contamination will adversely affect the performance of front-end-of-line (FEOL) devices located in the Si matrix. As can be seen in the micrograph in Figure 2.4 taken from reference [14], the metallic conductive fill material of the via, is not perfect in its cross-sectional uniformity as it contains defects and other non-uniformities, directly related to the processing methodology used in its fabrication. These attributes and their possible influence on RF signal integrity and changes in microstructure that can be induced with thermal cycling, are discussed in subsequent sections.

Figure 2.4: Illustration of the three layers of typical TSV, insulator, diffusion barrier, and conductive layer, taken from reference [14].

## 2.5 Integrated Circuit (IC) Materials

#### 2.5.1 Wafer Materials

High purity semiconductors wafer substrates are the backbone of IC structures. Semiconductors are utilized because their properties are readily manipulated and controlled through doping. Silicon (Si) is the most common material for this application; although Germanium (Ge) and gallium arsenide (GaAs) are relatively expensive alternatives. Another qualification for semiconductor substrates is homogeneity. Maintaining property consistency throughout the entire wafer is crucial for the prevention of failure and to minimize variability across the wafer. It is for this reason that chips are made from monocrystalline (single crystal) substrates instead of polycrystalline materials, which introduce defects in the form of grain boundaries.

#### 2.5.2 TSV Filling Materials

Silicon oxide (SiO<sub>x</sub>) derived from tetraethyl orthosilicate (TEOS) precursors is primarily used as the isolation liner for the TSV. The amorphous nature and poor electrical conductivity of this material impedes propagation of current. The silicon oxide's lack of free electrons makes this material a good insulator. Tabased barrier layers are commonly used with Cu interconnects. Ta compounds used are generally inert to Cu as well as Si. Thus, it resists diffusion between itself and the Cu as well as the isolation liner [15].

The conductive layer of the TSV is perhaps the most important material. Its characteristics control the current flow. Many materials have been exploited because of their good conductive properties, including aluminum (AI), tungsten (W), and polycrystalline silicon (Poly-Si), but nothing matches copper's (Cu) low resistivity and cost. Due to its lower resistivity and superior electro-migration resistance, Cu replaced AI as the conventional material of choice for interconnects [16].

# 2.6 TSV Processing

The TSV processing scheme is characterized by the chronology in which the TSVs are integrated into chip fabrication. There are three categories for TSV processing. Via-first, is the fabrication of the TSVs at the beginning of the chip production cycle, before the integration of front-end-of-line (FEOL) devices, such as transistors. Via-last processing includes the creation of vias toward the end of the chip production steps, after the back-end-of-line (BEOL), or planar interconnects, have been deposited. In via middle production, TSVs are constructed between the integration of FEOL devices and the BEOL interconnects. Currently, via middle processing is the industry standard. While via middle processing forces the TSVs to undergo heat treatments from the BEOL addition, via first requires more extensive heating from the FEOL and via

last fabrication creates design problems from the many layers of devices and materials already added to the wafers.

Integrating the fabrication of TSVs in the process flow of 3D ICs requires many steps. The visual representation of via middle manufacturing scheme, shown in Figure 2.5, gives a hint of the complexity associated with TSV First, FEOL devices such as transistors, capacitors, and other fabrication. devices are implanted on the chip. Afterwards, a deep reactive ion etching (DRIE) process, which utilizes ion bombardment, is used to create high aspect ratio via trenches in the silicon substrate. Next, the TEOS isolation liner is deposited using chemical vapor deposition (CVD). A physical vapor deposition (PVD) process, is then employed for deposition of the barrier layer and copper seed laver. The Cu seed layer enables the impending electrochemically deposited (ECD) copper to have optimal microstructure. A chemical mechanical planarization process rids the surface of excess material from the deposition processes and leaves the surface flat for the BEOL. The BEOL, consisting of layers of planar interconnects and dielectric insulators, are the last features positioned onto the wafer, before the chip is flipped, thinned, and aligned to be stacked. Integrating the BEOL and stacking the chips usually require thermal processes, 350 °C for BEOL [17] and up to 400 °C for chip bonding [18].

Figure 2.5: Process flow of via middle filling. a.) FEOL is placed on chip; b.)DRIE cuts via holes in the Si chip; c.) CVD of isolation layer; d.) PVD of barrier layer; e.) deposition of Cu seed layer and fill using PVD and ECD respectively; f.) CMP of surface; g.) addition of BEOL; h.) flipping of the chip in preparation for final steps; i.) alignment and stacking of multiple chips.

# 2.7 Thermo-Mechanical Reliability of TSVs

# 2.7.1 Thermo-Mechanical Stresses

The Cu-TSVs and Si matrix have very different material properties as made evident by Table 2.1. Due to the mismatch in coefficient of thermal expansion (CTE), 16.7 ppm/°C for Cu and 2.3 ppm/°C for Si, the Cu expands much faster than the surrounding Si substrate when heated. This creates stresses in the system. Chip processing, joule heating, and environmental conditions constitute for heat changes in 3D ICs. These temperature fluctuations generate thermomechanical reliability concerns. Non-destructive methods, such as Raman spectroscopy and finite element analysis (FEA), have been utilized to measure and estimate stresses in the Si surrounding the TSVs. At room temperature the Si regions nearest to copper TSVs were found to be under compression, however, when moving further from the TSVs, there are tensile stresses in the Si, before they dissipate far from the TSVs [19-24]. This stress profile is seen in Figure 2.6. These thermo-mechanical stresses also cause TSV reliability concerns, such as out of plane expansions, defect formation and growth, and microstructural changes, all of which are discussed in this section.

| Material         | Young's Modulus<br>[GPa] | Poisson<br>Ratio | Coefficient of Thermal Expansion<br>(CTE) [ppm/°C] |

|------------------|--------------------------|------------------|----------------------------------------------------|

| Silicon          | 169                      | 0.26             | 2.3                                                |

| SiO <sub>2</sub> | 75                       | 0.17             | 0.5                                                |

| Copper           | 117                      | 0.3              | 16.7                                               |

Table 2.1: Material properties of Si and Cu, data taken from reference [25].

Figure 2.6: Stress map of Silicon substrate, measured by micro-raman, taken from reference [23].

# 2.7.2 Out of Plane Expansion

Out of plane expansion of TSVs are observed as these thermomechanical stresses build up. The Cu is constrained by the surrounding Si substrate so the only expansion direction for the Cu is axially, out of the trench. There are two possible mechanisms proposed for this protrusion. The temperature increase could be pushing the Cu past its elastic limit and causing plastic deformation to occur [26]. Kumar *et.al.* suggested that another possible mechanism for copper protrusions is diffusional sliding, where the copper atoms want to minimize stresses and move out of the compressive stress field found in the copper [27]. The amount of expansion has been found to increase linearly with heat treatment temperature [26]. Furthermore, increasing the amount of thermal cycling, slows down the rate of expansion [27]. Deformation and delamination of the BEOL can result from this copper TSV expansion. This is illustrated in Figure 2.7. However, this problem can be alleviated by heating immediately following deposition and chemical mechanical polishing (CMP) to flatten the surface. It has been found that by heat treating these Cu-TSVs, less expansion will occur upon reheating during processing or use [26,28,29].

Figure 2.7: Cross-section of a TSV, which has undergone out-of-plane expansion, leading to deformation of the BEOL. A dashed line has been added for planar reference, taken from reference [29].

## 2.7.3 TSV Defects

# 2.7.3.1 Voids

Voids are a defect in Cu-TSVs, which can be detrimental to electrical stability and overall reliability. They are characterized as local regions in a TSV, which are not occupied by the Cu. Their shapes and sizes vary greatly. Seams, as illustrated in Figure 2.8a, accommodate vertical areas along the center of TSVs. On the other hand, micro-voids are generally small spherical voids that are dispersed throughout the TSV, such as those in Figure 2.8c. Electrical

properties, such as resistance and capacitance, are sensitive to voids. Voids can serve as a scattering center for electrical current, causing high losses in the TSVs and even failure if the voids become too big.

Figure 2.8: Different void types found from flawed processing. A.) seam void; b.) void at bottom of a incompletely filled TSV; c.) microvoids.

Voids originate in one of two fashions, most commonly through processing or stress. Pre-existing voids in TSVs are formed due to inadequate processing procedures. Filling techniques are a major cause of voids in high aspect ratio TSVs. When TSV trenches are filled with conductive material from the sidewalls, air easily becomes encapsulated. At the end of deposition, the result is usually a seam of air trapped in the center of the TSV. Since high aspect ratio TSVs are tall and narrow, they are more prone to these defects. The sequence in Figure 2.9 demonstrates this phenomenon. Deposition chemistries and electrochemical deposition (ECD) parameters have also been found to greatly affect void formation upon filling [30-34]. Probably the most notable development in filling processes is bottom-up ECD. Instead of filling from the sidewalls, the conductive material is deposited onto the bottom surface of the TSV and filled upwards, greatly reducing the probability of trapping air. Significant reduction in void formation is found when utilizing this filling method [35-37].

Figure 2.9: The process flow for filling TSVs, revealing how bottom up filling creates voidfree TSVs while sidewall filling can produce seams.

Unlike pre-existing, process-induced voids, stress-induced voids nucleate as TSVs are introduced to stress. As mentioned previously, most stresses in TSVs are caused by CTE mismatch between the copper interconnects and silicon matrix when heating occurs. This, along with differences in grain orientation, give rise to stress gradients from the highly anisotropic copper grain growth. As a result, voids form along grain boundaries to relieve stresses [30,38]. Coble creep, or diffusion along grain boundaries, has been identified as the mechanism for void formation [30].

Similar to void formation, void growth also occurs in high purity copper due

to grain boundary diffusion. Vacancy diffusion along the grain boundaries can cause microvoids, which are formed in adjacent locations, to coalesce during heating. Furthermore, void growth has been shown to occur almost exclusively along high angle grain boundaries [39]. X-ray imaging was used by Kong et al. to confirm that increasing holding temperatures from 225 °C to 300 °C, increased the sizes of voids in Cu-TSVs [40].

## 2.7.3.2 Barrier Layer and Isolation Liner Defects

Interfaces result from the multiple layered TSVs, including the conduction/barrier layer interface, barrier layer/isolation liner interface, and the isolation liner/substrate interface. These interfaces are vulnerable areas in the structure that are suseptible to defects and create reliability concerns. Improper etching of the TSV trenches can form scallops, or uneven sidewalls, like those shown in Figure 2.10. Once the barrier layer and isolation liner are deposited, they are prone to defects like cracking and thinning. Defects in the isolation liner give the current a pathway out of the TSV, causing leakage. Smooth isolation liners have proven to be much more thermally stable. Nakamura *et al.* concluded that increasing heat treatment temperature for scalloped TSVs increases the amount of current leakage drastically, compared to TSVs with even sidewalls [41].

Figure 2.10: Scalloped Ta barrier layer, taken from reference [20].

Like the isolation liner, the barrier layer must also be thermally stable. Material choice and deposition thickness are important as this layer prevents diffusion of the copper into the substrate. Studies have found tantalum, (Ta) to be more thermally stable than titanium (Ti) barrier layers. Therefore, smaller Ta thicknesses are needed to fulfill its duty compared to Ti [42]. In addition, the barrier layer can dictate grain sizes of the electrodeposited copper layer. Ta barrier layers were also found to be superior compared to Ti based layers in that Ta promotes seed layers of strong orientations. Strong grain oriented Cu seed layers translate to smoother seed layers and larger grain sizes [43]. The microstructure of the copper has a large impact on TSV reliability, as will be discussed in further detail in the next section as well as throughout the rest of this proposal.

### 2.7.4 Microstructure

Microstructure can affect the electrical properties of a metal. Since grain boundaries are defects that resist the flow of electrons, electrical properties are inherently affected by grain size. As grain size increases, the amount of grain boundaries generally decreases. Since electrons don't have to flow through as many of these defect areas, this results in less signal scattering and loss, decreasing the electrical resistance.

Heat treatment of copper TSVs have revealed much about the microstructural evolution of these structures. The middle and bottom of blind TSVs tend to have larger grains than the top region [38,44,45]. These results are postulated to be related to an excess of additives from copper plating at the top of the TSVs [44]. Upon heat treatment, average grain sizes have been found to increase with holding temperatures above 300 °C. Little growth is seen at lower temperatures [26,38,45]. As in all systems, enough energy needs to be provided to cause the movement of grain boundaries, leading to grain growth.

To our knowledge, microstructural effects from long term thermal cycling have not been studied extensively for these structures. Okoro *et al.* cycled Cu-TSVs from room temperature to 420 °C to replicate chip processing conditions [30]. Thermal cycling was found to increase Cu grain sizes in the TSVs. Furthermore, the electroplating chemistry may have affected the type of grain growth (abnormal and normal) that occurred [30]. Although these microstructural

changes were observed in the TSVs, a small number of cycles were performed and slow heating/cooling rates were used. No studies were found in the literature that observes the microstructural evolution of Cu-TSVs over many thermal cycles. Additionally, heat treatments have been shown to have little to no effect on the Cu grain orientation. Preferential grain orientation has not been found in Cu-TSVs due to thermal cycling or isothermal heat treatments [26, 30, 44, 45].

Although there are not many studies conducted on long term cycling of TSVs, Joule heating has been applied to small structures, such as Cu thin films, to examine thermal fatigue. Alternating current (AC) is passed through thin metal films inducing Joule heating, which results in cycling due to the fluctuations in current applied. This is different from the blanket thermal cycling performed in most TSV studies, where the entire sample is heated instead of local heating. If the power is held constant, the frequency of the current dictates the maximum temperature of cycling, where lower temperature ranges were applied at higher frequencies [46]. Increasing thermal cycling causes more defects to build up until failure occurs and current can no longer pass through the film. Also, increasing the temperature range of cycling also increased the likelihood of failure at an earlier number of cycles [46]. As mentioned in earlier sections, the mismatch in CTE between the Si substrate and the Cu films results in stresses that are detrimental to the material's reliability. Wang *et.al.* found that the thickness of the films widely impacts the mechanisms for defect formation in the Cu films [47].

Below 0.1  $\mu$ m thick films, cracks initiate and propagate along grain and twin boundaries, however, between 0.1  $\mu$ m and 1  $\mu$ m film thicknesses, cracks form proceeding extrusions within the grains. The extrusions occur sequentially along slip planes until the stresses eventually form cracks at the intrusions of the multimaterial interface that propagate through the slip planes and lastly across these extrusions. Cu film thicknesses above 1  $\mu$ m were shown to typically contain an insignificant amount of cracks compared to the smaller film thicknesses, as extrusions were found to make up a majority of the deformation in these films [47]. Thus, the mechanisms for defect formation and growth become reliant on grain boundary diffusion rather than slip plane gliding as film thicknesses are decreased and the Cu consists of smaller average grain sizes [46]. Grain growth was also found to occur from cyclic Joule heating in these Cu thin films [46,48]. Lastly, defects were more susceptible in certain Cu grain characteristics, such as larger grains and the <001> orientation [48].

# 2.8 Real World Conditions and Potential Impact on TSVs

While consumer electronic components are typically expected to operate below 100 °C, extreme applications, such as military and aerospace, may require more extreme, higher threshold conditions. Consumer electronics can undergo up to 10 cycles a day if extensively used and are designed to last up to 10 years. On the other hand, specific applications can see up to 14 cycles per day with an

expected lifetime of up to 25 years [49]. Powering on and off devices as well as using these devices for overbearing tasks are the major contributors to the thermal cycling in electronics. Environmental changes also cause temperature fluctuations for these chips. This thesis will simulate the thermal cycling of Cu-TSVs and analyze the effects it has on reliability.

# 2.9 TSV analysis – Common Analytical Techniques

To examine the various thermo-mechanical reliability concerns of Cu-TSVs many analytical tools can be utilized. Some of the following analysis tools were mentioned in section 2.7, but all present different ways of viewing the multifaceted problems TSVs face. Some of these tools will be employed in the present study and will be discussed in more detail in Chapter 3 along with the specifics of their use and specific experimental and sample conditions.

- Finite Element Analysis (FEA): Is also known as finite element modeling (FEM). These computer simulations provide a preexperimental analysis of the stresses seen in the three layers of the TSVs and surrounding substrate.

- Raman Spectroscopy: A non-destructive technique, which can determine relative stresses on the surface of the TSV-enveloping substrate through atomic interaction.

- 3. Nano-Indentation: C. Okoro *et al.* used nano-indentation to deduce the elastic modulus and hardness values of the electroplated Cu with thermal treatments [30].

- Focused Ion Beam (FIB): The FIB is a high precision ion beam used to cross-section and image the TSVs for defect analysis.

- 5. Scanning Electron Microscope (SEM): SEM is utilized for void and other defect analysis of the TSV layers.

- 6. X-Ray Microscope: This instrument allows for a non-destructive means for examining void size and growth within the TSVs [40].

- Electron Backscattering Diffraction (EBSD): EBSD can be conducted to investigate microstructural changes, such as grain size and grain orientation, of the Cu-TSVs.

- White Light Interferometry (WLI): Like atomic force microscopy (AFM), WLI can be applied to detect the magnitude of Cu protrusion after heat treatments.

# 2.10 Focus of This Work

This thesis will strive to answer the following questions:

- With the tools available, can a sample preparation method be developed to monitor variations of the following TSV characteristics?

- a. Assessment of TSV process uniformity/variation

- i. Within wafer uniformity (vias on the same wafer)

- ii. Wafer-to-wafer uniformity (vias on different wafers processed using the same fabrication method)

- b. Void and other defect configurations

- c. Defects and uniformity of the barrier layer and isolation liner

- d. Grain sizes

- e. Grain orientations

- 2. Are thermal cycling induced defects forming and evolving in industry prepared TSVs?

- 3. Is the RF performance hindered by thermal cycling parameters such as:

- a. Number of cycles

- b. Maximum temperature of cycling

- c. Cycling samples with or without pre-existing voids

- 4. Are one or more thermal cycling conditions altering the following internal

TSV properties?

- a. Void and other defect size and probability

- b. Microstructure

- 5. Can links be made between shifts in the TSV signal loss and changes found within the TSVs?

6. What conclusions can be drawn from the results of these analyses, which will aid in understanding the relationship between processing and performance characteristics of TSVs.

# 2.11 References

1. B. Vandevelde, C. Okoro, M. Gonzalez, B. Swinnen and E. Beyne, 'Thermomechanics of 3D-wafer level and 3D stacked IC packaging technologies,' *Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Micro-Systems, 2008. EuroSimE 2008. International Conference on* 1-7 (2008).

2. P. Rickert and W. Krenik, 'Cell phone integration: SiP, SoC, and PoP,' *Design & Test of Computers, IEEE*, 23 [3] 188-195 (2006).

3. J. Yannou, 'SiP and WLP-CSP Trends: State-of-the-art and future trends,' *Electronics System-Integration Technology Conference, 2008.* ESTC 2008. 2nd 3-6 (2008).

4. D. S. Tezcan, F. Duval, H. Philipsen, O. Luhn, P. Soussan and B. Swinnen, 'ScalableVia with polymer deep trench isolation for 3D wafer level packaging,' *Electronic Components and Technology Conference, 2009. ECTC 2009. 59th* 1159-1164 (2009).

5. M. Koyanagi, '3D integration technology and reliability,' *Reliability Physics Symposium (IRPS), 2011 IEEE International* 3F.1.1-3F.1.7 (2011).

6. S. F. Al-Sarawi, D. Abbott and P. D. Franzon, 'A review of 3-D packaging technology,' *Components, Packaging, and Manufacturing Technology, Part B: Advanced Packaging, IEEE Transactions on*, 21 [1] 2-14 (1998).

7. J. A. Davis, R. Venkatesan, A. Kaloyeros, M. Beylansky, S. J. Souri, K. Banerjee, K. C. Saraswat, A. Rahman, R. Reif and J. D. Meindl, 'Interconnect limits on gigascale integration (GSI) in the 21st century,' *Proceedings of the IEEE*, 89 [3] 305-324 (2001).

8. J. H. Lau, 'Overview and outlook of through-silicon via (TSV) and 3D integrations,' *Microelectronics International*, 28 [2] 8-22 (2011).

9. K. Nomura, K. Abe, S. Fujita, Y. Kurosawa and A. Kageshima, 'Performance analysis of 3D-IC for multi-core processors in sub-65nm CMOS technologies,' *Circuits and Systems (ISCAS), Proceedings of 2010 IEEE International Symposium on* 2876-2879 (2010).

10. S. S. Wong and A. El Gamal, 'The prospect of 3D-IC,' *Custom Integrated Circuits Conference, 2009. CICC '09. IEEE* 445-448 (2009).

11. A. W. Topol, D. C. L. Tulipe, L. Shi, D. J. Frank, K. Bernstein, S. E. Steen, A. Kumar, G. U. Singco, A. M. Young, K. W. Guarini and M. leong, 'Threedimensional integrated circuits,' *IBM Journal of Research and Development*, 50 [4.5] 491-506 (2006).

12. Z. Xu and J. Lu, 'High-Speed Design and Broadband Modeling of Through-Strata-Vias (TSVs) in 3D Integration,' *Components, Packaging and Manufacturing Technology, IEEE Transactions on*, 1 [2] 154-162 (2011).

13. 'International Technology Roadmap for Semiconductors (ITRS), Interconnect,' (2011).

14. M. G. Farooq *et al*, '3D Copper TSV Integration, Testing and Reliability,' *International Electron Devices Meeting (IEDM)*, 7.1.1 – 7.1.4 (2011).

15. B. Li, T. D. Sullivan, T. C. Lee and D. Badami, 'Reliability challenges for copper interconnects,' *Microelectronics Reliability*, 44 [3] 365-380 (2004).

16. A. Pratt, 'Overview of the Use of Copper Interconnects in the Semiconductor Industry,' (2004).

17. M. Motoyoshi, 'Through-Silicon Via (TSV),' *Proceedings of the IEEE*, 97 [1] 43-48 (2009).

18. C. Ko and K. Chen, 'Low temperature bonding technology for 3D integration,' *Microelectronics Reliability*, 52 [2] 302-311 (2012).

19. C. Okoro, Y. Yang, B. Vandevelde, B. Swinnen, D. Vandepitte, B. Verlinden and I. de Wolf, 'Extraction of the Appropriate Material Property for Realistic Modeling of Through-Silicon-Vias using  $\mu$ -Raman Spectroscopy,' *Interconnect Technology Conference, 2008. IITC 2008. International* 16-18 (2008).

20. T. Chidambaram, C. McDonough, R. Geer and Wei Wang, 'TSV Stress Testing and Modeling for 3D IC Applications,' *Physical and Failure Analysis of Integrated Circuits, 2009. IPFA 2009. 16th IEEE International Symposium on the* 727-730 (2009).

21. N Ranganathan and K Prasad and N Balasubramanian and,K.L.Pey, 'A study of thermo-mechanical stress and its impact on through-silicon vias,' *J Micromech Microengineering*, 18 [7] 075018 (2008).

22. B. Backes, C. McDonough, L. Smith, W. Wang and R. Geer, 'Effects of Copper Plasticity on the Induction of Stress in Silicon from Copper Through-Silicon Vias (TSVs) for 3D Integrated Circuits,' *Journal of Electronic Testing*, 28 [1] 53-62 (2012).

23. W. S. Kwon, D. T. Alastair, K. H. Teo, S. Gao, T. Ueda, T. Ishigaki, K. T. Kang and W. S. Yoo, 'Stress evolution in surrounding silicon of Cu-filled throughsilicon via undergoing thermal annealing by multiwavelength micro-Raman spectroscopy,' *Applied Physics Letters*, 98 [23] 232106-232106-3 (2011).

24. C. McDonough, B. Backes, Wei Wang and R. E. Geer, 'Thermal and spatial profiling of TSV-induced stress in 3DICs,' *Reliability Physics Symposium (IRPS), 2011 IEEE International* 5D.2.1-5D.2.6 (2011).

25. C. Okoro, M. Gonzalez, B. Vandevelde, B. Swinnen, G. Eneman, P. Verheyen, E. Beyne and D. Vandepitte, 'Prediction of the Influence of Induced Stresses in Silicon on CMOS Performance in a Cu-Through-Via Interconnect Technology,' *Thermal, Mechanical and Multi-Physics Simulation Experiments in Microelectronics and Micro-Systems, 2007. EuroSime 2007. International Conference on* 1-7 (2007).

26. A. Heryanto, W. N. Putra, A. Trigg, S. Gao, W. S. Kwon, F. X. Che, X. F. Ang, J. Wei, R. I Made, C. L. Gan and K. L. Pey, 'Effect of Copper TSV Annealing on Via Protrusion for TSV Wafer Fabrication,' *Journal of Electronic Materials*, 41 [9] 2533-2542 (2012).

27. P. Kumar, I. Dutta and M. S. Bakir, 'Interfacial Effects During Thermal Cycling of Cu-Filled Through-Silicon Vias (TSV),' *Journal of Electronic Materials*, 41 [2] 322-335 (2012).

28. I. De Wolf, K. Croes, O. Varela Pedreira, R. Labie, A. Redolfi, M. Van De Peer, K. Vanstreels, C. Okoro, B. Vandevelde and E. Beyne, 'Cu pumping in TSVs: Effect of pre-CMP thermal budget,' *Microelectronics Reliability*, 51 [9–11] 1856-1859 (2011).

29. C. Okoro, C. Huyghebaert, J. Van Olmen, R. Labie, K. Lambrinou, B. Vandevelde, E. Beyne and D. Vandepitte, 'Elimination Of The Axial Deformation Problem Of Cu-TSV In 3D Integration,' *AIP Conference Proceedings*, 1300 [1] 214-220 (2010).

30. C. Okoro, R. Labie, K. Vanstreels, A. Franquet, M. Gonzalez, B. Vandevelde, E. Beyne, D. Vandepitte and B. Verlinden, 'Impact of the electrodeposition chemistry used for TSV filling on the microstructural and thermo-mechanical response of Cu,' *Journal of Materials Science*, 46 [11] 3868-3882 (2011).

31. K. Kondo, Y. Suzuki, T. Saito, N. Okamoto and M. Takauchi, 'High Speed Through Silicon Via Filling by Copper Electrodeposition,' *Electrochemical and Solid-State Letters*, 13 [5] D26-D28 (2010).

32. Moongon Jung, J. Mitra, D. Z. Pan and Sung Kyu Lim, 'TSV Stress-Aware Full-Chip Mechanical Reliability Analysis and Optimization for 3-D IC,' *Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on*, 31 [8] 1194-1207 (2012).

33. Sang-Soo Noh, Eun-Hey Choi, Yong-Hyuk Lee, Hyun-jin Ju, Sa-Kyun Rha, Boung-ju Lee, Dong-Kyu Kim and Youn-Seoung Lee, 'Optimization of Cu electrodeposition parameters for Through Silicon Via (TSV),' *Physical and Failure Analysis of Integrated Circuits (IPFA), 2011 18th IEEE International Symposium on the* 1-4 (2011).

34. Myung-Won Jung, Young-Sik Song, Tae-Hong Yim and Jae-Ho Lee, 'Evaluation of additives and current mode on copper via filling,' *Electronic Components and Technology Conference (ECTC), 2011 IEEE 61st* 1908-1912 (2011).

35. T. P. Moffat and D. Josell, 'Extreme Bottom-Up Superfilling of Through-Silicon-Vias by Damascene Processing: Suppressor Disruption, Positive Feedback and Turing Patterns,' *Journal of The Electrochemical Society*, 159 [4] D208-D216 (2012). 36. M. Saadaoui, H. van Zeijl, W. H. A. Wien, H. T. M. Pham, C. Kwakernaak, H. C. M. Knoops, W. M. M. Erwin Kessels, R. M. C. M. van de Sanden, F. C. Voogt, F. Roozeboom and P. M. Sarro, 'Enhancing the Wettability of High Aspect-Ratio Through-Silicon Vias Lined With LPCVD Silicon Nitride or PE-ALD Titanium Nitride for Void-Free Bottom-Up Copper Electroplating,' *Components, Packaging and Manufacturing Technology, IEEE Transactions on*, 1 [11] 1728-1738 (2011).

37. C. Song, Z. Wang and L. Liu, 'Bottom-up copper electroplating using transfer wafers for fabrication of high aspect-ratio through-silicon-vias,' *Microelectronic Engineering*, 87 [3] 510-513 (2010).

38. H. Shin, B. Kim, J. Kim, S. Hwang, A. Budiman, H. Son, K. Byun, N. Tamura, M. Kunz, D. Kim and Y. Joo, 'Microstructure Evolution and Defect Formation in Cu Through-Silicon Vias (TSVs) During Thermal Annealing,' *Journal of Electronic Materials*, 41 [4] 712-719 (2012).

39. R. Page and J. R. Weertman, 'HVEM observations of grain boundary voids in high purity copper,' *Acta Metallurgica*, 29 [3] 527-535 (1981).