# Clemson University TigerPrints

All Theses

Theses

12-2007

# Fabrication, Electrical Characterization, and Annealing of Al/, Cu/, and Au/4H-SiC Schottky Diodes

Nikhil Karkhanis *Clemson University*, nkarkha@clemson.edu

Follow this and additional works at: https://tigerprints.clemson.edu/all\_theses Part of the <u>Electrical and Computer Engineering Commons</u>

**Recommended** Citation

Karkhanis, Nikhil, "Fabrication, Electrical Characterization, and Annealing of Al/, Cu/, and Au/4H-SiC Schottky Diodes" (2007). *All Theses*. 280. https://tigerprints.clemson.edu/all\_theses/280

This Thesis is brought to you for free and open access by the Theses at TigerPrints. It has been accepted for inclusion in All Theses by an authorized administrator of TigerPrints. For more information, please contact kokeefe@clemson.edu.

# FABRICATION, ELECTRICAL CHARACTERIZATION AND ANNEALING OF AL/, CU/, AND AU/4H-SIC SCHOTTKY DIODES

A Thesis Presented to the Graduate School of Clemson University

In Partial Fulfillment of the Requirements for the Degree Master of Science Electrical Engineering

> by Nikhil Karkhanis December 2007

Accepted by: William R. Harrell, Committee Chair Kelvin F. Poole Michael A. Bridgwood

#### ABSTRACT

Schottky diodes were fabricated on n-type 4H-SiC with Nickel ohmic contacts and Aluminum, Copper, and Gold Schottky contacts. An improved and revised fabrication process was developed in the course of this research project. The Schottky diodes were electrically characterized using I-V and C-V measurements to extract electrical parameters which include Schottky barrier height, ideality factor, the diode series resistance, and substrate doping density. Al/4H-SiC and Au/4H-SiC were annealed at 600°C and 500°C respectively to improve the Schottky parameters. Schottky barrier height was raised and the ideality factor was reduced in both cases. Significant improvement was observed in the ideality factor of Al/4H-SiC diodes. XPS was performed on Al/4H-SiC samples to investigate the effects of annealing at the Aluminum-SiC interface. Analysis of the XPS results showed traces of Aluminum-Silicon bonding at the interface. The change in the Schottky parameters is attributed to this phenomenon. The electrical characterization of Au/4H-SiC showed that the devices had a very low ideality factor of 1.1 and represented some of the best results obtained in our research lab. The thesis establishes the effect of annealing on Schottky diodes and presents some of the very few surface analysis results performed on Al/4H-SiC.

# DEDICATION

I would like to dedicate this thesis to my parents for their continuous support and faith in me. It is also dedicated to my brother for all the advice and aid he has provided.

#### **ACKNOWLDEGEMENTS**

I would like to thank my advisor Dr. William R. Harrell for all his help and contribution throughout the duration of my research. This thesis would not have been possible without his direction and guidance. I would also like to thank Dr. Jim Harriss, who has been an ideal mentor and teacher throughout my training and research. I am indebted to Dr. Poole for his experienced advice and criticisms, which were useful during my graduate student life and beyond. I am also grateful to Dr. Bridgwood for his time and efforts in reviewing my thesis. Finally, I would like to thank Dr. Doug Hirt, Dr. Chad Sosolik and Dr. Santosh Rahane for their help in analyzing XPS results.

# TABLE OF CONTENTS

| Pa <sub>i</sub><br>TITLE                                                                                                                                                                              | -                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| ABSTRACT                                                                                                                                                                                              | ii                      |

| DEDICATION                                                                                                                                                                                            | iii                     |

| ACKNOWLEDGEMENTS                                                                                                                                                                                      | iv                      |

| LIST OF TABLESv                                                                                                                                                                                       | iii                     |

| LIST OF FIGURES                                                                                                                                                                                       | ix                      |

| CHAPTER                                                                                                                                                                                               |                         |

| 1. INTRODUCTION                                                                                                                                                                                       | .1                      |

| <ul><li>1.1 Overview</li><li>1.2 Synopsis of Chapters</li></ul>                                                                                                                                       |                         |

| 2. REVIEW OF SILICON CARBIDE                                                                                                                                                                          | .4                      |

| <ul> <li>2.1 Physical Properties</li></ul>                                                                                                                                                            | 4<br>5<br>9<br>10<br>11 |

| <ol> <li>METAL SEMICONDUCTOR CONTACTS</li> <li>3.1 Ideal Metal Semiconductor Contacts</li> <li>3.2 Schottky Barrier Height</li> <li>3.2.1 Schottky-Mott Limit</li> <li>3.2.2 Bardeen Limit</li> </ol> | 16<br>19<br>19<br>22    |

| <ul> <li>3.3 Current Transport Mechanisms</li> <li>3.3.1 Electron Emission over the Barrier</li> <li>3.3.2 Quantum-mechanical tunneling through the barrier</li> </ul>                                | 25                      |

Table of Contents (Continued)

|    | 3.3.3 Electron-hole recombination in the space-charge region |    |

|----|--------------------------------------------------------------|----|

|    | 3.3.4 Hole injection in the neutral region of semiconductor  |    |

|    | 3.4 Ohmic Contacts                                           | 29 |

| 4. | FABRICATION OF METAL/4H-SIC SCHOTTKY DIODES                  | 31 |

|    | 4.1 Basic Structure of Schottky Diode                        | 32 |

|    | 4.2 Materials and Resources Used                             |    |

|    | 4.3 Preceding Procedure for Fabrication of Schottky Diode    |    |

|    | 4.3.1 Degrease and Back-side Surface Etch                    |    |

|    | 4.3.2 Deposition of Nickel on the Back-side                  |    |

|    | 4.3.3 Annealing of Nickel to make Ohmic contacts             |    |

|    | 4.3.4 Deposition of Protective Layer on the Back-side        |    |

|    | 4.3.5 Second Degrease and Front-side Surface Etch            |    |

|    | 4.3.6 Deposition of Schottky contacts on the Front-side      |    |

|    | 4.3.7 Removal of Protective Layer                            |    |

|    | 4.4 Shortcomings of the Preceding Fabrication Process        |    |

|    | 4.5 Revised Procedure for Fabrication of Schottky Diode      |    |

|    | 4.5.1 Initial Degrease and Back-side Surface Etch            |    |

|    | 4.5.2 Deposition of Nickel on the Back-side                  |    |

|    | 4.5.3 Annealing of Nickel to form Ohmic Contacts             |    |

|    | 4.5.4 Deposition of the Protective Layer on the Back-side    |    |

|    | 4.5.5 Second Degrease and Front-side Surface Etch            |    |

|    | 4.5.6 Deposition of Schottky contacts on the Front-side      |    |

|    | 4.5.7 Removal of Protective Layer                            |    |

|    | 4.6 Annealing of the Schottky Contacts                       |    |

|    | 4.7 Conclusions                                              |    |

| 5. | MEASUREMENTS AND PARAMETER EXTRACTION                        | 64 |

|    | 5.1 Measurement Techniques                                   | 65 |

|    | 5.2 Current-Voltage (I-V) Measurements                       |    |

|    | 5.2.1 Theory                                                 |    |

|    | 5.2.2 Data Plotting and Extraction of Parameters             |    |

|    | 5.3 Capacitance-Voltage (C-V) Measurements                   |    |

|    | 5.3.1 Theory                                                 |    |

|    | 5.3.4 Data Plotting and Extraction of Parameters             |    |

|    | 5.4 X-ray Photoelectron Spectroscopy (XPS)                   |    |

|    | 5.5 Conclusions                                              |    |

|    |                                                              |    |

Table of Contents (Continued)

| 6.    | RESULTS AND DISCUSSION                                             | 89  |

|-------|--------------------------------------------------------------------|-----|

|       | 6.1 Characterization of Al/4H-SiC Schottky Diodes                  | 91  |

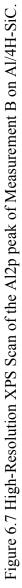

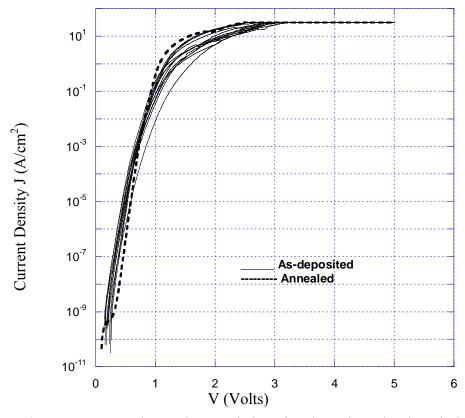

|       | 6.1.1 Electrical Characterization by I-V and C-V Measurements      | 91  |

|       | 6.1.2 Surface Characterization by X-ray Photoelectron Spectroscopy | 96  |

|       | 6.2 Characterization of Cu/4H-SiC Schottky Diodes                  | 105 |

|       | 6.2.1 Electrical Characterization by I-V and C-V Measurements      | 105 |

|       | 6.3 Characterization of Au/4H-SiC Schottky Diodes                  | 111 |

|       | 6.3.1 Electrical Characterization by I-V and C-V Measurements      |     |

|       | 6.4 Conclusions                                                    | 115 |

| 7.    | SUMMARY AND CONCLUSIONS                                            | 116 |

| REFER | ENCES                                                              | 121 |

# LIST OF TABLES

| Pag                                                                                                  | Table |

|------------------------------------------------------------------------------------------------------|-------|

| 2.1 Thermal properties of common polytypes of SiC                                                    | 2.1   |

| 2.2 Mechanical properties of common polytypes of SiC                                                 | 2.2   |

| 2.3 Optical properties of common polytypes of SiC1                                                   | 2.3   |

| 2.4 Electrical Properties of common polytypes of SiC                                                 | 2.4   |

| 2.5 Properties of Silicon, GaAs, and SiC at T=300K1                                                  | 2.5   |

| 4.1 Annealing Times and Temperatures for different metals on 4H-SiC                                  | 4.1   |

| 6.1 List of 4H-SiC Wafers used with their Doping Concentrations                                      | 6.1   |

| 6.2 Schottky-Mott Limits for Al, Cu and Au for SiC polytypes used9                                   | 6.2   |

| 6.3 List of Parameters for As-deposited Al/4H-SiC Sample AC0113-06J239                               | 6.3   |

| 6.4 List of Parameters for Annealed Al/4H-SiC Sample AC0113-06J239                                   | 6.4   |

| 6.5 Comparison of Average Parameters for As-deposited and<br>Annealed Al/4H-SiC Sample AC0113-06J23  | 6.5   |

| 6.6 List of Parameters for As-deposited Cu/4H-SiC Sample B1145-06I1210                               | 6.6   |

| 6.7 List of Parameters for Annealed Cu/4H-SiC Sample B1145-06I1210                                   | 6.7   |

| 6.8 Comparison of Average Parameters for As-deposited and<br>Annealed Cu/4H-SiC Sample B1145-06I1210 | 6.8   |

| 6.9 List of Parameters for as-deposited Au/4H-SiC Sample AC0113-06K1311                              | 6.9   |

# LIST OF FIGURES

| Figure | Page                                                                                                      |

|--------|-----------------------------------------------------------------------------------------------------------|

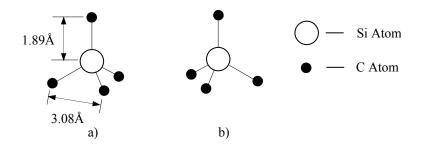

| 2.1    | Basic tetrahedral unit in SiC                                                                             |

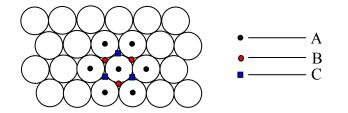

| 2.2    | Different possible stacking positions relative to a bilayer                                               |

| 2.3    | Stacking sequences of SiC bilayers in common polytypes7                                                   |

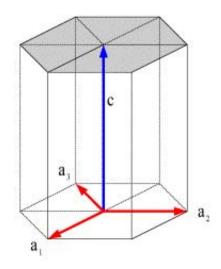

| 2.4    | Unit cell of hexagonal polytypes of SiC                                                                   |

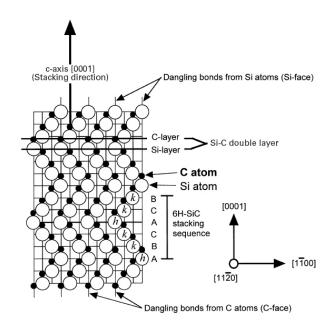

| 2.5    | Schematic cross-section of the 6H-polytype illustrating the silicon face and carbon face                  |

| 3.1    | Formation of Schottky barrier between metal and n-type semiconductor17                                    |

| 3.2    | Barriers for semiconductors of different types and work functions                                         |

| 3.3    | Energy Band Diagram of the Schottky contact                                                               |

| 3.4    | Metal-Semiconductor contact with surface states                                                           |

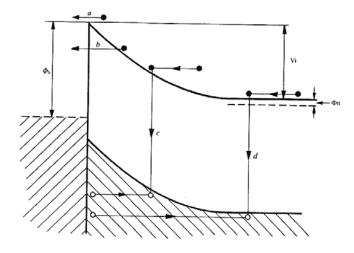

| 3.5    | Current transport mechanisms in a forward-biased Schottky Barrier24                                       |

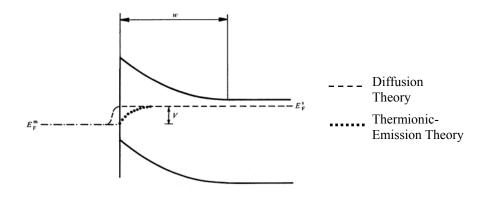

| 3.6    | Electron quasi-Fermi level in a forward-biased Schottky barrier                                           |

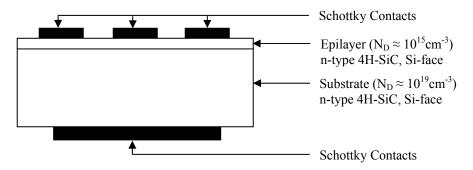

| 4.1    | Basic Structure of a Schottky Diode                                                                       |

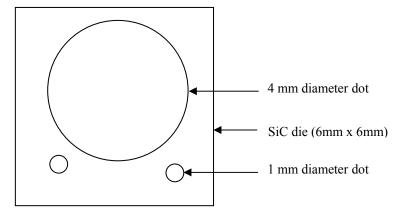

| 4.2    | Pattern of Ohmic contacts on the back-side of 4H-SiC sample                                               |

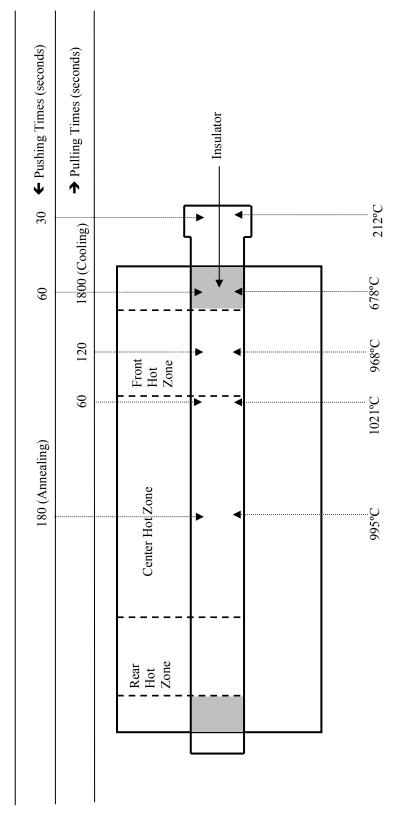

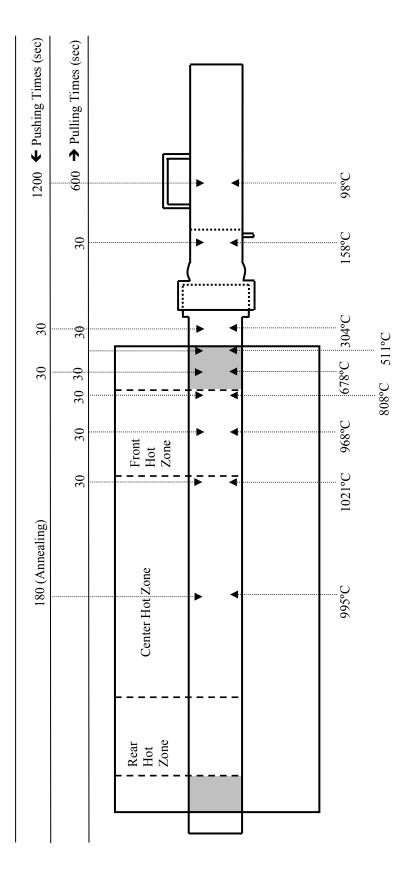

| 4.3    | Schematic of Annealing Furnace tube with temperatures and<br>time for annealing Nickel contacts at 1000°C |

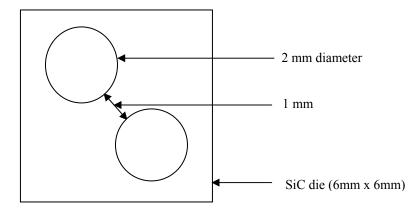

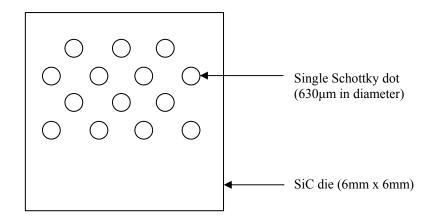

| 4.4    | Pattern of Schottky contacts on the Front-side of the sample44                                            |

| 4.5    | Pattern of Ohmic contacts on the back-side of 4H-SiC sample50                                             |

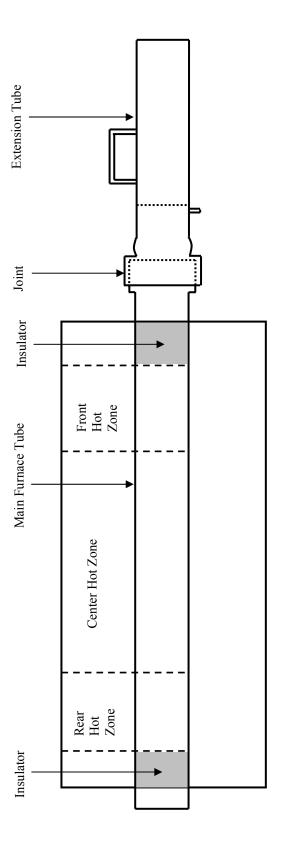

| 4.6    | Schematic of Annealing Furnace tube with the Extension tube<br>attached to the main furnace tube          |

| 4.7    | Schematic of Annealing Furnace tube and Extension tube for<br>Annealing Nickel at 1000°C53                |

# List of Figures (Continued)

| Figure |                                                                                           | Page |

|--------|-------------------------------------------------------------------------------------------|------|

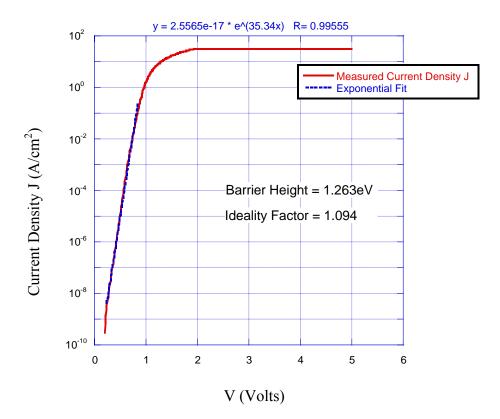

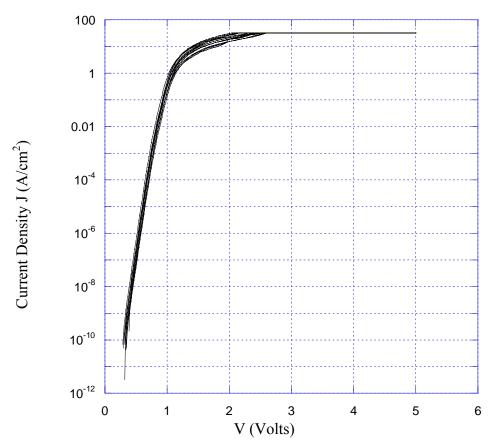

| 5.1    | Forward I-V Characteristics of a Cu/4H-SiC Schottky Diode                                 | 74   |

| 5.2    | Plot of $dV d\ln(J)$ vs. J for extracting Diode Series Resistance                         | 76   |

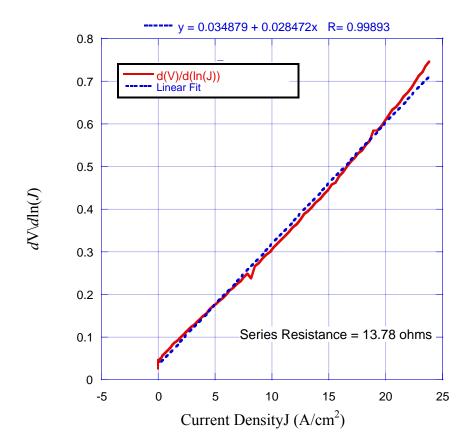

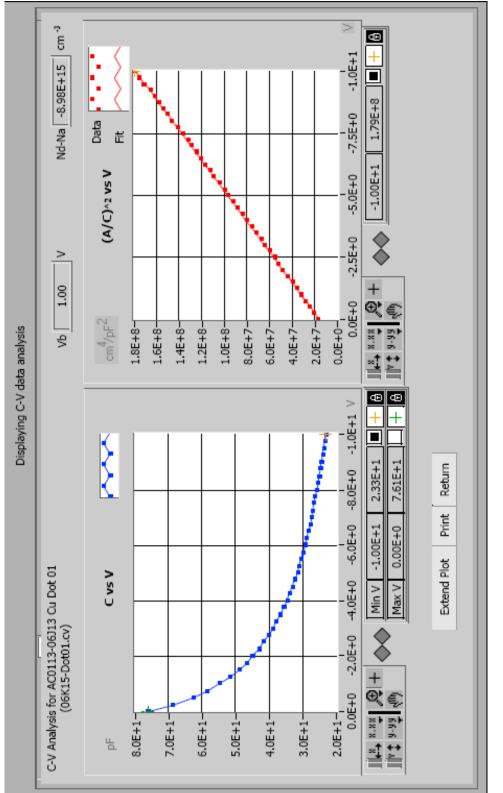

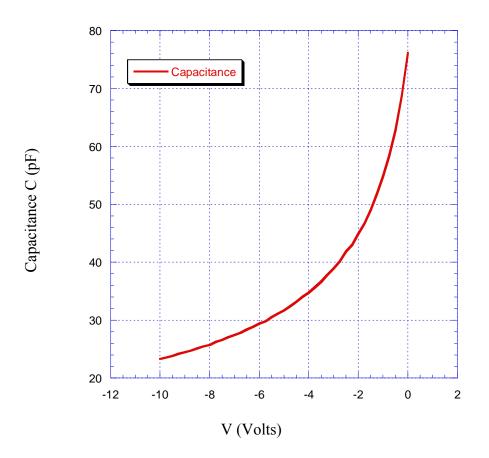

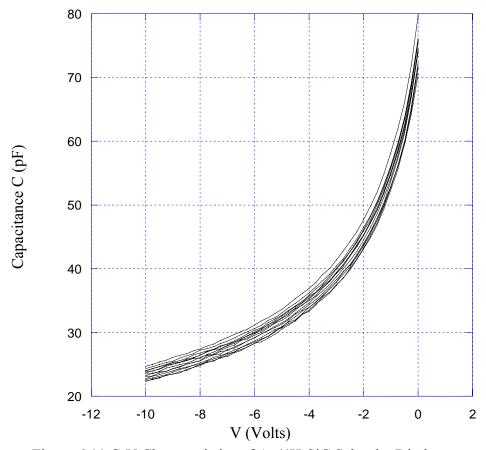

| 5.3    | C-V Characteristics of a Schottky Diode as obtained from Sula Software                    | 80   |

| 5.4    | C-V Characteristics of a Cu/4H-SiC Schottky Diode                                         | 81   |

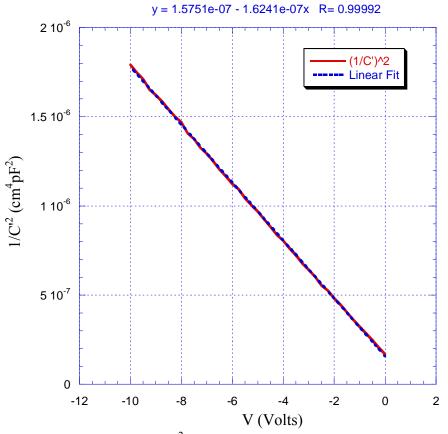

| 5.5    | Plot of 1/C <sup>2</sup> versus voltage V with linear curvefit to the plot                | 82   |

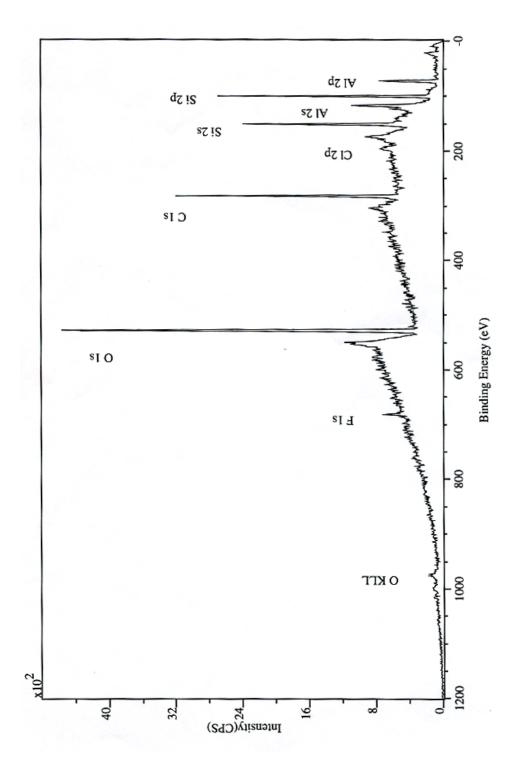

| 5.6    | XPS Wide-Spectrum Survey Scan of Al/4H-SiC                                                | 85   |

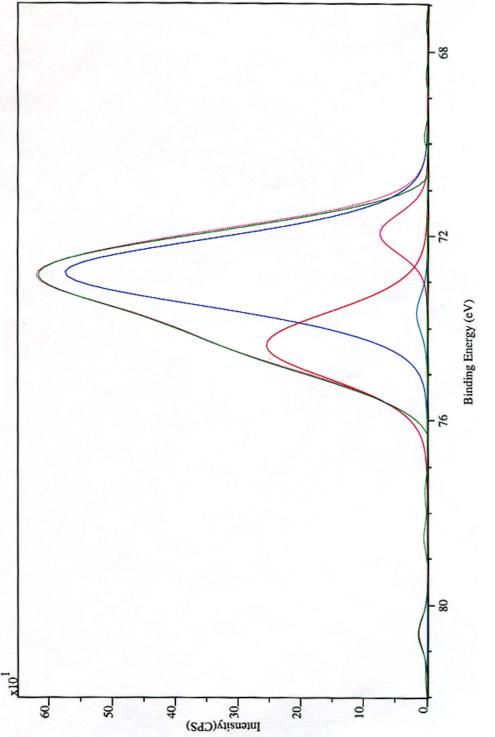

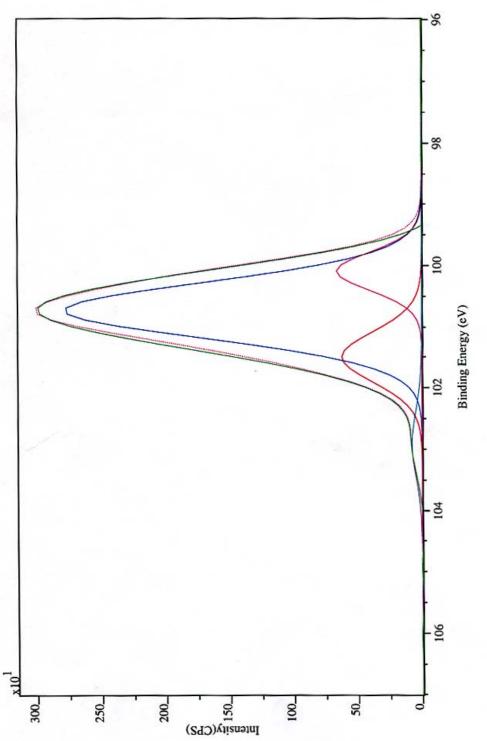

| 5.7    | High-Resolution XPS Scan of the Al2p peak of Al/4H-SiC                                    | 87   |

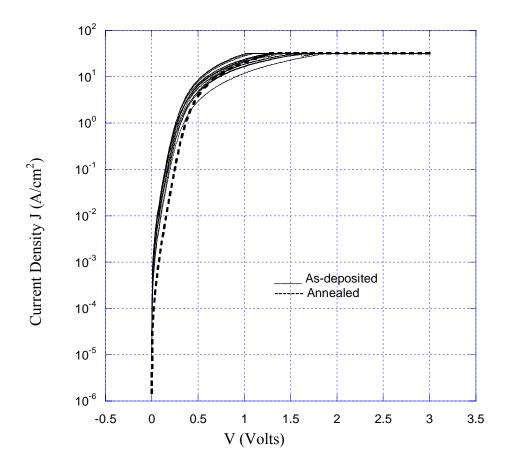

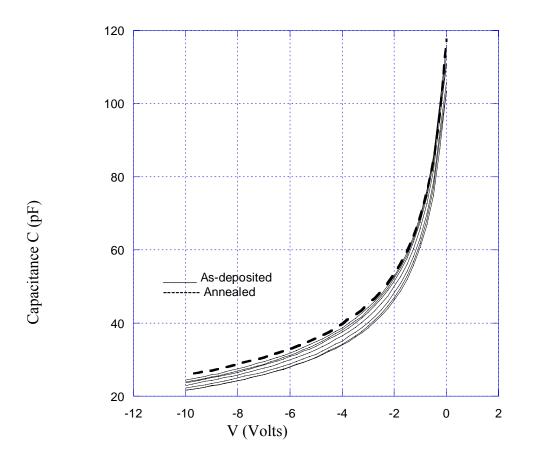

| 6.1    | Forward I-V Characteristics of Al/4H-SiC Schottky diodes                                  | 94   |

| 6.2    | C-V Characteristics of Al/4H-SiC Schottky diodes                                          | 95   |

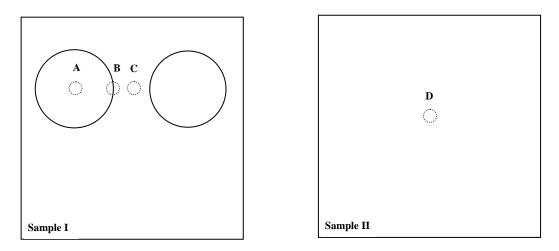

| 6.3    | XPS samples and Measurement Positions for XPS                                             | 98   |

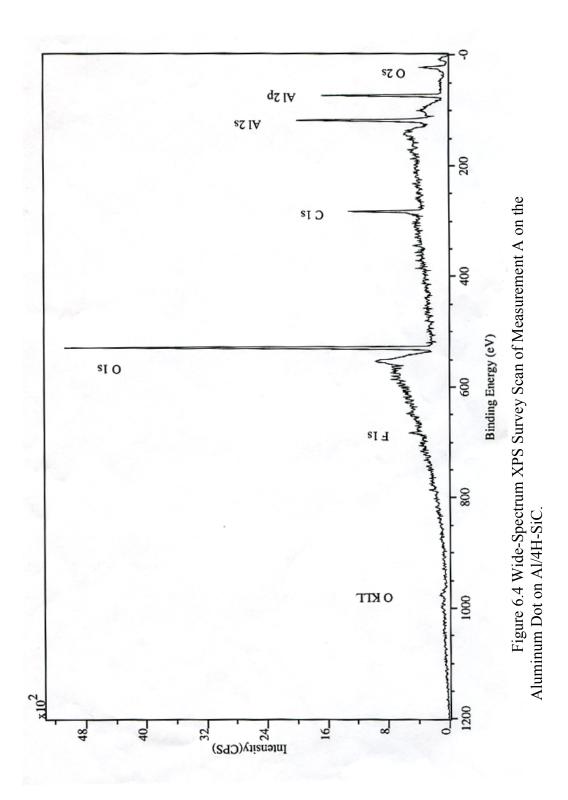

| 6.4    | Wide-Spectrum XPS Survey Scan of the Aluminum Dot<br>(Measurement A) on Al/4H-SiC         | 100  |

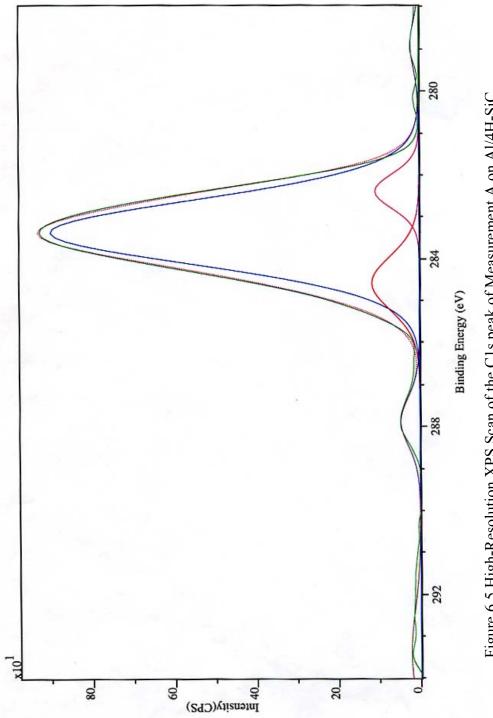

| 6.5    | High-Resolution XPS Scan of the C1s peak of Measurement A<br>on Al/4H-SiC                 | 101  |

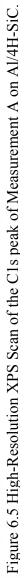

| 6.6    | Wide-Spectrum XPS Survey Scan of the edge of Aluminum Dot<br>(Measurement B) on Al/4H-SiC | 102  |

| 6.7    | High-Resolution XPS Scan of the Al2p peak of Measurement B<br>on Al/4H-SiC                | 103  |

| 6.8    | Forward I-V Characteristics of Cu/4H-SiC Schottky Diodes                                  | 108  |

| 6.9    | C-V Characteristics of Cu/4H-SiC Schottky Diode                                           | 110  |

| 6.10   | Forward I-V Characteristics of Au/4H-SiC Schottky Diodes                                  | 113  |

| 6.11   | C-V Characteristics of Au/4H-SiC Schottky Diodes                                          | 114  |

# CHAPTER 1 INTRODUCTION

#### 1.1 Overview

Silicon Carbide (SiC) is the only known stable binary compound of Silicon and Carbon. SiC is an attractive semiconductor due to its superior electrical, thermal, chemical and mechanical properties. Its properties such as wide band gap, high thermal conductivity, high breakdown field, high saturation electron drift velocity, high chemical stability, and strong mechanical strength make it a promising material for next generation electronic devices for high power, high temperature and high frequency applications.

One unique aspect of SiC is that it possesses a one-dimensional polymorphism called polytypism. Among the numerous known polytypes, three polytypes have generated much interest, namely 3C-, 4H- and 6H-SiC. There have been a large number of studies on 6H-SiC because single crystal 6H-SiC has been relatively easy to obtain as compared to other polytypes. However, 4H-SiC has superior electronic properties over the other two, including wider band-gap and higher, more isotropic electron mobility.

Schottky Barrier Diodes (SBDs) are used as rectifiers to suppress high-voltage transients induced on the power line during current switching. For a negligible dissipation of power during switching, the reverse current transient of the SBD must be suppressed, maintaining a high reverse voltage without breakdown. SiC Schottky Barrier Diodes are especially attractive because of their high breakdown voltages and low leakage currents.

The focus of this research project is to fabricate and characterize metal/4H-SiC Schottky Diodes and to study the effects of annealing on the Schottky parameters.

### 1.2 Synopsis of the chapters

Chapter 2 reviews the basic properties of SiC in terms of Crystal structure, various polytypes with an emphasis on the three primary polytypes, thermal, mechanical, optical, and electronic properties. The comparison of these properties with Silicon (Si) and Gallium Arsenide (GaAs) will also be included, highlighting the superiority of SiC and in particular, the 4H polytype.

Chapter 3 reviews the theory of metal-semiconductor contacts, both rectifying and ohmic. The various current conduction mechanisms in metal-semiconductor contacts are also reviewed.

Chapter 4 introduces the entire fabrication process of metal-4H-SiC diodes followed in this research project. This includes the previous fabrication process and the revised fabrication process, with emphasis on the reasons for the changes in the process and the consequent improvements.

Chapter 5 explains the different measurement techniques used, the measurement setup for each technique and the extraction of Schottky parameters from the measured results. The theories behind each technique, along with the tools used for the parameter extractions are also discussed.

Chapter 6 discusses the results of the measurements in detail. The performance of the Schottky diodes is discussed in detail, with comparison of the Schottky parameters for different metals used. The benefits of the revised fabrication process are also explained. Finally, the effect of annealing of Schottky contacts on the device performance is explained with comparison of the Schottky parameters before and after annealing.

#### CHAPTER 2

#### **REVIEW OF SILICON CARBIDE**

SiC is an attractive semiconductor due to its superior electrical, thermal, chemical and mechanical properties such as wide band gap, high thermal conductivity, high breakdown field, high saturation electron drift velocity, high chemical stability, and good mechanical strength. These properties make SiC a promising material for next generation electronic devices for high power, high temperature and high frequency applications that are not possible using Si or GaAs. SiC is also resistant to high radiation doses, which makes it potentially the ideal material for nuclear power applications [1]. SiC can also be used for various optical device applications such as blue and ultraviolet (UV) light emitting diodes (LEDs) and photodetectors. In this chapter, some of the basic physical, thermal, mechanical, optical and electronic properties are discussed.

## 2.1 Physical Properties

# 2.1.1 Crystal Structure

SiC is the only known stable binary compound of Silicon (Si) and Carbon (C). It contains an equal number of Silicon and Carbon atoms. The basic structural unit of SiC is a covalently bonded (88% covalent and 12% ionic) tetrahedron between Si and C atoms. Each Si atom is covalently bonded with four C atoms in a tetrahedral structure and similarly, each C atom is bonded to four Si atoms. The approximate bond length between the Si-Si or C-C atoms is 3.08Å, while the approximate bond length between the Si-C atoms is 1.89Å [1]. The SiC crystals are formed by the tetrahedrons joined to each other at the corners.

Figure 2.1 Basic tetrahedral unit in SiC consisting of a tetrahedron of four C atoms with one Si atom in the middle: a) Basic tetrahedron with bond lengths. b) Basic tetrahedron rotated 180° around the stacking direction.

# 2.1.2 Polytypes

SiC possesses a one-dimensional polymorphism called polytypism. In a polytypic compound, similar sheets of atoms are stacked on top of each other and related according to a symmetry operator. The differences among the polytypes arise in the direction perpendicular to the sheets. In SiC, each sheet represents a bilayer composed of one layer of Si atoms and one layer of C atoms. To stack an identical second sheet on top of the first, there are two possibilities for arranging the second sheet relative to the first sheet, as shown in Fig. 1.2. Thus a sheet can be denoted as A, B or C depending on its position of the spheres relative to the previous layer.

Figure 2.2 Different possible stacking positions relative to a bilayer.

Depending on the stacking sequence, the crystal structures of SiC are cubic, hexagonal, or rhombohedral. The only known cubic polytype (3C) is referred to as  $\beta$ -SiC, while the hexagonal and rhombohedral polytypes are collectively referred to as  $\alpha$ -SiC. Depending on the periodicity in the stacking sequence, the polytypes are referred as 3C, 4H, 6H, 15R, etc. Thus, 4H-SiC has a hexagonal crystal structure with a periodicity of 4 bilayers, while 15R-SiC has a rhombohedral crystal structure with a periodicity of 15 bilayers. The stacking sequences of the common polytypes of SiC are shown in Fig. 1.3.

Figure 2.3 Stacking sequences of SiC bilayers in common polytypes.

The unit cell of the hexagonal polytypes of SiC is shown in Fig. 1.4. The plane formed by the bilayer sheet of Si and C atoms is known as the basal plane [2]. The basal plane has 3 axes at an angle of  $120^{\circ}$  with each other. The axis perpendicular to the basal plane is the *c*-axis, which is also the stacking direction of the bilayers. The SiC crystal planes thus need four Miller indices for reference. Thus, the stacking direction or the [0001] direction is the crystallographic *c*-axis which is defined normal to the basal plane.

Figure 2.4 Unit cell of hexagonal polytypes of SiC.

SiC is a polar semiconductor across the *c*-axis. As shown in Fig. 1.5, one surface normal to the *c*-axis is terminated with Si atoms while the opposite surface is terminated with C atoms. These surfaces are commonly referred to as "Silicon face" and "Carbon face" respectively. The Silicon atoms in Fig. 1.5 labeled "h" or "k" denote the Si-C bilayers which are in "quasi-hexagonal" or "quasi-cubic" environments with respect to their immediate neighboring bilayers.

Figure 2.5 Schematic cross-section of the 6H-polytype illustrating the silicon face and carbon face[2].

# 2.2 Thermal Properties

The excellent high-temperature properties make SiC very suitable for hightemperature electronic applications. The high elastic modulus of SiC and the relatively low atomic weights of Si and C promote harmonic lattice vibrations, giving SiC a high thermal conductivity [1]. From the device application point of view, the thermal conductivity of SiC exceeds that of Copper, BeO, Al<sub>2</sub>O<sub>3</sub> and AlN [3]. The thermal properties of 3C-, 4H- and 6H-SiC are listed in Table 2.1.

| Properties                                                  | 3C                   | 4H     | 6Н                                                                                   |

|-------------------------------------------------------------|----------------------|--------|--------------------------------------------------------------------------------------|

| Melting Point (°C)                                          | ~3100K               | ~3100K | ~3100K                                                                               |

| Specific Heat (J g <sup>-1</sup> °C <sup>-1</sup> )         | 0.69                 | 0.69   | 0.69                                                                                 |

| Thermal Conductivity (W cm <sup>-1</sup> °C <sup>-1</sup> ) | 4.9                  | 4.9    | 4.9                                                                                  |

| Thermal Diffusivity (cm <sup>2</sup> s <sup>-1</sup> )      | 1.6                  | 1.7    | 2.2                                                                                  |

| Thermal Expansion (°C <sup>-1</sup> )                       | $\sim 3.8 * 10^{-6}$ |        | $4.3 * 10^{-6} (\perp c \text{-axis})$<br>$4.7 * 10^{-6} (\parallel c \text{-axis})$ |

|                                                             |                      |        | 4.7 * 10 <sup>-6</sup> (   c-axis)                                                   |

# 2.3 Mechanical Properties

SiC is one of the hardest known materials and is widely used as a cutting tool or

an abrasive. Listed below in Table 2.2 are some of the excellent mechanical properties.

Table 2.2 Mechanical properties of common polytypes of SiC [1].

| Properties                            | 3C      | 4H    | 6H            |

|---------------------------------------|---------|-------|---------------|

| Bulk Modulus (GPa)                    | 392-448 |       | 97            |

| Mohs hardness                         | ~9      | ~9    | ~9            |

| Acoustic velocity (ms <sup>-1</sup> ) | 12600   | 13730 | 13100 - 13260 |

## 2.4 Optical Properties

Silicon carbide is an electroluminescent material and hence is widely used for manufacturing blue LEDs and ultraviolet detectors. Table 2.3 lists some of the optical properties of SiC.

| Properties                 | 3C      | 4H                                                                                          | 6Н                                                                                        |

|----------------------------|---------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Optical Bandgap (eV)       | 2.4-2.6 |                                                                                             | 2.86                                                                                      |

| Excitation Energy Gap (eV) | 2.39    | 3.27                                                                                        | 3.02                                                                                      |

| Infrared Refractive Index  | 2.55    | $\begin{array}{c c} 2.55 \perp c \text{-axis} \\ 2.59 \parallel c \text{-axis} \end{array}$ | $\begin{array}{c} 2.55 \perp c \text{-axis} \\ 2.59 \parallel c \text{-axis} \end{array}$ |

| Table 2.3 Optica | l properties | s of commor | n polytypes | of SiC | [1], | [4]. |

|------------------|--------------|-------------|-------------|--------|------|------|

|------------------|--------------|-------------|-------------|--------|------|------|

# 2.5 Electrical Properties

SiC has generated much interest in power applications due to its superior electrical properties. Among other properties, the wide bandgap energy and low intrinsic carrier concentration of SiC allow it to maintain semiconductor behavior at much higher temperatures than Silicon, which permits SiC device functionality at elevated temperatures. A natural consequence of the wider bandgap of SiC is higher effective Schottky barrier heights, which allows Schottky Barrier Diodes to suppress currents at high reverse voltages without breakdown. Also, a lower intrinsic carrier concentration leads to lower leakage currents due to minority carriers. Listed below in Table 2.4 are some of the important electrical properties of the common polytypes of SiC. Comparison of some the properties with the corresponding properties of Silicon (Si) and Gallium Arsenide (GaAs) are presented in Table 2.5.

| Properties                                                  | 3C            | 4H                | 6H                |

|-------------------------------------------------------------|---------------|-------------------|-------------------|

| Breakdown Field (V cm <sup>-1</sup> )                       | $\sim 10^{6}$ | 6*10 <sup>5</sup> | 6*10 <sup>5</sup> |

| Mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) |               |                   |                   |

| electrons                                                   | ≤800          | ≤900              | ≤400              |

| holes                                                       | ≤320          | ≤120              | ≤90               |

| Diffusion coefficient ( $cm^2 s^{-1}$ )                     |               |                   |                   |

| electrons                                                   | ≤20           | ≤22               | ≤10               |

| holes                                                       | $\leq 8$      | ≤3                | ≤2                |

| Electron Thermal Velocity (m s <sup>-1</sup> )              | $2 * 10^5$    | $1.9 * 10^5$      | $1.5 * 10^5$      |

| Hole Thermal Velocity (m s <sup>-1</sup> )                  | $1.5 * 10^5$  | $1.2 * 10^5$      | $1.2 * 10^5$      |

| Saturated Electron Drift Velocity (cm s <sup>-1</sup> )     | $2 * 10^7$    | $2 * 10^7$        | $2 * 10^7$        |

| Electron Affinity (eV)                                      |               | 3.6               | 3.3               |

Table 2.4 Electrical Properties of common polytypes of SiC [1], [4].

# 2.6 Choice of 4H-SiC polytype

A large number of studies have been done on 6H-SiC because single crystal 6H-SiC has been relatively easy to obtain as compared to other polytypes [5]. However, 4H-SiC is a superior semiconductor because of its wider bandgap and higher electron mobility. Table 2.5 lists the important properties of 4H-SiC in comparison with the other polytypes, along with Silicon and GaAs.

| Property                                                           | Si                    | GaAs                 | SiC                  |                                                                 |                                                         |

|--------------------------------------------------------------------|-----------------------|----------------------|----------------------|-----------------------------------------------------------------|---------------------------------------------------------|

|                                                                    |                       |                      | 3C                   | 4H                                                              | 6Н                                                      |

| Bandgap Energy (eV)                                                | 1.12                  | 1.42                 | 2.36                 | 3.26                                                            | 3                                                       |

| Breakdown Field (V cm <sup>-1</sup> )                              |                       |                      | ~10 <sup>6</sup>     | 6*10 <sup>5</sup>                                               | 6*10 <sup>5</sup>                                       |

| Density (gm cm <sup>-3</sup> )                                     | 2.33                  | 5.32                 | 3.21                 | 3.21                                                            | 3.21                                                    |

| Static Dielectric Constant                                         | 11.7                  | 13.1                 | 9.72                 | 9.66 $\perp$ <i>c</i> -axis<br>10.03 $\parallel$ <i>c</i> -axis | 9.66 ⊥ <i>c</i> -axis<br>10.03 <b>  </b> <i>c</i> -axis |

| Electron Mobility (cm <sup>2</sup> s <sup>-1</sup> )               | 1350                  | 8500                 | ≤800                 | ≤900                                                            | <u>≤</u> 400                                            |

| Hole Mobility (cm <sup>2</sup> s <sup>-1</sup> )                   | 480                   | 400                  | ≤320                 | ≤120                                                            | ≤90                                                     |

| Intrinsic Carrier<br>Concentration (cm <sup>-3</sup> )             | 1.5*10 <sup>10</sup>  | 1.8*10 <sup>6</sup>  | 6.9                  | 8.2*10 <sup>-9</sup>                                            | 2.3*10 <sup>-6</sup>                                    |

| Saturated Electron Drift<br>Velocity (cm s <sup>-1</sup> )         | 1.0*10 <sup>7</sup>   | 1.0*10 <sup>7</sup>  | 2.0*10 <sup>7</sup>  | 2.0*10 <sup>7</sup>                                             | 2.0*10 <sup>7</sup>                                     |

| Thermal Conductivity<br>(W cm <sup>-1</sup> °C <sup>-1</sup> )     | 1.5                   | 0.5                  | 4.9                  | 4.9                                                             | 4.9                                                     |

| Electron Affinity (eV)                                             | 4.01                  | 4.07                 | 4.0                  | 3.6                                                             | 3.3                                                     |

| Effective Conduction Band<br>Density of States (cm <sup>-3</sup> ) | 2.8*10 <sup>19</sup>  | 4.7*10 <sup>19</sup> | 1.5*10 <sup>19</sup> | $1.7*10^{19}$                                                   | 8.9*10 <sup>19</sup>                                    |

| Effective Valence Band<br>Density of States (cm <sup>-3</sup> )    | 1.04*10 <sup>19</sup> | 7.0*10 <sup>18</sup> | 1.2*10 <sup>19</sup> | 2.5*10 <sup>19</sup>                                            | 2.5*10 <sup>19</sup>                                    |

| Effective Electron Mass<br>(in units of m <sub>0</sub> )           |                       |                      |                      |                                                                 |                                                         |

| longitudinal $m_l/m_0$                                             | 0.98                  | 0.067                | 0.68                 | 0.29                                                            | 2.0                                                     |

| transverse $m_{\rm t}/m_0$                                         | 0.19                  |                      | 0.25                 | 0.42                                                            | 0.42                                                    |

| Effective Hole Mass<br>(in units of m <sub>0</sub> )               | 0.49                  | 0.45                 | 0.6                  | ~1                                                              | ~1                                                      |

Table 2.5 Properties of Silicon, GaAs, and SiC at T=300K [1], [4], [6].

The basal plane electron mobility of 4H-SiC is reported to be more than twice than that of 6H-SiC, while the electron mobility of 4H-SiC in the direction of *c*-axis is almost 10 times that of 6H-SiC [7]. Furthermore, the anisotropy ratio ( $A_e = 0.83$ ) of 4H-SiC between the electron mobilities parallel to and along the *c*-axis is much closer to unity than the anisotropy ration ( $A_e = 4.9$ ) in 6H-SiC [1]. Hence, to realize Schottky Barrier Diodes with maximum performance, 4H-SiC was chosen for this work.

### CHAPTER 3

#### METAL-SEMICONDUCTOR CONTACTS

The earliest investigation of metal-semiconductor rectifying contacts is attributed to Braun, who in 1874 noted the dependence of the total resistance on the polarity of the applied voltage and on detailed surface conditions [8]. In 1931, it was discovered that if a current flows through a metal-semiconductor contact, then the potential drop occurs almost entirely at the contact, implying the existence of a potential barrier. In 1938, Schottky and Mott, both independently, came up with a theory explaining the transport of electrons over the potential barrier through drift and diffusion. This was the groundwork on which subsequent work done on Schottky and Ohmic contacts was based. In this chapter, the theory of ideal metal-semiconductor contacts is introduced. Then, the concept of barrier height and the various current conduction mechanisms are reviewed. Finally, the applications of metal-semiconductor contacts in microelectronics will be discussed.

#### 3.1 Ideal Metal-Semiconductor contacts

A Metal-Semiconductor contact is formed when a metal and a semiconductor are brought into intimate contact with each other. Depending on the work-functions of the metal and the semiconductor, the contact may be either Schottky (rectifying) or Ohmic (non-rectifying). In this chapter, we will primarily focus on the Schottky contacts because the majority of metal-semiconductor combinations form rectifying or "blocking" contacts.

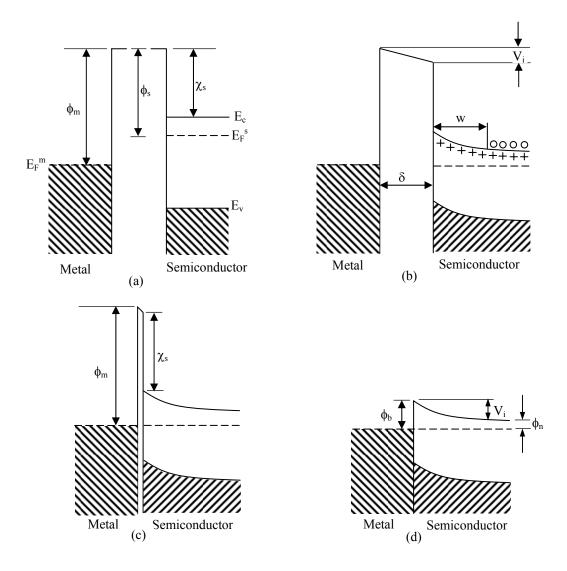

To see how a Schottky barrier is formed, suppose that the metal and semiconductor are both electrically neutral and isolated from each other. The energy band-diagram in Fig. 3.1(a) is for an n-type semiconductor whose work function ( $\phi_s$ ) is less than that of the metal ( $\phi_m$ ). This is the most common case observed when forming Schottky contacts. If the metal and semiconductor are electrically connected by a wire, electrons will pass from the semiconductor into the metal and the two Fermi levels are forced to align as shown in Fig. 3.1(b). There is an electric field in the gap and there is a negative charge on the surface of the metal, which is balanced by a positive charge in the semiconductor. If the metal and the semiconductor approach each other as shown in Fig. 3.1(c), the potential difference between the electrostatic potentials between the surfaces of the metal and the semiconductor tends to zero, since the electric field is finite. When they finally touch, the barrier due to the gap vanishes altogether and we get an ideal metal-semiconductor contact.

Figure 3.1 Formation of Schottky barrier between metal and n-type semiconductor: (a) neutral and electrically isolated, (b) electrically connected, (c) separated by a narrow gap, (d) in perfect contact[9].

In most practical cases, the ideal situation shown in Fig. 3.1(d) is never reached because there is usually a thin insulating layer of oxide about 10-20Å thick on the surface of the semiconductor. Such an insulating layer is called an interfacial layer. A practical

contact is thus more like that shown in Fig. 3.1(c). However, the barrier presented to the electrons by the interfacial layer is usually so narrow that the electrons can tunnel through it quite easily.

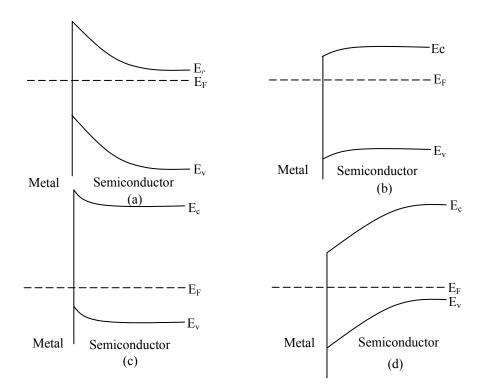

Fig 3.2 illustrates barrier height for various combinations of the semiconductor type and the M-S work function difference ( $\phi_{ms}$ ). The cases shown in Fig. 3.2 (b) and (c) are very uncommon in practice and the majority of the metal-semiconductor combinations form rectifying contacts.

Figure 3.2 Barriers for semiconductors of different types and work functions; n-type: (a)  $\phi_m > \phi_s$  (rectifying), (b)  $\phi_m < \phi_s$  (ohmic). p-type: (c)  $\phi_m > \phi_s$  (ohmic). (d)  $\phi_m < \phi_s$  (rectifying).

If we consider other combinations of the semiconductor type and metal, for instance a case when  $\phi_s$  is greater than  $\phi_m$  as shown in Fig. 3.2(b), then the barrier height encountered in the Fig. 3.1(d) is no longer applicable. If the contact was biased such that the electrons flow from semiconductor to the metal, they encounter no barrier. The current is then determined by the bulk resistance of the semiconductor. Such a contact is called an Ohmic contact. This type of contact has sufficiently low resistance for the current to be determined by the resistance of the bulk semiconductor rather than the contact properties.

# 3.2 Schottky Barrier Height

#### 3.2.1 Schottky-Mott Limit

The work function is defined as the energy difference between the vacuum level and the Fermi level. This quantity is denoted by  $\phi_m$  for the metal and  $\phi_s$  for the semiconductor. The semiconductor work function is given by:

$$\phi_s = \chi + \phi_n \tag{3.1}$$

where  $\phi_n$  is the energy difference between the E<sub>C</sub> and the Fermi level E<sub>F</sub>, and is given by

$$\phi_n = E_C - E_F = \frac{kT}{q} \ln\left(\frac{N_C}{N_D}\right)$$

3.2

The potential difference between the work functions  $\phi_m$  and  $\phi_s$  is called the contact potential and is equal to the built-in potential at equilibrium when no bias is applied. The potential difference is given by:

$$\phi_{ms} = V_i = \phi_m - \phi_s \tag{3.3}$$

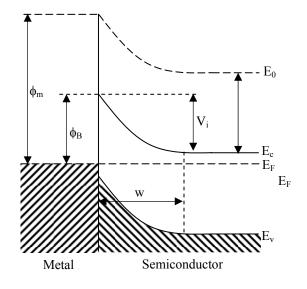

Thus the barrier height,  $\phi_{Bn}$ , for the ideal case is given by

$$\phi_{Bn} = \phi_m - \chi \tag{3.4}$$

For an ideal contact between a metal and a p-type semiconductor, the barrier height  $\varphi_{Bp}$  is given by

$$\phi_{Bp} = Eg - (\phi_m - \chi) \tag{3.5}$$

Equation 3.4 is referred to as the Schottky-Mott Limit, and gives the limiting value for the barrier height in ideal metal-semiconductor contacts. In obtaining equation 3.4, a number of important assumptions have been made, specifically:

- a) The surface dipole contributions to  $\phi_m$  and  $\chi$  do not change when the metal and semiconductor are brought in contact with each other.

- b) There are no localized states on the surface of the semiconductor.

c) There is perfect contact between the metal and the semiconductor; i.e., there is no interfacial layer of any kind.

Figure 3.3 Energy Band Diagram of the Schottky contact

### 3.2.2 Bardeen Limit

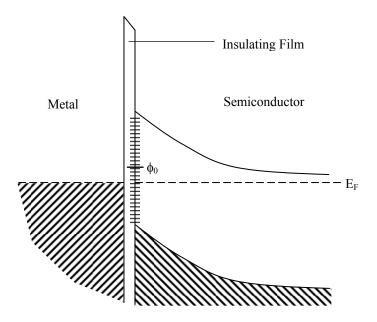

The Schottky-Mott theory suggests that the barrier height,  $\phi_B$ , is strictly a function of the metal work function and the electron affinity of the semiconductor. However, it is practically found that the barrier height is a less sensitive function of  $\phi_m$  and in some circumstances is almost independent of  $\phi_m$ . An explanation of this was put forward by Bardeen in 1947, who suggested that the discrepancy may be due to the effect of surface states. Figure 3.4 illustrates a Schottky contact with the presence of a thin interfacial layer, and a continuous distribution of surface states at the interface.

Figure 3.4 Metal-Semiconductor contact with surface states.

The occupancy of the surface states is determined by the Fermi level. If the neutral level  $\phi_0$  of the insulator is above the Fermi level  $E_F$ , the surface states contain a net positive charge. On the other hand, if  $\phi_0$  is below  $E_F$ , then the surface states have a net negative charge. The surface states behave like a negative feedback loop, the error signal of which is the deviation of  $\phi_0$  from  $E_F$ . If the density of surface states becomes very large, the error signal will be very small and  $\phi_0 \approx E_F$ . In this case, the density of surface states is large enough to accommodate any additional surface charges without appreciably altering  $E_F$ . As a result, the barrier height is determined by the property of the barrier height is said to be "pinned" by the high density of the surface states. This is called the Bardeen Limit. Effectively, when the Bardeen Limit is reached, the surface states screen the semiconductor from the electric field in the insulating layer so that the charge in the depletion region and the barrier height are independent of the metal work function  $\phi_m$ . The Bardeen Limit is given by:

$$\phi_B = E_g - \phi_0 \tag{3.6}$$

The Schottky-Mott Limit and the Bardeen Limit are the two limiting cases of the barrier height,  $\phi_b$ , for a metal-semiconductor contact. Usually the actual Schottky Barrier Height falls somewhere between the Schottky-Mott Limit and the Bardeen Limit. In SiC, there is no Fermi-level pinning, thus the SBH is metal work function dependent [10].

# 3.3 Current Transport Mechanisms

The current transport mechanisms which determine the conduction in the Schottky contact are discussed in this section. The ways in which electrons can be transported from the semiconductor across the barrier into the metal are:

- a) Emission of electrons over the top of the barrier.

- b) Quantum-mechanical tunneling through the barrier.

- c) Electron-hole recombination in the space-charge region.

- d) Electron-hole recombination in the neutral region of the semiconductor.

Figure 3.5 Current transport mechanisms in a forward-biased Schottky Barrier.

#### 3.3.1 Electron Emission over the Barrier

The flow of electrons from the semiconductor to the metal is mainly governed by two processes. First, the electrons traverse the depletion region in the semiconductor near the metal under the influence of the drift and diffusion mechanisms. When they arrive at the metal/semiconductor interface, they are emitted into the metal across the boundary. The two processes are effectively in series and the current is predominantly controlled by the mechanism which offers the most obstruction to the flow of the electrons. According to the diffusion theory, the first process is the limiting factor, while the thermionicemission theory claims the second process is the limiting factor. The primary difference between the two theories is the behavior of the quasi-Fermi level in the semiconductor.

According to the diffusion theory, the quasi-Fermi level at the interface coincides with the Fermi level in the metal. When the electrons flowing in the semiconductor arrive at the interface, they are in thermal equilibrium with the conduction electrons in the metal. Thus, the concentration of the electrons on the semiconductor side is unaltered by the application of bias, and the transition of the quasi-Fermi level from the semiconductor bulk Fermi level,  $E_{Fs}$ , to the metal Fermi level,  $E_{Fm}$ , occurs in the depletion region.

The thermionic-emission theory postulates that the quasi-Fermi level at the interface is not coincident with the Fermi level of the metal, and remains constant throughout the depletion region at  $E_{Fs}$ , similar to a p-n junction. Therefore, the electrons emitted from the semiconductor are not in thermal equilibrium with the conduction electrons in the metal, but have an energy which equals the sum of the Fermi energy of

the metal and the barrier height. These are referred to as "hot electrons". When these hot electrons penetrate into the metal, they lose energy by collisions with the conduction electrons and eventually become in equilibrium with them. This indicates that the quasi-Fermi level falls in the metal until it coincides with the metal Fermi level.

Figure 3.6 Electron quasi-Fermi level in a forward-biased Schottky barrier

Thus, even though the gradient of the quasi-Fermi level is ultimately the driving force for electrons, the diffusion theory claims that the gradient occurs in the depletion region, while the thermionic-emission theory claims that it occurs in the metal. The diffusion theory attributes the main obstacle to the current flow to be the combined effects of drift and diffusion, while the thermionic-emission theory attributes the main obstacle to the current flow to the process of thermionic emission of electrons into the metal. In practice however, the true behavior of the current transport lies somewhere between the two extremes of the diffusion theory and the thermionic emission theory.

# 3.3.2 Quantum-mechanical tunneling through the barrier

Under certain circumstances, it may be possible for electrons with energies below the top of the barrier to penetrate the barrier through quantum-mechanical tunneling. In the case of degenerate semiconductors at low temperature, current may arise from tunneling of electrons close to the Fermi level. This is called "field emission". Field emission is of considerable importance for ohmic contacts. Ohmic contacts usually consist of Schottky barriers on very heavily doped material, which makes the depletion region so thin that field emission takes place and the contact has very low resistance.

As the temperature is increased, electrons are excited to higher energies and the tunneling probability increases since they face a thinner barrier. However, the number of excited electrons decreases rapidly with increasing energy. There will be an optimum energy at which the contribution of excited electrons to the current will be maximum. This is called "thermionic-field emission". If the temperature is further raised, more and more electrons will be energized to go over the top of the barrier, until a point is reached when the effect of tunneling as compared to the pure thermionic emission is negligible.

### 3.3.3 Electron-hole recombination in the space-charge region

The recombination in the depletion region normally takes place due to the localized states in the semiconductor. The localized states are often referred to as "traps" since they tend to capture minority carriers. The localized states are formed due to a number of reasons such as defects, surface states, dangling bonds, and impurities. These traps have an energy level associated with them, which is usually located in the forbidden energy gap. The most effective trap centres are those with energies lying near the center of the forbidden gap. The theory of current due to such recombination centers is similar to that for p-n junctions, and is predicted by the S-H-R (Shockley, Hall and Read) model. Recombination current is a common cause for non-ideal behavior in Schottky diodes. Such departures from ideal behavior are more pronounced at low voltage and low temperature conditions.

# 3.3.4 Hole Injection in the neutral region of semiconductor

When the height of the Schottky barrier is higher than half of the energy band gap, then the semiconductor region at and near the surface becomes p-type and contains a high-density of holes. The holes diffuse into the neutral region under the influence of forward bias and recombine with the electrons in the neutral region. If the hole concentration exceeds that of the electrons, then the surface is inverted and forms a p-n junction with the bulk. This effect is only noticeable in large barrier heights with weaklydoped semiconductors. Since SiC has a very low intrinsic carrier concentration and has a large bandgap, the hole injection is negligible in SiC devices.

#### 3.4 Ohmic Contacts

Ohmic contacts are contacts whose current-voltage (I-V) characteristics are determined by the resistivity of the semiconductor rather than the behavior of the actual metal-semiconductor contact. The essential criteria for this contact is that its resistance should be very small compared with the resistance of the semiconductor. Also, the contact itself should be both electrically and mechanically stable and should not inject minority carriers.

The fabrication of ohmic contacts more or less follows one of the following methods:

- a) An ohmic contact can be formed by finding a suitable metal-semiconductor combination which yields a negative barrier height or a positive barrier height, as shown in Fig. 3.2(b) and (c), that is so small that the contact can have a low enough resistance to be effectively ohmic.

- b) An ohmic contact can also be formed by having a heavily doped semiconductor immediately adjacent to the metal. Thus, the depletion region can be so thin that field emission is dominant enough for the contact to have a very low resistance

c) Crystal defects formed near a damaged surface of a semiconductor can act as efficient recombination centres. If the density of the defects is high enough, the recombination in the depletion region can become the dominant current conduction mechanism and will reduce the contact resistance significantly.

The most widely used of these methods is the second method. However, for SiC, the first method is preferred. It is generally difficult to make ohmic contacts on wide bandgap semiconductors like SiC as a metal does not exist with a work function low enough to yield a low barrier height. Since there aren't a lot of metal-SiC combinations available which naturally yield an ohmic contact, the common process is to create a Schottky contact and then modify the contact properties to reduce the Schottky barrier height enough to make it ohmic. The most commonly used method is to anneal certain metal-SiC contacts at the corresponding eutectic temperature in an inert gas to yield ohmic behavior. For example, Nickel/SiC contacts annealed at 1000°C corresponds to a barrier height of 0.38eV [11].

## **CHAPTER 4**

### FABRICATION OF METAL/4H-SIC SCHOTTKY DIODES

This primary aim of this project is to research the effect of thermal annealing on the parameters of Schottky diodes. The three metals used in this project for the Schottky contacts to SiC are Copper, Aluminum and Gold. The Schottky devices were fabricated on SiC substrates using an elaborate fabrication process. The Schottky devices are then annealed in a furnace for an appropriate time at an appropriate temperature. Electrical measurements were performed on the sample upon fabrication. These measurements will be presented and analyzed in detail in the next chapter. In this chapter, the entire fabrication procedure is presented in detail. The problems encountered and their solutions are discussed, which resulted in the development of a revised fabrication process. The annealing of ohmic and Schottky contacts is also discussed in detail in this chapter, and the schematics and temperature profiles of the furnace are presented to assist in the understanding of the process.

### 4.1 Basic Structure of Schottky Diode

A Schottky diode consists of a metal-semiconductor junction as compared to a semiconductor-semiconductor junction in p-n diodes. The metal is the anode terminal of the diode while the semiconductor substrate is the cathode. An ohmic contact is made to the substrate to provide the cathode terminal. To form a good ohmic contact, a substrate with high doping concentration is preferred. On the other hand, a good Schottky contact requires a substrate with moderate doping concentration. Hence, a highly-doped substrate with an loe to moderately doped epitaxial layer is often preferred for creating Schottky diodes.

The basic structure of a typical SiC Schottky diode is shown in Fig 4.1. The Schottky contacts are formed on the epitaxial layer (also known as epilayer). The side of substrate on which the Schottky contacts are deposited will be called as the Front-side. Ohmic contacts are formed on the other side of the substrate, which is also called as the Back-side. Since Schottky diodes are majority-carrier devices, n-type substrates are preferred since electron-mobility is usually higher than hole-mobility in semiconductors.

Figure 4.1 Basic Structure of a Schottky Diode

## 4.2 Materials and Resources Used

In this project, the substrates used were n-type 4H-SiC with Si-face purchased from Cree, Inc. The SiC die used were from a 1.5-inch wafer with 0.3375mm thickness cut into 6mm squares. The bulk doping concentration was on the order of  $10^{18}$  cm<sup>-3</sup>. The epilayer had a thickness of 5-10µm with a doping concentration on the order of  $10^{15}$  cm<sup>-3</sup>.

The Schottky diodes were fabricated at the Microstructures Laboratory in the Milton W. Holcombe Department of Electrical and Computer Engineering, Clemson University. The wet chemical processes were performed in a Class-100 cleanroom. The thermal evaporations were performed using a thermal evaporator made by Edwards Vacuum Ltd. The annealing steps were performed in a Thermo Products Ltd. Mini-Brute furnace. Post fabrication, the I-V measurements were taken with a Hewlett-Packard 4156B Precision Semiconductor Parametric Analyzer and the C-V measurements were taken using a Deep Level Transient Spectrometer from Sula Technologies. For surface characterization, X-ray Photoelectron Spectroscopy was performed using a XPS-KRATOS AXIS 165.

## 4.3 Preceding Procedure for Fabrication of Schottky Diode

The fabrication of a Schottky diode involves an elaborate procedure including surface treatment, thermal evaporation, and annealing. Since the metal-semiconductor interface is the most critical aspect of a Schottky diode, the fabrication processes used plays an important role in determining the Schottky parameters of the diode. Typical processes use surface treatments for etching the surface oxide and any other surface contaminants present on the semiconductor substrate, followed by thermal evaporations to deposit the Schottky and ohmic contacts. Annealing is performed at suitable stages for either obtaining ohmic behavior on the back-side contacts or improving the Schottky parameters of the front-side contacts. Prior research done by this group at Clemson University utilized a procedure which is reviewed in the following sub-sections [12], [13].

# 4.3.1 Initial Degrease and Back-side Surface Etch

The substrates used in fabricating these Schottky diodes were 6mm square die obtained from a 1.5-inch n-type 4H-SiC wafer with Si face. In factory-sealed condition, the SiC die were attached to a plastic pellicle with an adhesive, with a plastic layer on top to prevent exposure to atmosphere. As a result, the first logical step was to put the SiC substrate through a surface clean to remove any contaminants from the packaging. Also, before proceeding to deposit any metal contacts on the substrate, any oxide on the

- 1) The sample was degreased by immersion in Acetone for 2 minutes followed by immersion in Methanol for 2 minutes.

- 2) The sample was then immersed in a solution of diluted Hydrofluoric Acid (48% HF) and water in the volumetric ratio 1:25 HF:H<sub>2</sub>O for 2 minutes.

- 3) The sample was rinsed in three beakers of de-ionized (DI) water for a period of 15 seconds, 30 seconds and 5 minutes respectively.

- 4) The sample was blow-dried with a Nitrogen gun.

During the degreasing of the sample with Acetone and Methanol, care was taken to flip the sample upside-down halfway during each step to make sure that each surface received equal exposure to the Acetone and Methanol. However, during the etching of the sample with HF, the sample was placed with the back-side facing up so that the backside received the most exposure to the acid. The reason for this was since the next step was to deposit the Nickel contacts on the back-side, more emphasis was given to cleaning the back surface.

#### 4.3.2 Deposition of Nickel on the Back-side

Nickel is widely used as an ohmic electrode to n-type 4H-SiC and 6H-SiC [14]. The choice of Nickel as the metal for creating ohmic contacts is elaborated in the next sub-section. In creating the ohmic contacts, approximately 1700Å of Nickel was deposited by thermal evaporation on the back-side of the sample. The thermal evaporation was performed at a pressure of 5 x  $10^{-6}$  Torr to minimize contamination. During the evaporation, the sample rests on top of a suitable shadow mask so that the Nickel is deposited in the desired pattern. The pattern used for depositing the Nickel dots is shown in Fig. 4.2. Ideally the ohmic contact should cover a large portion of the back-side of the sample. However, this particular pattern was chosen because it provides two physically separated Nickel dots. The separate dots are useful in testing the resistance of the ohmic contacts at a later stage. The measurement will be discussed in greater detail in Chapter 5.

Figure 4.2 Pattern of Ohmic contacts on the back-side of 4H-SiC sample.

# 4.3.3 Annealing of Nickel to make Ohmic contacts

As discussed in Chapter 3, the most popular method of formation of ohmic contacts to SiC is to modify a Schottky contact to make it ohmic in behavior. This approach was employed in this project by annealing the Nickel contact for a suitable time and at a suitable temperature to make it ohmic. In the previous section, it was mentioned that Nickel was the metal of choice as an ohmic electrode for n-type 4H-SiC and 6H-SiC. The reason for the choice of Nickel is that Nickel forms an excellent ohmic contact with SiC after annealing [11], [14-16]. During the annealing, formation of a Ni<sub>2</sub>Si phase occurs in a large temperature range between 600°C and 950°C [16]. However, below 900°C-950°C a rectifying behavior is observed [11], [16]. To obtain the lowest contact resistivity, the optimum condition for annealing Nickel ohmic contacts is approximately 1000°C for 3 minutes [15]. The specific contact resistivity of such a contact is reported to be in the range of  $10^{-6} \Omega \text{ cm}^2$  [14].

The as-deposited Nickel contacts were annealed in a Mini-Brute furnace at  $1000^{\circ}$ C for 3 minutes under an inert atmosphere consisting of a mixture of 10% Hydrogen and 90% Argon (Forming Gas). Annealing in an Argon environment reduces structural defects as the Argon atoms penetrate the material and occupy the interstitial vacancies, thereby reducing stress. The addition of H<sub>2</sub> leads to the saturation of the dangling bonds at the surface, thus reducing leakage current [17].

Figure 4.3 shows a detailed schematic of the furnace tube is shown along with the temperatures at various points during the annealing and the time intervals for which the sample was let sit at each point. The Mini-Brute furnace mainly consists of a quartz furnace tube surrounded by heating coils. The quartz tube is held in place with the help of white insulation pads at the front and back end of the furnace and thus is physically separated from the heating coils. The heating coils are arranged in three separate zones; front, center and rear. The center heating coils are heated to the desired temperature, while the front and the rear heating coils are adjusted relative to the center heating coils to compensate for the heat loss at either ends of the furnace tube, thus creating a uniform temperature in the center of the furnace. The forming gas is injected into the furnace tube through the front mouth. Before insertion, the sample is placed on a quartz boat, which can be pushed into and pulled out of the furnace tube with the help of a quartz rod.

For the sake of convenience, the length of the furnace tube is considered to be divided into four regions:

- 1) The Rear Hot Zone (upstream of the forming gas flow).

- 2) The Center Hot Zone.

- 3) The Front Hot Zone (downstream of the forming gas flow).

- 4) The White Insulation located at the front (near the mouth of the tube).

The placement of the sample during insertion, annealing, and extraction are discussed in terms of there four regions or zones. Figure 4.3 shows the placement of the sample relative to these zones for annealing Nickel at 1000°C along with the time intervals for which the sample sits at a particular point along with the temperature at that point.

The detailed annealing process is explained below:

- 1) Before starting the annealing process, sufficient time was allowed for the furnace to stabilize at 1000°C.

- 2) The forming gas flow was started at 30 s.c.c.h. and let flow for 3 minutes to purge the entire furnace quartz tube of any contaminant gases.

- 3) The sample was placed with the back-side facing up on a quartz boat before inserting it into the furnace. The sample was inserted slowly into the center of the furnace in the following steps to reduce thermal stress:

- a) The sample was placed at the edge of the furnace tube for 30 seconds then pushed further ahead.

- b) The sample was placed at the center of the tube holder (white insulation isolating the quartz tube from the furnace body), for 60 seconds then pushed further ahead in the center.

- c) The sample was pushed all the way into the middle of the center hot zone.

- 4) The sample was placed at the center of the furnace for 3 minutes, which is defined as the actual annealing time.

- 5) The sample was slowly pulled out of the furnace in the following steps to reduce the thermal stress and also reduce the risk of oxidation of the Nickel dots.

- a) The sample was placed for 1 minute at the boundary between the center hot zone and front hot zone then pulled further back.

- b) The sample was placed for 2 minutes at the center of the front hot zone then pulled further back.

- c) The sample was placed at the center of the white insulation for 30 minutes to cool down. Finally, the sample was completely pulled out of the furnace.

The annealing of Nickel at such temperatures leads to the formation of Nickel Silicide (Ni<sub>2</sub>Si) at the interface. However, the Nickel dots still exhibit rectifying behavior for annealing temperatures below 900°C. Annealing of SiC above 900°C results in the out diffusion of a large number of free Carbon atoms towards the surface. This out-diffusion of Carbon atoms is supposed to be the reason for the ohmic behavior of annealed Nickel contacts on SiC [11].

It was observed frequently that the Nickel dots were darkened in varying degrees after annealing. This was attributed to oxidation of Nickel during the annealing process. A layer of oxide covered the surface of the Nickel dots, which could result in problems during the measurements by preventing good electrical contact of the measurement probes with the ohmic contacts. The most obvious cause was the mouth of the furnace tube being open during the annealing process, which could easily allow the inflow of atmospheric gases into the furnace tube. Even though the forming gas continuously flowed throughout the annealing process, there was no absolute control over the ambience in the furnace tube. Also, during the cooling off period of 30 minutes, the sample was located over the white insulation region where the temperature was recorded as approximately 678°C. This white insulation region is very close to the mouth of furnace tube and hence, the sample has higher risk of oxidation in this region. Ideally, the mouth of the furnace should be closed completely with an end-cap containing a small outlet tube for the forming gas. Also, during the cooling period, the sample should be rested in a cooler region with a neutral ambience. This suggests the use of an extension tube to the furnace whereby the sample can rest in a much cooler place and still be in the of the forming gas. Since neither the end-cap nor the extension tube was available, a work-around was developed to reduce the risk of oxidation. An end-cap was designed using Aluminum foil which could be wrapped around the mouth of the furnace tube with a small opening in it for the push-rod. This significantly reduced the risk of oxidation; however, a more robust solution was required.

### 4.3.4 Deposition of Protective Layer on the Back-side

After the annealing of the back-side contacts to make them ohmic, the next goal is to deposit Schottky contacts on the front-side. Prior work done on this project has revealed that at this stage of fabrication, there is significant oxide present on the frontside [12]. The presence of an oxide layer presents an undesirable effect on the Schottky barrier and hence, additional surface treatment is recommended. Hydrofluoric Acid (HF) is widely considered to be one of the best etchants for Silicon Dioxide (SiO<sub>2</sub>) and was used for the second surface etch. However, HF is also a known etchant of Nickel. Therefore, it was imperative that the Nickel contacts be protected during the HF etch.

A protective coating of Aluminum was deposited over the back-side contacts to protect them from getting etched during the second surface etch. A 0.5µm thick layer of Aluminum was thermally evaporated onto the back-side with an appropriate shadow mask pattern such that both the Nickel dots were completely blanketed by the Aluminum layer. The sample was then allowed to rest for 24 hours to improve the adhesion of Aluminum to the surface.

## 4.3.5 Second Degrease and Front-side Surface Etch

The second surface treatment was similar to the first surface clean, with some suitable changes in etch time to make sure that the Nickel dots on the back-side are not affected. The procedure for the second surface clean is listed in detail:

- 1) The sample was degreased by immersion in Acetone for 2 minutes followed by immersion in Methanol for 2 minutes.

- 2) The sample was immersed in a solution of diluted Hydrofluoric Acid (48% HF) and water in the volumetric ratio of 1:25 HF:H<sub>2</sub>O for 45 seconds.

- 3) The sample was rinsed in three beakers of de-ionized (DI) water for a period of 15 seconds, 30 seconds and 5 minutes respectively.

- 4) The sample was dried with a Nitrogen gun.

The second surface etch with a dilute solution of HF was significantly shorter than the first surface etch. The sample was immersed in HF for only 45 seconds during the second surface etch as compared to 2 minutes during the first surface etch. This was done to reduce the etching of the Aluminum protective layer by HF. Although Aluminum is deposited as the protective layer, it was observed that it still gets etched slowly by the HF. This etching of Aluminum is particularly fast over the Nickel dots, indicating that the Aluminum does not adhere particularly well to the Nickel.

# 4.3.6 Deposition of Schottky contacts on the Front-side

After the second surface clean, Schottky contacts were deposited on the frontside. Since the project involved investigating different metals for Schottky diodes, the fabrication process is not discussed relative to any particular Schottky metal, but rather as a general process which can be employed with suitable changes for the different metals. The deposition of Schottky contacts is also discussed in general because the same evaporator was used in the case of all metals.

The Schottky contacts were deposited on the front-side by thermal evaporation performed under high-vacuum of  $5 \times 10^{-6}$  Torr. The deposited Schottky dots were roughly 630µm in diameter and 0.5µm thick. Figure 4.4 exhibits the pattern of dots deposited on the front-side by the use of a suitable shadow mask. The pattern consists of 14 dots arranged in four separate rows, thereby yielding 14 Schottky diodes on one die.

Figure 4.4 Pattern of Schottky contacts on the Front-side of the sample.

### 4.3.7 Removal of Protective Layer

The final step of the fabrication process is to remove the remnant of the Aluminum layer covering the back side so that the ohmic Nickel dots can be exposed for measurement purposes. Aluminum can be easily etched away with Potassium Hydroxide (KOH) without adversely affecting the Nickel contacts. However, the same cannot be said about the effect of KOH on the Schottky contacts. Along with Aluminum, KOH also readily attacks Copper. Therefore, a similar protective approach must be employed while removing the Aluminum layer to keep the Schottky contacts intact. To achieve this, the front-side of the sample was coated with nail paint and dried for at least 60 minutes. This dried nail paint thus forms a protective layer over the Schottky contacts, protecting them from the consecutive chemical treatments. The elaborate method for removing the Aluminum protective layer is listed below:

- 1) Apply an even coating of nail paint on the front-side of the sample, taking care not to spill any nail paint on the back-side of the sample. Let the sample sit for at least 60 minutes for the nail paint to dry completely before proceeding.

- 2) Immerse the sample in Potassium Hydroxide (KOH) with the back-side facing up. Let the sample sit in KOH for ample time to ensure complete etching of Aluminum from the back-side.

- 3) Immerse the sample in Acetone with the front-side facing up. Let the sample sit in Acetone for ample time to ensure complete removal of nail paint from the front-side.

- 4) The sample was rinsed in three beakers of de-ionized (DI) water for a period of 15 seconds, 30 seconds and 5 minutes respectively.

- 5) The sample was dried with a Nitrogen gun.

After the completion of this final step, the Schottky diode is ready for electrical measurement. The sample was stored in an airtight container for handling and moving.

# 4.4 Shortcomings of the Preceding Fabrication Process

The fabrication process highlighted in the previous section was successfully employed in fabricating Schottky diodes on 4H-SiC. However, there were some shortcomings in the process which caused problems during the fabrication process. As such, successful repeatability of the process could not be guaranteed. Listed below are the encountered problems in detail. The probable causes of and possible solutions to the problems are also discussed.

- 1) During the second front-side surface etch, the back-side Aluminum protective layer gets etched away by HF. This etching is particularly noticeable right over the Nickel dots, indicating that Aluminum does not adhere well to Nickel. Consequently, the annealed Nickel dots are exposed to the HF and hence get etched away. Since ohmic contacts are essential to provide an electrode to the substrate, even partial etching of the dots gives significant problems during electrical measurements. Also, the choice of Aluminum as the protective material is not the best one. Efforts should be made to find a better protective material which resists etching by HF.

- 2) During the removal of Aluminum covering the back-side by KOH, it is necessary to protect the front-side Schottky contacts from KOH. This requires coating of the front-side with nail paint. This is an additional step introduced in the process, which could probably be avoided. The Aluminum coating could be stripped with a different chemical which doesn't chemically affect the front-side Schottky contacts. Also, a material other than Aluminum could be used to protect the back-side contacts. The chief requirements for such a material should be resistance to the HF etch, while also is easily removable by a chemical which doesn't affect any of the Schottky metals used.

- 3) It was observed that during the stripping of Aluminum with KOH, the nail paint coating had a tendency of getting detached from the front-side of the sample, thereby exposing the Schottky contacts to the KOH. Also, sometimes the Schottky contacts come loose along with the nail paint coating. This was mostly observed in the case of Copper, which has poor adhesion with the surface anyhow. The probable cause of this was that the nail paint was not allowed to dry completely before proceeding with immersion in KOH. The most logical solution was to let the sample sit for 24 hours before proceeding with the removal of the Aluminum layer on back-side with KOH.

- 4) One of the most vital concerns with the use of nail paint was the matter of its composition. The nail paint used in the fabrication process was not an electronic grade material and there was no strict control of its composition since different manufacturers use different compositions. Also, colored nail paint consists of suspended metal flakes, which is highly undesirable from a contamination perspective. Therefore, clear nail paint is preferred over the colored nail paint.

After reviewing the shortcomings in the above process, the most preferable solution was to substitute another material for Aluminum as the back-side protective layer. The requisites for this material were as follows:

- 1) The material should be strongly resistant to HF.

- 2) The material should be removable by a chemical which does not adversely affect any of the Schottky metals or the Nickel contacts.

- 3) The material should be an electronic grade material with high purity.