# Clemson University **TigerPrints**

Clemson Patents

1-29-2013

# Impedance-based arc fault determination device (IADD) and method

Edward Randolph Collins

Timothy Lee Smith

Randall J. Emanuel

Follow this and additional works at: https://tigerprints.clemson.edu/clemson patents

# Recommended Citation

Collins, Edward Randolph; Smith, Timothy Lee; and Emanuel, Randall J., "Impedance-based arc fault determination device (IADD) and method" (2013). Clemson Patents. 310.

$https://tigerprints.clemson.edu/clemson\_patents/310$

This Patent is brought to you for free and open access by TigerPrints. It has been accepted for inclusion in Clemson Patents by an authorized administrator of TigerPrints. For more information, please contact kokeefe@clemson.edu.

US008362789B2

US 8,362,789 B2

\*Jan. 29, 2013

# (12) United States Patent

Collins, Jr. et al.

# (54) IMPEDANCE-BASED ARC FAULT DETERMINATION DEVICE (IADD) AND METHOD

(75) Inventors: Edward Randolph Collins, Jr., Seneca,

SC (US); Timothy Lee Smith, Seneca,

SC (US); Randall J. Emanuel,

Charlotte, NC (US)

(73) Assignees: Clemson University Research

Foundation, Clemson, SC (US); Duke Energy Carolina, LLC, Charlotte, NC

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 12/573,084

(22) Filed: Oct. 2, 2009

## (65) Prior Publication Data

US 2010/0026317 A1 Feb. 4, 2010

### Related U.S. Application Data

- (63) Continuation of application No. 11/838,831, filed on Aug. 14, 2007, now Pat. No. 7,598,751.

- (60) Provisional application No. 60/837,537, filed on Aug. 14, 2006.

- (51) Int. Cl. G01R 27/28 (2006.01) H02H 3/00 (2006.01)

- (52) **U.S. Cl.** ...... **324/649**; 324/650; 361/79

See application file for complete search history.

# (56) References Cited

(10) **Patent No.:**

(45) Date of Patent:

### U.S. PATENT DOCUMENTS

| 3,976,868 A * | 8/1976  | Lane 703/4             |

|---------------|---------|------------------------|

| 4,192,981 A * |         | Barkan et al 218/118   |

| 4,517,513 A   | 5/1985  | Brown                  |

| 5,541,498 A * | 7/1996  | Beckwith 323/211       |

| 6,449,568 B1  | 9/2002  | Gerrish                |

| 6,466,031 B1  | 10/2002 | Hu                     |

| 6,778,921 B2* | 8/2004  | Keane et al 702/62     |

| 7,002,321 B2* | 2/2006  | McDaniel et al 323/211 |

| 7,164,275 B2  | 1/2007  | Gasperi                |

| 7,200,500 B2* | 4/2007  | Larsson et al 702/64   |

| 7,526,392 B2  | 4/2009  | Gasperi                |

| 7,603,203 B2* | 10/2009 | Zhang et al 700/295    |

# OTHER PUBLICATIONS

Gasperi, et al., "Method for AC Powerline Impedance Measurement," IEEE pp. 1-4 2007.

Arc Flash Hazard Analysis and Mitigation (Christopher Inshaw and Robert Wilson: 20 pgs.) Dated: Oct. 20, 2004

Robert Wilson; 20 pgs.). Dated: Oct. 20, 2004. ARCPRO The Industry Standard Software for Arc Hazard Assessment and Protective Clothing Selection (2 pgs.). Dated: Dec. 12, 2007.

Frequency Control Concerns in The North American Electric Power System (B.J. Kirby, J. Dyer, C. Martinez, Sr, Rhamat Shoureshi, R. Guttromson, and J. Dagle; 27 pgs.). Dated: Dec. 2002.

(Continued)

Primary Examiner — Jeff Natalini (74) Attorney, Agent, or Firm — Ballard Spahr LLP

# (57) ABSTRACT

Embodiments according to the present invention provide an Impedance-based Arc-Fault Determination Device (IADD) and method that, when attached to an electrical node on the power system and through observations on voltage, current and phase shift with a step load change, determine the effective Thevenin equivalent circuit or Norton equivalent circuit at the point of test. The device and method determine the expected bolted fault current at the test location of interest, which enables calculation of incident energy and the assignment of a flash-hazard risk category.

#### 39 Claims, 35 Drawing Sheets

# OTHER PUBLICATIONS

IEEE Standard 1584a IEEE Guide for Performing Arc-Flash Hazard Calculations—Amendment 1 (IEEE Industry Applications Society; 9 pgs.). Dated: Nov. 29, 2004.

Occupational Related Injuries in the United States, 1992-1998, and Recommendations for Safety Research (James C. Cawley, Gerald T. Homce; 8 pgs.). Dated: Aug. 2003.

Preventing Arc-Flash Incidents in the Workplace (George Gregory, published in EC&M Magazine; 4 pgs.). Dated: Jun. 2003.

The Other Electrical Hazard: Electric Arc Blast Burns (Ralph H. Lee, published by IEEE; 6 pgs.). Dated: 1982.

Impedance, Short Circuit Currents, and Voltage Distortion (Application Notes from Controlled Power Company; 2 pgs.). Dated: Apr. 6, 1998.

Understanding and Reducing Art Flash Hazards (Littlefue POWR-GARD Products; 8 pgs. ) Dated: Undated document.

Using a Microprocessor-Based Instrument to Predict the Incident

Using a Microprocessor-Based Instrument to Predict the Incident Energy From Arc-Flash Hazards (Thomas L Baldwin, Michael J. Hittel, Lynn F. Saunders, and Frank Renovich, Jr., published by IEEE; 10 pgs.). Dated: May/Jun. 2004.

Using the General Duty Clause 5(a)(1) (No author listed, 4 pgs.). Dated: Undated document.

\* cited by examiner

FIG. 1A

FIG. 1B

Impedance Domain

FIG. 4B

FIG. 6

FIG. 8B

FIG. 19

FIG. 22

FIG. 32

FIG. 33

**FIG. 36A**

**FIG. 36B**

FIG. 36C

FIG. 37

FIG. 39

# IMPEDANCE-BASED ARC FAULT DETERMINATION DEVICE (IADD) AND METHOD

# CROSS REFERENCE TO RELATED PATENT APPLICATIONS

This application is a continuation of U.S. application Ser. No. 11/838,831 filed Aug. 14, 2007, now U.S. Pat. No. 7,598, 751 which claims benefit of the filing date of U.S. Provisional Application No. 60/837,537 filed Aug. 14, 2006, each of which are herein incorporated in their entirety by this reference.

## **BACKGROUND**

Between five and 10 times a day, an arc flash explosion occurs in electric equipment in the United States that sends a burn victim to a special burn center, according to statistics compiled by CapSchell, Inc., a Chicago-based research and 20 consulting firm that specializes in preventing workplace injuries and deaths.

In response to these statistics and the obvious detrimental affects of arc fault incidents on workers, in the United States the Occupational Safety and Health Administration (OSHA) 25 has begun enforcing recommendations by the National Electric Code (NEC) and National Fire Protection Association (NFPA) regarding employee safety procedures when work on energized systems must be performed. Admittedly, it is preferable and mandated that, when possible and practical, electrical systems are to be worked on in a zero energy state (ZES). However, this condition does not exist under all circumstances and sometimes work on energized systems is necessary.

The 2000 release of the NFPA's 70E document, incorporated herein by reference, recommended the use of personal protective equipment (PPE) based on the potential for exposure to heat energy radiated by electric arcs. NFPA 70E specifies the need for proper personal protective equipment (PPE), in all conditions where there is a possibility of harm induced 40 due to electrical arcing. Previously, electric shock was thought to be the primary and most frequent type of injury sustained when working with electrical systems. A recent study conducted by the National Institute for Occupational Safety and Health on injuries sustained during work with 45 electrical components points to the fact that a significant portion, approximately 40 percent, of these injuries were due to arc flash; an arc flash exposure may result in severe burns to the skin and, in some cases, death.

Burns are sustained due to exposure to a heat source, in this case the heat radiated from an electrical arc. Arcs have temperatures of around 35,000 degrees F. (19500° C.). Distance plays a role in the degree to which injury is sustained. The amount of energy absorbed by the skin at any given time is a function of the temperature of the heat source and the distance from this source to exposed skin. In this case, incident energy is typically calculated in cal/cm². An energy density of 1.2 cal/cm² is sufficient exposure to result in second degree burns on exposed human skin.

In 2002, the NEC 70-2002 document, incorporated herein 60 by reference, further expanded on this requirement by mandating that all electrical services that can be accessed while energized be labeled with the hazard category as defined by the NFPA. However, neither document has yet to specify the method by which these values are to be calculated. In 65 response to this fact, the Institute of Electrical and Electronic Engineers (IEEE), in 2004, issued Standard 1584, fully incor-

2

porated herein by reference and made a part hereof. IEEE 1584 gives the electric power industry a way to gauge arcflash hazards. It lets designers and facility operators determine arc-flash hazard distance and how much incident energy employees might be exposed to when they work on or near electrical equipment. These calculations form the basis for re-engineering systems to reduce incident energy to manageable levels or to provide guidance for the appropriate level of personal protective equipment (PPE) to be worn while working on or near energized equipment.

As stated previously, the NFPA 70E document requires calculation of arc fault incident energy but neither provides or specifies any one method of determining this value. Several methods of determining arc fault incident energy have been proposed and are acceptable methods, as defined by the NFPA. These methods include the IEEE 1584, NFPA 70E, Lee's Calculation, ARCPRO by Kinetrics of Toronto, and the Duke Heat Flux Calculator, by Duke Energy. The IEEE Standard, Duke Heat Flux, and NFPA 70E use equations developed from empirical testing, while the Lee paper and ARCPRO use equations based on theoretical analysis.

Article 130 of the NFPA 70E document, incorporated herein by reference, details the requirements for establishment of boundaries for safe working under live circuit conditions.

The IEEE 1584 standard is only one of several methods of calculating potential arc fault incident energy, but is widely used in the industry. The variables used in the IEEE calculations can be readily obtained with some knowledge of enclosure geometry, wire spacing, and fault duty; also, the IEEE standard has been tested and validated for a wide range of conditions. It specifies that the Lee equations should be used for voltages above 15 kV. The calculations consider threephase arcs in enclosures and in air. The standard is applicable for input ranges for voltage of 208 to 15,000 volts, bolted fault current of 700 A to 106 kA, equipment enclosures of commonly available sizes, and gaps between conductors of 13 mm to 152 mm (0.5 to 6 inches). The equations were developed from curve fitting of results of values measured from testing performed by the standard's working group. Several general conclusions resulting from their testing were found. System X/R (reactance/resistance) ratio, system frequency, and electrode material had little or no effect. Instead, the incident energy depends primarily on arc current. The buss gap (arc length) is only a small factor in the final result.

The IEEE 1584 standard outlines nine procedural steps in determining arc fault incident energy:

- 1. Collect the system and installation data

- 2. Determine the system modes of operation

- 3. Determine the bolted fault currents

- 4. Determine the arc fault currents

- 5. Find the protective device characteristics and duration of the arcs

- 6. Document the system voltages and classes of equipment

- 7. Select the working distances

- 8. Determine the incident energy for all equipment

- 9. Determine the flash-protection boundary for all equipment

The document states that by far, the majority of the work in completing an arc flash assessment is in the collection of system and installation data (step 1). This singular step is expected to account for fully one-half of all the effort in performing such a study. Obtaining the fault duty at a particular electric node can be difficult to determine. Often, wiring diagrams for electrical installations are outdated or lacking necessary information, such as wire size or feeder length, or the drawings may be incorrect all together. Rotating loads and

varying generation, particularly near the node of interest can also have major effects on fault duty and is time varying in nature. The majority of remaining analytical work is contained in steps 2 and 3.

Many entities are currently not compliant with OSHA <sup>5</sup> regulations concerning arc-flash assessments and documentation. Previously, OSHA has taken a lenient stand on this issue because methods for determining boundaries as defined the NFPA have only recently been developed. However, now that the IEEE 1584 standard has been accepted as a viable method of performing these assessments, OSHA has begun vigorously enforcing these requirements to better protect workers from this hazard.

By effectively skipping steps one and two of the nine step procedure outlined by the IEEE, a significant source of manpower, time and money can be eliminated from an arc flash assessment. The development of a method to reduce the effort required to reach these end results could radically impact the compliance issues now being faced by most industrial and commercial customers.

OSHA requires all electrical panels under its jurisdiction to be labeled to indicate the appropriate amount of PPE required while working inside of the panel with it energized. Currently, OSHA code requires that all employers make an effort to investigate the potential for injury due to arc flash; noncompliance with this directive may result in monetary penalties and liability in the event of an accident. This new requirement has prompted an influx in the awareness of the potential damage as a result of arc flash and consequently is forcing engineers to find ways to determine the appropriate level of protection required in each case. Companies may spend millions of dollars on arc flash assessment surveys and currently only a very limited number of entities are providing these assessments because of the high cost in manpower and time.

There exist few methods for establishing the potential for exposure to arc flash energy that are currently available. The classical method of obtaining fault current is to determine fault current capacity from information based on power system information.

$$I_{Fault-duty} = \frac{V_{Nominal}}{Z_{Service-Impedance}}$$

Typically the electric utility company that supplies a site with electrical power can give service impedance based on fault duty calculations and system models. IEEE 1584 specifies that "available fault data must be realistic; not conservatively high." The document goes further to offer the following 50 reasons for this requirement:

"Available bolted fault currents should be determined at the point of each potential fault. Do not use overly conservative bolted fault current values. A conservatively high value may result in lower calculated incident energy 55 than may actually be possible depending on the protective device's time-current curves. The lower results would be caused by using a faster time-current response value from the protective device's time-current curve."

Overestimating fault current can be dangerous for the 60 simple reason that protective devices often have an inverse or extremely inverse time curve. This means that the length of time before operation is inversely proportional to the amount of current flowing through the fuse. For example, using a fuse with a current rating of 200 A and an arc of 1 kA would blow 65 in 0.5 seconds whereas an arc of 500 A would blow in 9 seconds. The first condition results in a delivery of 500 A-s

4

(coulombs) of electric charge and the second results in an exposure of 4500 A-s of electric charge. Therefore, the likelihood of significant bodily injury due to incident energy exposure may be greater under the lower arc fault condition. Following this reasoning, conservatively high arc fault duty estimations may result in underestimating the potential for exposure to incident energy if protection curves are taken into account; protection data is one of the parameters taken into account in the IEEE 1584 calculations.

Another method of performing arc fault assessment include a detailed analysis of the system in conjunction with specialized computer software to simulate and make determinations of arc flash incident energy potential. To adequately complete such an analysis, an effective power system impedance is once again assumed at the service to the site of interest. This type of analysis goes a step further to include all wires sizes and lengths, protection equipment, and enclosure types for the system. This data can then be entered into the appropriate analysis program and results obtained. While this method is valid and has a high degree of accuracy, it tends to be time and labor intensive, leading to large costs for compliance. Also, in many cases, one-line diagrams for an industrial site are out-dated and do not contain modifications that have been completed over the years. Incorrect drawings may result in incorrect estimates on arc-fault potential due to errors in fault duty.

One recent paper has been presented in the IEEE Transactions on Power Systems that suggests an alternate method of obtaining bolted arc fault potential. "Using a Microprocessor-Based Instrument to Predict the Incident Energy From Arc-Flash Hazards" by Baldwin, Hittel, Saunders, and Renovich, suggests the application of current injection at varying frequencies to obtain impedance values; frequency modulation of the current signal quite accurately yields an X/R ratio and application of Ohm's Law will yield the impedance modulus. To obtain accurate results, current levels in the 30 amp range are specified to mitigate the effects of power system noise. This implies that a significant amount of power may be required, particularly on higher voltage systems.

Therefore, what is needed is a device and method that overcomes many of the challenges in the art, some of which are presented above.

# SUMMARY

Provided herein are embodiments of a device and method that can accurately and correctly predict the expected bolted fault current at the test location of interest. Embodiments of the device and method apply a known load and measure the change in RMS and instantaneous voltage due to the step increase in loading conditions and the phase shift in the voltage waveform as a result of the change in loading conditions at the test node. Subsequently, the load current is measured to more accurately determine the real time load imposed upon the system. With knowledge of the load impedance, an accurate equivalent Thevenin or Norton system along with resistive and reactive parameters and X/R ratio can be derived through a series of mathematical calculations. Then, using the derived equivalent circuit, an accurate estimate of the fault duty can be obtained.

One aspect describes a test device comprised of a load bank; voltage measurement circuitry and devices; current measurement circuitry and devices; relaying and switching devices; and data acquisition, measurement and control devices comprising at least one processor and a memory operably connected with said voltage measurement circuitry and devices, current measurement circuitry and devices, and

relaying and switching devices. The test device is configured to determine a first set of results comprised of at least a first voltage and first current and a first phase angle of an electrical node on an electrical power system and store the first set of results in the memory, operably connect the load bank to the selectrical power system at the electrical node using said switching devices and determine a second set of results comprised of at least a second voltage, second current and a second phase angle of said electrical power system at said electrical node, and retrieve the first set of results from the memory and compare the first set of results to the second set of results to determine at least one of an effective Thevenin equivalent circuit or Norton equivalent circuit for the electrical power system.

In another aspect the test device is further configured to 15 store the second set of results in the memory; operably disconnect the load bank from the electrical power system at the electrical node using the switching devices and determine a third set of results comprised of at least a third voltage, third current and a third phase angle of said electrical power system 20 at said electrical node, and retrieve either the first set of results or the second set of results from the memory and compare the third set of results to either the first set of results or the second set of results to determine an effective Thevenin equivalent circuit or Norton equivalent circuit for the electrical power 25 system.

In another aspect, the test device further configured to determine a bolted fault current at the electrical node from the effective Thevenin equivalent circuit or Norton equivalent circuit, determine one or more of resistive and reactive 30 parameters, or an X/R ratio at the electrical node from the effective Thevenin equivalent circuit or Norton equivalent circuit, determine fault incident energy available at the electrical node, and assign a hazard risk category based on the fault incident energy available at the electrical node, where 35 the hazard risk category is determined by the National Fire Protection Association (NFPA) 70E standard.

In another aspect, a testing method is disclosed. The testing method comprises determining a first set of results comprised of at least a first voltage, a first current and a first phase angle 40 of an electrical node on an electrical power system; connecting a load to the electrical power system at the electrical node; determining a second set of results comprised of at least a second voltage, a second current and a second phase angle of the electrical power system at the electrical node; disconnect- 45 ing the load bank from the electrical power system at the electrical node; determining a third set of results comprised of at least a third voltage, a third current and a third phase angle of the electrical power system at the electrical node from the third voltage and third current; and comparing the first set of 50 results to either the second set of results or the third set of results, or comparing the second set of results to the third set of results to determine at least one of an effective Thevenin equivalent circuit or Norton equivalent circuit for the electrical power system.

The testing method can in various embodiments further comprise determining a bolted fault current at the electrical node from the effective Thevenin equivalent circuit or Norton equivalent circuit; determine one or more of resistive and reactive parameters, or an X/R ratio at the electrical node 60 from the effective Thevenin equivalent circuit or Norton equivalent circuit; determining fault incident energy available at the electrical node; assigning a hazard risk category based on the fault incident energy available at the electrical node.

Another aspect according to the present invention comprises a computer program product for determining arc fault energy in an electrical power system. The computer program 6

product comprises at least one computer-readable storage medium having computer-readable program code portions stored therein, the computer-readable program code portions comprising a first executable portion for receiving a first set of results comprised of at least a first voltage, a first current and a first phase angle determined by the first executable portion from the first voltage and first current of an electrical node on an electrical power system; a second executable portion for receiving a second set of results comprised of at least a second voltage, a second current and a second phase angle determined by the second executable portion from the second voltage and second current of the electrical power system at the electrical node after connecting a load to the electrical power system at the electrical node; a third executable portion for receiving a third set of results comprised of at least a third voltage, a third current and a third phase angle determined by the third executable portion from the third voltage and third current of the electrical power system at the electrical node after disconnecting the load to the electrical power system at the electrical node; a fourth executable portion for comparing the first set of results to either the second set of results or the third set of results, or comparing the second set of results to the third set of results to determine at least one of an effective Thevenin equivalent circuit or Norton equivalent circuit for the electrical power system; and a fifth executable portion for determining a bolted fault current at the electrical node from the effective Thevenin equivalent circuit or Norton equivalent circuit and determining fault incident energy available at the electrical node.

In various aspects, the computer program product is further configured to determine one or more of resistive and reactive parameters, or an X/R ratio at the electrical node from the effective Thevenin equivalent circuit or Norton equivalent circuit; and assign a hazard risk category based on the fault incident energy available at the electrical node.

Additional advantages will be set forth in part in the description which follows or may be learned by practice. The advantages will be realized and attained by means of the elements and combinations particularly pointed out in the appended claims. It is to be understood that both the foregoing general description and the following detailed description are exemplary and explanatory only and are not restrictive, as claimed.

## BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings, not drawn to scale, which are incorporated in and constitute a part of this specification, illustrate embodiments and together with the description, serve to explain the principles of the methods and systems:

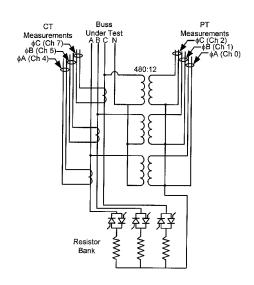

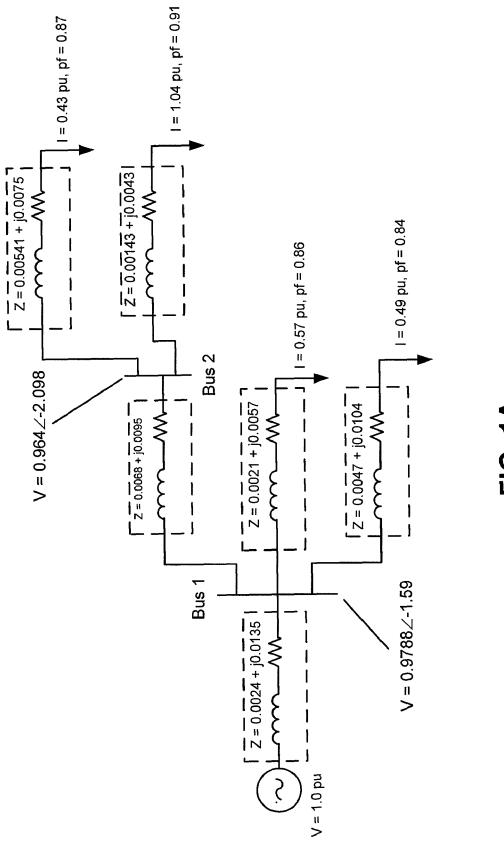

FIG. 1A shows a typical electrical system with a single point of generation and four loads drawing current with specified magnitude and power factor, and computed voltages at Busses 1 and 2;

FIG. 1B shows the addition of another load to FIG. 1A, in this case the addition of the IADD device at Buss 2, according to an embodiment of the present invention, that draws current at a unity power factor and effects both the voltage magnitude and phase angle at Busses 1 and 2;

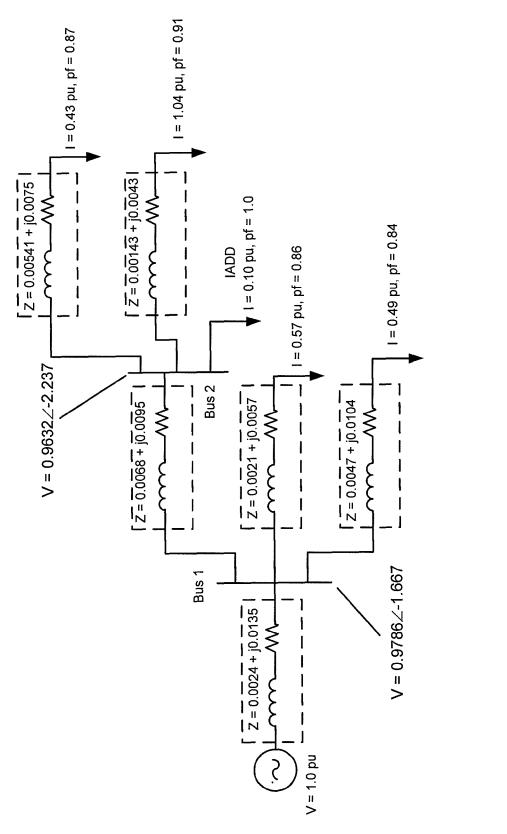

FIG. 2 schematically illustrates an embodiment according to the present invention;

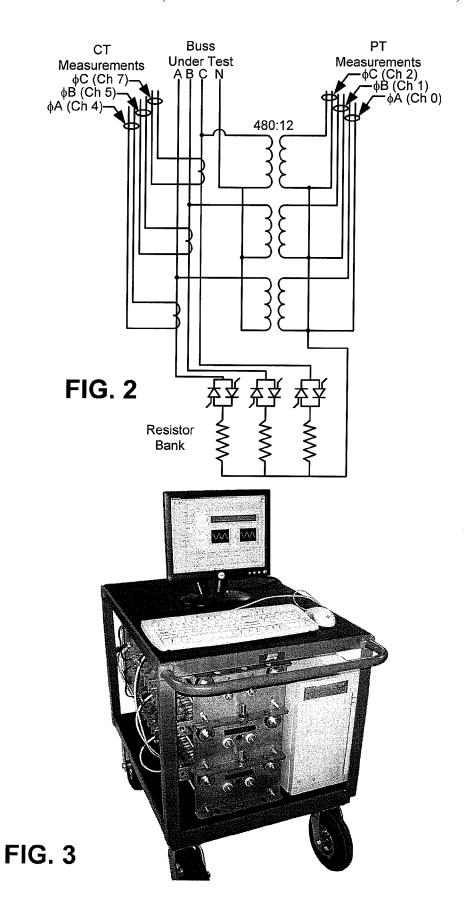

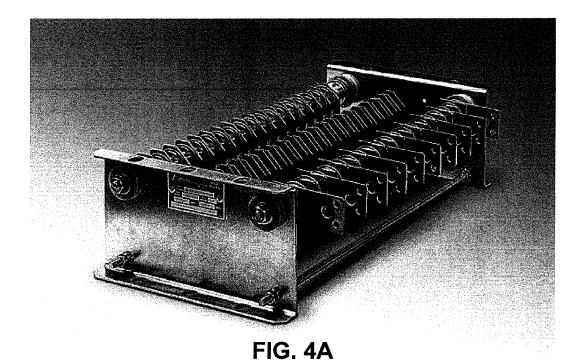

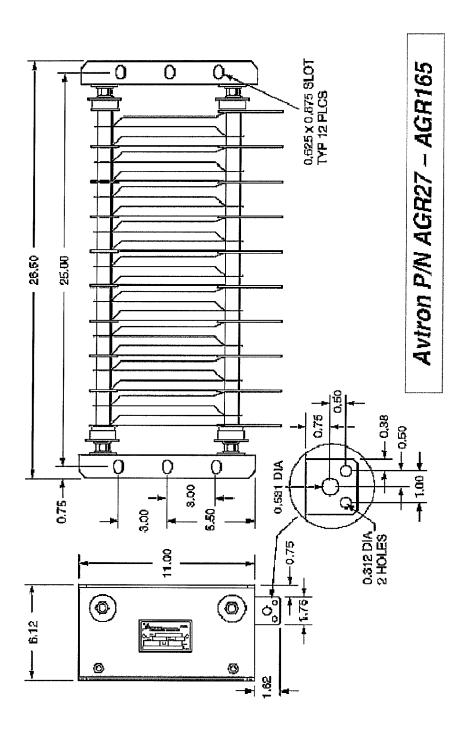

FIG. 3 illustrates an exemplary embodiment of an IADD; FIGS. 4A and 4B illustrate an exemplary resistive load bank that can be used in embodiments according to the present invention;

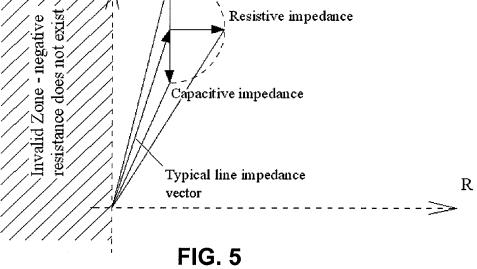

FIG. 5 is an impedance diagram illustrating the effect of various loading conditions on the resultant impedance vector;

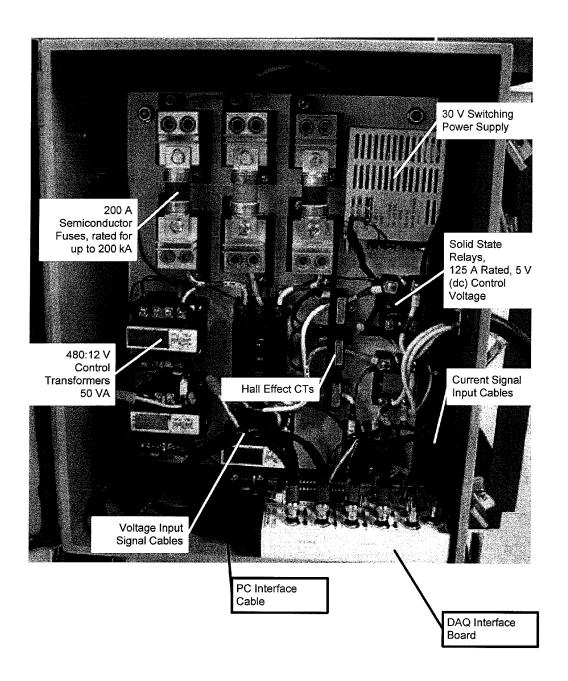

FIG. 6 illustrates an exemplary control cabinet according to an embodiment of the present invention;

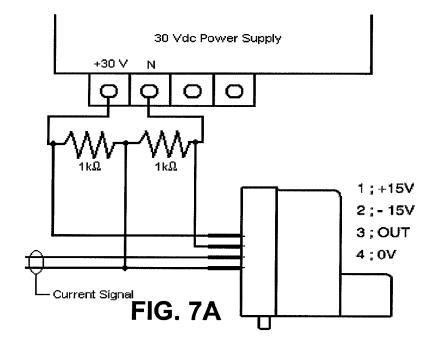

FIG. 7A illustrates two-watt, 1000 Ohm resistors can be placed in series across the output of the power supply and wired to each CT using standard 4-pin connectors, and FIG. 5 7B illustrates wiring diagrams of the CT:

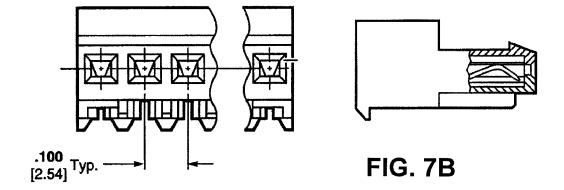

FIGS. 8A and 8B depict images of exemplary data acquisition components, FIG. 8A shows a DAQ card, which includes the eight independent A/D converters, amplifiers and memory modules and FIG. 8B shows a BNC connection port that takes analog signals from shielded coaxial cables to a data cable that interfaces with the DAQ card;

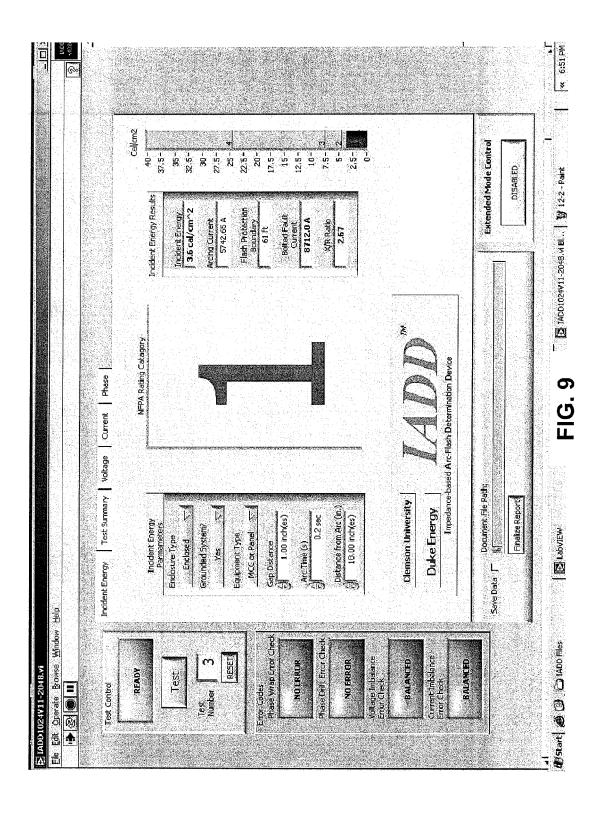

FIG. 9 shows an exemplary Incident Energy screen of the front panel GUI used in an embodiment of the IADD system; 15

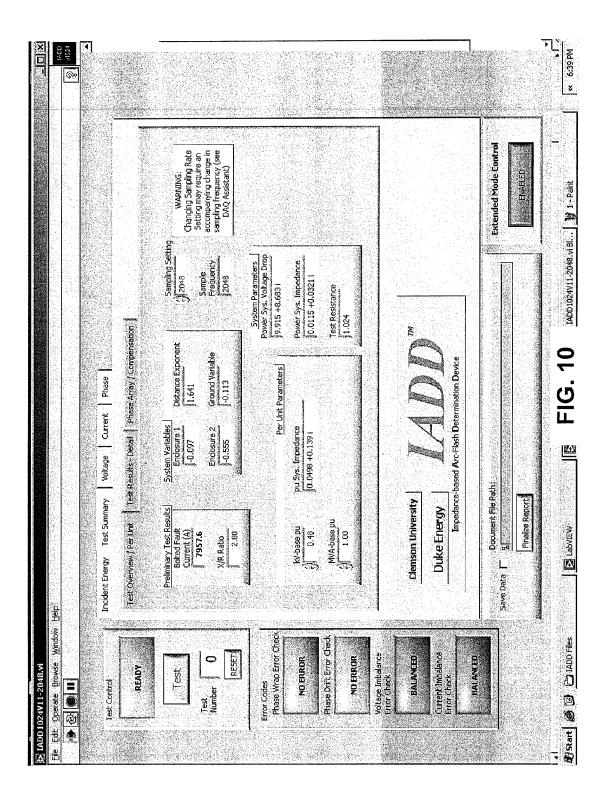

FIG. 10 shown an exemplary Test Summary—Test Overview/Per Unit screen;

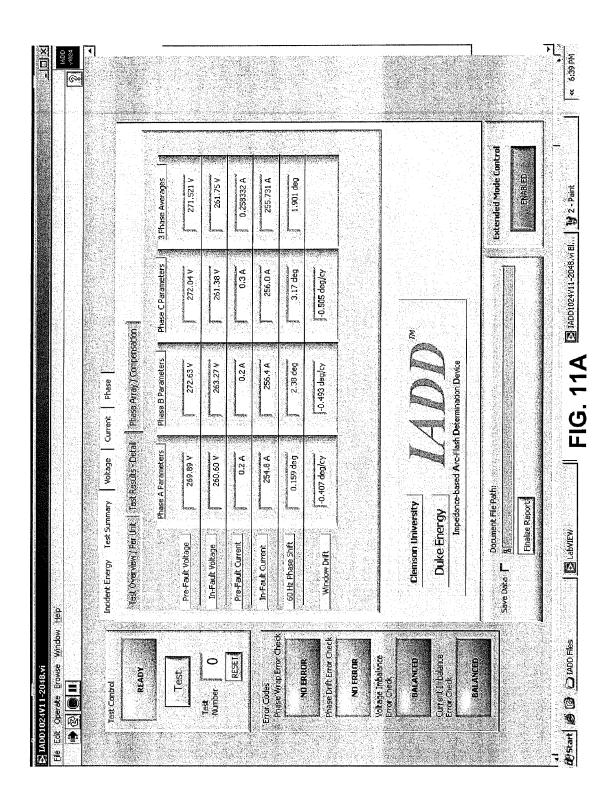

FIG. 11A is an exemplary Test Summary—Test Results— Detail tab screen;

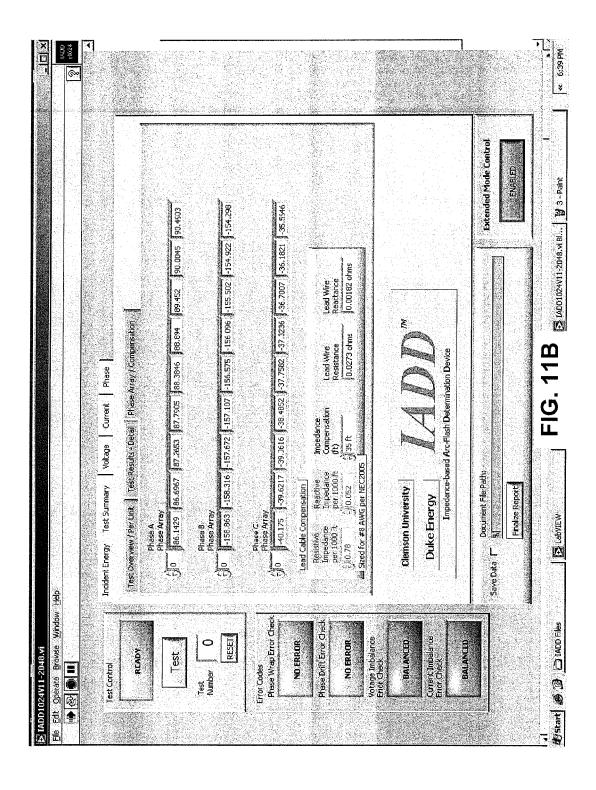

FIG. 11B is an exemplary Voltage—Phase Array/Compen- 20 sation tab screen;

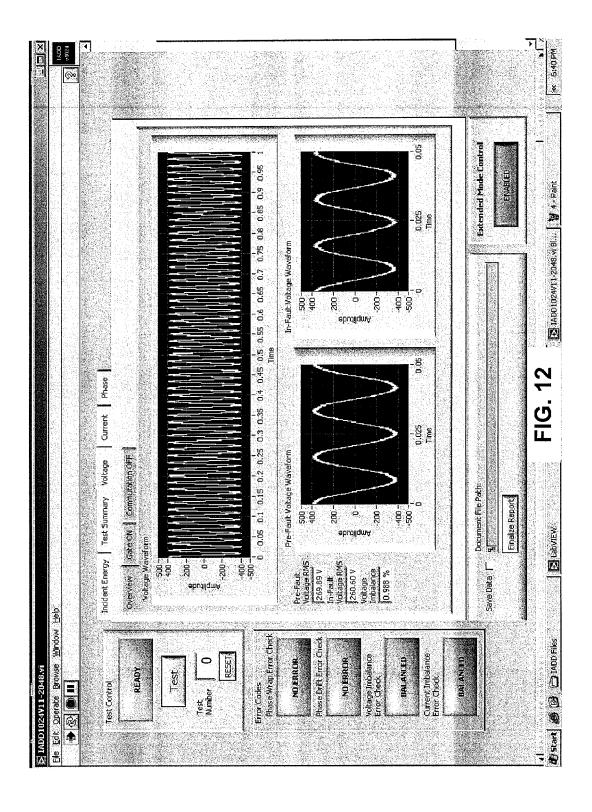

FIG. 12 is an exemplary Voltage—Overview screen;

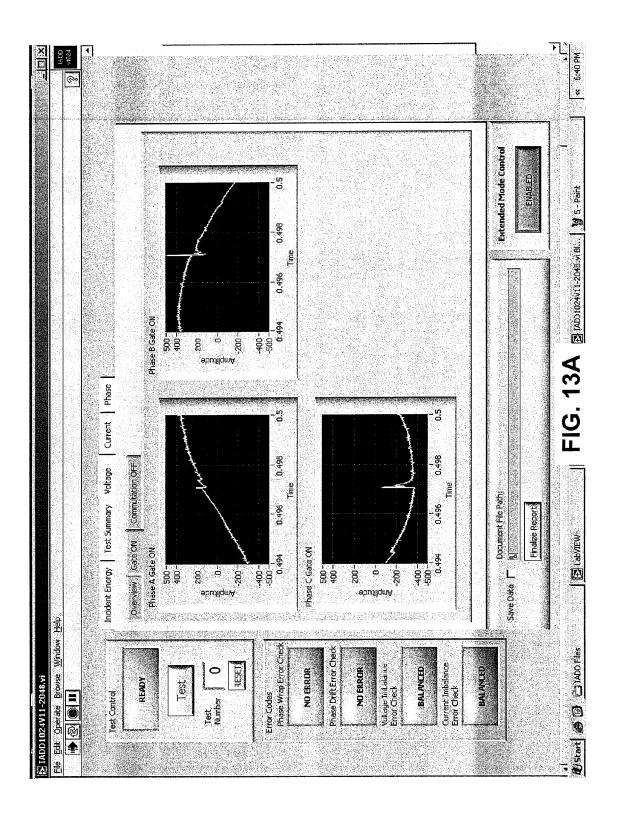

FIG. 13A is an exemplary Voltage—Gate On tab screen;

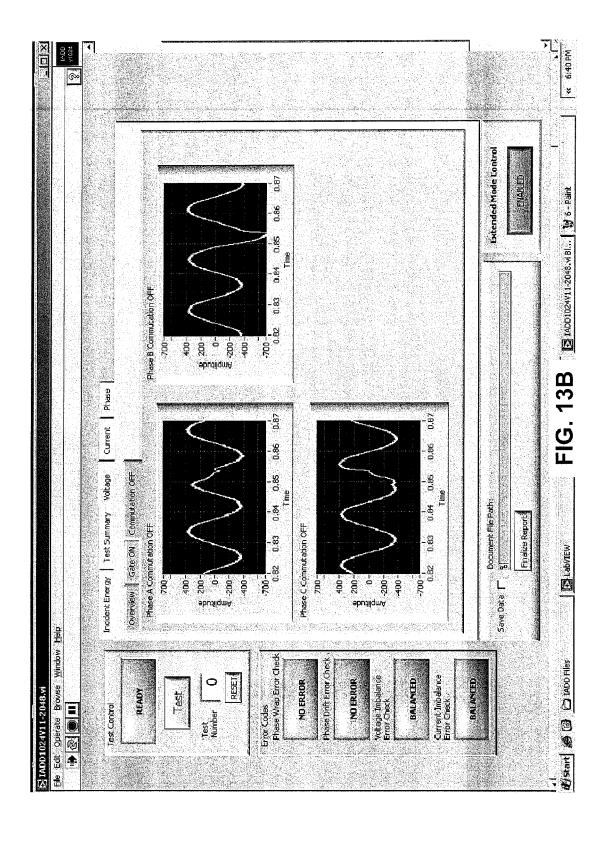

FIG. 13B is an exemplary Voltage—Commutation OFF tab screen;

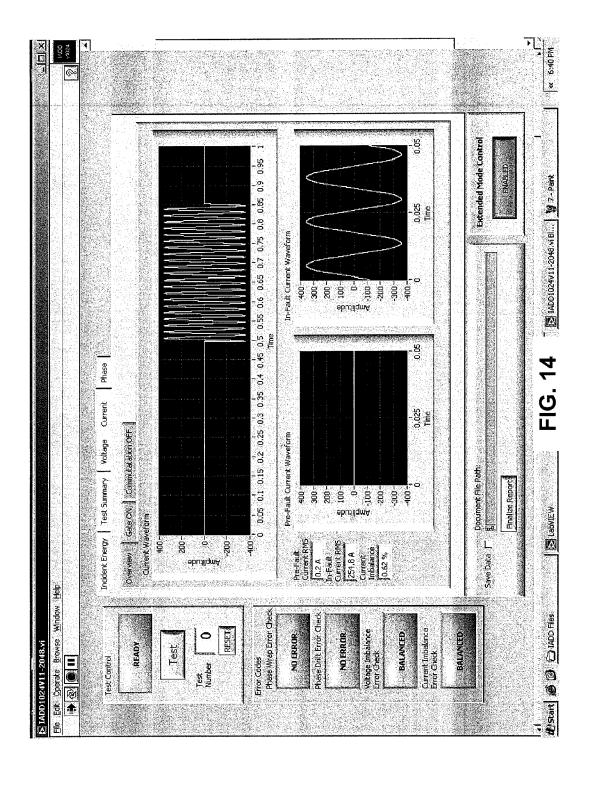

FIG. 14 is an exemplary Current—Overview tab screen;

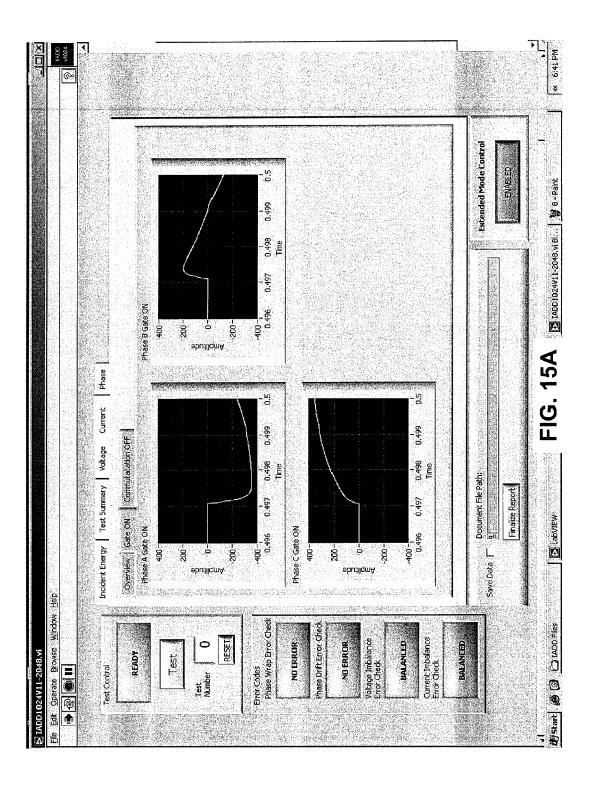

FIG. **15**A is an exemplary Current—Gate On tab screen;

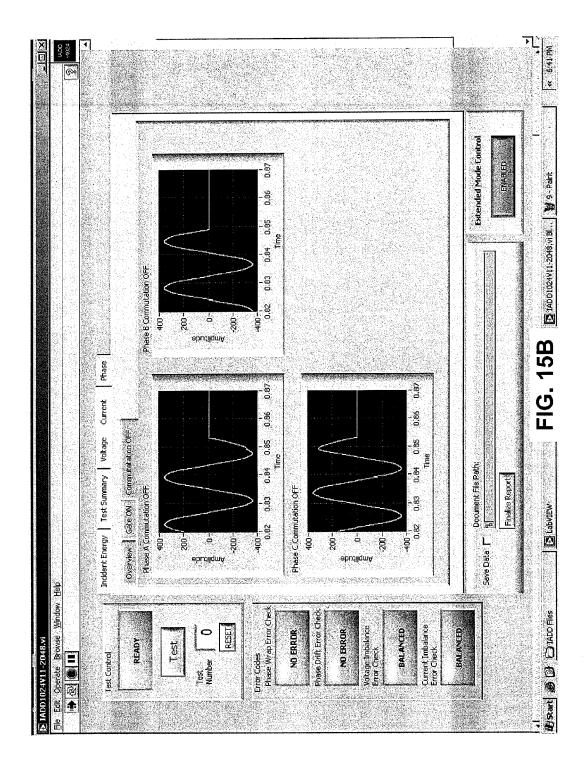

FIG. 15B is an exemplary Current—Commutation OFF tab screen:

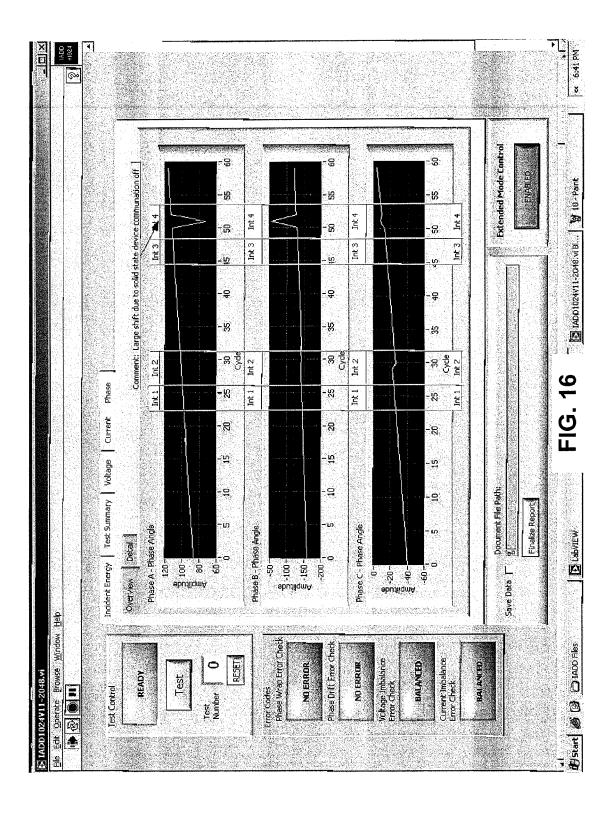

FIG. 16 is an exemplary Phase—Overview tab screen;

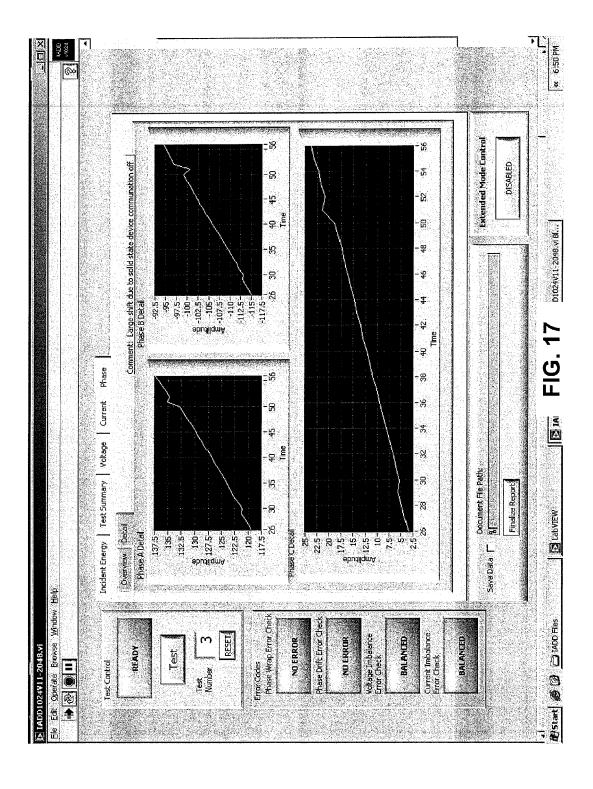

FIG. 17 is an exemplary Phase—Details tab screen;

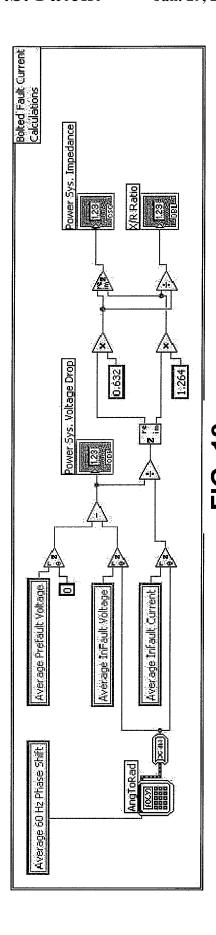

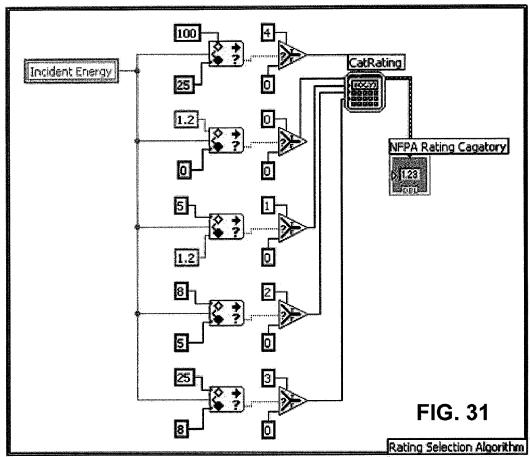

FIG. 18 illustrates an implementation of calculations leading to determination of bolted fault duty, impedance and X/R

FIG. 19 illustrates an electrical system diagram a portion of 35 the block diagram implementation of FIG. 18;

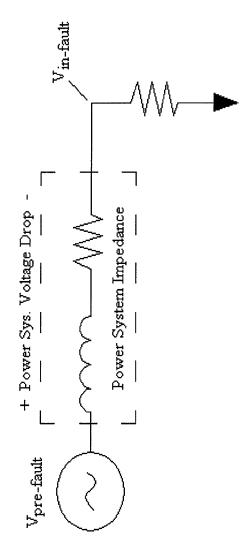

FIG. 20 illustrates a cycle-by-cycle phase extraction algorithm as implemented in software such as, for example, Lab-View<sup>TM</sup>:

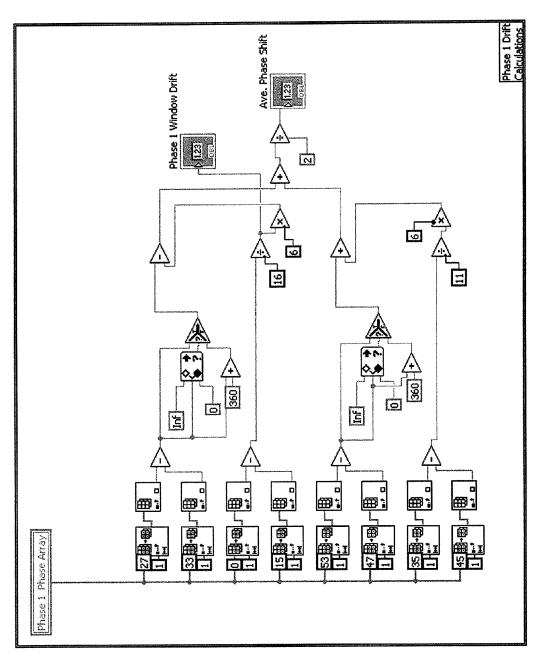

FIG. 21 graphically illustrates an algorithm for determin- 40 ing phase shift in each phase of the incoming voltage wave-

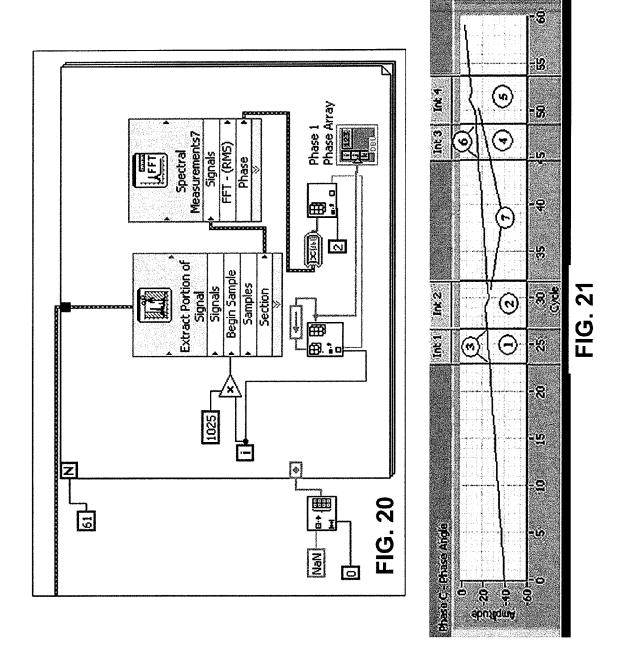

FIG. 22 is a graphical representation of a LabView<sup>TM</sup> implementation of a phase-detection algorithm;

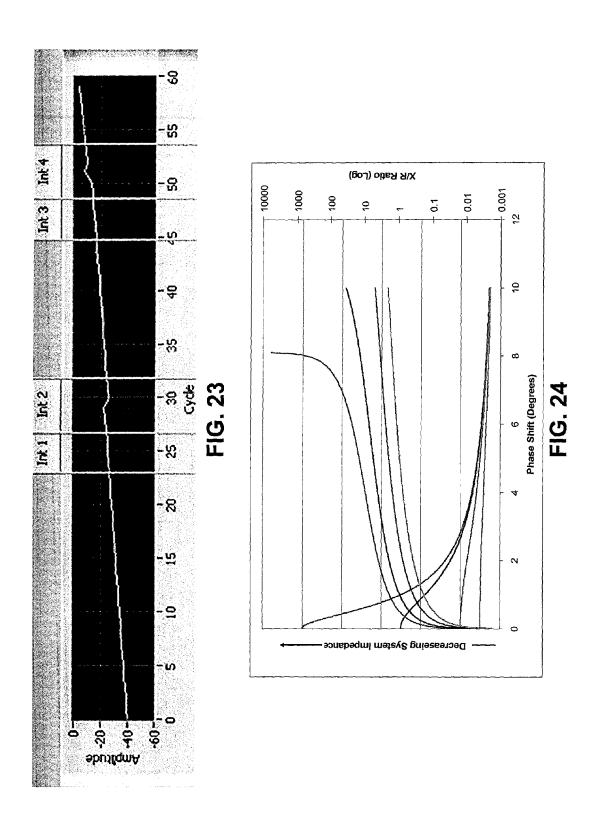

FIG. 23 is a graphical representation of the implementation 45 of the algorithm of FIG. 22;

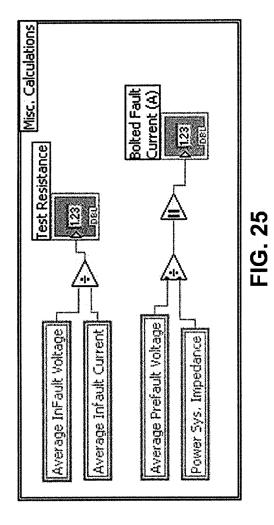

FIG. 24 shows typical relationships between the computed X/R to measured phase shift for varying power system imped-

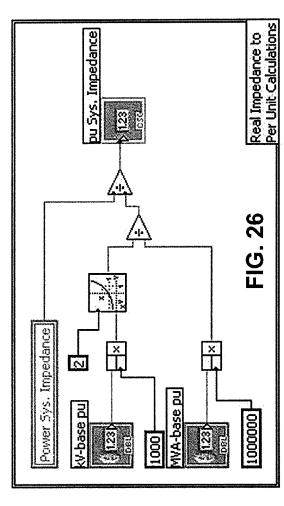

FIG. 25 is a algorithm to determine the load (test) imped-50 ance and the bolted fault current, implemented in LabView<sup>TM</sup>;

FIG. 26 is an exemplary LabView<sup>TM</sup> algorithm for calculation of per-unit system impedance;

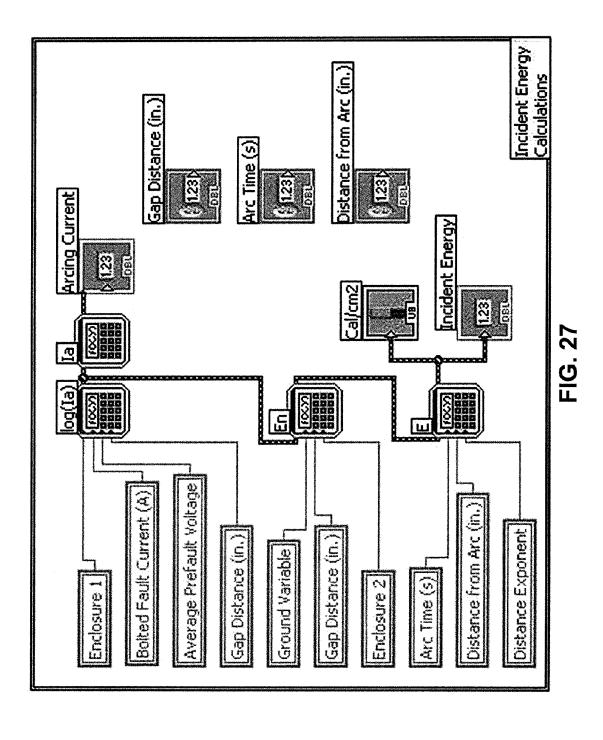

FIG. 27 is an exemplary algorithm to determine arc flash incident energy is presented using LabView™ graphical cod- 55 convey an indication of a preferred or ideal embodiment.

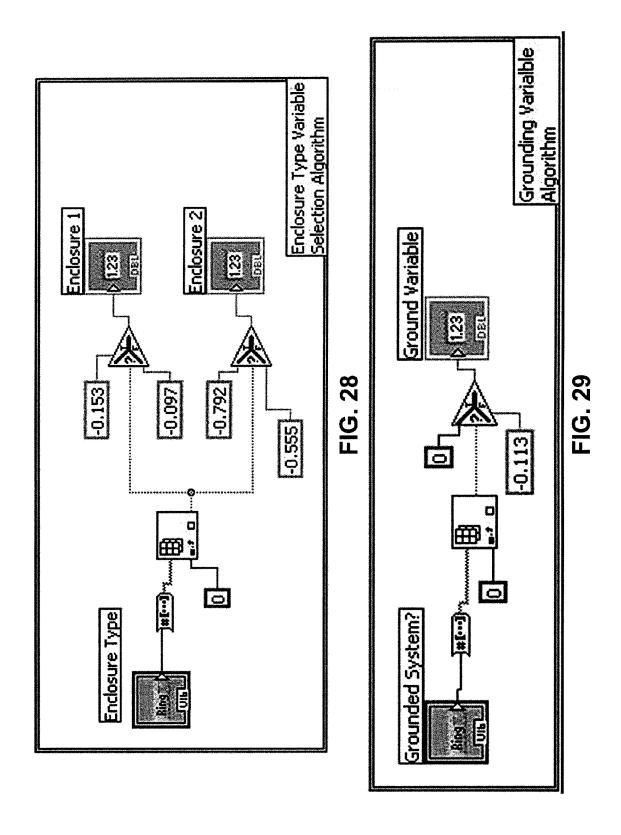

FIG. 28 is an illustration of an exemplary algorithm to select values for variables K and K1 based on enclosure type based on Equations 4 and 5;

FIG. 29 is an illustration of an exemplary algorithm to 60 select values for variable K2 based on presence or absence of a ground;

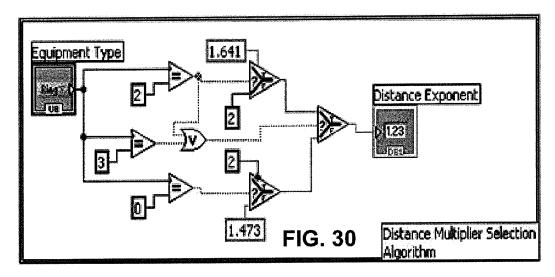

FIG. 30 is an illustration of an exemplary algorithm to select values for variable x based on equipment type;

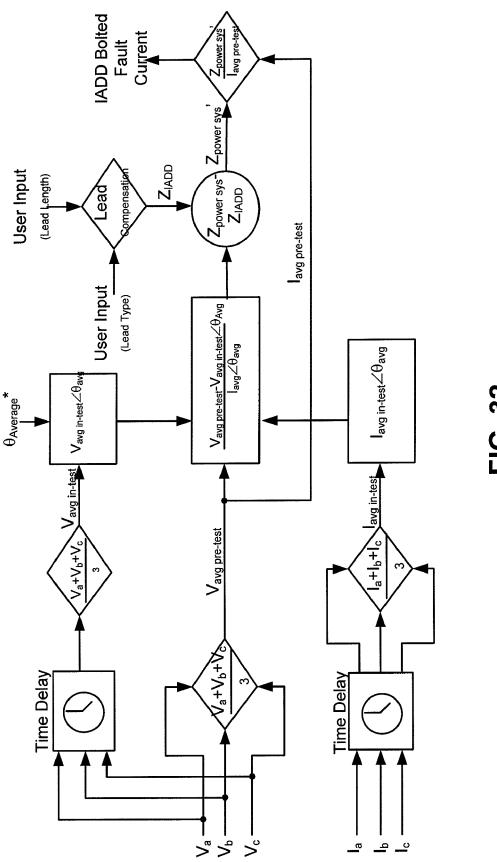

FIG. 31 is an illustration of an exemplary algorithm to 65 determine NFPA rating category based on calculated incident energy;

8

FIG. 32 illustrates a flow diagram for the steps to determine an NFPS category rating;

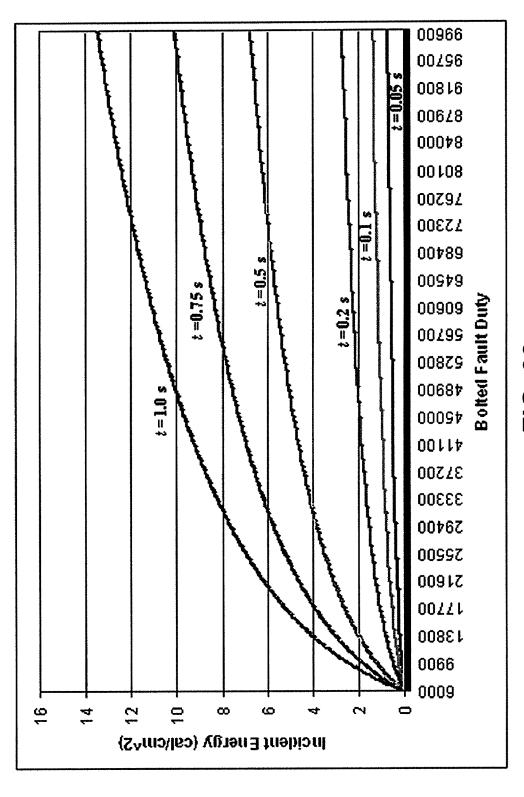

FIG. 33 illustrates incident energy as a function of bolted fault duty and primary protection trip times;

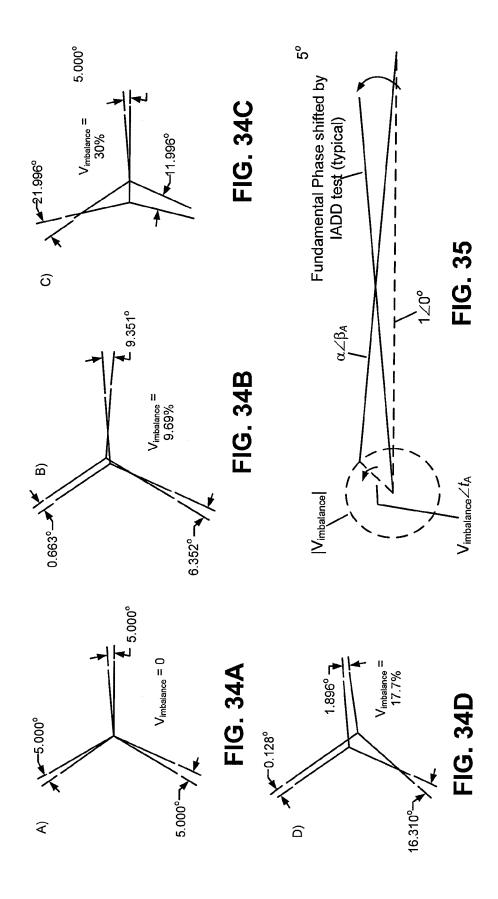

FIGS. 34A, 34B, 34C, 34D depict the neutral shift caused in the load resistance due to imbalance, for four possible scenarios of 0, 9.69%, 30%, and 17.79% load phase-to-neutral voltage imbalance, respectively.

FIG. 35 depicts the phase A condition where neutral shift plays a factor in the overall determination of calculated phase shift as determined by the IADD;

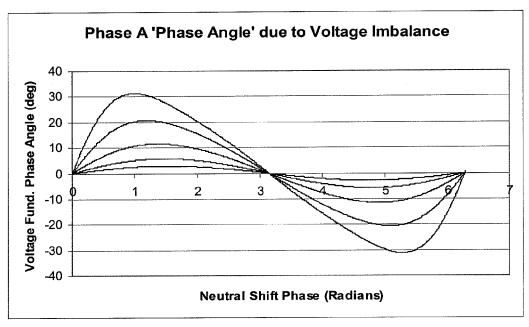

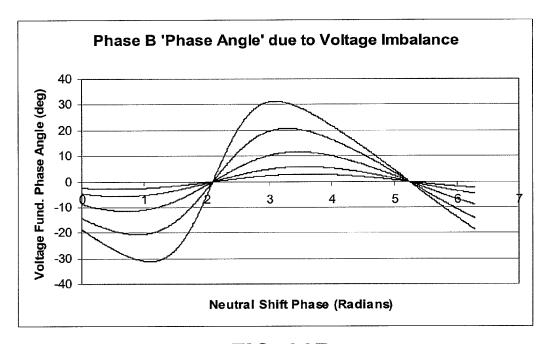

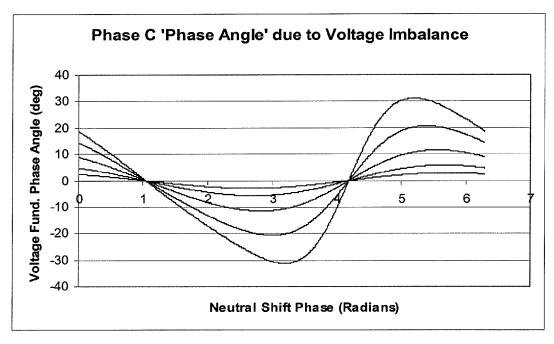

FIGS. 36A, 36B, 36C graphically illustrates non-linear equations that are evaluated below for selected values Of  $V_{\it imbalance}$  at 5%, 10%, 20%, 35% and 50% and as can be seen from the graphs of FIGS. 36A, 36B and 36C, the solution is highly sinusoidal when magnitude of imbalance is low (below 20%);

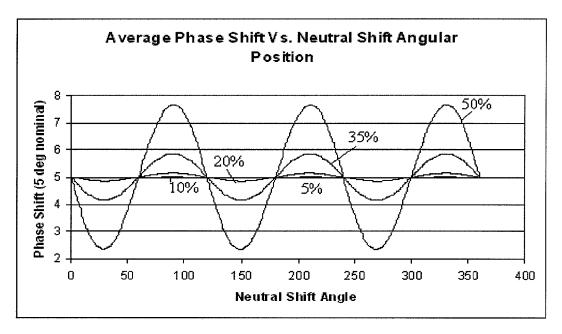

FIG. 37 shows average deviation from the nominal phase shift of 5 degrees;

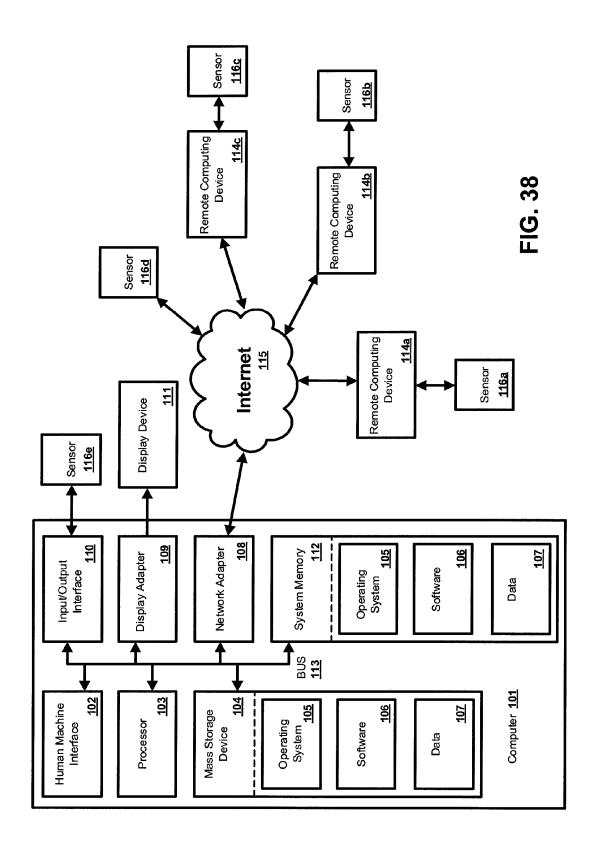

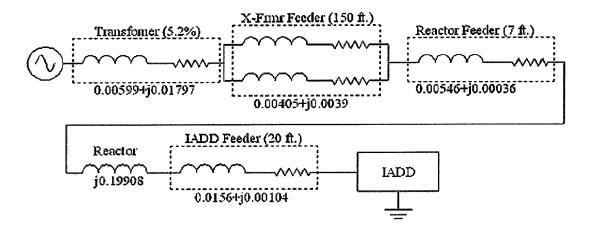

FIG. 38 is a block diagram illustrating an exemplary operating environment for performing the disclosed methods; and FIG. 39 illustrates the impedances of the system for

Example 2.

25

# DETAILED DESCRIPTION

Before the present methods and systems are disclosed and described, it is to be understood that the methods and systems are not limited to specific synthetic methods, specific components, or to particular compositions, as such may, of course, vary. It is also to be understood that the terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting.

## **DEFINITIONS**

As used in the specification and the appended claims, the singular forms "a," "an" and "the" include plural referents unless the context clearly dictates otherwise. Ranges may be expressed herein as from "about" one particular value, and/or to "about" another particular value. When such a range is expressed, another embodiment includes from the one particular value and/or to the other particular value. Similarly, when values are expressed as approximations, by use of the antecedent "about," it will be understood that the particular value forms another embodiment. It will be further understood that the endpoints of each of the ranges are significant both in relation to the other endpoint, and independently of the other endpoint.

"Optional" or "optionally" means that the subsequently described event or circumstance may or may not occur, and that the description includes instances where said event or circumstance occurs and instances where it does not.

"Exemplary" means "an example of" and is not intended to

Arc Fault Incident Exposure Energy: The amount of energy received at a surface, as a direct result of an electrical arc, as measured by the temperature rise on copper calorim-

Calorie: An energy measurement used to characterize the amount of arc flash energy which is required to cause a second degree (blister burn) on human skin. Without protection, according to the Stoll Curve, it takes about 1.2 cal/cm<sup>2</sup> to cause a second degree burn.

Bolted Fault Current: The condition that exists when maximum energy transfer occurs between two points of differing voltage, having little or no arcing resistance.

Equivalent Generation Combining all points of electric generation into one Thevenin voltage source.

Frequency Bin: A band of frequencies of a specific width. This term is most often applied to signals processed by a Fast Fourier Transform (FFT) because frequency bands of equal 5 width are partitioned by the FFT algorithm.

Hall Effect The Hall Effect refers to the potential difference (Hall voltage) on opposite sides of a thin sheet of conducting or semiconducting material in the form of a 'Hall bar' (or a van der Pauw element) through which an electric current is flowing, created by a magnetic field applied perpendicular to the Hall element. Edwin Hall discovered this effect in 1879.

In-Test Mode: A mode of operation for the IADD. In-Test Mode refers to the test step in which current is flowing through the load bank and the IADD induced voltage drop and phase angle shift on the measured buss.

Pre-Test Mode: A mode of operation for the IADD. Pre-Test Mode refers to the test step in which the Thevenin voltage value is determined and a reference phase angle is established.

Stoll Curve This is a standard curve, based on heat and time, used by the American Society for Testing Materials (ASTM) to predict the onset of second-degree burn injury. Energies above the Stoll curve would normally produce a second-degree burn. Those below the Stoll curve would normally not produce a second-degree burn.

Triplen Harmonics Odd Harmonics divisible by three (e.g. 3, 9, 15, 21, 27, 33...). These harmonics are particularly troublesome in three phase power systems because they remain in phase with one another in each of the three phases, 30 possibly causing resonant coupling between phases and are additive in the neutral or cause circulating currents in the case of a delta configuration.

## INTRODUCTION

The present methods and systems may be understood more readily by reference to the following detailed description of embodiments and the examples included therein and to the Figures and their previous and following description.

The underlying principle for arc fault detection and the operation of embodiments of the IADD is the ability to determine the Thevenin or Norton equivalent circuit as seen "looking" into the buss at the test location. This equivalent circuit would include the effect of all series and parallel devices 45 connected to the buss, including switchgear, cables, transformers, etc. as well as the networked sources. In general, the Thevenin equivalent impedance can be determined from two conditions: (a) the open circuit voltage, which is the Thevenin voltage source; and (b) the short circuit current in a zero 50 impedance fault at the test location bus. Alternatively, embodiments of the IADD can compute the dual of the Thevenin equivalent circuit, called the Norton equivalent circuit. The Norton equivalent circuit comprises a parallel ideal current source and impedance. The Norton current source is 55 equal to the short circuit current into a zero impedance fault (the so-called "bolted fault current") and the Norton impedance is equal to the Thevenin equivalent impedance.

Defining these values from an intrinsic sense can be challenging. Due to the dynamic nature of the power system, the 60 voltage at any given location in the power grid is always in a state of flux, both in magnitude and phase angle. There are several reasons for voltage fluctuation on the power system including, but not limited to, the amount of generation present on the system as well as voltage regulation devices such as 65 switching power factor correcting capacitors and tap changing transformers. A significant source of voltage variation is

10

the constant changes in loading conditions, particularly large load changes such as motor starting that may cause momentary changes in the RMS voltage. Several strategies can be employed to mitigate the likelihood of error due to voltage/load variation. To minimize the likelihood of error due to voltage variation and changes in loading conditions, the time of a complete test should be minimized such that establishment of baseline voltage data is not skewed when the test load is applied.

The theory of voltage division states that the voltage across any series element is distributed according to the ratio of total series impedance to the impedance of measurement. Therefore, any change in the system results in a change in the observed voltage at any given point, except at the point of equivalent generation, where voltage is assumed to be regulated and constant. This idea is illustrated in FIGS. 1A and 1B.

FIG. 1A shows a typical electrical system with a single point of generation and four loads drawing current with specified magnitude and power factor. Voltages at busses one and two are also displayed in per unit magnitude and phase angle with respect to a reference angle of zero at the generator. FIG. 1B shows the addition of another load, in this case the addition of the IADD device during the in-test mode, according to an embodiment of the present invention, that draws current at a unity power factor and effects both the voltage magnitude and phase angle at buss two.

FIGS. 1A and 1B illustrate the small variations in voltage and phase angle that occur when a step change in loading condition is made on a system. If these variables, voltage magnitude change and phase angle change, can be measured then a determination of the impedance between the test node and the equivalent source can be made. With this information, the bolted fault current at the test node becomes apparent. An embodiment of a device according to the present invention provides for capture of waveforms that can be analyzed for voltage change and phase shift.

By non-limiting example, FIG. 2 schematically illustrates one embodiment according to the present invention. In the embodiment of FIG. 2, three phase, real-time, voltage and 40 current measurement through magnetically isolated potential transformers (PTs) and current transformers (CT), though other embodiments, for example, may use different components such as optically isolated differential voltage probes. The current transformers are Hall Effect type CTs that have the ability to measure DC offsets present during most transient events. The resistor bank is a modified dynamic braking resistor bank commonly used in adjustable speed motor drives for dissipating energy from a regenerating or overhauling rotating load or other energy source. The resistors are switched in and out of the circuit through three solid state voltage controlled relays with a gate signal provided by the control unit; these are modeled here as two thyristors with bipolar operation. Other embodiments according to the present invention double the current-drawing capacity by adding a second set of solid state relays in parallel with the three shown in FIG. 2 and use a separate digital gating signal that may be selected on demand via user control input, though other switching and/or relaying schemes and devices are contemplated within the scope of the invention. A control system (not shown in FIG. 2) can comprise a personal computer (PC) running, for example, LabView<sup>TM</sup> development software and integrating an eight channel simultaneously sampling data acquisition (DAQ) card as the principal method of both gathering measurement data and outputting control signals to solid-state relays. LabView<sup>TM</sup> is a graphical development environment for creating flexible and scalable design, control, and test applications rapidly and at minimal cost as

available from National Instruments Corporation (Austin, Tex.). LabView<sup>TM</sup>, is configured to allow users to interface with signals; analyze data for meaningful information; and share results through intuitive displays, reports, and the web, though other software packages or custom-developed software for implementing the algorithms described herein are contemplated within the scope of the embodiments of the present invention.

11

IADD

FIG. 3 illustrates an exemplary embodiment of an IADD. 10 The embodiment of FIG. 3 is comprised of a load bank, voltage measurement circuitry and devices, current measurement circuitry and devices, relaying and switching, and data acquisition, measurement and control.

#### A. Load Bank

FIGS. 4A and 4B illustrate an exemplary resistive load bank that can be used in embodiments according to the present invention. In one aspect according to the present invention an AGR41 dynamic braking resistor, as available from Avtron Manufacturing, based in Cleveland Ohio, is 20 used. The AGR41 dynamic braking resistor is a tapped resistor, capable of handling 8.3 kW of power continuously, and has a maximum resistance of 5.1 ohms, which allow the resistive load to be used on systems of varying voltage levels. A relatively heavy load can be created by appropriate selection of one of eleven taps on the resistor for the desired load. For instance, on a 600  $\rm V_{1-1}$  system, the phase voltage is approximately 380 V  $_{rms}$ . A resistance between three or four ohms might be chosen to draw currents of approximately 100 A  $_{rms}$ . On a 208 V system, a resistance closer to one ohm might be chosen to draw the same amount of current.

The amount of current to be drawn depends on how "stiff" this system is, that is, how much impedance is between the test location and the Thevenin equivalent voltage source. Field tests have shown that, in some instances, the current 35 drawn during testing should be increased based on the parameters of the system and how immune the system is to transient load changes. Generally, the accuracy of the results improves with increases in loading. However, increases in loading cause increases in voltage drop. It is undesirable to cause a 40 voltage drop (a so-called voltage "dip" or "sag") deep enough that either equipment in the facility misoperates or that an undesired power system dynamic results. Voltage drop at or below 5% can be well-tolerated in most situations. A qualitative analysis examining the impact of current drawn to 45 detection accuracy is also examined herein.

Of course, each electrical power system differs resulting in different optimum amounts of current to draw in order to create a measurable change in voltage sag and phase shift. Other embodiments can include a switching scheme that 50 automatically selects the appropriate resistance level based on measured voltage prior to testing.

Other loads that can be used in various embodiments according to the present invention include inductors, capacitors, and combinations of RL and RC circuits or an induction 55 motor starting (especially one with a high inertia mechanical load). An examination of phasor diagrams is used to illustrate the potential advantages and disadvantages of using such loads. FIG. 5 is an impedance diagram illustrating the effect of various loading conditions on resultant impedance phasor. 60 In FIG. 5, each loading condition offers different results in terms of changes in magnitude and phase angle of the resultant impedance phasor. For instance, both the inductive and capacitive loads offer large changes in impedance magnitude, but only a marginal change in impedance angle. The resistive 65 load, however, changes both the magnitude and phase angle of the resultant phasor significantly. Therefore, in most prac-

12

tical situations, the resistive load facilitates effecting both voltage magnitude and phase angle of the electrical system simultaneously to successfully measure changes in both magnitude and phase angle.

There are some challenges with using a capacitive load due to the potential for exciting resonances between capacitance and natural inductance present in the system. These transient over-voltages can sometimes result in voltage magnitudes twice that of system steady state voltage. Overvoltages may cause measurement error due to A/D saturation, can pose threats to the test equipment as it is rated for  $600\,\mathrm{V}_{rms}$  as well as for the system itself under certain conditions. Adjustable speed drives might also trip due to over voltage transients and the IADD needs to be able to conduct testing without disturbing a facility's loads.

Since most electrical power system equivalents are dominated with inductive reactance, using a purely inductive load will also be problematic. Although the voltage drop magnitude can be significantly affected, since the drop is closely in-phase with system impedance the changes in phase shift during testing are likely to be small.

It is to be appreciated that any combination of resistance, inductance, and capacitance used as loads is possible, spanning the entire right half side of the impedance domain, and is contemplated within the scope of the present invention. This includes loads such as induction motors which look like a series connected resistance and inductance during starting. This is illustrated by the semi-circle surrounding the impedance fundamental vector in FIG. 5.

#### B. Voltage Measurement Circuitry

In one aspect, voltage waveform information can be obtained through the use of, for example, optically isolated voltage though other voltage detection devices (such as PTs) are contemplated within the scope of this invention, though they may operate in non-linear regions and be susceptible to saturation. FIG. 6 illustrates an exemplary control cabinet according to an embodiment of the present invention.

Voltage can be measured in single and poly-phase systems as line-to-line, line-to-neutral, and in a three-phase system, for example, the voltage can be measured either in delta (line to line voltage) or wye (line to neutral voltage) configuration C. Current Measurement Circuitry

In one aspect, current measurements are made through the use of three externally powered Hall-effect current transformers (CT) (refer to FIG. 6). For example, a Hall-effect current sensor manufactured by Tamura Corporation (Temecula, Calif.) can be used for this application, though others are also contemplated within the scope of the invention. In one aspect, the CT can be rated for a nominal current of 250  $A_{rms}$ , 4 V output, which are linear over the range of anticipated currents and the desired bandwidth. In one aspect, the CTs have good frequency response at 60 Hz, with a -3 dB frequency response at 10 kHz. Current transformers designed for both ac and dc signals measure transverse force on moving charge carriers, typically referred to as the Hall Effect, to measure any variations in DC current. Hall Effect sensors require an external power supply to measure transverse forces. The Tamura CTs utilize positive and negative 15  $V_{dc}$  power to operate. In one aspect, the power requirements can be satisfied by using a single 30  $V_{\it dc}$  switching power supply that operates on  $120 \, \mathrm{V}_{rms}$ . Building a resistive divider creates a phantom neutral that can be used as the reference on all CTs. Two watt, 1000 Ohm resistors can be placed in series across the output of the power supply and wired to each CT using standard 4-pin connectors as shown in FIG. 7A. Wiring diagrams are also shown in FIG. 7B.

## D. Relaying and Switching

In one aspect, a Crydom HD60125-10 series solid state relay (SSR) can be used to serve as switches for transferring load during the testing sequence as available from Crydom, Inc. (San Diego, Calif.), though other relays are contemplated within the scope of this invention. These relays have a load current rating of 125 amperes per device and are controlled by a five volt DC signal supplied by the DAQ card. These relays also have a random turn-on feature, which is useful for this application, as all three relays generally turn on at relatively the same point to minimize any transient reaction and provide a balanced load to all three phases whenever possible. The devices can be paralleled, two per phase, to double the ampacity of the device. The added capacity allows for greater latitude in measuring at high power locations. Electromechanical relays are also contemplated within the scope of this invention

Voltage drop across the solid state relays represents a measurable impedance that would require compensation if voltage measurements were taken downstream of this device. 20 However, by taking voltage measurements upstream of this device, it becomes part of the steady state load. Furthermore, because the voltage distortion is cyclic and consistent in magnitude from cycle to cycle, it does not skew phase angle measurement in a steady state condition. Based on these 25 considerations, there is no need for additional compensation due to the effects of crossover distortion or gated voltage drop are required.

# E. Data Acquisition, Measurement and Control

In one aspect, a National Instruments PCI-6123 data acquisition card can be used to sample and capture data (National Instruments Corporation, Austin, Tex.), though other data acquisition cards are contemplated within the scope of this invention. Criteria for selection of a data acquisition card include: simultaneous sampling is desired to minimize phase shift due multiplexing of voltage and current signals on different channels since final calculations are highly susceptible to phase shift; 16-bit precision on sampled values versus 12 or 14 bit options increases the accuracy of readings by a factor of 4 to 16 times; and a sampling frequency sufficiently high to 40 capture all spectral data of interest and further minimize error due to phase shift and quantization error.

FIGS. 8A and 8B depict images of exemplary data acquisition components. FIG. 8A shows a DAQ card, which includes the eight independent A/D converters, amplifiers and 45 memory modules. FIG. 8B shows a BNC connection port that takes analog signals from shielded coaxial cables to a data cable that interfaces with the DAQ card. In one aspect the data cable can be, for example, a proprietary data cable as available from National Instruments, Inc. Preferably, coaxial 50 cables and BNC connectors are selected for performance in electrically noisy environments; electromagnetic fields that typically couple to signal wires are shielded due to the large current and voltage levels present in the proximity of the measurement devices.

# Software for the IADD

In one aspect, development of software for the IADD was accomplished using National Instruments' LabView<sup>TM</sup> software, though other software packages or custom-developed software are contemplated within the scope of the present 60 invention. In conjunction with the DAQ, signals are processed and analyzed to determine the bolted fault current at the buss of interest. Several components are required to accomplish this task and are discussed in sequence.

In one aspect, the PC can be custom-built to be able to 65 handle large amounts of incoming data efficiently while still having enough processor power to send control signals to

14

switching elements at the proper time. In one aspect, the computer is comprised of a 3.2 GHz dual core Intel<sup>TM</sup> processor and has a data bus speed of 800 MHz, though other computers are contemplated within the scope of this invention. Other computer aspects are described herein in reference to FIG. 38. In one embodiment, software based timers are used to create control signals that gate the solid state relays and the computer should have sufficient processing capability to implement these timers.

#### ' A. GUI

The front panel refers to the Graphical User Interface (GUI) that users see initially when the application is started. Several screens described below present the user with as much information about testing as possible, though it is to be appreciated that these are non-limiting examples of screens that can be used and more, fewer or different screens are contemplated within the scope of the invention.

#### 1. Incident Energy

FIG. 9 shows an exemplary screen of the front panel GUI used in an embodiment of the IADD system. The main panel that opens when the program is executed features a large number, centrally located, that represents the NFPA category number previously discussed herein. This number is based on the cal/cm² found in NFPA 70E, Table 3-3.9.3 for determining personal protective equipment (PPE) hazard risk category, or any replacements thereof, as shown below.

TABLE 3-3.9.3

| _ | NFPA 70E |                     |                                                                                        |  |  |  |  |

|---|----------|---------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| _ | Category | Cal/cm <sup>2</sup> | Clothing                                                                               |  |  |  |  |

| _ | 0        | 1.2                 | Untreated cotton                                                                       |  |  |  |  |

| ; | 1        | 5                   | Flame retardant (FR) shirt and FR pants                                                |  |  |  |  |

|   | 2        | 8                   | Cotton underwear, FR shirt, and FR pants                                               |  |  |  |  |

|   | 3        | 25                  | Cotton underwear, FR shirt, FR pants, and FR coverall                                  |  |  |  |  |

| ) | 4        | 40                  | Cotton underwear, FR shirt, FR pants,<br>and double-layer switching coat<br>and pants. |  |  |  |  |

The incident energy exposure in cal/cm<sup>2</sup> is given in the upper right hand corner of the screen of FIG. **9** and a graphic representation of this data with respect to category level is given on the right hand side.

By using the equations developed in, for example, IEEE 1584, the category rating is calculated based on bolted fault current and several other variables. These variables are listed under the Incident Energy Parameters menu to the left of the large rating number of FIG. 9. Changing any of these values changes the calculated incident energy and may change the rating category. Additional fields illustrated on FIG. 9 include:

Enclosure Type is a variable used in the incident energy calculations. The user can select either an enclosed or non-enclosed panel configuration. Enclosed panels can reflect energy off of their surfaces and increase exposure to radiating energy.

Grounded System is a yes or no variable used in arcing current calculations to categorize the system connection type.

Equipment Type is a variable used to categorize the type of system being tested. Certain types of equipment are more robustly constructed and provide lower fault resistance, such as MCCs when compared to an arc occurring in a cable.

Gap Distance is user specified in inches based on the distance between conductors with potential to arc. The arcing

distance has a small effect on both arcing current and the amount of energy radiated during an arc.

Arc Time is user specified in seconds based on the type of protection present in the vicinity of test location. As discussed, protection plays a key role in reducing energy exposure levels by reducing the arcing time.

Distance from Arc is user specified in inches based on the type of equipment, voltage level and standard practices used at a test location. For example closer working distances are expected at voltage levels below 600 V when compared to voltages of 4.16 kV.

To the left of the main page of FIG. 9 are the Test Control and Error Codes dialog boxes. Generally, these are always visible while the program is running and allows the user to initiate a test at any time. The large button labeled Test initiates the IADD program and a test is performed. A numeric indicator below the test button indicates what test number has just been performed and serves as a marker if tracking of data is being performed. The test counter can be reset by pressing 20 the button below the counter number. Also, the test number is automatically reset every time the program is terminated or started. The test status indicator as shown in FIG. 9 can be color-coded (e.g., green) and displays "Ready" indicating that the system is ready to test the connected buss. The indi- 25 cator turns, for example, yellow and display the message "Test in Progress" while the IADD is performing the test and making result calculations. A test typically takes about 3 seconds to complete.

The Error Codes dialog box can be displayed below the 30 Test Control box previously described. This dialog allows the user to determine the validity of the most recent test. The Phase Wrap Error Check determines if an error has occurred due to phase wrap phenomenon, described in more depth herein. If significant voltage or current imbalance is observed 35 during a test sequence, the appropriate indicator changes to, for example, red and messages such as "Voltage Imbalance" or "Check Connection" can be displayed based on the type of error detected. Voltage imbalance errors are triggered by the voltage imbalance calculation discussed in greater detail 40 herein. In the case of current imbalance in the presence of balanced phase voltage, the connections and load taps should be examined and confirmed prior to additional testing.

Capturing data can be accomplished through the dialog box at the bottom of the screen. To save test data, the user 45 checks the box next to 'Save Data'. After the first test is complete, the user is prompted to save the file in a specified location on, for example, the hard drive. Once this location is established, the data capture process is automated. When all tests in a series have been completed, the user has the option 50 to finalize testing, writing all the selected incident energy parameters to the file for later reference. After finalizing the test series, the user is then prompted to start a new test or end the session.

The selection button in the lower left-hand corner of the screen is user selectable and determines whether the IADD will operate in standard or extended mode. In one aspect, the resistor bank can be segregated into two effective load banks by creating a neutral at the center tap of each phase of the resistor bank. Standard mode uses one half of the resistor bank as a load resistor to draw current. When the IADD is used in extended mode, both sides of the load are energizes and current flow is doubled. When operating the IADD in extended mode, it is suggested that cycle time between subsequent tests be increased to allow time for the solid state of relay's semiconductor material to cool properly prior to additional test runs. In one aspect, the suggested cycle time for

16

standard mode is one (1) test every thirty (30) seconds. The suggested cycle time for extended mode is one (1) test every sixty (60) seconds.

2. Test Results

An exemplary Test Summary screen as shown in FIG. 10 gives numerical information about the last test conducted. 'Test Overview/Per Unit' is displayed in FIG. 10 and additional test information is provided in Test Results—Detail tab in FIG. 11A and Phase Array/Compensation tab in FIG. 11B.

The Preliminary Test Results box shown in FIG. 10 contains two numeric indicators that present intermediate results of the test, also displayed on the Incident Energy Tab. These indicators display estimated bolted fault current in amps and reactance-resistance ratio (X/R ratio) of the system's Thevenin impedance. Calculations and algorithms used in calculating these values are discussed in detail in the forthcoming subsection.

In the lower left-hand corner of the box titled Per Unit Parameters of FIG. 10, additional calculations are incorporated to determine the per-unit system impedance based on user input values. To obtain these values, the user manually enters the system per-unit voltage base  $(V_{base})$  and per-unit power base  $(S_{base})$ .

In the lower center of the exemplary screen of FIG. 10 is an additional informational box, titled System Parameters. This box provides data about the system that is used in calculating intermediate results: bolted fault current and X/R ratio. Power System Voltage Drop is a complex numeric value that estimates the voltage drop in the power system due to the change in loading conditions. This value is derived from measured values of voltage drop across a known load and observed phase shift of the voltage fundamental. Power System Impedance is a complex numeric value that estimates the power system impedance in terms of resistance and reactance on a 60 Hz base. This value is used to compute the bolted fault current that is possible at the test site. Test Resistance gives information on the resistance calculated by taking a ratio of averaged load voltage to averaged load current during the test. This value should remain relatively constant since the load is resistive; however, some variation may be observed due to heating of the resistor coils and is a function of the duration and frequency of testing.

Some compensation is provided to these values based on the cable leads used to connect the test buss to the IADD. Two modes or time periods are commonly referred to herein Pre-Test mode is the time period prior to switching of the resistive load bank into the circuit while In-Test mode is the time period in which current is flowing through the load bank.

The Test Results—Details tab, depicted in FIG. 11A, displays all measured values taken from each phase of the system. The three phase values are averaged and the calculated value is displayed in the fourth column of the display. Several frequency based measurements are made on the incoming voltage waveforms.

Pre-Test Voltage parameter measures and displays the three phase voltages prior to switching in the resistive load bank. The RMS measurement is made over approximately thirty (30) cycles just before switching in the load in an attempt to mitigate the facility's load switching or cycling on the power system as a source of error due a test sequence. The three phases are then averaged and displayed in the first row, fourth column of FIG. 11A.

In-Test Voltage parameter measures and displays the three phase voltages after switching in the resistive load bank. The RMS measurement is made over a few cycles (e.g., 4-5) after switching for the same reasons applied to Pre-Test Voltage

RMS measurements. The three phases are then averaged and displayed in the second row, fourth column of FIG. 11A.

Pre-Fault Current parameter is displayed for test validation purposes and is measured over the same time interval as Pre-Test Voltage parameter. These values should always be 5 approximately zero, though some variation (less than one-half of an amp) is often observed due to noise inherent in the system and the large gain factor used in signal processing.

In-Fault Current parameter measures and displays the three phase currents after switching in the resistive load bank. The 10 RMS measurement is made over the same time interval as In-Test Voltage parameter. The three phases are then averaged and displayed in the fourth row, fourth column of FIG. 11A.

60 Hz Phase Shift parameter is a measure of the change in phase shift, based on calculations including Window Drift compensation (see below). Accurate phase shift detection is extremely critical in estimating system parameters, particularly X/R Ratio. The method and means of compensation are discussed in detail herein.

Window Drift displays the estimated shift in voltage from the reference phase angle due to sampling frequency imposed during test conditions. Optimal sampling frequency was determined by applying guidelines from National Instruments related to sampling and also by observing the phase shift on a cycle by cycle basis and minimizing this value, 25 resulting in a sampling frequency that most closely coincides with the 60 Hz fundamental to be measured. Because the DAQ system is not synchronized with the power system frequency and is clocked internally, frequency drift may vary with changes in ambient temperature inside of the computer chassis. The Phase Drift Error Check indicator light alters the user if phase drift exceeds, for example, one (1) degree per cycle.

The exemplary Phase Array/Compensation tab screen, depicted in FIG. 11B, displays information about phase angle 35 changes on a cycle by cycle basis and allows the user to compensate for wire lead impedance that may otherwise skew final bolted fault current calculations.

The three arrays displayed on this tab give information on phase angle as it is output by the FFT calculation used to track 40 phase shift. Each number represents a fundamental phase angle unique to each cycle of the phase voltage waveform for each phase measured during the entire duration of the test. Ideally, the value should not vary under steady state conditions from cycle to cycle, except when there is a change in the 45 system, such as the moment that the resistive load bank is switched into the circuit. However, due to slight differences in sampling frequency with respect to the 60 Hz input waveform, there is some drift noted from cycle to cycle. The program has been optimized with respect to sampling frequency to minimize the amount of variation due to sampling frequency and additional compensation is made as part of the window drift parameter previously discussed herein.

Compensation for connection cable length has been implemented to take into account additional impedance of the lead 55 wires that would not be present should a fault occur at a buss under test. In one embodiment of the current version of the IADD, the impedance values are selected for #8 AWG wire because this is the size wire used for testing. Other embodiments can include a user selection for wire size and type of 60 wire-way used in connection the IADD to the measurement point implemented as a lookup table that selects values as they are given in National Electric Code (NEC), or other appropriate documents. The user can select the length of the wire connection and a calculation is made based on the 65 expected additional impedance input to the system as a result of this wire length. Additional compensation is made inter-

18

nally for the line-side fuses used to protect the system and is generally not a user defined variable.

#### 3. Voltage

The exemplary Voltage display screens give graphical information about the last test conducted. The Overview tab is displayed in FIG. 12 and additional test information is provided in Gate On tab in FIG. 13A and Commutation OFF tab in FIG. 13B.

The Voltage—Overview tab, shown in FIG. 12, displays detailed Pre-Test and In-Test voltage waveforms (approximately three cycles each) in the two smaller waveform graphs at the bottom. The top graph shows the total observed waveform for the duration of the test. This is useful for quickly evaluating the validity of test results since the user can view voltage waveforms to verify that no unexpected transient condition was present during the test. To the left of the detailed Pre-Test and In-Test graphs are RMS calculations and approximate voltage imbalance.

Because the system measures voltage on a per phase basis, the voltage imbalance equation has been modified from the standard accepted NEMA voltage imbalance equation. The calculation assumes that phase voltages are reasonably balanced and the following formula is applied:

$$V_{lmbalance} = \frac{\left(V_{\theta-MAX} - V_{3\theta-Average}\right)}{V_{3\theta-Average}} \tag{1}$$

Care should be taken when applying this equation since its use is for ascertaining whether the system unbalance is within acceptable levels. In other embodiments, other accepted unbalance formulas could be used, such as the one found in NEMA/ANSI C84.1.

FIG. 13A illustrates an exemplary Voltage—Gate ON tab, which displays the three phase voltage waveforms at the moment of switching. No calculations are associated with this tab and the waveforms are presented for information purposes only.

FIG. 13B illustrates an exemplary Voltage—Commutation OFF tab, which displays the three phase voltage waveforms at the moment of switching. No calculations are associated with this tab and the waveforms are presented for information purposes only.

#### 4. Current

An exemplary Current screen gives graphical information about the last test conducted. The Overview tab is displayed in FIG. 14 and additional test information is provided in Gate On tab in FIG. 15A and Commutation OFF tab in FIG. 15B.

FIG. 14 shows an exemplary Current—Overview tab, which displays detailed Pre-Test and In-Test current waveforms (approximately three cycles each) in the two smaller waveform graphs at the bottom. The top graph shows the total observed waveform for the duration of the test. This is useful in quickly evaluating the validity of test results since the user can view current waveforms to verify that no unexpected switching within the IADD occurred during the test. To the left of the detailed Pre-Test and In-Test graphs are RMS calculations and approximate current imbalance which are calculated using the same method presented in Equation 1, above.

The Current—Gate ON tab, shown in FIG. **15**A, displays the three line current waveforms at the moment of switching. No calculations are associated with this tab and the waveforms are presented for information purposes only.

The Current—Commutation OFF tab, shown in FIG. 15B, displays the three line current waveforms at the moment of

commutation. No calculations are associated with this tab and the waveforms are presented for information purposes only. Because commutation occurs naturally at a zero crossing and can vary between two cycles depending on point in wave when the gating signal is removed from the relays, these views each span several cycles of data. This has an effect on the phase angle during switching that is discussed in the following section.

## 5. Phase

The Phase page gives graphical information about the last 10 test conducted. The Overview tab is displayed in FIG. **16** and additional test information is provided in the Details tab displayed in FIG. **17**.

The exemplary Phase—Overview tab, shown in FIG. 16, displays a view of phase angles for each phase on a cycle by 15 cycle basis. Because the FFT algorithm produces only one phase data point at the fundamental per cycle, this graph is made up of discrete points connected by straight lines representing the values discussed above. A visual inspection of the phase arrays shows that detection of phase shift by the method described herein is viable. As expected, a phase shift occurs at the point when the load is connected to the system and a nearly identical shift in the opposite direction is observed when the load is disconnected.

The Phase—Overview tab, shown in FIG. 16, shows more 25 clearly how phase angle is affected due to load switching at the test point. Window drift can be apparent and manifests itself in the form of a slope in the phase angle from point to point that remains constant for the entire length of the test. Compensation can be made for this drift due to its constant 30 slope.

An additional variation in the phase angle can been seen when the resistive load is disconnected from the source. This variation is due to commutation of the current wave at the zero crossing in each line of the current waveform. One solid state relay commutates off prior to the other two, resulting in a single phase circuit. Current continues to flow through the two remaining conducting phases until their relays also commutate off. This transient condition can manifest itself as a larger than expected change in phase angle during the cycle when the single phase condition exists. As shown in FIG. 17 the phase returns to its steady state pre-test condition after the remaining conduction paths have commutated off and the load is fully disconnected from the source.

Testing Cycle and Back Panel Programming

Calculations used to determine power system impedance, bolted arc-fault current and incident energy are presented herein. The results of these calculations are ultimately applied to assigning an NFPA arc-flash category to the electrical node connected to the IADD.

In one aspect, DAQMX<sup>TM</sup> Assistant as part of the Lab-View<sup>TM</sup> software, allows a user to easily configure a National Instruments DAQ (data acquisition) card to input and output digital and analog signals, though other software packages and custom-developed software are contemplated within the 55 scope of the invention. This module is used to capture voltages and currents during the testing cycle, as well as to output signals to relays using internal computer power. The IADD device is configured, upon initialization, to obtain a predetermined number of samples at a user specified sampling rate. 60 Once a signal has been input into an array, various mathematical operations can be applied to the acquired and stored input signals for post processing.

For an aspect according to the present invention, a test sequence is divided into separate and independent acquisitions. During the first portion of the test, voltage and current are measured on, for example, a three phase basis to obtain a 20

baseline RMS values, though single-phase and other polyphase systems are contemplated within the scope of the embodiments of the present invention. An RMS calculation is performed on each phase of the system using analysis tools that are shipped with the software. The card can sample with, for example, 14 bit accuracy, so there is some quantization error associated with the RMS measurements. This percent error is a function of the voltage being measured, as the bits are distributed evenly over the range zero to ten volts. For example, if voltage of up to 1500 V (line-to-neutral) is read using the previously described voltage isolator, the resolution will be approximately 0.0488 V. With this level of resolution, a  $120V_{rms}$  signal would have a maximum error of 0.04% error and a  $330V_{1-n}$  (575  $V_{1-1}$ ) signal would have a maximum error of 0.01%.

In an attempt to further reduce error, the RMS values of each phase are averaged in the standard method and the average three phase RMS value is used in final calculations. During this portion of testing, no current flows in the test circuit, therefore no phase shift due to testing occurs.

For instance, FIG. 18 illustrates a LabView software implementation of calculations leading to determination of bolted fault duty. FIG. 19 illustrates a system diagram of the block diagram implementation of FIG. 18. FIG. 19 can be modeled by equation (2), which allows determination of Thevenin impedance. From this value, the bolted fault current, arc-flash incident energy and X/R ratio (ratio of reactance to resistance) can be determined.

Power System Impedance or Z<sub>Power System</sub>

Power System Impedance or  $Z_{Power System} =$

$\frac{\overline{V}_{\textit{Pre-Fault}} \angle 0^0 - \overline{V}_{\textit{In-Fault}} \angle \theta_{\textit{PhaseShift}}}{I_{\textit{In-Fault}} \angle \theta_{\textit{PhaseShift}}}$

(2)

Therefore, the following values are obtained in order to determine the Thevenin impedance, where the vertical bars indicate the magnitude of the phasor quantity:  $|\nabla_{Pre-Fault}|$ ,  $|\nabla_{In-Fault}|$ ,  $|\Pi_{In-Fault}|$  and  $\overline{\theta}_{PhaseShift}$ . Note that the phase angle of the pre-test (open circuit) voltage,  $\nabla_{Pre-Fault}$ , can be set to zero degrees for a convenient (and arbitrary) reference.

In one aspect, two separate calculations are performed approximately simultaneously to find these variables. One algorithm is used to determine voltage and current magnitudes, the other is used to define phase angle. Furthermore, the phase angle algorithm is sub-divided into two parts: (i) forming the phase angle data into a matrix and (ii) performing specific calculations using elements of this matrix.