### Rose-Hulman Institute of Technology Rose-Hulman Scholar

Graduate Theses - Electrical and Computer Engineering

Graduate Theses

Spring 5-2016

# NEUROSim: Naturally Extensible, Unique RISC Operation Simulator

David Eric McNeil Rose-Hulman Institute of Technology, mcneilde@rose-hulman.edu

Follow this and additional works at: http://scholar.rose-hulman.edu/electrical\_grad\_theses Part of the <u>Other Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

McNeil, David Eric, "NEUROSim: Naturally Extensible, Unique RISC Operation Simulator" (2016). Graduate Theses - Electrical and Computer Engineering. Paper 8.

This Thesis is brought to you for free and open access by the Graduate Theses at Rose-Hulman Scholar. It has been accepted for inclusion in Graduate Theses - Electrical and Computer Engineering by an authorized administrator of Rose-Hulman Scholar. For more information, please contact weir1@rose-hulman.edu.

### **NEUROSim:**

### Naturally Extensible, Unique RISC Operation Simulator

A Thesis

Submitted to the Faculty

of

Rose-Hulman Institute of Technology

by

David Eric McNeil

In Partial Fulfillment of the Requirements for the Degree

of

Master of Science in Electrical Engineering

May 2016

©2016 David Eric McNeil

# **ROSE-HULMAN INSTITUTE OF TECHNOLOGY**

**Final Examination Report**

David E. McNeil

Electrical Engineering

Name

Graduate Major

DATE OF EXAM:

April 22, 2016

**EXAMINATION COMMITTEE:**

| Thesis Advisory Committe     | ee Department |

|------------------------------|---------------|

| Thesis Advisor: Daniel Chang | ECE           |

| Yong Jin Kim                 | ECE           |

| Mario Simoni                 | ECE           |

| Claude Anderson              | CSSE          |

| PASSED X FAI                 | ILED          |

#### ABSTRACT

McNeil, David Eric M.S.E.E Rose-Hulman Institute of Technology May 2016 NEUROSim: Naturally Extensible, Unique RISC Operation Simulator Thesis Advisor: Dr. Daniel Chang

The NEUROSim framework consists of a compiler, assembler, and cycle-accurate processor simulator to facilitate computer architecture research. This framework provides a core instruction set common to many applications and a simulated datapath capable of executing these instructions. However, the core contribution of NEUROSim is its flexible and extensible design allowing for the addition of instructions and architecture changes which target a specific application. The NEUROSim framework is presented through the analysis of many system design decisions including execution forwarding, control change detection, FPU configuration, loop unrolling, recursive functions, self modifying code, branch predictors, and cache architectures. To demonstrate its flexible nature, the NEUROSim framework is applied to specific domains including a modulo instruction intended for use in encryption applications, a multiply accumulate instruction analyzed in the context of digital signal processing, Taylor series expansion and lookup table instructions applied to mathematical expression approximation, and an atomic compare and swap instruction used for sorting.

**Keywords:** electrical engineering, computer architecture, RISC, compiler, assembler, simulator

### DEDICATION

To my wife, Meg, for her constant encouragement and love. I am truly blessed to have you in my life. And to my parents, David and Dorothy, for their support, love, and wonderful examples.

#### ACKNOWLEDGEMENTS

I would like to express my gratitude to my advisor, Dr. Daniel Chang, for his time, expertise, and dedication. I appreciate the many hours you spent meeting with me, reviewing this document, and practicing with me for the defense. I would also like to thank the members of my defense committee Dr. Claude Anderson, Dr. Yong Jin Daniel Kim, and Dr. Mario Simoni for their time and valuable suggestions.

### TABLE OF CONTENTS

| $\mathbf{LI}$ | LIST OF FIGURES                  | iv   |

|---------------|----------------------------------|------|

| $\mathbf{LI}$ | LIST OF TABLES                   | vi   |

| $\mathbf{LI}$ | LIST OF CODE EXCERPTS            | viii |

| $\mathbf{LI}$ | LIST OF ABBREVIATIONS            | x    |

| 1             | 1 Introduction                   | 1    |

|               | 1.1 Background Knowledge         | 1    |

|               | 1.2 NEUROSim Implementation      |      |

| <b>2</b>      | 2 Related Work                   | 3    |

| 3             | 3 Motivation                     | 4    |

| 4             | 4 Axon (Compiler)                | 5    |

|               | 4.1 Supported Syntax             | 6    |

| <b>5</b>      | 5 Synapse (Assembler)            | 7    |

|               | 5.1 Register Sets                | 7    |

|               | 5.2 Instruction Set Architecture | 9    |

|               | 5.3 Sample Compiled Code         |      |

| 6             | 6 Neurosim (Simulator)           | 14   |

|               | 6.1 The Datapath                 | 15   |

| 7             | 7 Hardware Design Decisions      | 17   |

|               | 7.1 Execute Forwarding           |      |

|               | 7.2 Control Change Detection     |      |

|               | 7.3 FPU Configuration            |      |

|               | 7.4 Conclusion                   |      |

| 8             | 8 Software Design Decisions      | 21   |

|    | 8.1  | Loop Unrolling                        | 22 |

|----|------|---------------------------------------|----|

|    | 8.2  | Recursive Function Calls              | 23 |

|    | 8.3  | Self Modifying Code                   | 24 |

| 9  | Bra  | nch Prediction                        | 25 |

|    | 9.1  | Static Branch Predictors              | 26 |

|    | 9.2  | Dynamic Branch Predictors             | 27 |

| 10 | Cac  | he Architecture                       | 29 |

| 11 | Setu | up and Configuration of Examples      | 31 |

| 12 | Mo   | dulo Instruction                      | 32 |

| 13 | Dig  | ital Signal Processing Example        | 35 |

|    | 13.1 | Lowpass Filter                        | 35 |

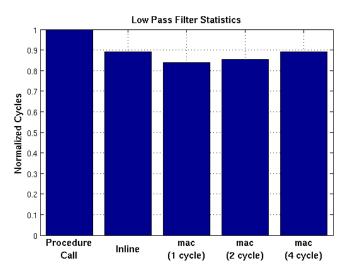

|    | 13.2 | Multiply Accumulate (MAC) Instruction | 37 |

|    | 13.3 | Lowpass Filter Implementation         | 38 |

| 14 | Mat  | thematical Expression Approximation   | 40 |

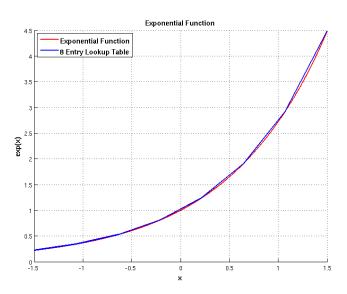

|    | 14.1 | Lookup Table Approximation            | 40 |

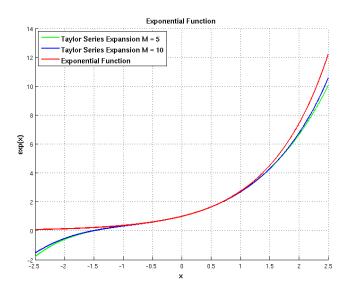

|    | 14.2 | Taylor Series Expansion Approximation | 42 |

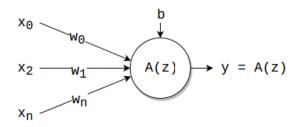

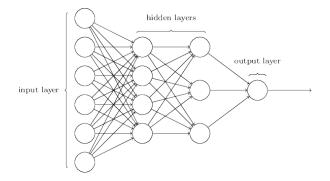

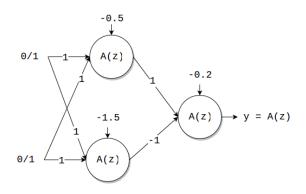

|    | 14.3 | Artificial Neural Network Example     | 43 |

| 15 | Arr  | ay Sorting Example                    | 47 |

|    | 15.1 | Compare and Swap (CAS) Instruction    | 47 |

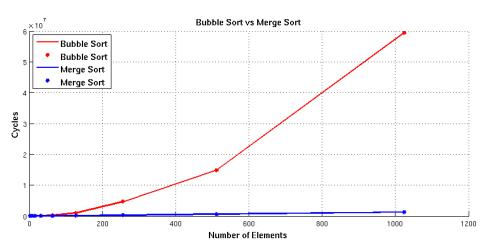

|    | 15.2 | Bubble Sort vs Merge Sort             | 49 |

| 16 | Con  | aclusion                              | 51 |

| 17 | Fut  | ure Work                              | 52 |

| A  | PPE  | NDIX                                  | 69 |

### LIST OF FIGURES

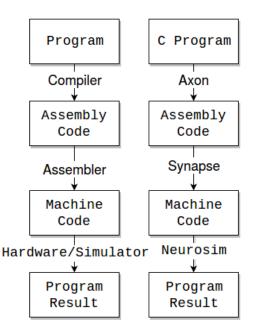

| 1  | The NEUROSim technology stack.                         | 3  |

|----|--------------------------------------------------------|----|

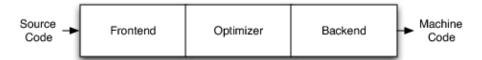

| 2  | Compiler architecture [1].                             | 6  |

| 3  | LLVM retargetable architecture [1]                     | 6  |

| 4  | RISC datapath [2]                                      | 16 |

| 5  | Data hazard [2]                                        | 18 |

| 6  | Loop unrolling statistics graph.                       | 23 |

| 7  | 2-bit saturating counter state diagram                 | 27 |

| 8  | Branch predictor statistics graph.                     | 28 |

| 9  | Basic cache structure                                  | 29 |

| 10 | Cache hit rates graph.                                 | 31 |

| 11 | Modulo test program statistics graph                   | 34 |

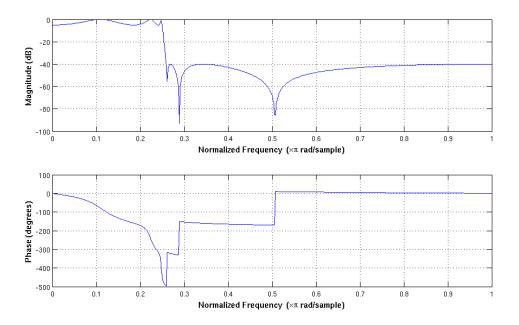

| 12 | Lowpass filter magnitude and frequency response.       | 36 |

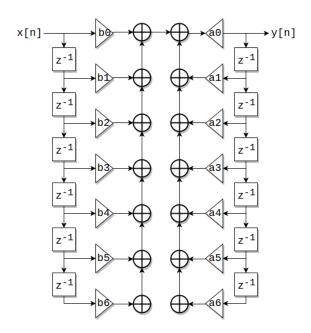

| 13 | Flowgraph representation of filter                     | 37 |

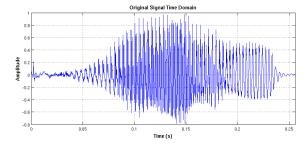

| 14 | Original signal time domain                            | 38 |

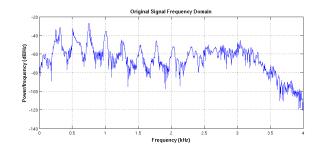

| 15 | Original signal frequency domain.                      | 38 |

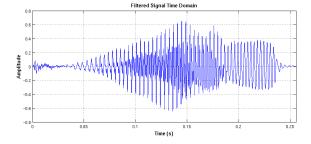

| 16 | Filtered signal time domain.                           | 38 |

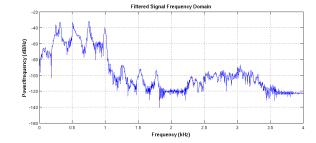

| 17 | Filtered signal frequency domain.                      | 38 |

| 18 | Low pass filter statistics graph.                      | 39 |

| 19 | Exponential function with lookup table approximation.  | 41 |

| 20 | Exponential function with Taylor series approximation. | 42 |

| 21 | Single artificial neuron.                              | 44 |

| 22 | Artificial neural network [3]                          | 44 |

| 23 | XOR neural network.                                    | 44 |

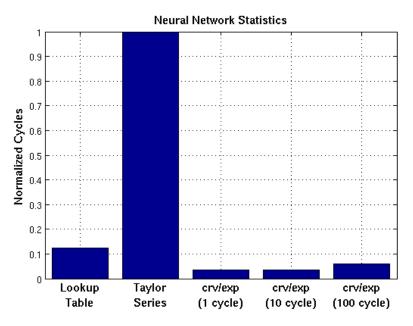

| 24 | Neural network statistics graph | 46 |

|----|---------------------------------|----|

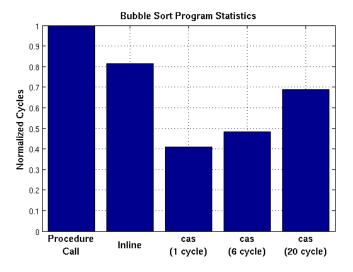

| 25 | Bubble sort statistics graph    | 48 |

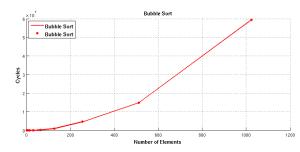

| 26 | Bubble sort run time            | 50 |

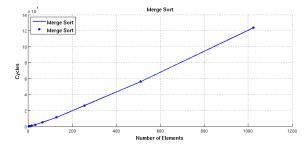

| 27 | Merge sort run time             | 50 |

| 28 | Bubble Sort vs Merge Sort.      | 50 |

### LIST OF TABLES

| 1  | Single precision floating point format.                           | 8  |

|----|-------------------------------------------------------------------|----|

| 2  | Integer registers.                                                | 9  |

| 3  | Floating point registers.                                         | 9  |

| 4  | Instruction formats.                                              | 10 |

| 5  | R type instructions                                               | 11 |

| 6  | I type instructions.                                              | 12 |

| 7  | M type instructions.                                              | 12 |

| 8  | B type instructions                                               | 12 |

| 9  | J type instructions.                                              | 12 |

| 10 | FR type instructions                                              | 13 |

| 11 | FI type instructions.                                             | 13 |

| 12 | FM type instructions                                              | 13 |

| 13 | FB type instructions                                              | 13 |

| 14 | Assembly directives.                                              | 14 |

| 15 | Execute forwarding statistics.                                    | 19 |

| 16 | Control change detection statistics.                              | 20 |

| 17 | FPU configuration statistics                                      | 21 |

| 18 | Loop unrolling statistics.                                        | 22 |

| 19 | Factorial algorithm statistics.                                   | 24 |

| 20 | Self modifying code statistics.                                   | 25 |

| 21 | Static branch predictor statistics.                               | 26 |

| 22 | Dynamic branch predictor statistics.                              | 28 |

| 23 | Cache example configuration: Size=64, Associativity=2, LineSize=4 | 30 |

| 24 | Cache hit rates.                                    | 31 |

|----|-----------------------------------------------------|----|

| 25 | MOD instruction.                                    | 33 |

| 26 | Modulo test program statistics                      | 34 |

| 27 | MAC instruction.                                    | 37 |

| 28 | Lowpass filter statistics.                          | 39 |

| 29 | Lookup table approximation instruction.             | 41 |

| 30 | Taylor series exponential approximation instruction | 42 |

| 31 | XOR logic table.                                    | 44 |

| 32 | XOR neural network output                           | 45 |

| 33 | Neural network statistics.                          | 45 |

| 35 | CAS instruction.                                    | 47 |

| 36 | Bubble sort statistics                              | 48 |

| 37 | Bubble Sort vs Merge Sort statistics.               | 50 |

### LIST OF CODE EXCERPTS

| 1  | Axon supported syntax.                   | 55 |

|----|------------------------------------------|----|

| 2  | Addition in C                            | 56 |

| 3  | Addition in assembly.                    | 56 |

| 4  | For loop in C                            | 57 |

| 5  | For loop in assembly                     | 57 |

| 6  | Function call in C.                      | 57 |

| 7  | Function call in assembly.               | 57 |

| 8  | Execute forwarding example               | 58 |

| 9  | Control change detection example.        | 58 |

| 10 | FPU configuration example.               | 58 |

| 11 | Loop unrolling.                          | 59 |

| 12 | Recursive implementation of factorial    | 59 |

| 13 | Loop implementation of factorial.        | 60 |

| 14 | Self modifying code.                     | 60 |

| 15 | Branch prediction test.                  | 61 |

| 16 | Random cache access.                     | 62 |

| 17 | Few random cache access.                 | 62 |

| 18 | Linear cache access.                     | 63 |

| 19 | Inlined function example                 | 63 |

| 20 | Modulo test program                      | 64 |

| 21 | Mac Instruction                          | 65 |

| 22 | Lookup table exponential approximation   | 66 |

| 23 | Taylor series exponential approximation. | 67 |

| 24 | Bubble sort | 68 |

|----|-------------|----|

| 25 | Merge sort. | 68 |

### LIST OF ABBREVIATIONS

- ALU ..... Arithmetic Logic Unit

- CAS..... Compare And Swap

- CISC..... Complex Instruction Set Computer

- CPU ..... Central Processing Unit

- DSP..... Digital Signal Processing

EX..... Execute Stage

FPU ..... Floating Point Unit

ID..... Instructions Decode Stage

IF ..... Instructions Fetch Stage

IPC . . . . . Instructions Per Cycle

IR..... Intermediate Representation

ISA ..... Instructions Set Architecture

L1..... Level 1 Cache

- MAC..... Multiply Accumulate

- MEM..... Memory Stage

- MOD....Modulo

- NOP ..... No Operation

- RISC..... Reduced Instruction Set Computer

- SPU..... Special Purpose Unit

- WB . . . . . Write Back Stage

- $\operatorname{XOR}$  ..... Exclusive Or

### 1 INTRODUCTION

Computers are everywhere and range in complexity from multi-core supercomputers to simple microprocessors. Behind each of these computers is a processor which has undergone a series of design decisions intended to optimize the computer for a specific purpose or a target domain. These design decisions are intended to strike a balance between a variety of factors including speed, power, area, and cost. During the design process, a simulator capable of quantifying the consequences of a given design decision becomes invaluable. They provide a method to quickly determine the merits of a design without requiring the resources of an actual implementation.

The NEUROSim framework provides a cycle-accurate simulator targeting a reduced instruction set computer (RISC) architecture and the surrounding resources for targeting this architecture including an assembler and compiler. The simulator is capable of executing a core instruction set common to many applications, but the primary contribution of NEU-ROSim is its flexible and extensible design allowing this core instruction set to be augmented by instructions optimized for a specific domain.

#### 1.1 Background Knowledge

The NEUROSim framework is intended to encompass the design process from implementing an algorithm in software to executing that software on a hardware platform. The interaction of software with hardware has multiple layers of abstraction intended to ease human computer interaction as well as generalize this interaction over a variety of platforms. A look at the various components in this stack is necessary in order to fully understand the breadth of NEUROSim.

At a high level, a computer program is written in a programming language. In general this program is intended to be capable of running on multiple hardware platforms. Assuming this language is a compiled language, this program will be passed through an architecture specific compiler which converts the high level language into assembly code for the targeted platform. The assembly code describes the program in terms of instructions in the hardware's instruction set architecture (ISA). After being compiled, the resulting assembly program is passed through an assembler which converts the assembly program into machine code. The machine code is a binary representation of the assembly program. This binary representation can then be loaded into the memory of a processor and executed on hardware or passed to a simulator capable of simulating the execution. Executing a program in a simulator has the advantage of allowing one to easily record statistics on the underlying hardware beyond what the program has been programmed to output. Simulators allow one to easily change the configuration of the underlying hardware and quickly obtain statistics on the corresponding performance changes. This tight feedback loop of being able to make a design decision and quickly view its results is what makes simulators an indispensable tool in the design process. This is in contrast to requiring design decisions be implemented in actual hardware before their merits can be determined.

#### 1.2 **NEUROSim Implementation**

The NEUROSim framework includes specific implementations of each of the components in the aforementioned stack as seen in Figure 1. The components of NEUROSim are named after components of a neuron because NEUROSim was originally developed with the intent of optimizing an architecture for simulating neurons. The programming language used by the NEUROSim framework is a subset of C. The NEUROSim compiler is named Axon, the assembler is named Synapse, and the simulator is named Neurosim (not to be confused with NEUROSim which represents the entire framework).

This document begins by examining related work in computer architecture simulators, motivates the contribution of NEUROSim, and analyzes the individual components of NEU-ROSim. Then this document inspects system design decisions in the context of NERUOSim including execute forwarding, control change detection, floating point unit (FPU) configuration, loop unrolling, recursive functions, self modifying code, branch predictors, and cache

Figure 1: The NEUROSim technology stack.

architectures. To demonstrate its flexible nature, the NEUROSim framework is applied to specific domains namely implementing a modulo instruction intended for use in encryption applications, a multiply accumulate instruction analyzed in the context of digital signal processing, Taylor series expansion and lookup table instructions applied to mathematical expression approximation, and an atomic compare swap instruction used for sorting. Finally, this document concludes by proposing potential future work. The relevant code excerpts can be found at the end of this document in the appendix.

### 2 Related Work

There exists a plethora of computer architecture simulators, SimpleScalar [4], gem5 [5], and MARSSx86 (Micro-ARchitectural and System Simulator for x86-based Systems) [6], to name a few. These simulators are primarily concerned with supporting cutting edge research in computer architecture. As such they focus on supporting existing ISAs and platforms. For example, gem5 focuses on supporting interchangeable CPU (central processing unit) models for the Alpha, ARM, SPARC, MIPS, POWER, and x86 ISAs [5], and the MARSSx86 provides full system simulation of the x86-64 architecture [6]. These simulators use existing tool chains for handling the compiling and assembling of the programs they run. The ability to use existing tools is excellent for comparing the impact of computer architecture research as it provides a common benchmark by which to compare changes. However, because these simulators use existing tools and implement existing ISAs, these simulators are somewhat limited to analyzing changes which advance existing technologies. For instance, it would be difficult to develop a custom ISA for a target application or optimize a compiler for a specific algorithm using these simulators. These simulators are intended to be used for computer architecture design and analysis, but are not intended to be used as full system design and analysis tools. NEUROSim aims to differentiate itself from these other simulators because it is intended to be used as a design tool from compiler optimizations to ISA design to hardware configuration.

### 3 MOTIVATION

NEUROSim aims to provide the design tools for custom RISC architectures, ISAs, and software development tools. NEUROSim's target use case is as follows. There is a given domain which could potentially see a performance increase by using a custom instruction. NEUROSim provides a way to quickly add this instruction and evaluate its benefit. First, the logic to execute the instruction is added to the simulator. Then, the ability to translate the instruction is added to the assembler. Finally, the compiler is edited to generate the new instruction. The properties of the new instruction can now be configured to strike a balance between the performance of the algorithm given the new instruction and design parameters from other sources such as cost, area, and power. The results of the simulation can potentially follow two paths. It could be deemed that adding the new instruction is not worth the resources. In which case, the simulator was still successful because it avoided the need to implement the proposed change to come to this conclusion. The other outcome is that a good balance of the relevant parameters was determined and the designer now has a set of target specifications and an approximation of the corresponding performance benefits.

Essentially, NEUROS is a tool intended to aid in striking a balance between hardware and software components of a system. Hardware represents the spatial component of the design and consumes space and power. Whereas, software represents the temporal portion of design taking a given amount of time to run. Software layers abstract away components of the hardware layer easing software development. However, the price of these abstractions is a loss of control over the underlying hardware. The purpose of NEUROSim is to give direct control over these abstractions allowing the user to determine what portion of the algorithm should be handled by hardware and what portion should be handled by software. NEUROSim is intended to provide exactly what the standard computer architecture simulators provide, a tight feedback loop between design and results, but with a broader scope. The ability to simulate all components of a system during the design process significantly reduces the resources needed to try a new design. Simulation allows the design process to be easily modeled as an optimization problem where the optimization parameters are the various parameters of the simulator. These parameters are adjusted to find an optimal configuration in regard to a specific output parameter such as latency, area, or power. Simulation even allows for the automation of this optimization process where an algorithm is used to fine-tune parameters until a desired outcome is reached.

### 4 AXON (COMPILER)

Axon is responsible for converting a program written in the supported subset of C to the NEUROSim ISA. Axon is implemented using the LLVM toolchain. "The LLVM Project is a collection of modular and reusable compiler and toolchain technologies [7]."

Basic compiler architecture is composed of a front end, an optimizer, and a back end as seen in Figure 2. The front end converts the source code of a programming language into an intermediate representation (IR). This intermediate representation is then used to perform optimizations. Finally, this intermediate language is converted to the target assembly. This architecture segments the development of the front end, optimizer, and back end allowing for individuals to tap into any layer of this stack without having to reinvent the other components. Figure 3 illustrates how this architecture can support multiple front end languages which all compile down to the common IR code. This IR code can then undergo a set of common optimizations and finally be converted by the back end to the desired hardware platform.

Figure 2: Compiler architecture [1].

Figure 3: LLVM retargetable architecture [1].

The segmented design of LLVM allows Axon to use an existing C front end known as Clang [8] and a common set of optimizations. However, a new back end was written capable of converting the LLVM IR code to the NEUROSim ISA.

#### 4.1 Supported Syntax

Currently, the Axon compiler supports a subset of C. The available syntax constructs are illustrated in Code 1. The next section will examine NEUROSim's instruction set and how the compiler converts C code into equivalent assembly language expressions.

## 5 SYNAPSE (ASSEMBLER)

Synapse is responsible for converting the assembly program output of Axon to machine code. The tools Flex [9] and Bison [10] were used to construct the assembler. Flex is a lexical analysis generator and Bison is a parser generator. The lexical analyzer produces a token stream given an input file and a specified grammar. Bison generates a parser which given a token stream and grammar applies meaning, or semantics, to the lexical structure. In the case of an assembler, the tokens are instructions, labels, and assembler directives, and the meaning is the corresponding machine code. Intrinsic to the assembler's function are the ISA and register set used by the underlying hardware.

#### 5.1 Register Sets

NEUROSim's ISA works on two sets of thirty-two element 32-bit register files. One register file holds integer values while the other holds single precision floating point values. It is important to realize that the registers in both register files are simply 32-bit values. It is the way these values are interpreted which dictates the type. The integer registers are interpreted as two's complement while the floating point registers are interpreted according to the IEEE floating point standards, shown in Table 1 and Equation 1. The range of integer values is calculated with Equation 2 and the floating point max value is calculated with Equation 3. Floating point values guarantee six digits of precision. The register files were split, instead of using a single sixty-four register register file, because it has been found that partitioning the register file decreases access latency as well as providing the possibility to read from both register files simultaneously [11].

| $sign{32}$ | $exponent{30-23}$ | $fraction{22-0}$ |

|------------|-------------------|------------------|

|            |                   |                  |

Table 1: Single precision floating point format.

$$FP_{value} = (-1)^{sign} * (1 + \sum_{i=1}^{23} fraction_{23-i}2^{-i}) * 2^{exponent-127}$$

(1)

$$min = -1 \times 2^{32-1} = -2,147,483,648$$

$$max = 2^{32-1} - 1 = 2,147,483,647$$

(2)

$$(1 - 2^{-24}) * 2^{128} \approx 3.402823466 \times 10^{38}$$

(3)

Table 2 lists the integer registers and Table 3 lists the floating point registers. The first column indicates the unique token by which the register is identified in the assembly language. The assembler converts this token to the index of the register in the register file. In the third column, the table indicates whether or not the register is preserved following a call to a function. Common to both register files is a hardwired zero register, a reserved register for use by the assembler and compiler, and sets of both temporary and saved registers. The integer register file also contains special registers which could potentially be used by an operating system kernel as well as registers to track the global data pointer, stack pointer, frame pointer, and return address from a function call.

| Register         | Description                          | Preserved |

|------------------|--------------------------------------|-----------|

| rO               | Hardwired to zero.                   | NA        |

| at               | Reserved for assembler and compiler. | NA        |

| v0, v1           | Return values from functions.        | Ν         |

| a0 - a3          | Arguments to functions.              | Ν         |

| t0 - t9          | Temporary registers.                 | Ν         |

| s0 - s7          | Saved registers.                     | Y         |

| k0, k1           | Reserved for kernel.                 | NA        |

| gp               | Global data pointer.                 | NA        |

| $^{\mathrm{sp}}$ | Stack pointer.                       | NA        |

| fp               | Frame pointer.                       | NA        |

| ra               | Return address.                      | Ν         |

Table 2: Integer registers.

Table 3: Floating point registers.

| Register   | Description                          | Preserved |

|------------|--------------------------------------|-----------|

| fr0        | Hardwired to zero.                   | NA        |

| fat        | Reserved for assembler and compiler. | NA        |

| fv0, fv1   | Return values from functions.        | N         |

| fa0 - fa3  | Arguments to functions.              | N         |

| ft0 - ft11 | Temporary registers.                 | N         |

| fs0 - fs11 | Saved registers.                     | Y         |

#### 5.2 Instruction Set Architecture

The instruction set provides the programmer a set of commands which can be used to modify the underlying hardware, specifically the registers and memory, to produce meaningful and useful results. Table 4 shows the three instruction formats present in the ISA. "op" denotes the opcode of the instruction. An opcode is a unique identifier that the hardware can use to determine the type of the instruction. The opcode is six bits allowing for a total of sixty-four unique instructions. "reg" denotes a register identifier. "imm" indicates an immediate and "address" is an immediate which should be treated as an address to a location in instruction memory.

| Register Format |                                                         |                                         |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------|-----------------------------------------|--|--|--|--|--|--|

| op{31:26}       | $reg0{25:21}$ $reg1{20:16}$ $reg2{15:11}$ $unused{10:}$ |                                         |  |  |  |  |  |  |

|                 | Immediate Format                                        |                                         |  |  |  |  |  |  |

| op{31:26}       | reg0{25:21}                                             | $reg0{25:21}$ $reg1{20:16}$ $imm{15:0}$ |  |  |  |  |  |  |

|                 | Address Format                                          |                                         |  |  |  |  |  |  |

| op{31:26}       | $address{25:0}$                                         |                                         |  |  |  |  |  |  |

Table 4: Instruction formats.

Tables 5 – 13 represent the various types of instructions included in the ISA. The assembler assumes the instructions are written with the opcode preceding the operands. For example, "addi s6 t7 -6" would add -6 to the value of register "t7" and then store the result in register "s6". In the instruction type tables, lowercase register names represent the unique register identifier while capitalized register names represent the value of a register. An "f" preceding the identifier or value of a register indicates that it is a floating point register. For some instructions, a register is explicitly defined. For example, the "no operation" instruction (nop) uses implied argument "r0". The use of explicit registers like this indicates that when writing the instruction, specifying the operand is optional. If the register is not included the assembler will assume the indicated operand. All immediate values are sign extended before being used as operands. "MEM" represents a byte addressable memory block. and "PC" represents the program counter which is used to store the address of the current instruction.

Tables 5 - 9 display the integer instructions. These are divided into five instruction types. "R" type instructions are mathematical or logical operations. They also include the

special "brk" and "halt" instructions which indicate to the simulator either a breakpoint or the end of simulation. "I" type instructions are arithmetic and logic operators which take an immediate as the last operand. This type also includes instructions for loading an immediate into the lower and upper sixteen bits of a register. "M" type instructions deal with memory and can either be used to load memory data to a register or store register data to a memory address. "B" type instructions are used to handle conditional jumps to addresses in program memory. It is important to note that these jumps are relative to the current PC and not to an absolute address. This allows the branch instructions to handle a larger range of addresses. The "J" type instructions perform absolute jumps and provide the option to link. A jump and link stores the address of what would have been the next instruction in the return address register. This allows the called function to return to the calling location in program memory after it has completed execution.

| Opcode               | Op | erai | nds                 | Result                   |

|----------------------|----|------|---------------------|--------------------------|

| nop                  | r0 | r0   | r0                  |                          |

| add                  | rd | rs   | $\mathbf{rt}$       | RD := RS + RT            |

| sub                  | rd | rs   | $\operatorname{rt}$ | RD := RS - RT            |

| mul                  | rd | rs   | $\mathrm{rt}$       | RD := RS * RT            |

| div                  | rd | rs   | $\mathrm{rt}$       | $RD := RS \div RT$       |

| and                  | rd | rs   | $\mathbf{rt}$       | RD := RS & RT            |

| or                   | rd | rs   | $\mathbf{rt}$       | $RD := RS \mid RT$       |

| xor                  | rd | rs   | rt                  | $RD := RS \oplus RT$     |

| $\operatorname{shl}$ | rd | rs   | $\mathbf{rt}$       | RD := RS << RT           |

| shr                  | rd | rs   | rt                  | RD := RS >> RT           |

| slt                  | rd | rs   | rt                  | RD := RS < RT            |

| brk                  | r0 | r0   | r0                  | Indicates breakpoint     |

| halt                 | r0 | r0   | r0                  | Indicates end of program |

Table 5: R type instructions.

| Opcode | Operands |    | nds | Result                     |

|--------|----------|----|-----|----------------------------|

| addi   | rd       | rs | im  | RD := RS + im              |

| andi   | rd       | rs | im  | RD := RS & im              |

| ori    | rd       | rs | im  | $RD := RS \mid im$         |

| slti   | rd       | rs | im  | RD := RS < im              |

| loi    | rd       | r0 | im  | $RD := 0 \ge 0 \ge 0 $ im  |

| hii    | rd       | r0 | im  | $RD := (im << 16) \mid RD$ |

Table 6: I type instructions.

Table 7: M type instructions.

| Opcode | Operands |    | nds | Result             |

|--------|----------|----|-----|--------------------|

| lw     | rd       | rs | im  | RD := MEM[RS + im] |

| sw     | rd       | rs | im  | MEM[RS+im] := RD   |

Table 8: B type instructions.

| Opcode | Operands      |    | nds | Result                           |

|--------|---------------|----|-----|----------------------------------|

| beq    | $\mathbf{rs}$ | rt | im  | IF(RS = RT) : PC := PC + im      |

| bne    | $\mathbf{rs}$ | rt | im  | $IF(RS \neq RT) : PC := PC + im$ |

Table 9: J type instructions.

| Opcode | Operands |               | nds | Result                          |

|--------|----------|---------------|-----|---------------------------------|

| j      | address  |               | SS  | PC := address                   |

| jal    | address  |               | ss  | $RA := PC + 4; \ PC := address$ |

| jr     | r0       | rs            | r0  | PC := RS                        |

| jrl    | r0       | $\mathbf{rs}$ | r0  | RA := PC + 4; PC := RS          |

Tables 10 - 13 display the floating point instructions. These are divided into four instruction types. "FR" type instructions are general mathematical or logical operations. "FI" type instructions are used to load an immediate floating point value into a register. "FM" type instructions deal with memory and can either be used to load memory data to a register or store register data to a memory address. It is important to note that these instructions require an integer register and not a floating point register to represent the address. "FB" type instructions are used to handle conditional jumps in program memory.

| Opcode | Operands |     | nds | Result                |

|--------|----------|-----|-----|-----------------------|

| addf   | frd      | frs | frt | fRD := fRS + fRT      |

| subf   | frd      | frs | frt | fRD := fRS - fRT      |

| mulf   | frd      | frs | frt | fRD := fRS * fRT      |

| divf   | frd      | frs | frt | $fRD := fRS \div fRT$ |

| sltf   | frd      | frs | frt | fRD := fRS < fRT      |

Table 10: FR type instructions.

Table 11: FI type instructions.

| Opcode | Operands |     | $\mathbf{ds}$ | Result                                                            |

|--------|----------|-----|---------------|-------------------------------------------------------------------|

| lof    | frd      | fr0 | im            | $fRD := 0 \ge 0 $ |

| hif    | frd      | fr0 | im            | $fRD := (im \ll 16) \mid fRD$                                     |

Table 12: FM type instructions.

| Opcode | Operands |    | nds | Result              |

|--------|----------|----|-----|---------------------|

| lwf    | frd      | rs | im  | fRD := MEM[RS + im] |

| swf    | frd      | rs | im  | MEM[RS+im] := fRD   |

Table 13: FB type instructions.

| Opcode | Operands |     | nds | Result                             |

|--------|----------|-----|-----|------------------------------------|

| beqf   | frs      | frt | im  | IF(fRS = fRT) : PC := PC + im      |

| bnef   | frs      | frt | im  | $IF(fRS \neq fRT) : PC := PC + im$ |

Synapse is also capable of handling three assembly directives listed in Table 14 as well as labels which end in a colon. Labels provide a simple way for one instruction to refer to the memory address of a specific instruction or datum.

| Directive | Meaning                                          |

|-----------|--------------------------------------------------|

| .text     | Start of the text segment (program instructions) |

| .data     | Start of the static data segment                 |

| .datum    | 32 bits of data in the data segment              |

Table 14: Assembly directives.

#### 5.3 Sample Compiled Code

Code 2-6 are three simple examples of C code and the corresponding compiled assembly instructions. Comments have been included in the resulting assembly code to make it explicit what lines of assembly correspond to which C constructs.

### 6 NEUROSIM (SIMULATOR)

The Neurosim simulator is the core of the NEUROSim framework. Neurosim provides cycle-accurate execution of a program on a RISC datapath. Cycle-accurate indicates that the simulator is executing the program cycle-by-cycle, as opposed to simply using heuristics to determine the run time of the program. This is significant because in general the results of a cycle-accurate simulator will better represent the results of actual hardware.

The general idea behind a simulator is that the user can specify and change settings of the target datapath, run the program, and then see the resulting statistics. In Neurosim, the simulator settings are specified using a config file and the resulting statistics written to an output file. Some example settings would be the number of cycles an instruction takes in each stage of the datapath, memory size, cache configuration, and branch predictor algorithm. Examples of some of the statistics Neurosim reports are the count of retired instructions of a given type, the total number of cycles executed, the accuracy of the branch predictor, the hit rate of the cache, and the size of different memory segments.

#### 6.1 The Datapath

Processor design has two competing design philosophies RISC (reduced instruction set computer) versus CISC (complex instruction set computer) [12]. The tenants of a RISC architecture involve using a relatively small instruction set, consistent instruction length and format, register mapped operands, and relatively shallow pipelines. A CISC architecture generally embraces the converse of these philosophies having many instructions with different lengths and formats which make use of memory mapped operands. The pipeline of CISC architectures are often very deep and complex to facilitate the fetching and decoding of these complex instructions. In fact, one can think of CISC architectures as converting the complex instructions into a sequence of RISC like instructions which are then executed further along in the pipeline.

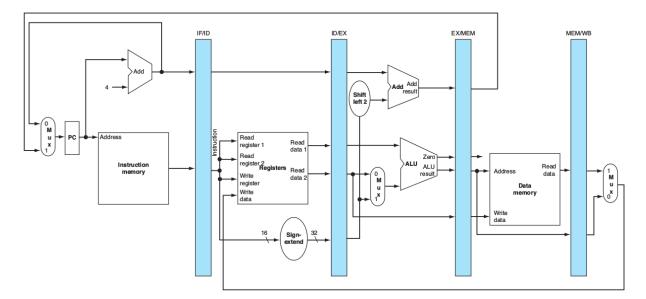

Neurosim simulates a pipeline very similar to the classic RISC pipeline illustrated in Figure 4. A RISC pipeline was chosen because it simplifies the primary purpose of NEUROSim, which is to provide for the addition of domain specific instructions. RISC processors are also more common in embedded systems, and embedded systems often involve developing a system optimized for a specific task. As such a RISC datapath was a natural choice for Neurosim. The software representations of the datapath was constructed with the intent of representing the hardware equivalent as faithfully possible. This is important because it allows users to make changes which are more likely to reflect the capabilities of actual hardware.

The simulated datapath is broken up into five distinct stages. The first stage is instruction fetch (IF) which simply retrieves the instruction at the address of the PC from instruction memory. The next stage, instruction decode (ID), decodes the instruction, determining the opcode of the instruction and producing the correct operands for subsequent stages. The

Figure 4: RISC datapath [2].

register file in Figure 4 is a black box representation of the two register files Neurosim uses. The datapath chooses the correct register file to read from either integer registers or floating point registers. After the instruction has been decoded, the operands enter into the execute stage (EX). Here the arithmetic logic unit (ALU) performs the correct operation on the operands. In the case of the Neurosim pipeline there are actually three potential logic units: the ALU, floating point unit (FPU), and the special purpose unit (SPU). The ALU is used for integer operations, the FPU operates on floating point values, and the SPU is used for special instructions which have been added to the ISA. The next stage is the memory stage (MEM) where the instruction can read from or write to data memory. Finally, the instruction enters the write back (WB) stage where the value computed by the instruction is written back to the appropriate register.

Neurosim implements a pipelined datapath meaning that the datapath does not wait to finish execution of an instruction to begin executing the next instruction. Instead, after one instruction leaves the IF stage the next instruction is fetched and execution begun. This significantly increases the instruction throughput of the datapath.

This concludes an overview of the three components of NEUROSim. To summarize,

Axon converts a source code file written in C to the supported assembly language. Synapse converts this textual assembly language to its binary equivalent. This binary file can then be passed to Neurosim for simulation.

### 7 HARDWARE DESIGN DECISIONS

Neurosim has been structured in such a way as to allow for modifications to the base datapath. This allows users to analyze the value of datapath enhancements in the context of a specific algorithm. Three such modifications are built into Neurosim. These optimizations will be analyzed with very simple examples, but these examples could easily be extrapolated to larger more complex algorithms.

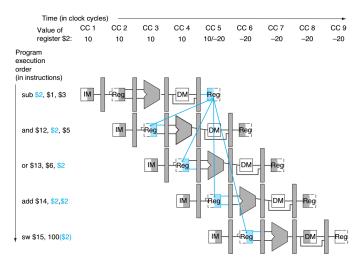

#### 7.1 Execute Forwarding

A data hazard is one of the most common hazards in a standard RISC pipeline. This situation arises when an instruction requires the data of a previous instruction which has not written the data back to the register file. Figure 5 illustrates this scenario. The simple fix is to simply stall the pipeline until the instruction has had a chance to write the necessary data. A more efficient method is to implement an execute forwarding unit. The unit is responsible for looking at the register operands of the incoming instruction and determining if the data should be retrieved from the register file or the output of the execute stage. Code 8 presents a very simple example program used to demonstrate the merits of execute forwarding.

An abbreviated version of the statistics from running the program in Neuosim are presented in Table 15. Each column represents a unique run of the simulator given different settings. In this case without and with execute forwarding. Statistic tables such as these are very common throughout this document and are the means by which various algorithms or hardware configurations are analyzed. In this case the first four rows represent the count of total retired instructions of the indicated type. Clearly, using execute forwarding results in a

Figure 5: Data hazard [2].

decrease in the number of no operations, "nops." The "NonNop Instructions" entry povides a count of the total number of retired instructions without counting "nops." This a measure of the amount of useful work done by the processor. In this case the datapath executed one addition instruction, one subtraction instruction, and two load immediate instructions, but the simulator reports five "NonNop Instructions" this is because the "halt" instruction, which is used to indicate the end of execution to the simulator, is also counted. The "Cycles" row is simply a count of the total number of cycles, including cycles spent on "nops," executed by the simulator before the simulator encountered the halt instruction. In this example, the "Cycles" row clearly illustrates the merits of using execute forwarding decreasing the total number of cycles from 13 to 9. The instructions per cycle (IPC) row provides a measure of the throughput of the datapath. Ideally this number would be one, indicating that every cycle an instruction is retired. There are many more statistics Neurosim reports which will be discussed as they arise.

|              | No Forwarding | With Forwarding |

|--------------|---------------|-----------------|

| nop          | 8             | 4               |

| add          | 1             | 1               |

| sub          | 1             | 1               |

| loi          | 2             | 2               |

| NonNop       | 5             | 5               |

| Instructions |               |                 |

| Cycles       | 13            | 9               |

| IPC          | 0.384615      | 0.555556        |

Table 15: Execute forwarding statistics.

#### 7.2 Control Change Detection

The pipelined structure of a RISC datapath works well until it encounters an instruction which changes the PC. Such instructions include jumps and taken branches. The datapath must now flush all of the previous instructions it has begun executing and fetch the correct instruction. This can severely reduce the IPC of the processor. The solution to this problem is to try and detect a control change as soon as possible. The traditional pipeline handles control change in the execute stage. However, hardware can be added to detect a jump or branch instruction in the decode stage or even as early as the fetch stage. Code 9 presents an example program used to demonstrate the merits of early control change detection with the statistics summarized in Table 16. The "Cycles" row can again be used to clearly demonstrate that early control change detection can improve pipeline performance.

|              | EX Detection | ID Detection | IF Detection |

|--------------|--------------|--------------|--------------|

| nop          | 1,014        | 913          | 812          |

| slt          | 101          | 101          | 101          |

| addi         | 102          | 102          | 102          |

| loi          | 3            | 3            | 3            |

| lw           | 201          | 201          | 201          |

| SW           | 102          | 102          | 102          |

| bne          | 101          | 101          | 101          |

| j            | 102          | 102          | 102          |

| NonNop       | 713          | 713          | 713          |

| Instructions |              |              |              |

| Cycles       | 1,727        | 1,626        | 1,525        |

| IPC          | 0.41285      | 0.43849      | 0.46754      |

Table 16: Control change detection statistics.

#### 7.3 FPU Configuration

A fundamental detail of an instruction in a RISC style processor is how many cycles it takes to complete a given stage. For most instructions, it is assumed that it only takes one cycle. However, it is typical that floating point instructions can take orders of magnitude longer in the execute stage than integer instructions. Neurosim provides for the easy customization of instruction cycle counts. A potential use case for this would be determining how fast to make the FPU. Neurosim quickly allows one to see the performance increase of a floating point unit with various cycle times. Code 10 presents an example program used to analyze different FPU execute cycle counts with the statistics summarized in Table 17. These statistics clearly demonstrate what one would expect. Increasing the cycle count of a stage significantly decreases the IPC slowing down the entire pipeline. The manual configuration of stage cycle counts will be used extensively as instructions are added to the core ISA.

|              | 1 Cycle | 10 Cycles | 40 Cycles |

|--------------|---------|-----------|-----------|

| nop          | 10      | 55        | 205       |

| addf         | 1       | 1         | 1         |

| subf         | 1       | 1         | 1         |

| mulf         | 1       | 1         | 1         |

| divf         | 1       | 1         | 1         |

| sltf         | 1       | 1         | 1         |

| lof          | 2       | 2         | 2         |

| hif          | 2       | 2         | 2         |

| NonNop       | 10      | 10        | 10        |

| Instructions |         |           |           |

| Cycles       | 20      | 65        | 215       |

| IPC          | 0.50000 | 0.15384   | 0.046512  |

Table 17: FPU configuration statistics.

#### 7.4 Conclusion

These examples clearly demonstrate that implementing an execute forwarding unit, early control change detection, or decreasing the number of cycles an FPU needs to execute increases performance. However, the fact that these design decisions improve performance is not the point. Instead it is to show that these design decisions can be implemented in NEUROSim allowing users to determine if the benefits of implementing a datapath enhancement are worth the increase in other potential variables, such as area and power, for a given algorithm.

### 8 SOFTWARE DESIGN DECISIONS

Neurosim also provides a testbed for quickly analyzing different algorithm implementations and software design techniques. The following sections analyzes three design decisions which are particularly relevant in developing algorithms for embedded applications with limited resources.

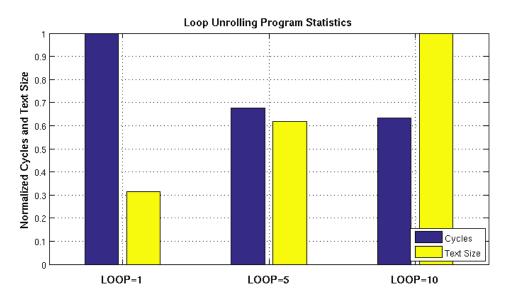

### 8.1 Loop Unrolling

Loop unrolling is a technique used to optimize the execution time of a loop by attempting to decrease the number of instructions spent on loop overhead. Code 11 presents a simple program which adds all of the elements in an array together. The code also provides a macro "LOOP" which allows the number of times the loop is unrolled to be changed. The statistics from running the program given different settings of "LOOP" are presented in Table 18 and in Figure 6.

|              | LOOP=1  | LOOP=5  | LOOP=10 |

|--------------|---------|---------|---------|

| nop          | 18,014  | 13,214  | 12,614  |

| add          | 2,000   | 2,000   | 2,000   |

| shl          | 1,000   | 1,000   | 1,000   |

| slt          | 1,001   | 201     | 101     |

| addi         | 1,002   | 1,002   | 1,002   |

| loi          | 4       | 4       | 4       |

| hii          | 1       | 1       | 1       |

| lw           | 5,002   | 2,602   | 2,302   |

| SW           | 2,004   | 1,204   | 1,104   |

| beq          | 0       | 0       | 0       |

| bne          | 1,001   | 201     | 101     |

| j            | 1,002   | 202     | 102     |

| NonNop       | 14,018  | 8,418   | 7,718   |

| Instructions |         |         |         |

| Cycles       | 32,032  | 21,632  | 20,332  |

| IPC          | 0.43763 | 0.38915 | 0.37960 |

| TextSize     | 29      | 57      | 92      |

Table 18: Loop unrolling statistics.

Clearly unrolling the loop decreases the number of cycles needed to execute the program. The statistics reported by Neurosim clearly illustrate where this performance increase is coming from. Fewer "j" and "bne" instructions are executed because the loop is iterated fewer times. However, the unrolling produces diminishing returns and comes at the cost of substantially increasing the number of instructions stored in instruction memory. This is expressed in the "TextSize" row of the statistics. This statistic represents the number of words stored in the text, or instruction, portion of memory. Because each instruction is one

Figure 6: Loop unrolling statistics graph.

word, this statistic provides a count of the total number of instructions. This illustrates an example where Neurosim provides the user the ability to strike a balance between the loop unrolling performance improvements and the increased memory needed for the text segment.

### 8.2 Recursive Function Calls

The factorial function is a canonical example of a function which can be more intuitive when implemented recursively as seen in Code 12. This implementation will be compared with a loop version of the algorithm as seen in Code 13. The statistics from running the program given the factorial implementations are presented in Table 19.

Given the NEUROSim environment the loop implementation runs in approximately 40% fewer cycles compared to the recursive implementation. This is primarily due to the overhead required to call a function illustrated by the considerable decrease in the number of "jr" and "jrl" instructions. The simulator statistics also provide information on the stack size and shows a potential danger of recursive functions. The used stack space for the recursive implementation is significantly greater than that of the loop implementation as with each new function call more memory is allocated on the stack. As such there is a potential

danger of encountering a stack overflow especially in embedded applications where stack space is limited. It should be noted that this problem can be easily reconciled with tail call optimization and in general is not a reason to avoid recursive functions.

|              | Recursive | Loop    |

|--------------|-----------|---------|

| nop          | 453       | 265     |

| add          | 20        | 1       |

| mul          | 19        | 19      |

| slt          | 21        | 21      |

| addi         | 44        | 25      |

| loi          | 65        | 6       |

| hii          | 39        | 1       |

| lw           | 83        | 104     |

| SW           | 68        | 49      |

| bne          | 21        | 21      |

| j            | 22        | 22      |

| jr           | 21        | 2       |

| jrl          | 21        | 2       |

| NonNop       | 445       | 274     |

| Instructions |           |         |

| Cycles       | 898       | 539     |

| IPC          | 0.49555   | 0.50835 |

| TextSize     | 43        | 40      |

| StackSize    | 44        | 8       |

Table 19: Factorial algorithm statistics.

### 8.3 Self Modifying Code

Self modifying code is one of the lowest level manifestations of the concept that code is simply data and as such can be manipulated by a program like other data. This is a very common concept in higher level languages that implement powerful macro systems. At the assembly language level, self modifying code involves writing a value to an address in instruction memory. Now when the processor reads this address the new instruction will be executed. This is potentially a very dangerous tool because the instruction could potentially be invalid. However, this technique can often be used to pack considerable functionality into a few number of instructions. RISC datapaths are often implemented as Harvard architectures, where the instruction and data memory are separated. This allows the datapath to access both blocks of memory in a single clock cycle. However, this makes writing self modifying code more difficult because the instructions and data are not in the same address space. The converse is a Von Neumann architecture which uses a single memory block and a unified address space. Neurosim allows for either architecture allowing algorithms which use self modifying code to be easily implemented. Code 14 shows an example of a self modifying code algorithm and Table 20 shows the corresponding statistics proving that Neurosim actually executes the modified instructions.

Table 20: Self modifying code statistics.

| nop | add | sub | mul | div | addi | loi | lw | $\mathbf{SW}$ | bne | j |

|-----|-----|-----|-----|-----|------|-----|----|---------------|-----|---|

| 30  | 1   | 1   | 1   | 1   | 4    | 5   | 5  | 4             | 4   | 1 |

## 9 BRANCH PREDICTION

It is estimated that in an average program, one in three instructions are branch instructions. Therefore, being able to correctly predict which branches will be taken is of extreme importance. If the datapath is unable to successfully predict the correct outcome of the branch valuable cycles will be wasted fetching and decoding instructions that will not be used.

Code 15 presents an example test case for evaluating the performance of various branch predictors. This program takes an array of 1,000 values which have a range from 0 to 100 and counts how many values are less than 10, less than 15, less than 20, and so on up to less than 100. The intuition behind how this tests branch predictors is that the tests against smaller values will generally not be taken whereas tests against greater values are more likely to be taken. A good branch predictor should be able to pick up on this pattern. The last line of the main test loop repeatedly divides the current value by two until the value reaches zero; this is to test the branch predictor's ability to find patterns in loops.

### 9.1 Static Branch Predictors

The predictions of static branch predictors can be deterministically resolved before run time and will always select the same prediction for a given branch instruction. Four examples of static predictors are always taken, always not taken, forwards taken, and backwards taken. What each of these predictors do is fairly evident from their names. Always taken predicts the branch is always taken. Always not taken always predicts the branch is not taken. This is essentially the same as having no branch predictor. Forward taken predicts taken if the branch offset is greater than the address of the current branch instruction and not taken otherwise. Backwards taken predicts taken if the branch offset is less than the address of the current branch instruction and not taken otherwise. Forward and backward taken are particularly well suited for loops in which the majority of the time the program will simply branch back to the beginning of the loop. Which one is more effective depends on whether a branch is used to go back to the start of the loop or a branch is used to break out of the loop. The results of using each static branch predictor while running the test code is presented in Table 21. This table shows that Neurosim is capable of presenting a complete breakdown of what branches were taken and the predictions of the predictor.

|                     | Always  | Always    | Forward | Backward |

|---------------------|---------|-----------|---------|----------|

|                     | Taken   | Not Taken | Taken   | Taken    |

| nop                 | 108,182 | 111,870   | 98,684  | 121,368  |

| beq                 | 6,749   | 6,749     | 6,749   | 6,749    |

| bne                 | 10,565  | 10,565    | 10,565  | 10,565   |

| NonNop Instructions | 85,302  | 85,302    | 85,302  | 85,302   |

| Cycles              | 193,484 | 197,172   | 183,986 | 206,670  |

| IPC                 | 0.44087 | 0.43263   | 0.46363 | 0.41275  |

| Correct Taken       | 9,579   | 0         | 8,579   | 1,000    |

| Predicted Taken     | 17,314  | 0         | 10,565  | 6,749    |

| Actual Taken        | 9,579   | 9,579     | 9,579   | 9,579    |

| Correct Not Taken   | 0       | 7,735     | 5,749   | 1,986    |

| Predicted Not Taken | 0       | 17,314    | 6,749   | 10,565   |

| Actual Not Taken    | 7,735   | 7,735     | 7,735   | 7,735    |

| Accuracy            | 0.55325 | 0.44675   | 0.82754 | 0.17246  |

Table 21: Static branch predictor statistics.

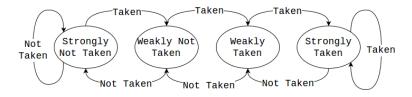

#### 9.2 Dynamic Branch Predictors

The predictions of dynamic branch predictors are unknown until runtime and have the potential to predict differently for the same branch instruction at different times in the execution of the program. A simple dynamic branch predictor randomly chooses taken or not taken. A more complex branch predictor is a local 2-bit saturating counter, Figure 7. In this type of branch predictor, the datapath keeps a history, represented by 2-bits, for each unique branch in the program. The prediction is made based on the current state of the history and the state is updated after the actual branch address is known.

Figure 7: 2-bit saturating counter state diagram.

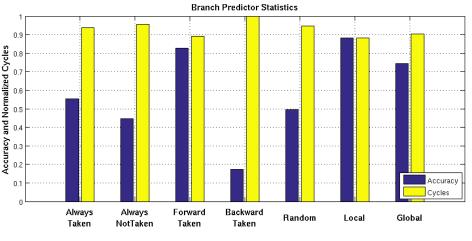

Another dynamic predictor is the global predictor which uses one 2-bit saturating counter history for all branches in the program. This predictor has the benefit of using less hardware because only one table is needed, but the branch history will be corrupted by different branches. The results of using each dynamic branch predictor while running the test code is presented in Table 22. Figure 8 shows the accuracy and normalized cycle counts of both the static and dynamic branch predictors.

|                     | Random  | Local   | Global  |

|---------------------|---------|---------|---------|

|                     |         | History | History |

| nop                 | 110,170 | 96,814  | 101,572 |

| beq                 | 6,749   | 6,749   | 6,749   |

| bne                 | 10,565  | 10,565  | 10,565  |

| NonNop Instructions | 85,302  | 85,302  | 85,302  |

| Cycles              | 195,472 | 182,116 | 186,874 |

| IPC                 | 0.43639 | 0.46839 | 0.45647 |

| Correct Taken       | 4,781   | 8,436   | 6,813   |

| Predicted Taken     | 8,712   | 9,344   | 8,477   |

| Actual Taken        | 9,579   | 9,579   | 9,579   |

| Correct Not Taken   | 3,804   | 6,827   | 6,071   |

| Predicted Not Taken | 8,602   | 7,970   | 8,837   |

| Actual Not Taken    | 7,735   | 7,735   | 7,735   |

| Accuracy            | 0.49584 | 0.88154 | 0.74414 |

Table 22: Dynamic branch predictor statistics.

Figure 8: Branch predictor statistics graph.

The statistics from the the branch predictor test program follows intuition. As branch predictor accuracy increases, the total number of cycles needed to run the program decreases. This is because the pipeline wastes fewer cycles fetching and then flushing the wrong instructions. Choosing a branch predictor presents a design decision with distinct trade-offs. A local branch predictor certainly has the best performance with an accuracy of 88%. However, this comes with the cost of expensive hardware. Whereas a simple static forward taken predictor performed almost as well with an accuracy of 82%. Obviously, these performance numbers are heavily dependent on the algorithm. NEUROSim provides a framework to implement an algorithm and compare the performance given different branch predictors. This prevents overengineering at the microarchitecture level when developing an application, for example implementing a complex local predictor when a simple static predictor would have worked comparably well.

# 10 CACHE ARCHITECTURE

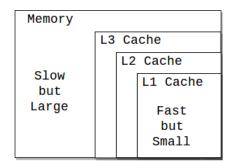

Memory operations can easily take several orders of magnitude longer than normal datapath operations, necessitating the ability to cache results from memory. The general theory behind memory architecture is that ideally memory would be large and fast. However, memory is slow and large, but caches are fast and small. By using the two in tandem and having effective cache maintenance a memory module that appears to be large and fast can be achieved as seen in Figure 9.

Figure 9: Basic cache structure.

Neurosim is currently equipped with a level 1 (L1) cache and allows for the custom setting of cache hit latency and cache miss latency. Neurosim allows for the custom configuration of the L1 cache size, associativity, and cache line size. An example configuration is illustrated in Table 23. The cache is 64 words in size with an associativity of two and line size of four. An incoming memory address is broken into an index used to select a set, a tag used to verify it is the correct line of data, and an offset used to select the correct data block from the line. All cache lines have a valid bit which confirms that the cache line is up to date.

|         | Way 0                               | Way 1                               |

|---------|-------------------------------------|-------------------------------------|

| set 0   | v tag [block0 block1 block2 block3] | v tag [block0 block1 block2 block3] |

| set 1   | v tag [block0 block1 block2 block3] | v tag [block0 block1 block2 block3] |

| set $2$ | v tag [block0 block1 block2 block3] | v tag [block0 block1 block2 block3] |

| set $3$ | v tag [block0 block1 block2 block3] | v tag [block0 block1 block2 block3] |

| set 4   | v tag [block0 block1 block2 block3] | v tag [block0 block1 block2 block3] |

| set $5$ | v tag [block0 block1 block2 block3] | v tag [block0 block1 block2 block3] |

| set $6$ | v tag [block0 block1 block2 block3] | v tag [block0 block1 block2 block3] |

| set $7$ | v tag [block0 block1 block2 block3] | v tag [block0 block1 block2 block3] |

Table 23: Cache example configuration: Size=64, Associativity=2, LineSize=4.

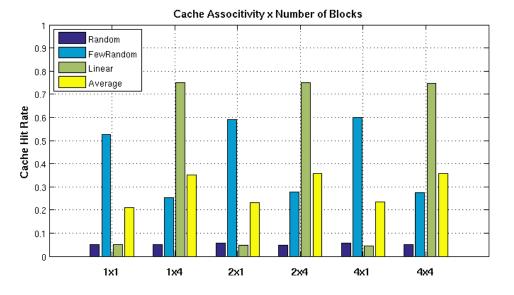

Six different 64 word cache configurations are analyzed under three different access conditions: random indices, a randomized few indices, and linear indices. All tests involve indexing into a 2,048 element array. The random test simply uses 1,024 random values between 0 and 2,047 as indices. Because the size of the array is so much larger than the cache, it is nearly impossible for the cache to perform well. The randomized few indices uses 122 indices randomly selected 1,024 times. Caches with a higher associativity will perform better on this test because the ability to map multiple pieces of data to different cache lines prevents the eviction of data which still needs to be used. The linear test selects 512 random indices and then reads a random number, from 1 to 100, of elements from the array. Caches with a larger line size should perform well under these test conditions as the subsequent pieces of data in the array are prefetched.

Table 24 and Figure 10 summarize the results of running these tests. What should be evident from these tests is that there is no absolute correct cache configuration; it largely depends on the type of memory accesses. This illustrates the value of NEUROSim; it provides a quick testing environment to compare different configurations for a specific application.

|             |          | Associtivity x Line Size |          |          |          |          |  |  |

|-------------|----------|--------------------------|----------|----------|----------|----------|--|--|

| Access Type | 1x1      | 1x4                      | 2x1      | 2x4      | 4x1      | 4x4      |  |  |

| Random      | 0.0501   | 0.0501                   | 0.058116 | 0.046092 | 0.056112 | 0.0501   |  |  |

| Random Few  | 0.527132 | 0.251938                 | 0.589147 | 0.27907  | 0.600775 | 0.275194 |  |  |

| Linear      | 0.051736 | 0.749587                 | 0.048595 | 0.748512 | 0.044463 | 0.74719  |  |  |

| Average     | 0.20966  | 0.35054                  | 0.23195  | 0.35789  | 0.23378  | 0.35749  |  |  |

Table 24: Cache hit rates.

Figure 10: Cache hit rates graph.

# 11 Setup and Configuration of Examples

In the following sections, instructions will be added to the core ISA and the impact of those instructions evaluated. This is where NEUROSim begins to truly differentiate itself from other computer architecture simulators because it was designed with the purpose of allowing for the addition of new instructions and provides the surrounding tooling to easily accomplish this.

A question presents itself: how to compare the benefits of adding an instruction. The following sections all use the same basic testing environment. First, the desired functionality of the instruction is factored out from the program into a separate function. Then the algorithm is run with the function called normally and with the function inlined in the program. The inlining of the function removes the overhead associated with the function call giving a more accurate representation of the potential benefits of adding an instruction. Code 19 gives a simple example of factoring out the "add" functionality and then calling the normal and inlined version of the function. After these two tests are run, the inlined portion of the code is then removed and replaced with the new instruction. The program is then executed with different cycle counts for the instruction to evaluate how efficient the hardware would need to be to get the desired performance increase.

The configuration of the simulator, barring the experimentation with the new instruction's cycle counts, is the same for all trials: local branch predictor with control change detection handled in the fetch stage, a zero cycle cache miss penalty, and an FPU execute stage latency of 10 cycles. This configuration was chosen to try and represent a basic system while preventing the statistics from being skewed in favor of the implementation with the custom instruction. The software implementation of the functionality intrinsically executes more instructions providing the possibility for a greater number of branch mispredictions and more cache miss penalties to be incurred. By using the best branch predictor and no cache miss penalties this inequality is mitigated. This configuration can be thought of providing a nearly ideal run of the program, allowing for the sole analysis of the new instruction's performance.

## 12 MODULO INSTRUCTION

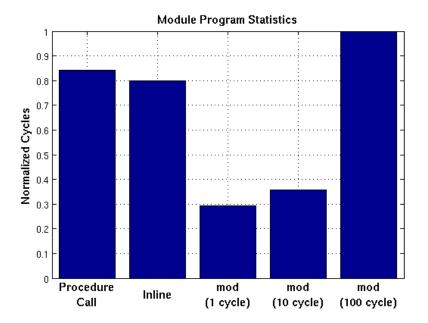

Several basic design decisions have been examined in the context of NEUROSim. However, NEUROSim's true strength is seen in the context of adding new instructions to its core ISA. The simplest type of instructions to add are ones that follow the R type format. An example of such an instruction would be adding hardware support for the modulo operator. "Modular reduction, also known as the modulo or mod operation, is a value within Y, such that it is the remainder after Euclidean division of X by Y. This operation is heavily used in encryption algorithms, since it can 'hide' values within large prime numbers, often called keys [13]." Due to the computational needs of encryption algorithms, the mod operation is often optimized to improve performance. Table 25 presents the proposed instruction. Code 20 provides an example program to test the performance benefits of using a hardware optimized mod instruction. Essentially, this program computes the mod between every element in array "X". It should be noted that the software implementation of mod is very inefficient and better algorithms exist. However, for the sake of showing an example design process in NEUROSim it is sufficient.

Table 25: MOD instruction.

| Opcode | Operands |    | nds | Result             |

|--------|----------|----|-----|--------------------|

| mod    | rd       | rs | rt  | $RD := RS \mod RT$ |

Table 26 and Figure 11 show the statistics of running the program with five different configurations. The first trial is with the modulo functionality called as a function, then the functionality is inlined, and finally three different runs with the new "mod" instruction are run with a 1 cycle, 10 cycle, and 100 cycle execute stage latencies. Clearly, adding a "mod" instruction can significantly improve performance. Even if the instruction takes ten cycles to compute, the program still undergoes a 55% decrease in the number of cycles taken to execute in comparison to the inlined version.

|              | Function  | Inlined   | mod             | mod         | mod             |

|--------------|-----------|-----------|-----------------|-------------|-----------------|

|              | Call      | Function  | 1 cycle EX      | 10 cycle EX | 100 cycle EX    |

| nop          | 2,308,686 | 2,268,682 | 962,818         | 1,322,818   | 4,922,818       |

| add          | 80,000    | 80,000    | 80,000          | 80,000      | 80,000          |

| sub          | 134,766   | 134,766   | 0               | 0           | 0               |

| shl          | 80,000    | 80,000    | 80,000          | 80,000      | 80,000          |

| slt          | 215,167   | 215,167   | 40,401          | 40,401      | 40,401          |

| addi         | 120,202   | 40,202    | 40,202          | 40,202      | 40,202          |

| lw           | 939,671   | 939,665   | 240,601         | 240,601     | 240,601         |

| SW           | 335,174   | 335,168   | 80,402          | 80,402      | 80,402          |

| bne          | 215,167   | 215,167   | 40,401          | 40,401      | 40,401          |

| j            | 214,968   | 174,968   | 40,202          | 40,202      | 40,202          |

| jr           | 40,000    | 0         | 0               | 0           | 0               |

| jrl          | 40,000    | 0         | 0               | 0           | 0               |

| mod          | 0         | 0         | 40,000          | 40,000      | 40,000          |

| NonNop       | 2,415,124 | 2,215,110 | 682,216         | 682,216     | 682,216         |

| Instructions |           |           |                 |             |                 |

| Cycles       | 4,723,810 | 4,483,792 | $1,\!645,\!034$ | 2,005,034   | $5,\!605,\!034$ |

| IPC          | 0.51127   | 0.49403   | 0.41471         | 0.34025     | 0.12172         |

Table 26: Modulo test program statistics.

Figure 11: Modulo test program statistics graph.

The statistics from Neurosim explicitly indicate the source of the performance improvements. First, it can be seen that by inlining the function call, the program goes from executing 40,000 "jr" and "jrl" instructions down to zero. There is also some savings in the number of "addi" and memory operations which are used for maintaining the stack. However, the true performance benefits come when the new "mod" instruction is used, which cuts the number of executed instructions in almost every category. As one would expect, the only instruction count that goes up is for the "mod" instruction itself. The statistics also demonstrate the considerable decrease in IPC as the "mod" instruction execute stage latency is increased. Overall, these statistics provide exactly the information needed for a systems designer to determine which portions of an algorithm should be handled in hardware and which should be handled in software.

# 13 DIGITAL SIGNAL PROCESSING EXAMPLE

Digital signal processing (DSP) algorithms involve the manipulation of signals in the digital domain and are commonly done using dedicated embedded systems. With the great popularity of cellphones, DSP specific hardware has become ubiquitous. The following section looks at implementing a dedicated multiply accumulate instruction intended to improve the performance of DSP filter implementations.

### 13.1 Lowpass Filter