# Multi-Carrier Spread-Spectrum Transceiver for WiNoC

Joel Ortiz Sosa, Olivier Sentieys, Christian Roland, Cédric Killian

## ► To cite this version:

Joel Ortiz Sosa, Olivier Sentieys, Christian Roland, Cédric Killian. Multi-Carrier Spread-Spectrum Transceiver for WiNoC. NOCS 2019 - 13th IEEE/ACM International Symposium on Networks-on-Chip, Oct 2019, New York, United States. pp.1-2, 10.1145/3313231.3352373. hal-02394890

# HAL Id: hal-02394890 https://hal.inria.fr/hal-02394890

Submitted on 5 Dec 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Multi-Carrier Spread-Spectrum Transceiver for WiNoC

Joel Ortiz, Olivier Sentieys {joel.ortiz-sosa,olivier.sentieys}@ inria.fr Univ Rennes 1, Inria, CNRS/IRISA Lannion, France Christian Roland christian.roland@univ-ubs.fr UBS - Lab-STICC Lorient,France Cedric Killian cedric.killian@irisa.fr Univ. Rennes 1, Inria, CNRS/IRISA Lannion,France

### ABSTRACT

In this paper, we propose a low-power, high-speed, multi-carrier reconfigurable transceiver based on Frequency Division Multiplexing to ensure data transfer in future Wireless NoCs. The proposed transceiver supports a medium access control method to sustain unicast, broadcast and multicast communication patterns, providing dynamic data exchange among wireless nodes. The proposed transceiver designed using a 28-nm FDSOI technology consumes only 2.37 mW and 4.82 mW in unicast/broadcast and multicast modes, respectively, with an area footprint of 0.0138 mm<sup>2</sup>.

### **CCS CONCEPTS**

• Networks  $\rightarrow$  Network on chip; • Hardware  $\rightarrow$  Radio frequency and wireless interconnect.

#### **KEYWORDS**

Wireless Network-on-Chip, WiNoC Channel, Communication Reliability, Digital Transceiver Architecture

#### **1** INTRODUCTION

Massive parallelism in manycore architectures for emerging highperformance computing applications requires the use of an efficient interconnection system. However, current electrical interconnections are not efficient enough to support an increasing number of cores while ensuring high performance and energy efficiency. For this reason, on-chip wireless interconnection technologies can provide a promising solution for a massive number of cores requiring a large Network-on-Chip (NoC), especially when considering broadcast/multicast system requirements. Nevertheless, the bandwidth needed to reach very high-speed data rate for each wireless link, highly increases the power consumption in all the Wireless NoC (WiNoC) transceivers. In order to keep a reasonable trade-off between power consumption and data rate, WiNoC designers have decreased the minimum required bandwidth to support a given data rate (e.g. 16 Gbps). However, this reduction produces significant communication errors that have to be compensated by increasing the transmission signal power and the receiver sensitivity.

NOCS '19, October 17-18, 2019, New York, NY, USA

© 2019 Association for Computing Machinery. ACM ISBN 978-1-4503-6700-4/19/10...\$15.00

ACM ISBN 978-1-4503-6700-4/19/10...\$15.0 https://doi.org/10.1145/3313231.3352373

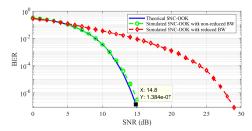

Current Single-carrier Non-Coherent On-Off Keying (SNC-OOK) transceiver architectures are designed to reach a communication link of 20 mm with a data transfer rate of 16 Gbps. The SNC-OOK transmitter output power  $P_t$  required to establish a wireless link into a noisy wireless channel is -14 dBm. However, as a large receiver bandwidth (BW) can reach prohibited levels of power consumption [3], designers have reduced the 3 dB receiver BW required to achieve 16 Gbps, from 16 GHz to 9.2 GHz [6]. This reduction intensifies the bit error rate (BER) at the receiver side and necessitate to increase  $P_t = -0.5$  dBm to reach the same  $BER = 10^{-15}$ . This problem was modeled in MATLAB to verify the effects of the receiver BW reduction, using a second-order band-pass Butterworth filter configured with the parameters described above. As shown in Fig. 1, the system SNR is degraded by 14 dB at  $10^{-7}$ , which is traduced in a high  $P_t$  to reach the same BER. In order to overcome this performance degradation, this work proposes a Multi-carrier NC-OOK (MNC-OOK) transceiver architecture, which allows to avoid BW reduction.

Figure 1: Single-carrier non-Coherent OOK system model

### 2 PROPOSED MULTI-CARRIER WIRELESS INTERFACE ARCHITECTURE

The MNC-OOK transceiver is based on Frequency Division Multiplexing (FDM) and Direct Sequence Spread Spectrum (DSSS) to overcome bandwidth reduction problems. The FDM technique is used as a mean to divide the total bandwidth into four different carrier frequencies with shorter bandwidth, *e.g.*, 10 GHz/4 = 2.5 GHz. On the other hand, the DSSS technique enables parallel channel access, reusing existing frequencies.

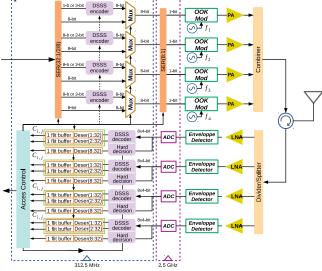

Digital Transmitter Architecture. A transmitter assigned to a carrier frequency  $f_i$  is composed of three blocks: a serializer SER(32:1/2/8), a DSSS encoder, and an SER(8:1), as illustrated in Fig. 2. The DSSS encoder is designed using 8-bit and 4-bit registers initialized by the considered Hadamard codes ( $C_i$ ). The output of this sub-block is a specific code ( $C_i$ ) or its complement ( $\overline{C_i}$ ). The SER (32:1/2/8) 2-bit output is associated with a 4-bit code, and the 1-bit output is related with an 8-bit code. In case of a simple point-to-point communication, no code is necessary and the system therefore

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

configures the SER 8-bit output. Hadamard codes are only used for *multicast* (all/many-to-one, many-to-many, and multiple-unicast) communications. Otherwise, in *unicast/broadcast* mode, no code is required.

**Figure 2: Proposed MNC-OOK transceiver architecture.** *Digital Receiver Architecture.* A receiver sub-block tuned for a certain carrier frequency  $f_i$ , receives an analog signal and converts it into eight 4-bit words using its respective ADC, as depicted in Fig. 2. Afterwards, this digitized signal is forwarded to the DSSS decoder and hard decision sub-blocks. The DSSS decoder follows the architecture from [5], but without considering the channel compensation techniques. Each DSSS decoder and hard decision sub-block outputs are forwarded into their respective deserializer DESER(1:32), DESER(2:32), DESER(8:32) and buffer blocks. The access control sub-block deactivates unused sub-blocks during the configuration phase of the communication patterns, to save energy.

#### **3 RESULTS**

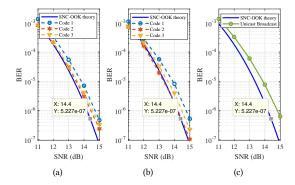

In order to evaluate the BER, the end-to-end system is modeled in MATLAB using the channel model provided by [4]. This channel model consists of 4 antennas tuned at 200 GHz with a frequency range of 62 GHz, which is used by the FDM scheme. The nonoverlapping frequency bands are distributed using different carrier frequencies:  $f_1 = 195$  GHz,  $f_2 = 200$  GHz,  $f_3 = 205$  GHz, and  $f_4 = 210$  GHz. Simulation results are reported in Fig. 3 for unicast/broadcast and multicast communications. The modeled communication system comprises four wireless nodes, which requires three codes  $(i = 1 \dots 3)$  by each code size group *j*. The first group j = 1 provides a Processing Gain PG = 6 dB using a 4-bit code size, and the second group j = 2 brings a PG = 9 dB for 8-bit code size. The PG has two applications [2]. The first one is to improve the signal resilience providing better BER with the same  $P_t$ , and the second one aims at reducing  $P_t$  keeping the same BER. However, in order to make a fair comparison between both code sizes in terms of BER, the PG effects was suppressed during simulation. The different communication patters based on the MNC-OOK scheme are compared with the theoretical BER for SNC-OOK. As shown in Figure 3, the average BER for each communication pattern is slightly

different from the theoretical BER for SNC-OOK. Consequently, the  $P_t$  does not require to be highly incremented, as previously explained. Moreover, in case of multicast mode, an 8-bit code size will provide better signal resilience considering the PG effects, as well as it can allocate more parallel channels [5].

Figure 3: BER performance for multicast with (a) PG = 6 dB, (b) PG = 9 dB, and (c) unicast/broadcast.

The digital transceiver architecture is modeled in C/C++, synthesized from C to RTL by Catapult HLS and to the gate level by Synopsys Design Compiler. A 28-nm FDSOI technology library is used during hardware synthesis as a target with a supply voltage of 1 Volt. Data interfaces with the router/switch have 32-bit width. Synthesis results of the digital transceiver are detailed in Table 1, which reports both static and dynamic power consumption of each component.

Table 1: Area and power consumption of digital transceiver architecture designed using 28-nm FDSOI.

| WI Block                             | Area (µm²) | Power (mW) | clock (GHz) |

|--------------------------------------|------------|------------|-------------|

| DSSS encoder                         | 121        | 0.03       |             |

| DSSS decoder and Hard Decision       | 150        | 0.04       | 0.3125      |

| Serializer 32:1:2:8-bit (312.5 Mbps) | 391        | 0.16       |             |

| Serializer 8:1-bit (2.5 Gbps)        | 94         | 0.27       | 2.5         |

| Deserializer 8:32-bit (312.5 Mbps)   | 190        | 0.082      | 0.3125      |

| Deserializer 2:32-bit (312.5 Mbps)   | 200        | 0.089      |             |

| Deserializer 1:32-bit (312.5 Mbps)   | 221        | 0.093      |             |

| Access Control Block                 | 500        | 0.7        |             |

The area overhead of the MNC-OOK digital transceiver for a four-cluster architecture is around 0.0138 mm<sup>2</sup>, which is 17 times smaller than the digital transceiver proposed in [1] for multicast communications. Unfortunately, the authors do not provide the power consumption, however, the large area overhead suggests a high power consumption compared to our proposition, which consumes only 2.37 mW in unicast/broadcast mode and 4.82 mW for the full multicast mode.

#### REFERENCES

- K. Duraisamy, Y. Xue, et al. Multicast-aware high-performance wireless networkon-chip architectures. *IEEE Trans. onVLSI Systems*, 25(3):1126–1139, 2017.

- [2] J. Fakatselis and M. Belkerdid. Processing gain for direct sequence spread spectrum communication systems and prism<sup>®</sup>. Appli. Note AN9633, Intersil, four pages, 1996.

- [3] H. Hsieh, P. Wu, C. Jou, F. Hsueh, and G. Huang. 60ghz high-gain low-noise amplifiers with a common-gate inductive feedback in 65nm cmos. In *IEEE Radio Freq. Integ. Circ. Sympo.*, pages 1–4, 2011.

- [4] I. E. Masri et al. Accurate channel models for realistic design space exploration of future wireless nocs. In IEEE/ACM Inter. Symp. on (NOCS), pages 1–8, 2018.

- [5] J. O. Sosa et al. A Diversity Scheme to Enhance the Reliability of Wireless NoC in Multipath Channel Environment. In Int. Symp. on NOCS, pages 1–8, 2018.

- [6] X. Yu et al. A 1.2-pJ/bit 16-Gb/s 60-GHz OOK Transmitter in 65-nm CMOS for Wireless Network-On-Chip. IEEE Trans. on MTT, 62(10):2357–2369, 2014.