# PRACTICAL TECHNIQUES FOR IMPROVING PERFORMANCE AND EVALUATING SECURITY ON CIRCUIT DESIGNS

A Dissertation

by

#### WENBIN XU

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Chair of Committee, Jiang Hu Committee Members, Anxiao Jiang

> Peng Li Tie Liu

Head of Department, Miroslav M. Begovic

August 2019

Major Subject: Computer Engineering

Copyright 2019 Wenbin Xu

#### **ABSTRACT**

As the modern semiconductor technology approaches to nanometer era, integrated circuits (ICs) are facing more and more challenges in meeting performance demand and security. With the expansion of markets in mobile and consumer electronics, the increasing demands require much faster delivery of reliable and secure IC products. In order to improve the performance and evaluate the security of emerging circuits, we present three practical techniques on approximate computing, split manufacturing and analog layout automation.

Approximate computing is a promising approach for low-power IC design. Although a few accuracy-configurable adder (ACA) designs have been developed in the past, these designs tend to incur large area overheads as they rely on either redundant computing or complicated carry prediction. We investigate a simple ACA design that contains no redundancy or error detection/correction circuitry and uses very simple carry prediction. The simulation results show that our design dominates the latest previous work on accuracy-delay-power tradeoff while using 39% less area. One variant of this design provides finer-grained and larger tunability than that of the previous works. Moreover, we propose a delay-adaptive self-configuration technique to further improve the accuracy-delay-power tradeoff.

Split manufacturing prevents attacks from an untrusted foundry. The untrusted foundry has front-end-of-line (FEOL) layout and the original circuit netlist and attempts to identify critical components on the layout for Trojan insertion. Although defense methods for this scenario have been developed, the corresponding attack technique is not well explored. Hence, the defense methods are mostly evaluated with the k-security metric without actual attacks. We develop a new attack technique based on structural pattern matching. Experimental comparison with existing attack shows that the new attack technique achieves about the same success rate with much faster speed for cases without the k-security defense, and has a much better success rate at the same runtime for cases with the k-security defense. The results offer an alternative and practical interpretation for k-security in split manufacturing.

Analog layout automation is still far behind its digital counterpart. We develop the layout automation framework for analog/mixed-signal ICs. A hierarchical layout synthesis flow which works in bottom-up manner is presented. To ensure the qualified layouts for better circuit performance, we use the constraint-driven placement and routing methodology which employs the expert knowledge via design constraints. The constraint-driven placement uses simulated annealing process to find the optimal solution. The packing represented by sequence pairs and constraint graphs can simultaneously handle different kinds of placement constraints. The constraint-driven routing consists of two stages, integer linear programming (ILP) based global routing and sequential detailed routing. The experiment results demonstrate that our flow can handle complicated hierarchical designs with multiple design constraints. Furthermore, the placement performance can be further improved by using mixed-size block placement which works on large blocks in priority.

# DEDICATION

To my mother, my father, my grandmother, and my grandfather.

#### **ACKNOWLEDGMENTS**

I would like to thank my advisor, Professor Jiang Hu, for his advice on my PhD program. During the past four years, I've learned a lot from Professor Hu, not only the academic knowledge but also the attitude to work and research. Without his guidance and encouragement, it is almost impossible for me to complete the program.

I would like to thank my committee members, Professor Anxiao Jiang, Professor Peng Li and Professor Tie Liu of Texas A&M University, for their helpful suggestions and comments on my research and dissertation.

I would like to thank Professor Sachin S. Sapatnekar of University of Minnesota for his help and advice on approximate computing project and analog layout automation project. I would like to thank Professor Jeyavijayan (JV) Rajendran of Texas A&M University for his help and advice on split manufacturing project. I would like to thank Professor Duncan M. (Hank) Walker of Texas A&M University for his helpful discussion on approximate computing project.

I would like to thank Lang Feng of Texas A&M University for his help on preparing test cases in split manufacturing project. I would like to thank Yaguang Li of Texas A&M University for his collaboration in analog layout automation project. I would like to thank Arvind Sharma, Kishor Kunal, and Meghna Madhusudan of University of Minnesota for preparing the benchmarks and helpful discussion on analog circuits.

Thanks to my mates in Texas A&M University, Hao He, Lin Huang, Hongxin Kong, Rongjian Liang, and Jiafan Wang. Special thanks to my former managers in Synopsys, Liwen Xu, Yan Zhai and Zhibo Ai who introduced me to the semiconductor industry. Special thanks to Daniel Xu for his support and encouragement during the past four years.

At last, many thanks to my parents for their strong support and endless love to me.

#### CONTRIBUTORS AND FUNDING SOURCES

#### **Contributors**

This work was supported by a dissertation committee consisting of Professor Jiang Hu, advisor, and Professor Peng Li, Professor Tie Liu of the Department of Electrical and Computer Engineering, and Professor Anxiao Jiang of the Department of Computer Science and Engineering.

Some test cases for Chapter 3 were prepared by Lang Feng of Texas A&M University. Some codes of constraint-driven routing for Chapter 4 were implemented by Yaguang Li of Texas A&M University. The benchmarks for Chapter 4 were provided by Arvind Sharma, Kishor Kunal, and Meghna Madhusudan of University of Minnesota.

All other work conducted for the dissertation was completed by the student independently.

#### **Funding Sources**

Graduate study was supported by National Science Foundation (NSF) under Grant CCF-1255193, Grant CCF-1525749, Grant CCF-1525925, Grant CNS-1618824, and Grant CNS-1618797, and Semiconductor Research Corporation (SRC) under Grant 2016-TS-2688, and Grant 2016-TS-2689.

### NOMENCLATURE

IC Integrated Circuits

VLSI Very Large Scale Integration

DVS Dynamic Voltage Scaling

CVS Clustered Voltage Scaling

FEOL Front-End-Of-Line

BEOL Back-End-Of-Line

SoC System-on-Chip

EDA Electronic Design Automation

DVFS Dynamic Voltage and Frequency Scaling

DCT Discrete Cosine Transform

CRA Carry Ripple Adder

CLA Carry Look-ahead Adder

VLCSA Variable Latency Carry Select Adder

ETA Error Tolerant Adder

CASA Correlation-Aware Speculative Adder

ACA Accuracy Configurable Adder

GDA Accuracy Gracefully-Degrading Adder

RAP-CLA Reconfigurable Approximate Carry Look-ahead Adder

SARA Simple Accuracy Reconfigurable Adder

PDP Power Delay Product

EDP Energy Delay Product

PSNR Peak Signal-to-Noise Ratio

LSB Least Significant Bit

MSB Most Significant Bit

DAR Delay Adaptive Reconfiguration

RAC ROM and Accumulator Component

SAT Boolean Satisfiability

DRC Design Rule Check

ILP Integer Linear Programming

MILP Mixed Integer Linear Programming

HPWL Half-parameter Wirelength

# TABLE OF CONTENTS

|     |                                        | P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | age                                                    |

|-----|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| ABS | STR                                    | ACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ii                                                     |

| DEI | DICA                                   | ATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | iv                                                     |

| ACl | KNO                                    | WLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | v                                                      |

| CO  | NTR                                    | IBUTORS AND FUNDING SOURCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | vi                                                     |

| NO  | MEN                                    | NCLATURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | vii                                                    |

| TAI | BLE :                                  | OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ix                                                     |

| LIS | T OF                                   | FFIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | xii                                                    |

| LIS | Т ОҒ                                   | F TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | XV                                                     |

| 1.  | INTI                                   | RODUCTION AND MOTIVATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                      |

|     | 1.1<br>1.2<br>1.3                      | Approximate Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2                                                      |

|     |                                        | PLE YET EFFICIENT ACCURACY CONFIGURABLE ADDER                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |

|     | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Introduction.  Prior Works and Rationale of Our Design  Simple Accuracy Reconfigurable Adder  2.3.1 Preliminaries  2.3.2 SARA: Simple Accuracy Reconfigurable Adder Design  2.3.3 Usage of SARA.  SARA Error Analysis  Delay-Adaptive Reconfiguration of SARA  Experimental Results  2.6.1 Experiment Setup and Evaluation  2.6.2 Results of Tradeoff for Different Configurations  2.6.3 Results of Tradeoff for Delay-Adaptive Reconfiguration  2.6.4 Impact of Detection Window in Delay-Adaptive Reconfiguration | 6<br>9<br>10<br>12<br>13<br>19<br>21<br>22<br>26<br>28 |

|     | 2.7                                    | 2.6.5 Results of Iso-delay Power and Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                        |

|    |      | 2.7.2 DCT Computation in Image Processing                         | 35       |

|----|------|-------------------------------------------------------------------|----------|

|    | 2.8  | Conclusion.                                                       |          |

| 3. | LAY  | OUT RECOGNITION ATTACKS ON SPLIT MANUFACTURING                    | 41       |

|    |      |                                                                   |          |

|    | 3.1  | Introduction                                                      |          |

|    | 3.2  | Preliminary                                                       |          |

|    |      | 3.2.1 Attack Scenario                                             |          |

|    |      | 3.2.2 Related Work                                                |          |

|    |      | 3.2.3 SAT-based Bijective Mapping                                 |          |

|    | 3.3  |                                                                   |          |

|    |      |                                                                   | 48       |

|    |      | 3.3.2 Matching a Subcircuit with FEOL Layout                      |          |

|    |      | 3.3.3 Pruning by Hints from Design Conventions                    |          |

|    |      | 3.3.4 Propagating Candidates along Subcircuit                     |          |

|    | 2.4  | 3.3.5 Matching of the Entire Circuit                              |          |

|    | 3.4  | Experiment Results                                                |          |

|    |      | 3.4.1 Experiment Setup                                            |          |

|    |      | 3.4.2 Experiments on Cases without k-security Defense             |          |

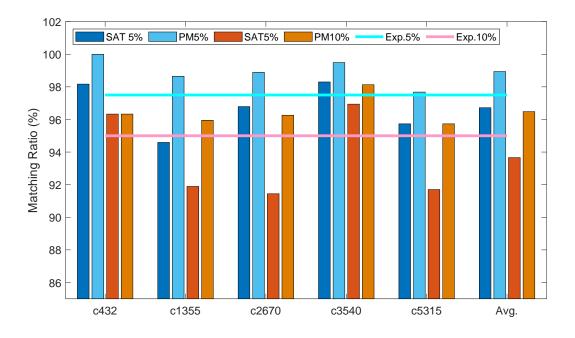

|    | 2.5  | 3.4.3 Experiments on Cases with k-security Defense                |          |

|    | 3.5  | Discussions                                                       |          |

|    |      | 3.5.1 Comparison with Other Attack Methods                        |          |

|    | 2.6  | 3.5.2 Extension to Attacks with Incomplete Netlist                |          |

|    | 3.6  | Conclusion                                                        | 61       |

| 4. | HIEI | RARCHICAL CONSTRAINT-DRIVEN ANALOG LAYOUT AUTOMATION              | 63       |

|    | 4.1  | Introduction                                                      | 62       |

|    | 4.1  | Related Work                                                      |          |

|    | 4.2  | 4.2.1 Analog Placement                                            |          |

|    |      | 4.2.1 Analog Flacement 4.2.2 Analog Routing                       |          |

|    | 4.3  | Constraint-driven Placement.                                      |          |

|    | 4.3  | 4.3.1 Topological Representation                                  |          |

|    |      |                                                                   |          |

|    |      | 4.3.1.1 Sequence Pair                                             |          |

|    |      | 4.3.1.2 Constraint Graph  4.3.2 Handling of Placement Constraints |          |

|    |      | e                                                                 | 71       |

|    |      | y y                                                               | 73       |

|    |      | c                                                                 | 74       |

|    |      |                                                                   |          |

|    |      | · · · · · · · · · · · · · · · · · · ·                             | 75<br>76 |

|    |      | •                                                                 | 76       |

|    |      | $\mathcal{E}$                                                     | 76       |

|    |      |                                                                   | 77       |

|    |      |                                                                   |          |

|    |      |                                                                   |          |

|    |      |                                                                   | 79<br>79 |

|    | 4.4   | Consti | aint-driven Routing                              | 80 |

|----|-------|--------|--------------------------------------------------|----|

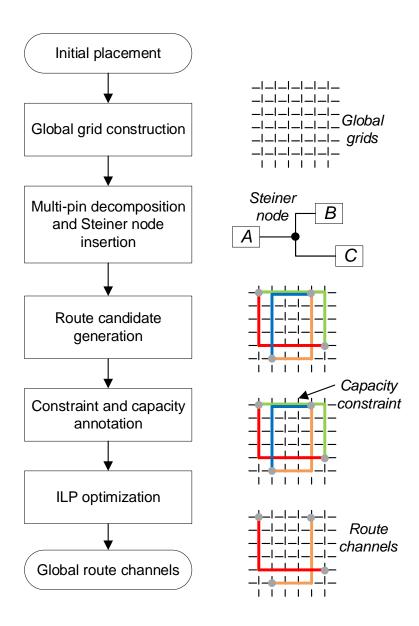

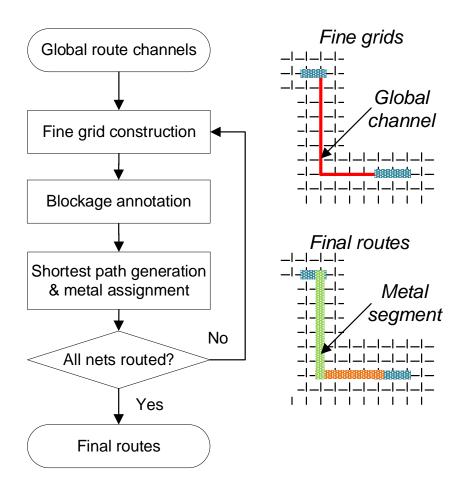

|    |       | 4.4.1  | Global Routing                                   | 81 |

|    |       |        | 4.4.1.1 Basic Flow                               | 81 |

|    |       |        | 4.4.1.2 Global Grids                             | 82 |

|    |       |        | 4.4.1.3 Multi-pin Net Decomposition              | 83 |

|    |       |        | 4.4.1.4 Route Candidate Generation               | 84 |

|    |       |        | 4.4.1.5 Constraint Annotation                    | 84 |

|    |       |        | 4.4.1.6 ILP Optimization                         | 85 |

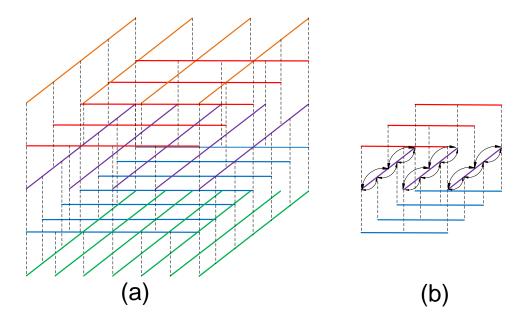

|    |       | 4.4.2  | Detailed Routing.                                | 86 |

|    |       |        | 4.4.2.1 Basic Flow                               |    |

|    |       |        | 4.4.2.2 Handling of Symmetry Net Constraints     | 87 |

|    | 4.5   |        | 1                                                | 89 |

|    | 4.6   | Mixed  | -size Block Placement                            |    |

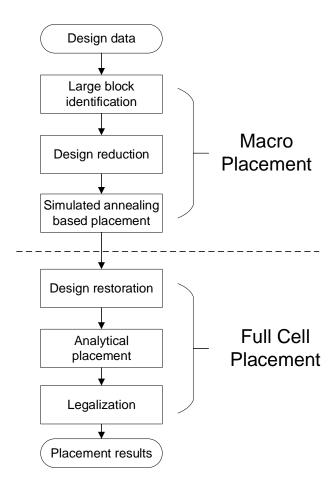

|    |       | 4.6.1  | Overall Flow                                     |    |

|    |       | 4.6.2  | Macro Placement                                  |    |

|    |       | 4.6.3  | Full Cell Placement.                             |    |

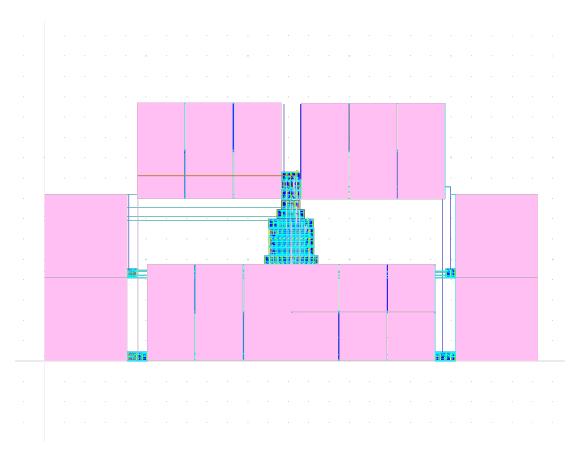

|    | 4.7   |        | ment Results                                     |    |

|    |       | 4.7.1  | Experiment Setup                                 |    |

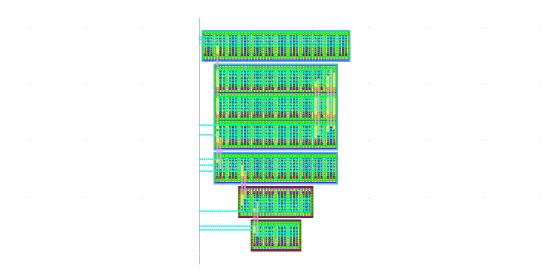

|    |       | 4.7.2  | Experiment Results of Hierarchical Flow          |    |

|    |       | 4.7.3  | Experiment Results of Mixed-size Block Placement |    |

|    | 4.8   | Conclu | ısion1                                           | 01 |

| 5. | SUN   | 1MARY  | AND CONCLUSIONS1                                 | 04 |

| RF | EFERI | ENCES  |                                                  | 05 |

# LIST OF FIGURES

| FIGURI | ∃ 1                                                                                                             | Page |

|--------|-----------------------------------------------------------------------------------------------------------------|------|

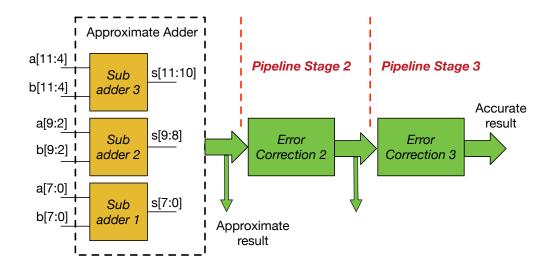

| 2.1    | Error-correction-based configurable adder.                                                                      | . 7  |

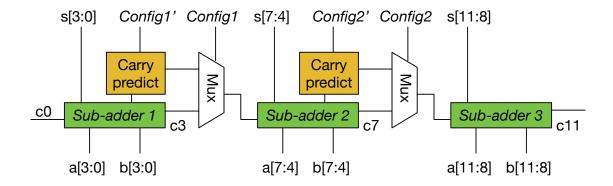

| 2.2    | Carry-prediction-based configurable adder                                                                       | . 7  |

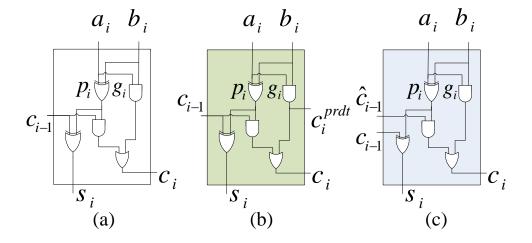

| 2.3    | (a) Conventional full adder; (b) Our carry-out selectable full adder; (c) Our carry-in configurable full adder. | . 9  |

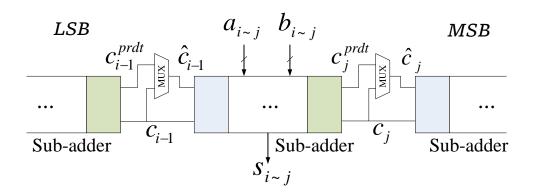

| 2.4    | Design of SARA                                                                                                  | . 11 |

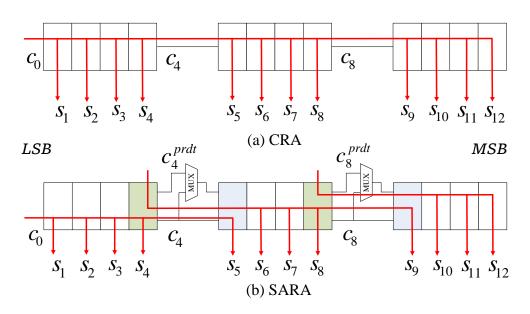

| 2.5    | Implementation of 12-bit adder in (a) CRA and (b) SARA.                                                         | . 12 |

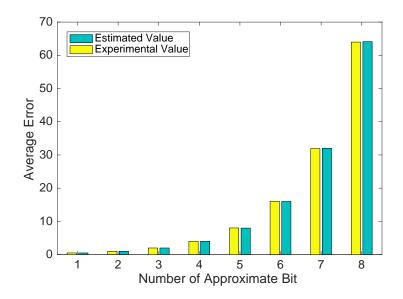

| 2.6    | Average error of 9-bit SARA in different configuration.                                                         | . 18 |

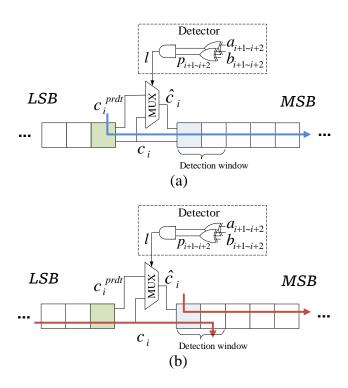

| 2.7    | Design of DAR for SARA operating in a) approximate mode and b) accurate mode.                                   | . 20 |

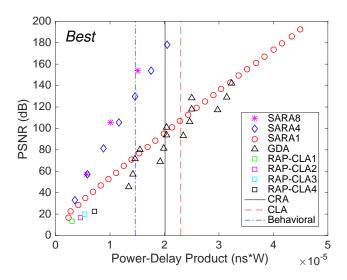

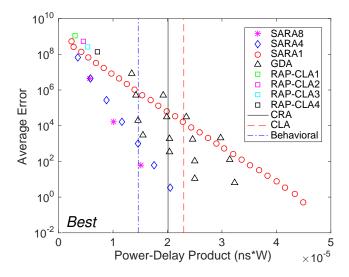

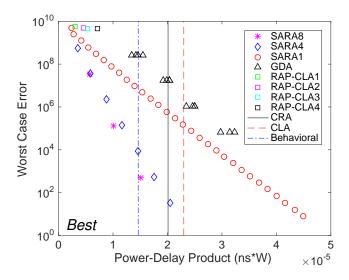

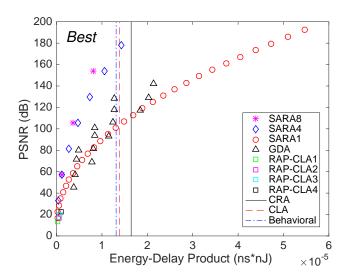

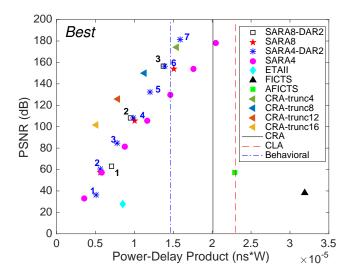

| 2.8    | SARA: PSNR versus power-delay product.                                                                          | . 23 |

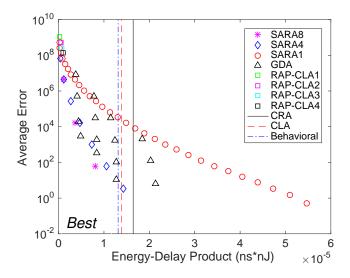

| 2.9    | SARA: Average error versus power-delay product.                                                                 | . 24 |

| 2.10   | SARA: The worst case error versus power-delay product                                                           | . 24 |

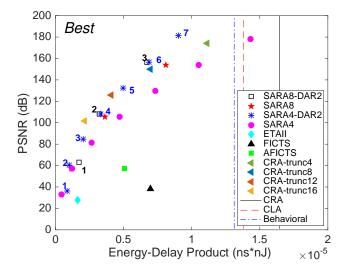

| 2.11   | SARA: PSNR versus energy-delay product.                                                                         | . 25 |

| 2.12   | SARA: Average error versus energy-delay product.                                                                | . 26 |

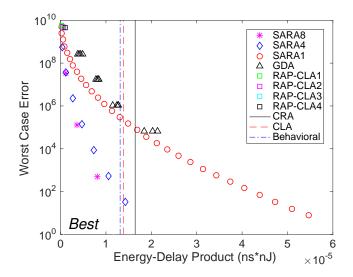

| 2.13   | SARA: The worst case error versus energy-delay product.                                                         | . 26 |

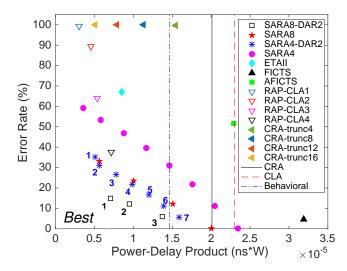

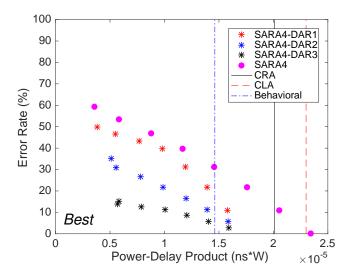

| 2.14   | SARA-DAR: Error rate versus power-delay product.                                                                | . 27 |

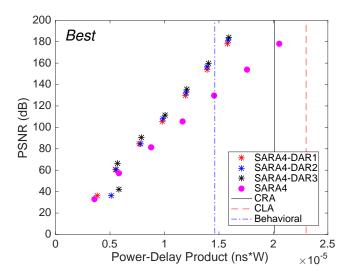

| 2.15   | SARA-DAR: PSNR versus power-delay product.                                                                      | . 28 |

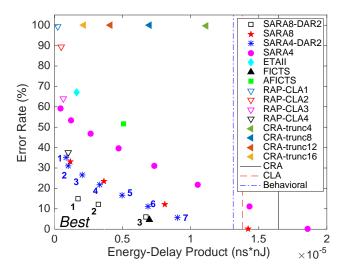

| 2.16   | SARA-DAR: Error rate versus energy-delay product.                                                               | . 29 |

| 2.17   | SARA-DAR: PSNR versus energy-delay product.                                                                     | . 29 |

| 2.18   | Error rate of SARA4-DAR with different detection window.                                                        | . 30 |

| 2.19   | PSNR of SARA4-DAR with different detection window.                                                              | . 30 |

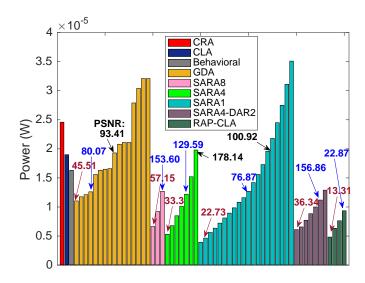

| 2.20   | Iso-delay power comparison. The numbers are PSNR.                                                               | . 31 |

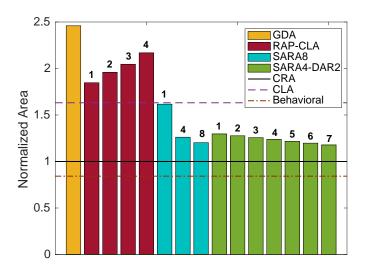

| 2.21 | Area comparison                                                                                                                                        | 32 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

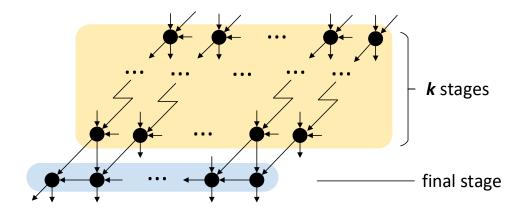

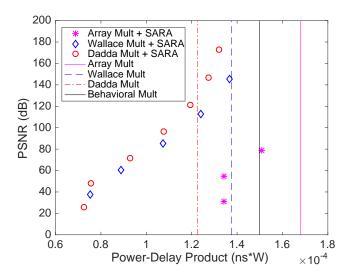

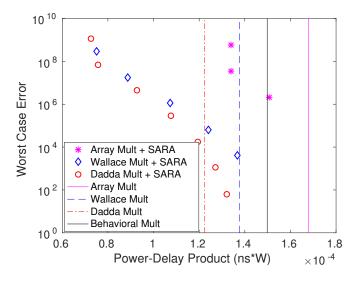

| 2.22 | Basic structure of multiplier                                                                                                                          | 34 |

| 2.23 | Multiplier: PSNR versus power-delay product.                                                                                                           | 35 |

| 2.24 | Multiplier: The worst case error versus power-delay product                                                                                            | 35 |

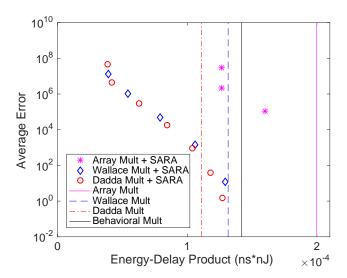

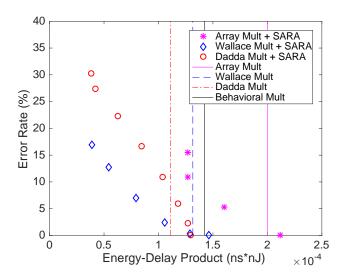

| 2.25 | Multiplier: Average error versus energy-delay product.                                                                                                 | 36 |

| 2.26 | Multiplier: Error rate versus energy-delay product.                                                                                                    | 36 |

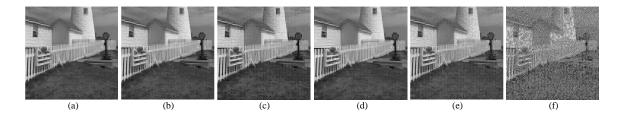

| 2.27 | Comparison of image lenna: (a) accurate adder; (b) SARA4; (c) SARA8; (d) SARA4-DAR2; (e) GDA; (f) RAP-CLA                                              | 37 |

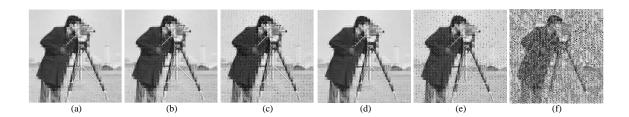

| 2.28 | Comparison of image cameraman: (a) accurate adder; (b) SARA4; (c) SARA8; (d) SARA4-DAR2; (e) GDA; (f) RAP-CLA.                                         | 37 |

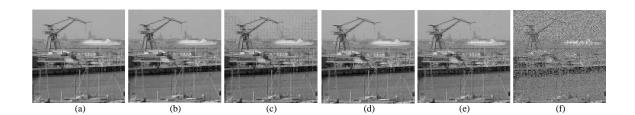

| 2.29 | Comparison of image kiel: (a) accurate adder; (b) SARA4; (c) SARA8; (d) SARA4-DAR2; (e) GDA; (f) RAP-CLA.                                              | 37 |

| 2.30 | Comparison of image house: (a) accurate adder; (b) SARA4; (c) SARA8; (d) SARA4-DAR2; (e) GDA; (f) RAP-CLA.                                             | 38 |

| 2.31 | 2 dimensional descrete cosine transform.                                                                                                               | 38 |

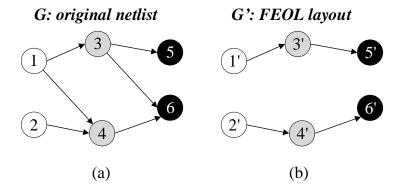

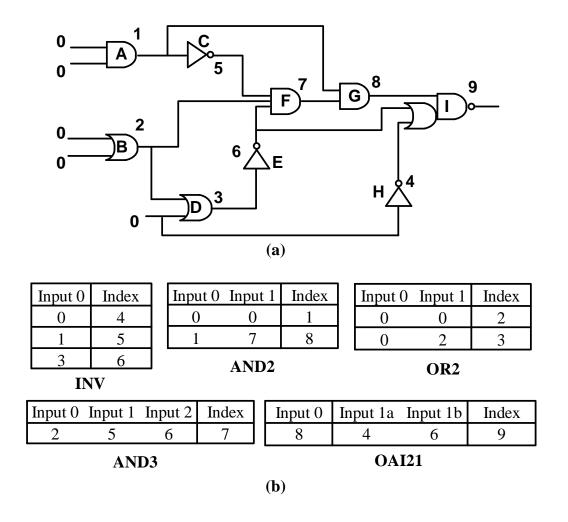

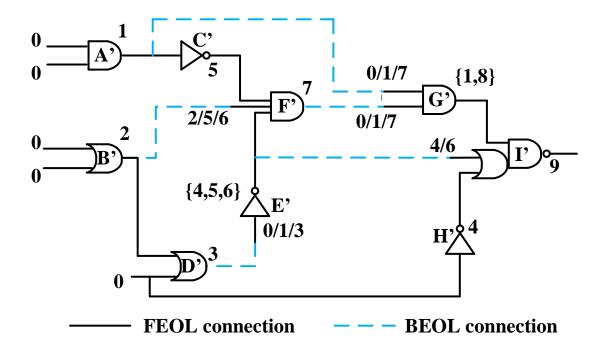

| 3.1  | Graph representations of (a) circuit netlist and (b) its FEOL layout. Each vertex indicates a logic gate, whose logic type is represented by grayscale |    |

|      | with input pins of logic gates and indices.                                                                                                            | 49 |

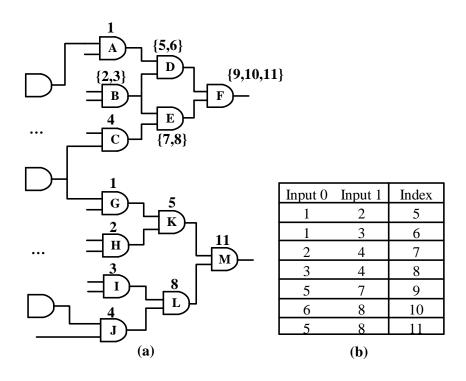

| 3.3  | Matching cells with FEOL layout by using pattern tables (solid line: FEOL connection, dashed line: BEOL connection).                                   | 52 |

| 3.4  | Example of propagating candidates along subcircuit: (a) the subcircuit from layout and (b) the pattern table from netlist                              | 55 |

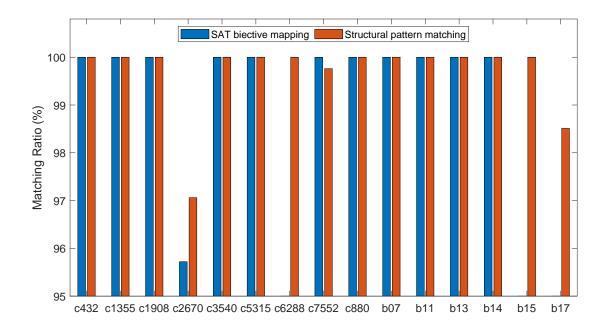

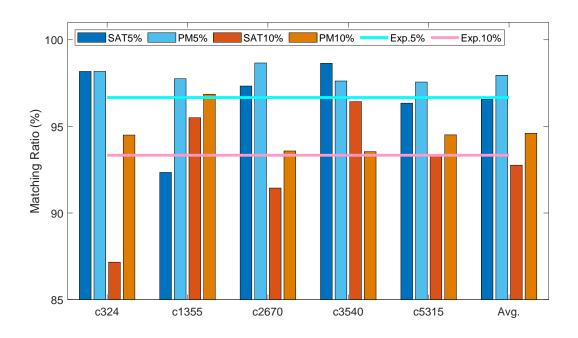

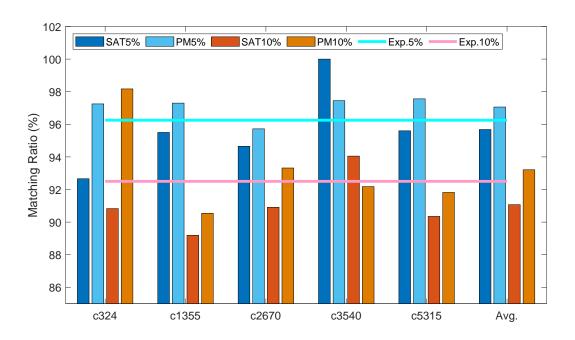

| 3.5  | Experiment results of cases without k-security defense.                                                                                                | 59 |

| 3.6  | Experiment results of cases with 2-security defense.                                                                                                   | 59 |

| 3.7  | Experiment results of cases with 3-security defense.                                                                                                   | 60 |

| 3.8  | Experiment results of cases with 4-security defense.                                                                                                   | 60 |

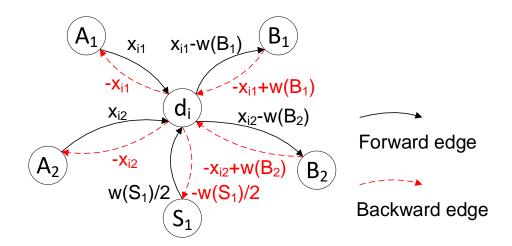

| 4.1  | Example of constraint graph with symmetry constraint.                                                                                                  | 73 |

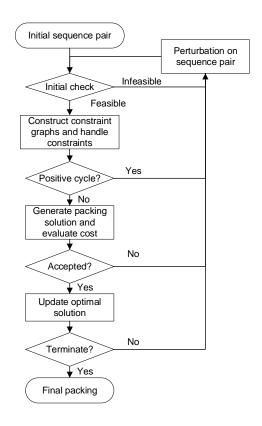

| 4.2  | Overview of simulated annealing algorithm.                                                                                                             | 77 |

| 4.3  | Flow of global route.                                                    | 81  |

|------|--------------------------------------------------------------------------|-----|

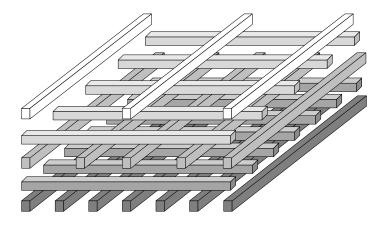

| 4.4  | Model of metal templates.                                                | 83  |

| 4.5  | Scheme of global grids in (a) full view and (b) detailed view            | 84  |

| 4.6  | Flow of detailed routing.                                                | 86  |

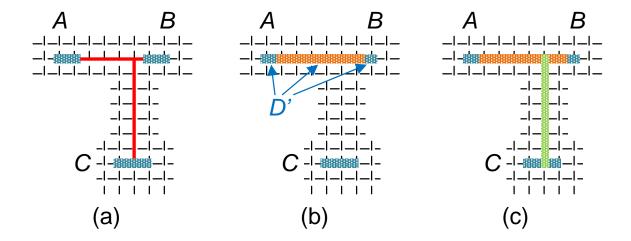

| 4.7  | Example of detailed routing on a three-pin net.                          | 88  |

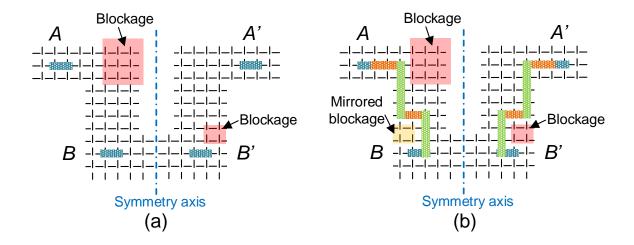

| 4.8  | Example of symmetry nets (a) before and (b) after detailed routing       | 88  |

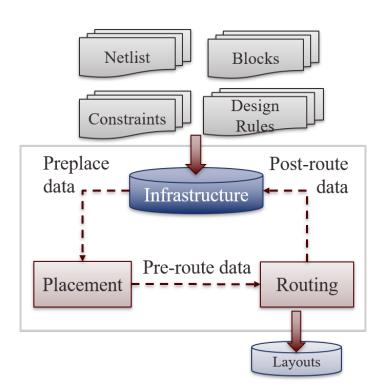

| 4.9  | Infrastructure in hierarchical process and the data flow.                | 89  |

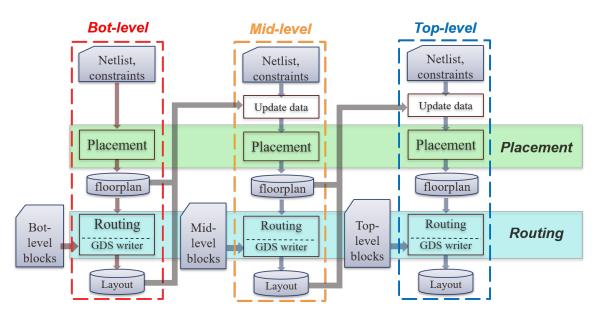

| 4.10 | Scheme of the bottom-up hierarchical flow.                               | 90  |

| 4.11 | Scheme of the mixed-size block placement.                                | 93  |

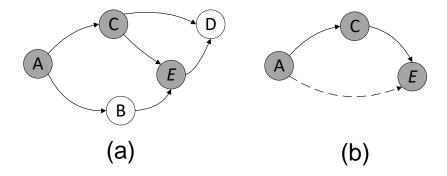

| 4.12 | Example of design reduction: (a) original design v.s. (b) reduced design | 94  |

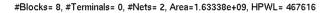

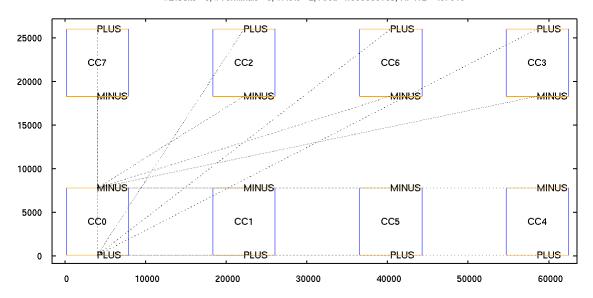

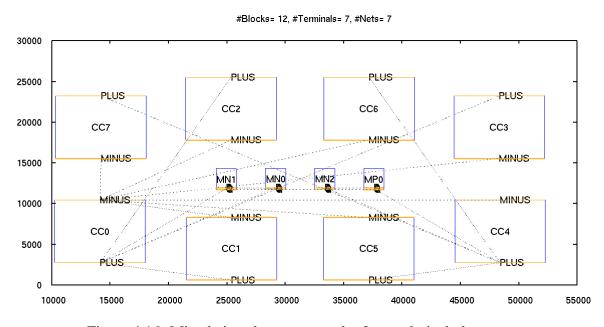

| 4.13 | Layouts of design opamp                                                  | 00  |

| 4.14 | Layouts of design SCF                                                    | 00  |

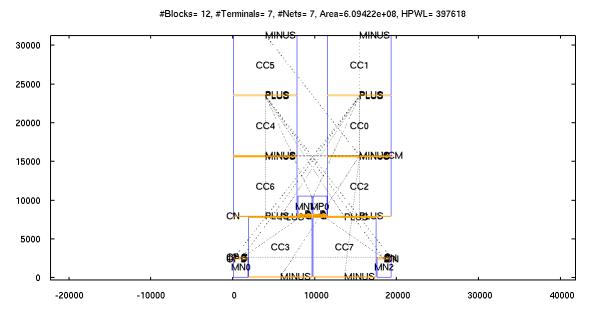

| 4.15 | Mixed-size placement result after macro placement                        | .02 |

| 4.16 | Mixed-size placement result after analytical placement                   | .02 |

| 4.17 | Mixed-size placement result after legalization                           | 03  |

| 4.18 | Simulated annealing based placement result.                              | 03  |

# LIST OF TABLES

| IABLE | P                                                                                                                                                                                                             | age |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1   | Comparison of characteristics for different techniques.                                                                                                                                                       | 8   |

| 2.2   | Definition of parameters for error analysis                                                                                                                                                                   | 13  |

| 2.3   | Error rate of sub-adder with different width                                                                                                                                                                  | 15  |

| 2.4   | Image Quality Comparison in PSNR                                                                                                                                                                              | 39  |

| 3.1   | Comparison of different attack methods.                                                                                                                                                                       | 41  |

| 3.2   | Comparison of different defense methods                                                                                                                                                                       | 42  |

| 3.3   | Experiment results on cases without k-security defense ("MR" indicates the ratio of correctly matched cell).                                                                                                  | 58  |

| 3.4   | Experiment results on cases with k-security defense ("MR" indicates the ratio of correctly matched cell). Number in bold indicates higher ratio than the expected success rate that k-security can guarantee. | 62  |

| 4.1   | Benchmark circuits for experiments                                                                                                                                                                            | 98  |

| 4.2   | Results of hierarchical flow on benchmarks                                                                                                                                                                    | 99  |

| 4.3   | Comparison of performance between different placement on design trackhold                                                                                                                                     | 101 |

#### 1. INTRODUCTION AND MOTIVATION

As the modern semiconductor technology approaches to nanometer era, integrated circuits (ICs) are facing more and more challenges in meeting performance demand and security. With the expansion of markets in mobile and consumer electronics, the increasing demands require much faster delivery of reliable and secure IC products. The conflict between circuit performance, design effort/period and intellectual property security becomes more prominent than ever before. Our research aims to examine the performance and security of circuit designs in three aspects, approximate computing in circuit level, split manufacturing in design level and analog layout automation in flow level. In order to improve the performance and evaluate the security of emerging circuits, we are proposing three practical techniques covering three sub-topics, simple accuracy configurable adders for approximate computing circuits, layout recognition attacks for split-manufactured hardware and hierarchical constraint-driven method for analog layout automation.

# 1.1 Approximate Computing

As the VLSI technology advances to nanometer process, power consumption has become a well-known challenge to further improve the circuit performance. Low power techniques for the conventional exact computing paradigm, such as dynamic voltage scaling (DVS) and clustered voltage scaling (CVS), have been already extensively studied. A comparatively new direction is approximate computing, where errors are intentionally allowed in exchange for power reduction. In many applications, such as audio, video, haptic processing and machine learning, occasional small errors are indeed acceptable. Such error-tolerant applications are found in abundance in emerging applications and technologies.

Approximate computing covers a wide range of research activities across different layers of computing system, from programming languages [1] to transistor-level circuits [2]. Unlike stochastic computing, approximate computing introduces deterministic designs/systems which produce imprecise results [3]. The statistical properties of errors in data or algorithms can be utilized to

tradeoff computation accuracy with performance and energy. As one of the essential basic modules of arithmetic and logic systems, multiple-bit adders have been recently studied in the context of approximate computing [4, 5, 6, 7, 8, 9, 10, 11, 12, 13]. The main idea is based on the fact that critical delay of adder is determined by the length of carry propagation. The reduction in the path of carry propagation provides the opportunity for power reduction by voltage scaling or performance improvement with higher operating frequency.

### 1.2 Split Manufacturing for Hardware Security

Split manufacturing is a security technique against untrusted foundries. By having only front-end-of-line (FEOL) layers manufactured at an untrusted foundry while the back-end-of-line (BEOL) is fabricated at a trusted foundry, attackers in the untrusted foundry do not have complete information to perform attacks such as Trojan insertion, piracy, and overproduction [14, 15, 16]. The same principle can be applied to 3D ICs, where different dies are manufactured by different foundries, since each 3D IC contains two or more independently manufactured ICs which are vertically stacked on top of each other [17]. Despite the security enhancement, split manufacturing still has a significant risk of being successfully attacked [18, 19, 20].

There are two attack scenarios in split manufacturing. (i) The attacker at FEOL foundry does not have circuit netlist and attempts to reverse engineering the entire design for stealing intellectual property, and conducting piracy and overproduction; (ii) The attacker has circuit netlist and tries to recognize critical components on the layout for inserting Trojans. The investigation on scenario (ii) is mostly restricted to only defense techniques. For example, a previous work [17] proposed a method using a metric called k-security to protect the layout by obfuscation. The metric k-security means that for every group of components of which the connections are visible in FEOL, it will have at least another k-1 groups (k is an integer larger than 1) which are identical to it logically. They also proposed a SAT-based algorithm [17] for selecting wires to be manufactured in BEOL to achieve the k-security. Moreover, another work [21] improves the algorithm in [17] and realizes a shorter runtime for achieving k-security. However, the lack of actual attack still limits the ability of evaluating the security of split-manufactured circuits.

## 1.3 Analog Layout Automation

Analog circuits are playing a more and more important role in modern system-on-chip (SoC) applications. At the same time, the demands of analog electronic design automation (EDA) have dramatically increased. However, the physical implementation of analog designs has not been automated to the same degree as digital designs. Analog layout synthesis still remains a manual and time-consuming task due to a large amount of expert knowledge involved, such as complex constraints that are specified manually and satisfied through manual layout.

In the past decade, constraint-driven design approach has been recognized as one potential evolution in analog design automation. The performance specifications can be mapped onto geometric analog-specific constraints relevant to the physical parasitics in layouts. Then, each constraint is enforced during the physical implementation, which guarantees the satisfaction of the original specifications. The quality of an analog design is mostly determined by the degree to which complicated constraints can be satisfied and pre-defined design objectives achieved.

Analog placement is one of the most important step in analog layout synthesis. It determines the physical location of each device or device group, which also limits the degree of design freedom in routing. The problem of placing analog devices with different symmetry and matching constraints has been extensively studied [22, 23, 24, 25, 26]. Moreover, the symmetry constraint, common centroid constraint and other general placement constraints can be simultaneously handled in [27]. Although these geometric constraints can help reduce the errors induced by parasitic mismatch, there is still no guarantee for the performance of the resulting placements. Another problem is that it is very difficult to estimate the circuit performance without actual simulation in placement stage. Besides placement part, analog routing also has great impact on the circuit performance. Although a plenty of work has tried to improve the routing method [28, 29, 30, 31, 32], the challenges in handling multiple constraints and complicated designs are still left unresolved.

#### 2. SIMPLE YET EFFICIENT ACCURACY CONFIGURABLE ADDER\*

#### 2.1 Introduction

Power constraints are a well-known challenge in advanced VLSI technologies. Low power techniques for the conventional exact computing paradigm have already been extensively studied. A comparatively new direction is approximate computing, where errors are intentionally allowed in exchange for power reduction. In many applications, such as audio, video, haptic processing and machine learning, occasional small errors are indeed acceptable. Such error-tolerant applications are found in abundance in emerging applications and technologies.

A great deal of approximate computing research has been concentrated on arithmetic circuits, which are essential building blocks for most of computing hardware. In particular, several approximate adder designs have been developed [2, 3, 5, 4, 6, 7, 8, 9, 10, 11, 33, 34, 35, 36]. One such design [2] achieves 60% power reduction for DCT (Discrete Cosine Transform) computation without making any discernible difference to the images being processed. In realistic practice, accuracy requirements may vary for different applications. In mobile computing devices, different power modes may entail different accuracy constraints even for the same application. Specifically, arithmetic accuracy can be adjusted at runtime using methods such as dynamic voltage and frequency scaling (DVFS) to obtain the best accuracy-power tradeoff. The benefit of runtime accuracy adjustment is demonstrated in [33], but their approximation is realized by voltage over-scaling, where errors mostly occur at the timing-critical path associated with the most significant bits, i.e., errors are often large.

To reduce the overall error, a few approximate designs have been developed by intentionally allowing errors in lower bits with shorter carry chain in addition operation. In [34], a design that considers only the previous k inputs instead of all input bits can approximate the result with the benefit in half of the logarithmic delay. Reliable variable latency carry select adder (VLCSA)

<sup>\*©2018</sup> IEEE. Reprinted, with permission, from Wenbin Xu, Sachin S. Sapatnekar, Jiang Hu, A Simple Yet Efficient Accuracy-Configurable Adder Design, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, June 2018.

shows a speculation technique which introduces carry chain truncation and carry select addition as a basis [4]. A series of Error Tolerant Adders (ETAI, ETAII, ETAIIM), which truncate the carry propagation chain by dividing the adder into several segments, have been proposed [6, 7, 8]. Correlation-aware speculative adder (CASA) in [9] relies on the correlation between MSBs of input data and carry-in values. Another approximate adder that exploits the generate signals for carry speculation is presented [10]. These designs focus on static approximation which pursues almost correct results at the required accuracy. However, in some applications such as image processing or audio/video compression, the required accuracy might vary during runtime. To meet the need of runtime accuracy adjustment, a series of designs are developed to implement accuracy configurable approximation which could be reconfigured online to save more power.

A few accuracy configurable adder designs that use approximation schemes other than voltage over-scaling have been proposed. An early work [12], called ACA, starts with an approximate adder and augments it with an error detection and correction circuit, which can be configured to deliver varying approximation levels or accurate computing. Its baseline approximate adder contains significant redundancy and the error detection/correction circuit further increases area overhead. The ACA design [12] is generalized to a flexible framework GeAr in [37]. In both ACA and GeAr, the error correction must start from the least significant bits and hence accuracy improves slowly in the progression of configurations. The work of Accurus [38] modifies ACA/GeAr to overcome this drawback and achieves graceful degradation. However, in ACA, GeAr as well as Accurus, the error correction circuit is pipelined, implying that the computation in accurate mode takes multiple clock cycles and causes data stalls.

An alternative direction of accuracy configurable adder design is represented by GDA [13] and RAP-CLA [39]. These methods start with an accurate adder and use carry prediction for optional approximation. As such, they no longer need error detection/correction and do not incur any data stall. In addition, they intrinsically support graceful degradation. The GDA design [13] is composed by accurate CRA (Carry Ripple Adder) and extra configurable carry prediction circuitry, similar as the carry look-ahead part of CLA (Carry Look-ahead Adder). Thus, its area is generally

quite large. RAP-CLA [39] is based on accurate CLA design and reuses a portion of the carry look-ahead circuit as carry prediction. This leads to an overall area that is less than GDA but greater than CLA. In [39], the carry-prediction-based approach is shown to be superior to error-correction-based design [37].

We propose a new carry-prediction-based accuracy configurable adder design: SARA (Simple Accuracy Reconfigurable Adder). It is a simple design with significantly less area than CLA, which, to the best of our knowledge, has not been achieved in the past in accuracy configurable adders. SARA inherits the advantages of all previous carry-prediction-based approaches: no error correction overhead, no data stall and allowing graceful degradation. Compared to GDA [13], SARA incurs 50% less PDP (Power Delay Product) and can reach the same PSNR (Peak Signal-to-Noise Ratio). Moreover, SARA demonstrates remarkably better accuracy-power-delay tradeoff than the latest, and arguably the best, previous work RAP-CLA [39]. A delay-adaptive reconfiguration technique is developed to further improve the accuracy-power-delay tradeoff. The proposed designs are also validated by multiplication and DCT computation in image processing.

## 2.2 Prior Works and Rationale of Our Design

We review a few representative works on accuracy configurable adder design and show the relation with our method. These designs can be generally categorized into two groups: error-correction-based configurations [12, 37, 38] and carry-prediction-based configurations [13, 39].

The main idea of an error-correction-based approach [12, 37, 38] is shown in Figure 2.1. The scheme starts with an approximate adder (the dashed box), where the carry chain is shortened by using separated sub-adders with truncated carry-in. In order to reduce the truncation error, the bitwidth in some sub-adders contains redundancy. For example, *sub-adder2* calculates the sum for only bit 8 and 9, but it is an 8-bit adder using bit [9 : 2] of the addends, 6 bits of which are redundant. Even with the redundancy, there is still residual error which is detected and corrected by additional circuits. In Figure 2.1, the errors of *sub-adder2* must be corrected by *error-correction2* before the errors of *sub-adder3* are rectified by *error-correction3*. As such, the configuration progression always starts with small accuracy improvements. The redundancy and error detection/correction

Figure 2.1: Error-correction-based configurable adder.

incur large area overhead. Since the error correction circuits are usually pipelined, an accurate computation may take multiple clock cycles and could stall entire datapath, depending on the addend values.

Figure 2.2: Carry-prediction-based configurable adder.

The framework of carry-prediction-based methods [13, 39] is shown in Figure 2.2. These schemes start with an accurate adder design, which is formed by chaining a set of sub-adders.

Each sub-adder comes with a fast but approximated carry prediction circuit. By selecting between the carry-out from sub-adder or carry prediction, the overall accuracy can be configured to different levels. Such an approach does not need error detection/correction circuitry. Moreover, the configuration of higher bits is independent of lower bits. This leads to fast convergence or graceful degradation in the progression of configurations. In GDA [13], the sub-adders are CRA designs while the carry-prediction circuit is similar to the carry look-ahead part of CLA. Further, its carry prediction can be configured to different accuracy levels. However, the complicated carry prediction induces large area overhead. The RAP-CLA scheme [39] uses CLA for its baseline where the carry-ahead of each bit is computed directly from the addends of all of its lower bits. Its carry prediction reuses a part of the look-ahead circuit rather than building extra dedicated prediction circuitry, and hence is more area-efficient than GDA. But its baseline is much more expensive than GDA.

Table 2.1: Comparison of characteristics for different techniques.

|              | Baseline      | Error      | Graceful    | Carry       |

|--------------|---------------|------------|-------------|-------------|

| Method       | sub-adder     | correction | degradation | prediction  |

| ACA [12]     | Redundant CRA | Yes        | No          | No          |

| GeAr [37]    | Redundant CRA | Yes        | No          | No          |

| Accurus [38] | Redundant CRA | Yes        | Yes         | No          |

| GDA [13]     | CRA           | No         | Yes         | Stand-alone |

| RAP-CLA [39] | CLA           | No         | Yes         | Reuse       |

| SARA (ours)  | CRA           | No         | Yes         | Reuse       |

Our design is a carry-prediction-based approach. Its sub-adders are CRA instead of expensive CLA as in RAP-CLA. Its carry prediction also reuses part of the sub-adders rather than having dedicated prediction circuitry. As such, it avoids the disadvantages of both GDA and RAP-CLA. A comparison among the characteristics of these different techniques is provided in Table 2.1.

# 2.3 Simple Accuracy Reconfigurable Adder

#### 2.3.1 Preliminaries

An N-bit adder operates on two addends  $A=(a_N,...,a_i,...,a_1)$  and  $B=(b_N,...,b_i,...,b_1)$ . For bit i, its carry-in is  $c_{i-1}$  and its carry-out is  $c_i$ . Defining the carry generate bit  $g_i=a_i\cdot b_i$ , propagate bit  $p_i=a_i\oplus b_i$  and kill bit  $k_i=\bar{a}_i\cdot \bar{b}_i$ , the conventional full adder computes the sum  $s_i$  and carry  $c_i$  according to

$$s_i = p_i \oplus c_{i-1}, \tag{2.1}$$

$$c_i = g_i + p_i \cdot c_{i-1}. \tag{2.2}$$

A gate level schematic of conventional full adder is provided in Figure 2.3(a). A CRA is used to chain N bits of conventional full adders together.

Figure 2.3: (a) Conventional full adder; (b) Our carry-out selectable full adder; (c) Our carry-in configurable full adder.

By applying Equation (2.2) recursively, one can get

$$c_i = g_i + p_i g_{i-1} + \dots + g_1 \prod_{k=2}^i p_k + c_0 \prod_{k=1}^i p_k.$$

(2.3)

This equation implies that  $c_i$  can be computed directly from g and p of all bits, without waiting for the c of its lower bits to be computed. This observation is the basis for CLA adder.

# 2.3.2 SARA: Simple Accuracy Reconfigurable Adder Design

In SARA, an N-bit adder is composed by K segments of L-bit sub-adders, where  $K = \lceil N/L \rceil$  (see Figure 2.2). Each sub-adder is almost the same as CRA except that the MSB (Most Significant Bit) of a sub-adder, which is bit i, provides a carry prediction as

$$c_i^{prdt} = q_i (2.4)$$

For the LSB (Least Significant Bit) of the higher-bit sub-adder, which is bit i+1, its carry-out  $c_{i+1}$  can be computed using one of two options: either by the conventional  $c_{i+1} = g_{i+1} + p_{i+1} \cdot c_i$ , or by using the carry prediction as

$$c_{i+1} = g_{i+1} + p_{i+1} \cdot c_i^{prdt} = g_{i+1} + p_{i+1} \cdot g_i$$

(2.5)

The selection between the two options is realized using MUXes as in Figure 2.4 and the MUX selection result is denoted as  $\hat{c}_i$ . Comparing Equation (2.5) with (2.3), we can see that the carry prediction is a truncation-based approximation to carry computation\*. Therefore,  $\hat{c}_i$  can be configured to either accurate mode or approximation mode, i.e.,

$$\hat{c}_i \leftarrow \begin{cases} c_i^{prdt}, & \text{if approximation mode} \\ c_i, & \text{if accurate mode.} \end{cases}$$

(2.6)

It should be noted that the carry prediction  $c_i^{prdt}$  reuses  $g_i$  in an existing full adder instead of introducing an additional dedicated circuit as in [13] or Figure 2.2. This prediction scheme makes a very simple modification to the conventional full adder, as shown in Figure 2.3(b).

One can connect  $\hat{c}_i$  to its higher bit i+1 to compute both carry  $c_{i+1}$  and sum  $s_{i+1}$ , as in

<sup>\*</sup>A similar approximation is used in static approximate adder design [10].

GDA [13] and RAP-CLA [39]. We suggest an improvement over this approach by another simple change as in Figure 2.3(c), where  $s_{i+1}$  is based on  $c_i$  instead of  $\hat{c}_i$ . Such approach can help reduce the error rate in outputs when an incorrect carry is propagated. Because the sum keeps accurate and the carry will not be propagated when addends are exactly the same. Moreover, out of all four configurations of sum/carry calculation by approximate/accurate carry-in, the most meaningful way is to have sum bit calculated by accurate carry and make carry bit configurable. So sum  $s_{i+1}$  is calculated directly by accurate carry  $c_i$  without the option of  $c_i^{prdt}$ . Applying this in SARA as in Figure 2.4, in the approximation mode, computing  $s_{j+1}$  from  $c_j$  can still limit the critical path to be between  $c_{i-1}^{prdt}$  and  $s_{j+1}$ , but has higher accuracy than computing  $s_{j+1}$  from  $\hat{c}_j$ . Compared to sum computation in GDA and RAP-CLA, this technique improves accuracy with almost no additional overhead. Compared to CRA, the overhead of SARA is merely the MUXes, which is almost the minimum possible for configurable adders.

Figure 2.4: Design of SARA.

Although  $s_{j+1}$  is calculated by accurate carry  $c_j$ , its delay can still be reduced by approximate carry in lower sub-adder. In a multi-bit adder, the delay of sum bit depends on the carry chain propagated from its lower bits. In our SARA structure, even when accurate carry  $c_j$  is propagated at bit j, the carry chain might be truncated by approximate carry in other lower bits. In Figure 2.4, when  $c_{i-1}^{prdt}$  is propagated, the delay of  $s_{j+1}$  is reduced as its path is shorten to be between bit i-1

and j+1. We can take the 12-bit adder in Figure 2.5 as an example. For 12-bit SARA working in approximate mode, the sum  $s_9$  uses the accurate carry  $c_8$  from a lower sub-adder (bit 5 to 8). But  $c_8$  is propagated from approximate carry  $c_4^{prdt}$  of another sub-adder (bit 1 to 4). As shown in the figure, the delay of  $s_9$  in SARA is about 6 stages. Compared with the same bit in CRA, the delay of sum bit  $s_9$  in SARA is reduced by 3 stages. Similar delay reduction can be observed in other sum bits (bit 6 to 12). For sums at bit 1 to 5, their delay is the same as CRA because they are using an accurate carry  $c_0$  from LSB. As a result, the maximum delay in 12-bit SARA is reduced, since for a multi-bit adder its maximum delay depends on the longest critical path.

Figure 2.5: Implementation of 12-bit adder in (a) CRA and (b) SARA.

## 2.3.3 Usage of SARA

When  $\hat{c}_i$  is configured to be  $c_i$  for all K sub-adders, SARA operates very much like the CRA, where the critical path is along N-bit full adders. If all  $\hat{c}_i$  are selected to be  $c_i^{prdt}$ , the critical path is shortened to roughly L-bit full adders. This large delay reduction can be translated to power reduction by supply voltage scaling. Voltage scaling (reducing supply voltage) on digital circuits will lead to increase in delay. So we can reduce the supply voltage on SARA to make its critical

delay same as that of CRA under normal voltage. As the supply voltage decreases, the power consumption could be reduced. There can be  $2^{K-1}$  different configurations. For two configurations with the same critical path length, obviously we only need the one with higher accuracy. Therefore, there are K effective configurations, with critical path length of L-bit, 2L-bit,  $..., K \cdot L \simeq N$ -bit full adders. The delay of such configurable design varies according to configured accuracy, which results in different power reduction by voltage scaling.

### 2.4 SARA Error Analysis

In this section, we give a theoretical analysis on the expected error of our SARA design and validate the results by numerical experiments. To make it easier for readers to follow the analysis, we list the parameters used in this section as Table 2.2.

Table 2.2: Definition of parameters for error analysis

| Parameter        | Definition                           |

|------------------|--------------------------------------|

| $p_i$            | propagate bit at bit $i$             |

| $g_i$            | generate bit at bit $i$              |

| $k_i$            | kill bit at bit i                    |

| $c_i$            | accurate carry-out bit at bit i      |

| $c_i^{prdt}$     | approximate carry-out bit at bit $i$ |

| $\hat{c}_i$      | carry-in bit at bit $i+1$            |

| $ER_i^{prdt}$    | error rate of $c_i^{prdt}$           |

| $\widehat{ER}_i$ | error rate of $\hat{c}_i$            |

For any bit i in carry-out selectable full adder as in Figure 2.3(b), an error in approximate carry-out occurs when  $c_i^{prdt} \neq c_i$ . There is only one situation where this error may happen: when  $c_{i-1} = 1$ ,  $p_i = 1$ ,  $c_i^{prdt} = 0$  and  $c_i = 1$ . Then the error rate, or probability of such error, is given by

$$ER_i^{prdt} = P(c_i^{prdt} \neq c_i) = P(c_i^{prdt} = 0, c_i = 1)$$

$$= P(c_{i-1} = 1, p_i = 1)$$

$$= P(c_{i-1} = 1)P(p_i = 1)$$

(2.7)

where P indicates probability and the last part assumes that  $c_{i-1}$  and  $p_i$  are independent of each other. Then, if the approximate/accurate carry-out can be selected by a MUX gate, the error rate of MUX output  $\hat{c}_i$  is

$$\widehat{ER}_i = P(\hat{c}_i \neq c_i) = \begin{cases} ER_i^{prdt}, & \text{if } \hat{c}_i \leftarrow c_i^{prdt} \\ 0, & \text{if } \hat{c}_i \leftarrow c_i. \end{cases}$$

(2.8)

Let's consider a configuration of SARA in Figure 2.4, which has both bit j and bit i-1 in approximate mode. For the sub-adder which calculates addends from bit i to bit j, its LSB (bit i) is using carry-in configurable full adder, while its MSB (bit j) is in carry-out selectable full adder. According to Equation (2.7) and (2.8), the error rate of  $\hat{c}_j$  is determined by the probabilities of  $c_{j-1}=1$  and  $p_j=1$ .

$$\widehat{ER}_j = P(c_{j-1} = 1)P(p_j = 1)$$

(2.9)

According to the logic of addition, the carry-out bit is calculated by the carry-in and addends. There are two cases which can result in  $c_{j-1} = 1$ : generate bit  $g_{j-1}$  should be 1 in case of carry-in  $c_{j-2} = 0$ ; or kill bit  $k_{j-1}$  must be 0 when carry-in comes with  $c_{j-2} = 1$ . Then, the probability of  $c_{j-1} = 1$  can be computed by the probability of  $c_{j-2} = 1$  as

$$P(c_{j-1} = 1) = P(c_{j-2} = 0, g_{j-1} = 1) + P(c_{j-2} = 1, k_{j-1} = 0)$$

$$= P(c_{j-2} = 0)P(g_{j-1} = 1) + P(c_{j-2} = 1)P(k_{j-1} = 0)$$

$$= [1 - P(c_{j-2} = 1)]P(g_{j-1} = 1) + P(c_{j-2} = 1)P(k_{j-1} = 0).$$

(2.10)

Similarly, the probability of  $c_{j-2}=1$ ,  $c_{j-3}=1$ , ...,  $c_{i+1}=1$  can be calculated using the same formula. For the probability of  $c_i=1$ , it's a little different because the carry-out  $c_i$  in our carry-in configurable full adder is based on predicted carry-in  $\hat{c}_{i-1}$  instead of  $c_{i-1}$ . Considering that bit i-1 is configured in approximate mode, we have

$$P(\hat{c}_{i-1}=1) = P(c_{i-1}^{prdt}=1) = P(g_{i-1}=1). \tag{2.11}$$

Table 2.3: Error rate of sub-adder with different width

| Sub-adder length L | Calculated error rate | Simulated error rate |

|--------------------|-----------------------|----------------------|

| 1                  | 1/8 = 0.125           | 0.1257               |

| 2                  | 3/16 = 0.1875         | 0.1879               |

| 3                  | 7/32 = 0.21875        | 0.2187               |

| 4                  | 15/64 = 0.234375      | 0.2347               |

| 5                  | 31/128 = 0.2421875    | 0.2424               |

| 6                  | 63/256 = 0.24609375   | 0.2464               |

Then, the probability of  $c_i = 1$  can be expressed as

$$P(c_i = 1) = [1 - P(g_{i-1} = 1)]P(g_i = 1) + P(g_{i-1} = 1)P(k_i = 0).$$

(2.12)

By expanding Equation (2.10) recursively till bit i, the probability of  $c_{j-1} = 1$  can be calculated by a function of generate bit and kill bit from bit i - 1 to bit j - 1.

$$P(c_{i-1}=1) = f\{P(g_{i-1}=1), \dots, P(g_{i-1}=1), P(k_i=0), \dots, P(k_{i-1}=0)\}.$$

(2.13)

Assuming that the inputs for adder are uniformly distributed random numbers, we have P(g=1)=1/4, P(k=0)=3/4. As the length of sub-adders varies from 1 to 6, the error rates of  $\hat{c}_j$  calculated by Equation (2.9) are listed in the second column of Table 2.3. Corresponding data from numerical simulation in Matlab are also presented in the last column. The error rates calculated by our method match well with experiment results, which demonstrates the correctness of our mathematical analysis. We can also observe that as the length of sub-adder increases the error rate is bounded by 0.25. That is because when the length of sub-adder comes to infinite the probability of c=1 will become 0.5 as the normal carry in accurate adder.

**Theorem 1.** If  $\mathcal{I}$  is the set of bits with MUX at output, the expected error of SARA for unsigned integers is

$$\sum_{\forall i \in \mathcal{I}} \widehat{ER}_i \cdot P(p_{i+1} = 1) \cdot 2^{i+1}.$$

*Proof.* The overall expected error of SARA can be calculated by summing respective error intro-

duced by every approximate bit from LSBs to MSBs. But the propagation of inaccurate carry bit may cause error in higher bit which also be counted in the calculation of lower bit. So we need to exclude those errors to avoid over-calculation in the total error.

Let's consider the SARA design in Figure 4 which have approximate configuration at both bit i-1 and bit j. Assuming that bit i-1 is the lowest bit configured in approximate mode, we know that all sum bits  $s_k$  ( $k \in [1, i-1]$ ) as well as carry bit  $c_{i-1}$  are accurate.

$$c_{i-1} = c_{i-1}^{acc} (2.14)$$

Then the probability that carry prediction at MUX output  $\hat{c}_{i-1}$  mismatches with accurate carry  $c_{i-1}^{acc}$  should be the same as the error rate of MUX ouput  $\hat{c}_{i-1}$ .

$$P(\hat{c}_{i-1} \neq c_{i-1}^{acc}) = P(\hat{c}_{i-1} \neq c_{i-1}) = \widehat{ER}_{i-1}$$

(2.15)

According to the structure of carry-in configurable full adder (Figure 3(c)), sum bit  $s_i$  calculated from  $c_{i-1}$  is always accurate; however, the carry-out bit  $c_i$  becomes conditionally accurate which depends on both carry-in bit and propagate bit. As shown in Equation (2.16), the scenario of accurate carry-out can be attributed to two conditions: when the carry-in is not accurate, the carry-out bit becomes accurate as the propagate bit is false; otherwise, it must be accurate no matter what kind of addends are given.

$$P(c_i = c_i^{acc}) = P(\hat{c}_{i-1} = c_{i-1}^{acc}) + P(\hat{c}_{i-1} \neq c_{i-1}^{acc})P(p_i = 0)$$

(2.16)

Its complementary part, the probability of inaccurate carry  $c_i$ , can be expressed as

$$P(c_{i} \neq c_{i}^{acc}) = P(\hat{c}_{i-1} \neq c_{i-1}^{acc})P(p_{i} = 1)$$

$$= P(\hat{c}_{i-1} \neq c_{i-1})P(p_{i} = 1)$$

$$= \widehat{ER}_{i-1} \cdot P(p_{i} = 1).$$

(2.17)

As a result, the approximation at bit i-1 would cause an inaccurate carry-in  $c_i$  at bit i+1, which introduces the magnitude of  $2^i$  to the overall error in final result. Then the expected error introduced by approximation at bit i-1 can be estimated by

$$E[e_{i-1}] = P(c_i \neq c_i^{acc}) \cdot 2^i = \widehat{ER}_{i-1} \cdot P(p_i = 1) \cdot 2^i.$$

(2.18)

Next, we consider the expected error introduced by approximation at bit j. As bit j is not the lowest bit in approximate mode, there is a chance that the propagation of inaccurate carry from bit i-1 induces error at bit j while it has be taken into account in the error calculation of bit i-1. Then the problem is whether the carry  $c_j$  is accurate when there is a mismatch between  $\hat{c}_j$  and  $c_j$ . If not, we need to exclude the impact from lower bit when estimating the error at bit j. Let's answer this question in the following cases.

- Case 1: If any propagate bit in sub-adder (bit i to j) equals 0, the error propagation by inaccurate carry will be paused. In another word, the error carried by inaccurate carry bit cannot be propagated to higher bit any more, because the carry-out is independent of carry-in when propagate bit is false. In this case, the carry  $c_j$  should be always accurate regardless of the configuration at bit j.

- Case 2: If all propagate bits of sub-adder equal 1, the value of inaccurate carry  $\hat{c}_{i-1}$  (0 instead of 1) will be propagated to  $c_j$ . In this situation, the actual value of  $c_j$  propagated from bit i-1 must be 0, while the accurate value should be 1. Assuming that  $\hat{c}_j$  mismatches with  $c_j$ , we can state that the value of  $\hat{c}_j$  must be 1. However, it conflicts with the generation of  $c_j$ , because carry  $c_j$  is the logical conjunction of  $\hat{c}_j$  and  $p_j \cdot c_{j-1}$ . So there should be no mismatch between  $\hat{c}_j$  and  $c_j$  in this case.

In conclusion, when there is a mismatch between  $\hat{c}_j$  and  $c_j$ , the value of carry  $c_j$  must be accurate. We can further conclude that the contributions of every approximate bit to the total error

are independent to each other. Similar to bit i-1, the expected error at bit j can be estimated by

$$E[e_j] = \widehat{ER}_j \cdot P(p_{j+1} = 1) \cdot 2^{j+1}. \tag{2.19}$$

Thus, the total error can be obtained by summing up the errors respectively introduced by every approximate bit.

$$E = \sum_{\forall i \in \mathcal{I}} E[e_i] = \sum_{\forall i \in \mathcal{I}} \widehat{ER}_i \cdot P(p_{i+1} = 1) \cdot 2^{i+1}$$

(2.20)

If input addends are random variables following uniform distribution, the expected error of SARA is given by

$$E = \sum_{\forall i \in \mathcal{I}} \widehat{ER}_i \cdot 2^i. \tag{2.21}$$

Figure 2.6: Average error of 9-bit SARA in different configuration.

We can verify Equation (2.21) by numerical simulation of a 9-bit SARA design. In our experiment, SARA consists of 9 sub-adders whose width is 1 bit. The results are from 200K run

of Monte Carlo simulation with uniform distributed numbers as input. As shown in Figure 2.6, there are 2 sets of data for comparison, experimental data are obtained directly in experiments and estimated data are calculated by Equation (2.21). The average errors from experiment are almost the same as the estimated values. According to the analysis above, we can estimate the average error of SARA in any configuration, given the distribution of input numbers.

Since  $|\mathcal{I}| = K-1$ , the error of the worst case approximation mode increases with the number of sub-adders, K. In addition, area overhead increases with K. On the other hand, a large K implies smaller L, and thus often facilitates shorter critical path and more power reductions. Therefore, K significantly affects the tradeoff among accuracy, power, delay and area.

#### 2.5 Delay-Adaptive Reconfiguration of SARA

Almost all previous works on accuracy configurable adder [12, 37, 38, 13, 39] reasonably assume that accuracy configuration is decided by architecture/system level applications. We propose a self-configuration technique for the scenarios where architecture/system level choice is either unclear or difficult. Simulation results show that SARA with the self-configuration outperforms several previous static approximate adder designs.

The main idea of self-configuration is based on the observation that the actual worst case path delay depends on addend values. Specifically, the actual path delay is large only when a carry is propagated through several consecutive bits. Any false propagate bit from the addends results in a shorter carry propagation chain. When the actual carry propagation chain is short, there is no need to use approximation configuration, which is intended to cut carry chain shorter. We propose a Delay Adaptive Reconfiguration (**DAR**) technique: the output of a MUX in SARA is set to approximation mode only when a potentially long carry chain is detected. Compared to the constantly-approximate configuration, some errors for actual short carry chains are avoided, the actual long carry chain is cut shorter, and delay/power reduction can be still obtained.

The long carry chain detection and SARA-DAR design are shown in Figure 2.7(a). When MUX is switched to accurate mode by any false propagate bit in detection window, the actual carry chain is retained by the position of false propagate bit. To obtain a shorter carry chain in

Figure 2.7: Design of DAR for SARA operating in a) approximate mode and b) accurate mode.

accurate mode, the detection window for MUX at bit i in MSB should start from bit i + 1. In the example of Figure 2.7, we use a detection window of 2 bits  $(p_{i+1} \text{ and } p_{i+2})$  to tell if there is a carry propagation across two sub-adders, and configure the MUX according to

$$\hat{c}_i \leftarrow \begin{cases} c_i^{prdt}, & \text{if } p_{i+1} \cdot p_{i+2} \text{ is true} \\ c_i, & \text{otherwise.} \end{cases}$$

(2.22)

In approximation mode, the effective carry chain is represented by the blue line in Figure 2.7(a) and its length is no greater than L+1 bits. When the MUX is set to accurate mode, the carry chain is indicated by the red lines in Figure 2.7(b) and their lengths can be restrained to within L+2 bits. Since the propagate bits only depend on local primary inputs, we can reuse propagate bits in higher bits to save cost. Note that in this case the detection overhead here is almost the minimum possible, i.e., only one NAND gate for configuring each MUX.

In Figure 2.7, we use 2-bit detection window, which can be generalized to W-bit. Then, the error rate for MUX at bit i becomes

$$\widehat{ER}_i^{dar} = ER_i^{prdt} \cdot \prod_{j=1}^W P(p_{i+j} = 1)$$

(2.23)

The detection window size W decides the tradeoff between accuracy and the effective carry chain length in accurate mode, which is L+W. When W increases, the error rate decreases while the critical path length in accurate mode increases.

#### 2.6 Experimental Results

## 2.6.1 Experiment Setup and Evaluation

Our SARA, SARA-DAR and several previous designs are synthesized to 32-bit adders by Synopsys Design Compiler using the Nangate 45nm Open Cell Library. The synthesized circuits are placed and routed by Cadence Encounter. The default supply voltage level is 1.25V. To make fair comparisons across architectures, we describe all designs by structural modeling in Verilog to reduce the impact of synthesis and optimization. For comparison, we synthesize the accurate adder in behavioral modeling which is described by expressional operator in Verilog. The netlist of such accurate adder should be automatically optimized by synthesizer in Design Compiler, which is different from any man-craft gate-level design. In addition, we set the same supply voltage and no delay constraint on all designs for the same reason.

The evaluation of accuracy configurable adder designs can be subtle and therefore is worth some discussion.

- 1. **Area**: In the literature, the area sometimes refers to the part of the circuit working in a certain mode, e.g., the circuit for the accurate part is not included in area estimation when evaluating approximation mode. We report the routed layout area of each entire design.

- 2. **Delay**: Some configurable adders, such as ACA [12] and GeAr [37], implement error correction with pipelining, which sometimes takes multiple clock cycles to determine the complete

result. The delay or performance evaluation of such designs is much more complicated than unpipelined designs. Our work is focused on unpipelined implementation, although it can be pipelined. Thus, the reported delay is the maximum combinational logic path delay obtained from Synopsys PrimeTime with consideration of wire delay.

- 3. **Power**: The power dissipation is estimated by Synopsys PrimeTime considering both static and dynamic power.

- 4. **Accuracy**: We use PSNR (Peak Signal-to-Noise Ratio), where errors are treated as noise, as a composite accuracy metric for considering both error magnitude and error rate. In addition, the worst case error, which is equivalent to the maximum error magnitude [11], and error rate are also reported. Each error result is from 100K-run Matlab-based Monte Carlo simulation assuming uniform distribution of addends.

- 5. **Tunability**: This means the range and granularity of runtime accuracy configurations. Sometimes, this can be confused with design-time flexibility.

- 6. **Tradeoff**: The tradeoff among the above factors is complex and is difficult to capture in a simple picture. To this end, we use composite metrics including power-delay product (PDP), energy-delay product (EDP) and iso-delay power.

### 2.6.2 Results of Tradeoff for Different Configurations

In this part, we mainly compare the following accuracy configurable adder designs:

- GDA [13]: We use the same design as in [13], where each sub-adder has 4 bits. This design can be configured by choosing accurate or predicted carry-out for each sub-adder. The carry prediction at each segment can also be configured to different accuracy levels by using different number of lower-bit addends.

- RAP-CLA [39]: We implement four different designs with carry prediction bit-width from 1 bit to 4 bits, which is reflected in the name. For example, RAP-CLA2 means each of its

carry prediction is from its 2 lower bits. As in [39], each design can be configured to either only one approximation mode or accurate mode.

• SARA: This is our proposed design and we evaluate sub-adder bit-width of 1 bit, 4 bits and 8 bits, referred to as SARA1, SARA4 and SARA8, respectively.

Figure 2.8: SARA: PSNR versus power-delay product.

The main result is shown in Figure 2.8, where each point is from one configuration of one design. The computation accuracy is evaluated by PSNR while the conventional design objectives are characterized by PDP. A design and configuration is ideal if it has large PSNR but low PDP, i.e., northwest in the figure. PDPs of two classic accurate designs, CRA and CLA, are indicated by the two vertical lines as their PSNR is near infinity. The result of SARA working in completely accurate mode is unable to be presented in the figure, because its infinite PSNR cannot be displayed as a single dot in the plot. Evidently, the best solutions are from SARA4 and SARA8. At 100dB PSNR, the PDP of SARA4 and SARA8 is about a half of GDA or CRA. The solutions from RAP-CLA, the latest previous work, are also largely dominated by SARA in PSNR-PDP tradeoff. An interesting case is SARA1. Its tradeoff is similar as GDA and not as good as SARA4 or SARA8.

Figure 2.9: SARA: Average error versus power-delay product.

Figure 2.10: SARA: The worst case error versus power-delay product.

However, its runtime tunability is superior to all the other designs. It has the largest tuning range, the finest tuning granularity and very smooth tradeoff.

Figure 2.9 and 2.10 show the tradeoff between error magnitude and power-delay product. Ideally a better design or configuration has smaller average error or worst case error with lower PDP, which can be marked in the lower left corner of the figure. In Figure 2.9, SARA4 and SARA8 dom-