# TRANSISTOR-LEVEL DEFECT-TOLERANT TECHNIQUES FOR RELIABLE DESIGN AT THE NANOSCALE

BY

## FARHAN KHAN

A Thesis Presented to the DEANSHIP OF GRADUATE STUDIES 四於一条一条一条一条一条一条一条一条一条一条一条一条一条一条一条一条

#### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

# MASTER OF SCIENCE

In COMPUTER ENGINEERING

June 2009

## KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN 31261, SAUDI ARABIA

#### DEANSHIP OF GRADUATE STUDIES

This thesis, written by FARHAN KHAN under the direction of his thesis adviser and approved by his thesis committee, has been presented to and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE IN COMPUTER ENGINEERING.

Thesis Committee Dr. Aiman H. El-Maleh (Adviser) Dr. M. E. S. Elrabaa (Co-adviser) Dr. Sadiq M. Sait (Member) Dr. Adnan A. Gutub (Member) Dr. Abdelhafid Bouhraoua (Member) Dr. Adnan A. Gutub Department Chairman Dr. Salam A. Zummo Dean of Graduate Studies 14 909 Date

Dedicated to my beloved father Mr. Abdul Aziz Khan

# ACKNOWLEDGMENTS

In the name of Allah, the Most Beneficent, the Most Merciful

All praise be to Allah (The One and The Only Creator of everything) for His limitless blessings. May Allah bestow peace and His choicest blessings on the last prophet, Muhammad (Peace Be Upon Him), his family (May Allah be pleased with them), his companions (May Allah be pleased with them) and his followers.

I would like to express my profound gratitude and appreciation to my thesis committee chairman and adviser, Dr. Aiman Helmi El-Maleh, whose expertise, understanding, and patience, added considerably to my graduate experience. I appreciate his vast knowledge and skill in many areas e.g., digital system design, modeling, synthesis, testing, fault-tolerance. Dr. El-Maleh is the one professor who truly made a difference in my life. It was under his tutelage that I developed a focus and became interested in research. He provided me with direction, intellectual support and became more of a mentor than a professor. It was through his persistence, understanding and kindness that I completed my degree. I doubt that I will ever be able to convey my appreciation fully, but I owe him my eternal gratitude. I am grateful to Computer Engineering department Chairman Dr. Adnan Abdul-Aziz Gutub for providing me an opportunity to work on this thesis project with my adviser. Without his support and understanding at the very initial stages, this thesis work would have been impossible.

I would like to thank my co-adviser Dr. Muhammad El-Rabaa and the other member of my committee Dr. Abdelhafid Bouhraoua for the guidance they provided at all levels of the coursework projects and thesis research. Finally, I would like to thank Dr. Sadiq Mohammed Sait for his very useful suggestions and for taking out time from his very busy schedule to serve as committee member.

I would also like to thank my friends at Computer Engineering Department, particularly Ahmed Al-Masri, Abdul Rahman Elshafei and Syed Usama Idrees for our exchange of knowledge, ideas, skills, and venting of frustration during Master's studies, which helped enrich the experience. I also sincerely appreciate the help provided by my friends Ihab Hawari, Omair Khan, Ali Zaidi, Rahil, Zeeshan, Babar, Monim, Khizer, Zeehasham and Asif during my stay in the university.

I would also like to thank my family for the support they provided me throughout my life and in particular, I must acknowledge my beloved father and best friend, Mr. Abdul Aziz Khan, without whose love and encouragement, I would not have accomplished anything worthwhile in my career.

In addition, I acknowledge that this research would not have been possible without the support and assistance provided by the King Fahd University of Petroleum & Minerals.

# TABLE OF CONTENTS

|          | LIS            | T OF   | TABLES                                       | x    |

|----------|----------------|--------|----------------------------------------------|------|

|          | LIS            | TOF    | FIGURES                                      | xii  |

|          | AB             | STRA   | CT (ENGLISH)                                 | xvii |

|          | AB             | STRA   | CT (ARABIC)                                  | xix  |

| 1        | INT            | rodu   | UCTION AND MOTIVATION                        | 1    |

|          | 1.1            | Introd | luction                                      | 1    |

|          | 1.2            | Motiv  | ation                                        | 3    |

|          | 1.3            | Techn  | iques for Reliable Design of Nanoelectronics | 4    |

|          | 1.4            | Thesis | o Objectives                                 | 5    |

|          | 1.5            | Thesis | contributions                                | 5    |

|          | 1.6            | Thesis | Organization                                 | 7    |

| <b>2</b> | $\mathbf{LIT}$ | ERAT   | URE REVIEW                                   | 9    |

|          | 2.1            | Introd | luction                                      | 9    |

|          | 2.2            | Defini | tions                                        | 10   |

|          |                | 2.2.1  | Defects, Faults and Errors                   | 10   |

|          |                | 2.2.2  | Defect (or Fault) Models                     | 11   |

|          |                | 2.2.3  | Yield                                        | 14   |

|          |                | 2.2.4  | Reliability                                  | 14   |

|          |                | 2.2.5  | Fault Tolerance                              | 16   |

|   |     | 2.2.6  | Defect Tolerance                                             | 17 |

|---|-----|--------|--------------------------------------------------------------|----|

|   | 2.3 | Defect | -Tolerant Design Techniques                                  | 19 |

|   |     | 2.3.1  | Von Neumann's Multiplexing                                   | 19 |

|   |     | 2.3.2  | N-tuple Modular Redundancy (NMR) & Triple Modular Re-        |    |

|   |     |        | dundancy (TMR)                                               | 21 |

|   |     | 2.3.3  | Intervowen Redundant Logic & Quadded Logic                   | 24 |

|   |     | 2.3.4  | N-tuple Intervowen Redundancy (NIR) & Triple Intervowen      |    |

|   |     |        | Redundancy (TIR)                                             | 29 |

|   | 2.4 | Defect | Avoidance Design Techniques                                  | 33 |

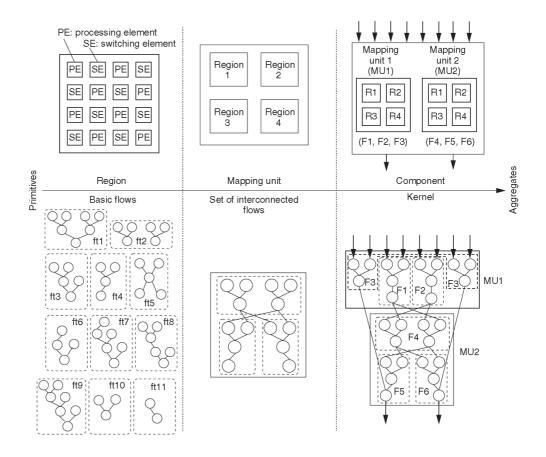

|   |     | 2.4.1  | Mishra & Goldstein's Technique                               | 33 |

|   |     | 2.4.2  | Chen He and M. F. Jacome's Technique                         | 35 |

|   | 2.5 | Transi | ent & Soft Error Mitigation Techniques                       | 37 |

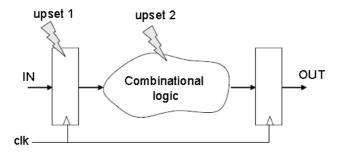

|   |     | 2.5.1  | Single Event Upsets and Single Event Transients              | 38 |

|   |     | 2.5.2  | Single Event Upset Mitigation Techniques                     | 43 |

|   |     | 2.5.3  | Single Event Upset Mitigation Techniques for FPGAs           | 50 |

|   |     | 2.5.4  | Empirical Model for Soft Error Rate Estimation               | 54 |

|   |     | 2.5.5  | Soft-Spot Analysis                                           | 54 |

|   | 2.6 | Defect | -Tolerant Crossbar Design Techniques                         | 60 |

|   |     | 2.6.1  | Crossbar Architecture                                        | 60 |

|   |     | 2.6.2  | Tahoori's Defect-Tolerant Design Techniques for 2D Crossbars | 65 |

|   |     | 2.6.3  | Hogg and Snider's Defect Tolerant Design Technique           | 69 |

|   |     | 2.6.4  | DeHon and Naemi's Defect Tolerant Design Technique           | 73 |

|   | 2.7 | Defect | -Tolerant FPGA Design Techniques                             | 76 |

|   |     | 2.7.1  | Field Programmable Gate Array Architecture                   | 76 |

|   |     | 2.7.2  | Categorization of Defect and Fault-Tolerant Techniques for   |    |

|   |     |        | FPGAs                                                        | 78 |

|   |     | 2.7.3  | Survey of Defect-Tolerant Techniques for FPGAs               | 82 |

| 3 | DE  | FECT-  | TOLERANT N <sup>2</sup> -TRANSISTOR STRUCTURES               | 84 |

|   | 3.1 | Introd | uction                                                       | 85 |

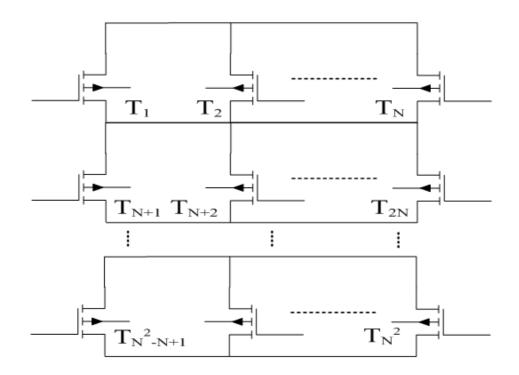

|   | 3.2           | $N^2$ -Tr | ansistor Structures                                               | 86     |

|---|---------------|-----------|-------------------------------------------------------------------|--------|

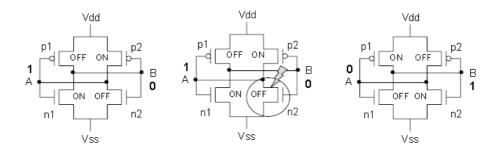

|   |               | 3.2.1     | Quadded-Transistor Structure                                      | 87     |

|   |               | 3.2.2     | Nona-Transistor Structure                                         | 93     |

|   | 3.3           | Exper     | imental Results                                                   | 100    |

|   |               | 3.3.1     | Stuck-Open and Stuck-Short Defect Analysis                        | 103    |

|   |               | 3.3.2     | Bridging Defect Analysis                                          | 108    |

|   |               | 3.3.3     | Hybridization of Quadded and Nona-Transistor structures           |        |

|   |               |           | with TIR and TMR                                                  | 110    |

|   | 3.4           | Summ      | ary                                                               | 112    |

| 4 | $\mathbf{TR}$ | ANSIE     | NT AND SOFT ERROR MITIGATION USING                                | r<br>J |

|   | $\mathbf{QU}$ | ADDE      | D-TRANSISTOR STRUCTURE                                            | 113    |

|   | 4.1           | Introd    | uction                                                            | 114    |

|   | 4.2           | Quado     | led Modular Redundancy Technique                                  | 115    |

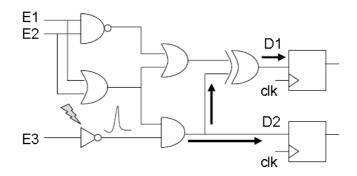

|   | 4.3           | Quado     | led-Transistor based SEU Mitigation Technique (QT16) $\therefore$ | 118    |

|   | 4.4           | Gate-s    | specific Quadded-Transistor based SEU Mitigation Technique        |        |

|   |               | (QT8)     |                                                                   | 118    |

|   | 4.5           | Exper     | imental Results                                                   | 122    |

|   |               | 4.5.1     | Quadded Modular Redundancy Technique Analysis                     | 122    |

|   |               | 4.5.2     | Quadded-Transistor based SEU Mitigation Technique Anal-           |        |

|   |               |           | ysis (QT16)                                                       | 147    |

|   |               | 4.5.3     | Gate-specific Quadded-Transistor based SEU Mitigation             |        |

|   |               |           | Technique Analysis (QT8)                                          | 148    |

|   |               | 4.5.4     | Reversed Gate-specific Quadded-Transistor based SEU Mit-          |        |

|   |               |           | igation Technique Analysis (QT8R)                                 | 149    |

|   |               | 4.5.5     | Circuit Reliability Comparison of QT(QMR1), QMR3,                 |        |

|   |               |           | TMR9, QT16 and QT8 Techniques                                     | 150    |

|   |               | 4.5.6     | Circuit Area Comparison of QT, QMR, TMR, QT16 and                 |        |

|   |               |           | QT8 Techniques                                                    | 152    |

|   | 4.6           | Summ      | ary                                                               | 153    |

| <b>5</b> | DE  | FECT-TOLERANT CROSSBAR DESIGN TECHNIQUE | 154 |

|----------|-----|-----------------------------------------|-----|

|          | 5.1 | Introduction                            | 154 |

|          | 5.2 | Multi-Crosspoint Architecture           | 157 |

|          |     | 5.2.1 Quadded MCP Architecture          | 157 |

|          |     | 5.2.2 Nona MCP Architecture             | 164 |

|          | 5.3 | Experimental Results                    | 165 |

|          |     | 5.3.1 Reliability Analysis              | 166 |

|          |     | 5.3.2 Area Analysis                     | 174 |

|          | 5.4 | Summary                                 | 177 |

| 6        | DE  | FECT-TOLERANT FPGA DESIGN TECHNIQUE     | 179 |

| 0        |     |                                         |     |

|          | 6.1 | Introduction                            | 179 |

|          | 6.2 | Defect-Tolerant CLBs for FPGAs          | 180 |

|          | 6.3 | Experimental Results                    | 182 |

|          |     | 6.3.1 Reliability Analysis              | 182 |

|          |     | 6.3.2 Area Analysis                     | 185 |

|          | 6.4 | Summary                                 | 187 |

| 7        | CO  | NCLUSION                                | 188 |

|          | 7.1 | Conclusion                              | 188 |

|          | 7.2 | Future Work                             | 191 |

|          | RE  | FERENCES                                | 192 |

|          | VIT | ΓΑΕ                                     | 206 |

# LIST OF TABLES

| 3.1 | Comparison of circuit failure probability between quadded-             |     |

|-----|------------------------------------------------------------------------|-----|

|     | transistor structure and quadded logic approaches for stuck-open       |     |

|     | and stuck-short defects                                                | 106 |

| 3.2 | Comparison of circuit reliability between quadded-transistor struc-    |     |

|     | ture and quadded logic approaches for stuck-open and stuck-short       |     |

|     | defects                                                                | 107 |

| 3.3 | Circuit failure probability for the nona-transistor structure ap-      |     |

|     | proach for stuck-open and stuck-short defects                          | 108 |

| 3.4 | Circuit reliability for the nona-transistor structure approach for     |     |

|     | stuck-open and stuck-short defects.                                    | 109 |

| 3.5 | Comparison of circuit failure probability between quadded-             |     |

|     | transistor structure and quadded logic approaches for bridging de-     |     |

|     | fects                                                                  | 110 |

| 4.1 | Comparison of circuit reliability between QMR and TMR tech-            |     |

|     | niques for a module size of 1 (i.e., full QT implementation). $\ldots$ | 143 |

| 4.2 | Comparison of circuit reliability between QMR and TMR tech-            |     |

|     | niques for a module size of 3                                          | 143 |

| 4.3 | Comparison of circuit reliability between QMR and TMR tech-            |     |

|     | niques for a module size of 5                                          | 145 |

| 4.4 | Comparison of circuit reliability between QMR and TMR tech-            |     |

|     | niques for a module size of 7                                          | 145 |

| 4.5 | Comparison of circuit reliability between QMR and TMR tech-        |       |

|-----|--------------------------------------------------------------------|-------|

|     | niques for a module size of 9                                      | 146   |

| 4.6 | Comparison of circuit reliability between quadded-transistor based |       |

|     | technique and TMR9 technique for SEU mitigation                    | 148   |

| 4.7 | Comparison of circuit reliability between gate-specific quadded-   |       |

|     | transistor based technique and TMR9 technique for SEU mitigation   | n.149 |

| 4.8 | Comparison of circuit reliability between reversed gate-specific   |       |

|     | quadded-transistor based technique and QT8 technique for SEU       |       |

|     | mitigation.                                                        | 150   |

| 4.9 | Circuit area comparison of QT, QMR, TMR, QT16 and QT8 tech-        |       |

|     | niques                                                             | 153   |

| 5.1 | Comparison of circuit reliability between quadded MCP and          |       |

|     | monomorphism-based reconfiguration approaches                      | 172   |

| 5.2 | Comparison of circuit reliability between nona MCP and             |       |

|     | monomorphism-based reconfiguration approaches                      | 173   |

| 5.3 | Crossbar area in terms of number of crosspoints for the            |       |

|     | monomorphism-based reconfiguration architecture                    | 175   |

| 5.4 | Crossbar area in terms of number of crosspoints for the quadded    |       |

|     | MCP architecture.                                                  | 176   |

| 5.5 | Crossbar area in terms of number of crosspoints for the nona MCP   |       |

|     | architecture                                                       | 177   |

| 6.1 | Comparison of circuit failure probability between QT CLB and 2     |       |

|     | spares based reconfiguration approaches                            | 186   |

| 6.2 | Comparison of circuit failure probability between QT CLB and 3     |       |

|     | spares based reconfiguration approaches                            | 186   |

| 6.3 | Comparison of area in terms of number of transistors and CLBs for  |       |

|     | QT based CLB approach and 2 and 3 spares based approach            | 187   |

|     |                                                                    |       |

# LIST OF FIGURES

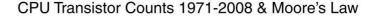

| 1.1  | Growth of transistor counts for Intel processors (dots) and Moore's  |    |

|------|----------------------------------------------------------------------|----|

|      | law (vertical log scale)                                             | 2  |

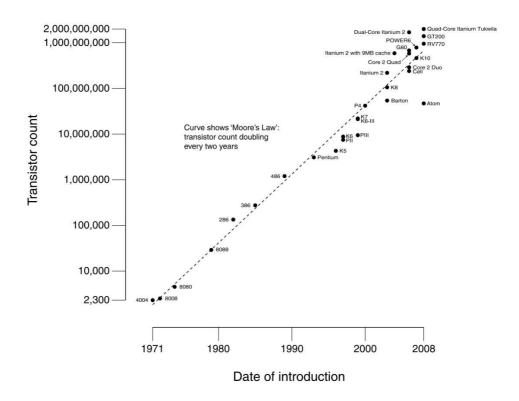

| 2.1  | Von Neumann NAND Multiplexing                                        | 20 |

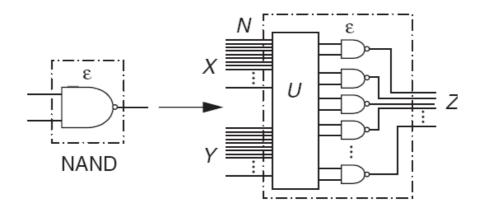

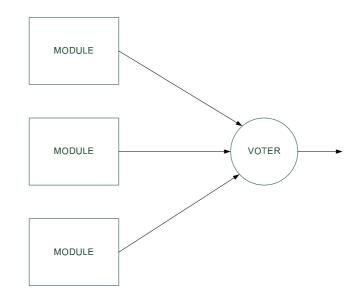

| 2.2  | A Triple Modular Redundant (TMR) structure                           | 23 |

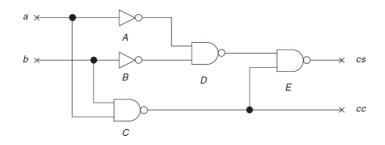

| 2.3  | Nonredundant complementary half adder implemented with NAND $$       |    |

|      | logic                                                                | 26 |

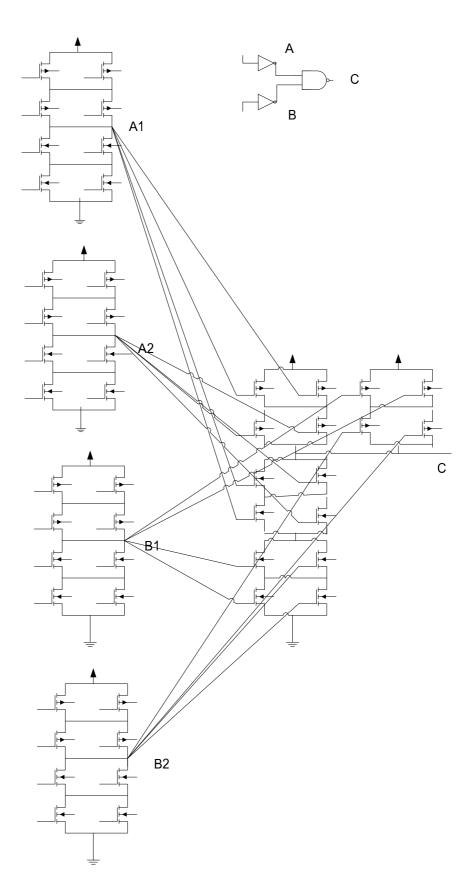

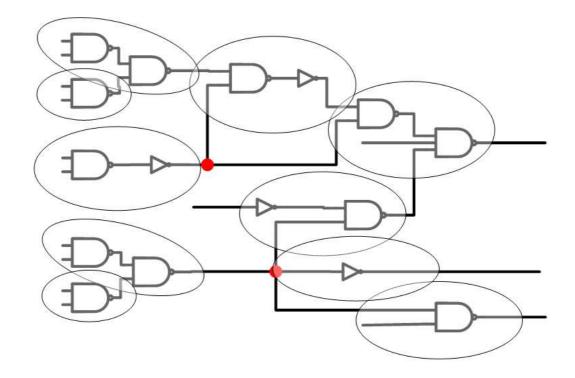

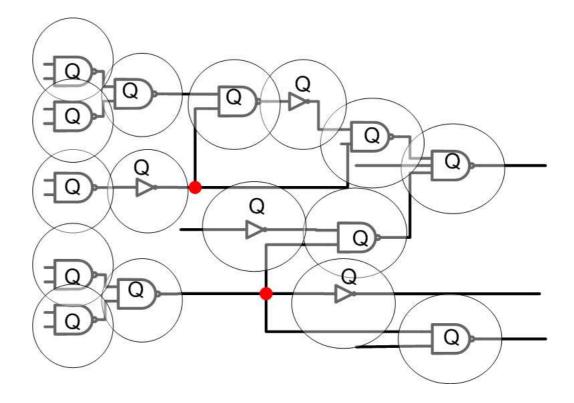

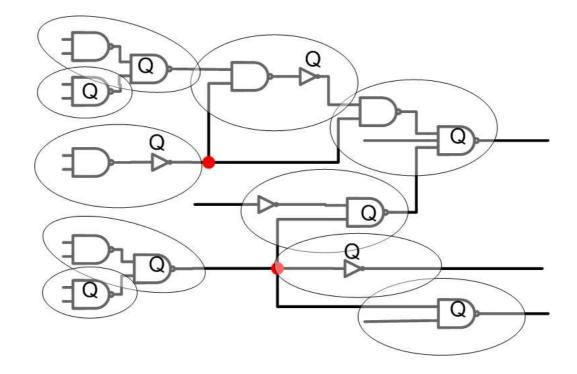

| 2.4  | Quadded implementation of the complementary half adder               | 27 |

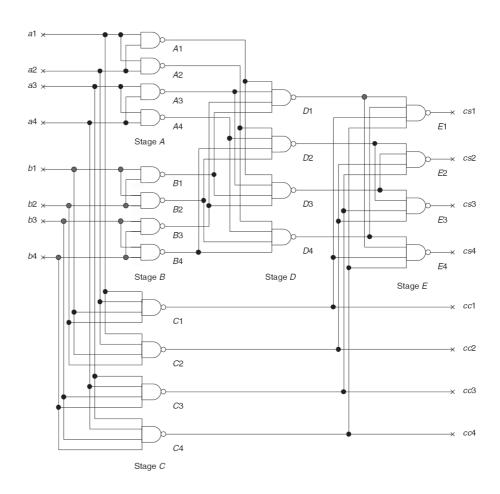

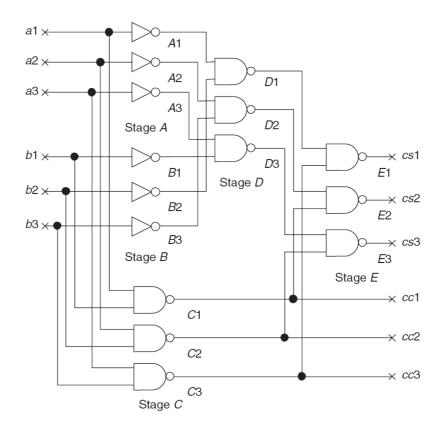

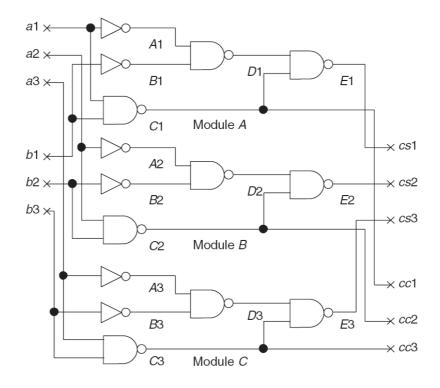

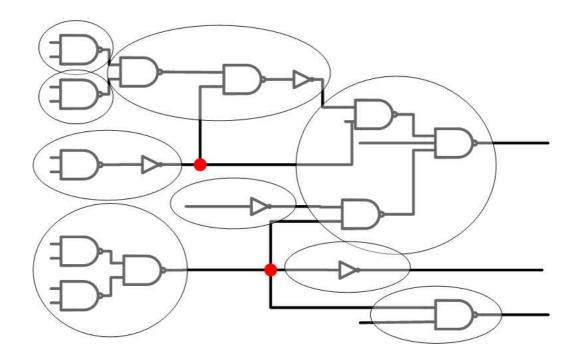

| 2.5  | TIR implementation of the complementary half adder. $\ . \ . \ .$ .  | 31 |

| 2.6  | TMR configuration of the TIR complementary half adder. $\ . \ . \ .$ | 32 |

| 2.7  | Three-level design hierarchy showing abstractions in the form of     |    |

|      | region, mapping unit and component on the upper level and be-        |    |

|      | havioral abstractions on the lower level                             | 36 |

| 2.8  | Upsets hitting combinational and sequential logic                    | 38 |

| 2.9  | Single Event Upset (SEU) effect in a SRAM Memory cell                | 39 |

| 2.10 | Single Event Transient (SET) Effect in Combinational Logic based     |    |

|      | on [53]                                                              | 40 |

| 2.11 | Single Event Upset (SEU) effect in a SRAM Memory cell                | 42 |

| 2.12 | Full Time Redundancy                                                 | 45 |

| 2.13 | TMR implemented in the entire device                                 | 46 |

| 2.14 | TMR memory cell with single voter                                    | 47 |

| 2.15 | TMR memory cell with three voters and refreshing                     | 47 |

| 2.16 | Full time redundancy scheme for combinational logic combined with          |     |

|------|----------------------------------------------------------------------------|-----|

|      | full hardware redundancy in the sequential logic                           | 49  |

| 2.17 | Full hardware redundancy scheme for combinational and sequential           |     |

|      | logic                                                                      | 49  |

| 2.18 | Duplication to mitigate SET in combinational logic                         | 50  |

| 2.19 | Time redundancy to mitigate SET in combinational logic. $\ . \ . \ .$      | 51  |

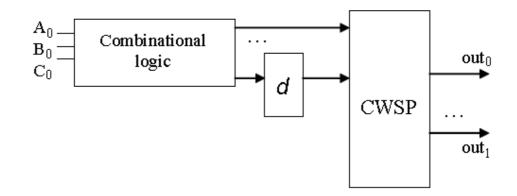

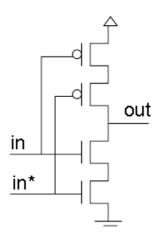

| 2.20 | Example of INVERTER logic with the code word state preserving              |     |

|      | (CWSP) in the duplication and time redundancy to mitigate SET              |     |

|      | in combinational logic.                                                    | 51  |

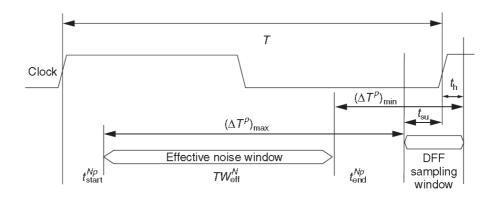

| 2.21 | The effective noise window.                                                | 56  |

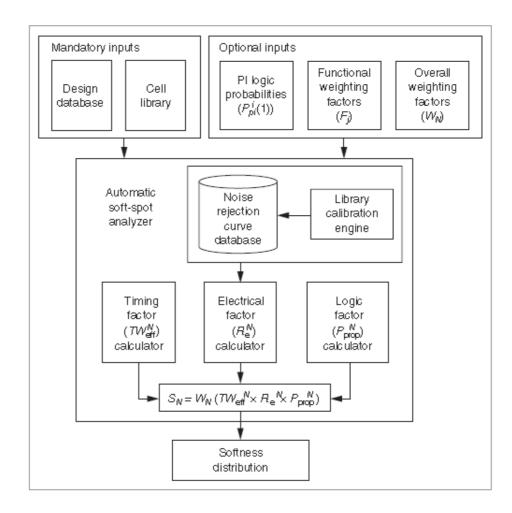

| 2.22 | Automatic soft-spot analysis.                                              | 59  |

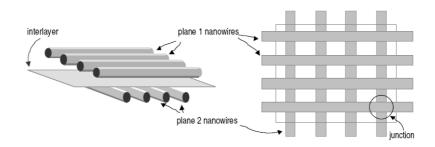

| 2.23 | Schematic view of a molecular crossbar from two different perspec-         |     |

|      | tives                                                                      | 61  |

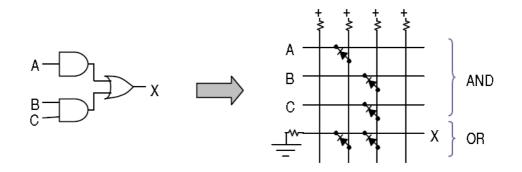

| 2.24 | Implementing the AND/OR function $X = A + BC$ with a diode                 |     |

|      | crossbar and resistor                                                      | 63  |

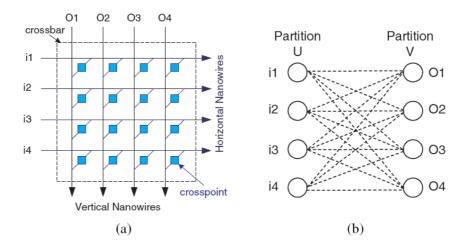

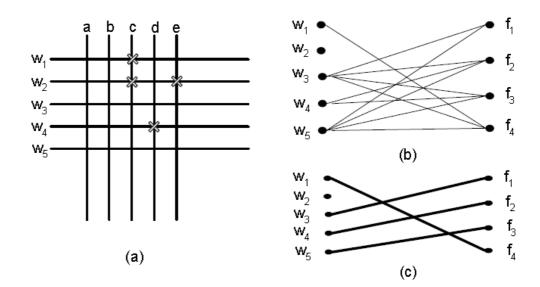

| 2.25 | (a) 4 x 4 2D nanoscale crossbar (b) Bipartite graph representation.        | 67  |

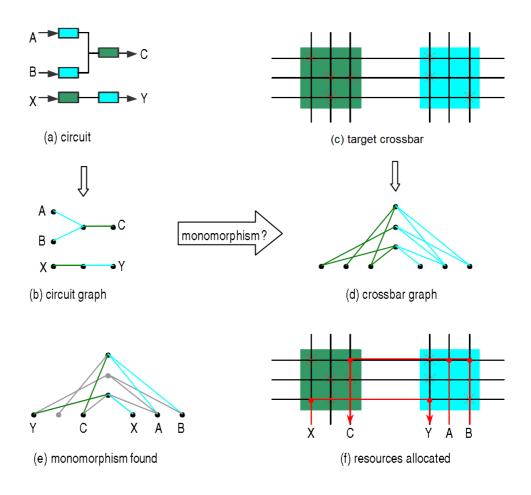

| 2.26 | Resource Allocation: Searching for a monomorphism between cir-             |     |

|      | cuit and a crossbar graph.                                                 | 70  |

| 2.27 | (a) A logic array of NanoPLA (b) Programmed logic array                    | 74  |

| 2.28 | (a) Crosses show defective junctions (b) Graph of the OR-term              |     |

|      | nanowi<br>ores and OR functions (c) One possible assignment.<br>$\ldots$ . | 75  |

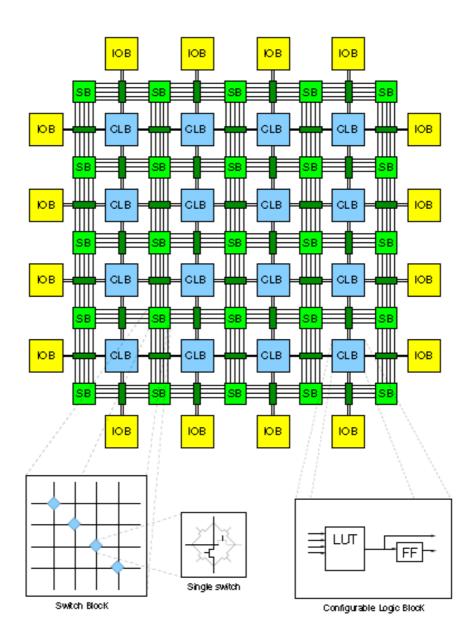

| 2.29 | Simplified example of an FPGA with 16 CLBs                                 | 79  |

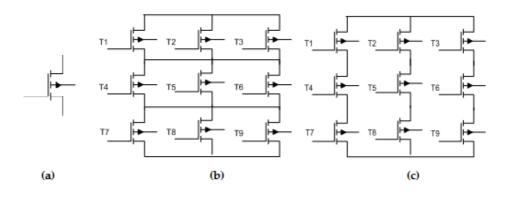

| 3.1  | (a) Transistor in original gate implementation, (b) First quadded-         |     |

| 0.1  | transistor structure, (c) Second quadded-transistor structure              | 88  |

| วา   |                                                                            |     |

| 3.2  | Defect-tolerant $N^2$ -transistor structure                                | 92  |

| 3.3  | (a) Transistor in original gate implementation, (b) First nona-            |     |

|      | transistor structure, (c) Second nona-transistor structure                 | 94  |

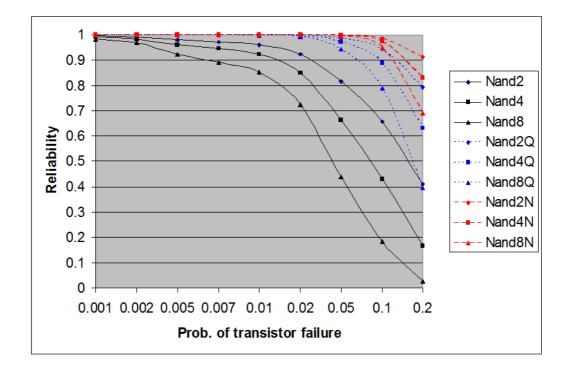

| 3.4  | Gate reliability comparison between quadded-transistor structure           |     |

|      | (Q), nona-transistor structure (N) and conventional CMOS                   | 101 |

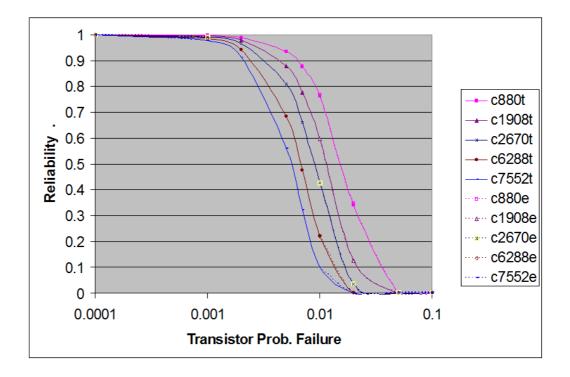

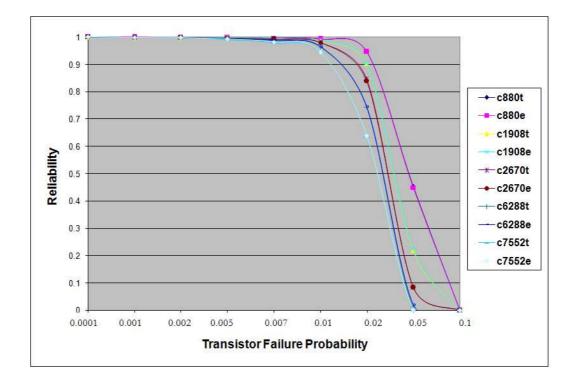

| 3.5  | Reliability obtained both theoretically (t) and experimentally (e)  |       |

|------|---------------------------------------------------------------------|-------|

|      | based on quadded-transistor structure and stuck-open and stuck-     |       |

|      | short defects.                                                      | 104   |

| 3.6  | Reliability obtained both theoretically (t) and experimentally (e)  |       |

|      | based on nona-transistor structure and stuck-open and stuck-short   |       |

|      | defects                                                             | 105   |

| 3.7  | Comparison of circuit failure probability for an 8-stage cascaded   |       |

|      | half-adder circuit for stuck-open and stuck short defects           | 111   |

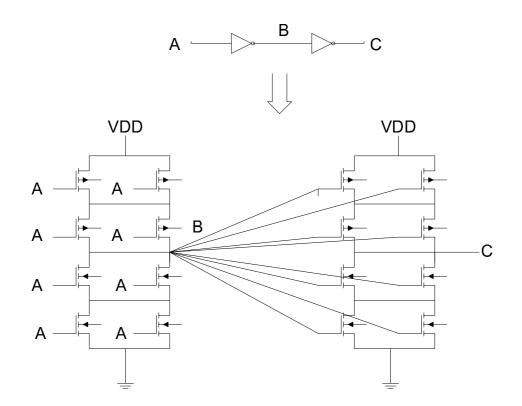

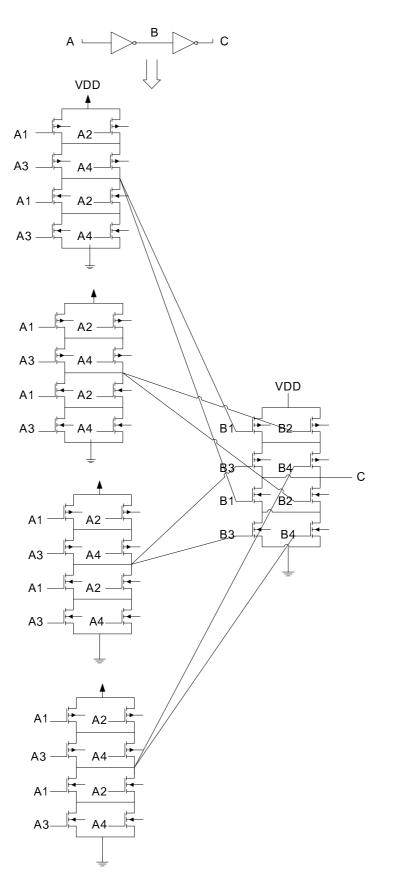

| 4.1  | Quadded-Transistor based technique for permanent defects            | 116   |

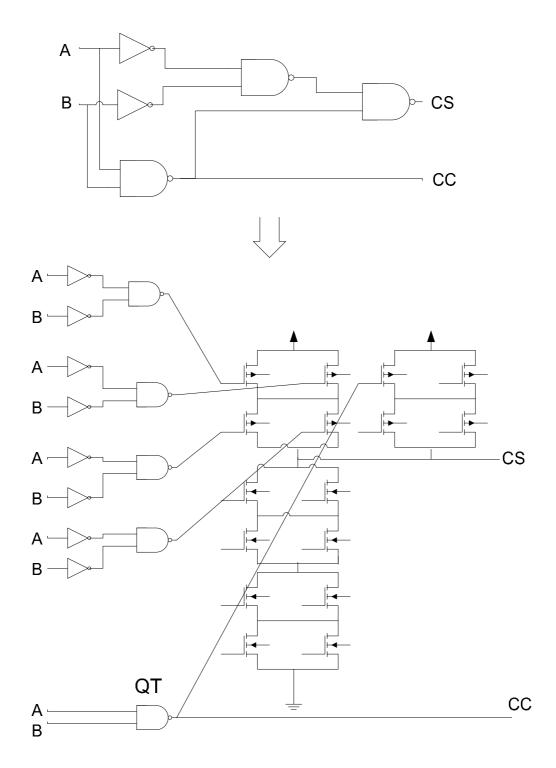

| 4.2  | Quadded Modular Redundancy technique for a simple 2-input circuit   | .117  |

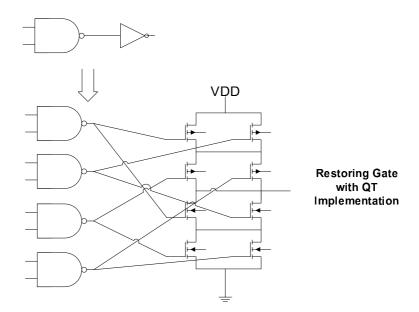

| 4.3  | Quadded-Transistor based technique for SEU Mitigation               | 119   |

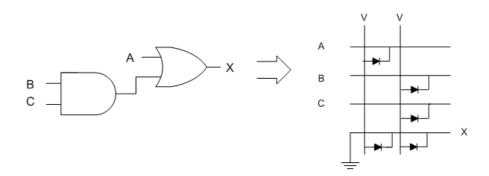

| 4.4  | Gate-specific connections for NAND gate to mask faulty transistors. | . 121 |

| 4.5  | Triple Modular Redundancy technique for single stage of 2-input     |       |

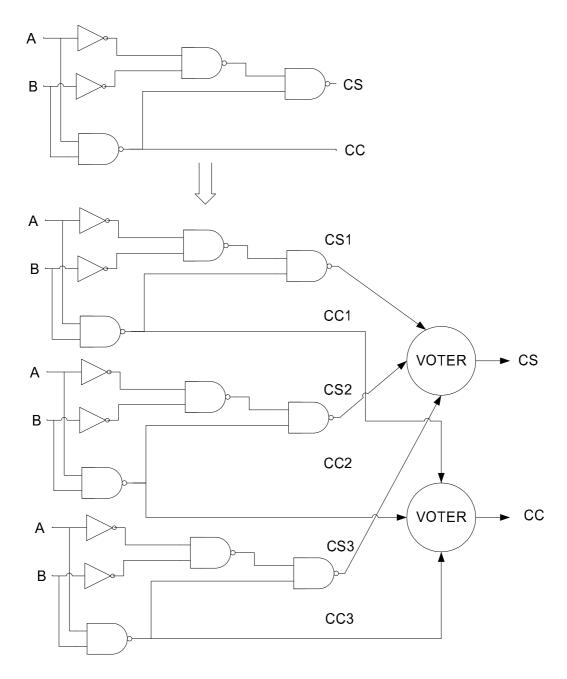

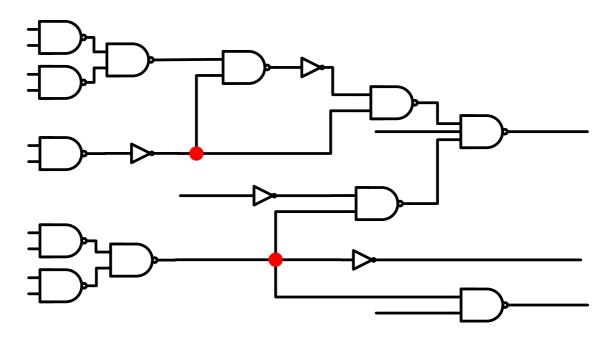

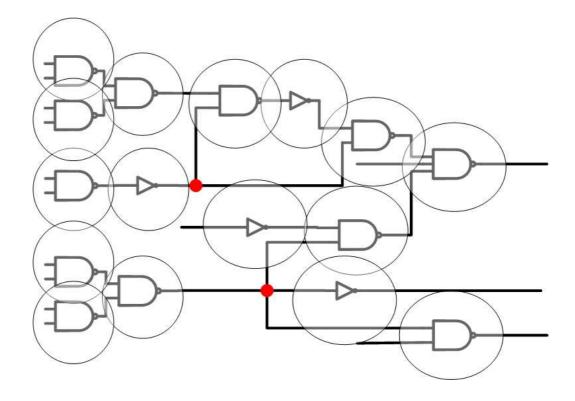

|      | complementary half adder                                            | 125   |

| 4.6  | Quadded Modular Redundancy technique for single stage of 2-input    |       |

|      | complementary half adder                                            | 126   |

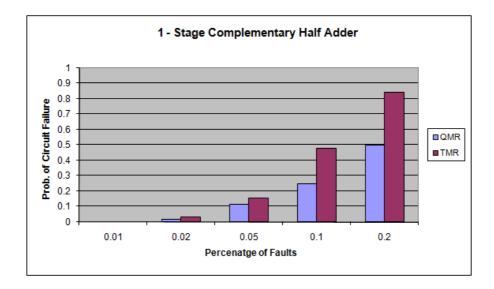

| 4.7  | Comparison of circuit failure probability for a 1-stage complemen-  |       |

|      | tary half-adder circuit for transient faults                        | 127   |

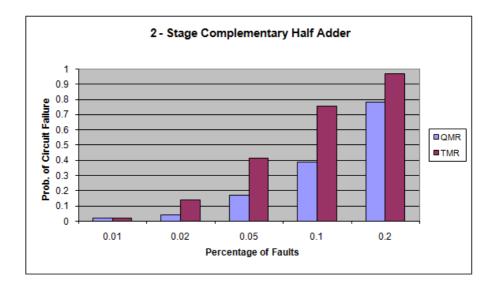

| 4.8  | Comparison of circuit failure probability for a 2-stage cascaded    |       |

|      | complementary half-adder circuit for transient faults               | 127   |

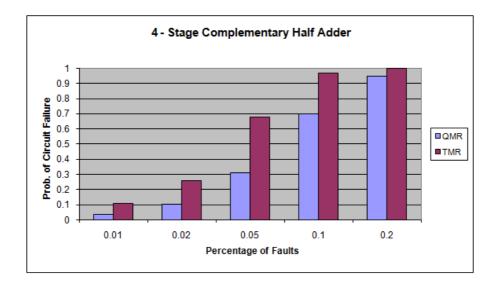

| 4.9  | Comparison of circuit failure probability for a 4-stage cascaded    |       |

|      | complementary half-adder circuit for transient faults               | 128   |

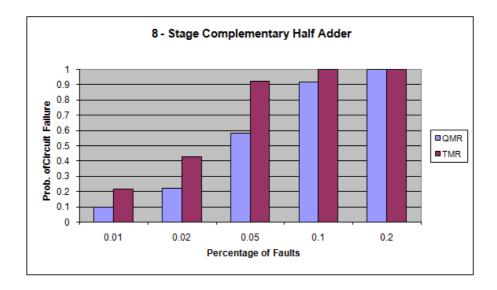

| 4.10 | Comparison of circuit failure probability for a 8-stage cascaded    |       |

|      | complementary half-adder circuit for transient faults               | 128   |

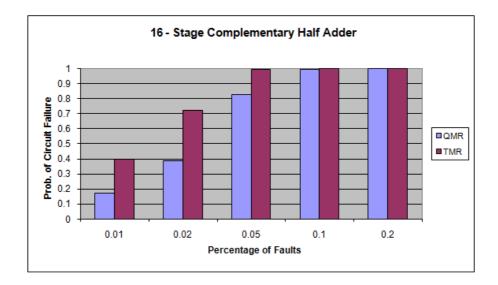

| 4.11 | Comparison of circuit failure probability for a 16-stage cascaded   |       |

|      | complementary half-adder circuit for transient faults               | 129   |

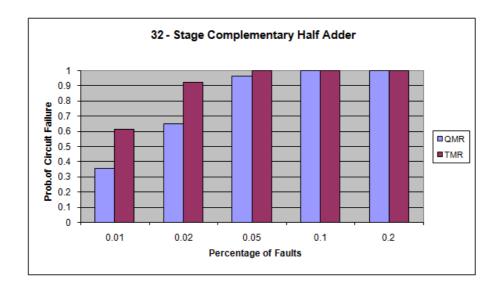

| 4.12 | Comparison of circuit failure probability for a 32-stage cascaded   |       |

|      | complementary half-adder circuit for transient faults               | 129   |

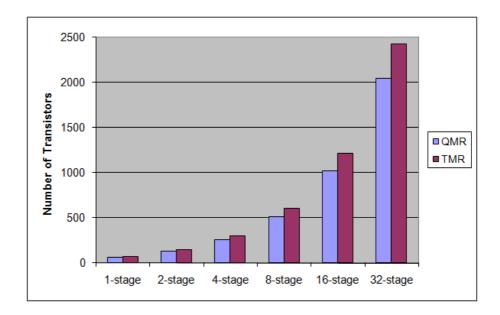

| 4.13 | Comparison of area in terms of number of transistors for 1, 2, 4, 8,                                                             |     |

|------|----------------------------------------------------------------------------------------------------------------------------------|-----|

|      | $16~{\rm and}~32\mbox{-stage}$ cascaded complementary half adders for QMR and                                                    |     |

|      | TMR implementation.                                                                                                              | 130 |

| 4.14 | Example Circuit.                                                                                                                 | 134 |

| 4.15 | Application of modular TMR algorithm on example circuit for a                                                                    |     |

|      | module size of 1                                                                                                                 | 135 |

| 4.16 | Application of modular TMR algorithm on example circuit for a                                                                    |     |

|      | module size of 2                                                                                                                 | 136 |

| 4.17 | Application of modular TMR algorithm on example circuit for a                                                                    |     |

|      | module size of 3                                                                                                                 | 137 |

| 4.18 | Application of modular TMR algorithm on example circuit for a                                                                    |     |

|      | module size of 1                                                                                                                 | 140 |

| 4.19 | Application of modular TMR algorithm on example circuit for a                                                                    |     |

|      | module size of 2                                                                                                                 | 141 |

| 4.20 | Application of modular TMR algorithm on example circuit for a                                                                    |     |

|      | module size of 3                                                                                                                 | 142 |

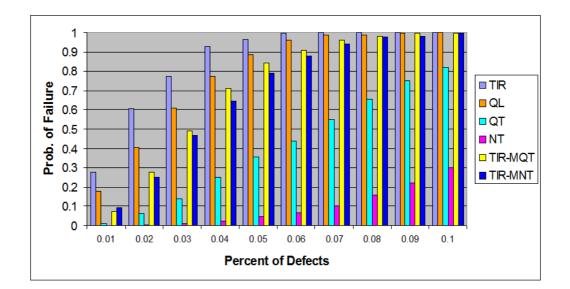

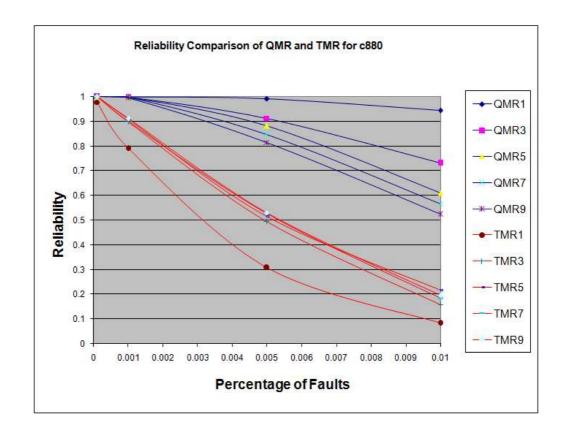

| 4.21 | Comparison of circuit reliability for QMR and TMR techniques                                                                     |     |

|      | module sizes of 1, 3, 5, 7 and 9. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                            | 144 |

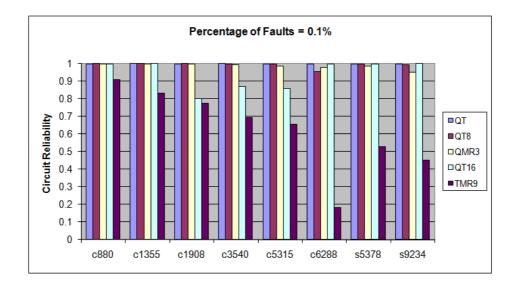

| 4.22 | Comparison of circuit reliability of all approaches for ISCAS bench-                                                             |     |

|      | marks for injecting 0.1% faults.                                                                                                 | 151 |

| 4.23 | Comparison of circuit reliability of all approaches for ISCAS bench-                                                             |     |

|      | marks for injecting $0.5\%$ faults                                                                                               | 152 |

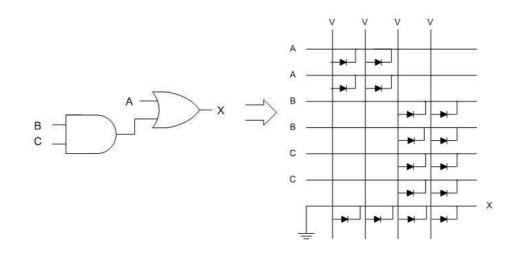

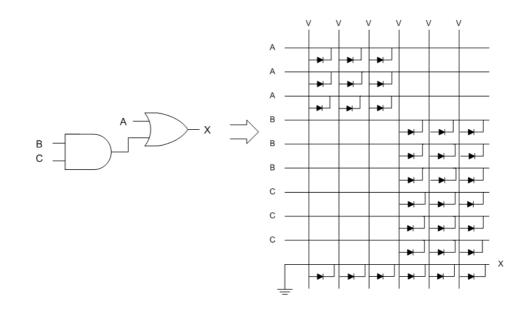

| 5.1  | Crossbar implementation for a simple function $X = A + BC$                                                                       | 158 |

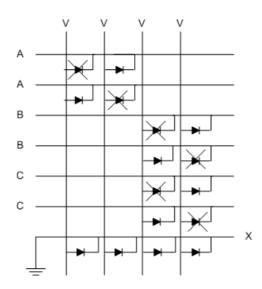

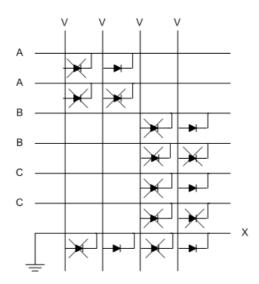

| 5.2  | Multi-crosspoint architecture using row and column redundancy for                                                                |     |

| 0.2  | a simple function $X = A + BC$ for $k = 2$                                                                                       | 159 |

| 5.3  | Allowable defect configuration in which the function will remain                                                                 | 100 |

| 0.0  | X = A + BC                                                                                                                       | 160 |

| 5.4  | A = A + DC                                                                                                                       | 100 |

| 0.4  | X = A + BC.                                                                                                                      | 160 |

|      | $21 = 21 + D0 \cdot \cdot$ | 100 |

| 5.5  | Allowable defect configuration in which the function will remain                                                                        |      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|------|

|      | X = A + BC.                                                                                                                             | 161  |

| 5.6  | Allowable defect configuration in which the function will remain                                                                        |      |

|      | X = A + BC.                                                                                                                             | 161  |

| 5.7  | Obstructive defect configuration in which the function will become                                                                      |      |

|      | $X = 1. \ldots $ | 162  |

| 5.8  | Obstructive defect configuration in which the function will become                                                                      |      |

|      | $X = BC.  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                              | 162  |

| 5.9  | Obstructive defect configuration in which the function will become                                                                      |      |

|      | $X = 1. \ldots $ | 163  |

| 5.10 | Obstructive defect configuration in which the function will become                                                                      |      |

|      | $X = 1. \dots $                   | 163  |

| 5.11 | Multi-crosspoint architecture using row and column redundancy for                                                                       |      |

|      | a simple function $X = A + BC$ for $k = 3$                                                                                              | 165  |

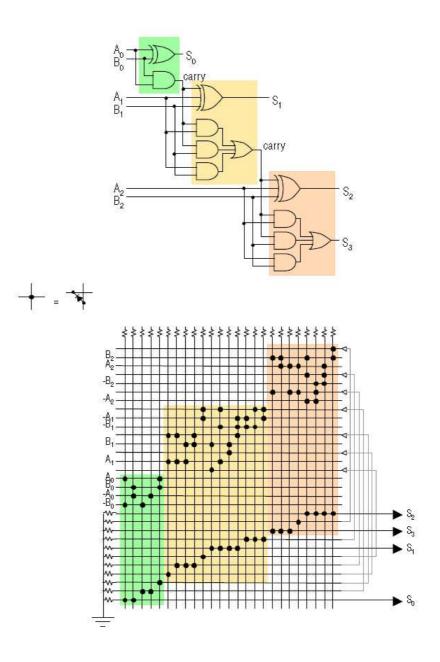

| 5.12 | A 3-bit adder which adds two 3-bit numbers (denoted as the bits                                                                         |      |

|      | $A_2A_1A_0$ and $B_2B_1B_0$ , respectively) to produce a 4-bit sum (with                                                                |      |

|      | bits $S_3 S_2 S_1 S_0$ )                                                                                                                | 169  |

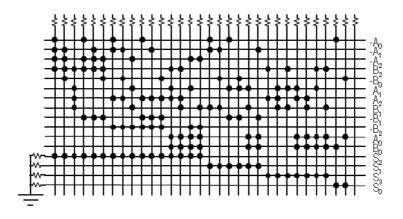

| 5.13 | A 3-bit adder implemented as 2-level logic in a single diode crossbar                                                                   | .170 |

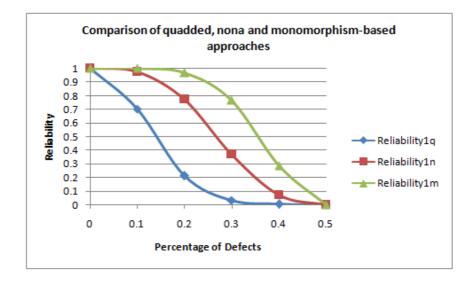

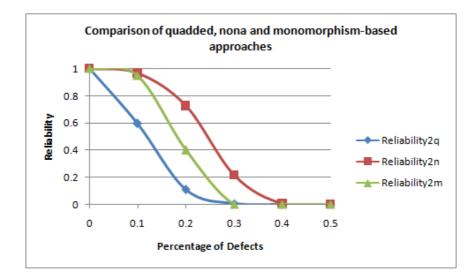

| 5.14 | Reliability comparison of quadded, nona and monomorphism-based                                                                          |      |

|      | approaches for 3-bit adder shown in Figure 5.12                                                                                         | 170  |

| 5.15 | Reliability comparison of quadded, nona and monomorphism-based                                                                          |      |

|      | approaches for 3-bit adder shown in Figure 5.13                                                                                         | 171  |

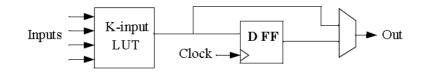

| 6.1  | A basic FPGA logic block.                                                                                                               | 181  |

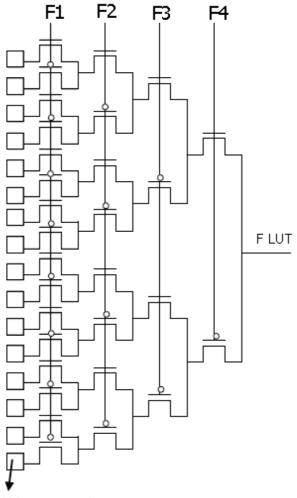

| 6.2  | Schematic of 4-input LUT                                                                                                                | 181  |

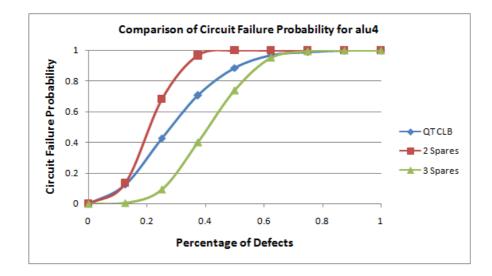

| 6.3  | Comparison of circuit failure probability for alu4 benchmark                                                                            | 185  |

# THESIS ABSTRACT

NAME:Farhan KhanTITLE OF STUDY:Transistor-Level Defect-Tolerant Techniques for Reliable<br/>Design at the NanoscaleMAJOR FIELD:Computer EngineeringDATE OF DEGREE:June 2009

Nanoelectronics based systems offer an attractive alternative for present day CMOS technology. It is estimated that nanoelectronics can achieve very high densities (billion devices per centimeter square) and operate at very high frequencies. With such high device densities, nanotechnology has the potential to take electronic circuits to the next higher level of integration. Nanoelectronic devices like carbon nanotubes (CNT), silicon nanowires (NWs) and quantum dot cells have already been demonstrated successfully by researchers. These devices are normally manufactured using bottom-up self-assembly fabrication process which results in higher defect densities in comparison to conventional lithography-based VLSI fabrication. Therefore, there is a renewed interest in using hardware redundancy to mask faulty behavior in order to increase reliability of nanoelectronic components. In this thesis, detailed investigation of a recently proposed transistor-level defect-tolerant technique for nanoelectronics is performed. The investigated technique replaces each transistor by a  $N^2$ -transistor structure (N = 2, 3, ..., k) and guarantees defect tolerance of all permanent defects of multiplicity  $\leq (N - 1)$  in each transistor structure. The theoretical and experimental analysis for the defect tolerance of stuck-open and stuck-short defects for quadded-transistor structure i.e.,(N = 2) is extended for the nona-transistor structure i.e.,(N = 3). Comparison of defect tolerance of transistor structures (N = 2, 3) against other techniques like Triple Intervowen Redundancy (TIR) and Quadded Logic (QL) is carried out experimentally. It is shown that the combinations of defect tolerance at both the transistor level and gate level have significantly improved circuit defect tolerance. For this, combination of Triple Modular Redundancy (TMR) with majority gate implemented with N<sup>2</sup>-transistor structure is investigated in this thesis.

Application of  $N^2$ -transistor structure for handling soft errors is also investigated and a novel approach based on quadded-transistor structure is proposed. Finally, techniques for the defect tolerance of logic implemented using crossbar switches and FPGAs are also investigated.

Keywords: Defect Tolerance, Quadded Logic, Quadded-Transitor structure, Triple Modular Redundancy, Triple Intervowen Redundancy, Quadded Modular Redundancy, Defect-tolerant Nanoscale Crossbars, Defect-tolerant FPGAs

#### ملخص الرسالة

الاسم: فرحان خان

**عنوان الدراسة:** تقنية احتمال العيوب على مستوى الترانزستور للتصميم الموثوق بمقياس النانو

التخصص: هندسة الحاسب الألي

#### سنة التخرج: يونيو 2009

توفر أنظمة إليكترونيات النانو بديلاً جذاباً لتقنية CMOS المستخدمة في هذه الأيام ، فمن المقدر أن إلكترونيات النانو يمكن أن تحقق درجات عالية من الكثافة (مليار ترانزستور لكل سنتيمتر مربع) وتعمل على ترددات عالية جداً. بهذه الكثافة العالية تملك تقنية النانو المقدرة لتطوير مستوى تكامل الدوائر الالكترونية إلى أعلى المستويات. الكترونيات النانو أجهزة مثل الكربون نانوتيوب (CNT) وأسلاك السليكون المتناهية الصغر (NWs) وخلايا نقطة الكم قد تم بالفعل توضيح البرهنة على عملهم بنجاح من قبل الباحثين. هذه الأجهزة عادة ما تكون مصنوعة من أسفل إلى أعلى باستخدام تقنية التصنيع بالتجميع الذاتي والتي تنتج أجهزة بنسب خلل وأعطال عالية في هذه الأجهزة مقارنة بطريقة الطباعة الحجرية التقليدية في تصنيع دارات التكامل الفائق (VLS). لذلك هناك اهتمام متجدد لاستخدام دوائر الكترونية احتياطية أو كنسخ إضافية لحب أخطاء تلك الدوائر في حال وجودها مما يزيد من فعالية وموثوقية مكونات الكترونيات النانو.

في هذه الأطروحة ، نقدم تحقيقاً مفصلاً لتقنية احتمال العيوب التصنيعية على مستوى الترانزستور والتي تم عرضها مؤخراً. هذه التقنية تقوم باستبدال كل ترانزستور بتشكيلة أو بنية مكونة من (ن<sup>2</sup>) من الترانزستورات بحسب مستوى السماحية للعيوب المطلوبة بحيث تكون (ن = 2 ، 3 ، 4 ، ...ك) ، هذه الترانزستورات الإضافية تضمن تغلب الدائرة الاكترونية على جميع العيوب الدائمة فيها بتعددية تكون فيها عدد تلك العيوب أقل أو تساوي (ن-1) المختارة في كل بنية واحدة من الترانزستورات. التحليل النظري والتجريبي لاحتمال العيوب عندما يكون هذا العيب عالقاً كدائرة فتح أو عالقاً كدائرة غلق لتشكيلات الترانزستورات الراباعية (ن = 2) قد تم تمديده للتشكيلات التساعية (ن = 3) في هذه الرسالة ، كذلك تمت مقارنة احتمالية العيوب التشكيلات الترانزستورات (ن = 2 ، 3) بتلك التقليدية مثل التكرار الثلاثي المتشابك (الموائر المنطقية الرباعية (QL). عن طريق إجراء التجارب ، يتبين أن التركيبات التي في مقدورها احتمال وجود عيوب على مستوى الترانزيستور أو مستوى البوابات المنطقية أدت إلى تحسين مستوى موثوقية الدوائر المنطقية ملحوظ وملفت ، لهذا فإنه تم بحث وتحقيق القيام بدمج تقنية الوحات التي في مقدورها احتمال وجود عيوب على الرباعية متوى الترانزيستور أو مستوى البوابات المنطقية أدت إلى تحسين مستوى موثوقية الدوائر المنطقية مستوى الترانزيستور أو مستوى البوابات المنطقية أدت إلى تحسين مستوى موثوقية الدوائر المنطقية ملحوظ وملفت ، لهذا فإنه تم بحث وتحقيق القيام بدمج تقنية الوحدات الثلاثية مع تنفيذ بوابة العالبية بين الإشارات

واحد من التطبيقات المستخدمة لتشكيلات (ن<sup>2</sup>) من الترانزستورات هو معالجة الأخطاء الخافتة تم البحث فيه و تم تقديم طريقة جديدة استناداً على تقنية الترانزستور الرباعية المقترحة في هذه الأطروحة ، أخيراً تقدم الأطروحة تحقيقاً على استخدام تقنيات احتمال العيوب للدوائر المنطقية في شبكة الخطوط المستعرضة و مصفوفة البوابات المنطقية القابلة للبرمجة (FPGA).

الكلمات الرئيسية : احتمال العيوب ، المنطق الرباعي ، بنية الترانزستورات الرباعية ، الوحدات الثلاثية المتكررة ، التكرار الثلاثي المتشابك ، الوحدات الرباعية المتكررة ، شبكة الخطوط المستعرضة المقاومة اللعيوب ، مصفوفة البوابات المنطقية القابلة للبرمجة المقاومة للعيوب.

# CHAPTER 1

# INTRODUCTION AND MOTIVATION

# 1.1 Introduction

In the past few decades, the rapid pace with which microelectronics has progressed is driven by the continual miniaturization of CMOS technology. This miniaturization of CMOS technology is manifested in the popular Moore's law which states that the number of electronic components per chip doubles every 18 months (formerly 2 years). The growth by Moore's law is shown in Figure 1.1. As the CMOS technology enters the nanometer scale, quantum mechanical effects come into play creating many technological challenges for further scaling of CMOS devices [34]. This has triggered research in two dimensions. One dimension of research is the invention and investigation of novel CMOS structures to achieve more scaling in current CMOS technology. The other dimension of work is the exploration of

Figure 1.1: Growth of transistor counts for Intel processors (dots) and Moore's law (vertical log scale).

alternative technologies for information processing [34]. Nanoelectronic devices and circuits based on nanotechnology-based fabrication are expected to offer the extra density and performance to take electronic circuits to the next higher level of integration stage. It is estimated that nanoelectronics can achieve very high densities (10<sup>12</sup> devices per cm<sup>2</sup>) and operate at very high frequencies (of the order of THz) [1]. Several research groups have proposed and successfully demonstrated novel nanoelectronic devices at the logic circuit level. These devices include resonant tunneling diodes (RTDs), single electron tunneling (SET) devices, quantum cellular automata (QCA), rapid single flux quantum (RSFQ), supercon, carbon nanotubes (CNTs), silicon nanowires (SiNWs), molecular nanoelectronics, quantum dot cells etc. [2, 3, 4, 5, 34]. These nanoelectronic devices share one or more characteristics such as extremely small dimensions, high switching speed, low power consumption, ease of fabrication and very good scaling potential [34]. It is expected in near future that one or more of these devices will be integrated on a CMOS platform, serving as complementary components to CMOS. Moreover, in the long run, one can expect nanoelectronic devices are normally manufactured using bottom-up self assembly fabrication processes as compared to normal CMOS fabrication which uses top-down lithography based fabrication. Due to fabrication regularity imposed by the self-assembly fabrication process, nanoelectronic devices are presently being manufactured as regular structures like two-dimensional (2-D) crossbars.

## 1.2 Motivation

Nanoscale devices whether manufactured using self-assembly or lithograpy-based processes have several characteristics which impose limitations on their use in nanoelectronic architectures. The most prominent characteristics are the devices' lower reliability and higher defect rates. This low reliability and higher defect rates of nanoelectronic devices arise from two sources [34].

- One source is the inherent imprecision and randomness in the bottom-up manufacturing process which results in a large number of defective devices during the fabrication process [34].

- The other source is the reduced noise tolerance of these devices which can be responsible for inducing device malfunctions by external influences like EMI, thermal perturbations, cosmic radiations etc [34].

Therefore, permanent defects may emerge during manufacturing process and transient errors can happen during the operation rendering nanoelectronic connections, wires and devices effectively unusable [4, 6, 7]. In order to address issues of unreliability in nanoelectronics and to ensure reliable system design and operation, defect tolerant design techniques need to be devised and applied for emerging nanoelectronic devices.

# 1.3 Techniques for Reliable Design of Nanoelectronics

The techniques for reliable design of nanoelectronics can be categorized as defecttolerant and defect avoidance techniques. Defect-tolerant design techniques are based on adding redundancy in the design to mask faulty behavior due to defects or faults. However, defect avoidance techniques are based on identifying defects and bypassing them based on reconfiguration. Both these techniques are discussed in detail in Chapter 2. For defect-tolerant techniques, hardware redundancy can be added at logic block level, gate level or transistor level. The work investigated in this thesis is based on adding redundancy at the transistor level. The proposed work will be discussed in detail in Chapters 3, 4, 5 and 6.

## 1.4 Thesis Objectives

The main goal of this work is to develop novel transistor-level defect-tolerant techniques that can be employed at nanoscale to afford enhanced reliability to the nanoelectronic circuits. In addition, defect-tolerant techniques have also been developed for specific nanoscale architecture like crossbars and FPGAs.

## **1.5** Thesis Contributions

The work presents the results of investigation related to the objectives mentioned in previous section. In particular, the main contributions can be summarized as follows:

• A recently proposed transistor-level defect-tolerant technique called Quadded-Transistor structure [31, 32] is studied in detail and is extended to develop another transistor-level defect-tolerant technique called Nona-Transistor technique. Both theoretical and experimental analysis is performed for tolerating transistor stuck-open and stuck-short defects. Reliability and failure rate analysis of Nona-Transistor technique and Quadded Logic technique for transistor stuck-open and stuck-short defects has proved that Nona-Transistor technique has outperformed Quadded Logic technique in terms of defect tolerance. Nona-Transistor technique has also shown better reliability than Quadded-Transistor technique at the cost of higher area.

- Hybridization of Nona-transistor technique with TMR is proposed in order to achieve higher reliability following the idea of hybridization of quaddedtransistor technique with TMR as proposed in [31, 32].

- A new transistor-level technique is proposed for mitigating transient and soft errors in digital circuits. The proposed technique is based on selective application of the Quadded-Transistor structure and is called Quadded Modular Redundancy(QMR). Simulation-based comparison of QMR with TMR for transient faults has shown that QMR affords more tolerance to transient faults in comparison to TMR. Two more variants of the same technique are also explored. Experimental analysis has shown that the proposed techniques are more efficient in terms of defect-tolerance than TMR but at the cost of higher area.

- A new defect-tolerant architecture for implementing logic circuits on partially defective nanoscale crossbars is proposed. The proposed crossbar architecture called Multi-crosspoint(MCP) architecture uses row and column redundancy in order to achieve higher defect tolerance in nanoscale crossbarbased circuits. A comparison of the proposed architecture is made with the monomorphism based reconfiguration algorithm for defect-tolerant crossbar design for a number of circuits and the experimental analysis has shown that

the MCP architecture performs better than monomorphism based approach on circuits with more dense product terms.

• Transistor-level defect-tolerant FPGA design technique is also explored for realizing reliable Configurable Logic Blocks (CLBs). Simulation based comparison of QT based CLBs is performed with 2-spares and 3-spares based reconfiguration technique which shows that the QT based CLB affords better defect tolerance than 2 spares based technique but is inferior to 3-spares based technique.

## **1.6** Thesis Organization

The rest of the thesis is organized as follows. In Chapter 2, a survey of defecttolerant design techniques available in literature is presented. The chapter covers various techniques concerning the objectives of this work that are reported in literature, discussing relevant algorithms and architectures wherever required. The chapter starts with surveying gate-level defect-tolerant design techniques. After that, relevant literature pertaining to SEU mitigation in digital circuits is presented. Then defect-tolerant crossbar design techniques are briefly surveyed. At the end of the chapter, defect-tolerant FPGA design techniques are briefly surveyed.

Chapter 3 discusses in detail the proposed transistor-level defect-tolerant design techniques for masking the effects of transistor stuck-open, stuck-short and bridging defects. The chapter covers in detail the theoretical and experimental analysis of Quadded-Transistor and Nona-Transistor techniques along with a discussion on the simulation framework used for experimental analysis.

In Chapter 4, detailed discussion is presented on the proposed transistor-level defect-tolerant technique for mitigating Single Event Upsets in digital circuits. This is followed by a detailed discussion of the proposed defect-tolerant design technique for crossbar-based designs in Chapter 5. Chapter 6 presents the proposed defect-tolerant techniques for design of defect-tolerant FPGAs. This thesis ends with conclusion and some future directions in Chapter 7.

## CHAPTER 2

# LITERATURE REVIEW

## 2.1 Introduction

In this chapter, a survey of various defect-tolerant design techniques is reported. The chapter begins with definitions of important terms in the field of defect tolerant digital design. This is followed by a discussion of gate-level defect-tolerant design techniques like NAND Multiplexing, N-Modular Redundancy (NMR), Quadded Logic, N-tuple Intervowen Redundancy (Section 2.3). This is followed by a brief description of defect avoidance design techniques (Section 2.4). Soft and transient error mitigation techniques are discussed in Section 2.5. Section 2.6 describes algorithms for defect-tolerant crossbar design techniques. Defect-tolerant FPGA design techniques are briefly described in Section 2.7.

# 2.2 Definitions

#### 2.2.1 Defects, Faults and Errors

Many terms are used to describe incorrectness in electronic systems. One may find that the terms defects, errors and faults are used in confusing ways. In the next few sub-sections, the definitions of these terms as defined in the book by Michael Bushnell [49] are presented.

#### Defect

A defect in the electronic system is the unintended difference between the implemented hardware and its intended design.

Some typical defects in VLSI chips are:

- Process Defects missing contact windows, parasitic transistors, oxide breakdown.

- Material Defects bulk defects (cracks, crystal imperfections), surface impurities.

- Age Defects dielectric breakdown, elctro-migration etc.

- Package Defects contact degradation, seal leaks.

Defects occur either during manufacture or during the use of devices. Repeated occurrence of the same defect indicates the need for improvement in the manufacturing process or the design of the device.

#### Fault

A representation of a "defect" at the abstracted function level is called a fault.

The difference between a defect and a fault is rather subtle. They are the imperfections in the hardware and function respectively.

#### Error

A wrong output signal produced by a defective system (or circuit) is called an error. An error is an "effect" whose cause is some "defect".

Fabrication defects, fabrication errors and physical failures are collectively termed as physical faults [50]. According to their stability in time, physical faults can be classified as:

- *Permanent faults*: They are those which are always present after their occurrence.

- Intermittent faults: They are those which exist only during some intervals.

- Transient faults: They are one-time occurrence (also known as Single Event Upsets (SEUs) or Single-Event Transients (SETs)) which are caused by a temporary change in some environment factor e.g., due to α-particle radiation etc.

### 2.2.2 Defect (or Fault) Models

While analyzing the defect tolerance of a circuit, the effect of defects in the circuit needs to be simulated. The effect of a production defect can be complex. Accu-

rate defect modeling based on layout and geometrical considerations is normally not an option when the effect of production defects is to be analyzed. For this reason, several defect(or fault) models have been proposed at different levels of abstraction. In the following, only those defect(or fault) models are defined which are relevant to our work. For other defect (or fault) models, the interested reader may refer to the book by Michael Bushnell [49].

- Stuck-at defect (or fault) model: It is based on assigning a fixed (0 or 1) value to a signal line in the circuit. A signal line is an input or an output of a logic gate or a flip-flop. The most popular forms are the single stuck-at faults i.e., stuck-at-1 and stuck-at-0.

- Stuck-open and Stuck-short defect (or fault) model: It is used for modeling transistor defects. In this model, a MOS transistor is modeled as an ideal switch and a defect is modeled as the switch being permanently either in the open (never conducting) or the shorted state(always conducting). In general, a MOS logic gate consists of more than one transistor. This defect model assumes just one transistor to be stuck-open or stuck-short. The stuck-open and stuck-short defect (or fault) model is also called transistor defect (or fault) model.

- Bridging defect (or fault) model: Usually modeled at the gate or transistor level, a bridging fault represents a short between a group of signals. The logic of the shorted net may be modeled as 1-dominant(OR bridge), 0dominant(AND bridge) or intermediate, depending upon the technology in

which the circuit is implemented. Non-feedback bridging faults are combinational and their coverage by stuck-at fault tests is normally very high. It is not always the case with the feedback bridging faults that produce memory states in the otherwise combinational logic. Bridging faults are often used as examples of "defect-oriented faults".

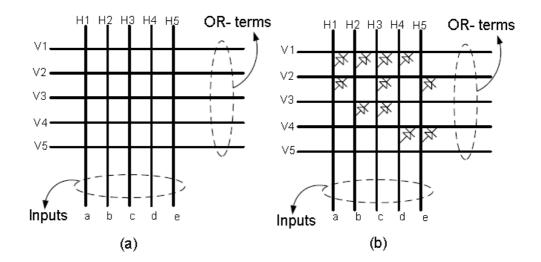

• Crosspoint defect(or fault) model: It is used for modeling crosspoint defects (or faults) in the programmable logic arrays (PLAs). In the layout of a PLA, input and output variable lines are laid out perpendicular to the product lines. Crossing signal lines either form specific types of connections or remain unconnected at crosspoints, depending on the function implemented. There are two types of crosspoint defects (or faults). A missing crosspoint defect means a missing connection at a crossing where a connection was intended. An extra crosspoint defect means a faulty connection at a crosspoint where no connection was intended. Based on their effect on AND and OR planes of the PLA, the crosspoint defects (or faults) are further classified as shrinkage, growth, appearance and disappearance defects (or faults). A missing crosspoint in the AND plane is called a growth defect (or fault). An extra crosspoint in the AND plane is called a shrinkage defect (or fault). A missing crosspoint in the OR plane is termed as disppearance defect (or fault). An extra crosspoint in the OR plane is termed as appearance defect (or fault).

#### 2.2.3 Yield

Yield can be defined as the ratio of the number of usable items after production to the number of potentially usable items [62]. The main contributor to low yield for ICs is defects during production and fabrication. Yield is an important measure because only usable items are sellable. Low yield can make production prohibitively expensive.

For chip production, the total yield is the product of wafer process yield, device yield and module test yield. Wafer process yield is the ratio of usable wafers. Device yield is the ratio of usable dies after photolithography and module test yield is the ratio of usable chips after packaging. Device yield is the most important component, and the only one that is dependent on the specific circuit [71].

Redundancy techniques, such as the ones explained in Section 2.3 to 2.7, can improve device yield by tolerating a certain amount of defects.

#### 2.2.4 Reliability

The reliability of a system can be defined as the ability to perform the specified function under stated conditions [63].

For hardware systems, the most common way of evaluating reliability is to apply a probabilistic reliability function R(t) that gives the probability that a system is working correctly between time 0 and time t, given certain conditions and correct behavior at time 0. If the failure rate of the system is constant over time, the reliability function is  $R(t) = e^{-\lambda t}$  where  $\lambda$  is the constant failure rate for one unit of time. When  $\lambda t$  is small,  $R(t) \approx 1 - \lambda t$ .

In a system composed from several subcomponents, all of which must be working, the reliability of the system is given as  $R = \prod_{c=1}^{n} R_c$  where  $R_c$  is the reliability of subcomponent c and n is the number of subcomponents. A defect-tolerant system can continue to operate despite a certain number of defects. For such systems, where not all subcomponents need to be working, more elaborate reliability calculations need to be performed or, more realistically for complex systems, Monte Carlo simulations need to be employed.

An alternative evaluation criterion is Mean Time To Failure (MTTF) which is the average time a system will run before failing. MTTF is linked to the failure rate in the following way:  $MTTF = (1/\lambda)$ . If  $\lambda$  is the failure rate per hour, MTTF is the average number of hours before failing.

When considering how reliable a system is in the presence of production defects, time is not relevant. MTTF is therefore not applicable and reliability is simply  $R = (1 - \lambda)$  where  $\lambda$  is the probability of failing under stated conditions. It should be noted that reliability in this case is similar, but not the same as yield. Yield is the percentage of chips that can be sold. Reliability is a probability of working given certain conditions. These conditions need not be directly linked to what actually causes unsellable chips. However, if the stated conditions are realistic and relevant for what constitutes a sellable chip, high reliability will lead to high yield [71].

#### 2.2.5 Fault Tolerance

The term fault-tolerance first appeared in technical literature in 1967, defined as:

A system is fault-tolerant if its programs can be properly executed despite the occurrence of logic faults [64].

The prime motivation at that time was challenges in interplanetary exploration. Today, the importance of fault-tolerance is increasing, and, as mentioned in Chapter 1, fault-tolerance is a long term grand challenge of the semiconductor industry [65].

The objective of fault-tolerance is either to mask, or to recover from, faults once they have been detected [66]. It is in contrast to the second method of achieving system reliability, fault prevention, which seeks to eliminate all faults before the system is put to use. Complete fault prevention is impossible to achieve in practice and high degrees of prevention is costly [72].

Fault-tolerance is therefore commonly used in increasing system reliability, often in combination with partial fault prevention. Much research on reliable systems is concerned with the detection of faults using error detecting and correcting codes or fault-detecting and self-repairing circuits. The tolerance itself is achieved using redundancy techniques. Such techniques can be classified as hardware, time, information or software redundancy [66]. With hardware redundancy there are spare elements available to replace faulty ones. Time redundancy implies that elements still operating may perform the functions that were originally intended to be performed by now faulty elements [67]. With information redundancy, redundant information is added to an existing data set, for instance by using codes that enable detection and correction of errors. Software redundancy uses techniques such as N-version programming [68], where N independently constructed programs run in parallel.

The research work reported in this thesis is concerned with only hardware redundancy to afford defect tolerance in digital circuits particularly at the nanoscale. Hardware redundancy can be implemented as either static or dynamic redundancy. As defined in the next section, out of these two types, our approach is the application of static hardware redundancy at the transistor level.

#### 2.2.6 Defect Tolerance

A defect-tolerant circuit is a circuit that functions correctly even if there are defective subcomponents, for example defective transistors and/or wires. Defect tolerance can be seen as a special case of fault tolerance where only permanent defects are considered. Transient faults that do not result in permanent damage are not an issue [71].

A defect-tolerant circuit is a circuit that is designed to tolerate a certain amount of defective components. The term defect coverage refers to the percentage of all possible defects a defect tolerant system can tolerate. 100% defect coverage means that any possible single defect anywhere in the system is tolerated. Often, defect coverage is less than 100%, either because not all defect types are tolerated or because some parts of the system are not defect- tolerant [71]. In the beginning of the history of digital electronic circuits, logic was built from unreliable vacuum tubes. As a result, there was a significant amount of research on how to build reliable computers from unreliable components and many of the most well known defect tolerance techniques date from the early period of computing. After the introduction of the IC, failure rates dropped drastically and reduced the importance of defect and fault tolerance techniques, except for a few extreme cases such as for space exploration. Recent predictions on failure rates in future production processes have renewed interest in defect tolerance [71].

Defect tolerance is achieved through the use of redundancy techniques. Redundancy techniques relevant for tolerating hardware defects can be classified as static hardware redundancy and dynamic hardware redundancy [71].

- Static hardware redundancy involves having redundant hardware components connected in such way that defects are tolerated without any need to first detect the defects. They are briefly covered in section on Defect-Tolerant Design Techniques.

- Dynamic hardware redundancy involves first detecting a defect and then applying measures, for example reconfiguration, for avoiding the detected defect. They are briefly covered in section on Defect Avoidance Design Techniques.

### 2.3 Defect-Tolerant Design Techniques

Defect-tolerant digital system design techniques are based on the concept of adding redundancy in order to mask faulty behavior in the nanoelectronic components due to defects, faults or errors. Examples of defect-tolerant design techniques are Von Neumann Multiplexing, N-tuple Modular Redundancy (and its derivative Triple Modular Redundancy), Quadded Logic, N-tuple Intervowen Redundancy (and its derivative Triplicated Intervowen Redundancy).

#### 2.3.1 Von Neumann's Multiplexing

In the 1950s, John von Neumann initiated the study of techniques for the design of reliable systems using redundant unreliable components [9]. In his multiplexing structure, von Neumann considered two types of basic logic, namely majorityvoting and NAND logic. He duplicated each logic gate N times and replaced each input with a bundle of N lines, thus, each output bundle also had N lines. For NAND logic, the inputs from the first bundle randomly pair with those from the second bundle to form the input pairs of the duplicated NANDs (as illustrated in Figure 2.1). Instead of requiring all or none of the output bundle's lines to produce correct answers, von Neumann set a certain critical (or threshold) level  $\Delta$  such that  $0 < \Delta < 1/2$ . If the number of lines carrying the correct signal was larger than  $(1 - \Delta)N$ , he interpreted it as a positive state of the bundle, if it was less than  $\Delta N$ , he considered it a negative state. By using a massive duplication of unreliable components, von Neumann concluded that the construction can be

Figure 2.1: Von Neumann NAND Multiplexing.

reliable with a high probability if the failure probability of the gates (denoted by  $\varepsilon$ ) is sufficiently low for example, lower than approximately  $10^{-2}$  [9]. In general, von Neumann's construction requires a large amount of redundancy ( $N > 10^3$ ) and a low error rate for individual gates. These features motivated extensive research efforts in later decades to find the complexity of redundancy required to cope with errors. It is shown in [20] that for deep logic with a gate failure probability  $\varepsilon = 0.01$  and N = 100, it is possible to achieve circuit failure probability in the order of  $10^{-6}$ . This required amount of redundancy is excessive and is considered impractical. In order to reduce this large amount of redundancy, the works in [21, 22] combine NAND multiplexing with reconfiguration.

Because CMOS devices became dominant in industry and showed an amazing performance in terms of reliability and scalability, chip designers never used von Neumann's multiplexing technique in practice. However, researchers have implemented many redundancy techniques derived from von Neumann's proposal, such as triple modular redundancy (TMR) and error-correcting codes (ECC), in high-reliability applications and in memory circuits [11].

# 2.3.2 N-tuple Modular Redundancy (NMR) & Triple Modular Redundancy (TMR)

N-tuple modular redundancy (NMR) design of which TMR is the most-used particular case have been used as benchmarks for evaluating fault-tolerant approaches and have been implemented in VLSI for high-reliability applications. NMR techniques, generally implemented at the modular rather than gate level, use redundant components to mask fault effects.

An NMR system (also known as M-of-N system) is a system that consists of Nmodules and needs at least M of them for proper operation. Thus, the system fails when fewer than M modules are functional. The reliability of an NMR system as computed in [35] is presented next. The assumption is that the failures of the different modules are statistically independent and that there is no repair of failing modules. If R(t) is the reliability of an individual module (the probability that the module is still operational at time t), the reliability of an NMR system is the probability that M or more modules are functional at time t. The system reliability is therefore given by:

$$R_{NMR}(t) = \sum_{i=M}^{N} \begin{pmatrix} N \\ i \end{pmatrix} R^{i}(t) [1 - R(t)]^{N-i}$$

(2.1)

The assumption that failures are independent is the key assumption to the high reliability of NMR systems. Even a slight extent of positively correlated failures can greatly diminish their reliability. For example, suppose  $q_{cor}$  is the probability that the entire system suffers a common failure. The reliability of the system now becomes:

$$R_{NMR}(t) = (1 - q_{cor}) \sum_{i=M}^{N} \begin{pmatrix} N \\ i \end{pmatrix} R^{i}(t) [1 - R(t)]^{N-i}$$

(2.2)

If the system is not designed carefully, the correlated failure factor can dominate the overall failure probability.

The best-known example of NMR type of systems is the triplex, which consists of three identical modules whose outputs are voted on. This is a 2-of-3 system so long as a majority of the modules produce correct results, the system will be functional. In TMR, all the three identical modules perform the same operation, and a voter accepts outputs from all three modules, producing a majority vote at its output as shown in Figure 2.2. In such a structure, M = 2 and N = 3 and a voter selects the majority vote. If a single voter is used, that voter becomes a

Figure 2.2: A Triple Modular Redundant (TMR) structure.

critical point of failure and the reliability of the TMR structure is:

$$R_{NMR}(t) = R_{voter}(t) \sum_{i=2}^{3} \begin{pmatrix} 3\\ i \end{pmatrix} R^{i}(t) [1 - R(t)]^{3-i}$$

$$R_{NMR}(t) = R_{voter}(t)[3R^2(t) - 2R^3(t)]$$

(2.3)

where  $R_{voter}(t)$  is the reliability of the voter. As shown in the above equation, the reliability of TMR design is limited by that of the final arbitration unit (i.e., voter), making the approach difficult in the context of highly integrated nanosystems [8]. In TMR, however, the reliability of a module imposes a demanding requirement on a module's size i.e., the modules involved in TMR should be modest in size in relation to the error rate of an individual component in the circuit, in other words, a module with many components will present a serious limit on the upper bound of the device error rate that TMR can tolerate [11].

A TMR circuit can be further triplicated. The obtained circuit thus has nine copies of the original module and requires two layers of majority gates to collect information at outputs. This process can be repeated if necessary, resulting in a technique called cascaded triple modular redundancy (CTMR). Spagocci and Fountain [12] have shown that using CTMR in a nanochip with many (for example, 10<sup>11</sup> or 10<sup>12</sup>) nanoscale devices would require an extremely low device error rate. However, the method might be effective in modest or small circuit modules. Another disadvantage of the CTMR scheme is that it introduces an exponential growth in redundancy as the cascaded layers increase. In [13], it is shown that recursive voting leads to a double exponential decrease in a circuit's failure probability. However, a single error in the last majority gate can cause an incorrect result, hampering the technique's effectiveness.

#### 2.3.3 Intervowen Redundant Logic & Quadded Logic

Pierce [10] generalized von Neumann's and his contemporaries' ideas on faulttolerant logic to a theory termed interwoven redundant logic. This theory interprets the faults it considers as  $0 \rightarrow 1$  and  $1 \rightarrow 0$  faults. The error correction mechanism in interwoven redundant logic depends on asymmetries in the effects of these two types of binary errors. The effect of a fault depends on the value of the erroneous input and the type of gate. Consider a NAND gate, for instance. If the binary value of one of its inputs is 0 while it should be 1, possibly because of a faulty gate or interconnection, the NAND's output value will remain a 1 regardless of the values of other inputs. If an input value is 1 while it should be 0, the output will not be stuck but will depend on other inputs. Thus, there are two types of faults for a NAND gate. One is critical in the sense that its occurrence on one of the inputs leads to a stuck output, the other is subcritical in the sense that its occurrence alone does not cause an output error. Hence, alternating layers of NAND (or NOR) gates can correct errors by switching them from critical to subcritical.

Quadded logic [11, 14, 15] is an ad hoc configuration of the interwoven redundant logic. It requires four times as many circuits, interconnected in a systematic way, and it corrects errors and performs the desired computation at the same time. Researchers have studied quadded logic for use with AND, OR, and NOT logic, and for use with NOR logic. Consider the schematic of a complementary half adder (computing the complements of carry and sum, denoted as cc and cs) shown in Figure 2.3 and its quadded form in Figure 2.4, both implemented with NAND gates (including inverters, considering them a special form of NAND gate).

#### Interconnection in Quadded Logic

The quadded implementation in Figure 2.4 replaces each NAND gate from Figure 2.3 with a group of four NAND gates, each of which has twice as many inputs as the one it replaces. The four outputs of each group are divided into two sets of two outputs, each providing inputs to two gates in a succeeding stage. The

Figure 2.3: Nonredundant complementary half adder implemented with NAND logic.

interconnections in a quadded circuit are hence eight times as many as those used in the nonredundant form. The interconnect patterns in a quadded network are important to the network's capability of error correction, yet the rules are simple. The outputs of four gates, numbered 1 to 4 in Figure 2.4, are divided into two sets. Each set forms a pair of inputs and each pair feeds the two gates with the same numbers as the set in succeeding stages. If the four outputs are divided into two sets of (1,3) and (2,4), for instance, set (1,3) will provide inputs to gates 1 and 3 in the next stage and set (2,4) will provide inputs to gates 2 and 4. There are three possible ways to break four inputs into two sets to form an interconnect pattern: (1,2) and (3,4); (1,3) and (2,4); and (1,4) and (2,3). The rule to arrange these patterns is that the interconnect pattern at the outputs of a stage must differ from the interconnect patterns of any of its input variables.

#### Error Correction in Quadded Logic

In the pattern of interconnection in quadded logic, any single error introduced in the network is correctable by the network itself, provided that the network is

Figure 2.4: Quadded implementation of the complementary half adder.

large enough. In Figure 2.4, assume that output B1 in stage B is wrongly in the 0 state when it should be in the 1 state (a critical  $1 \rightarrow 0$  error for the NAND gate). Because of this error, outputs D1 and D3 of stage D must be 1, this can be erroneous, but it would be a subcritical  $0 \rightarrow 1$  error. Since outputs D2 and D4 of stage D are not in error (thus in the correct 0 state), the subcritical errors at outputs D1 and D3 are masked at stage E, producing the expected (correct) 1 state at all the outputs of stage E. It is observed that a subcritical  $0 \rightarrow 1$  error is even more promptly corrected in the NAND network. In general, a single critical error in a quadded circuit will be eliminated after passing through two stages, and a single subcritical error will be corrected in the next stage after its occurrence. The error correction property of a quadded NAND network is in fact a result of its logical characteristics. Consider the outputs of stage B in Figure 2.4: B1, B2, B3, and B4. After passing through two NAND stages, the outputs of stage B can be represented at stage E by the following Boolean function: B1B3 + B2B4. All Bs in this function should be the same in the absence of errors, but any single error in the Bs will not affect the function's correct value. In a quadded circuit, a single error is correctable in at most two logic layers. Errors occurring on the circuit's edge, however, might not be eliminated at outputs (more specifically, a critical error within the last two layers or a subcritical error in the last layer is not correctable at outputs). Therefore, the gates on the edge are critical in the sense that the failure of any critical gate will cause a high probability of failure for the whole circuit. Because a single error is corrected within a rather short logical path, many multiple errors do not interact. Hence, multiple errors are also correctable in many cases. This is a particular merit of quadded logic.

# 2.3.4 N-tuple Intervowen Redundancy (NIR) & Triple Intervowen Redundancy (TIR)

Jie Han and Pieter Jonker present a new design of interwoven redundant logic, called random interwoven redundancy, which can serve as the basis for building any realistic circuit. The investigation of the fault tolerance of random interwoven redundant circuits is done through a simulation-based experimental approach [34].

Triplicated interwoven redundancy (TIR) is the simplest form of random intervowen redundancy. Figure 2.5 shows the schematic of a TIR implementation for the complementary half adder in Figure 2.3. The TIR circuit triplicates each NAND gate in the nonredundant circuit, as well as all the interconnections. A TIR circuit thus has three times as many gates and interconnections as the corresponding nonredundant circuit. The interconnections in a TIR circuit are, in principle, arranged randomly. For example, in a TIR circuit comprising twoinput NAND gates, for instance, there are six possible pair connections: (1,1), (2,2), (3,3), (1,1), (2,3), (3,2), (1,2), (2,3), (3,1), (1,2), (2,1), (3,3), (1,3), (2,1), (3,2), and (1,3), (2,2), (3,1). The notation (i, j) means that the output of gate *i* in a triplet of gates, pairs with the output of gate *j* in another triplet to form the inputs of a gate in the next stage. The total interconnect pattern becomes 36 (or  $6 \times 6$ ) if the gate orders of a triplication in the next stage are distinguished. One method of arranging the interconnections is to randomly adopt one of the 36 connection patterns for all connecting pairs in adjacent layers. As shown in Figure 2.5, the interconnect patterns used in the three layers from inputs to outputs of the circuit are (1,1), (2,2), (3,3), (1,2), (2,3), (3,1), and (1,3), (2,1), (3,2), although the circuit can use any other interconnect pattern. Notice that, if the pattern (1,1), (2,2), (3,3) is used in all layers for all interconnections, the circuit in Figure 2.5 will perform a computation as three independent modules, it will actually work as a TMR circuit, as depicted in Figure 2.6. TIR is hence a generalization of TMR to allow for random interconnections. The randomness in the TIR interconnections is particularly interesting in the physical implementation of molecular electronics, for which stochastic chemical assembly will most likely be the manufacturing method.

The principle of TIR is applicable to arbitrary logic circuits. A general procedure for constructing a TIR circuit is as follows [34]:

- 1. Start with a nonredundant form of the circuit.

- 2. Triplicate each gate.

- 3. Following the interconnect pattern of the nonredundant circuit, randomly select a gate from a triplet to use as an input for a gate that has no other inputs from the same triplet.

- 4. Repeat Step 3 until all the gates are connected in the TIR circuit

As in TMR, a TIR circuit requires a decision element (a voter) as a restor-

Figure 2.5: TIR implementation of the complementary half adder.

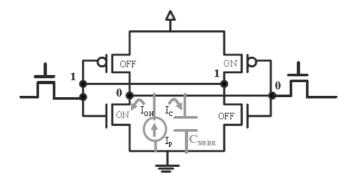

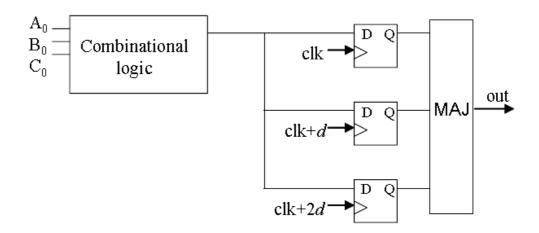

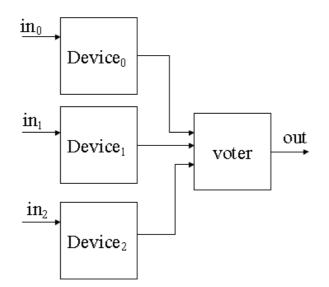

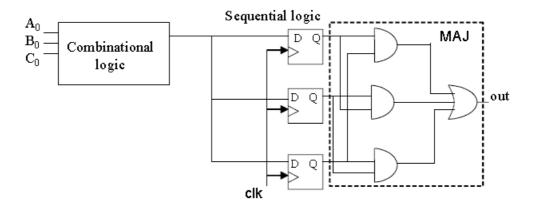

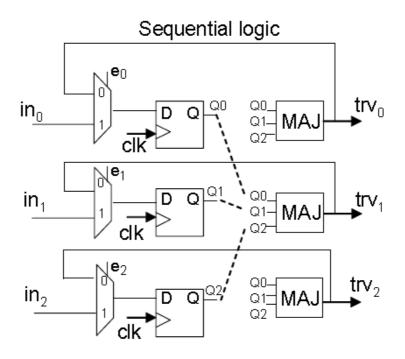

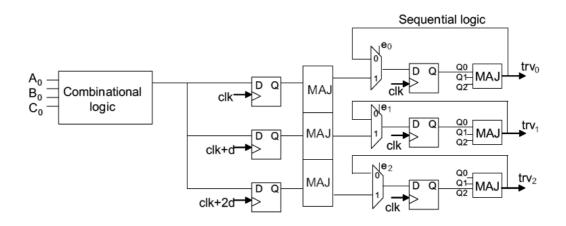

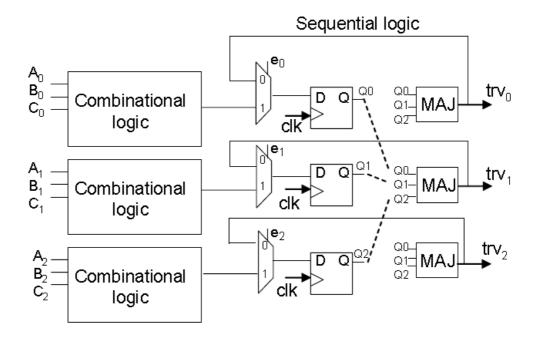

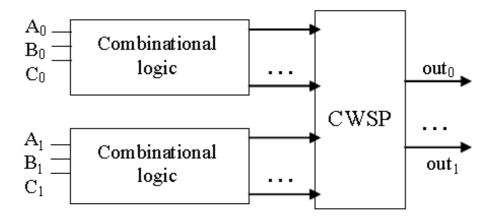

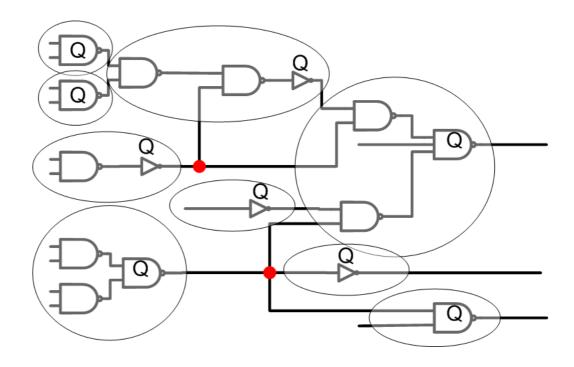

Figure 2.6: TMR configuration of the TIR complementary half adder.