### A Parallel Tabu Search Algorithm for VLSI Standard Cell Placement

by

### Ahmad Abdul-Jabbar Al-Yamani

### A Thesis Presented to the

### FACULTY OF THE COLLEGE OF GRADUATE STUDIES

### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

### DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

### **MASTER OF SCIENCE**

In

### **COMPUTER ENGINEERING**

May, 1999

### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

| A Parallel Tabu Search Algorithm                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| for VLSI Standard Cell Placement                                                                                                                 |

|                                                                                                                                                  |

| BY                                                                                                                                               |

| Ahmad Abdul-Jabbar Al-Yamani                                                                                                                     |

| A Thesis Presented to the                                                                                                                        |

| FACULTY OF THE COLLEGE OF GRADUATE STUDIES                                                                                                       |

| <section-header><section-header><text><text><text><text><text><text></text></text></text></text></text></text></section-header></section-header> |

|                                                                                                                                                  |

| Requirements for the Degree of                                                                                                                   |

|                                                                                                                                                  |

| MASTER OF SCIENCE                                                                                                                                |

| in                                                                                                                                               |

| Computer Engineering                                                                                                                             |

|                                                                                                                                                  |

|                                                                                                                                                  |

| May 1999                                                                                                                                         |

|                                                                                                                                                  |

-.

j

#### UMI Number: 1395608

UMI Microform 1395608 Copyright 1999, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

### UMI 300 North Zeeb Road

Ann Arbor, MI 48103

### KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN 31261, SAUDI ARABIA DEANSHIP OF GRADUATE STUDIES

This thesis, written by

AL-YAMANI, AHMAD ABDUL-JABBAR

under the direction of his Thesis Advisor and approved by his Thesis Committee, has been presented to and accepted by the Dean of the Deanship of Graduate Studies, in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE IN COMPUTER ENGINEERING

Thesis Committee

chairman)

Hassan Barada (Member)

1815140

Dr. Abdullah I. Almojel Department Chairman

Dr. Abdullah M. Al – Shehri

Dean of Graduate Studies

<u>18/5/9</u>9 Date

# "هذا من فنخل روي ليبلونيي الشكر أم أكفر ومن شكر فإنما يشكر لنغسه ومن كغر فإن روي نمنيي كريم"

النمل -2-

Dedicated

$\mathbf{to}$

my beloved parents

and to the memory of my sister

Ameerah

## Acknowledgments

All praise be to Allah, Subhanahu-wa-ta-Aaala, for his unlimited help and guidance. May Allah bestow peace on his prophet, Muhammad (pbuh), and his family. I acknowledge the support and facilities provided by King Fahd University of Petroleum and Minerals, Dhahran, Saudi Arabia.

Thanks to my father and mother who were -after Allah- the source of all success in my life. I was carried through the most difficult moments in my life by their prayers, love, and support. My sisters and brothers were a great source of support in all achievements I accomplished.

I would like to express my extreme thanks to the one who did the difficult part of the work. The one who was living the difficult moments before the nice ones. The one whose support, appreciation and patience made it possible. All thanks are to my wife 'Alaa Olwi'. I also thank my father-in-law and my mother-in-law who were in touch throughout all the steps in my MS program.

I would like to express my profound gratitude and appreciation to my thesis committee Dr. Sadiq M. Sait, Dr. Habib Youssef and Dr. Hassan Barada, for their guidance and patience throughout this thesis. It was because of them that the work at any point of time, never got stressful.

I also wish to thank the Chairman of Computer Engineering Department, Dr. Abdullah Almojel and Dean of College of Computer Science and Engineering, Dr. Khalid AlTawil, for all the support they provided in order to achieve this work. Also, my thanks go to the faculty and staff members of Computer Engineering Department for their encouragement. I also thank Hussain Ali for helping in providing a lot of useful functions without which the comparison would not have been possible.

# Contents

.

|   | Ack  | cnowledgments v                           |

|---|------|-------------------------------------------|

|   | List | of Tables ix                              |

|   | List | of Figures x                              |

|   | Abs  | stract (English) xii                      |

|   | Abs  | stract (Arabic) xiii                      |

| 1 | Intr | roduction 1                               |

|   | 1.1  | VLSI Placement Problem Definition         |

|   | 1.2  | VLSI Design Styles                        |

|   | 1.3  | Multi-Objective Placement Problem         |

|   |      | 1.3.1 Interconnection Length              |

|   |      | 1.3.2 Area                                |

|   |      | 1.3.3 Critical Path Delay                 |

|   |      | 1.3.4 Overall Solution Quality Evaluation |

|   | 1.4  | Heuristics Applied to VLSI Placement      |

|   | 1.5  | Organization of the Thesis                |

| 2 | Tab  | ou Search 13                              |

|   | 2.1  | Basic Tabu Search Algorithm               |

|   | 2.2  | Tabu Search Parameters    16              |

|   |      | 2.2.1 Candidate List                      |

|   |      | 2.2.2 Moves and Move Attributes                       | 19 |

|---|------|-------------------------------------------------------|----|

|   |      | 2.2.3 Evaluation Function                             | 19 |

|   |      | 2.2.4 Tabu List                                       | 20 |

|   |      | 2.2.5 Aspiration Criteria                             | 21 |

|   | 2.3  | Tabu Search Classes                                   | 23 |

|   | 2.4  | Summary                                               | 24 |

| 3 | Lite | erature Review                                        | 26 |

|   | 3.1  | Heuristics Applied to VLSI Placement                  | 26 |

|   | 3.2  | Tabu Search in VLSI Placement                         | 28 |

|   | 3.3  | Tabu Search Parallelization                           | 29 |

|   | 3.4  | Summary                                               | 32 |

| 4 | Par  | allel TS for VLSI Standard-Cell Placement             | 33 |

|   | 4.1  | Proposed Tabu Search Algorithm                        | 33 |

|   | 4.2  | Parallelization of the Algorithm                      | 35 |

|   | 4.3  | Applying the Algorithm in a Heterogeneous Environment | 38 |

|   | 4.4  | Diversification of the Search Process                 | 41 |

|   | 4.5  | Summary                                               | 43 |

| 5 | Exp  | perimental Results                                    | 45 |

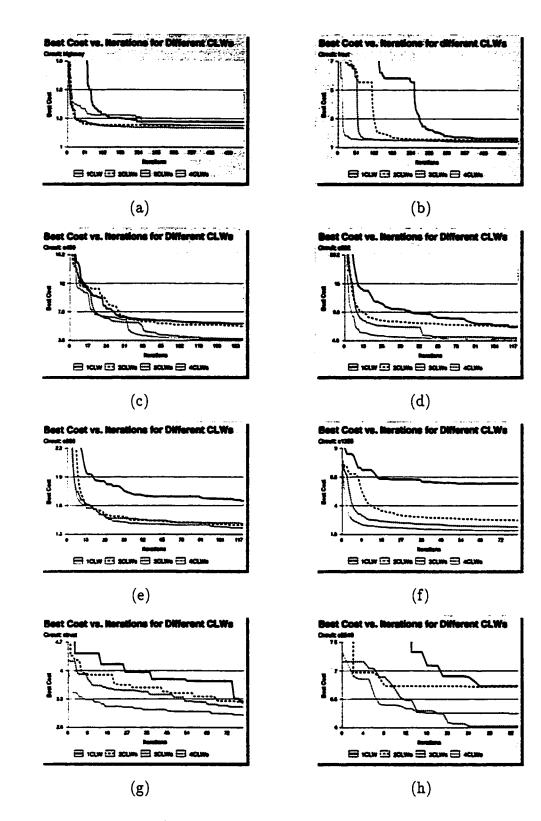

|   | 5.1  | Effect of Degree of Low-level Parallelization         | 47 |

|   | 5.2  | Effect of Degree of High-level Parallelization        | 53 |

|   | 5.3  | Accounting for Speed and Load Heterogeneity           | 57 |

|   | 5.4  | Effect of Diversification                             | 61 |

|   | 5.5  | Interarrival of a q-Quality Solution                  | 65 |

|   | 5.6  | Fuzzy Cost Evaluation vs. Weighted Sum                | 67 |

|   | 5.7  | Comparison with Previous Work                         | 68 |

|   | 5.8  | Summary                                               | 70 |

| 6 | Cor  | nclusions                                             | 71 |

| A | Parallel Virtual Machine 7 |         |                           |    |

|---|----------------------------|---------|---------------------------|----|

|   | A.1                        | Introd  | uction                    | 74 |

|   | A.2                        | Paralle | el Virtual Machine (PVM)  | 75 |

|   |                            | A.2.1   | PVM Daemon (pvmd)         | 75 |

|   |                            | A.2.2   | PVM Library (PVML)        | 75 |

|   |                            | A.2.3   | Architectural Description | 76 |

# List of Tables

| 5.1 | Characteristics of circuits and layouts used. $(LH = layout)$ |    |

|-----|---------------------------------------------------------------|----|

|     | heights and Avg. $RCH$ = average routing channel height in    |    |

|     | microns)                                                      | 46 |

| 5.2 | Parameters of parallel experiments. $(GI = Global Iterations$ |    |

|     | and $LI = Local Iterations)$                                  | 47 |

| 5.3 | Runtime of homogeneous and heterogeneous runs in seconds      |    |

|     | for seven circuits                                            | 59 |

| 5.4 | Best solution achieved by fuzzy evaluation run vs. weighted   |    |

|     | sum run                                                       | 68 |

| 5.5 | Best solution achieved by parallel tabu search vs. classical  |    |

|     | simulated evolution                                           | 69 |

| 5.6 | Best solution achieved by parallel tabu search vs. simulated  |    |

|     | evolution with fuzzy evaluation.                              | 69 |

| 5.7 | Best solution achieved by parallel tabu search vs. simulated  |    |

|     | evolution with fuzzy allocation.                              | 70 |

# List of Figures

| 1.1 | Levels of abstraction for VLSI circuits design.                    | 2  |

|-----|--------------------------------------------------------------------|----|

| 1.2 | Configuration of a VLSI standard cell layout                       | 4  |

| 1.3 | Range of acceptable solutions for a tri-valued cost vector         | 8  |

| 1.4 | Range of acceptable solutions for a the proposed cost vector       | 9  |

| 1.5 | The membership function within acceptable criterion $i$            | 10 |

| 2.1 | Algorithmic description of tabu search (TS)                        | 14 |

| 2.2 | Basic tabu search algorithm flowchart.                             | 15 |

| 2.3 | Aspiration plus strategy                                           | 17 |

| 2.4 | Elite candidate list strategy                                      | 17 |

| 2.5 | Sequential fan candidate list strategy                             | 18 |

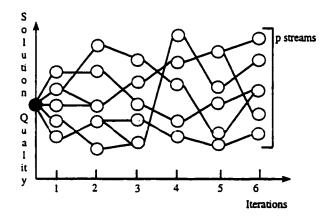

| 4.1 | Paradigm of tabu search parallel implementation.                   | 36 |

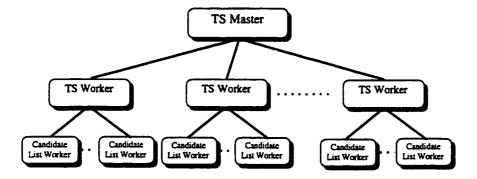

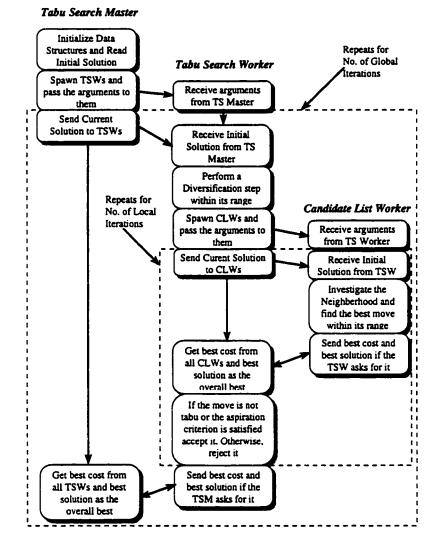

| 4.2 | Algorithmic description of master process of parallel TS. $\ldots$ | 39 |

| 4.3 | Algorithmic description of worker process of parallel TS           | 39 |

| 4.4 | A scenario of the master, the $TSW$ and the $CLW$ processes        | 40 |

| 5.1 | Effect of number of CLWs on the solution quality                   | 49 |

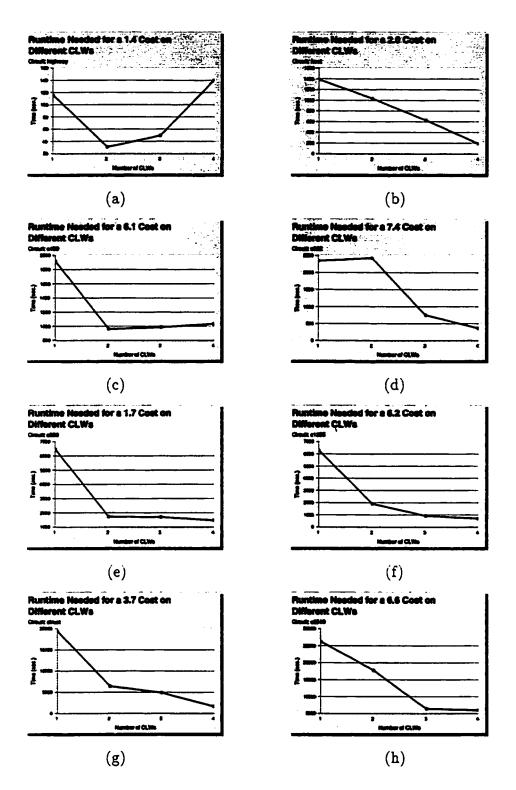

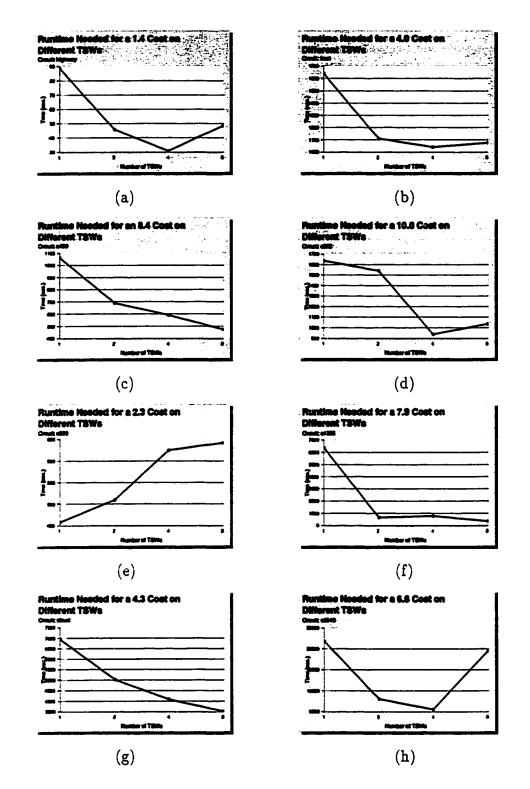

| 5.2 | Runtime needed to achieve a solution of cost less than $x$ for     |    |

|     | different numbers of CLWs.                                         | 50 |

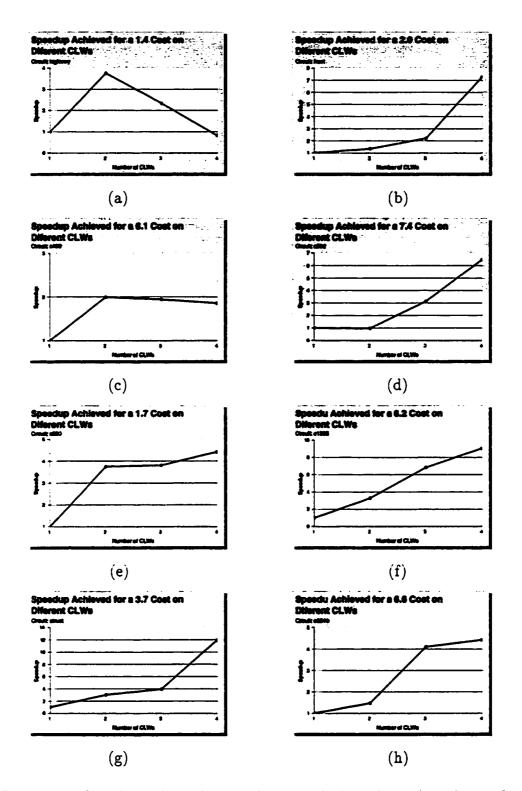

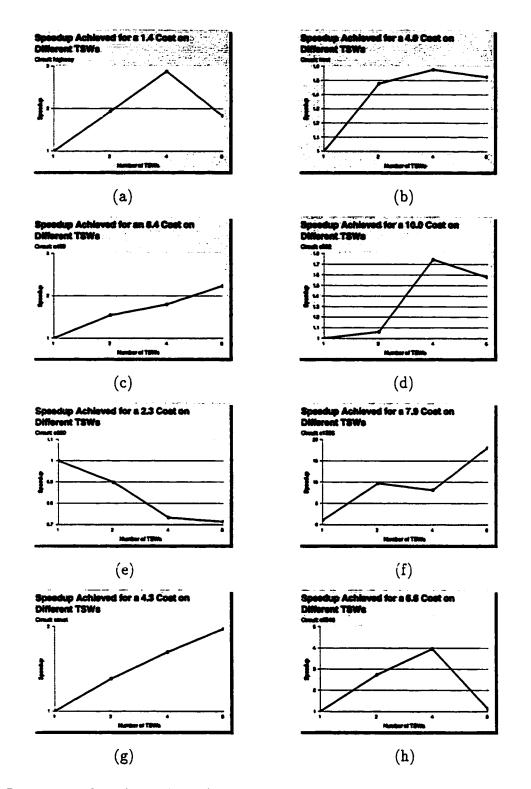

| 5.3 | Speedup achieved in reaching a solution of cost less than $x$ for  |    |

|     | different numbers of CLWs.                                         | 51 |

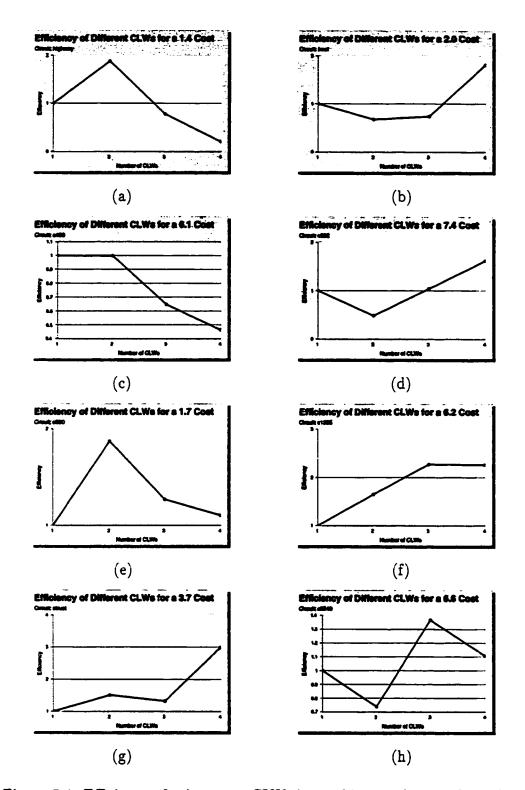

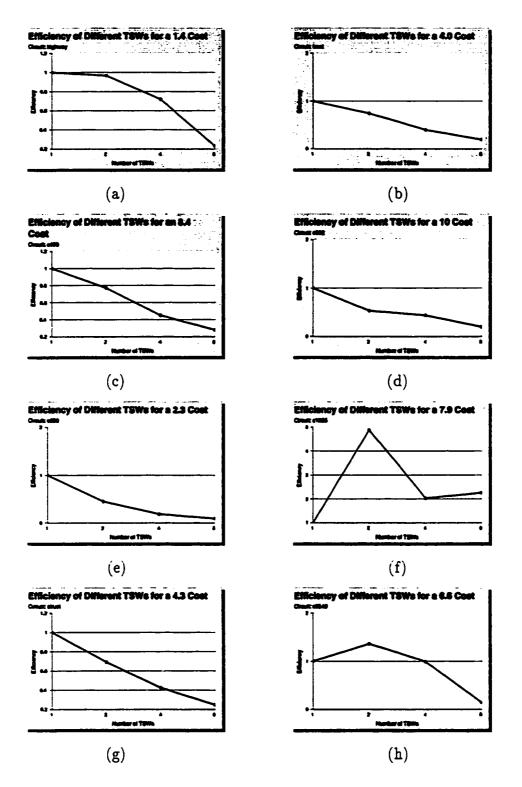

| 5.4 | Efficiency of using more CLWs in reaching a solution of cost       |    |

|     | less than $x$                                                      | 52 |

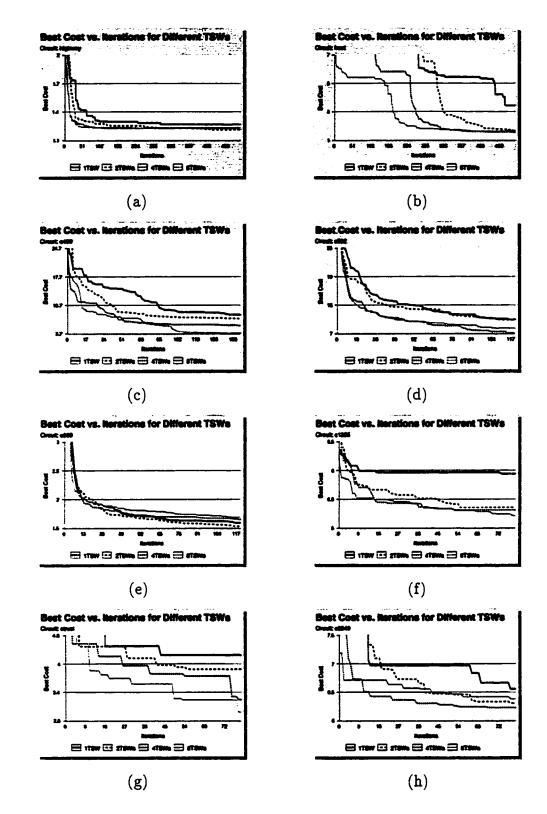

| 5.5 | Effect of number of TSWs on the solution quality                   | 54 |

| 5.6  | Runtime needed to achieve a solution of cost less than $x$ for    |    |

|------|-------------------------------------------------------------------|----|

|      | different numbers of TSWs                                         | 55 |

| 5.7  | Speedup achieved in reaching a solution of cost less than $x$ for |    |

|      | different numbers of TSWs                                         | 56 |

| 5.8  | Efficiency of using more TSWs in reaching a solution of cost      |    |

|      | less than $x$                                                     | 58 |

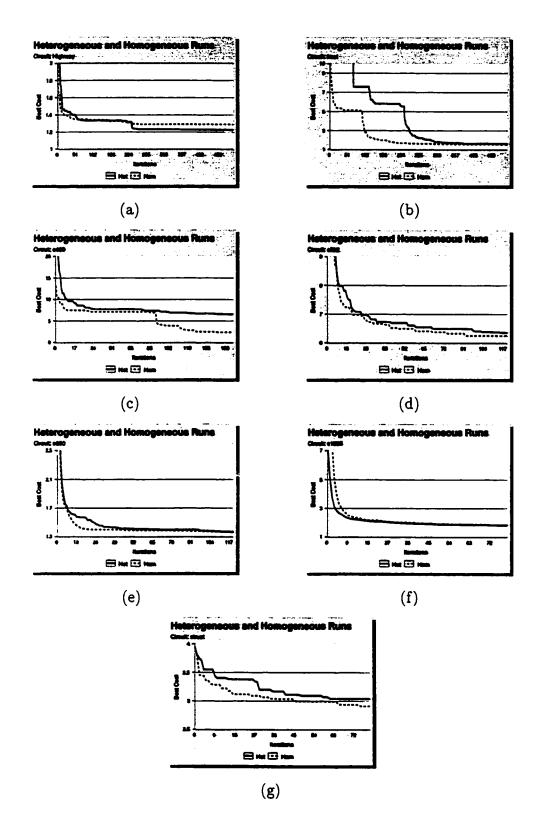

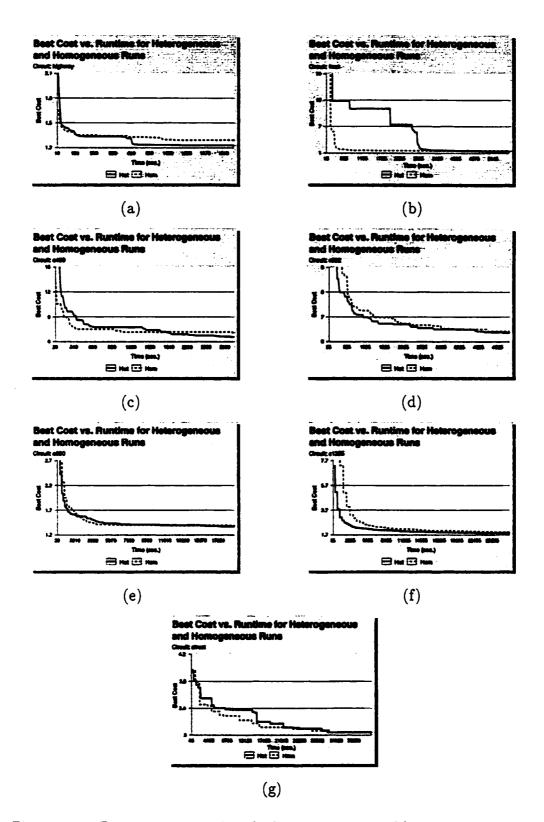

| 5.9  | Heterogeneous vs. homogeneous runs                                | 60 |

| 5.10 | Best cost vs. runtime for heterogeneous and homogeneous runs.     | 62 |

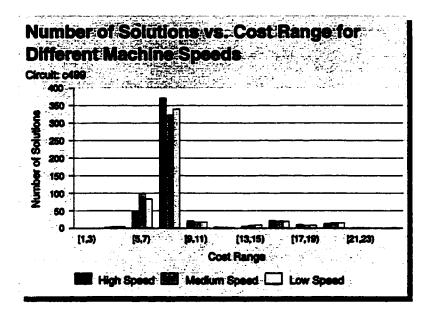

| 5.11 | Number of solutions provided by machines of different speeds      |    |

|      | within various solution ranges                                    | 63 |

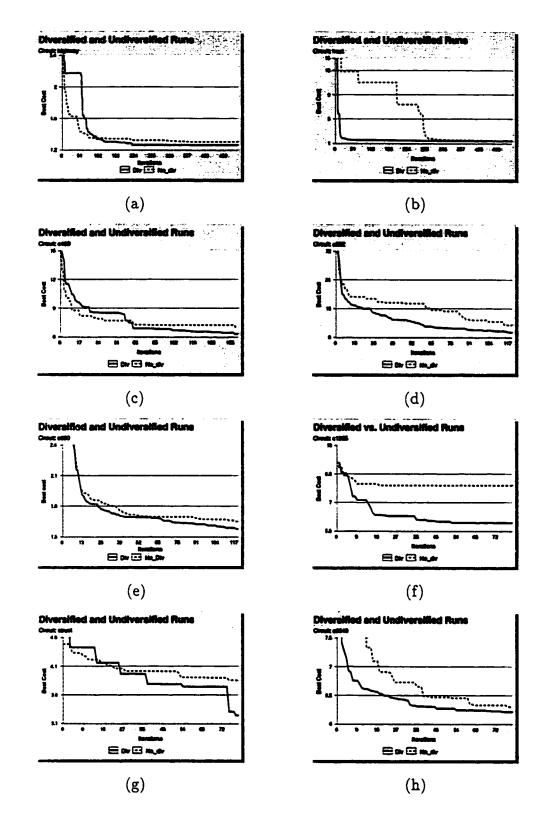

| 5.12 | Effect of diversification                                         | 64 |

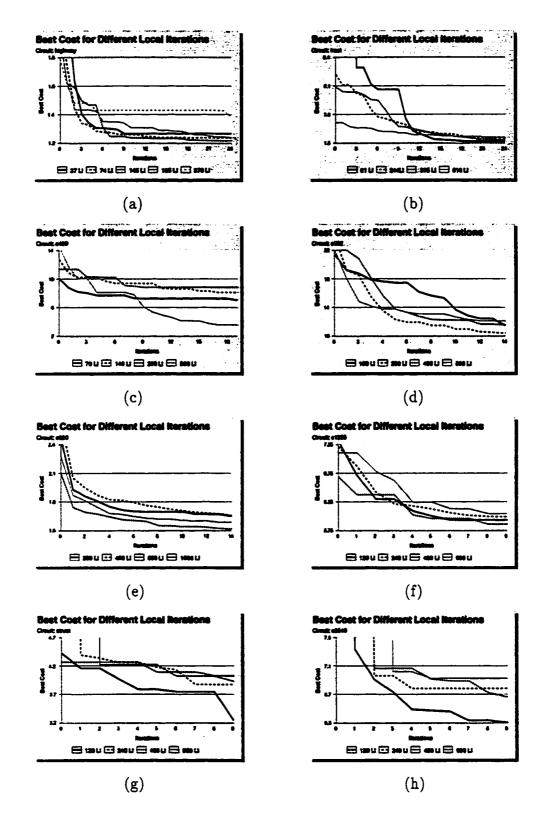

| 5.13 | Local vs. global iterations                                       | 66 |

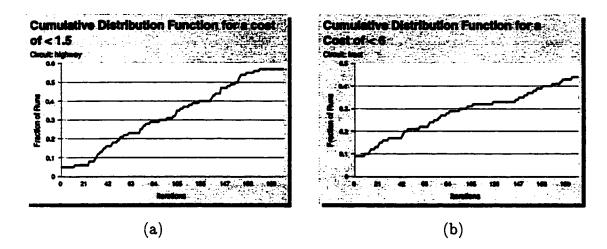

| 5.14 | CDF for getting a solution of quality $< q$                       | 67 |

|      |                                                                   |    |

### THESIS ABSTRACT

Name:AL-YAMANI, AHMAD ABDUL-JABBARTitle:A PARALLEL TABU SEARCH ALGORITHMFOR VLSI STANDARD CELL PLACEMENTMajor Field:COMPUTER ENGINEERINGDate of Degree:May 1999

VLSI standard cell placement is an NP-hard problem to which various heuristics have been applied. In this work, tabu search, which is an iterative heuristic, is used. The objective of the algorithm is to achieve the best possible placement solution in terms of interconnection length, overall area of the circuit, and critical path delay (circuit speed). The algorithm is parallelized on a network of stations using PVM. The proposed tabu search algorithm integrates two parallelization strategies. These are functional decomposition strategy and multi-search threads strategy. Furthermore, domain decomposition strategy is implemented probabilistically. The performance of each strategy is observed and analyzed. The goal of the parallelization is to speedup the search and to improve the solution quality. A diversification scheme is applied to make sure that different processes investigate different regions of the search space. The performance of this scheme is studied and analyzed. The algorithm is applied in a heterogeneous environment and a suitable strategy is adopted to account for that heterogeneity. The effect of accounting for heterogeneity is observed and analyzed. Experimental results are presented. Index Terms: VLSI, Standard Cell Design, Placement, Tabu Search, Parallel Tabu Search, Functional Decomposition, Multi-Search Threads, Combinatorial Optimization, Diversification.

### MASTER OF SCIENCE DEGREE

KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS Dhahran, Saudi Arabia

May 1999

### خلاصة الرسالة

الاسمـم: أحمد بن عبد الجبار اليماني عنوان الرسالة: خوارزم متوازي للبحث المحظور لمشكلة ترتيب الخلايا في الدوائر عالية الكثافة جدا التممحصص: هندسة الحاسب الآلي تاريخ الشهادة: مايو ١٩٩٩

ترتيب الخلايا في الدوائر عالية الكثافة جداً مشكلة لا يمكن تمثيلها بكثيرات الحدود وطبق عليها أكثر مسن خوارزم. في هذه الرسالة، يستخدم خوارزم البحث المحظور وهو خوارزم عشوائي تسلسسلي. هدف الخوارزم المستخدم هو تحقيق أفضل الحلول الممكنة من حيث طول التوصيلات، المساحة الكلية للدائسرة، وسرعة عمل الدائرة. ينفذ الخوارزم بالتوازي على شبكة من محطات العمل باستخدام (PVM). الخسوارزم المقترح يكامل استراتيجيتين للتنفيذ المتوازي هما استراتيجية التحليل الوظيفي واستراتيجية عمليات البحث من هذه الإضافة إلى ذلك، فإن استراتيجية تقسيم المجال تطبق احتمالياً. يتم تحليل و ملاحظة أداء كسل من هذه الاستراتيجيات. هدف التنفيذ المتوازي هو تطوير سرعة البحث ونوعية الخسل. تطبسق طريق المتراتيجيات. هدف التنفيذ المتوازي هو تطوير سرعة البحث ونوعية الحل. تطبسق طريق من هذه الاستراتيجيات. هدف التنفيذ المتوازي هو تطوير سرعة البحث ونوعية الحل. المتراتيجيات. هدف التنفيذ المتوازي هو تطوير سرعة البحث ونوعية الحسل. تطبسق المنوارزم في بيئة من مطات عمل متغايرة. تتم ملاحظة وتحليل تأثير اعتبار التغاير بين الأجهزة. وأخسيراً، تتم مقارنة نتائج الخوارزم بنتائج عمل سابق من أجل التحقق من عمله.

مصطلحات البحث: الدوائر عالية الكثافة جداً، التصميم القياسي، ترتيب الخلايا، زمن التنفيـــذ، طـــول التوصيلات، البحث المحظور، البحث المحظور المتوازي، التحليل الوظيفي، عمليـــات البحـــث المتعــددة، التكفىء التجميعي، التباعد.

# Chapter 1

# Introduction

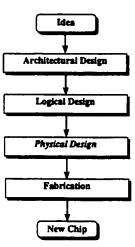

Complexity of Very Large Scale Integration (VLSI) circuits requires breaking the design process into various levels of abstraction. These levels are shown in Figure 1.1 [1]. Architectural design is the task of human experts who determine the behavior of the product under various circumstances and different inputs. This stage has a great effect on the cost and the performance of the final product. Logical design phase takes care of defining the data path and the control path of the circuit to be designed. The fabrication of the circuit, i.e., Printed Circuit Board (PCB) or VLSI, is also part of this design level.

Physical design refers to all steps that follow the logical design before the fabrication of the circuit. These steps include partitioning, floorplanning, placement and routing. The wire length of the circuit, the overall area, and the delay, are dramatically affected by how the circuit is laid out. In this work, placement problem, which is one of the VLSI physical design problems, is addressed and *Tabu Search* algorithm, which is an iterative heuristic, is applied to it.

Figure 1.1: Levels of abstraction for VLSI circuits design.

### 1.1 VLSI Placement Problem Definition

In VLSI design, placement is the process of arranging components on the circuit surface [1]. These components are interconnected functional blocks that vary in size according to their functions.

The process of placement is directed towards satisfying some objectives. These objectives can be the overall area of the circuit [2, 3], the total wire length [4], the delay of the critical paths [5, 6, 7], the routability of the interconnections [8], or a combination of these.

The problem of cell placement can be defined as finding suitable locations for all cells in the two-dimensional layout surface of a VLSI circuit. A suitable location is one that optimizes some objectives like wire length, area, and/or delay. Cell placement problem can be formally defined as follows. Given a set of modules  $M = \{m_1, m_2, \dots, m_n\}$ , and a set of signals  $S = \{s_1, s_2, \dots, s_k\}$ , each module  $m_i \in M$  is associated with a set of signals  $S_{m_i}$ , where  $S_{m_i} \subseteq S$ . Also each signal  $s_i \in S$  is associated with a set of modules  $M_{s_i}$ , where  $M_{s_i} = \{m_j | s_i \in S_{m_j}\}$ .  $M_{s_i}$  is called a signal net. Placement problem is to assign each module  $m_i \in M$  to a unique location such that a given cost function is optimized and a number of constraints are satisfied. Cost function and constraints depend on the layout style and the objectives [9].

Even in its simple case, where components and slots are of equal sizes and one objective is to be satisfied, placement is an NP-hard<sup>1</sup> problem [8]. Since the number of cells can be in thousands, it is impractical to use brute force technique to solve it.

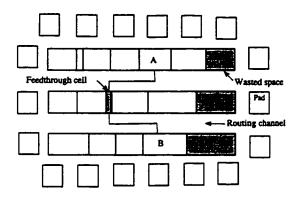

### 1.2 VLSI Design Styles

Various layout styles differ in the structural constraints imposed on the components and the layout surface. These styles include the full-custom layout where no constraints are applied, the automation becomes difficult and the layout is hand-crafted. Gate array methodology imposes the restriction that the surface is a two dimensional array of equal-size slots and the components have to be equally sized [1]. Macro cell methodology allows cells to vary in both dimensions to allow smaller area placement or better routing of interconnections [1, 11]. Standard cell methodology assumes the cells to be of same height and variable width to be arranged in rows. Channels between the rows are of variable height to allow routing of connections between cells. Connections between cells on the same row or opposite rows are routed through adjacent channels. Connections between non-adjacent rows are routed through feed-through cells placed in the intermediate row(s) [1, 2, 4, 8, 12, 13, 14]. Figure 1.2 shows the configuration of a standard cell layout.

### **1.3 Multi-Objective Placement Problem**

Modern placement programs usually require the optimization of several objectives and the satisfaction of several constraints. Typical objectives are the overall area of the circuit i.e., the functional area and the wiring area

<sup>&</sup>lt;sup>1</sup>NP-Hard Problems are a class of problems that cannot be solved by a deterministic algorithm of polynomial complexity [10].

Figure 1.2: Configuration of a VLSI standard cell layout.

[2, 3], the total wire length [4], the delay of the critical paths [5, 6, 7], the routability of the interconnections [8], or a combination of some or all of these. Some of the objectives might be conflicting. For example, to have the smallest possible area, one might have to accept a larger delay. A similar conflict might exist between routability and wire length. In order to combine conflicting objectives in the evaluation function, either weighted sum or fuzzy evaluation should be used. In this work, interconnection length, overall area, and critical path delay will be used to quantify the goodness of a specific solution. The objective of the search is to define the *most acceptable* solution and to allow the designer to express her/his preferences for each criterion. In this work, fuzzy algebra is used to evaluate the overall cost of the solution.

#### **1.3.1** Interconnection Length

One of the most important characteristics of a proposed solution is its wire length. This is due to the rapid improvement in the switching delay of the transistors. As a result, the interconnection delay is becoming the bottleneck in VLSI technology. Another reason is that the functional area is getting much smaller compared to the interconnection area. These factors led to considering wire length as a critical measure in any proposed layout configuration. Different models are used to estimate the length of a given *net* which is a set of points or pins that have to be in the same voltage level (connected points). Half-perimeter bounding box, minimum Steiner tree, and minimum spanning tree are among those models [1, 8].

Steiner tree approximation is fast and accurate enough in modeling actual wire length and it has been used in this work [15]. To apply this model, the bounding box, which is the smallest rectangle bounding a net, is found for each net. The average vertical distance Y and horizontal distance X of all cells in the net are computed from the origin which is the bottom left corner of the bounding box of the net. A central point (X, Y) is placed at the computed average distances. If X is greater than Y then the vertical line crossing the central point is considered as the bisecting line. Otherwise, the horizontal line is considered as the bisecting line. Steiner tree approximation of a net is the length of the bisecting line added to the summation of perpendicular distances to it from all cells belonging to the net. Steiner trees is considered as the interconnection length of the proposed solution.

$$X = \frac{\sum_{i=1}^{n} x_i}{n} \qquad Y = \frac{\sum_{i=1}^{n} y_i}{n}$$

(1.1)

where n is the number of cells contributing to the current net.

Steiner Tree =

$$B + \sum_{j=1}^{k} P_j$$

(1.2)

Where B is the length of the bisecting line, k is the number of cells contributing to the net and  $P_j$  is the perpendicular distance from cell j to the bisecting line.

Interconnection Length =

$$\sum_{l=1}^{m} Steiner Tree_l$$

(1.3)

Where m is the number of nets.

#### 1.3.2 Area

In standard cell placement, cells (or blocks) of fixed heights are placed in rows. It is the width of these rows that varies with the proposed solution according to the type and number of cells placed in the row. Heights of routing channels are initially estimated and assumed to be fixed because routing is not in the scope of this work. The overall area of a given solution is estimated as follows

$A = (n_rows \times row_height + (n_rows - 1) \times channel_height) \times longest_width$ (1.4)

$n\_rows$  gives the number of rows used in the solution under test. The number of channels is 1 less than the number of rows. When  $n\_rows$  and  $(n\_rows-1)$ are multiplied by  $row\_height$  and  $channel\_height$  respectively, they give the overall height of the layout. Multiplied by the longest row, it gives the area of the bounding rectangle of the proposed solution. Since  $row\_height$  is constant and  $channel\_height$  is assumed to be constant, width of the longest row will be measured as it is the only thing that differs from solution to another<sup>2</sup>.

### **1.3.3** Critical Path Delay

A digital circuit comprises a collection of paths. A path is a sequence of nets and blocks from a source to a sink. A source can be an input pad or a memory cell output, and a sink can be an output pad or a memory cell input. The longest path (*critical path*) is the dominant factor in deciding the clock frequency of the circuit. A critical path makes a problem in the design if it has a delay that is larger than the largest allowed delay (period) according to the clock frequency.

The delay of any given path is computed as the summation of the delays of the nets  $v_1, v_2, ..., v_k$  belonging to that path and the switching delay of the

<sup>&</sup>lt;sup>2</sup>From here on, in this thesis, width will be used in place of area because the height of the layout is assumed to be constant.

cells driving these nets. The delay of a given path  $\pi$  is given by

$$T_{\pi} = \sum_{i=1}^{k-1} (CD_{vi} + ID_{vi})$$

(1.5)

where  $CD_{vi}$  is the switching delay of the driving cell and  $ID_{vi}$  is the interconnection delay that is given by the product of the load factor of the driving cell and the capacitance of the interconnection net, i.e.,

$$ID_{vi} = LF_{vi} \times C_{vi} \tag{1.6}$$

$SLACK_{\pi}$  of path  $\pi$  is given by

$$SLACK_{\pi} = LRAT_{\pi} - T_{\pi} \tag{1.7}$$

where  $LRAT_{\pi}$  is the latest required arrival time and  $T_{\pi}$  is the path delay [16, 17]. If  $T_{\pi}$  is greater than  $LRAT_{\pi}$ , then the path  $\pi$  will have a negative SLACK which is an indicator of a **long path** problem. Upper bounds can be applied to nets belonging to the critical path as constraints not to allow them to exceed a certain limit beyond which the SLACK will be negative.

### **1.3.4** Overall Solution Quality Evaluation

The overall quality (or cost) of a multi-objective problem is a vector quantity. In this work, since we are using three criteria to represent a solution cost, the cost is a tri-valued vector. To represent this vector as a scalar quantity for comparison between solutions, weighted sum can be used. The main disadvantage in using weighted sum scheme is the difficulty in finding the appropriate combination of weights. The objective of the search is to find the *most acceptable* solution with respect to the evaluation criteria. This makes fuzzy algebra a suitable way for defining the goodness of a given solution with respect to different criteria [11, 15, 18, 19, 20]. The evaluation function should allow expressing designer preferences with respect to each evaluation criterion. For this, the scheme we are using for fuzzification is called *Fuzzy Goal Based Cost Measure* which was proposed in [15].

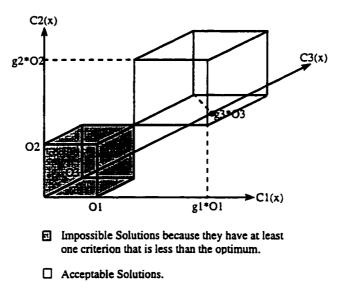

Let there be p values in the solution cost vector. For a given solution x, the cost is given by the vector  $C(x) = (C_1(x), C_2(x), \dots, C_p(x))$ . Let  $O = (O_1, O_2, \dots, O_p)$  be a vector representing the optimum quantities for all cost criteria i.e.,  $O_i \leq C_i(x) \ \forall i, \forall x \in \Pi$ , where  $\Pi$  is the set of possible solutions.  $G = (g_1, g_2, \dots, g_p)$  is a user-specified goal vector representing the acceptable limits for all cost criteria in the cost vector. A solution x is considered acceptable by the user if  $C_i(x) \leq g_i \times O_i$ ,  $\forall i$ . Since the acceptable limit has to be greater than the optimum value,  $g_i > 1.0 \ \forall i$ .

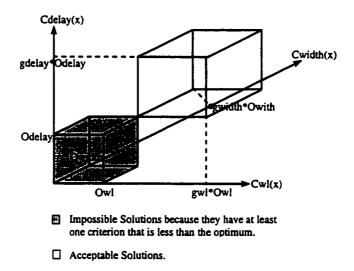

Figure 1.3 shows the region of acceptable solutions for a tri-valued cost vector given  $O_1$ ,  $O_2$ ,  $O_3$ ,  $g_1$ ,  $g_2$  and  $g_3$ . The projection of that figure on our cost function that has  $O_{wl}$ ,  $O_{delay}$  and  $O_{width}$  as the optimum values for wire length, delay and longest width respectively and  $g_{wl}$ ,  $g_{delay}$  and  $g_{width}$  as the goals for those criteria is shown in Figure 1.4.

Figure 1.3: Range of acceptable solutions for a tri-valued cost vector.

In this work, the rule for determining membership in the fuzzy set is taken as in [15]. The rule is as follows:

**Rule1**: If a solution is within acceptable wire length AND within acceptable circuit delay AND within acceptable width, THEN it is an acceptable solution.

Figure 1.4: Range of acceptable solutions for a the proposed cost vector.

Using fuzzy algebraic notation, while adopting the andlike ordered weighted averaging (OWA) operator of Yager [21], the above rule is expressed as follows,

$$\mu(x) = \beta \times \min(\mu_1(x), \mu_2(x), \mu_3(x)) + (1 - \beta) \times \frac{1}{3} \sum_{i=1}^3 \mu_i(x)$$

(1.8)

where,  $\mu(x)$  is the membership value for solution x in the fuzzy set acceptable solutions.  $\mu_i$  for  $i \in \{1, 2, 3\}$  (or  $i \in \{wl, delay, width\}$ ) represents the membership values for solution x in fuzzy sets within acceptable wire length, within acceptable circuit delay and within acceptable width respectively.  $\beta$  is an averaging constant in the range [0, 1]. The solution that results in the maximum value for Equation 1.8 is considered as the best solution found.

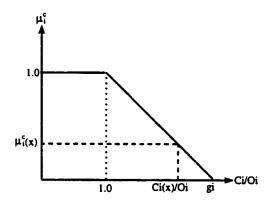

The membership functions used for wire length, delay and width are the same. They are computed as follows:

$$\mu_{i} = \begin{cases} 1 & \text{if } C_{i}(x)/O_{i} \leq 1\\ \frac{g_{i}-C_{i}(x)/O_{i}}{g_{i}-1} & \text{if } 1 < C_{i}(x)/O_{i} \leq g_{i}\\ 0 & \text{if } C_{i}(x)/O_{i} > g_{i} \end{cases}$$

(1.9)

Where,  $i \in \{1, 2, 3\}$  (or  $i \in \{wl, delay, width\}$ ). The membership function is shown in Figure 1.5.

Figure 1.5: The membership function within acceptable criterion i.

The lower bounds for wire length, delay and width were computed in [15] using the following formulae:

$$O_1 = \sum_{i=1}^n OWL_{vi} \ \forall v_i \in \{v_1, v_2, \cdots, v_n\} n \text{ nets in the circuit}$$

(1.10)

$$O_2 = \sum_{j=1}^k CD_{vi} \ \forall v_i \in \{v_1, v_2, \cdots, v_k\} k \text{ nets in path } \pi$$

(1.11)

$$O_3 = \left\lceil \frac{\sum_{i=1}^n Width_i}{\# \text{ of cell rows in layout}} \right\rceil$$

(1.12)

Where,  $O_1$ ,  $O_2$  and  $O_3$  are taken as lower bounds for wire length, delay and width respectively.

The value  $g_i$ , where  $i \in \{1, 2, 3\}$  (or  $i \in \{wl, delay, width\}$ ), which is specified by the user allows increasing or decreasing the contribution of the criterion *i* to the overall cost because  $\mu_i(x)$  is directly proportional to  $g_i$ .

### **1.4 Heuristics Applied to VLSI Placement**

The number of blocks to be placed in a VLSI circuit is very large (can be in thousands or more) and this makes a brute force approach an impractical way for solving such a problem. Heuristics applied to VLSI placement problem can be classified into *deterministic heuristics*, which move towards the solution by making deterministic decisions at each step, and *stochastic heuristics* which make controlled random decisions. Heuristics can be also classified as *constructive heuristics*, which construct the solution by placing one or few cells at a time, and *iterative heuristics* which start from an initial solution and modify it in several iterations to improve it with respect to an objective function.

Among the constructive deterministic heuristics applied to placement problem is the maximum connectivity strategy [1] and the min-cut algorithm [9, 22, 23]. Force directed algorithm is an iterative deterministic algorithm that was applied to placement [24]. Among the iterative stochastic heuristics are Simulated Annealing [25, 26, 27], Genetic Algorithm [28, 29], Simulated Evolution [30, 15] and Tabu Search [11, 31].

Constructive heuristics might trap the search at a solution which does not meet the constraints. For large problems, they usually lead to a solution that is far from the global optimum. In such a situation, numerous tedious manual modifications are needed and that is impractical in case of VLSI design [32]. Iterative heuristics, on the other hand, try to escape from local optima searching for a global one by accepting to climb hills in the search space through making non-improving moves at some stages of the search. In this thesis, we investigate *Tabu Search* as one of these iterative heuristics.

In this work, *Tabu Search* is applied to VLSI standard cell placement to optimize the wire length, the delay, and the total area of the final layout. Some standard benchmark circuits are used to test the performance of the proposed algorithm. The algorithm is parallelized on a network of stations including heterogeneous architectures and machines of varying speeds. Parallel Virtual Machine (PVM) is used to parallelize the algorithm. PVM is a system that makes a network of stations look like a single distributed machine for parallel computing using message passing [33] (see Appendix A). A diversification strategy for *Tabu Search* is proposed to make each process investigate a different area of the search space.

### **1.5** Organization of the Thesis

In this chapter, VLSI placement was introduced and defined and its complexity discussed. Different VLSI placement methodologies were addressed. The multi-objective placement problem was introduced. Three criteria for placement solution quality were discussed. Interconnection length, circuit delay and overall delay of the solution were explained. Combining conflicting objectives in one evaluation function using weighted sum and fuzzy logic was presented. Various heuristics that were applied to VLSI placement problem were presented and classified. The outline of the rest of the thesis was given.

Chapter 2 discusses Tabu Search and its main characteristics and parameters. The literature available on Tabu Search for VLSI placement problem and on Tabu Search Parallelization is reviewed in Chapter 3. The proposed Parallel Tabu Search Algorithm for VLSI Standard Cell Placement problem is explained in Chapter 4. Experimental results of the proposed methods and comparisons with other earlier approaches are presented and discussed in Chapter 5. Chapter 6 concludes the thesis.

# Chapter 2

### Tabu Search

Tabu Search (TS) is a general iterative metaheuristic that is used for solving combinatorial optimization problems. The heuristic is based on selected concepts from AI [32]. The rules used in *Tabu Search* are broad enough to make it applicable separately or as a guide for other heuristic procedures applied to combinatorial optimization problems [34].

A key feature of TS is that it imposes restrictions on the search process preventing it from moving in certain directions to drive the process through regions desired for investigation [35, 36]. An important component that enables TS to achieve the mentioned feature is the use of an adaptive flexible memory that distinguishes TS from other memoryless optimization heuristics. Various ways for using this memory are possible and applied for different objectives [34, 37, 36].

Tabu Search is a generalization of a local search. It searches for the best move in the neighborhood of the current solution. As opposed to local search, TS does not get trapped in local optima because it accepts bad moves if they are expected to lead to unvisited solutions [32].

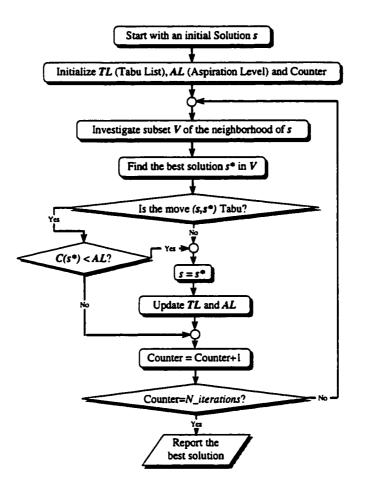

### 2.1 Basic Tabu Search Algorithm

In its very basic operation, TS works as follows. It starts with an initial solution s that is selected randomly or using any constructive algorithm. It defines a subset  $V^*(s)$  of its neighborhood N(s). The algorithm evaluates the solutions in  $V^*(s)$  and finds the best (in terms of the evaluation function) among them, call it  $s^*$  to be considered as the next solution. If the memory component (tabu list) used does not define the move leading to  $s^*$  as tabu, it is accepted as the new solution even if it is worse than the current solution in terms of the evaluation function. However, if the move leading to  $s^*$  is defined as tabu by the memory component, the solution is not accepted until it has one or more features that makes the algorithm override its tabu status to accept it. Aspiration criterion is used to check whether the tabu solution is to be accepted or not. The basic description of Tabu Search is shown in Figure 2.1 [32]. A flowchart of the basic algorithm is also shown in Figure 2.2.

| X          | : Set of feasible solutions.                                   |

|------------|----------------------------------------------------------------|

| 5          | : Current solution.                                            |

| 5*         | : Best admissible solution.                                    |

| С          | : Objective function.                                          |

| X(s)       | : Neighborhood of $s \in X$ .                                  |

| <b>V</b> * | : Sample of neighborhood solutions.                            |

| TL         | : Tabu list.                                                   |

| AL         | : Aspiration Level.                                            |

|            |                                                                |

| 1.         | Start with an initial feasible solution $s \in X$ .            |

| 2.         | Initialize tabu lists and aspiration level.                    |

| 3.         | For fixed number of iterations Do                              |

| 4.         | Generate neighbor solutions $\mathbf{V}^* \subset \aleph(s)$ . |

| 5.         | Find best $s^{\bullet} \in \mathbf{V}^{\bullet}$ .             |

| 6.         | If move s to s <sup>•</sup> is not in <b>TL</b> Then           |

| 7.         | Accept move and update best solution.                          |

| 8.         | Update tabu list and aspiration level.                         |

| 9.         | Increment iteration number.                                    |

| 10.        | Else                                                           |

| 11.        | If $C(s^{\bullet}) < AL$ Then                                  |

| 12.        | Accept move and update best solution.                          |

| 13.        | Update tabu list and aspiration level.                         |

| 14.        | Increment iteration number.                                    |

| 15.        | EndIf                                                          |

| 16.        | EndIf                                                          |

| 17.        | EndFor                                                         |

| ×(+        |                                                                |

Figure 2.1: Algorithmic description of tabu search (TS).

Figure 2.2: Basic tabu search algorithm flowchart.

### 2.2 Tabu Search Parameters

### 2.2.1 Candidate List

Examining all neighbors of the current solution is impossible in case of large neighborhoods. For this reason, a *candidate list*, which contains only a subset of all possible moves from the current solution, is used to select the next move to be made. It can be constructed by making random moves from the current solution.

Various strategies for constructing and examining candidate lists are given in [37, 38]. Some of these are:

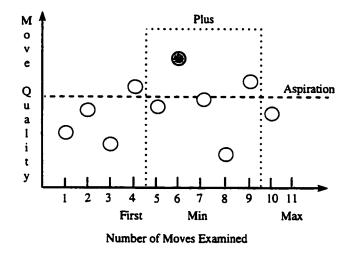

- Aspiration Plus: In this strategy, moves from the current solution are examined until an empirically determined threshold of quality is achieved by a move. The strategy then continues for *plus* more moves. The best move among all examined ones is chosen as the new solution. In order to make sure that neither too few nor too many moves are tested, two limits *Min* and *Max* are put on the number of moves to be tested. The values for *Min* and *Max* are also empirically determined. The operation of this strategy is shown in Figure 2.3. As shown in the figure, moves are tried until a quality greater than 'aspiration' is found. A number of additional moves between the *Min* and the *Max* values is examined and the best is taken.

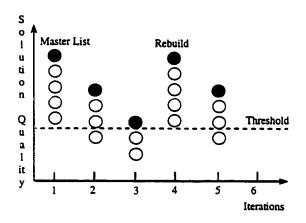

- Elite Candidate List: In this strategy, a master list is built by examining a large number of moves and selecting the k best moves among them, where k is a parameter of the implementation. At each iteration, the current best move from the master list is chosen. This continues until the quality of the move becomes less than a case-dependent threshold. At that point, a new master list is constructed and the process repeats. The strategy relies on the concept that good moves might have a good effect if not on the current solution, then on the coming ones. The operation of this strategy is shown in Figure 2.4. The master list

Figure 2.3: Aspiration plus strategy.

shown in the figure is constructed first. The best moves in that list are made one after another. When the next move to be made leads to a solution of a quality worse than the threshold, the list is rebuilt and the process continues.

Figure 2.4: Elite candidate list strategy.

• Successive Filter Strategy: This strategy tries to improve the search efficiency by examining the effects of separate components of the move

operation on the solution quality. A single component of the operation is considered at a time and the best moves with respect to that component are chosen to join the candidate list. By doing this, a smaller set of possible combinations of changes are to be examined. For example, if several criteria are to optimized by the move, moves improving a criterion at a time join the candidate list successively.

• Sequential Fan Candidate List: This strategy is most suitable if parallel processing is used to construct the list. It works by generating p best alternative moves. Then a stream of moves is constructed from each of these moves. Again the best p moves of each stream are considered. The overall p best complex moves among all examined are the candidates to join the list. p and the depth of the operation are casedependent. The operation of this strategy is shown in Figure 2.5. As shown in the figure, p moves are made first. From those moves, streams of moves are tried and only p streams of moves are maintained.

Figure 2.5: Sequential fan candidate list strategy.

• Bounded Change Candidate List: In this strategy, the domain of moves is restricted such that no move is accepted if it causes a change that exceeds a certain limit in a given component of the solution. Such

a strategy allows intensifying the search in a specific area of the search space if the designer expects it to be a promising area.

### 2.2.2 Moves and Move Attributes

In order to construct the candidate list, neighbor solutions must be generated. These solutions are generated from the current solution by applying what is called a *move*. Swapping two elements in the solution configuration can be considered as a move. It can also be taken as dropping some edges from the graph representing the current solution (or adding some edges). A move can be composed of multiple modifications.

In order to utilize the memory concept employed by *Tabu Search*, the move attributes (or the reverse move attributes) are to be stored in a data structure that corresponds to the memory. Storing complete solutions is not feasible when the solution representation is large or complex. The infeasibility is in the storage required and the time needed for future manipulations. A list of possible attributes to be stored in the memory could be:

- Complementing the value of a selected binary variable  $x_i$  that represents a component of the current solution.

- Having a change in the cost that is equivalent to Cost(s<sup>\*</sup>) Cost(s), where s<sup>\*</sup> is the new solution and s is the current solution.

- Another function that depends on the problem under investigation might be used as basis for the difference mentioned above.

- Any combination of the above can also be used as an attribute [32, 39].

#### 2.2.3 Evaluation Function

The whole process of *Tabu Search* Algorithm is performed in order to minimize/maximize a given function while satisfying given constraints of the solution. The targeted function is called *Cost Function* or *Evaluation Function*. This cost might be the implementation cost like the interconnection length and overall area or the operation cost like the critical path delay as in the case of VLSI placement problem.

The cost function might have one or multiple objectives to minimize (or maximize) simultaneously. It might also minimize one variable under some constraints of another according to the user specification and application.

#### 2.2.4 Tabu List

At any given point of time during the operation of the algorithm, there are n possible directions for future investigation of the search space, where n is the number of possible moves at that point and many directions might be overlapping. One of the objectives of *Tabu Search* is to prevent cycling back to previous solutions. Another objective might be to stay around the same neighborhood of solutions that have specific features (intensification). Moving to diverse solutions from the current one might be a third objective during (diversification) phase. In order to achieve these objectives, TS should use some sort of history.

For the purpose of not cycling back to recently visited solutions, reverse attributes of the accepted moves are made tabu for a specific number of coming iterations called Tabu Tenure or Tabu List size. To implement this, a queue of attributes can be used, or, an array whose entries are the remaining iterations during which the attribute will remain tabu where the array size is the number of attributes.

Tabu tenure depends primarily on the size of the problem as well as the objective of the search whether it is intensification, diversification or normal continuation of the search process. Generally, the size can be determined using experimental runs.

If the objective varies during various stages of the search, then a dynamic tabu list (variable tabu tenure) can be used [37]. The concept of a variable tabu tenure showed better performance in general even when the objective of the search was constant as in [36, 40, 41]. In case of a variable tabu tenure, empirically determined bounds are used to control the change in the tenure.

#### 2.2.5 Aspiration Criteria

Saving on storage and computation time achieved by storing only attributes of accepted moves is paid for in the accuracy. By preventing the complement of an attribute to occur right after that attribute, cycling back is prevented. However, preventing the reverse attribute of the  $n^{th}$  recent move might cause a state that was never encountered to be considered *tabu*. Of course, this contradicts with the algorithm initial objective that is defined as trying to investigate the unseen parts of the search space. In order to give the algorithm a chance of not loosing good solutions because of this misuse of the tabu list, an aspiration criterion is used. This criterion is used to override the tabu status of a specific move attribute if the move leads to a solution that is desirable as far as the objective of the search at that stage is concerned.

The following are some of the possible aspiration criteria and their corresponding objectives:

1. Global Objective Aspiration: If the objective of the search is to continue normal operation searching for the best solution, then the aspiration criterion can be taken as achieving a cost that is better than all of those solutions encountered so far.

$$AC = Cost(s^{\bullet}) < Best\_Cost$$

(2.1)

2. Regional Objective Aspiration: The previous aspiration criterion can take a regional shape if the target is the best solution in the current neighborhood of size R.

$$AC = Cost(s^*) < Best\_Cost(R)$$

(2.2)

3. Aspiration by Search Direction: If the current objective of the search is to traverse the search space towards a local optimum i.e., intensification, then aspiration by search direction can be used. In this case, if the tabu move is improving i.e.,  $Cost(s^*) < Cost(s)$  and the reverse of that move that caused the tabu status was also improving then the solution is considered to be satisfying the aspiration criterion. To implement this, a bit per entry in the tabu list can be used. If the move accepted is improving, the bit is set to 1. When the reverse attribute is found tabu but improving the bit is checked. If it is 1, the attribute is accepted.

$$AC = (improving == 1)\&\&(Cost(s^{-}) < Cost(s))$$

$$(2.3)$$

4. Aspiration by Influence: If the current objective of the search is to go to a diverse point in the search space, then aspiration by influence can be used. In this method, a tabu move is considered to be satisfying the aspiration criterion if its reverse attributes that established the tabu status had a low influence and occurred before a considerable change in the current solution. To implement this aspiration technique, a bit per entry in the tabu list is used to represent influence. If the accepted attribute causes a change greater than L in the cost of the current solution, then influence bit is set. An array *Latest* of size 2 is used to store the latest iteration that had influence of level 0 and 1.

$$AC = ((influence(e) == 0)\&\&(tabu\_start(e) < latest(L)))$$

(2.4)

where e is the tabu attribute and  $tabu\_start(e)$  is the iteration where e joined the tabu list. This can be generalized to include various levels of influence by increasing that size of the array Latest and satisfying that influence(e) < L such that  $tabu\_start(e) < Latest(L)$  [32, 37, 39].

### 2.3 Tabu Search Classes

According to the way memory is used, *Tabu Search* can be classified into three categories:

- 1. Short Term Memory Tabu Search

- 2. Intermediate Term Memory Tabu Search

- 3. Long Term Memory Tabu Search

#### 1. Short Term Memory Tabu Search

The Tabu Search algorithm where a list of attributes of n recently accepted moves is maintained to prevent accepting any of them in the next iteration until and unless it satisfies the aspiration criterion is called short term memory class. It is called so because it uses the memory as a recent short history to prevent cycling back to visited points. This class shows good performance where the search space is not of huge size. Otherwise, it might be trapped in a specific proximity of the search space.

#### 2. Intermediate Term Memory Tabu Search

The main function of the intermediate term memory tabu search is to intensify the search by aggressively forcing some common features of good solutions in the new solution.

The algorithm records the common features between the most recent best m solutions or the most recent m local optima and forces the new solution to satisfy those features in order to be considered for acceptance. A move leading to a solution that does not satisfy these features may not be included in the candidate list.

#### 3. Long Term Memory Tabu Search

It might be the objective during some stage of the search process to move to a diverse point in the search space. The motivation behind this is the observation that the search has been trapped in a certain region i.e., several features have been repeated in most of the recent solutions. It might also be that the search has not been giving good results after running for a comparatively long time. A third motivation, in case of parallelization, might be to make sure that a set of processors are not searching in the same areas of the search space. One of the distinct features of tabu search is the fact that its memory component can be modified such that it supports this objective by making deterministic diversification steps. The frequently repeating features could be avoided by storing them in a special memory component.

In the diversification stage, the evaluation function can be modified to include a term that penalizes frequent moves as follows

$$F(s^{*}) = \begin{cases} Cost(s^{*}) & \text{if } Cost(s^{*}) \leq Cost(s) \\ Cost(s^{*}) + \alpha \times Freq(M(s^{*})) & \text{if } Cost(s^{*}) > Cost(s) \end{cases}$$

(2.5)

where F is the evaluation function,  $\alpha$  is a positive constant that depends on the range of the evaluation function values, the number of iterations, the history, etc. The value of  $\alpha$  should be chosen such that cost and frequency are appropriately balanced. M is the move attribute that leads to the new solution  $s^-$ .

#### 2.4 Summary

In this chapter, Tabu Search as a stochastic iterative heuristic to be applied to VLSI placement was presented. The basic algorithm was introduced. Various parameters of Tabu Search were discussed. Candidate List strategies were presented and explained. Different moves and move attributes were discussed. The evaluation function and the Tabu List were mentioned. Aspiration Criteria of different types were presented. Finally, Tabu Search classes and their objectives were discussed.

### Chapter 3

### Literature Review

Section 3.1 of this chapter reviews the heuristics applied to VLSI placement problem. In Section 3.2, the application of *Tabu Search* to VLSI placement problem is reviewed in the literature. In Section 3.3, the parallelization of Tabu Search algorithm is addressed.

### 3.1 Heuristics Applied to VLSI Placement

Heuristics that have been applied to placement problem include Maximum Connectivity strategy which is a constructive deterministic strategy that works by placing a cell at each iteration. The selected cell for placement should have the maximum connectivity to the already placed cells. The complexity of this strategy is  $O(n^3)$  [1]. The main disadvantage of it is that it can be easily trapped at a local optimum.

Another constructive deterministic heuristic that has been applied to placement is called *Min-cut Placement* [9, 22, 23]. This algorithm is based on the observation that minimizing the number of horizontal and/or vertical lines that are cut when the layout is partitioned in gate-array placement or standard cell placement improves the routability and reduces the number of feedthrough cells. This heuristic suggests partitioning the layout at each step and dividing the cells between the partitions such that the number of lines cut by the partitioning is reduced. This heuristic also suffers from the local view of an optimum solution rather than a global view.

Force-directed Placement is a technique that belongs to the class of deterministic iterative heuristics. This heuristic starts from an initial solution and then starts taking a cell at a time and moving it to a more appropriate location according to its connectivity [24].

Iterative stochastic heuristics have been giving better results than constructive deterministic ones in placement problem. A reason for that is the global view of the optimum solution and the ability to escape from local optima through the controlled randomness introduced in these heuristics.

Among the iterative stochastic heuristics applied to placement is Simulated Annealing [25, 26, 27]. Simulated Annealing starts from an initial solution and keeps modifying the solution with random moves. It accepts a large portion of moves at the beginning of the search and then it becomes restricted to accept only improving moves towards the end.

Another heuristic which was applied to placement is *Genetic Algorithm* [28, 29]. It starts from a set of initial solutions called *initial population*. It then tries to combine features from good solutions to come up with better generations of solutions.

Simulated Evolution is another heuristic that was applied to placement [30, 15]. It depends on goodness of particular cells. At each iteration, a group of cells that are relatively badly placed are selected to be moved to better locations.

A common feature between all of the mentioned stochastic iterative heuristics is that they are memoryless. They don't utilize any memory structure to look at previous moves. On the other hand, *Tabu Search*, which was also applied to placement [31, 11], utilizes some memory to make decisions at various stages of the search process. This memory structure can be used to prevent reverses of recent moves by putting their attributes in a tabu list such that the algorithm does not cycle back to solutions that have been already investigated. It can be used to force the new solution to have different features than previously seen solutions (*diversification*). It can also be used to force the new solution to have some features that have been seen in recent good solutions (*intensification*). It is up to the user to specify what it is that is required from *Tabu Search* at various stages of the search process.

### **3.2 Tabu Search in VLSI Placement**

VLSI Placement is an NP-hard problem as discussed earlier. Tabu Search is a heuristic that was invented to be applied to NP-hard problems.

In [42], performance driven VLSI placement with global routing algorithm for Macro-Cell placement was presented. Quad partitioning approach was applied using *Tabu Search* Algorithm. The objective of the implementation was to minimize the delay.

Their algorithm obtains a placement for macro-cell layout with consideration of global routing. The overall delay is the main goodness criterion they used for a given solution. The overall delay is computed as the summation of the module delays and the interconnection delays in the path. Quad-partitioning is applied using *Tabu Search* and used weighted sum to find the overall cost of the solution considering imbalance of area usage, number of edges crossing boundaries, imbalance of edges passing boundaries, the largest net delay and the number of long paths in a region. Their results showed improvement in delay and run time compared to [43].

In [44], Tabu Search was applied to capacitor placement problem in a radial distribution system. Their design considered operating constraints of capacitor placement problem, load growth, the upper and lower bound constraints of voltage at different load levels, etc. The objective was to minimize the investment cost of capacitors and the system energy loss. The algorithm they applied was short term memory tabu search and the candidate list was generated randomly.

Their results showed improvements in energy and voltage loss. Their results were compared to previous results generated using Simulated Anneal-

ing [45, 46, 47] and the observation was that *Tabu Search* achieved the same quality of solution in much less time.

In [48], Short term memory tabu search was applied to placement of analog LSI chip designs. The objective was to minimize the overall interconnection length and layout area under the constraint of making routing an easy next step. *Tabu Search* was applied separately in one experiment and imposed on Genetic Algorithm in another experiment. Short term memory tabu search did not show good results when compared to Genetic Algorithm with dynamic adjustment of mutation rate.

In [11], Tabu Search was applied to quad-partitioning VLSI Macrocell placement problem. The objective was to minimize the interconnection length which in turn minimizes the delay. The results showed that using fuzzy cost function provided up to 43% improvements in the cost.

The cost function applied was a fuzzy cost function that included delay and interconnection length. The results were compared to [42] and [43] and significant cost improvement over both was observed.

### **3.3 Tabu Search Parallelization**

Saving in time to achieve the same quality of solution is the main goal behind distributing *Tabu Search* on a set of processors. Another goal can be achieving a better solution quality in the same time. The ideal improvement in investigation time is given by the following formula

$$ideal\_speedup = \frac{T_n + T_u}{T_n/p + T_u}$$

(3.1)

where  $T_n$  is the sequential time for achieving the computation to be parallelized,  $T_u$  is the non-parallelizable part and p is the number of processors [34]. One way of parallelization is to distribute the component that requires the most CPU time. In *Tabu Search*, this is neighborhood examination component. If TS behaves like a memoryless algorithm i.e., if the interarrival of a solution of a specific quality is exponentially distributed, then the probability of providing the desired solution quality during time t is given by

$$p(t) = 1 - e^{-\lambda t} \tag{3.2}$$

with  $\lambda > 0$ . In this case, it is *probabilistically* equivalent to perform one search for time t or p searches for time t/p [49]. If this is the case, many independent searches can be performed starting each one from a different initial solution.

According to Toulouse et. al taxonomy [37], a possible parallelization strategy of *tabu search* is to distribute the component that requires the most CPU time on available machines (functional decomposition). Another strategy is to perform many independent searches (multi-search threads). A third strategy, is to decompose the search space among processes (domain decomposition). A different taxonomy by Crainic et. al., classifies TS on the basis of three dimensions. The first dimension is control cardinality where the algorithm is either 1-control or p-control. In a 1-control algorithm, one processor executes the search and distributes numerically intensive tasks on other processors. In a *p*-control algorithm, each processor is responsible for its own search and the communication with other processors. Control and communication type is the other dimension where the algorithm can follow a rigid synchronization (RS), a knowledge synchronization (KS), a collegial (C), or a knowledge collegial (KC) strategy. The third dimension is search differentiation where the algorithm can be single point single strategy (SPSS), single point different strategies (SPDS), multiple points single strategy (MPSS), or multiple points different strategies (MPDS) [37].

In [50], a mechanism for parallelizing *tabu search* by dividing neighborhood examination among a number of slaves for solving flow shop sequencing problem was presented. A master process is used to send an initial solution to all slaves. At each iteration, each one of the slaves examines part of the neighborhood and reports the best move to the master process. The master process chooses the best move among all and sends it to all slaves as the next move to be performed if it is not tabu. The process then continues for a fixed number of iterations or until no improvement is observed for a given number of iterations. The algorithm presented uses *domain decomposition* strategy. It is a *1-control*, *RS*, *SPSS* algorithm.

Garcia et. al [51] presented a parallel implementation of tabu search for vehicle routing problem. In their work, a master process applies Tabu Search and calls slaves which (with the master) investigate the neighborhood of the current solution. Each process identifies its best move and sends it to the master. The master process selects a set of the best moves and broadcasts them to all slaves. Processes exchange only sequence of moves rather than exchanging complete solutions which causes redundant communication overhead. The algorithm uses domain decomposition strategy. It is a 1-control, RS, SPSS algorithm.

In [52, 53], evolution principles were included to improve parallel Tabu Search. In the given strategy, short term memory *tabu search* was applied on a set of machines. After a specific number of iterations, each machine exchanges best solutions with its neighbors. At each machine, If the received solution is better than the local best, it replaces it. The algorithm uses *multi-search threads* strategy. It is a *p-control*, *C*, *MPSS* algorithm.

Niar and Freville [54] proposed a parallel Tabu Search algorithm for the 0-1 multidimensional knapsack problem. In their algorithm, they had a master process that generates initial solutions for slaves. The initial solution for process *i* is taken as its previous best solution except in two cases: (1) if the quality of the best solution is less than a fraction  $\alpha$  of the overall best solution or, (2) if the best solution of process *i* has not been modified for a given number of iterations. For each slave, the master generates a different strategy where the strategy is represented by the tabu list size, the number of local iterations and the number of successive drops at each iteration. The algorithm uses *multi-search threads* strategy. It is a *p-control*, *RS*, *MPDS* algorithm. In [55], a parallel tabu search algorithm for voltage and reactive power control in power systems was presented. Two schemes were implemented in that work. In the first one, the neighborhood was decomposed for parallel processing at each iteration. This is a domain decomposition strategy. The algorithm is 1-control RS SPSS search. In the second scheme, tabu search was replicated with various tabu lengths at different processes. This is a multi-search threads strategy. The algorithm is p-control, RS, SPDS search.

In this work, tabu search algorithm is parallelized on a network of heterogeneous stations using Parallel Virtual Machine (PVM) [33]. The proposed algorithm uses two strategies simultaneously. It parallelizes the candidate list construction and examination at the low level (functional decomposition), and also coordinates several concurrent searches synchronously (multi-search threads). The algorithm also imposes some restriction on processes such that domain decomposition is probabilistically applied. The algorithm falls into p-control class at the higher parallelization level and into 1-control class at the lower level. It belongs to the rigid synchronization category on the control and communication type dimension. It is a multiple points single strategy (MPSS) search on the search differentiation dimension.

#### 3.4 Summary

In this chapter, a literature review was presented for three topics. The heuristics applied to VLSI placement problem were discussed. The application of *tabu search* to VLSI placement problem was reviewed. Parallelization of *tabu search* algorithm was introduced and some previous work addressed. The proposed parallel algorithm was identified.

### Chapter 4

# Parallel TS for VLSI Standard-Cell Placement

In this chapter, we describe our parallelization of the TS algorithm for VLSI standard-cell placement. First, we present a sequential version of TS for the placement problem in Section 4.1. Section 4.2 addresses parallelization of the algorithm. Applying the algorithm in a heterogeneous environment is presented in Section 4.3. Diversification of the search in the algorithm is investigated in Section 4.4.

### 4.1 Proposed Tabu Search Algorithm

As an essential starting step for this work, *tabu search* was applied in its very basic operation to VLSI standard-cell placement.

The algorithm starts by reading a randomly generated initial solution and storing it in a data structure that stores each cell with its size, the row where it is initially located and its index in the row i.e., the number of cells placed before it in the same row. It then starts from that solution as an initial solution s. It considers it as the best solution and sets the aspiration level to its cost. For a fixed iteration count, that is proportional to the number of cells in the circuit, the algorithm runs the simple short-term memory tabu search.

The algorithm constructs a candidate list by examining a number of moves. A move is taken as swapping the locations of two cells that are generated randomly. The move attribute stored in the tabu list is the numbers of the swapped cells. The change in the cost is computed after relocating the two cells.  $N_v$  cells are tried for swapping and the best swap is considered for the next move. A compound move is made where  $N_v$  other moves are tested for d times, where d is the desired move depth, and the best move is taken each time.  $N_v$  and are functions of the circuit size. By doing this, the algorithm applies Sequential Fan Candidate List Strategy with one stream (see Section 2.2.1). When the algorithm is parallelized it will be generating p streams, where p is the number of processes investigating the neighborhood of the current solution s. If the move gives improvement over the cost of the current solution, then the process does not need to proceed further in depth. It just considers the reached solution as the best it found and gives it to the algorithm as the next neighbor of the current solution.

If any of the cells to be swapped has been moved in the recent history, then the move is considered *tabu*. The algorithm checks if the move is tabu by considering only the two cells that were swapped first in the compound move. If the move is found tabu, the *aspiration criterion* is checked. If the move satisfies it, it is accepted. Otherwise, it is rejected and the process repeats.

The *tabu tenure* (tabu list size) used is a parameter of the circuit size. An array of size equal to the number of cells in the circuit is used. Whenever a swap is accepted, the swapped cells entries in the array are updated with the value of the *tabu tenure*. All other non-zero entries are decremented by one. When a tabu status of a cell is to be checked, its entry in the array is read. If it is non-zero, then the associated move is considered tabu.

The aspiration criterion used in the algorithm is Aspiration by Objective (see Section 2.2.5). If the tabu move leads to a solution whose cost is better than all of those seen so far, then the algorithm overrides the tabu status

and the move is accepted. This is a quite restricted criterion especially for huge search spaces. It is to be relaxed to a *Regional Aspiration by Objective* when the algorithm is parallelized as discussed in Section 4.2.

The cost function used by the algorithm is the same as the one proposed by Ali [15]. It computes the wire length, the circuit delay, and the width of the layout. It then computes the overall cost using *Fuzzy Goal Based Cost Measure*. The optimum values for wire length, delay and width are computed for each circuit as explained in Section 1.3.4. The goal values are taken as 2.0-3.0, 3.0-4.0, and 1.1-1.5 for wire length, delay and width respectively. It was experimentally found that the best combination of weights for weighted sum cost computation is 0.6, 0.1 and 0.3 for wire length, delay and width respectively [15]. Those weights are used in the experiment where weighted sum is applied.

### 4.2 Parallelization of the Algorithm

Tabu search is parallelized on a network of stations using PVM (see Appendix A). The purpose of parallelization in this work was saving some of the time required to achieve a certain solution quality (search speedup) and to achieve a better quality of solution in the same search time.

The algorithm is parallelized on two levels simultaneously. The higher one is at the *tabu search* process level where a master starts a number of *Tabu Search Workers* (*multi-search threads*) and provides them with the same initial solution. The lower level is the *Candidate List* construction level where each TSW starts a number of *Candidate List Workers* (*functional decomposition*). The paradigm of the parallel algorithm is shown in Figure 4.1. The algorithm falls into *p-control* class at the higher parallelization level and into *1-control* class at the lower level. It belongs to the *rigid synchronization* category on the *control and communication type* dimension. It is a *multiple points single strategy* (MPSS) search on the *search differentiation* dimension because TSWs diversify from the initial solution at each global iteration using the diversification scheme proposed by Kelly et. al [56] (see Section 4.4).

Figure 4.1: Paradigm of tabu search parallel implementation.

Because of memory component used by TS, the algorithm has to exchange information other than the best solution. This is unlike memoryless iterative algorithms such as SA, GA, and SE where best solution is all that is required to be exchanged. The algorithm proposed communicates the best solution as well as the associated *tabu list* between the master and the TSWs.

The parallel algorithm works as follows. The master starts the process by initializing the data structures, the tabu list and the aspiration level. It also reads the initial solution from a file. After that, it starts a number of Tabu Search Workers (TSWs) to perform Tabu Search starting from the given initial solution. The implementation has an option to start from the initial solution or from a previous best solution. It sends all parameters of the search to the workers and tells each worker about a range of cells within which that worker should diversify from the initial solution (diversification is discussed in Section 4.4). It broadcasts the same initial solution to all workers. Each TSW then initializes the aspiration level and the tabu list. After that it performs a diversification step. The TSW then starts a number of Candidate List Workers to investigate the neighborhood of the current solution. It sends the parameters and the initial solution to each CLW. It also gives each CLW a range of cells to search the neighborhood with respect to those cells as follows. The TSW divides the number of cells n by the kCLWs it has started. Each CLW gets the n cells of the circuit and is informed about the  $\frac{n}{k}$  cells belonging to its range.

For every move it makes, the CLW has to choose one of the cells from its range and the other as any other cell. The probability that it take the other cell from its range is  $\frac{1}{k}$ . The probability that two *Candidate List Workers* performing the same move is the probability that the 1<sup>st</sup> CLW chooses its second cell as a specific cell from the range of the other CLW and the other CLW does the same. The probability that two CLWs select the same two cells is given by  $\frac{1}{n-1} \times \frac{1}{n-1} = \frac{1}{(n-1)^2}$ . The probability that more than two CLWs select the same two cells is 0.