## A Framework for the VLSI Implementation of Systolic Tree Based Data Structure

by

Mohammed Abdul Aziz Khalid

A Thesis Presented to the

#### FACULTY OF THE COLLEGE OF GRADUATE STUDIES

### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

#### DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

#### **MASTER OF SCIENCE**

In

#### **COMPUTER ENGINEERING**

September, 1994

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

• -

Order Number 1359369

A framework for the VLSI implementation of systolic tree based data structures

Khalid, Mohammed Abdul Aziz, M.S.

King Fahd University of Petroleum and Minerals (Saudi Arabia), 1994

.-

### A FRAMEWORK FOR THE VLSI **IMPLEMENTATION OF SYSTOLIC TREE BASED DATA STRUCTURES**

BY

#### Mohammed Abdul Aziz Khalid

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

# **MASTER OF SCIENCE**

In

COMPUTER ENGINEERING

SEPTEMBER 1994

# **KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS** DHAHRAN, SAUDI ARABIA

This thesis, written by

### Mohammed Abdul Aziz Khalid

under the direction of his Thesis Advisor, and approved by his Thesis committee, has been presented to and accepted by the Dean, College of Graduate Studies, in partial fulfillment of the requirements for the degree of

**MASTER OF SCIENCE IN COMPUTER ENGINEERING**

Thesis Committee:

Sadiar Jait . M

Chairman (Dr. Sadiq M. Sait)

Chairman (Dr. Habib Youssef)

Member (Dr. M. S. T. Benten)

Member (Dr. Mostafa Abd-El-Barr)

· E/N/19 3.

Department Chairman

Dr. Ala H. Rabeh Dean, College of Graduate Studies

Hugust 20, 1994 Date:

23

Dedicated to

# My Grandmother, Parents,

## **Brothers and Sisters**

#### Acknowledgment

i

Praise to the Almighty Allah Who gave me the courage and patience to carry out this work. I am happy to have had a chance to glorify His name in the sincerest way through this small accomplishment and ask Him to accept my efforts. May He guide us and the whole humanity to the right path (Aameen).

Acknowledgement is due to King Fahd University of Petroleum and Minerals, Dhahran, for providing opportunity to carry out this research work.

My deep appreciation goes to my major thesis advisor Dr. Sadiq M. Sait for his constant help, guidance and the countless hours of attention he devoted throughout the course of this work. He was always kind, understanding and sympathetic towards me. Working with him was indeed a wonderful and learning experience which I thoroughly enjoyed. I express my thanks to my co-advisor Dr. Habib Youssef and committee members Dr. M. S. T. Benten and Dr. Mostafa Abd-El-Barr for their interest, cooperation, advice and constructive criticism.

I am also indebted to the department chairman, Dr. Samir Abdul-Jauwad

and other faculty members for their support.

Thanks are due to my father, younger brother Abed for their understanding and support, special thanks to my grandmother *Ammajan*, and my mother for their relentless attention throughout my academic career, thanks to my sisters and younger brother Rashed who deserve a lot of encouragement and hardwork.

Lastly, I wish to thank fellow graduate students and friends (in alphabetical order) Ahmed Mohiuddin, Asaf, Feroze, Ghouse, Haroon, Idrees, Javeed, Masood-Ul-Hassan, Mohammed, Naseer, Nisar, Sajjad, Sami, Shahid Akther, Shahid Tanvir, Waseem Akther and all my friends on the campus from whom I learned a lot and who made the long work hours pleasant.

# Contents

.

٠

|   | Ack  | nowledgement          | i  |

|---|------|-----------------------|----|

|   | List | of Figures            | vi |

|   | Abs  | tract (English)       | ix |

|   | Abs  | tract (Arabic)        | x  |

| 1 | Intr | oduction              | 1  |

|   | 1.1  | Introduction          | 1  |

|   | 1.2  | Systolic systems      | 4  |

|   | 1.3  | Thesis outline        | 6  |

| 2 | Lite | erature review        | 9  |

|   | 2.1  | Introduction          | 9  |

|   | 2.2  | High level synthesis  | 10 |

|   | 2.3  | Binary tree embedding | 11 |

.

|   |     | <b>2.3.1</b> H-trees                             |  |

|---|-----|--------------------------------------------------|--|

|   |     | 2.3.2 Hexagonal tree embedding                   |  |

|   |     | 2.3.3 Tile-based tree embedding                  |  |

|   | 2.4 | <b>Conclusion</b>                                |  |

| 3 | Des | ign Methodology 18                               |  |

|   | 3.1 | Introduction                                     |  |

|   | 3.2 | Operation of a queue                             |  |

|   | 3.3 | The structural model of a queue node             |  |

|   | 3.4 | Operation of a stack                             |  |

|   | 3.5 | The structural model of a stack node             |  |

|   | 3.6 | Embedding of binary-tree into tile-based schemes |  |

|   | 3.7 | Structure of basic modules                       |  |

|   |     | <b>3.7.1</b> Five and six level trees            |  |

|   |     | 3.7.2 Tree larger than six levels                |  |

|   | 3.8 | Evaluation of proposed tree layout scheme        |  |

|   |     | <b>3.8.1</b> Area efficiency                     |  |

|   |     | <b>3.8.2</b> Propagation delay                   |  |

|   |     | <b>3.8.3</b> Maximum edge length                 |  |

|   | 3.9 | Buses in the layouts                             |  |

|   | 3.1 | 0 Conclusion                                     |  |

| 4 | Imp | lementation in VLSI                            | 42  |

|---|-----|------------------------------------------------|-----|

|   | 4.1 | Introduction                                   | 42  |

|   | 4.2 | RTL model for stack and queue                  | 42  |

|   |     | 4.2.1 RTL model for queue                      | 43  |

|   |     | <b>4.2.2</b> RTL model for stack               | 44  |

|   | 4.3 | Layouts of systolic-tree based queue and stack | 51  |

|   |     | 4.3.1 Placement                                | 56  |

|   |     | <b>4.3.2</b> Routing                           | 58  |

|   | 4.4 | Layout of systolic tree-based queue            | 59  |

|   | 4.5 | Layout of systolic tree-based stack            | 68  |

|   | 4.6 | Conclusion                                     | 68  |

| 5 | Dis | cussion and Conclusions                        | 75  |

|   | Ар  | pendix A                                       | 78  |

|   | Ар  | pendix B                                       | 82  |

|   | Ap  | opendix C                                      | 95  |

|   | Bi  | bliography                                     | 103 |

v

# List of Figures

| 1.1 | An overview for DA system for generating layout from RTL specifi-    |    |

|-----|----------------------------------------------------------------------|----|

|     | cation and its verification [25].                                    | 3  |

| 1.2 | Various systolic array configurations.                               | 7  |

| 2.1 | A five-level tree embedding in H-tree layout.                        | 13 |

| 2.2 | The regular embedding scheme for hexagonal array [8]                 | 15 |

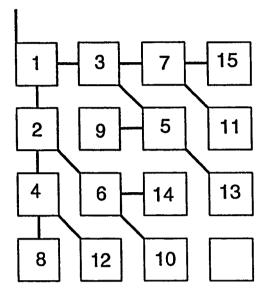

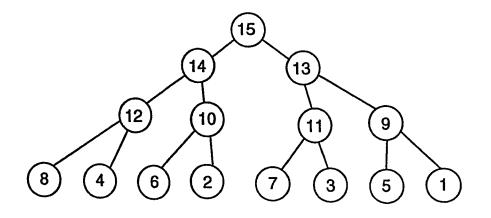

| 2.3 | Embedding of 15 node tree in $4 \times 4$ square array of processors | 16 |

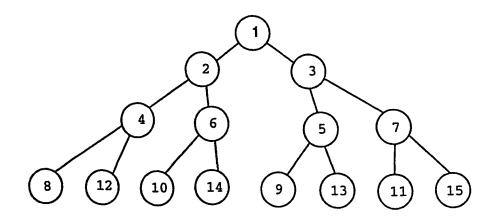

| 3.1 | Data distribution of the queue after 15 consecutive inserts          | 20 |

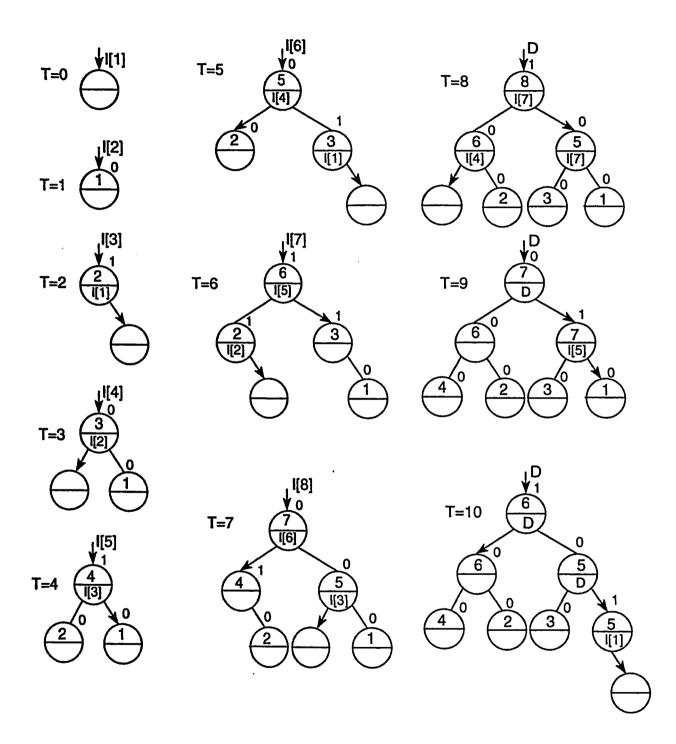

| 3.2 | The configurations of queue under a sequence of instructions         | 21 |

| 3.3 | Behavioral model of a node of a systolic-tree based queue            | 23 |

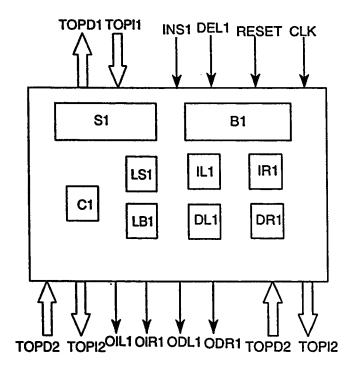

| 3.4 | Block diagram of a queue node                                        | 25 |

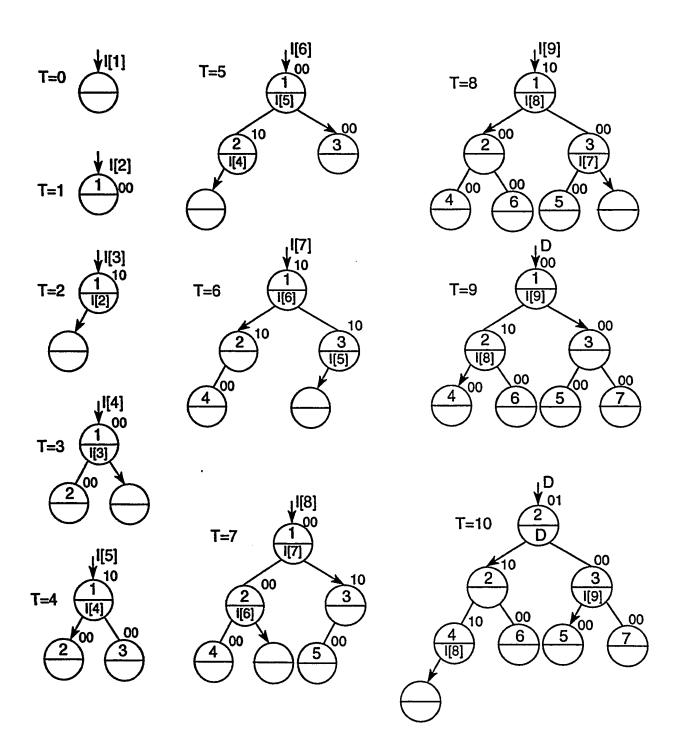

| 3.5 | Data distribution of the stack after 15 consecutive push operations  | 27 |

| 3.6 | The configurations of stack under a sequence of instructions         | 28 |

| 3.7 | Behavioral model of a node of a systolic-tree based stack            | 30 |

| 3.8 | Block diagram of a stack node.                                       | 31 |

| 3.9  | The structure of basic modules used for embedding trees with level       |    |

|------|--------------------------------------------------------------------------|----|

|      | greater than 4 [31]                                                      | 33 |

| 3.10 | A five-level tree embedding using two basic modules [31]                 | 35 |

| 3.11 | A six-level tree embedding using four basic modules [31]                 | 36 |

| 3.12 | A seven-level tree embedding using four basic modules [31]               | 37 |

| 4.1  | AHPL description of systolic tree-based queue                            | 45 |

| 4.2  | COMSEC file for AHPL description.                                        | 46 |

| 4.3  | Output of simulation at RT level for one node systolic tree-based queue. | 47 |

| 4.4  | AHPL description of systolic tree-based stack.                           | 48 |

| 4.5  | COMSEC file for AHPL description.                                        | 49 |

| 4.6  | Output for one node systolic tree-based stack                            | 50 |

| 4.7  | First part of netlist description for one node queue                     | 52 |

| 4.8  | Second part of netlist description for one node queue                    | 53 |

| 4.9  | First part of netlist description for one node stack                     | 54 |

| 4.10 | Second part of netlist description for one node stack                    | 55 |

| 4.11 | Layout of one node.                                                      | 61 |

| 4.12 | 2 Transistor-level simulation of one node of queue                       | 62 |

| 4.13 | 3 Layout of three node queue                                             | 63 |

| 4.14 | 4 Transistor-level simulation of three node queue.                       | 64 |

| 4.1  | 5 Layout of fifteen node queue.                                          | 65 |

| 4.16 | Transistor-level simulation of seven node queue | ; |

|------|-------------------------------------------------|---|

| 4.17 | Layout of sixty three node queue                | 7 |

| 4.18 | Layout of one node stack                        | ) |

| 4.19 | Transistor-level simulation of one node stack   | ) |

| 4.20 | Layout of three node stack                      | I |

| 4.21 | Transistor-level simulation of three node stack | 2 |

| 4.22 | Layout of fifteen node stack                    | 3 |

| 4.23 | Transistor-level simulation of seven node stack | 4 |

.

#### Abstract

Name:Mohammed Abdul Aziz KhalidTitle:A Framework for the VLSI implementationof Systolic Tree-Based Data Structures

Major Field: Computer Engineering

Date of Degree: September, 1994

Very Large Scale Integration (VLSI) technology has provided opportunities for implementing algorithms and data structures in silicon. Many innovative designs have been proposed for the implementation of data structures in hardware. However, these designs have been presented at an abstract behavioral level. Much remains to be done in investigating the methods and strategies that employ appropriate techniques, to reduce the design turn-around time and facilitate efficient physical implementation of these designs. In this thesis, a framework for VLSI implementation of systolic tree based data structures is introduced. A layout methodology and a VLSI CAD environment that facilitate fast and efficient layout of large binary trees is described. Performance features from the layout in  $2\mu$  n-well CMOS technology are presented. In this work the layout approach used for efficient VLSI implementations of generic binary tree-based architectures is emphasized.

> Master of Science Degree King Fahd University of Petroleum and Minerals Dhahran, Saudi Arabia September, 1994

اسم الطالسب : محمد عبدالعزيز خالد عتوان الرسالة : اطار عمل للتطبيق التكاملي ذر المقياس الكبير جداً للهياكل المعلوماتيه ذات قاعدة شجرية سيستولية . التخصصيص : هندسة الحاسب الآلي . تاريخ الشهادة : يونيو ١٩٩٤م .

إن تقنية التكامل ذو المقياس الكبير جداً قدمت فرصاً حقيقية لتطبيق الخوارزميات والهياكل المعلوماتية بالسيليكون . لقد تم اقتراح الكثير من التصميمات المبدعة لتطبيق الهياكل المعلوماتية باستخدام أجهزة الحاسب الآلي . على أية حال ، فإن هذه التصميمات قدمت على مستوى تصرفي تجريدي . يتبقى الكثري مما يكن عمله من ناحية التحقق والبحث في الطرق والإستراتيجيات التي توظف طرقاً تقنية مناسبة للتقليل من الوقت اللازم لدوران التصميم وكذلك لتمهد وتسهل التظبيق الفعال لهذه التصميمات . في هذه الرسالة ، نقدم إطار عمل لتطبيق الهياكل المعلوماتية ذات القاعدة الشجرية السيستولية . هذا الإطار يتاز بفعالية الهياكل المعلوماتية والخوارزميات المناسبة للتطبيق . يقوم بهذا عن طريق اختيار ويقد ليركيب البنيوي والمخطط الإخفائي الفعال في شبكة متسامتة من المنفذات . في هذا الرسالة أيضاً نصف طريقة للعرض ويبئة تصميم مساعد بالكمبيوتر لتكامل ذو مقياس كبير جداً مما يسهل عملية العرض الفعال والسريع لأشجار زوجية كبيرة . خصائص التأدية من عرض تقنية كالي عمهل عملية العرض الفعال هذا العمل نركز على طريقة العراض التأدية من عرض تقنية علي العرض الفعال ميا لهما المعلوم المت . هذا العمل المياز الميازة المياكل المعلوماتية والخوارزميات الماسبة للتطبيق . يقوم بهذا عن طريق اختيار عريقة للعرض ويبئة تصميم مساعد بالكمبيوتر لتكامل ذو مقياس كبير جداً عما يسهل عملية العرض الفعال والسريع لأشجار زوجية كبيرة . خصائص التأدية من عرض تقنية كالميور جلاً عا يسهل عملية العرض الفعال والسريع لأشجار زوجية كبيرة . خصائص التأدية من عرض تقنية الماليور المالة أي المالة . في هذا العمل نركز على طريقة العرض للتطبيقات المتكاملة ذات المقياس الكبير جداً للرسالة . في هذا العمل نركز على طريقة العرض للتطبيقات المتكاملة ذات المقياس الكبير جداً للرسالة . في هذا العمل نركز على طريقة العرض التأمية المائية المائية المائية المائية المائية المائية المائية . الأشجار الثنائية الخلاًةة.

> درجة الماجستير في العلوم جامعة الملك فهد لليترول والمعادن الظهران ، المملكة العربية السعودية يوتيو ١٩٩٤ م

х

# Chapter 1

# Introduction

### 1.1 Introduction

The advent of Very Large Scale Integration (VLSI) has led to the development of high performance, special purpose hardware to meet specific application requirements. This technology has given us the opportunity to implement algorithms and data structures on integrated circuits. Some of the desirable features of architectures which facilitate implementation in VLSI include modularity, regularity, and local inter-connectivity. Architectures having systolic nature, exhibit the above mentioned characteristics. Beside these, systolic architectures have strong parallelism thus yielding higher performance than conventional Von Neumann architectures. These architectures have been proposed for several applications, for example, in digital signal processing, matrix operations and in implementation of data structures [4, 30]. The architecture of a systolic array is characterized by the architecture of the processor, the size of the array and the inter-connectivity of the processors. The architecture is generally described at the behavioral level. Most systolic architectures are either 1-D or 2-D arrays. Some efficient systolic architectures are also based on tree-architectures and are commonly known as systolic trees. In systolic trees, the processors are nodes of the tree, and the edges correspond to the communications links between processors. Examples of data structures implemented as systolic trees are stack, queue, dequeue, priority queue, dictionary machine, etc. [3, 4, 17].

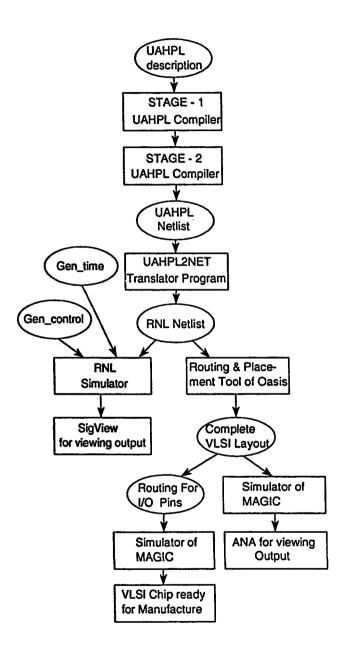

The objective of this work is to present a framework for the implementation of data structures in VLSI for systolic tree based architectures. As will be discussed in literature review of next chapter, not much work has been done in this area of implementation. The work is carried out in two phases: a logic synthesis phase and a layout phase. Referring to Figure 1.1, the system takes a register transfer level description (RTL). A processor (one node of systolic array) can be specified in RTL. The specification undergoes logic synthesis to give a netlist of standard gates (NAND, NOR etc.,) and flip-flops. Simulation is done both at register transfer level and gate level and compared to verify the translation process. This finishes the task of synthesis.

The netlist is given to another physical design subsystem which has placement,

Figure 1.1: An overview for DA system for generating layout from RTL specification and its verification [25].

routing and graphical manipulation tools along with a standard cell library. The layout produced is checked for design rules and the circuit is extracted. The extracted circuit is again simulated and the results compared with the results of the functional simulation at register transfer level.

The layout system of OASIS [21] called Vanilla Place aNd Route (VPNR) performs the routing and placement of the cells and generates the standard cell layout. VPNR [21] uses a library of predesigned standard cells. It also incorporates testability by including scan-path-based testing circuitry in the layout. VPNR is used to design the layout of one node of data structure. To synthesize the data structure of variable size, appropriate number of copies of one node are made, placed, and routed. Magic's router is used for routing between the nodes. The netlist file is saved and used for interconnection.

The MOSIS pad frame can be included in the layout. Finally the routing is performed and the chip is simulated. The verification of the result enhances the chances that the chip will work correctly after fabrication. The transistor level simulation with pad frame is viewed on ana, a waveform viewer.

### **1.2** Systolic systems

A systolic system can be defined as a network of processors that rhythmically compute and pass data among themselves. The analogy is with the rhythmic contraction and expansion of the heart which pulses blood through the circulatory system of the body. Each processor in a systolic network can be thought of as a heart that pumps multiple streams of data throughout the entire network [16]. As a processor pumps data items through, it performs some constant-time computation and may update some of the items. Systolic systems provide a realistic model of computations which capture the concepts of pipelining, parallelism and local interconnection structures. Many basic matrix computations can be performed by systolic systems whose underlying network is array structured [28]. Due to their regular structure and function systolic arrays are suitable for implementation in VLSI.

Unlike the closed-loop circulatory system, a systolic computer system usually has ports into which inputs flow and ports from which the results are retrieved. Thus, a systolic system can be a pipelined system in which input and output occur at every clock pulse. This makes them attractive as peripheral processors attached to the data channel of a host computer as well.

The activities of the processors in a systolic system can be assumed to be synchronous. With each pulse of a clock, a processor executes the same constant-time operation. Furthermore, each processor has equal amount of input and output lines and a constant amount of local storage. It is possible to view the processors as being asynchronous, each computing its output values when all its inputs are available, as in a data flow model. Each processing element in a systolic system is capable of performing some simple operation. Since simple, regular communications and control structures have substantial advantages over complicated ones in design and implementation, cells in a systolic system are typically interconnected to form a systolic array or a systolic tree. Information in a systolic system flows between cells in pipeline fashion, and communication with the outside world occurs only at the "boundary" cells. Only those cells on the array boundaries have the I/O ports for the communication with the outside world.

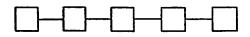

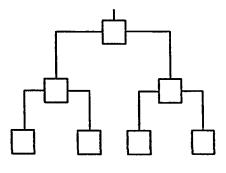

Systolic arrays can be of many different structures for different compute bound algorithms. Figure 1.2 shows various systolic array configurations. The computations which can be carried out using systolic arrays are image processing, matrix arithmetic, combinatorial, database algorithms. Due to the simplicity and strong appeal to intuition, systolic techniques have attracted a great deal of attention. However, the implementation of systolic arrays, especially systolic trees, on a VLSI chip has many practical constraints [12, 16].

### **1.3** Thesis outline

A study was carried out to devise a framework for the VLSI implementation of data structures. Two data structures, stack and queue are implemented in VLSI as examples. Chapter 2 discusses the background work done in the area of VLSI implementation of data structures and the layout of binary trees in different embedding strategies. Chapter 3 gives the design methodology at functional level. The tree

(a) One-dimensional linear array.

•

(b) Two-dimensional square array.

(d) Binary tree.

(e) Triangular array.

Figure 1.2: Various systolic array configurations.

· · -

embedding in 2-D grid of processors for maximum processor utilization is presented. The I/O buses and the control strategy for the node of a particular data structure is described. Chapter 4 presents the final layouts for stack and queue of variable sizes and simulation results of different size layouts. Finally, Chapter 5 summarizes the work accomplished and discusses future works which can be carried out using this framework.

-

# Chapter 2

# Literature review

### 2.1 Introduction

Many innovative designs have been proposed for hardware implementation of data structures, but much remains to be done in investigating the methods and strategies for VLSI implementation. In this chapter we review systolic algorithms for mapping various data structures in binary tree. Then, current literature on the problem of embedding a complete binary tree in the form of square grid of processors is presented.

### 2.2 High level synthesis

Implementation of data structures in VLSI results in numerous advantages. Due to this reason, a large number of researchers have been actively involved in this area. Leiserson proposed the design of a systolic priority queue [17] which uses tree topology to achieve a pipeline performance with  $O(\log n)$  response time for both delete and insert operations. The software implementation of sequential machine can guarantee  $O(\log n)$  performance by using a height balanced binary search tree. For sequential implementation of a priority queue, a heap is an attractive data structure because heap storage can be managed as easily as stack storage. These architectures can also be mapped on a two dimensional grid of processors. Other novel approaches appeared in the literature for the VLSI implementation of different data structures. Guibas and Lang [9] have given systolic array implementations of stack and queue. Ibarra and Culik [5] recently gave implementations of stacks and other linear systolic arrays on tree architecture.

The implementation of dictionary machine and other data structures were also proposed in [1, 22, 26]. Chang et al, proposed a simple finite state control mechanism for tree implementation of data structures [4]. Different algorithms were presented for hardware implementation of priority queue, dictionary machine, queue, stack and dequeue on a binary tree architecture. The algorithms for queue and stack are simple and straight forward but differ slightly in the implementation aspects and can easily be implemented on a tree based architecture. It is emphasized in the implementation that all the nodes in the tree are identical in all respects, and the control mechanism of each node is independent of the size of the data structure, the input and output operations are performed through the root of the tree.

The architecture of the FIFO queue described by Kanopolous and Hellenbeck [13] consists of two parts, FIFO storage part and control section part. The length of the queue is programmable, resulting in minimum data ripple through times for applications requiring the full length of the memory. The one-to-one transformation of the design is not practical because of the complexity of the controller. This is not a binary tree architecture and we are interested in systolic binary tree architectures.

Another architecture was proposed by Kulaib [15]. This approach is almost similar to that of [13]. It has faster access time and less power dissipation. This design although feasible in VLSI, is cumbersome to implement. The logic is complex and therefore a large area is required.

### 2.3 Binary tree embedding

After considering the algorithm for the implementation of data structures in binary trees, the problem of embedding a complete binary tree in a square grid of processors is considered. Mapping 1-D and 2-D arrays is not as difficult as mapping a tree onto a grid or 2-D array. A scheme is required to map the nodes of a binary-tree onto a

rectangular grid so that the amount of dead space is minimum. In order to avoid performance degradation, it is preferable that strongly connected nodes (parents and children of the tree) are placed as close as possible. In order to reduce the chip area, several proposals were studied to map nodes of a binary tree into a 2-D grid of processors. This mapping is referred to in the literature as "tree embedding". Important schemes available for tree embedding are described below.

#### 2.3.1 H-trees

H-trees represent a convenient way to place the nodes of a complete binary tree on a grid [2, 17]. The placement can be done recursively, and the final pattern looks like the letter 'H', hence the name. The nodes of the binary tree can be represented in a layout by grid points. A H-tree of order *i* represents a binary tree of height  $2 \times i$  (see Figure 2.1 on next page). Horowitz and Zorat [11] presented a detailed algorithm for mapping a binary tree in the form of a H-tree. As seen from the Figure 2.1, this form of embedding is not area efficient. Also the length of interconnects is large resulting in significant propagation delays. This scheme is only 50% area efficient and much of the chip area is wasted. The advantages, however, is ease of placement (recursively) and routing. Bounds on edge lengths and areas for embedding of trees with leaves on the border of the grid, and a plan of binary tree layout with low maximum wire length are presented in [30]. Clearly, the above scheme is not suitable for VLSI implementation because of low area efficiency and

Figure 2.1: A five-level tree embedding in H-tree layout.

•

high interconnection lengths [11, 30].

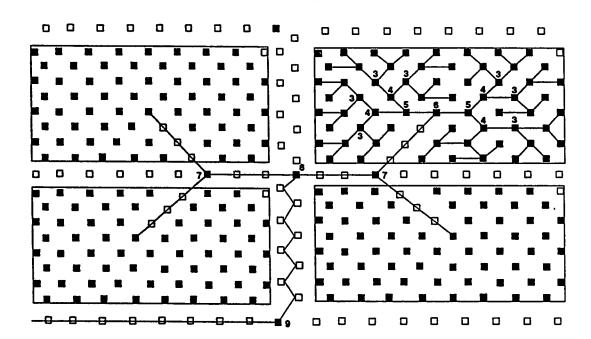

#### 2.3.2 Hexagonal tree embedding

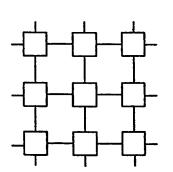

Another approach to solve the problem of embedding a complete binary tree in a square or hexagonally connected VLSI array of processing elements was studied by Gordon [8, 7]. The scheme is different from other techniques. Here, instead of considering the problem as that of laying out a graph in a plane, PEs are used both as tree nodes and as connecting elements between distant nodes. This approach shows slight improvement over the H-trees [11] in terms of utilization of chip area and propagation delay. It is 71% area efficient [7, 8]. It can also be seen from Figure 2.2 that the nodes marked with *empty squares* are wasted, creating long edges and hence large propagation delays [7].

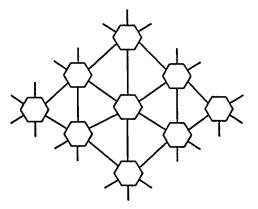

#### 2.3.3 Tile-based tree embedding

An very efficient scheme for the layout of large binary tree architectures by embedding the complete binary tree in a 2-D array of PEs was presented by Youn and Singh [31]. This scheme, also known as "tile based design", utilizes virtually 100% of all PEs in the array, and also shows substantial improvement in propagation delay and maximum edge length over H-tree layouts and hexagonal tree layouts. In addition, layouts produced readily lend themselves to fault-tolerant designs for overcoming fabrication defects in large area and wafer scale implementations of binary

Figure 2.2: The regular embedding scheme for hexagonal array [8].

Figure 2.3: Embedding of 15 node tree in  $4 \times 4$  square array of processors.

tree architectures. As an example, a 4-level (15 node) binary tree embedding is shown in Figure 2.3.

### 2.4 Conclusion

In this chapter various systolic topologies and algorithms for data structures and other applications were reviewed. The tree-based systolic algorithms were reviewed for stack, queue, priority queue and dictionary machine. A brief literature review of tree embedding was also presented. The embedding strategies which were studied

are H-tree embedding, Hexagonal tree embedding and tile-based tree embedding.

•

.

In the next chapter the design methodology is described for the implementation of data structures.

...

# Chapter 3

· ··· ·

# **Design Methodology**

### 3.1 Introduction

The VLSI implementation of tree based architectures consists of the following.

- 1. The translation of the behavioral model of systolic tree node into an efficient minimal structural level model.

- 2. Synthesis of the structural model.

- 3. The embedding of nodes of the tree into an area efficient 2-D grid.

The data structures described by Ibarra et al., [4] at the behavioral level are queue, stack, priority queue, dictionary machine and dequeue. These behavioral models are based on the systolic tree based architectures. In this chapter operation of a queue and stack are described with examples. The behavioral models of queue and stack are given. The block diagrams illustrating the hardware components of one node of a queue and stack are also presented.

## **3.2** Operation of a queue

A queue operates in a first-in first-out manner. The design of a FIFO queue is based on the tree architecture proposed by Chang et al [4]. The queue is implemented on a binary tree and has a unit response time and a unit pipeline interval. The root node contains the front of the queue, and the element to be inserted will move down the tree. All nodes of the tree are identical in all respects. Each node has two registers, a data and a buffer register, and two flags, an insert flag and a delete flag. The data register holds the data item to be stored in the node. The buffer register is used for temporary storage of data item to be passed on to the parent or child nodes in the case of delete and insert respectively. The concept underlying the queue operation can be briefly described as follows. When a node becomes active (i.e., an empty node receives an insert instruction), the data item will be stored in the data register of the node, and its insert and delete flags will be reset. When an active node receives an insert instruction, the data item is stored in the buffer register and the insert flag is complemented. Depending upon the value of the insert flag (0 or 1), the data item will be passed on to the right or left child respectively, in the following clock cycle. Successive insert instructions will make last-in data items move to the lowest levels of the tree, i.e., to the leaf nodes. When a delete instruction is applied to an active node, the data item stored in the data register of the root node is passed on to the output bus, and the data item from its left or right child is copied into the data register of the parent node, and the delete instruction is forwarded to the left or right child depending on the value of the delete flag (0 or 1). Basically, a delete instruction will cause deletion of data item from the root node, and movement of data towards the root of the tree such that the current first-in data item is moved to the root node. Similarly, an insert instruction will cause the data item to move down eventually to the lowest level (one of the leaf nodes) of the tree. For more details, the reader is referred to [4]. The data distribution of the queue when 15 consecutive inserts are made into the empty queue is shown in Figure 3.1. Figure 3.2

Figure 3.1: Data distribution of the queue after 15 consecutive inserts.

shows the configurations of the queue when the sequence of instructions is applied at every clock cycle. The flag values are given to the right of each node. Consider

Figure 3.2: The configurations of queue under a sequence of instructions.

the effect of the delete at timestep T = 9. Since the delete flag of the root is 0, the data element stored in its left child is copied into the root node. Note the content of the left child (which is 2) is not immediately deleted. Instead, the delete instruction is pipelined to the left. The actual deletion of the left child takes place at T = 10. The arrow indicates the node to which an instruction is being directed. Hence, it can be easily seen that the queue has unit response time for both insert and delete operations. Queues have a wide range of applications in computer systems such as, the queue of tasks waiting for the line printer, for access to the disk storage and for a time sharing system, tasks queue up for the CPU. Queues also find application in sorting, searching symbol table, decision table implementations, and in simulation studies [14].

## **3.3** The structural model of a queue node

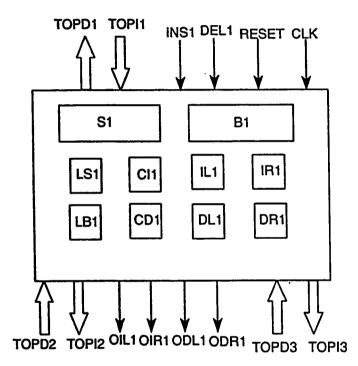

In this section we present the hardware implementation and discuss the hardware components of a queue node. The behavioral model of the tree node of a queue is shown in the Figure 3.3 and the block diagram is shown in Figure 3.4. The hardware components include two 8-bit registers S1, B1, and eight 1-bit flip-flops LS1, LB1, CI1, CD1, IL1, DL1, IR1, and DR1. The function of each flip-flop is as follows. LS1 and LB1 show the status (empty or full) of S1 and B1 registers. CI1 and CD1 are insert and delete flags used for the insertion and deletion of data. IL1 and IR1

Pseudo code for Insert and Delete Instructions of a queue

```

begin

if (LS1 = 0 \text{ and Insert present})

1^{st} condition

then S1 \leftarrow value; CI1 \leftarrow 0; CD1 \leftarrow 0; LS1 \leftarrow 1

else

2^{nd} condition

if (LS1 = 1 \text{ and Insert present})

then B1 \leftarrow value; CI1 \leftarrow \sim CI1; LB1 \leftarrow 1

endif

endif

if (LB1=LS2=LS3=0 and Delete is present)

3^{rd} condition

then LS1 \leftarrow 0

endif

if (LS2=LS3=0 and LB1=1 and Delete is present)

4^{th} condition

S1 \leftarrow B1; CD1 \leftarrow \sim CD1;

endif

if (~(3^{rd} condition) & ~(4^{th} condition and Delete present))

5^{th} condition

if CD1 = 0

then S1 \leftarrow S2 else S1 \leftarrow S3

endif

CD1 \leftarrow ~CD1;

endif

```

end.

Figure 3.3: Behavioral model of a node of a systolic-tree based queue.

specify the direction of data movement. If IL1 (IR1) is high then the value is inserted to the left (right) subtree. Similarly, if DL1 (DR1) is high then the value from the left (right) subtree is copied to the root node and the value of the root node appears on output bus TOPD1.

There are two 8-bit wide buses TOPI1 and TOPD1 for insertion and deletion of data into and from the root node respectively. Other four 1-bit input buses are INS1, DEL1, RESET and CLK. If INS1 (DEL1) is high, insert (delete) operation is performed. At the bottom of the node there are four 8-bit wide buses TOPI2, TOPD2, TOPI3 and TOPD3. The 8-bit data is inserted through TOPI2 into the left subtree, and through TOPI3 into the right subtree. The deletion of data from left and right subtrees are routed through TOPD2 and TOPD3 respectively. There are four 1-bit output lines OIL1, OIR1, ODL1 and ODR1. If OIL1 (OIR1) is high then the data is routed to the left (right) subtree. Similarly, if ODL1 (ODR1) is high then the data from the left (right) subtree is deleted.

## **3.4 Operation** of a stack

A stack operates in last-in first-out manner. The design of a LIFO stack is based on the architecture by Chang et al [8]. It is implemented on binary tree and also has unit response time and unit pipeline interval. The root node contains the top of the stack. The element pushed will remain in the root node and the rest of the

.

Figure 3.4: Block diagram of a queue node.

•

elements are pushed down the tree. All the nodes in the binary tree are identical in all respects. In the tree based implementation of the stack, each node has a binary flag, depending on this flag it is determined as to which child the next instruction is to be pipelined. The flag is complemented after each instruction. The last data which is entered into the stack is maintained in the root node of the tree. Each node except the root node gets the instruction from its parents buffer. The concept underlying the stack operation can be briefly described as follows. When a node becomes active (i.e., an empty node receives a push instruction), the value is pushed into the data register and the flag is set to 0. Since there is no instruction in the pipeline anymore, the buffer will remain empty. If the node is active, the instruction needs to be pipelined further. Suppose an element Y is entering a node containing X in the data register, then Y will be stored in the data register and X will be stored in the buffer register and the flag is complemented. If the flag is 1 or 0 the element is pipelined to the right or left child in the next cycle and this operation continues for the consecutive pushes. The contents of a stack after fifteen consecutive pushes to an empty stack is shown in the Figure 3.5. In this example the first number to be pushed is 1 and the last number pushed is 15.

When a pop instruction is applied to the active node, the data item stored into the data register is popped and the data item in the buffer register is copied to the data register of the root node. If the data items are present in the left and right children, then they are copied one after another depending on the flag. If the flag

123

Figure 3.5: Data distribution of the stack after 15 consecutive push operations.

is 1, the data of the right child is copied and if the flag is 0 the data item of the left child is copied. Basically the pop instruction will cause the movement of the data towards the root of the tree such that the last-in data item is moved to the root node. Figure 3.6 shows the configurations of the stack when a sequence of instructions is applied at every clock cycle. The status flag is shown to the upper right corner of the node. Note that the arrow indicates the node to which an instruction is being pipelined. Hence, it is clearly seen that the stack has unit response time with respect to the push and pop operations.

## 3.5 The structural model of a stack node

In this section we present the hardware design and discuss the hardware components of a stack node. The behavioral model of the tree node of a stack is shown in

Figure 3.6: The configurations of stack under a sequence of instructions.

Figure 3.7 and the block diagram is shown in Figure 3.8. It consists of two 8-bit registers S1, B1 and seven 1-bit flip-flops LS1, LB1, C1, IL1, DL1, IR1 and DR1. LS1 shows the status of data register S1, LB1 shows the status of buffer register B1. C1 is the status flag for push and pop operations. IL1 and IR1 specify the direction of the data movement. If IL1 (IR1) is high then the value is pushed to the left (right) subtree. Similarly, if DL1 (DR1) is high then the value from the left (right) subtree is copied to the root node and the value of the root node appears on output bus TOPD1.

There are two 8-bit wide buses TOPI1 and TOPD1 for push and pop operations into and from the root node. Other four 1-bit input buses are INS1, DEL1, RESET, CLK. If INS1 is high, push operation is performed. If DEL1 is high then the pop operation is performed. At the bottom of the node there are four 8-bit wide buses TOPI2, TOPD2, TOPI3 and TOPD3. The 8-bit data is pushed through TOPI2 into the left subtree and to the right subtree through TOPI3. The data which is popped from the left and right subtrees are routed through TOPD2 and TOPD3 respectively. There are four 1-bit output lines OIL1, OIR1, ODL1, and ODR1. If OIL1 (OIR1) is high then the data is routed to the left (right) subtree. Similarly, if ODL1 (ODR1) is high then the data from the left (right) subtree is popped. The node has been modeled using the hardware description language AHPL [24]. The implementation aspect is discussed in the next chapter. Pseudo code for Push and Pop Instructions of Stack

```

begin

1<sup>st</sup> condition

if (LS1 = 0 \text{ and } Push \text{ is present})

then S1 \leftarrow value; C1 \leftarrow 0; LS1 \leftarrow 1

else

2^{nd} condition

if (LS1 =1 and Push is present)

then S1 \leftarrow value; B1 \leftarrow S1; C1 \leftarrow \simC1; LB1 \leftarrow 1

endif

endif

3^{rd} condition

if (LB1=LS2=LS3=0 and Pop is present)

then LS1 \leftarrow 0

endif

4^{th} condition

if (LB1=1 and Pop is present)

S1 \leftarrow B1; C1 \leftarrow \sim C1;

endif

if (~(3^{rd} condition) & ~(4^{th} condition and Pop present))

5^{th} condition

if C1 = 0

S1 \leftarrow S2 else S1 \leftarrow S3

then

endif

C1 \leftarrow \sim C1;

endif

end.

```

Figure 3.7: Behavioral model of a node of a systolic-tree based stack.

Figure 3.8: Block diagram of a stack node.

•

# **3.6 Embedding of binary-tree into tile-based schemes**

A new tile (module) based design for laying out the complete binary tree in the form of two dimensional grid of processors with channel based interconnections is presented here. The design is suited to large processors with relatively narrow bus widths. The scheme is better in terms of area efficiency and propagation delay compared to previous designs. More importantly this scheme is 100 percent area efficient for practical size tree architecture, along with short propagation delay and minimum edge lengths.

Thus, using this design, tree architectures can be laid out in VLSI more efficiently than before, with significantly better performance.

# 3.7 Structure of basic modules

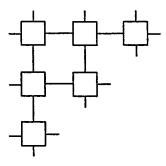

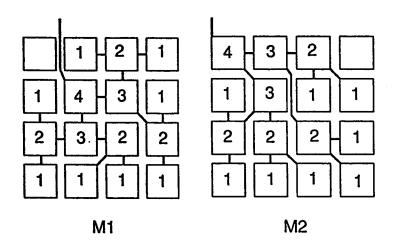

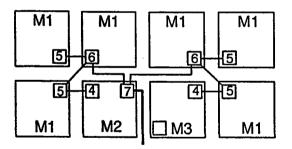

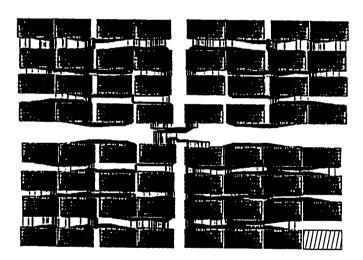

The layout scheme uses a hierarchical strategy such that any required size of tree larger than four levels is laid out by connecting the required number of basic modules of appropriate *type*. Each basic module is a  $4 \times 4$  square array of processors and contains a four level tree (Figure 3.9). Thus, 15 out of the 16 processors in the basic module are used as tree nodes, the remaining unused processor in each basic module is used as a tree node at some higher level when the basic modules are connected together to build a larger tree (this strategy is also employed in the hexagonal array design in [7]). In other words, each basic module contains a four level leaf subtree

Figure 3.9: The structure of basic modules used for embedding trees with level greater than 4 [31].

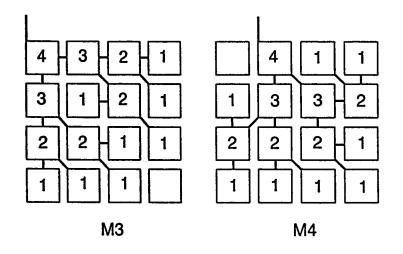

of the overall tree and one additional node belonging to a higher level in the tree. Whenever a large tree is constructed using the basic modules, the root node of the tree should be located at the center of the two-dimensional array for minimum propagation delay. In order to realize this, four types of 15 processor basic modules are used. They are different from one another in the relative position of the unused node with respect to the root node for the four-level subtree in each basic module. Figure 3.9 shows the four types of basic modules. We refer to them as M1, M2, M3 and M4, respectively. The number in each box (processor) denotes the level of the node in the tree, with the leaf node being at level 1. Observe that all nodes at adjacent levels, except two nodes in the basic module M2, are adjacent and can be connected with short links. This allows us to construct large trees using basic modules which are not only area efficient but also have short propagation delays.

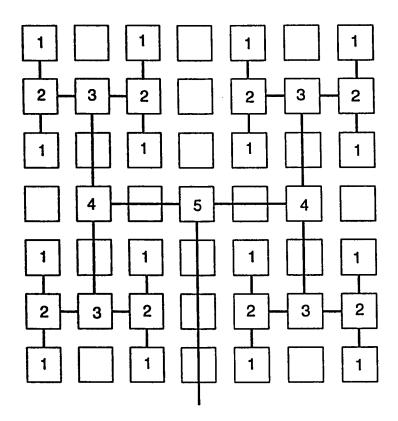

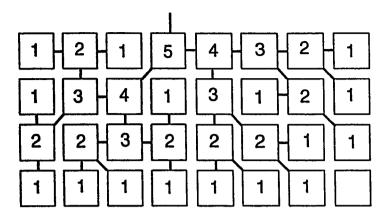

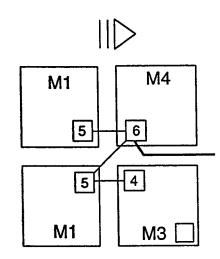

#### **3.7.1** Five and six level trees

A five-level tree can be constructed by laying out and connecting one M1 basic module with one M3 basic module side by side as shown in the Figure 3.10 (M3 to the left of M1). Observe that the unused node in the basic module M1 is utilized as the root node of the five level tree. Actually, one M1 basic module with either an M1 or M2 basic module can also be used to construct a five level tree. However, these combinations are not preferred because they lead to a longer propagation delay. Figure 3.11 shows how a six-level tree can be constructed using two M1, one

Figure 3.10: A five-level tree embedding using two basic modules [31].

M3, and one M4 basic modules. Here the number at one corner node of each basic module indicates the level of the node in the embedded tree. Also, the empty small box indicates the unused node. Other combinations of four basic modules such as four M1, or three M1 and one M3 can also realize the six level tree embedding while achieving minimum propagation delay.

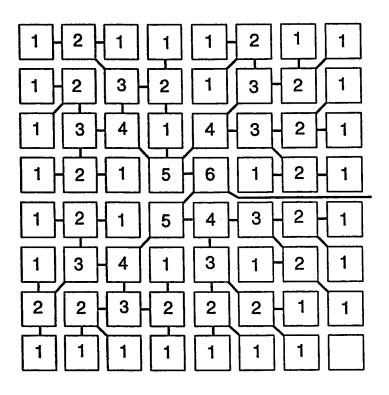

#### **3.7.2** Tree larger than six levels

123

A seven-level tree is shown in Figure 3.12. The unused processor is located in the middle of an edge and adjacent to the channel where the interconnection from the root node emerges from the array.

Trees greater than seven levels are obtained by repeatedly taking two trees of a given size and constructing a larger tree with one additional level. This process can be repeated beginning with two six level trees until a tree with the desired size is

Figure 3.11: A six-level tree embedding using four basic modules [31].

•

obtained.

The procedure to obtain an n + 1 level tree from n level trees is as follows :

- obtain the mirror image of the *n* level tree along the edge containing the unused processor,

- combine the two layouts and locate the root of the  $n + 1^{st}$  level tree in the unused processor in one of the original n level tree, and

- rotate the set of modules (in their correct relative positions) about an axis parallel to the appropriate array edge so as to move the unused processor to the outside of the array.

This process can be repeated recursively until the layout of the desired size is obtained.

Figure 3.12: A seven-level tree embedding using four basic modules [31].

### **3.8 Evaluation** of proposed tree layout scheme

For the evaluation of the effectiveness of embedding schemes to be used to layout large trees, the following criteria are important.

- Chip area efficiency: determined by the ratio of the active chip area utilized for actual computations to the entire chip area. When each processing element is relatively large, almost all the chip area is taken up by the processing elements. The area efficiency is then the ratio of the number of the processing elements actually utilized as tree nodes to the total number of processing elements implemented on the chip. Since the cost of a VLSI circuit increases with the chip area, this factor is a good metric of the cost effectiveness of the embedding scheme.

- Propagation delay (PD): defined as the maximum data propagation time between the root node and the leaf nodes. This determines the setup time and the data latency when the tree architecture executes a certain problem in parallel.

- Maximum edge length (MEL): defined as the maximum of the edge length between any pair of two directly connected nodes. This is important for two reasons. If the entire processor array operates with a common synchronous clock, then the maximum clock rate is determined by the propagation delay on the longest tree edge, this factor limits the execution speed of the design.

#### 3.8.1 Area efficiency

The area efficiency of an embedding scheme has traditionally been estimated by the ratio of the number of utilized processors to the total number of processors in the host array in which the tree topology is embedded. It can be seen from Figures 3.10, 3.11 and 3.12 that only one processor is left unutilized in our design for any tree size. Thus, the area efficiency of our scheme is  $(2^k - 1)/2^k$ ,  $k \ge 4$ , where k represents number of levels in the tree. This rapidly converges to 100 percent as the size of the embedded tree grows large. Since the number of nodes in the tree of any size is always  $2^k - 1$  (always odd) and we embed in an array of  $2^k$  processors, having one unused processor is unavoidable. Therefore, the tree embedding scheme is optimal with respect to the utilization of processors. Note that the area of interconnection buses running between the modules is not reflected in the area efficiency consideration because the interconnection area is assumed to be small in comparison to the total area of the processor.

#### 3.8.2 Propagation delay

The worst propagation delay (PD) in a tree architecture is equal to the delay along the distance between the root and leaf nodes. This can be expressed in terms of the processor edge dimension, which is the length of one side of the processor. To obtain a uniform and consistent measure of interconnect distances independent of the layout details, we index the processor in row *i* and column *j* as (i, j). We also assume that all data paths run horizontally and vertically (Manhattan interconnections). Then the distance between two directly connected processors located at  $(i_1, j_1)$  and  $(i_2, j_2)$  is  $|i_1-i_2|+|j_1-j_2|$ . The maximum root-to-leaf distance can be found by comparing the distances of all paths from the root node to the leaf nodes. These can be obtained by adding up the distances of each successive pair of two directly connected processors on the path from the root node to the leaf node. For example, the maximum distance of five-level tree in Figure 3.10 is 6 because the distance from the root node (1,4) to the leaf node (4,7) via (1,5), (2,5), and (3,6) is 1 + 1 + 2 + 2 = 6.

#### 3.8.3 Maximum edge length

The maximum edge length for the small size trees  $(k \leq 6)$  displays optimal maximum edge length because all the tree nodes are either adjacent or diagonal neighbors. However, for large trees, pattern interconnection of nodes at levels higher than six can result in relatively long upperlevel edges, and degrade performance. Thus, we need to develop a design which reduces the maximum edge length for trees with more than six levels, because such large designs now appear possible with WSI (wafer scale integration) technology. The propagation delay of the design is almost near optimal for any tree size. The propagation delay can be minimized by equally dividing the distance among the edges along each path from the root to a leaf node.

## **3.9** Buses in the layouts

Bus widths are considered negligible, as compared to a processor edge. The area efficiency of this scheme is almost twice as good as that for the H-tree scheme [31]. Thus, for bus widths upto 40 percent of the processor edge dimension, this scheme is more efficient than H-tree layouts while displaying much better propagation delay and maximum edge lengths. If the bus widths are greater than 40 percent of the processor edge, H-tree layouts will generally by more area efficient, although the tile-based design still displays better performance. The scheme is generally best on all three criteria for large processors and narrow bus widths.

# 3.10 Conclusion

In this chapter the operation of systolic tree-based queue and stack are described with an example each. The behavioral model of queue and stack are discussed and then internal components are explained with the help of block diagrams. Tile-based tree embedding strategy is presented. Moreover, embedding of different level binary trees is also presented.

# Chapter 4

# Implementation in VLSI

## 4.1 Introduction

In the previous chapter the detail design of the nodes of queue and stack and the interconnection of these nodes in the form of 2-D grid of processors was presented. In this chapter we give the implementation of queue and stack in VLSI. Other data structures can be implemented in same way. Only the architecture of the node (PE) needs to be changed.

# 4.2 RTL model for stack and queue

The hardware description languages (Verilog, CDL, DDL, AHPL, VHDL, ISPS etc.,) have been used successfully for documentation, communication and verification [10].

They have also been used as input specification languages to design automation (DA) systems which synthesize VLSI layouts [24]. The logic synthesis of the node of a systolic tree based data structure is done with the help of hardware compiler [19], for details refer to Appendix A.

#### 4.2.1 RTL model for queue

The hardware of a single node of a systolic queue consists of many components as stated in the earlier chapter. There are two 8-bit registers S1 (data register) and B1 (buffer register), and eight 1-bit flip-flops IL1, IR1, DL1, DR1, CD1, CI1, LS1 and LB1. TOPI1 and TOPD1 are the 8-bit wide buses for insertion and deletion of data. TOPI2 and TOPD2 are the 8-bit wide buses for the left subtree. TOPI3 and TOPD3 are also the 8-bit wide buses the right subtree. INS2 and DEL2 are the insert and delete lines for left child. INS3 and DEL3 are the insert and delete lines for the right child. RESET, CLK, and START are the external inputs so they are declared as EXINPUTS.

There are many conditional statements through which the various decisions are made. The AHPL description shown in the Figure 4.1 contains the code enclosed within the keywords BODY SEQUENCE and END. The controller of the node has only one C - step since the queue instructions (insert or delete) takes only one clock cycle. The operation of a queue has been simulated using the RT level functional simulator available in the AHPL DA system. The simulation results have

validated the design of the tree node and the stack at the register transfer level [24]. In the Figure 4.2 the COMSEC file is shown which is the input to the DA system. The output produced is shown in Figure 4.3.

#### 4.2.2 RTL model for stack

The hardware of a single node of a systolic stack consists of many components as shown in the block diagram of stack node in previous chapter. All the hardware components are same as that of queue node, because the stack is also 8-bit. The operations here are push and pop. The stack is also mapped on the same architecture as that of a queue.

The AHPL description shown in Figure 4.4 is enclosed within the keywords BODY SEQUENCE and END. The controller of the node has only one C-stepsince the stack instructions (push or pop) takes only one clock cycle. The input description file for AHPL DA system for stack is shown in Figure 4.5 and the output is shown in Figure 4.6

After the AHPL code is compiled, the simulation is performed at RT level with the help of functional level simulator [6]. Next logic synthesis is carried out [19]. UAHPL compiler generates a logic netlist of hardware circuit in terms of logic gates, flip-flops etc.,. The output of the stage 2 compiler of UAHPL is stored in the form of linked list consisting of GATE#, specifying the gate number for the element, followed by the GATE TYPE, specifying the type of the element, for example,

```

MODULE

: QNODE1.

MEMORY

: IL1; IR1; DL1; DR1; S1{8}; B1{8}; CD1; CI1; LS1; LB1.

EXBUSES

: DEL2; INS3; DEL3; TOPI2{8}; TOPI3{8}.

EXBUSES

: LSL1; LSR1; TOPD2{8}; TOPD3{8}; TOPD1{8}; OLS1; INS2; DEL2.

BUSES

: CC11; CC21; CC31; T11; T21; T31; T41; FALSE1.

: TOPI1{8}; INS1; DEL1; RESET; CLK; START.

EXINPUTS

BODY SEQUENCE :CLK.

1 \text{ CI1}^{*}(\text{T11})

\Leftarrow 1$0; CD1*(T11) \Leftarrow 1$0;

CI1*(T21)

\Leftarrow ~(CI1); LS1*(T11) \Leftarrow1$1;

LB1*(T21) \Leftarrow 1$1; IL1*(INS1) \Leftarrow(CI1 ! 1$0)*(LS1, ~LS1);

IR1*(INS1) \leftarrow (~CI1 ! 1$0)* (LS1, ~LS1); LS1*(CC11) \leftarrow 1$0;

CD1*(CC21) \Leftarrow (CD1); DR1*(T31) \Leftarrow 1

DL1*(T41) \Leftrightarrow 1$1; CD1*(CC31) \Leftrightarrow (\ CD1); B1*(T21) \Leftrightarrow TOPI1;

S1*(FALSE1) (TOPI1!B1!TOPD2!TOPD3) *(T11,CC21,T41,T31);

TOPD1

= S1*DEL1; \Rightarrow (~START)/(1).

ENDSEQUENCE

CONTROLRESET (1);

TOPI2 = B1 * IL1; TOPI3 = B1 * IR1;

FALSE1 = (T11 + CC21 + T41 + T31);

INS2 = IL1; DEL2 = DL1; OLS1 = LS1; INS3 = IR1;

DEL3= DR1; T11 = INS1 & LS1;

T21 = INS1 \& LS1; T31 = CC31 \& (~CD1); T41 = CC31 \& CD1;

CC11 = (LSR1 + LSL1 + LB1) \& DEL1;

CC21 = (LSR1 + LSL1 + LSL1) \& DEL1;

CC31 = \tilde{(CC11)} \& \tilde{(CC21)} \& DEL1.

END.

```

Figure 4.1: AHPL description of systolic tree-based queue.

OPTION 6. VIEW 5 VON. OUTPUTS INS1;DEL1;TOPI1;TOPD1;S1;B1;TOPI2;TOPI3; DEL2;DEL3;INS2;INS3;LS1;LB1. EXLINES RESET=1,0;START=0; LSL2=0;LSR2=0;LSL3=0;LSR3=0; INS1=1,1,1,1,1,0,0,0,0,0,0; TOPI1 = '11,'22,'33,'44,'55,'66,'77,'88,'99,'AA.

•

Figure 4.2: COMSEC file for AHPL description.

KING FAHD UNIV OF PETROLEUM & MINERALS, COLLEGE OF COMPUTER SCIENCE UNIVERSAL AHPL SIMULATOR OUTPUT DATE: WED 22 SEPT, 1993 TIME: 18:35:47

**\$\$\$\$\$\$ UNIVERSAL AHPL FUNCTIONAL LEVEL SIMULATOR OUTPUT:**

•

.

|         | INS1<br>  DEL1<br>    TOPI1<br>    TOPD1 |    |    |           |    |     |      |             |    |   |   |   |     |

|---------|------------------------------------------|----|----|-----------|----|-----|------|-------------|----|---|---|---|-----|

|         | 11                                       | I  | I. | <b>S1</b> |    |     |      |             |    |   |   |   |     |

|         | 11                                       | ł  | ł  | I         | B1 |     |      |             |    |   |   |   |     |

|         | 11                                       | 1  | 1  | 1         | l  | TOF | PI2  |             |    |   |   |   |     |

|         | 11                                       | I  | 1  | I         | I  | I   | TOF  | <b>PI</b> 3 | \$ |   |   |   |     |

|         |                                          | I  | I  | I         | I  | l   | DEL2 |             |    |   |   |   |     |

|         |                                          | I  | 1  | I         | 1  | I   | 1    | DEL3        |    |   |   |   |     |

|         |                                          | I  | 1  | I         | i  | I   | 1    | I INS2      |    |   |   |   |     |

|         | 11                                       | ł  | l  | ł         | I  | 1   | 1    | INS3        |    |   |   |   | 3   |

|         | 11                                       | ł  | l  | I         | 1  | 1   | I.   | LS1         |    |   |   |   | 51  |

|         |                                          | 1  | 1  | ł         | I  | I   | I    | I           | I  | l | I | I | LB1 |

| CLOCK # | 11                                       | 1  | 1  | 1         | I  | I   | 1    | 1           | I  | 1 | I | ł | I   |

| 0       | 00                                       | 00 | 00 | 00        | 00 | 00  | 00   | 0           | 0  | 0 | 0 | 0 | 0   |

| 1       | 1 0                                      | 11 | 00 | 00        | 00 | 00  | 00   | 0           | 0  | 0 | 0 | 0 | 0   |

| 2       | 10                                       | 22 | 00 | 11        | 00 | 00  | 00   | 0           | 0  | 0 | 0 | 1 | 0   |

| 3       | 1 0                                      | 33 | 00 | 11        | 22 | 22  | 00   | 0           | 0  | 1 | 0 | 1 | 1   |

| 4       | 1 0                                      | 44 | 00 | 11        | 33 | 00  | 33   | 0           | 0  | 0 | 1 | 1 | 1   |

| 5       | 10                                       | 55 | 00 | 11        | 44 | 44  | 00   | 0           | 0  | 1 | 0 | 1 | 1   |

::::: PROGRAM REACHED THE CLOCKLIMIT. AHPL SIMULATION STOPS. :::::

. .....

```

MODULE

: SNODE1.

MEMORY

: IL1; IR1; DL1; DR1; S1{8}; B1{8};C1;LS1; LB1.

EXBUSES

: DEL2; INS3; DEL3; TOPI2{8}; TOPI3{8}.

EXBUSES

: LSL1; LSR1; TOPD2{8}; TOPD3{8}; TOPD1{8}; OLS1; INS2; DEL2.

BUSES

: CC11; CC21; CC31; T11; T21; T31; T41; FALSE1.

EXINPUTS

: TOPI1{8}; INS1; DEL1; RESET; CLK; START.

BODY SEQUENCE :CLK.

1 C1*(T11)

⇐ 1$0;

C1*(T21)

\Leftarrow ~(CI1); LS1*(T11) \Leftarrow1$1;

LB1*(T21) \Leftarrow 1$1; IL1*(INS1) \Leftarrow(CI1 ! 1$0)*(LS1, ~LS1);

IR1*(INS1) \leftarrow (~CI1 ! 1$0)* (LS1, ~LS1); LS1*(CC11) \leftarrow 1$0;

C1*(CC21) \Leftrightarrow \tilde{(C1)}; DR1*(T31) \Leftrightarrow 1\$1;

DL1*(T41) \Leftrightarrow 1$1; C1*(CC31) \Leftrightarrow (\ \ C1); B1*(T21) \Leftrightarrow TOPI1;

S1*(FALSE1) ← (TOPI1!B1!TOPD2!TOPD3) * (INS1, CC21, T41, T31);

TOPD1

= S1*DEL1;

\Rightarrow (~START)/(1).

ENDSEQUENCE

CONTROLRESET (1);

TOPI2 = B1*IL1; TOPI3 = B1*IR1;

FALSE1 = (T11 + CC21 + T41 + T31);

INS2 = IL1; DEL2 = DL1; OLS1 = LS1; INS3 = IR1;

DEL3= DR1; T11 = INS1 & LS1;

T21 = INS1 \& LS1; T31 = CC31 \& C1; T41 = CC31 \& (~C1);

CC11 = ~LB1 \& DEL1;

CC21 = (LSR1 + LSL1 + LSL1 + LSL1) \& DEL1;

CC31 = \tilde{(CC11)} \& \tilde{(CC21)} \& DEL1.

END.

```

Figure 4.4: AHPL description of systolic tree-based stack.

OPTION 6. VIEW 7 VON. OUTPUTS INS1;DEL1;TOPI1;TOPD1;S1;B1;S2;B2;S3;B3.

EXLINES RESET=1,0; LSL2=0;LSR2=0;LSL3=0;LSR3=0; START=0; INS1=1,1,1,0,0,0,0; DEL1=0,0,0,0,1,1,1,0; TOPI1 = '11,'22,'33,'00,'00,'00,'00,'00.

Figure 4.5: COMSEC file for AHPL description.

49

.

KING FAHD UNIV OF PETROLEUM & MINERALS, COLLEGE OF COMPUTER SCIENCE UNIVERSAL AHPL SIMULATOR OUTPUT DATE: SUN 01 MAY, 1994 TIME: 10:44:09

**\$\$\$\$\$\$** UNIVERSAL AHPL FUNCTIONAL LEVEL SIMULATOR OUTPUT:

|       |   | INS1  |   |       |    |           |    |    |    |  |  |

|-------|---|-------|---|-------|----|-----------|----|----|----|--|--|

|       |   | DEL1  |   |       |    |           |    |    |    |  |  |

|       |   | TOPI1 |   |       |    |           |    |    |    |  |  |

|       |   | ł     | 1 | TOPD1 |    |           |    |    |    |  |  |

|       |   | I     | 1 | I     | I  | <b>S1</b> |    |    |    |  |  |

|       |   | 1     | l | I     | Ł  | I         | B1 |    |    |  |  |

|       |   | I     | I | ł     | 1  | I         | I  | S3 |    |  |  |

|       |   | I     | 1 | 1     | 1  | L         | I  | 1  | S2 |  |  |

|       |   | 1     | I | 1     | l  | ł         | I  | 1  | I  |  |  |

|       |   | I     | I | I     | I  | 1         | I  |    | F  |  |  |

| CLOCK | # | I     | I | I     | I  | 1         | I  | 1  | 1  |  |  |

|       | 0 | 0     | 0 | 00    | 00 | 00        | 00 | 00 | 00 |  |  |

|       | 1 | 1     | 0 | 11    | 00 | 00        | 00 | 00 | 00 |  |  |

|       | 2 | 1     | 0 | 22    | 00 | 11        | 00 | 00 | 00 |  |  |

|       | 3 | 1     | 0 | 33    | 00 | 22        | 11 | 00 | 00 |  |  |

|       | 4 | 0     | 0 | 00    | 00 | 33        | 22 | 11 | 00 |  |  |

|       | 5 | 0     | 1 | 00    | 33 | 33        | 22 | 11 | 22 |  |  |

|       | 6 | 0     | 1 | 00    | 22 | 22        | 22 | 11 | 22 |  |  |

|       | 7 | 0     | 1 | 00    | 11 | 11        | 22 | 11 | 22 |  |  |

|       |   |       |   |       |    |           |    |    |    |  |  |

•

::::: PROGRAM REACHED THE CLOCKLIMIT. AHPL SIMULATION STOPS. :::::

Figure 4.6: Output for one node systolic tree-based stack.

AND, OR, D flip-flop etc. The two fields in the record, ILINK and OLINK, are pointers to the IOLIST.

The AHPL netlist obtained from the stage 2 compiler is translated to RNL compatible logic level netlist using a translator written in "C" programming language. The netlist generated by the translator is in RNL format. It comprises combinational logic gates and three types of D flip-flop (set, reset and control flip-flops) with enable, asynchronous set and reset inputs. RNL compatible netlist for both queue and stack is shown in the Figures 4.7 to 4.10. The netlist generated is simulated by RNL [6], a timing and logic level simulator. The simulation results of RNL are observed using SigView, a signal viewing tool. The process was illustrated in the flow chart in chapter 1.

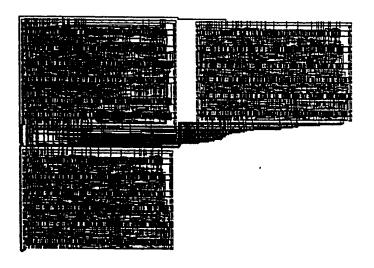

## 4.3 Layouts of systolic-tree based queue and stack

The OASIS layout design environment [21] is used for generating the layouts. OASIS is an abbreviation of Open Architecture Silicon Implementation Software. A number of design cells are integrated into the OASIS system. OASIS is a cell based system for IC design. The tools integrated into the OASIS system have been developed to automatically translate high level description of integrated circuits into testable physical layouts, using predesigned standard cells. One of the features of the OASIS system is the modularity of the software. New improved algorithms can be easily

```

(include "defi.net")

(include "drff.net")

(include "dsll.net")

(include "array.sub.net")

(include "standard.def")

(include "decal.del.W")

(include "others.def.W")

( node n100 n101 n102 n103 n104 n105 n106 n107 n108 n109)

(node n110 n111 n112 n113 n114 n115 n116 n117 n118 n119)

(node n120 n121 n122 n123 n124 n125 n126 n127 n128 n129)

( node n130 n131 n132 n133 n134 n135 n136 n137 n138 n139)

( node n140 n141 n142 n143 n144 n145 n146 n147 n148

n149)

( node n150 n151 n152 n153 n154 n155 n156 n157 n158 n159)

( node n160 n161 n162 n163 n164 n165 n166 n167 n168 n169)

( node n170 n171 n172 n173 n174 n175 n176 n177 n178 n179)

(node n180 n181 n182 n183 n184 n185 n186 n187 n188 n189)

( node n190 n191 n194 n201 n213 n314 n331 n335 n336 n338)

( node n339 n340 n342 n343 n344 n345 n347 n348 n349

n350)

( node n351 n373 n378 n383 n388 n393 n398 n403 n408 n453)

( node n455 n460 n465 n473 n478 n481 n482 n487 n491

n493)

(node n498 n502 n503 n504 n506 n508 n509 n510 n511 n513)

( node n515 n517 n519 n521 n523 n525 n563 n564 n565 n566)

( node n567 n568 n569 n570 n571 n573 n574 n575 n576 n578)

( node n579 n580 n581 n583 n584 n585 n586 n588 n589 n590)

( node n591 n593 n594 n595 n596 n598 n599 n600 n601 n603)

( node n612 n613 n614 n615 n616 n617 n518 n619 n620 n632)

(node n633 n634 n635 n636 n637 n638 n639 n649 n650 n651)

(node n652 n653 n654 n655 n656)

( node clic2 scantest Reset scanin )

(pin clic2 TOP 0 100 "pintype=clock")

(pin scantest TOP 0 100 "pintype=pi")

(pin scanin TOP 0 100 "pintype=clock" )

( dell n491 n190 n493 n100 clic2 scantest scanin Reset )

( defi n498 n190 n493 n101 clk2 scantest scanin Reset )

(defi n473 n190 n508 n102 clic2 scantest scanin Reset )

(defi n473 n190 n506 n103 clk2 scantest scanin Reset )

( defi n373 n190 n567 n104 cik2 scantest scanin Reset )

(doff n378 n190 n567 n105 clic2 scantest scanin Reset )

(defi n383 n190 n567 n106 cli/2 scantest scanin Reset )

(defi n388 n190 n567 n107 clk2 scantest scanin Reset )

( deff n393 n190 n567 n108 clic2 scantest scanin Reset )

(defi n398 n190 n567 n109 clk2 scantest scanin Reset)

( dell n403 n190 n567 n110 clk2 scantest scanin Reset )

(deff n408 n190 n567 n111 clk2 scantest scanin Reset)

(defi n511 n190 n482 n112 clk2 scantest scanin Reset )

(defi n513 n190 n482 n113 clk2 scantest scanin Reset )

( dell n515 n190 n482 n114 clk2 scantest scanin Reset )

(defi n517 n190 n482 n115 clk2 scantest scanin Reset )

(defi n519 n190 n482 n116 clic2 scantest scanin Reset )

( dell n521 n190 n482 n117 clic2 scantest scanin Reset )

( dolf n523 n190 n482 n118 clic2 scantest scanin Reset )

( deff n525 n190 n482 n1 19 clk2 scantest scanin Reset )

( dell n453 n190 n455 n120 clic2 scantest scanin Reset )

( deff n481 n190 n460 n121 clk2 scantest scanin Reset )

( deff n473 n190 n465 n122 clic2 scantest scanin Reset )

(delf n473 n190 n482 n123 clk2 scantest scanin Reset )

```

(( pin n124 BOTTOM 0 100 "pintype=pi") (pin n125 BOTTOM 0 100 "pintype=pi") (pin n126 BOTTOM 0 100 "pintype=pi") (pin n127 BOTTOM 0 100 "pintype=pi") (pin n128 BOTTOM 0 100 "pintype=pi") (pin n129 BOTTOM 0 100 "pintype=pi") (pin n130 BOTTOM 0 100 "pintype=pi") (pin n131 BOTTOM 0 100 "pintype=pi") (pin n132 BOTTOM 0 100 "pintype=pi") (pin n133 BOTTOM 0 100 "pintype=pi") (pin n134 BOTTOM 0 100 "pintype=pi") (pin n135 BOTTOM 0 100 "pintype=pi") (pin n136 BOTTOM 0 100 "pintype=pi") (pin n137 BOTTOM 0 100 "pintype=pi") (pin n138 BOTTOM 0 100 "pintype=pi") (pin n139 BOTTOM 0 100 "pintype=pi") (pin n140 BOTTOM 0 100 "pintype=pi") (pin n141 BOTTOM 0 100 "pintype=pi") (pin n142 BOTTOM 0 100 "pintype=po") (connect n142 n612) (pin n143 BOTTOM 0 100 "pintype=po") (connect n143 n613) (pin n144 BOTTOM 0 100 "pintype=po") (connect n144 n614) (pin n145 BOTTOM 0 100 "pintype=po") ( connect n145 n615 ) (pin n146 BOTTOM 0 100 "pintype=po") ( connect n146 n616 ) ( pin n147 BOTTOM 0 100 "pintype=po") (connect n147 n617) (pin n148 BOTTOM 0 100 "pintype=po") (connect n148 n618) (pin n149 BOTTOM 0 100 "pintype=po") (connect n149 n619) (pin n150 BOTTOM 0 100 "pintype=po") ( connect n150 n122 ) (pin n151 BOTTOM 0 100 "pintype=po") ( connect n151 n101 ) (pin n152 BOTTOM 0 100 "pintype=po") ( connect n152 n103 ) (pin n153 BOTTOM 0 100 "pintype=po") ( connect n153 n100 ) (pin n154 BOTTOM 0 100 "pintype=po") (connect n154 n102) (pin n155 BOTTOM 0 100 "pintype=po") ( connect n155 n649 ) (pin n156 BOTTOM 0 100 "pintype=po") ( connect n156 n650 ) (pin n157 BOTTOM 0 100 "pintype=po") ( connect n157 n651 ) (pin n158 BOTTOM 0 100 "pintype=po") (connect n158 n652) (pin n159 BOTTOM 0 100 "pintype=po") (connect n159 n653) (pin n160 BOTTOM 0 100 "pintype=po") (connect n160 n654) (pin n161 BOTTOM 0 100 "pintype=po") (connect n161 n655) (pin n162 BOTTOM 0 100 "pintype=po") ( connect n162 n656 )

Figure 4.7: First part of netlist description for one node queue.

123

connect n162 n656 ( pin n163 BOTTOM 0 100 "pintype=po") ( connect n163 n632 ) (pin n164 BOTTOM 0 100 "pintype=po") (connect n164 n633) (pin n165 BOTTOM 0 100 "pintype=po") ( connect n165 n634 ) ( pin n168 BOTTOM 0 100 "pintype=po") ( connect n168 n635 ) (pin n167 BOTTOM 0 100 "pintype-po") ( connect n167 n636 ) (pin n168 BOTTOM 0 100 "pintype=po") ( connect n168 n637 ) ( pin n169 BOTTOM 0 100 "pintype=po") ( connect n169 n638 ) (pin n170 BOTTOM 0 100 "pintype=po") ( connect n170 n639 ) (pin n171 BOTTOM 0 100 "pintype=po") ( connect n171 n343 ) (pin n172 BOTTOM 0 100 "pintype-po") (connect n172 n348) (pin n173 BOTTOM 0 100 "pintype=po") (connect n173 n351) (pin n174 BOTTOM 0 100 "pintype=po") ( connect n174 n335 ) (pin n175 BOTTOM 0 100 'pintype=po') ( connect n175 n336 ) (pin n176 BOTTOM 0 100 "pintype=po") ( connect n176 n338 ) (pin n177 BOTTOM 0 100 'pintype=po') ( connect n177 n339 ) (pin n178 BOTTOM 0 100 "pintype=po") nect n178 n331 ) ( pin n179 TOP 0 100 \*pintype=pi\*) ( pin n180 TOP 0 100 "pintype=pi") (pin n181 TOP 0 100 "pintype=pi") (pin n182 TOP 0 100 "pintype=pi") (pin n183 TOP 0 100 "pintype=pi") (pin n184 TOP 0 100 "pintype=pi") ( pin n185 TOP 0 100 "pintype=pi") ( pin n186 TOP 0 100 "pintype=pi") ( pin n187 TOP 0 100 "pintype=pi") ( pin n188 TOP 0 100 "pintype=pi") ( pin n189 LEFT 0 100 "pintype=reset") ( pin n190 LEFT 0 100 'pintype=clock') (pin n191 TOP 0 100 "pintype=pi") (connect n189 Reset) (i1 n121 n194) (i1 n122 n201) (i1 n120 n213) (i1 n191 n314) ( o4 n172 n174 n177 n176 n331) ( a2 n201 n187 n335) ( a2 n122 n187 n336) (a2 n213 n173 n338) ( a2 n120 n173 n339) ( o3 n124 n125 n123 n340)

(pin n162 BOTTOM 0 100 "pintype=po")

(i1 n340 n342) ( a2 n115 n504 n579) (a2 n188 n342 n343) ( a2 n129 n508 n580) (03 n124 n125 n345 n344) (a2 n137 n506 n581) (i1 n123 n345) (a2 n183 n478 n583) (a2 n116 n504 n584) (i1 n344 n347) (a2 n130 n508 n585) ( #2 n188 n347 n348) ( a2 n138 n506 n586) (i1 n171 n349) (i1 n172 n350) (a2 n184 n478 n588) ( a3 n350 n349 n188 n351) ( a2 n117 n504 n589) ( 04 n563 n564 n565 n566 n373) (a2 n131 n508 n590) ( o4 n568 n569 n570 n571 n378) (a2 n139 n506 n591) (a2 n185 n478 n593) ( o4 n573 n574 n575 n576 n383) (04 n578 n579 n580 n581 n388) (a2 n118 n504 n594) ( o4 n583 n584 n585 n586 n393) (a2 n132 n508 n595) ( o4 n588 n589 n590 n591 n398) (a2 n140 n506 n596) ( o4 n593 n594 n595 n596 n403) (a2 n186 n478 n598) ( o4 n598 n599 n600 n601 n408) (a2 n119 n504 n599) ( o2 n503 n509 n453) (a2 n133 n508 n600) ( o3 n478 n504 n510 n455) (a2 n141 n506 n601) . ( 02 n478 n482 n460) ( a2 n188 n473 n603) ( o2 n478 n502 n465) (a2 n104 n603 n612) (dsff n620 n190 n189 n473 clk2 scantest scanin ) (a2 n105 n603 n613) (a2 n174 n473 n478) (a2 n106 n603 n614) ( a2 n194 n473 n481) (a2 n107 n603 n615) (a2 n175 n473 n482) (a2 n108 n603 n616) (a2 n122 n473 n487) (a2 n109 n603 n617) (a2 n194 n487 n491) (a2 n110 n603 n618) ( #2 n187 n473 n493) (a2 n111 n603 n619) ( a2 n121 n487 n498) ( a2 n473 n314 n620) ( a2 n171 n473 n502) (a2 n112 n100 n632) (a2 n213 n473 n503) (a2 n113 n100 n633) ( a2 n172 n473 n504) (a2 n114 n100 n634) ( a2 n176 n473 n506) (a2 n115 n100 n635) ( a2 n177 n473 n508) (a2 n116 n100 n636) (a2 n213 n473 n509) (a2 n117 n100 n637) (a2 n173 n473 n510) (a2 n118 n100 n638) ( a2 n179 n473 n511) (a2 n119 n100 n639) (a2 n180 n473 n513) (a2 n112 n101 n649) (a2 n181 n473 n515) (a2 n113 n101 n650) ( a2 n182 n473 n517) (a2 n114 n101 n651) ( a2 n183 n473 n519) (a2 n115 n101 n652) (a2 n184 n473 n521) (a2 n116 n101 n653) (a2 n185 n473 n523) ( a2 n117 n101 n654) ( a2 n186 n473 n525) (a2 n118 n101 n655) ( a2 n179 n478 n563) (a2 n119 n101 n656) (a2 n112 n504 n564) (a2 n126 n508 n565) (a2 n134 n506 n566) (a2 n178 n473 n567) ( a2 n180 n478 n568) ( a2 n113 n504 n569) (a2 n127 n508 n570) (a2 n135 n506 n571) (a2 n181 n478 n573) (a2 n114 n504 n574) (a2 n128 n508 n575)

Figure 4.8: Second part of netlist description for one node queue.

( a2 n136 n506 n576)

( a2 n182 n478 n578)