# A New Transformation and Design Technique for Switched Capacitator High Pass Ladder Filters

by

Kemal Mehmet Fidanboylu

A Thesis Presented to the

# FACULTY OF THE COLLEGE OF GRADUATE STUDIES

# KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

# DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

# **MASTER OF SCIENCE**

In

# **ELECTRICAL ENGIEERING**

June, 1987

# **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

University Microfilms International A Bell & Howell Information Company 300 North Zeeb Road. Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

-

Order Number 1355744

# A new transformation and design technique for switched capacitor high pass ladder filters

Fidanboylu, Kemal Mehmet, M.S.

King Fahd University of Petroleum and Minerals (Saudi Arabia), 1987

. •

A NEW TRANSFORMATION AND DESIGN TECHNIQUE FOR SWITCHED CAPACITOR HIGH PASS LADDER FILTERS BY KEMAL MEMMET FIDANBOYLU A Thesis Presented to the MEGULTY OF THE COLLEGE OF GRADUATE STUDIES UNIVERSITY OF PETROLEUM & MINERALS UNIVERSITY OF PETROLEUM & MINERALS

**JUNE 1987**

# KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN, SAUDI ARABIA

### COLLEGE OF GRADUATE STUDIES

This thesis, written by Kemal Mehmet Fidanboylu under the direction of his Thesis Committee, and approved by all its members, has been presented to and accepted by the Dean, College of Graduate Studies, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering.

Dean he Graduate Date

23

Department Chairman

Thesis-Committee

Chai man

Member

LIBRABY KING FAHD UNIVERSITY OF PETROLEUM & MINEBALS Dhahran - 31261, SAUDI ARABIA ~

# This thesis is dedicated to my wife

### ACKNOWLEDGEMENT

Acknowledgement is due to King Fahd University of Petroleum & Minerals for support of this research.

I express my deep gratitude to Dr. Suleyman S. Penbeci who served as my major advisor. I also thank other members of my Thesis Committe, Dr. Gerhard F. Beckhoff and Dr. Ubaid Al-Saggaf to whom I indebted for a detailed review and very constructive criticism of the text material.

I express my thanks and appreciation to my closest brother Ishak Emir for his continuous moral support and for his help in drawing the figures and typing this thesis. Lastly, and in no sense the least, I am thankful to all faculty, colleagues and friends who made my stay at the university a memorable and valuable experience.

#### ABSTRACT

A new technique for the design of switched capacitor highpass ladder filters using the MLDD transformation is proposed. It is shown that by realizing the resistive source termination of the high-pass continuous ladder proto-type filter with a special delay free circuit, a much superior response is obtained. A new transormation named the modified bilinear transformation for the design of switched capacitor high-pass ladder filters is also proposed. Using this transformation and the proposed design tecnique, it is shown that the magnitude response of the switched capacitor high-pass ladder filter approximates the response of the continuous high-pass ladder proto-type much better than the MLDD transformation. However, in some of the applications this is achieved at the cost of a higher order filter. Finally, an interactive package for the design of switched capacitor high-pass Butterworth and Chebychev fiters using the MLDD and the modified bilinear transformations is presented as a bonus.

#### الخلاصية

فى هذا البحث نقترح طريقة جديدة لتصميم مرشح المكثف المفثامن السلمي للامرار الترددات العاليه باستعمــــال تحويل أل م ل ددد وعند استبدال عناية حصاد المقاومـــه فى النموذج الاولي لمرشح امرار الترددات العاليه المستمـر بدائرة اعاقة حرة حصلنا على نتائج متقدمه ٠

فى هذا البحث أيضا أستعملت طريقة تحويل جديدة سميت طريقة التحويل الثنائية الحطيه المعدله لتصميم مرشــــح المكثف المفتاحي لامرار الترددات العاليه • وقد كانــــحت القيمه المطلقه الناتج عن هذا التحويل أفضل بكثير مــــن استعمال تحويل أل م•ل•د•د•

أخيرا استعمل الحاسب الآلي لتصميم مرشحات المكثــــف المفتاحي ال بتردد دث د وتشبثت باستعمال تحويل الـ م •ل•د •د • وطريقة التحويل الثنائيه الخطيه المعدلة •

-vi-

## TABLE OF CONTENTS

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABSTRACT(Arabic)                                                                                                                                                                                                                                                                                                                                                              |

| Chapter I: INTRODUCTION                                                                                                                                                                                                                                                                                                                                                       |

| Historical Background<br>Evolution of Switched-Capacitor Filters                                                                                                                                                                                                                                                                                                              |

| Circuits                                                                                                                                                                                                                                                                                                                                                                      |

| Chapter II: SWITCHED CAPACITOR FILTER DESIGN USING<br>RESISTOR SIMULATION                                                                                                                                                                                                                                                                                                     |

| Parallel SC Resistor Simulation13Operation and Analyses13Effects of Stray Capacitances26Design Example26Series SC Resistor Simulation32Series SC Resistor Simulation39Operation and Analyses39Switched Capacitor Filter Design Using Series37Sc Resistor Simulation47Bilinear SC Resistor simulation53Operation and Analyses53Switched Capacitor Filter Design Using Bilinear |

| Resistor Simulation                                                                                                                                                                                                                                                                                                                                                           |

| Chapter III: SWITCHED CAPACITOR LADDER FILTER DESIGN . 61<br>Use of LDI Transformation in the Design of SC                                                                                                                                                                                                                                                                    |

| Ladder Filters                                                                                                                                                                                                                                                                                                                                                                |

| Transformation                                                                                                                                                                                                                                                                                                                                                                |

| Ladder Filters                                                                                                                                                                                                                                                                                                                                                                |

•

| Use of MLDD Transformation in the Design of SC<br>High-Pass Ladder Filters                                       |

|------------------------------------------------------------------------------------------------------------------|

| Chapter IV: A NEW SWITCHED CAPACITOR HIGH-PASS<br>FILTER REALIZATION USING THE MLDD<br>TRANSFORMATION            |

| Design Procedure<br>SFG Synthesis of High-Pass SC Ladder Filters                                                 |

| Pass SC Ladder Filters                                                                                           |

| Prototype                                                                                                        |

| Chapter V: A NEW TRANSFORMATION FOR THE DESIGN OF<br>SWITCHED CAPACITOR HIGH-PASS LADDER                         |

| FILTERS                                                                                                          |

| The Modified Bilinear Transformation109Definition and Mapping Properties109Warping Effects114Design Procedure116 |

| Building Block For Realizing the Modified<br>Bilinear Transfer Function                                          |

| Termination    124      Design Example    130                                                                    |

| Chapter VI: AN INTERACTIVE PACKAGE FOR DESIGNING<br>SWITCHED CAPACITOR HIGH-PASS LADDER<br>FILTERS               |

| 137                                                                                                              |

| Description of Package                                                                                           |

| Chapter VII: CONCLUSIONS                                                                                         |

| Comparison of Results                                                                                            |

| Appendix A:  | HPSC1 | FORTR  | AN FII | Æ | • | • | • | • | • | • | • | • | • | • | • | • | 150 |

|--------------|-------|--------|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| Appendix B:  | HPSC1 | EXEC ] | FILE   | • | • | • | • | • | • | • | • | • | • | • | • | • | 195 |

| Appendix C:  | HPSC2 | FORTRA | AN FIL | Æ | • | • | - | • | • | • | • | • | • | • | • | • | 196 |

| Appendix D:  | HPSC2 | EXEC I | FILE   | • | • | • | • | • | • | • | • | • | • | • | • | • | 199 |

| BIBLIOGRAPHY | (     |        | •••    | • | • | • | • | - | - | • | • | • | • | • | • | • | 200 |

.

- ix -

# LIST OF FIGURES

.

| Figu | re                                                  | Page |

|------|-----------------------------------------------------|------|

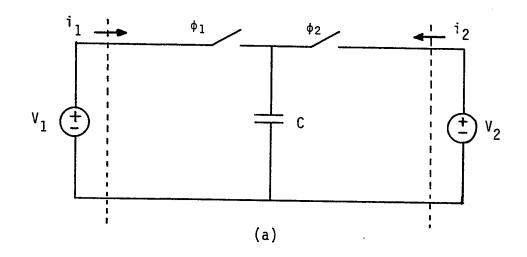

| 1.1  | (a) Parallel switched capacitor realization         |      |

|      | of a continuous resistor. (b) Continuous            |      |

|      | Resistor                                            | . 4  |

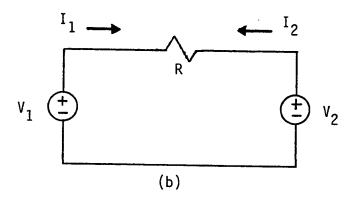

| 1.2  | Waveform of the two phase non-overlapping           |      |

|      | clock used in SC filters                            | . 5  |

| 1.3  | (a)Processing of an analog signal through a         |      |

|      | switched capacitor filter. (b) Typical mag-         |      |

|      | nitude responses                                    | . 11 |

| 2.1  | Active-RC Integrator                                | 14   |

| 2.2  | Switched Capacitor version of an active-RC          |      |

|      | integrator using a parallel equivalent              |      |

|      | branch for resistor simulation                      | 16   |

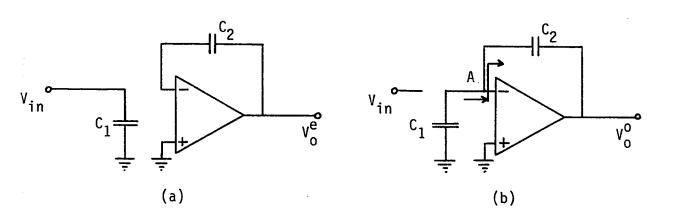

| 2.3  | Operation of the switched capacitor inte-           |      |

|      | grator of Fig. 2.2; (a) during odd phase            |      |

|      | (b) during even phase (c) Equivalent cir-           |      |

|      | cuit for the capacitors showing the charge          |      |

|      | storage at t=(n-1/2)T and (d) at t=nT $\dots \dots$ | 18   |

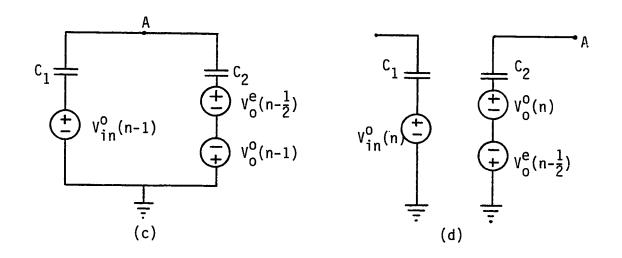

| 2.4  | Illustration of the parasitic capacitances          |      |

|      | due to the switches $M_1$ and $M_2$ of the SC       |      |

|      | integrator shown in Fig. 2.2                        | 27   |

| 2.5  | Switched Capacitor integrator of Fig. 2.2,          |      |

|      | showing the combined effect of the parasi-          |      |

|      | tic capacitances                                    | 29   |

- x -

123B

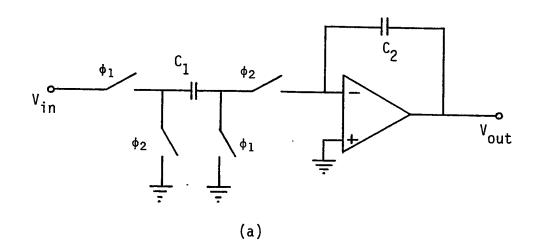

| 2.6  | (a) Stray-insensitive SC integrator (b)              |

|------|------------------------------------------------------|

|      | Analog integrator with negative resistance 31        |

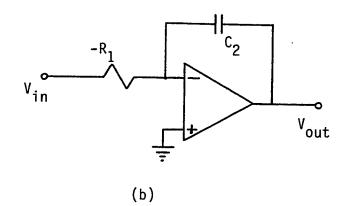

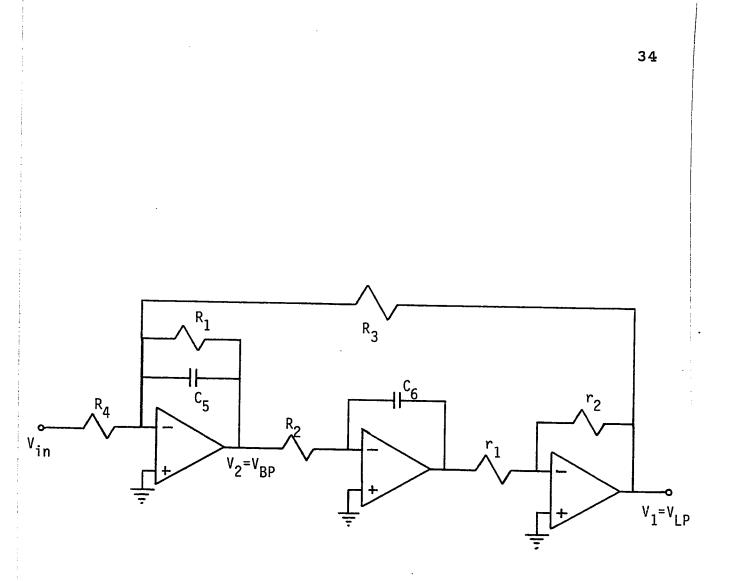

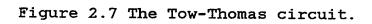

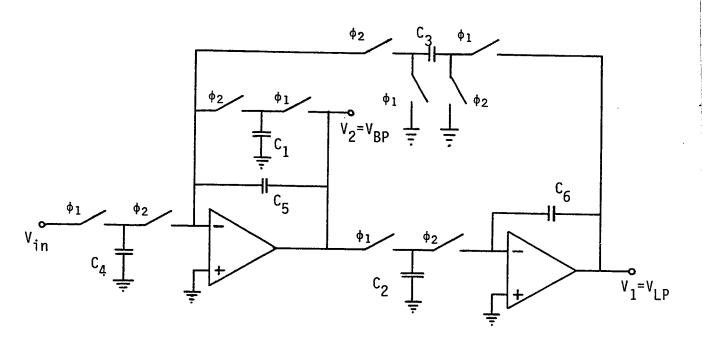

| 2.7  | The Tow-Thomas circuit                               |

| 2.8  | Switched Capacitor realization of the Tow-           |

|      | Thomas circuit using parallel SC equivalent          |

|      | branches                                             |

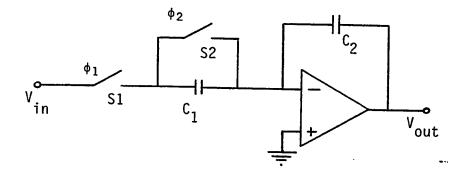

| 2.9  | Switched Capacitor Integrator using a                |

|      | series equivalent branch for resistor simu-          |

|      | lation                                               |

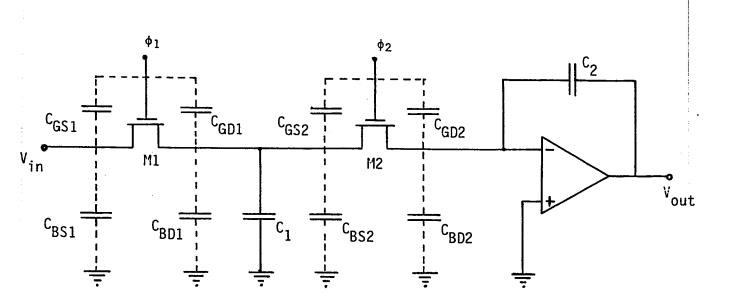

| 2.10 | Operation of the switched capacitor inte-            |

|      | grator of Fig. 2.9; (a) during odd phase             |

|      | (b) during even phase (c) Equivalent cir-            |

|      | cuit for the capacitors showing the charge           |

|      | storage at t=(n-1)T and (d) at t=(n-1/2)T $\dots$ 41 |

| 2.11 | Stray-insensitive version of the switched            |

|      | capacitor Integrator shown in Fig. 2.9 46            |

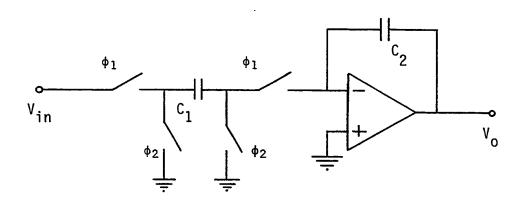

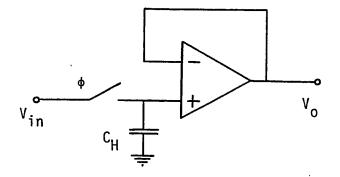

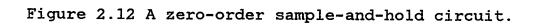

| 2.12 | A zero-order sample-and-hold circuit 48              |

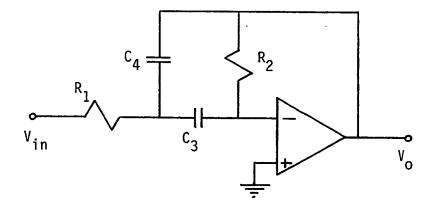

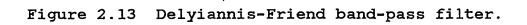

| 2.13 | Delyiannis-Friend band-pass filter 50                |

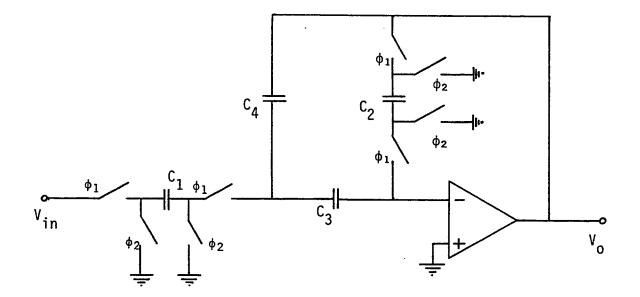

| 2.14 | Switched capacitor implementation of Fig.            |

|      | 2.13                                                 |

| 2.15 | (a) Bilinear SC integrator (b) Equivalent            |

|      | circuit for the charge distribution at               |

|      | t=(n-1)T (c) Equivalent circuit for the              |

|      | charge distribution at t=( $n-1/2$ )T                |

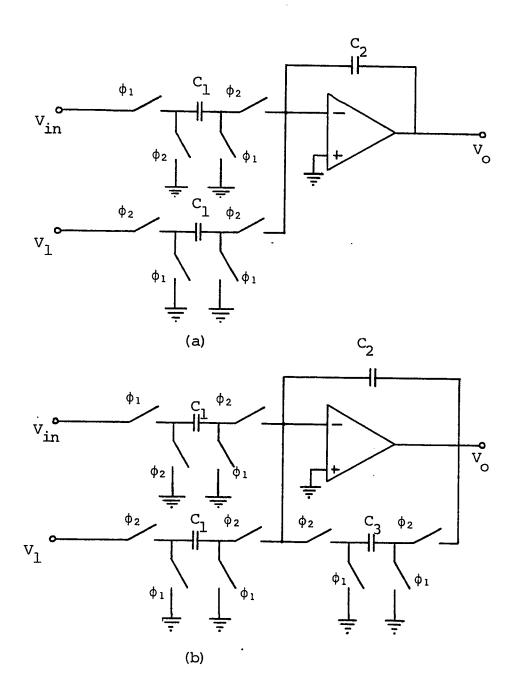

| 3.1  | Warping effect of the LDI transformation 64          |

- xi -

1238

٠

.

•

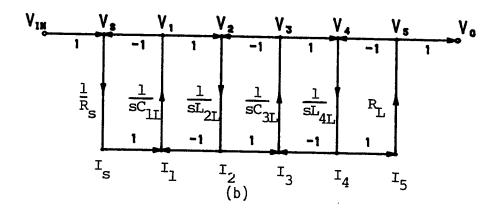

| 3.2 | (a) Fourth order doubly terminated all pole                                              |

|-----|------------------------------------------------------------------------------------------|

|     | low-pass filter. (b),(c) Signal-Flow-Graph                                               |

|     | of (a)                                                                                   |

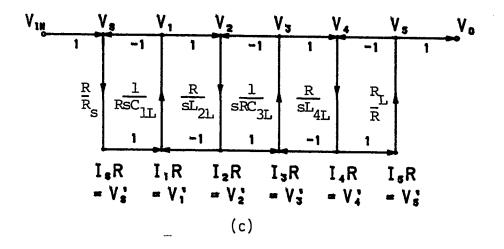

| 3.3 | (a) A differential input SC LDI building                                                 |

|     | block. (b) Modified LDI building block to                                                |

|     | realize the resistive source termination 71                                              |

| 3.4 | Warping effect of the Bilinear transforma-                                               |

|     | tion                                                                                     |

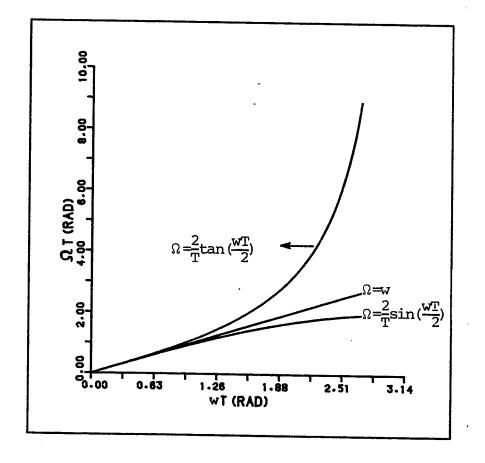

| 3.5 | First order low-pass SC building block                                                   |

|     | realizing the bilinear transfer function 78                                              |

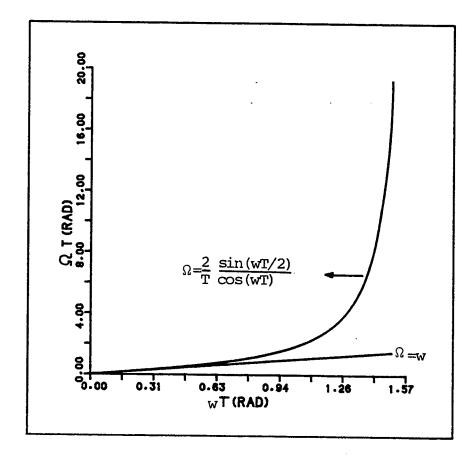

| 3.6 | Warping effect of the MLDD transformation 82                                             |

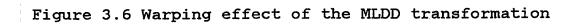

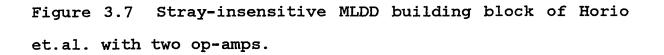

| 3.7 | Stray-insensitive MLDD building block of                                                 |

|     | Horio et.al. with two op-amps 83                                                         |

| 3.8 | Single op-amp MLDD building block of Horio                                               |

|     | et. al                                                                                   |

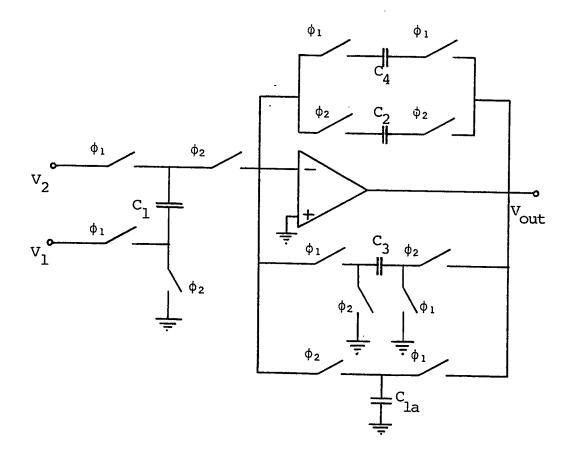

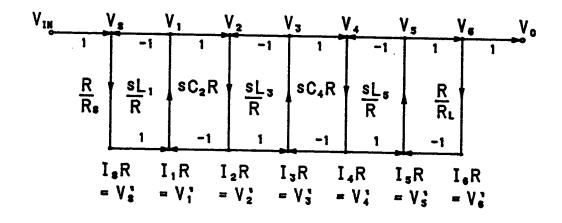

| 4.1 | SFG for an n'th order high-pass continuous                                               |

|     | Chebychev filter(n even)                                                                 |

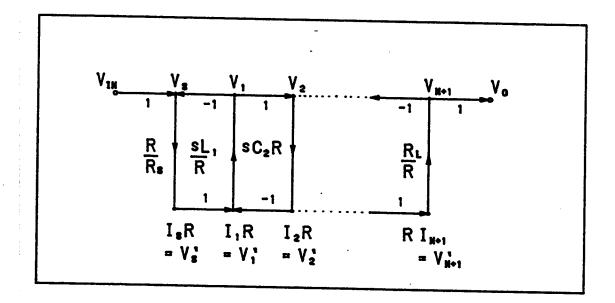

| 4.2 | Stray-insensitive, fully differential MLDD                                               |

|     | building Block                                                                           |

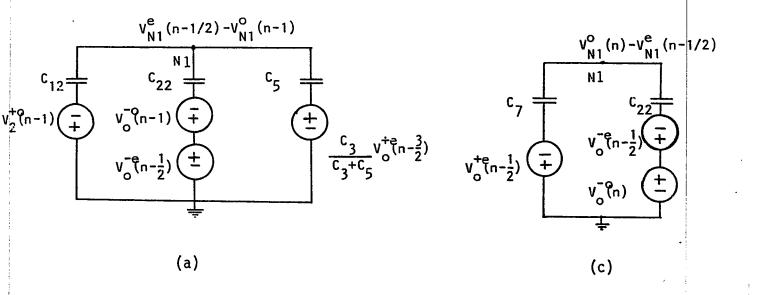

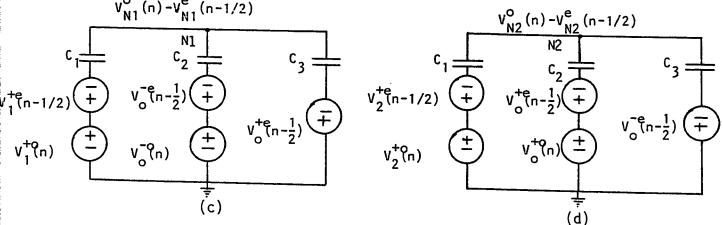

| 4.3 | Equivalent circuit for the charge distribu-                                              |

|     | tion (a) at node N1 when $t=(n-1/2)T$ (b) at                                             |

|     | node N2 when $t=(n-1/2)T$ (c) at node N1 when                                            |

|     | t=nT (d) at node N2 when t=nT $\dots \dots \dots \dots \dots \dots \dots \dots \dots 96$ |

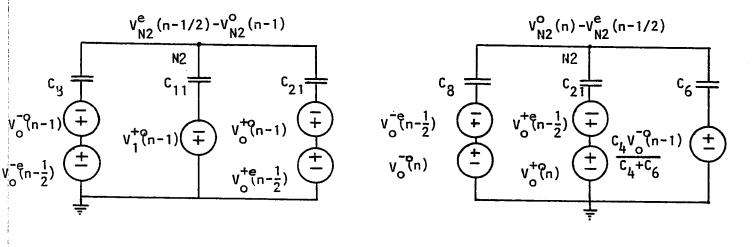

| 4.4 | (a) Stray-insensitive op-amp for realizing                                               |

|     | the resistive source termination (b)                                                     |

|     | Equivalent circuit for the charge distribu-                                              |

|     | tion at the inverting input for $t=(n-1/2)T.$ 100                                        |

|     |                                                                                          |

- xii -

123в

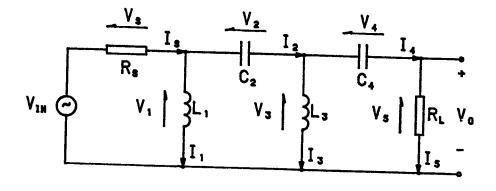

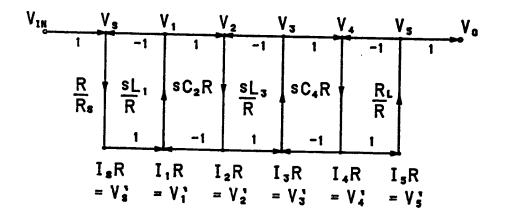

| 4.5 | (a) Fourth order continuous high-pass Che-     |

|-----|------------------------------------------------|

|     | bychev ladder filter. (b) SFG of 4.5(a) 102    |

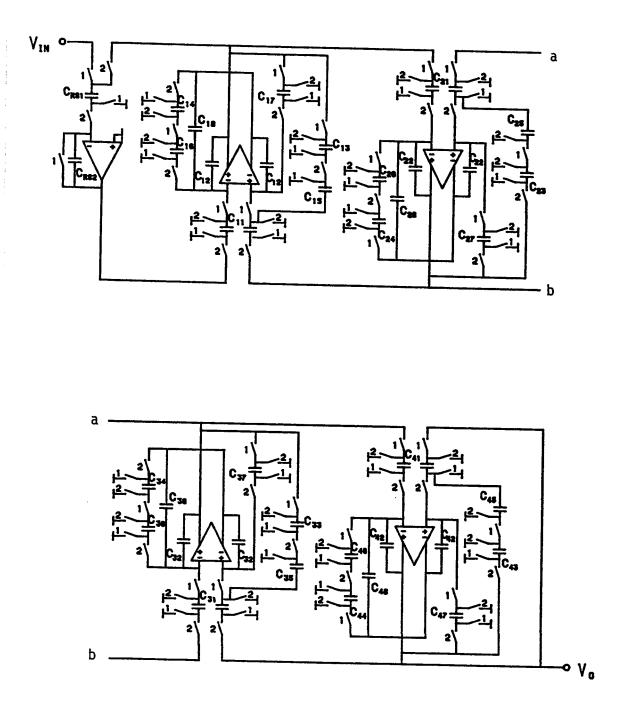

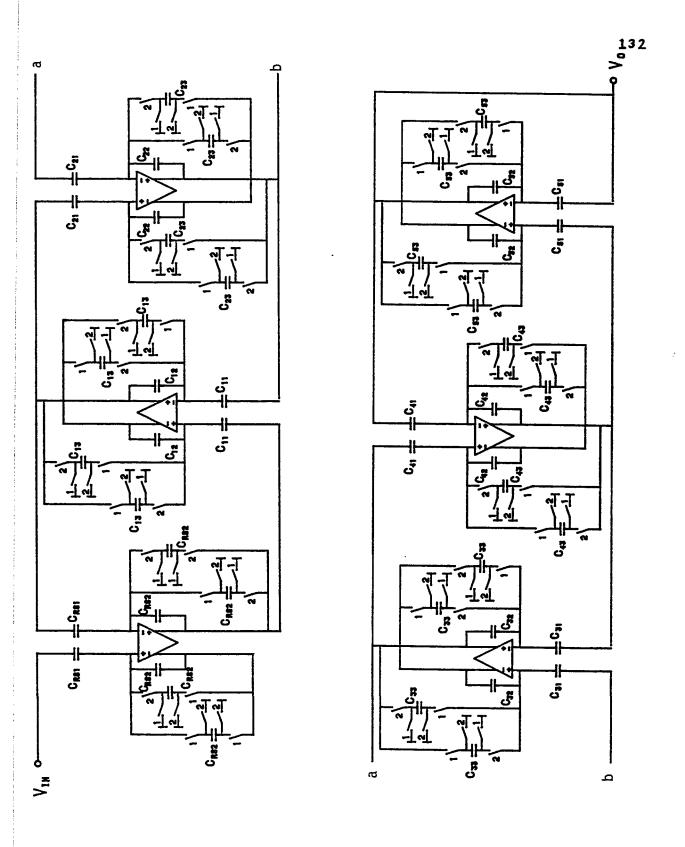

| 4.6 | Fourth order SC high-pass Chebychev ladder     |

|     | filter based on the MLDD transformation 104    |

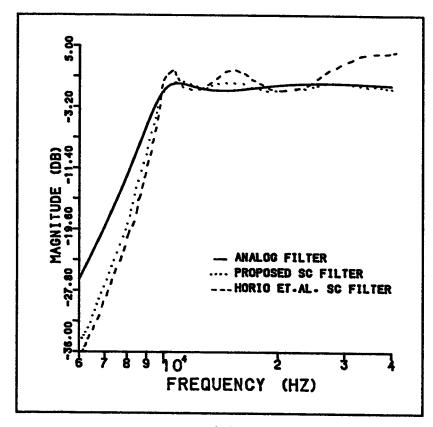

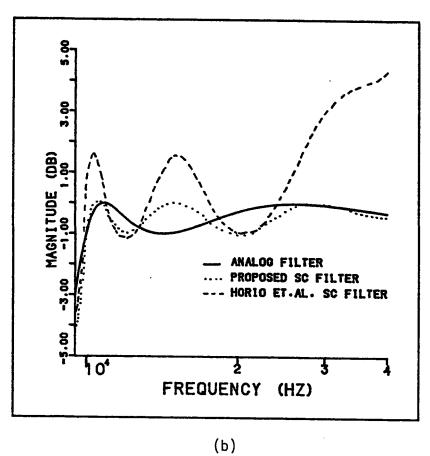

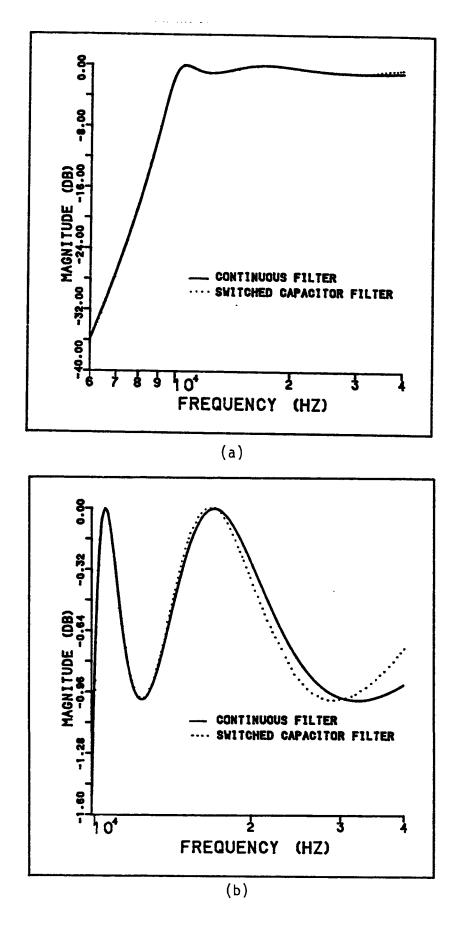

| 4.7 | Simulated responses of design example 108      |

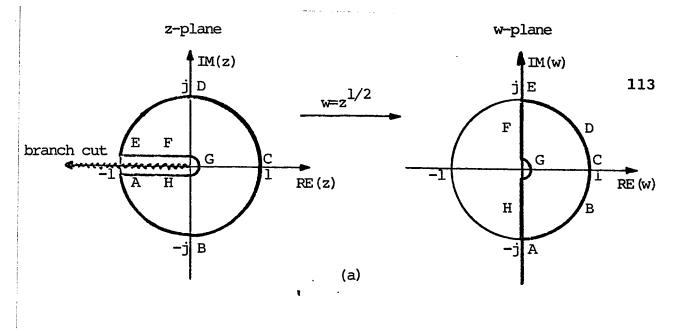

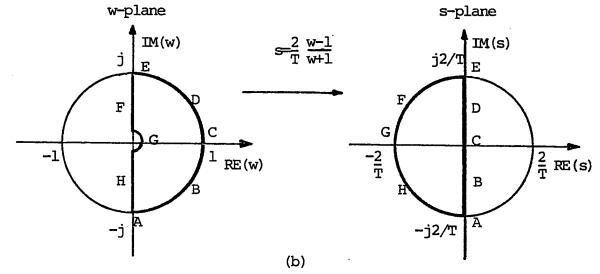

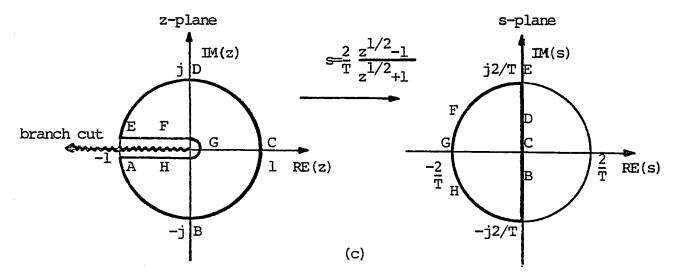

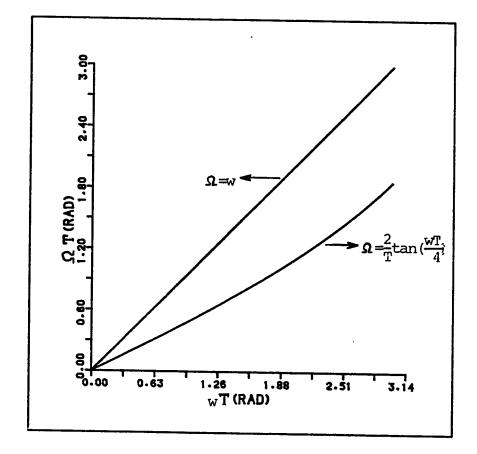

| 5.1 | Mapping properties of the modified bilinear    |

|     | transformation.                                |

| 5.2 | Warping effect of the modified bilinear        |

|     | transformation.                                |

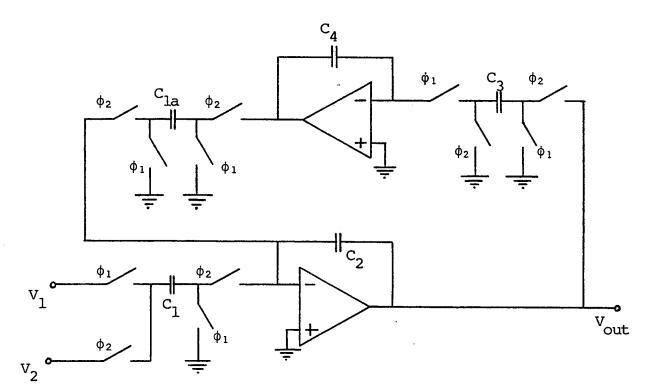

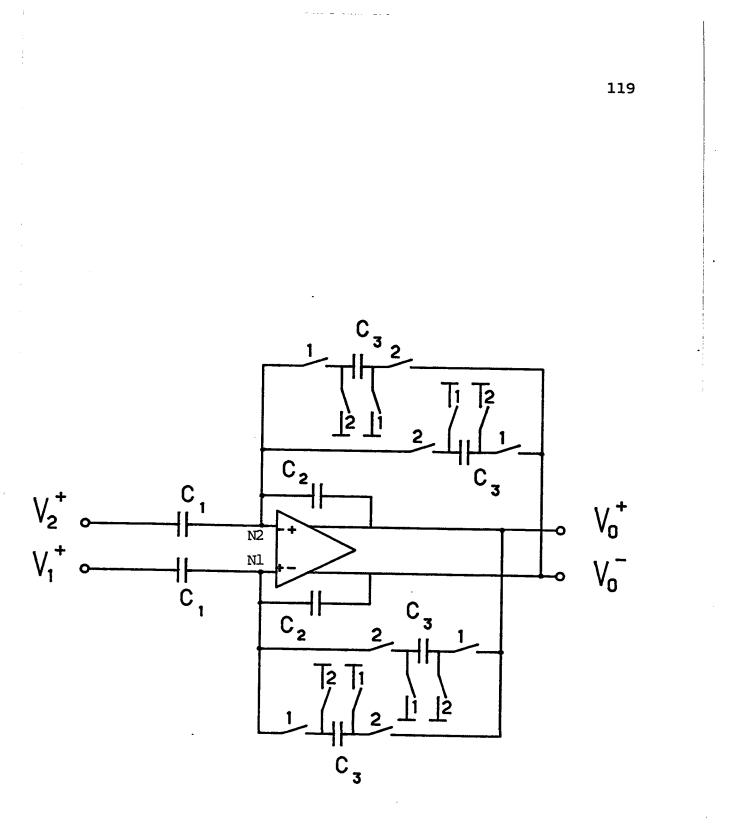

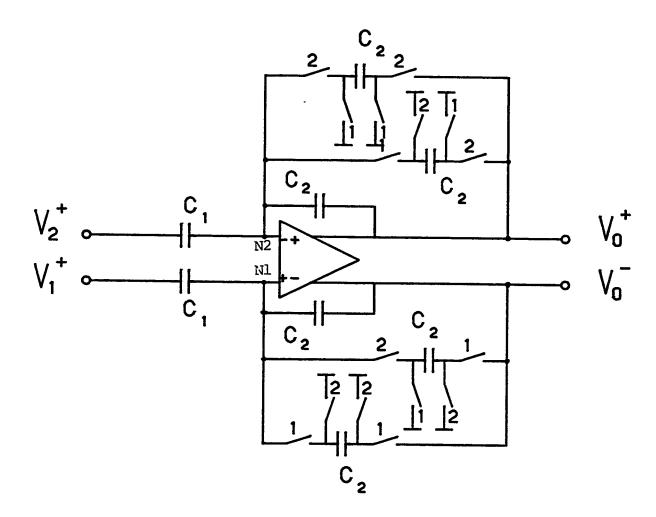

| 5.3 | Stray-insensitive, fully differential          |

|     | building block for realizing the modified      |

|     | bilinear transfer function                     |

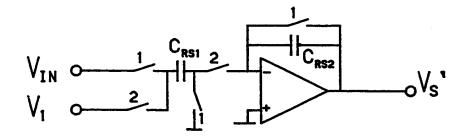

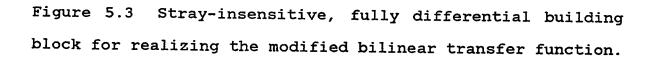

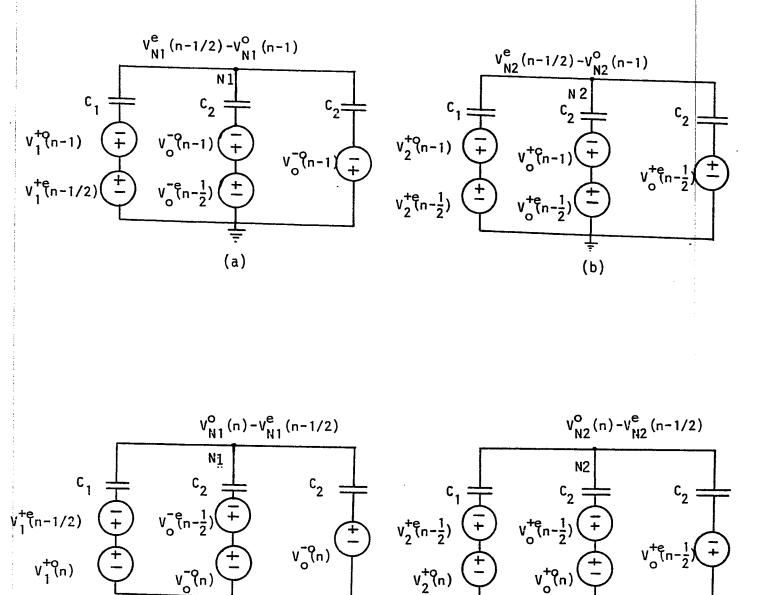

| 5.4 | Equivalent circuit for the charge distribu-    |

|     | tion of Fig. 5.3  (a) at node N1 when          |

|     | t=(n-1/2)T (b) at node N2 when $t=(n-1/2)T$    |

|     | (c) at node N1 when t=nT (d) at node N2        |

|     | when $t=nT$                                    |

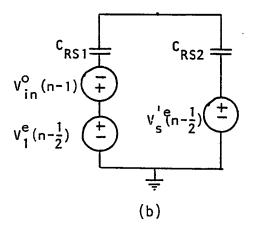

| 5.5 | Stray-insensitive op-amp for realizing the     |

|     | resistive source termination to be used in     |

|     | the design of SC high-pass ladder filters      |

|     | using the modified bilinear transformation 125 |

| 5.6 | Equivalent circuit for the charge distribu-    |

|     | tion of Fig. 5.5  (a) at node N1 when          |

|     | t=(n-1/2)T (b) at node N2 when $t=(n-1/2)T$    |

|     | (c) at node N1 when t=nT (d) at node N2        |

|     | when $t=nT$                                    |

|     |                                                |

- xiii -

| 5.7 | (a) Fifth order high-pass continuous Cheby- |

|-----|---------------------------------------------|

|     | chev ladder filter. (b) SFG of 5.7(a) 131   |

| 5.8 | Fifth order SC high-pass Chebychev ladder   |

|     | filter based on the modified bilinear       |

|     | transformation                              |

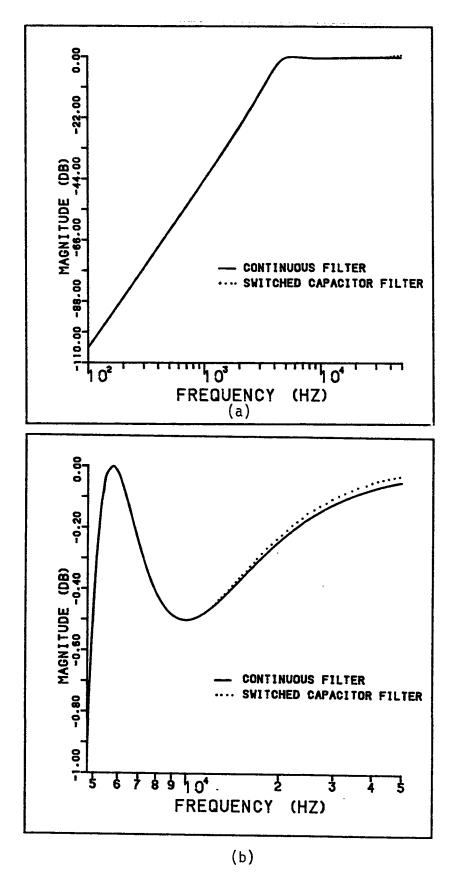

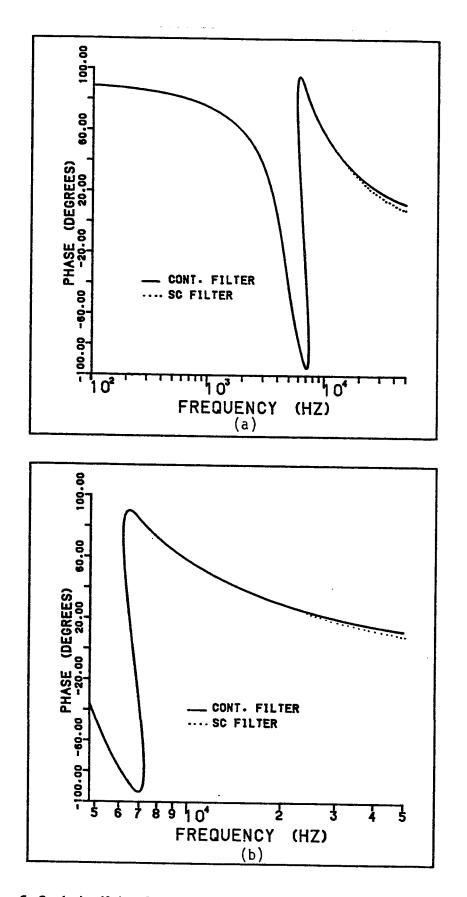

| 5.9 | (a),(b) Simulated responses of design exam- |

|     | ple                                         |

| 6.1 | (a),(b) Magnitude response of a third order |

|     | SC high-pass Chebychev ladder filter 142    |

| 6.2 | (a),(b) Phase response of a third order SC  |

|     | high-pass Chebychev ladder filter           |

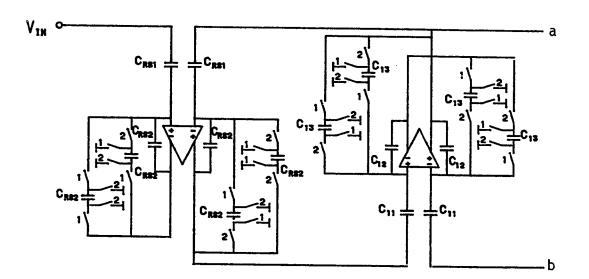

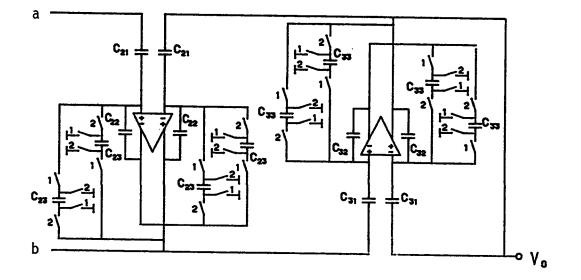

| 6.3 | Third order SC high-pass Chebychev ladder   |

|     | filter                                      |

# Chapter I INTRODUCTION

#### 1.1 Historical Background

The realization of passive RLC filters started in the 1920s[18]. Since inductors are physically large, electrically lossy and noisy, and unsuitable for miniaturization, their replacement by active-RC filters began in the mid 1960s[5,20]. The evolution of active-RC filters was mainly due to the development of low-cost high-performance monolithic operational amplifiers. The next step in miniaturization was the realization of fully integrated filters which started in the early 1970s. This technique makes use of metal-oxide-semiconductor(MOS) integrated circuit technology which offers high quality capacitors, low-leakage charge storage and offset-free switches[20]. However, direct integration of an active-RC filter leads to difficulties.

Active-RC filters are mainly used in telecommunication applications which require time constants of the order 0.1 milli-seconds. In integrated circuits, MOS capacitors are usually made smaller than 100pF, because for an oxide thickness of 700 Angstroms, a 1pF capacitor requires about 3 milsquare chip area. With a capacitor of 10pF, a time constant

- 1 -

123B

of the order 0.1 milli-seconds can be accomplished with a resistor of the order 10 Mega-Ohms. Such a resistor made by using a poly-silicon line occupies an area of 1600 mil-square, which is approximately 10 percent of the average chip area of an analog MOS integrated circuit[20]. There-fore, the large chip area required for constructing an integrated resistor is a major difficulty in the direct integra-tion of active-RC filters.

The second major difficulty of MOS resistors is their non-linear characteristics. Furthermore, since both capacitors and resistors have absolute accuracies in the range of 5-10 percent, and their errors are uncorrelated, the overall error of the RC time constant can be as high as 20 percent. This error also depends on the temperature and signal level[20].

#### 1.2 Evolution of Switched-Capacitor Filters

The difficulties in the direct integration of active-RC filters can be overcome by simulated resistors which are obtained by periodical switching of capacitors between two circuit nodes at a sufficiently high rate. The type of filters emerging from this theory are called switchedcapacitor(SC) filters which are analog sampled data circuits[23]. The periodic sampling of analog signals have been used for many years. The first known record of sampling analog signals is found on pages 420-425 of "Treatise on Elec-

2

tricity and Magnetism" by James Clerk Maxwell[1]. The theory of sampling analog signals was further developed in the late 1950s and several schemes that used switches and capacitors to simulate filters were proposed in the 1960s[13,16]. However, the practical realization of integrated circuit switched-capacitor filters was possible only in the late 1970s[5,23] when MOS technology provided high-quality capacitors, offset-free switches, and moderate quality op-amps.

To show that a simulated resistor can be constructed from capacitors and switches, consider the circuit given in Fig. 1.1(a). Without any loss of generality, assume that both switches are open and the capacitor C is initially discharged. It is further assumed that the voltage sources  $V_1$  and  $V_2$  are constant during all or most of the phase period. The clock waveforms used for driving the switches are shown in Fig. 1.2. As it can be observed from these waveforms, the phases  $\phi_1$  and  $\phi_2$  are non-overlapping. At t=(n-3/2)T+t<sub>1</sub>, the clock pulse  $\phi_1$  is applied to switch 1. This pulse closes switch 1 and causes a charge transfer from the voltage source  $V_1$  to the capacitor. In practice, a finite resistance R is associated with the switch. This resistance which is connected in series with the capacitor prevents the instantaneous charging of the capacitor C. Definitely, the RC time constant must be much smaller than T/2 in order to let the capacitor charge completely to  $\mathtt{V}_1$

238

Figure 1.1 (a) Parallel switched capacitor realization of a continuous resistor. (b) Continuous Resistor.

Figure 1.2 Waveform of the two phase non-overlapping clock used in SC filters.

The charge transfered to the capacitor while switch 1 was closed can be written as

$$Q((n-1)T) = CV_1$$

(1.1)

At t=(n-1)T+t<sub>1</sub>, the clock pulse  $\phi_2$  is applied to switch 2, while just before this time, due to the non-overlapping characteristics of the clock waveforms, the clock pulse  $\phi_1$ has already gone to the its low state and switch 1 has opened. During this period, the capacitor is discharged and then charged to V<sub>2</sub>, therefore the net charge transferred to the capacitor becomes

$$Q((n-1/2)T) = CV_2 - CV_1 = C(V_2 - V_1)$$

(1.2)

At t=(n-1/2)T+t<sub>1</sub>, the clock pulse  $\phi_1$  is again applied to switch 1, while just before this time the clock pulse  $\phi_2$  has gone to its low state. Therefore, the state of the two switches, 1 and 2 in this time interval become closed and open respectively. The capacitor is again discharged and then charged to V<sub>1</sub>. The net charge transferred to the capacitor becomes

23B

$$Q(nT) = C(V_1 - V_2)$$

(1.3)

7

This sequence of events will continue indefinitely and the net charge transfer for the even and odd phase periods are given by equations (1.2) and (1.3) respectively. To show that the two switches and the capacitor shown in Fig. 1.1(a) simulate the resistor of Fig. 1.1(b), we proceed as follows: First, define the resistance of Fig. 1.1(b) as

$$R = \frac{V_1 - V_2}{I_1} = \frac{V_2 - V_1}{I_2}$$

(1.4)

under the assumption that  $V_1$  and  $V_2$  are constants. The current flowing in a circuit is defined by

$$i = \frac{dq}{dt}$$

(1.5)

Therefore, under the steady state condition, the charge flowing from the left dotted line of Fig. 1.1(a) can be written as

$$Q_{l} = \int_{(n-1/2)T+t}^{nT+t} \int_{1}^{i} dt$$

(1.6)

But, since switch 1 is open for  $(n-1)T+t_1 \le t < (n-1/2)T+t_1$ , then  $i_1=0$  during this time interval. Therefore, equation (1.6) can be written as

$$Q_{l} = \int_{(n-1)T+t}^{nT+t} \int_{1}^{i} dt$$

(1.7)

8

Since  $Q_1$  given by equation (1.7) is equal to the charge given by Eq. (1.3), we obtain, after equating these two equations and dividing by T

$$\frac{1}{T}Q(nT) = \frac{1}{T}\int_{(n-1)T+t}^{n+t} \frac{1}{1}dt = I \text{ (aver)}$$

(1.8)

Substituting equation (1.3) into (1.8) gives

$$\frac{V_1 - V_2}{I_1 (\text{aver})} = \frac{T}{C}$$

(1.9)

Comparing Eq. (1.4) and (1.9), the following relationship is obtained

$$R = \frac{T}{C}$$

(1.10)

The above relationship is valid when  $I_1=I_1(aver)$ . This occurs when  $V_1$  and  $V_2$  are constant during the clock period T. Therefore, under the above assumptions, we have shown that a capacitor with two switches driven by two nonoverlapping clock pulses simulates a resistor of value T/C[5,23].

It can be concluded from the above results that an active-RC filter can now be realized by replacing all resistors by equivalent SC branches. A time constant  $T_1 = R_1 C_2$  will be transformed according to equation (1.10) into a new time constant  $T_2 = TC_2/C_1$ . If we let the clock frequency  $f_c = 1/T$ , then this new time constant becomes  $T_2 = C_2 / f_c C_1$ , which depends on the ratio of two capacitances and the clock frequency f<sub>c</sub>. The clock frequency f<sub>c</sub> can be accurately controlled by using a crystal resonator in the clock oscillator and the capacitor ratios can be realized to an accuracy as good as 0.1 percent in MOS technology. Therefore, the new time constant can be made as accurate as 0.1-0.5 percent. Furthermore, the area for resistors is highly reduced by using SC equivalent branches. For a resistor value of R=10 Mega-Ohms, if a 100KHz clock frequency is applied, then equation (1.10) dictates a capacitance value of C=1pF. The new area occupied by this capacitor is about 3 mil-square compared to an area of 1600 mil-square required to construct the above mentioned resistance value. This means that by replacing the above resistance with its equivalent SC branches a reduction in chip area has been accomplished by a factor of 533[20].

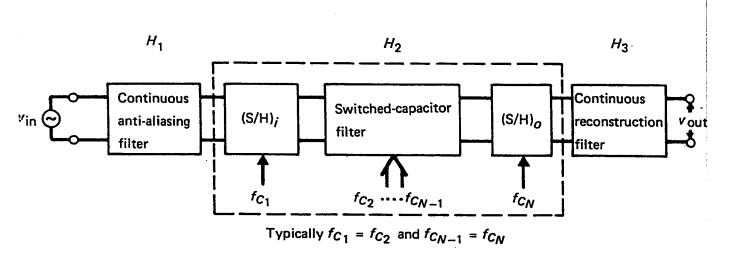

#### 1.3 Switched Capacitor Filters as Analog Sampled Data Circuits

As was mentioned earlier, switched capacitor filters are analog sampled data circuits. Due to this property, they are most conveniently analyzed and designed like digital filters, in the z-transform domain. The system given in Fig. 1.3(a) shows the most general form of a switched capacitor network[17]. An analog signal that requires filtering is first passed through a continuous anti-aliasing filter. This is usually a second order low-pass active-RC filter with a sufficiently high cut-off frequency which converts the infinite bandwidth input signal into a band-limited one. The band-limited analog signal is then passed through an input sample-and-hold circuit (S/H); and is sampled at intervals of 1/f<sub>c1</sub>. The discrete signal coming from the output of the sample-and-hold circuit passes through the desired SC filter. The filtered discrete signal is again passed through an output sample-and-hold circuit (S/H), and is resampled at intervals of  $1/f_{cN}$ . Finally, the desired signal coming from the output of the sample-and-hold circuit passes through a continuous reconstruction filter which converts the sharp transitions in the sampled-data waveform into smooth ones. The typical magnitude responses of the three filters used in an SC network are depicted in Fig. 1.3(b).

10

(a)

Figure 1.3 (a)Processing of an analog signal through a switched capacitor filter. (b) Typical magnitude responses

11

123B

Theoretically, a switched capacitor network can be controlled by multiple clock frequencies. However, usually in practice, two phase clocks are used. In most of the cases, the sample-and-hold operations are inherently performed by the SC filter. When this is so, the SC filter includes the three blocks shown inside the dashed rectangle. Furthermore, if the input or the output of the SC network is interfaced with another digital or sampled-data filter, such as D/A or A/D converters, some of the hardware shown in Fig. 1.3(a) is not necessary. As an example, suppose that the output is interfaced with a digital circuit, then, in such a case, the continuous reconstruction filter is not anymore needed and the sample-and-hold circuit is usually incorporated with the digital circuitry. However, a drawback to this case is the extra requirement of synchronization between the clocks that control the SC filter and those that control the external sampling operations.

12

#### Chapter II

# SWITCHED CAPACITOR FILTER DESIGN USING RESISTOR SIMULATION

The simplest SC filter design technique is the direct replacement of resistors in an active-RC filter by their SC equivalents. In this technique, the active-RC filter is first designed to meet certain desired specifications. The details of active-RC filter design can be found in references[9,17,24,25,33,38] listed in the bibliography. Once the active-RC filter is designed, each resistor is replaced by an SC equivalent circuit which will be described in the following Sections.

#### 2.1 Parallel SC Resistor Simulation

#### 2.1.1 Operation and Analyses

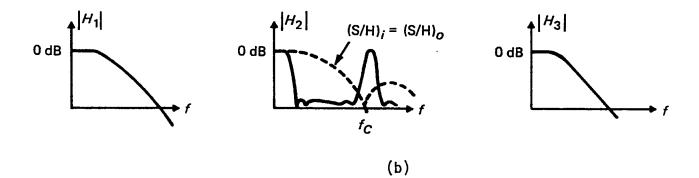

It has been shown in Chapter 1 that the switched capacitor shown in Fig. 1.1 simulates a resistor of value  $R=1/f_{\rm C}C$ . This configuration is called parallel SC realization of a resistance. Before proceeding into further design details, consider the active-RC integrator shown in Fig. 2.1. It is a known fact that the circuit shown in Fig. 2.1 is a basic building block of active-RC filters. The input output relation is given by

- 13 -

123E

123в

$$v_{out}(t) = \frac{-1}{R_1 C_2} \int_{-\infty}^{t} v_{in}(\tau) d\tau$$

(2.1)

Taking the Laplace transform of both sides of equation (2.1), we obtain

$$V_{out}(s) = \frac{-V_{in}(s)}{sR_{i}C_{i}}$$

(2.2)

The switched capacitor version of the active RC-integrator shown in Fig. 2.1 can be obtained by replacing  $R_1$  by its parallel SC equivalent circuit. The resulting SC integrator circuit is shown in Fig. 2.2. The clock waveforms  $\phi_1$  and  $\phi_2$ are shown in Fig. 1.2. The circuits shown in Fig. 2.1 and Fig. 2.2 are equivalent only when the sampling frequency  $f_c$ is much higher than the 3-dB frequency of the input signal. Actually, even under these conditions, these two circuits are not exactly equivalent. In order to observe the exact relation between an active-RC integrator and an SC integrator, it is necessary to analyze the SC integrator circuit using sampled data techniques.

Switched capacitor circuits are usually analyzed by making use of the law of conservation of charges rather than Kirchoff's Current Law. This law makes the analysis much easier since charges in an SC network remain finite in contrast to currents which can sometimes be impulses. Furthermore, the charges in an SC network are stored charges and

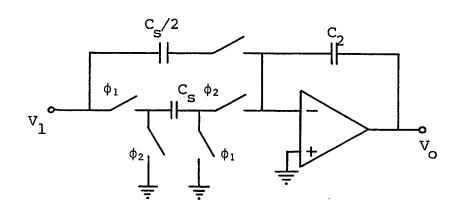

Figure 2.2 Switched Capacitor version of an active-RC integrator using a parallel equivalent branch for resistor simulation.

123в

the storage devices are the plates of a capacitor[36].

The operation of the SC circuit shown in Fig. 2.2 at different clock phases is depicted in Fig. 2.3(a) and Fig. 2.3(b). The description of this operation is given below. At t=(n-1)T, switch 2 has been closed long enough to charge the capacitor  $C_1$  to a voltage  $V_{in}(n-1)$ , while switch 2 was open. During this time, the input was isolated from the output and the capacitor  $C_2$  maintains its previous charge. At t=(n-1)T+t<sub>1</sub>, the clock pulse  $\phi_2$  goes to its high state and switch 2 becomes closed while switch 1 has already opened. Therefore, the capacitor  $C_1$  becomes isolated from the input voltage and the charge stored during the previous state is transfered to the capacitor  $C_2$  in the direction as shown in Fig. 2.3(b).

At t=(n-1/2)T, the charge distribution due to one full period is complete and the charge transfer is repeated again for all the other clock periods. To distinguish the charge transfer which takes place when the clock waveform  $\phi_1$  is high, from the one when the clock waveform  $\phi_2$  is high, let the clock phase  $\phi_1$  represent the odd phase and the clock waveform  $\phi_2$  represent the even phase. Then, the charge associated with the odd phase will be represented by the superscript "o" and the charge associated with the even phase will be represented by the superscript "e" on the voltages

17

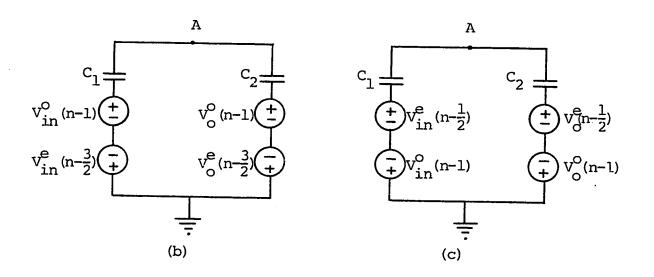

Figure 2.3 Operation of the switched capacitor integrator of Fig. 2.2; (a) during odd phase (b) during even phase (c) Equivalent circuit for the capacitors showing the charge storage at t=(n-1/2)T and (d) at t=nT

123B

characterizing these charges.

The charge stored on a capacitor at any phase can be represented by a voltage source in series with that capacitor, where the polarity of the voltage source represents the polarity of the stored charge. Using this representation, the charge storage on the two capacitors  $C_1$  and  $C_2$  is depicted in Fig. 2.3(c), where the op-amp has been omitted for clarity.

To obtain the difference equation characterizing the operation of the circuit, the conservation of charge law is applied at node A of Fig. 2.3(c). The resulting difference equation is given by

$$C_1 V_{in}^{o}(n-1) + C_2 V_{o}^{e}(n-1/2) - C_2 V_{o}^{o}(n-1) = 0$$

(2.3)

Taking the z-transform of both sides of equation (2.3), we obtain

$$C_1 z^{-1} V_{in}^0(z) + C_2 z^{-1/2} V_0^e(z) - C_2 z^{-1} V_0^0(z) = 0$$

(2.4)

As was mentioned earlier, during the odd phases, the capacitor  $C_2$  maintains the charge acquired from the previous even phase. Therefore at t=nT, the equivalent circuit showing the charge storage on capacitor  $C_2$  is as shown in Fig. 2.3(d). The conservation of charge law at node A gives

$$C_2 V_0^0(n) - C_2 V_0^0(n-1/2) = 0$$

(2.5)

taking the z-transform of both sides of equation (2.5) and simplifying, we obtain

$$V_0^0(z) = z^{-1/2} V_0^e(z)$$

(2.6)

Substituting (2.6) into Eq. (2.4) gives

$$C_1 z^{-1} V_{in}^{o}(z) + C_2 z^{-1/2} V_{o}^{e}(z) - C_2 z^{-3/2} V_{o}^{e}(z) = 0$$

(2.7)

The transfer function of the SC circuit shown in Fig. 2.2 is obtained from Eq. (2.7) as

$$H^{0e}(z) = \frac{V^{e}(z)}{V^{0}_{in}(z)} = -\frac{\frac{C}{1}}{\frac{z}{2}} \frac{z^{-1/2}}{1-z^{-1}}$$

(2.8)

Using (2.6), Eq. (2.8) can also be expressed as

$$H^{00}(z) = \frac{V^{0}(z)}{V^{0}(z)} = -\frac{\frac{1}{2} \frac{z^{-1}}{z^{-1}}}{V^{0}_{in}(z)}$$

(2.9)

The integrator defined by the transfer function given by equation (2.8) has a half delay in the forward path. This transfer function is obtained if the output of the SC cir-

cuit shown in Fig. 2.2 is sampled at the even clock phases. Such an integrator is known as Type I Lossles Discrete Integrator(LDI)[5,6]. The reason that this integrator is called the LDI integrator can be seen as follows: From Eq. (2.2), the transfer function of the analog integrator can be written as

$$H(s) = \frac{V_{out}(s)}{V_{in}(s)} = -\frac{1}{sR_{in}C_{2}}$$

(2.10)

For sinusoidal signals, substituting s=jw into the transfer function of the analog integrator, we obtain

$$H(jw) = \frac{V_{out}^{(jw)}}{V_{in}^{(jw)}} = -\frac{1}{jw R_{i} C_{2}}$$

(2.11)

On the other hand, for discrete frequencies, substituting z=exp(jwT) into Eq. (2.8) gives

$$\begin{array}{c} Oe \ jwT \\ H \ (e \ ) = - \frac{1}{C} \\ 2 \end{array} \begin{pmatrix} -jwT/2 \\ e \\ -jwT \\ 1-e \end{array} \end{pmatrix}$$

(2.12)

Multiplying the numerator and denominator by exp(jwT) gives

$$H^{0e}(e^{jwT}) = -\frac{\frac{C}{1}}{C} \frac{1}{jwT/2} \frac{1}{-e^{-jwT/2}}$$

(2.13)

Using Euler's formula in (2.13), the transfer function of the SC integrator becomes

$$H^{0e}(e^{jwT}) = -\frac{C_1}{jwTC_2} \begin{pmatrix} \frac{wT}{2} \\ \frac{2}{sin(\frac{wT}{2})} \end{pmatrix}$$

(2.14)

Equation (2.14) gives the exact transfer function of the SC integrator when its output is sampled at the end of even clock phases. For wT<<1,  $sin(wT/2) \simeq wT/2$  and Eq. (2.14) can be written as

$$\overset{\text{oe}}{\text{H}} \overset{\text{jwT}}{(\text{e})} \simeq \frac{\frac{-C}{1}}{\frac{1}{\text{jwTC}}}$$

(2.15)

Comparing (2.15) with Eq. (2.11), it can be observed that  $R_1=T/C_1=1/f_cC_1$ . Therefore, when the sampling frequency is much higher than the frequency of the input signal, the analog integrator is equivalent to a switched capacitor integrator. The error in the magnitude of the SC integrator, which is given by the factor (wT/2)/sin(wT/2) becomes appreciable when the signal frequency  $f > f_c/100$  [20].

Assuming that the signal frequency  $f < f_c/100$ , then, replacing  $R_1$  by  $T/C_1$  in the transfer function of the analog integrator gives

$$H(s) = -\frac{\frac{C}{1}}{\frac{1}{sTC}}$$

(2.16)

A direct comparison of (2.16) and (2.8) indicates that replacement of all RC integrators by the SC circuit of Fig. 2.2, is equivalent to replacing s by  $(1-z^{-1}/Tz^{-1/2})$  provided that the output of the SC circuit is sampled at the end of even phases. This is the well known lossless discrete integrator(LDI)[6] transformation which has found wide application in the design of switched capacitor filters[5,8,12,26,27].

The LDI transformation can also be written as

$$S = \frac{1}{T} \left( z^{1/2} - z^{-1/2} \right)$$

(2.17)

The mapping properties and its use in the design of SC filters will be discussed in detail in the next Chapter.

The integrator defined by the transfer function given by Eq. (2.9) has a full delay unit in the forward path. This transfer function is obtained if the output of the SC circuit shown in Fig. 2.2 is sampled at the end of odd clock phases. Such an integrator is known as a Type I Direct Discrete Integrator(DDI)[6]. Following an analysis similar to that for the LDI integrator, the discrete frequency response of Eq. (2.9) can be written as

$$\begin{array}{c} co \ jwT \\ H \ (e \ ) = - \frac{L}{C} \ \left( \frac{e^{-jwT}}{e^{-jwT}} \right) \end{array} \begin{array}{c} 24 \\ (2.18) \end{array}$$

Using Euler's formula in (2.18), we obtain

Equation (2.19) gives the exact transfer function of the SC integrator when its output is sampled at the end of the odd clock phase. The magnitude of Eq. (2.19) can be written as

$$|H^{OO}(e^{jwT})| = \frac{C}{wTC} \left( \frac{wT}{2} \right)$$

(2.20)

By the same argument given previously, if wT<<1, then the error in the magnitude of the SC integrator is negligible. In order to observe the frequency transformation characterizing the Type I DDI integrator, we proceed as follows: Multiplying the numerator and denominator of Eq. (2.18) by exp(jwT) gives

$$\begin{array}{c} & -C \\ H^{00}(e^{jwT}) = \frac{-1}{2} & \frac{1}{1} \\ C & jwT \\ 2 & (e^{jwT}-1) \end{array}$$

(2.21)

238

Since  $\exp(jwT)=1+jwT-(wT)^2/2-...$ , then, for wT<<1, the terms with second or higher degree can be neglected and Eq. (2.21) becomes

$$\overset{\text{oo}}{\text{H}} \stackrel{\text{jwT}}{\text{(e)}} \simeq \frac{-C}{\frac{1}{jwTC}}$$

(2.22)

Comparing (2.22) and (2.11), it can be observed that  $R_1=T/C_1=1/f_CC_1$  and the Type I DDI integrator becomes equivalent to the analog integrator. Furthermore, a direct comparison of (2.16) and (2.9) indicates that replacement of all RC integrators by the SC circuit of Fig. 2.2 is equivalent to replacing s by  $(1-z^{-1}/Tz^{-1})$  provided that the output is sampled at the end of the odd clock phase. This is the well known forward-difference(or forward Euler) mapping[1,3] used in the design of digital filters from an analog prototype. The phase shift of the LDI integrator discussed previously is  $\pi/2$  which is exactly the same as the phase shift of the Type I DDI integrator is given by

Arg

$$H^{00}(e^{jwT}) = \frac{\pi}{2} - \frac{wT}{2}$$

(2.23)

This shows that the Type I DDI integrator has an additional phase lag term of wT/2 radians. This is the major difference between the two SC integrators discussed so far.

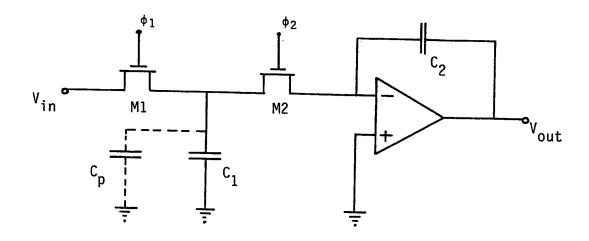

### 2.1.2 Effects of Stray Capacitances

The switched capacitor integrator shown in Fig. 2.2, unfortunately, suffers from a very serious shortcoming, which is the existence of several stray capacitances between various nodes (and lines) and ground. This makes the integrated circuit implementation impractical. The parasitic capacitances due to the switches  $M_1$  and  $M_2$  of the SC integrator shown in Fig. 2.2 is depicted in Fig. 2.4. The most serious problem caused by switches is the clock feed-through, where a portion of the control voltage appears at the Source and Drain terminals of the switch. Since the clock signal is making very large transitions, it can easily couple from the Gate to Source or Drain through C<sub>GS</sub> or C<sub>GD</sub>, respectively. The values of  $C_{GS1}$ ,  $C_{GD1}$ ,  $C_{GS2}$  and  $C_{GD2}$  are usually in the range of 0.02pF. Therefore, if the effect of feed-through is not minimized, these capacitances can effect the performance of the SC circuit[7,14]. In general, the clock feed-through is dependent upon the switch configuration and the size of the capacitors in the circuit. The best technique to reduce its effect is to use the largest possible capacitors and to keep the clock swings as small as possible[1,7,14].

A second important non-ideal characteristics of the MOS switches are the parasitic capacitances from the Source to Bulk(substrate) and from the Drain to Bulk, denoted as  $C_{BS}$  and  $C_{BD}$  respectively. If the parasitic capacitors are

26

Figure 2.4 Illustration of the parasitic capacitances due to the switches  $M_1$  and  $M_2$  of the SC integrator shown in Fig. 2.2.

123B

connected to a voltage source or to a virtual ground of an op-amp, then they do not affect the performance of the SC circuit[5]. Therefore, the effects of C<sub>BS1</sub> and C<sub>BD2</sub>, as shown in Fig. 2.4 are negligible and the only two parasitic capacitances that affect the performance of the SC circuit are  $C_{BD1}$  and  $C_{BS2}$ . Furthermore, there exist parasitic capacitances from the top and bottom plates of  $C_1$  to the Bulk. However, since the bottom plate of  $C_1$  is connected to the ground, its effect can be eliminated[1]. The parasitic capacitance from the top plate of  $C_1$  to the substrate is in parallel with  $C_{BD1}$  and  $C_{BS2}$ . These capacitances are combined into a single parasitic capacitance  $C_p$  as shown in Fig. 2.5. They can cause serious error, because C<sub>1</sub> is usually small. In addition to this,  $C_p$  can sometimes be voltage dependent which can result into non-linear distortion. Suppose that the top plate parasitic is  $0.1C_1$  and  $C_{BD1}=C_{BS2}=0.1pF$ , then an error of 30 percent may be realized if  $C_1$  is designed to be lpF[1]. Therefore, if a high accuracy is desired for  $C_1$ , it must be chosen such that  $C_1^{>5pF}$ . In general, since  $C_2^{>>C_1}$ , a large area is required for this SC integrator[20].

The existence of the above parasitic capacitances has caused the development of switched capacitor integrators which are insensitive to parasitic effects[5,23]. The SC

Figure 2.5 Switched Capacitor integrator of Fig. 2.2, showing the combined effect of the parasitic capacitances.

29

123в

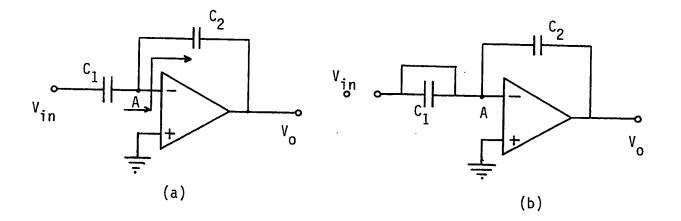

integrator shown in Fig. 2.6(a) is a stray insensitive version of the SC integrator shown in Fig. 2.2. The operation of this stray-free SC integrator is similar to the operation of its stray sensitive version, except for the non-inverting property. Hence the two transfer functions for the stray insensitive integrator can be written as

$$\overset{\text{oe}}{H}(z) = \frac{\frac{1}{2} - \frac{1}{2}}{\frac{1}{2} - \frac{1}{2}}$$

(2.24)

$$H^{00}(z) = \frac{\frac{C}{1}}{\frac{1}{2}} \frac{\frac{-1}{z}}{\frac{-1}{2}}$$

(2.25)

By a similar argument used to derive the relationship between the analog integrator and the stray-sensitive SC integrator, it can be shown that the non-inverting parallel SC branch is equivalent to a negative resistance. Hence, under the assumption that wT<<1, the stray-insensitive SC integrator is equivalent to the analog integrator shown in Fig. 2.6(b). Due to this property, the non-inverting parallel SC branch can not be directly used in replacing the resistors in an active-RC filter. However, as it will be shown in the next Chapter, the circuit shown in Fig. 2.6(a) is a very useful building block in the design of SC ladder filters.

30

Figure 2.6 (a) Stray-insensitive SC integrator (b) Analog integrator with negative resistance.

123в

The stray-free property was achieved at the cost of two extra switches. The reason for this insensitivity is due to the following factors:

Every capacitor terminal is either switched between ground and voltage source, which are low impedance nodes or between ground and a virtual ground which are both at the same potential. Hence, they do not affect the performance of the SC integrator[20].

Furthermore, in the case of stray-insensitive SC integrator, the capacitors  $C_1$  and  $C_2$  need not be much larger than the parasitic capacitances. However, they should still be much larger than the capacitance between the lines leading their electrodes which to varies between 1 - 5fF (1 fF=10<sup>-15</sup>F). This allows  $C_1$  to be chosen as small as 0.1pF which leads to a reduction of 10-50 in size with comparison to the stray-sensitive integrators. In addition to this, the accuracy is highly improved and the errors can be reduced to 0.1-0.5 percent[20].

## 2.1.3 Design Example

The concept of parallel SC resistor simulation to design SC filters from active-RC prototypes will be demonstrated by an example. The interested reader may refer to reference [1] for further details.

32

Example 2.1

Consider the Tow-Thomas three op-amp biquad shown in Fig. 2.7.

This circuit has both low-pass and band-pass transfer functions simultaneously available at  $V_1$  and  $V_2$ , respectively. The transfer functions in the continuous domain are given by[17]

$$H_{LP}(s) = \frac{V_{1}}{v_{in}} = \frac{-(r_{2}/r_{1}) \frac{1}{R_{R} C_{C}}}{s^{2} + \frac{1}{R_{1} C_{S}} s + \frac{2}{r_{1}} \frac{1}{R_{R} C_{C} C_{S}}}{(2.26)}$$

and

$$H_{BP}(s) = \frac{V_{2}}{V_{in}} = \frac{-\frac{1}{R_{45}^{C}}s}{s^{2} + \frac{1}{R_{5}^{C}}s + \frac{r}{r_{1}} \frac{2}{R_{5}^{R}} \frac{1}{r_{1}}}$$

(2.27)

The ideal design equations for this network are

$$R_{2} = \frac{\frac{r}{2}}{r_{1}} \frac{\frac{1}{\sqrt{2}}}{\frac{1}{\sqrt{2}} \frac{1}{\sqrt{2}}}$$

(2.28)

$$R_{l} = \frac{Q}{w_{0}C_{5}}$$

(2.29)

$$R_{4} = \frac{r_{1}}{r_{2}} \frac{w_{R}^{2}}{o_{3}} \text{ for H}_{LP}$$

(2.30)

or

$$R_{4} = \frac{1}{bC} \text{ for } H_{BP}$$

(2.31)

where b<sub>o</sub> and b<sub>1</sub> are the gain constants of the low-pass and band-pass filters respectively.

Suppose that we wish to design a switched capacitor lowpass filter using the Tow-Thomas circuit for a given filter specifications. First, we design the normalized filter and then perform the necessary magnitude and frequency scaling to meet the required specifications. This makes the design more general.

For a normalized low-pass filter with  $w_0$ =1 rad/sec, assume that  $r_2=r_1=1$  Ohm,  $C_5=C_6=1$  F and  $R_3=1$  Ohm. Computing  $R_2$  and  $R_1$  using equations (2.28) and (2.29), we obtain;  $R_2=1$ Ohm and  $R_1=0$  Ohms. Furthermore, assuming a maximum gain of 1, then,  $b_0=w_0^2$  and  $R_4$  is computed from Eq. (2.30) as 1 Ohm.

Now, suppose that the given specifications require a lowpass SC filter with  $w_0$ =1000 rad/sec, Q=5 and a maximum gain of 1.

In this design technique of SC filters, it is not necessary to perform magnitude scaling since all the resistors are replaced by SC equivalent branches and all the capacitances are usually normalized with respect to the smallest capacitance of the circuit. This smallest capacitance is usually named as the unit capacitance  $C_u$  which ranges between 0.5pF and 2pF, depending on the technology used. To replace the resistors by their equivalent branches, we have to calculate the capacitance associated with each branch using Eq. (1.10). Furthermore, we have to choose the sampling frequency such that wT<<1.

Choice of  $f_c$ =100 KHz guarantees that wT<<1. Next, applying a frequency scaling of  $k_f$ =1000 to the capacitances  $C_5$  and  $C_6$  gives

$C_5 = C_6 = 1/1000 F$

The capacitances associated with each SC equivalent branch are calculated as

$$C_1 = (1/R_1 f_c) = 1/500,000 F$$

$C_2 = (1/R_2 f_c) = 1/100,000 F$

$C_3 = (1/R_3 f_c) = 1/100,000 F$

$C_4 = (1/R_4 f_c) = 1/100,000 F$

Since the minimum capacitance is  $C_1$ , then all the capacitance values are normalized with respect to  $C_1$ . This gives the following normalized capacitance values

1238

$$C_1 = C_u$$

$C_2 = 5C_u$

$C_3 = 5C_u$

$C_4 = 5C_u$

$C_5 = 500C_u$

$C_6 = 500C_u$

The switched capacitor realization of the Tow-Thomas circuit is shown in Fig. 2.8. It should be noted that the last opamp section of the Tow-Thomas circuit behaves as an inverting amplifier. One of the advantages of SC filters in comparison to active-RC filters is the ability to invert a signal without requiring additional amplifiers. For the Tow-Thomas circuit, this inversion was accomplished simply by replacing the summing resistor with a non-inverting parallel SC equivalent branch. The exact transfer functions of this SC filter are found by applying the law of conservation of charges as[1]

$$H(z) = \frac{V_{LP}}{V_{in}} = \frac{-A_1 A_2 z^{-2}}{1 - (2 - A_3) z^{-1} + (1 + A_1 A_2 - A_3) z^{-2}}$$

(2.32)

$$H(z) = \frac{V_{BP}}{V_{in}} = \frac{-A z^{-1} (1-z^{-1})}{1-(2-A_3)z^{-1} + (1+A_1A_2 - A_3)z^{-2}}$$

(2.33)

Figure 2.8 Switched Capacitor realization of the Tow-Thomas circuit using parallel SC equivalent branches.

where  $A=C_4/C_5$ ,  $A_1=C_4/C_3$ ,  $A_2=C_2/C_6$  and  $A_3=C_4/C_1$

## 2.2 Series SC Resistor Simulation

# 2.2.1 Operation and Analyses

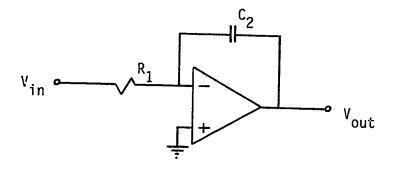

A second type of SC integrator which is commonly used as a building block in the design of SC filters makes use of a series SC equivalent branch to simulate a resistor. This circuit is shown in Fig. 2.9. The clock waveforms used for driving the switches are shown in Fig. 1.2. Using the conservation of charge analysis as explained in Section 2.1.1, the operation of this circuit is analyzed as follows: At t=(n-3/2)T+t<sub>1</sub>,  $\phi_1$  goes high and switch S1 is closed, while just before this time, switch S2 has already opened. During this time,  $C_1$  charges to the instantaneous value of  $V_{in}(n-1)$ . A current flows through  $C_2$  in the direction as indicated in Fig. 2.10(a). This implies that the charge on  $C_2$  changes by an amount equal to the charge deposited on  $C_1$ . At t=(n-1)T+t<sub>1</sub>,  $\phi_2$  goes high. This makes a short circuit across the terminals of  $C_1$  which will be discharged completely. Since switch S1 is closed during this time, C2 maintains the charge acquired from the previous state. At t=(n-1/2)T, the charge distribution due to one full period is complete and the charge transfer repeats in a similar fashion for all the other periods.

Figure 2.9 Switched Capacitor Integrator using a series equivalent branch for resistor simulation.

12Зв

Figure 2.10 Operation of the switched capacitor integrator of Fig. 2.9; (a) during odd phase (b) during even phase (c) Equivalent circuit for the capacitors showing the charge storage at t=(n-1)T and (d) at t=(n-1/2)T

To obtain the difference equation characterizing the performance of this circuit, the conservation of charge law is applied at node A. The equivalent circuit showing the distribution of charges is shown in Fig. 2.10(c) for t=(n-1)T. This difference equation is given by

$$C_1 V_{in}^0(n-1) + C_2 V_0^0(n-1) - C_2 V_0^e(n-3/2) = 0$$

(2.34)

At t=(n-1/2)T, the conservation of charge law at node A gives

$$C_2 V_0^e(n-1/2) - C_2 V_0^o(n-1) = 0$$

(2.35)

The equivalent circuit showing the charge distribution at this instant is shown in Fig. 2.10(d). Taking the z-transform of both sides of equation (2.34), we obtain

$$C_1 z^{-1} V_{in}^0(z) + C_2 z^{-1} V_0^0(z) - C_2 z^{-3/2} V_0^e(z) = 0$$

(2.36)

Multiplying both sides of equation (2.36) by z gives

$$C_1 V_{in}^0(z) + C_2 V_0^0(z) - C_2 z^{-1/2} V_0^e(z) = 0$$

(2.37)

Next, taking the z-transform of both sides of Eq. (2.35) and multiplying by  $z^{1/2}$ , we obtain

42

23B

$$V_{0}^{e}(z) = z^{-1/2} V_{0}^{0}(z)$$

(2.38)

Using Eq. (2.38) to eliminate  $V_o^o(z)$  in Eq. (2.37) gives the following transfer function

$$H^{0e}(z) = \frac{V^{0}(z)}{V^{0}(z)} = -\frac{\frac{C}{1}}{C} \frac{z^{-1/2}}{1-z^{-1}}$$

(2.39)

Moreover, if we use Eq. (2.38) to eliminate  $V_o^e(z)$  in Eq. (2.37), the following transfer function is obtained

$$H^{00}(z) = \frac{V^{0}(z)}{V^{0}(z)} = -\frac{C}{\frac{1}{C}} \frac{1}{\frac{1}{2}} \frac{1}{1-z^{-1}}$$

(2.40)

The transfer function given by Eq. (2.39) is identical to the one given by Eq. (2.8). Therefore, by the same argument presented in Section 2.1.1, sampling the output of the SC integrator at the end of even clock phases realizes the LDI transformation. This shows that the SC integrator shown in Fig. 2.9 is equivalent, in operation, to the SC integrator shown in Fig. 2.2, provided that their outputs are sampled at the end of even clock phase.

On the other hand, if the output of the SC integrator shown in Fig. 2.9 is sampled at the end of odd clock phase, the transfer function given by Eq. (2.40) is obtained. Comparing this transfer function with the one given by Eq. (2.9), it can be observed that no delay exists in the forward path. This type of integrator is called Type II Direct Transform Discrete Integrator(DDI). To observe the characteristics of this integrator, we proceed as follows: Substituting z=exp(jwT) into Eq. (2.40) gives

$$\begin{array}{c} C \\ H \\ H \\ e \end{array} = - \begin{array}{c} C \\ C \\ 2 \\ 1 - e \end{array} \end{array}$$

(2.41)

After multiplying the numerator and denominator by exp(jwT)and simplifying, Eq. (2.41) becomes

$$\begin{array}{c} \text{oo} \text{ } \text{jwT} \\ \text{H} \text{ } \text{ } \text{ } \text{(e)} \end{array} \right) = \frac{-C}{\text{jwT C}} \left( \frac{\underline{\text{wT}}}{2} \\ \frac{2}{\sin(\frac{\text{wT}}{2})} \right) \text{exp(jwT/2)}$$

(2.42)

The phase shift of Type II DDI integrator is given by the following equation

Arg H<sup>00</sup>(e<sup>jwT</sup>) =

$$\frac{\pi}{2} + \frac{wT}{2}$$

(2.43)

A comparison of (2.42) and (2.19) shows that the magnitude of Type II DDI integrator is the same as the magnitude of Type I DDI integrator. The only difference is the leading phase shift instead of a lagging one.

123B

By Euler's formula,  $exp(-jwT)=1-jwt-(wT)^2/2+...$  For wT<<1, the second and higher order terms can be neglected, therefore Eq. (2.41) can be written as

$$\begin{array}{c} & -C \\ & -C \\ H (e^{-}) \simeq -\frac{1}{2} & \frac{1}{2} \\ & C \\ & 2 \end{array}$$

(2.44)

Comparing (2.44) with Eq. (2.11), it is easily observed that  $R_1 = (T/C_1) = 1/f_cC_1$  and the Type II DDI integrator becomes equivalent to the analog integrator as shown in Fig. 2.1. Furthermore, if we compare Eq. (2.44) with Eq. (2.16), we can conclude that, replacement of all RC integrators by the circuit of Fig. 2.9 is equivalent to replace s by  $(1-z^{-1}/T)$ , provided that the output is sampled at the end of odd clock phase. This is recognized as the backward-difference (backward-Euler) mapping[1,31] used in the design of digital filters from an analog prototype.

Unfortunately, the series equivalent branch used in the SC integrator shown in Fig. 2.9 is stray sensitive due to the reasons explained in Section 2.1.2. The stray insensitive version of this integrator which has been extensively used in the design of SC filters[3,8,12,26,27] is shown in Fig. 2.11. The transfer functions of this integrator are also given by equations (2.39) and (2.40).

Figure 2.11 Stray-insensitive version of the switched capacitor Integrator shown in Fig. 2.9

123в

# 2.2.2 Switched Capacitor Filter Design Using Series SC Resistor Simulation

As was mentioned in the previous Section, replacement of resistors in an active-RC filter by series equivalent branches is equivalent to applying the backward-difference mapping to the transfer function of an active-RC filter. This mapping, unlike the forward-difference mapping, transforms a stable RC active filter into a stable SC filter. Assuming that a sample-and-hold circuit  $(S/H)_i$  is cascaded with an SC filter as shown in Fig. 1.3, the resulting transfer function denoted by  $H_{RE}(w)$  becomes[1]

$$H_{RE}(w) = H(w) \frac{\sin wT}{wT}$$

(2.45)

where H(w) is the transfer function of the SC filter obtained from the transfer function of the active RCprototype by the direct application of the backward transformation and  $\sin(wT)/wT$  is the spectrum for a zero order sample-and-hold circuit as shown in Fig. 2.12. The design procedure is similar to the one presented in Section 2.1.3. However, as was mentioned earlier, this design is accurate only when wT<<1. When the signal frequency is not much smaller than the sampling frequency, a set of prewarping equations based on a prewarping algorithm can be used to obtain more accurate results. The interested reader is referred to pages 193-194 of reference [1] for further

details. The design of SC filters based on series SC resistor simulation will be demonstrated by an example.

Example 2.2

Consider the Delyiannis-Friend bandpass circuit [38] shown in Fig. 2.13

The continuous domain transfer function of this circuit is given by

$$H(s) = \frac{\frac{-1}{R_{1}C_{4}}s}{\frac{2}{s+s(\frac{1}{R_{2}C_{3}} + \frac{1}{R_{2}C_{4}}) + \frac{1}{R_{1}R_{2}C_{3}C_{4}}}}$$

(2.46)

Assuming that  $C_3 = C_4 = C$  the center frequency  $w_0$  and the selectivity Q are given by

$$w_{0} = \frac{1}{C\sqrt{R_{R}}}$$

(2.47)

$$Q = \frac{1}{2} \sqrt{\frac{R}{\frac{2}{R_{1}}}}$$

(2.48)

choosing  $R_1=1$  gives the following design equations

$$R_2 = 4Q^2$$

,  $C = \frac{1}{2w_0Q}$  (2.49)

123B

Suppose that we are asked to design a bandpass SC filter using series SC equivalent branches with  $w_0$ =1000 rad/sec, Q=4 and a sampling frequency of 100 KHz. Using the Delyiannis-Friend circuit as the active RC-prototype, the component values are calculated using equation (2.49) and (1.9) as

$$R_2 = 4Q^2 = 64$$

Ohms

$C = C_3 = C_4 = (1/2w_0Q) = 1/8000$  E

By Eq. (1.9), the capacitances associated with each resistor branch are calculated as

$$C_1 = (1/R_1 f_c) = 1/100,000 F$$

$C_2 = (1/R_2 f_c) = 1/64 \times 10^5 F$

Normalizing all capacitances with respect to C2, we obtain

$$C_1 = 64C_u$$

$C_2 = C_u$

$C = C_3 = C_4 = 800C_u$

The desired SC filter which is shown in Fig. 2.14 is obtained by replacing  $R_1$  and  $R_2$  with the stray-insensitive series equivalent branches. The transfer function of this SC filter is obtained by using the backward transformation,  $s=(1-z^{-1}/T)$  in Eq. (2.46). After simplification, we obtain

123B

$$H(z) = \frac{-\frac{T^2}{C_{1}C}(1-z^{-1})}{z^{-2}-2z^{-1}(1+\frac{T^2}{C_{1}C}) + (1+\frac{2T^2}{C_{1}C} + \frac{T^4}{C_{1}C_{1}C})}$$

(2.50)

where  $T=1/f_c$ . The exact transfer function can be obtained by applying the law of conservation of charges.

## 2.3 Bilinear SC Resistor simulation

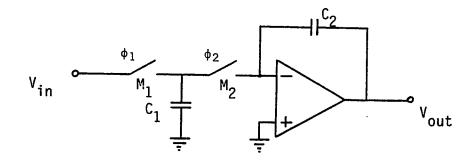

### 2.3.1 Operation and Analyses

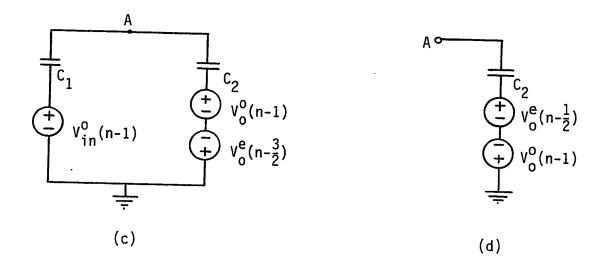

Consider the SC integrator shown in Fig. 2.15(a). With a similar discussion presented in the previous Sections, the circuit is analyzed using the law of conservation of charges. At t=(n-1)T, the conservation of charge law at node A gives

-

$$C_1 V_{in}^0(n-1) - C_1 V_{in}^e(n-3/2) + C_2 V_0^0(n-1) - C_2 V_0^e(n-3/2) = 0$$

(2.51)

Taking the z-transform of both sides of Eq. (2.51), we obtain

$$C_1 z^{-1} V_{in}^{o}(z) - C_1 z^{-3/2} V_{in}^{e}(z) + C_2 z^{-1} V_{o}^{o}(z) - C_2 z^{-3/2} V_{o}^{e}(z) = 0$$

(2.52)

Multiplying both sides by z gives

$$C_1 V_{in}^{o}(z) - C_1 z^{-1/2} V_{in}^{e}(z) + C_2 V_0^{o}(z) - C_2 z^{-1/2} V_0^{e}(z) = 0$$

(2.53)

23B

Figure 2.15 (a) Bilinear SC integrator (b) Equivalent circuit for the charge distribution at t=(n-1)T (c) Equivalent circuit for the charge distribution at t=(n-1/2)T

54

123в

At t=(n-1/2)T, the law of conservation of charges at node A yields

$$C_1 V_{in}^{e}(n-1/2) - C_1 V_{in}^{o}(n-1) + C_2 V_{o}^{e}(n-1/2) - C_2 V_{o}^{o}(n-1) = 0$$

(2.54)

Taking the z-transform of both sides, we obtain

$$C_{1}z^{-1/2}V_{in}^{e}(z) - C_{1}z^{-1}V_{in}^{o}(z) + C_{2}z^{-1/2}V_{o}^{e}(z) - C_{2}z^{-1}V_{o}^{o}(z) = 0 \qquad (2.55)$$

Multiplying both sides by  $z^{1/2}$  yields

$$C_1 V_{in}^{e}(z) - C_1 z^{-1/2} V_{in}^{o}(z) + C_2 V_{o}^{e}(z) - C_2 z^{-1/2} V_{o}^{o}(z) = 0$$

(2.56)

The equivalent circuit for the charge distribution at these two phases are shown in Fig. 2.15(b) and 2.15(c) respectively. If the output is sampled at both the even and odd phases, the transfer function of the SC circuit can be obtained by summing equations (2.53) and (2.54) and can be written as

$$H(z) = \frac{V(z)}{V_{in}(z)} = \frac{V_{i}^{0} + V_{in}^{0}}{V_{in}^{0} + V_{in}^{0}} = -\frac{\frac{C_{in}}{1}}{C_{in}^{0} - \frac{1}{2}}$$

(2.57)

This SC integrator operates somehow different than the SC integrators presented in the previous Sections. The first obvious difference is in the charge transfer of the SC equivalent branch. The capacitor  $C_1$  is discharged and

23B

charged twice at every clock period T. The second obvious difference is in the definition of the transfer function of the circuit. Unlike the previous integrators, the transfer function of this circuit is obtained by sampling the output at both phases. This doubles the effective period. Therefore, in order to establish a basis of comparison, a new period is defined as

$$T_1 = \frac{T}{2}$$

(2.58)

Defining a new discrete frequency as  $z_1 = \exp(jwT_1)$ , then, from equation (2.58), this new discrete frequency can be written as

$$z_1 = z^{1/2}$$

(2.59)

Substituting (2.59) into (2.57) gives the following transfer function

$$H(z_{1}) = \frac{-C}{2} \frac{1+z_{1}}{1-z_{1}}$$

(2.60)

Substituting  $z_1 = \exp(jwT_1)$  into Eq. (2.60), we obtain

23B

$$jwT = \frac{-C}{l} \begin{pmatrix} -jwT \\ 1 + e \\ -jwT \\ 2 \end{pmatrix}$$

(2.61)

Multiplying both sides of Eq. (2.61) by  $exp(jwT_1/2)$  gives

$$\begin{array}{c} jwT \\ H(e \end{array} ) = \frac{-C \left[ \begin{pmatrix} jwT /2 & -jwT /2 \\ 1 & 1 \end{pmatrix} \right]}{C \\ 2 \left[ \begin{pmatrix} jwT /2 & -jwT /2 \\ 1 & -e \end{array} \right]}$$

(2.62)

Equation (2.62) can be written as

$$\begin{array}{c} jwT \\ H(e \\ ) = \frac{-C}{1} \\ \frac{-L}{jC} \\ 2 \\ \frac{1}{sin(wT/2)} \end{array}$$

(2.63)

For wT<<1,  $sin(wT_1/2) \simeq wT_1/2$  and  $cos(wT_1/2) \simeq 1$ . Therefore, Eq. (2.63) becomes

$$jwT = \frac{-2C}{1}$$

H(e<sup>1</sup>)  $\approx \frac{-2C}{jwT_{1}C_{2}}$  (2.64)

A direct comparison of Eq. (2.64) and (2.11) shows that the SC integrator shown in Fig. 2.15(a) is approximately equivalent to the active-RC integrator of Fig. 2.1 when  $R_1 = T_1/2C_1$ . Substituting this value of  $R_1$  into Eq. (2.10) gives

$$H(s) = \frac{\frac{-2C}{1}}{sT_{12}C}$$

(2.65)

Comparing Eq. (2.65) with (2.60) shows that replacement of all RC integrators by the SC circuit of Fig. 2.15(a) is equivalent to repalacing s by  $2(1-z_1^{-1})/T_1(1+z_1^{-1})$ . This is the well known Bilinear Transformation which is very widely used in the design of digital filters from an analog model.

With the information given in Section 2.1.2, it can be shown that the Bilinear SC equivalent branch shown in Fig. 2.15(a) is stray-sensitive to parasitic effects.

# 2.3.2 Switched Capacitor Filter Design Using Bilinear Resistor Simulation

The design of SC filters based on the Bilinear SC resistor simulation is similar to the previous design techniques except for a few differences. The Bilinear Transformation transforms stable active-RC filters into stable SC filters. This property is shared with the backward difference transformation. In discrete filter design it is preferable that the transformation used maps the imaginary jw-axis of the s-plane onto the unit circle of the z-plane. This makes sure that the shape of the gain response can be preserved[17,31]. The Bilinear Transformation, unlike the backward difference mapping, satisfies the above property. However, due to the non-linear relationship between the discrete and continuous filter frequencies introduced by the Bilinear transformation, the SC filter specifications has to be prewarped. For the backward difference transformation, this was not neces-

sary when wT<<1. Details of prewarping for different transformations will be studied in detail in Chapter 3.

A general procedure for the design of SC filters based on an element by element resistor simulation in analog RC filters using the Bilinear transformation is presented below[1].

1. The desired passband and stopband limit frequencies,  $w_d$ 's of the SC filter are prewarped to obtain the corresponding  $\Omega_a$ 's of the active-RC prototype filter, using the relation

$$\Omega_{a} = \frac{2}{T} \tan\left(\frac{d}{2}\right)$$

(2.66)

- 2. The active-RC prototype is designed from the prewarped specifications using  $\Omega_a$ 's.

- 3. Each resistor  $R_m$  in the active RC circuit is replaced by the Bilinear SC equivalent branches, where  $R_m$  is given by

$$R_{m} = \frac{T_{1}}{2C_{m}}$$

(2.67)

Since  $T_1 = T/2$ , where T is the sampling period,  $R_m$  becomes

$$R_{m} = \frac{T}{4C_{m}}$$

(2.68)

60

For design examples and further details, the reader is referred to reference [1].

•

#### Chapter III

## SWITCHED CAPACITOR LADDER FILTER DESIGN

In the previous Chapter, we have presented the conceptually simplest design technique of SC filters. Unfortunately, for higher order and more complicated filters, some of the required pole-Q's are usually very high and the element value sensitivities of the corresponding section become too high for reliable fabrication. This leads to a very low yield and the circuit becomes uneconomical for fabrication[20].

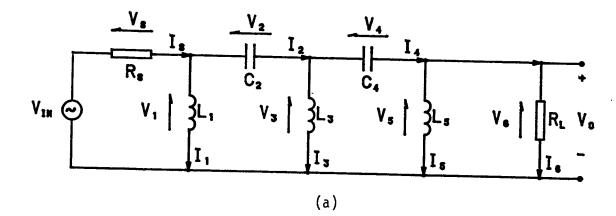

The most widely used SC filter design is based on the signal-flow-graph(SFG) representation of the current-voltage relations of a passive ladder prototype filter. The prototype filter used is usually a doubly-terminated LC ladder network that is designed to effect maximum power transfer from source to load over the filter passband. These filters have very low sensitivities to variations in their component values. It has been shown [5,23] that this low sensitivity is preserved in the switched capacitor filters whose design are based on the SFG representation of these ladder prototype filters.

- 61 -

In this design technique, the SC filter is obtained by replacing each reactive component of the SFG by SC building blocks. For the low-pass and band-pass SC ladder filters, the building blocks used are either LDI or Bilinear SC integrators which have been presented in Chapter 2. Replacing the reactive components by the SC integrator building blocks, actually corresponds to applying the LDI or Bilinear transformation(depending on the type of SC integrator used) to the transfer function of the passive prototype ladder filter[1,5,8,11,12,26,27,28]. Unfortunately, these two transformations can not be directly used to design SC high pass ladder filters[4,21,22,29,34,35]. In the following Sections, we shall present the use of different transformations in the design of SC ladder filters.

## 3.1 Use of LDI Transformation in the Design of SC Ladder Filters

## 3.1.1 Properties of LDI transformation

The LDI transformation was introduced in Chapter 2 and is repeated here for convenience

$$s = \frac{1}{T} \left( z^{1/2} - z^{-1/2} \right)$$

(3.1)

where 1/T is the sampling frequency. This transformation maps part of the imaginary axis  $(-2/T < \Omega < 2/T)$  in the s-plane onto the unit circle in the z-plane. The relationship between the continuous-time frequency  $\Omega$  and the discrete-

62

time frequency w can be found by letting  $s=\sigma+j\Omega$  and z=exp(jwT) in Eq. (3.1). This gives

$$\sigma + j\Omega = j\frac{2}{T}\sin\left(\frac{wT}{2}\right)$$

(3.2)

Equating the real and imaginary parts yields

$$\sigma = 0 \text{ and } \Omega = \frac{2}{T} \sin\left(\frac{wT}{2}\right)$$

(3.3)

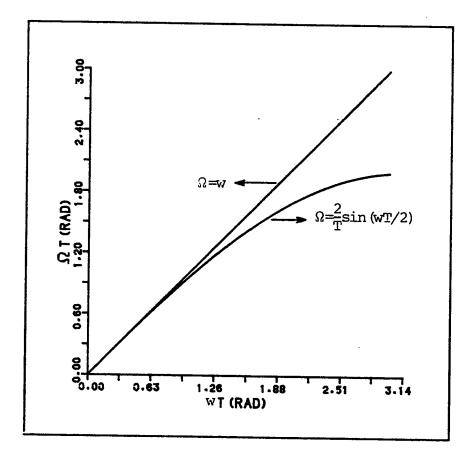

Equation (3.3) shows that the continuous time frequencies are not linearly related with discrete frequencies. This property of the LDI transformation requires the SC filter specifications to be "prewarped" according to Eq. (3.3). The warping effect of Eq. (3.3) is shown in Fig. 3.1. On the same graph, the  $\Omega$ =w curve has been also plotted for comparison. From Fig. 3.1, it can be observed that the effect of warping increases as wT approaches  $\pi$ , because the nonlinearity of the curve increases in this region.

The Lossless Discrete Integrator transfer function is given by[6]

$$H_{LDI}(z) = P \frac{\frac{1/2}{z}}{z-1} = P \frac{\frac{z^{-1/2}}{z}}{1-z}$$

(3.4)

where P is a constant. It has been shown in Section 2.1.1 that, if the output of the SC integrator shown in Fig. 2.2 is sampled at the end of even clock phase, the transfer

63

123B

123в

function becomes identical to the LDI transfer function. However, it has been shown in Section 2.1.2 that this SC integrator is sensitive to parasitic effects. In the same Section a stray-insensitive version of this integrator was also presented. The transfer function of the strayinsensitive integrator which is shown in Fig. 2.6(a) is repeated here for convenience.

$$H^{0e}(z) = \frac{V^{e}(z)}{V^{o}_{0}(z)} = \frac{\frac{C}{1} \frac{z^{-1/2}}{z^{-1}}}{C \frac{1}{2} \frac{1-z^{-1}}{1-z^{-1}}}$$

(3.5)

Comparing Eq. (3.4) and (3.5) shows that the two transfer functions become equivalent by choosing P equal to the capacitor ratio  $C_1/C_2$ . Therefore, the stray-insensitive SC integrator shown in Fig. 2.6(a) actually realizes the LDI transfer function. The general design of SC ladder filters based on the LDI transformation is studied in the following Section.

## 3.1.2 Design of SC Ladder Filters Based on the LDI Transformation

## 3.1.2.1 Low-Pass SC Ladder Filters

The following design procedure for the design of low-pass SC ladder filters has been compiled from various references [1,5,8,11,12,26,27,28] and put into a compact form. Suppose the following SC low-pass filter specifications:

$A_{max}$ : maximum attenuation in the passband region

|23B

$w_{p}$  : passband edge frequency

w<sub>c</sub> : stopband edge frequency

## Step 1

Obtain the low-pass continuous filter specifications  $\Omega_p$  and  $\Omega_s$  by prewarping  $w_p$  and  $w_s$  according to Eq. (3.3).

#### Step 2

Transform the low-pass continuous filter specifications into the normalized low-pass continuous filter specifications by using  $s=S/\Omega_{p}$  transformation.

## Step 3

Design the low-pass continuous filter by using the transformed specifications in step 2.

## Step 4

Apply  $S=s/\Omega_p$  transformation to the low-pass continuous filter of step 3 to obtain the denormalized low-pass continuous ladder prototype.

#### Step 5

Obtain the SFG of the low-pass continuous ladder filter obtained in step 4.

Realize the resistive source termination and the reactive components of the SFG using the method explained below.

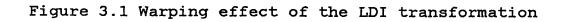

To demonstrate the above design procedure, suppose that for a given SC low-pass filter specifications, the application of steps 1 through 4 has resulted in a 4'th order allpole low-pass ladder prototype as shown in Fig. 3.2(a). The reactive components are the shunt capacitors and series inductors. The source termination is the resistive component which is connected at the input port. The load termination is the resistive component located at the output port. There are several techniques to obtain the signal-flow-graph(SFG) of a ladder structure. The interested reader may refer to the references[17,25,33,38] listed in the bibliography. In this thesis, we have used the technique presented in references [17,18], where all series elements or combination of elements are represented by their admittances and all shunt elements or combination of elements are represented by their impedances. The SFG of the 4'th order low-pass doubly terminated ladder filter shown in Fig. 3.2(a) is obtained as follows:

First, the voltage and current relations for the circuit are obtained such that loop and node equations involve only integrations. These relations are shown below.

$V_s = V_{in} - V_1 \tag{3.6a}$

$$I_{s} = \frac{V_{s}}{R_{s}}$$

(3.6b)

68

$$I_1 = I_s - I_2$$

(3.6c)

$$V_{1} = \frac{I_{1}}{sC_{1L}}$$

(3.6d)

$$I_2 = \frac{V_2}{sL_{2L}}$$

(3.6e)

$$V_2 = V_1 - V_3$$

(3.6f)

$$I_3 = I_2 - I_4$$

(3.6g)

$$V_3 = \frac{1_3}{sC_{3L}}$$

(3.6h)

$$I_4 = \frac{V_4}{sL_{4L}}$$

(3.61)

$$V_4 = V_3 - V_5$$

(3.6j)

$$V_5 = I_5 R_L$$

(3.6k)