# Test Vector Decomposition Based Static Compaction Algorithms for Combinational Circuits

Aiman H. El-Maleh and Yahya E. Osais King Fahd University of Petroleum and Minerals

Testing system-on-chips involves applying huge amounts of test data, which is stored in the tester memory and then transferred to the chip under test during test application. Therefore, practical techniques, such as test compression and compaction, are required to reduce the amount of test data in order to reduce both the total testing time and memory requirements for the tester. In this paper, a new approach to static compaction for combinational circuits, referred to as *test vector decomposition (TVD)*, is proposed. In addition, two new TVD based static compaction algorithms are presented. Experimental results for benchmark circuits demonstrate the effectiveness of the two new static compaction algorithms.

Categories and Subject Descriptors: B.6.2 [Logic Design]: Testing—static compaction; B.7.3 [Integrated Circuits]: Testing—static compaction; J.6 [Computer-Aided Engineering]: computer-aided design (CAD)

General Terms: Theory, Algorithms

Additional Key Words and Phrases: Static compaction, combinational circuits, taxonomy, test vector decomposition, independent fault clustering, class-based clustering

## 1. INTRODUCTION

Advances in the VLSI technology paved the way for System-on-Chips (SoCs). Traditional IC design, in which every circuit is designed from scratch and reuse is limited only to standard cell libraries, is more and more replaced by the SoC design methodology. However, this new design methodology has its own challenges. A major challenge is how to reduce the increasing volume of test data. Basically, there are two approaches: *compression* and *compaction*. In the first approach, test data is kept compressed while it is stored in the tester memory and transferred to the Chip Under Test (CUT). Then, it is decompressed on the CUT. This reduces the memory and transfer time requirements. In the second approach, however, the objective is to reduce the size of a test set while maintaining the same fault coverage.

Test compaction techniques are classified into two categories. The first category includes algorithms that can be integrated into the test generation process. Such algorithms are referred to as *dynamic* compaction algorithms. On the other hand,

Authors' addresses: Aiman H. El-Maleh, KFUPM, P.O. Box 1063, Dhahran 31261, Saudi Arabia; email: aimane@ccse.kfupm.edu.sa; Yahya E. Osais, KFUPM, P.O. Box 983, Dhahran 31261, Saudi Arabia; email: yosais@ccse.kfupm.edu.sa.

Permission to make digital/hard copy of all or part of this material without fee for personal or classroom use provided that the copies are not made or distributed for profit or commercial advantage, the ACM copyright/server notice, the title of the publication, and its date appear, and notice is given that copying is by permission of the ACM, Inc. To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee. © 2003 ACM 1084-4309/2003/0400-0001 \$5.00

the second category includes algorithms that are applied after the test sets are generated. Such algorithms are referred to as *static* compaction algorithms. There are several approaches to static compaction of a given test set as will be shown in the next section.

Since test application time is proportional to the length of the test set that needs to be applied, it is desirable to apply shorter test sets that provide the same fault coverage at reduced test application time. Although static compaction algorithms do not typically produce test sets of sizes equal to those generated using dynamic compaction, interests in developing more efficient static compaction algorithms have increased [Miyase et al. 2002]. Static compaction has the following advantages over dynamic compaction. First, generating smaller test sets using dynamic compaction is time consuming because many attempts to modify partially specified test vectors to detect additional faults often fail [Miyase et al. 2002]. Secondly, dynamic compaction does not take advantage of random test pattern generation. Thirdly, static compaction is independent of ATPG.

Given a test set T with single stuck-at fault coverage  $FC_T$  for a combinational circuit, the static compaction problem can be formulated as to find another test set,  $T^*$ , for the same circuit such that  $FC_{T^*} \ge FC_T$  and  $|T^*| < |T|$  [Chang and Lin 1995]. It should be pointed out that in the above definition, there is no constraint on the individual fault coverage of each test vector and the proximity between the test vectors of T and  $T^*$ . That is, the fault coverage of each test vector needs not remain intact and  $T^*$  needs not be a subset of T.

This paper is structured as follows. First, we give a taxonomy of static compaction algorithms for combinational circuits. In this section, we review the existing static compaction algorithms and show how they fit in our taxonomy. Besides, we introduce and motivate the new concept of *test vector decomposition*. Then, we describe two new static compaction algorithms based on test vector decomposition. After that, we present and discuss the experimental results. Finally, we conclude by summarizing the results of the paper and their significance.

#### 2. TAXONOMY OF STATIC COMPACTION ALGORITHMS

In this section, we give a taxonomy of static compaction algorithms for combinational circuits. We first start with an overview of the taxonomy. Then, we give a description of every class in the taxonomy with examples from the literature.

#### 2.1 Overview

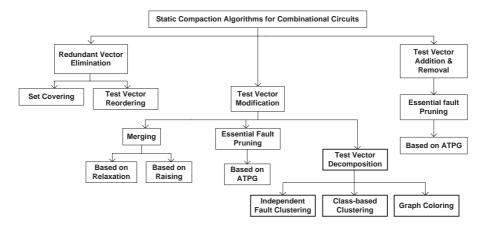

Static compaction algorithms for combinational circuits can be divided into three broad categories: (1) Redundant Vector Elimination, (2) Test Vector Modification, and (3) Test Vector Addition and Removal. Figure 1 shows our proposed taxonomy. In the first category, compaction is performed by dropping redundant test vectors. A redundant test vector is a vector whose faults are all detectable by other test vectors. Static compaction algorithms falling under this category can be further classified into two classes. The first class contains algorithms based on set covering in which faults are to be covered using the minimum possible number of test vectors. On the other hand, the second class contains algorithms based on test vector reordering in which reordering, fault simulation, fault distribution, and double detection are used to identify redundant test vectors and then drop them.

Fig. 1. Taxonomy of static compaction algorithms for combinational circuits.

In the second category, compaction is performed by modifying test vectors. Algorithms belonging to this category can be further classified into three classes. The first class contains algorithms based on merging of compatible test cubes. A test cube is a test vector that is partially specified. A test vector is made partially specified by unspecifying the unnecessary primary inputs. This process is referred to as relaxation. Relaxation can be performed using an ATPG or a stand-alone algorithm, such as [El-Maleh and Al-Suwaiyan 2002; Kajihara and Miyase 2001]. In addition to relaxation, raising can be used to enhance the compatibility among relaxed test vectors. If two relaxed test vectors conflict at one or more bit positions, they can be made compatible by raising one of them at the conflicting bit positions.

The second class contains algorithms that employ essential fault pruning to make some test vectors redundant. A test vector becomes redundant if it detects no essential faults. A fault is essential if it is detected only by a single test vector. Essential faults of a test vector can be pruned, i.e. made detected by some other test vectors, by reassigning values to those bits that are originally unspecified and have been randomly assigned values to detect additional faults.

The third class contains algorithms that are based on test vector decomposition. Test vector decomposition is the process of decomposing a test vector into its atomic components. An atomic component is a child test vector that is generated by relaxing its parent test vector for a single fault f. In this paper, we propose test vector decomposition as a new class of static compaction algorithms that modify test vectors to perform compaction.

Finally, the third category of static compaction algorithms consists of compaction algorithms that add new test vectors to a given test set in order to remove some of the already existing test vectors. The number of the newly added test vectors must be less than the number of test vectors to be removed. An ATPG is used to generate the new test vectors.

#### 2.2 Set Covering

Test compaction for combinational circuits can be modeled as a set covering problem. The set cover is set up as follows. Each column of the detection matrix

4 · El-Maleh and Osais

| Test  | Faults         |

|-------|----------------|

| $t_1$ | $f_{1}, f_{4}$ |

| $t_2$ | $f_{2}, f_{4}$ |

| $t_3$ | $f_2, f_3$     |

Fig. 2. Test vectors and their associated faults.

| Fault | Test  |

|-------|-------|

| $f_1$ | $t_1$ |

| $f_2$ | $t_2$ |

| $f_3$ | $t_3$ |

| $f_4$ | $t_1$ |

Fig. 3. First test vector that detects every fault.

corresponds to a test vector and each row corresponds to a fault. If a test vector j detects fault i, then the entry (i, j) is one; otherwise, it is zero. In this setup, the total amount of memory required for building the detection matrix is O(nf), where n is the number of test vectors and f is the number of faults.

Static compaction procedures based on set covering were described in [Flores et al. 1999; Boateng et al. 2001; Hochbaum 1996]. It should be pointed out that this approach has not been used much in the literature due to the huge memory and CPU time requirements.

## 2.3 Test Vector Reordering

Identification of redundant test vectors in a test set is an order dependent process. Given any order, redundant test vectors can be identified using fault simulation, fault distribution, or double detection. There are four variations of Test Vector Reordering (TVR) based static compaction algorithms.

2.3.1 *TVR with Fault Dropping Simulation.* Fault simulation of a test set in an order different from the order of generation is used as a fast and effective method to drop redundant test vectors. Under Reverse Order Fault simulation (ROF) [Schulz et al. 1988; Pomeranz and Reddy 2001], a test set is fault simulated with dropping in reverse order of generation. That is, a test vector that was generated later is fault simulated earlier. When it is simulated, a test vector that does not detect any new faults is removed from the test set.

The intuitive reason for this phenomenon is simply that test vectors which are further down the list detect faults which are most difficult to detect. Therefore, if we first fault simulate a test vector which is at the end of the list, it not only detects a hard fault right away, it also detects many others by pure chance. This way hard faults are out of the way early.

2.3.2 *TVR with Forward-Looking Fault Simulation.* The forward-looking fault simulation is an improved version of ROF [Pomeranz and Reddy 2001]. It is based on the idea that information about the first test vector that detects every fault can be used to drop test vectors that would not be dropped by ROF. That is, the yet undetected faults have lower indexed test vectors that detect them. So, some test vectors are skipped over and consequently dropped from the test set.

Let us consider the following example. Let the test set T be  $\{t_1, t_2, t_3\}$  and the

fault set F be  $\{f_1, f_2, f_3, f_4\}$ . Figure 2 shows the test vectors with their associated faults and Figure 3 shows the first test vector that detects every fault. Conventional ROF first simulates  $t_3$ . This test will be retained in the test set to detect  $f_2$  and  $f_3$ . Next,  $t_2$  is simulated. Since it detects the new fault  $f_4$ , it is retained in the test set. Finally,  $t_1$  is simulated and retained in the test set since it detects a new fault, which is  $f_1$ . No tests are dropped by ROF in this case.

Now, let us start ROF again taking into account the information given in Figure 3. ROF starts by simulating  $t_3$ . This test is retained in the test set to detect  $f_2$  and  $f_3$ . Next,  $t_2$  is simulated.  $t_2$  detects the new fault  $f_4$ . However,  $f_4$  is first detected by  $t_1$ . Therefore, we conclude that  $t_2$  is not necessary for the detection of any yet undetected fault and we drop it from the test set. Finally, when  $t_1$  is simulated, the remaining undetected faults  $f_1$  and  $f_4$  become detected and the detection process completes. In this case, one test vector is dropped from the test set.

2.3.3 *TVR with Fault Distribution*. In TVR with fault distribution, a test vector is fault simulated without fault dropping. Faults detected by every test vector are recorded. Besides, the number of test vectors that detect every fault is recorded. After that, given any order, a test vector whose number of essential faults is zero, i.e. the faults it detects can be distributed among other test vectors, is considered redundant and thus can be dropped. After a test vector is dropped, the number of test vectors that detect every one of its faults is reduced by one.

In [Hamzaoglu and Patel 1998], compaction based on fault distribution was used to compact test sets as a part of a dynamic compaction algorithm. The motive behind the proposed algorithm is the fact that ROF cannot identify a redundant test vector if some of the faults detected by it are only detected by the test vectors generated earlier. ROF can only identify a redundant test vector if all the faults detected by it are also detected by the test vectors generated later.

TVR with Double Detection Fault Simulation. Double Detection (DD) 2.3.4was first proposed in [Kajihara et al. 1995] as a dynamic compaction algorithm. Basically, when generating a new test vector, a yet undetected fault, called a primary target fault, is selected and a test vector t is generated to detect it. Next, other faults, called secondary target faults, are selected one at a time and the unspecified values in t are specified appropriately to detect the secondary target faults until no unspecified values remain in t or no additional secondary target faults can be detected. In choosing the secondary target faults, faults that are not detected are first considered and then faults detected at most once by earlier generated test vectors are considered. Faults are dropped from the list of target faults when they are detected twice. Test vectors that detect faults which are detected only once, i.e. essential test vectors, are marked. After the test generation is complete (when all the faults are detected at least once or aborted or proved to be untestable), the following static compaction procedure is used to reduce the test set size. The generated test vectors are fault simulated with dropping in the following order. First, all the essential test vectors are simulated in the order they were generated. The essential test vectors are followed by the non-essential test vectors in the order opposite to the order in which they were generated. During the fault simulation process, a test vector that does not detect any new fault is dropped. It should be

| Table I.           | Definition of the                         |        |   |  |  |

|--------------------|-------------------------------------------|--------|---|--|--|

| merging operation. |                                           |        |   |  |  |

|                    | 0                                         |        |   |  |  |

| 0                  | $egin{array}{c} 0 \ \phi \ 0 \end{array}$ | $\phi$ | 0 |  |  |

| 1                  | $\phi$                                    | 1      | 1 |  |  |

| x                  | 0                                         | 1      | x |  |  |

pointed out that essential test vectors cannot be dropped and thus simulating them first maximizes the ability to drop other test vectors.

DD can be used in static compaction procedures, e.g. [Lin et al. 2001]. However, since most test generators do not attempt to target faults for a second detection and do not use non-fault dropping simulation, they do not collect all the information necessary for static compaction based on DD. Therefore, the necessary information must be collected in a preprocessing step.

#### 2.4 Merging

Static compaction algorithms in this class can be divided into two groups. The first group contains algorithms based on the very simple and efficient approach of merging compatible test cubes. A test cube is a relaxed test vector. A test vector is relaxed by unspecifying the unnecessary primary inputs. A test vector can be relaxed using an ATPG or a stand-alone algorithm, such as [El-Maleh and Al-Suwaiyan 2002; Kajihara and Miyase 2001]. A merging procedure employing relaxation proceeds as follows. Given a test set T, test vectors in T are all relaxed. Then, an iterative search is performed for pairs of compatible test vectors. Two test vectors  $t_i$  and  $t_j$  are compatible if they do not specify complementary values in any bit position. If any two vectors, say  $t_i$  and  $t_j$ , are compatible, they are replaced by the vector  $t_i \circ t_i$ , where  $\circ$  represents the merging operation (see the definition in Table I). The new test vector  $t_i \circ t_j$  has all the binary values of both  $t_i$  and  $t_i$ . Hence, by a repetitive application of the above compaction operation, many test vectors (two or more) can be combined into fewer test vectors. As a result the total number of test vectors that need to be applied with the same fault detection capabilities is reduced. Examples of this approach can be found in [El-Maleh and Al-Suwaiyan 2002; Ayari and Kaminska 1994; Miyase et al. 2002].

In the second group, algorithms employ in addition to the relaxation operation a raising operation. For a test vector t, the raising operation raise(t, i) tries to set the  $i^{th}$  bit of t to x while preserving the coverage of the essential faults of t. The raising operation was proposed in [Chang and Lin 1995]. Raising is used to enhance compatibility among relaxed test vectors. For example, if two relaxed test vectors, say  $t_i$  and  $t_j$ , conflict at one or more bit positions, they can be made compatible by raising one of them at the conflicting bit positions. Typically, raising is used to resolve conflicts when a test set contains no compatible test vectors.

#### 2.5 Test Vector Decomposition

Test Vector Decomposition (TVD) is the process of decomposing a test vector into its atomic components. An atomic component is a child test vector that is generated by relaxing its parent test vector for a single fault f. That is, the child test vector contains the assignments necessary for the detection of f. Besides, the child test vector may detect other faults in addition to f. For example, consider the test vector

$t_p = 010110$  that detects the set of faults  $F_p = \{f_1, f_2, f_3\}$ . Using the relaxation algorithm in [El-Maleh and Al-Suwaiyan 2002],  $t_p$  can be decomposed into three atomic components, which are  $(f_1, 01xxxx)$ ,  $(f_2, 0x01xx)$ , and  $(f_3, x1xx10)$ . Every atomic component detects the fault associated with it and may accidentally detect other faults. An atomic component cannot be decomposed any further because it contains the assignments necessary for detecting its fault.

Static compaction based on merging is a very simple and efficient technique. However, it has the following problems. First, for a highly incompatible test set, merging achieves little reduction. Secondly, raising is a costly operation. Thirdly, a test vector must be processed as a whole. Therefore, we propose that a test vector be decomposed into its atomic components before it is processed. In this way, a test vector that is originally incompatible with all other test vectors in a given test set can be eliminated if its components can be merged with other test vectors.

By decomposing a test vector into its atomic components, a merging based compaction algorithm will have more degree of freedom. This is because of the fact that the number of unspecified bits in an atomic component is much larger than that in a parent test vector. Thus, the probability of merging a component is higher than that of merging its parent test vector.

The problem of static compaction based on TVD can be modeled as a graph coloring problem. Basically, given a test set T with single stuck-at fault coverage  $FC_T$ , the set of atomic components  $C_T$  is first obtained. Then, a graph G is built. In G, every node corresponds to a component and an edge exists between two nodes if their corresponding components are incompatible. Now, our objective is to partition  $C_T$  into k subsets such that k is as small as possible and no adjacent nodes belong to the same subset. The fault coverage of the new test set  $T^*$  whose size is k should be greater than or equal to  $FC_T$ .

It is well known that graph coloring is an NP-hard problem [Garey and Johnson 1979]. Thus, efforts of researchers are devoted to heuristic methods, rather than exact ones. Heuristic methods are simple schemes in which nodes are colored sequentially according to some criteria.

## 2.6 Essential Fault Pruning

Generally speaking, pruning a fault of a test vector decreases the number of its faults by one. A test vector becomes redundant if all of its faults are pruned. Fault Pruning (FP) is implemented as follows. Given a test vector t, an attempt is made to detect each of its faults by modifying the other test vectors in the test set. A fault of t is said to be pruned if it becomes detected by another test vector after the modification. If all the faults of t are pruned, then t can be removed from the test set.

The above operation of modifying a test vector, say t', to further detect an additional fault f of another test vector t is basically achieved by generating a new test vector t'' such that  $\text{DET}(t'') = \text{DET}(t') \cup f$ , where DET(t) is the set of faults detected by t. Multiple Target Faults Test Generation (MTFTG) is used for this purpose. In MTFTG, a test vector is to be found for a set of target faults. MTFTG will fail if there exists at least two independent faults in the set of target faults. Two faults are independent if they cannot be detected by a single test vector.

The run time of an FP based static compaction procedure can be greatly improved

ACM Transactions on Design Automation of Electronic Systems, Vol. V, No. N, July 2003.

by considering only essential faults. A fault is defined to be an essential fault of a test vector t if it is detected only by t. The set of essential faults of t is denoted by ESS(t). It should be pointed out that whenever a test vector t is eliminated, for every fault belonging to the set DET(t) - ESS(t), the number of test vector detecting it is reduced by one.

Few FP based static compaction algorithms have been reported in the literature. Generally, they fall into two categories. In the first category, a test vector is modified such that it detects the new additional faults. The test vector already detects its essential faults. Therefore, the test generation time for the essential faults is eliminated. Examples of such static compaction algorithms can be found in [Hamzaoglu and Patel 1998; Chang and Lin 1995; Reddy et al. 1992; Hamzaoglu and Patel 2000]. On the other hand, in the second category, a set of N test vectors is replaced by a set of M < N new test vectors. The basic idea is to determine the faults that are detected only by one or more test vectors among the N test vectors to be replaced and find M < N test vectors that detect all theses faults. Examples of such static compaction algorithms can be found in [Kajihara et al. 1995; 1994].

# 3. TEST VECTOR DECOMPOSITION BASED STATIC COMPACTION ALGORITHMS

## 3.1 Independent Fault Clustering

3.1.1 Preliminaries. Independent faults were defined in [Akers and Krishnamurthy 1989]. Basically, given a combinational circuit, let  $T_i$  be the set of all possible test vectors that detect  $f_i$  and  $T_j$  be the set of all possible test vectors that detect  $f_j$ . Then, two faults  $f_i$  and  $f_j$  are independent if and only if  $T_i \cap T_j = \phi$ . Independence among faults can also be defined with respect to a test set T. Let  $T'_i$  be the set of test vectors in T that detect  $f_i$  and  $T'_j$  be the set of test vectors in T that detect  $f_j$ . Then, two faults  $f_i$  and  $f_j$  are independent with respect to T if and only if  $T'_i \cap T'_j = \phi$ . In this paper, we use the term independent faults to mean independent faults with respect to a test set.

A fault set is called an Independent Fault Set (IFS) if all the faults in this set are pairwise independent. The problem of computing a maximum size IFS is NP-Hard [Krishnamurthy and Akers 1984]. Therefore, only *maximal* IFSs can be practically computed. Heuristic methods for computing IFSs were described in [Akers and Joseph 1987; Akers and Krishnamurthy 1989; Tromp 1991; Pomeranz and Reddy 1992].

IFSs were used in [Akers and Joseph 1987; Tromp 1991; Pomeranz et al. 1993; Kajihara et al. 1994; 1995; Chang and Lin 1995; Wang and Stabler 1995; Hamzaoglu and Patel 1998; 2000]. The importance of independent faults is threefold [Pomeranz and Reddy 1992]. First, they provide a lower bound on the size of the minimum test set, thus making it possible to estimate the success of test pattern generators in generating small test sets. Secondly, independent faults provide a method for ordering target faults for test generation. Ordering has been shown to be important for obtaining small test sets and reducing test generation time [Pomeranz et al. 1993]. Thirdly, the use of independent faults improves the efficiency of static compaction algorithms based on essential fault pruning.

Test Vector Decomposition Based Static Compaction Algorithms for Combinational Circuits

Algorithm IFC

**Input:** A test set T of size |T| and fault coverage  $FC_T$ . **Output:** A new test set  $T^*$  such that  $|T^*| \leq |T|$  and  $FC_{T^*} \geq FC_T$ .

- 1. Fault simulate T without fault dropping.

- 2. For every essential fault f that is detected by a test vector  $t{:}$

- 2.1. Extract the atomic component  $c_f$  from t.

- 2.2. If the number of compatibility sets is zero, create a new compatibility set, map  $c_f$  to it, and then go to Step 2.

- 2.3. Map  $c_f$  to an existing compatibility set, if possible, and then go Step 2.

- 2.4. Create a new compatibility set and map  $c_f$  to it.

- 3. Find sets of independent faults.

4. Sort sets of independent faults in decreasing order of their sizes.

5. For every fault in an IFS, sort the test vectors that detect the fault in

decreasing order of the number of faults they detect.

6. For every fault f, where f belongs to an IFS:

6.1. For every test vector t that detects f:

- 6.1.1. Extract the atomic component  $c_f$  from t.

- 6.1.2. If the number of compatibility sets is zero, create a new compatibility set, map  $c_f$  to it, and then go to Step 6.

- 6.1.3. Map  $c_f$  to an existing compatibility set, if possible, and go to Step 6.

- 6.2. Create a new compatibility set and map  $c_f$  to it.

7. Return  $T^*$ .

#### Fig. 4. The IFC algorithm.

3.1.2 Algorithm Description. In Independent Fault Clustering (IFC) algorithms, IFSs are first derived. Then, a fault matching procedure is used to find sets of compatible faults, i.e. faults that can be detected by a single test vector. In the IFS derivation phase, independent faults are identified with respect to a test set. On the other hand, in the fault matching phase, compatible components, corresponding to compatible faults, are mapped to the same compatibility set. Whenever a component is mapped to a compatibility set, it is merged with the partial test vector of that compatibility set. At the end, every compatibility set represents a single test vector.

Our IFC algorithm is shown in Figure 4 and proceeds as follows. First, the given test set T is fault simulated without fault dropping. This step is performed to find the number and set of test vectors that detect every fault. Secondly, essential faults are matched. In this step, for every essential fault f detected by t, the atomic component  $c_f$  corresponding to f is extracted from t. Then, for every compatibility set  $CS_i$ , if  $c_f$  is compatible with the partial test vector in  $CS_i$ ,  $c_f$  is mapped to  $CS_i$ . On the other hand, if the number of compatibility sets is zero or  $c_f$  is incompatibility with all partial test vectors in the existing compatibility sets, a new compatibility set is created and  $c_f$  is mapped to it.

It should be observed that an essential fault has a single component while nonessential faults have more than one. Therefore, if a component of a non-essential fault f is incompatible with all the partial test vectors in the existing compatibility sets, the other components of f will be tried before creating a new compatibility set. On the other hand, if the component of an essential fault is incompatible with all the partial test vectors in the existing compatibility sets, a new compatibility 9

| 0011  | iponents.  |              |            |

|-------|------------|--------------|------------|

|       | Test       | Fault        | Fault      |

|       | Vector     | Detected     | Component  |

| $v_1$ | 0xx11x0x10 | $f_1$        | xxx1xx0xxx |

|       |            | $f_2$        | 0xxx1xxxx0 |

|       |            | $f_3^e$      | 0xxxxx0x10 |

| $v_2$ | 10x1xxxx00 | $f_1$        | x0x1xxxxxx |

|       |            | $f_4^e$      | 1xxxxxxx00 |

|       |            | $f_5^e$      | 10x1xxxxxx |

| $v_3$ | 0xx0xxx00x | $f_6^e$      | 0xx0xxxxxx |

|       |            | $f_7^e$      | xxxxxxx00x |

| $v_4$ | 111xxxx0x0 | $f_2$        | x11xxxxxx0 |

|       |            | $f_8^e$      | 11xxxxx0xx |

| $v_5$ | xx000x11x1 | $f_9$        | xx000xxxxx |

|       |            | $f_{10}^{e}$ | xx0xxx11x1 |

| $v_6$ | x0x01xxx1x | $f_9$        | xxx0xxxx1x |

|       |            | $f_{11}^{e}$ | x0x01xxxxx |

Table II. Example test vectors and their components.

set must be created. Hence, essential faults should be matched first. Another advantage of first matching essential faults is that the number of faults that will be considered when deriving IFSs is reduced.

After essential faults are matched, IFSs are derived. Faults in an IFS are pairwise independent. Therefore, a fault  $f_i$  can be added to an IFS S if and only if for every fault  $f_j$  in S, the intersection of the sets of test vectors that detect  $f_i$  and  $f_j$  is empty. Next, IFSs are sorted in decreasing order of their sizes and for every fault in an IFS, the set of test vectors that detect the fault is sorted in decreasing order of the number of faults they detect. This is because a component that is extracted from a test vector that detects a large number of faults has high compatibility since it is compatible with all the components of the faults detected by that test vector.

Next, for every fault f in an IFS, its atomic component is extracted and then mapped to an appropriate compatibility set. For every component of a fault f, if it is incompatible with all partial test vectors in the existing compatibility sets, a new component will be tried. A new compatibility set is created if the number of compatibility sets is zero or all components of a fault f are incompatible with all partial test vectors in the existing compatibility sets. At the end, the algorithm returns the number of compatibility sets as the size of the new test set.

3.1.3 Illustrative Example. Table II shows an example of six test vectors and the faults they detect along with the components required for detecting the faults. The superscript e attached to some faults indicates that the faults are essential. As can be seen from the table, the six vectors cannot be merged together as there is at least one bit in conflict between each vector pair. Thus, the test vector merging method cannot compact these test vectors.

Table III illustrates applying the IFC algorithm on the test vectors in Table II. The first three columns show the clusters created after mapping the components of essential faults. After essential faults are mapped, IFSs are created and then their faults are mapped. There are two IFSs, namely  $IFS_1 = \{f_1, f_9\}$  and  $IFS_2 = \{f_2\}$ . Columns four and five show the clusters after mapping the components of faults in the IFSs. Finally, the last column shows the compacted test vectors after merging

|         | After Mapping |                 | After Mapping |                  | After Merging |

|---------|---------------|-----------------|---------------|------------------|---------------|

|         | $E_{i}$       | ssential Faults | Indep         | pendentFaultSets | Components    |

| Cluster | Fault         | FaultComponent  | Fault         | FaultComponent   | Test  Vector  |

| 1       | $f_3$         | 0xxxxx0x10      | $f_3$         | 0xxxxx0x10       | 00x01x0x10    |

|         | $f_6$         | 0xx0xxxxxx      | $f_6$         | 0xx0xxxxxx       |               |

|         | $f_{11}$      | x0x01xxxxx      | $f_{11}$      | x0x01xxxxx       |               |

|         |               |                 | $f_2$         | 0xxx1xxxx0       |               |

| 2       | $f_4$         | 1xxxxxx00       | $f_4$         | 1xxxxxxx00       | 10x1xx0000    |

|         | $f_5$         | 10x1xxxxxx      | $f_5$         | 10x1xxxxxx       |               |

|         | $f_7$         | xxxxxxx00x      | $f_7$         | xxxxxxx00x       |               |

|         |               |                 | $f_1$         | xxx1xx0xxx       |               |

| 3       | $f_8$         | 11xxxxx0xx      | $f_8$         | 11xxxxx0xx       | 11000xx0xx    |

|         |               |                 | $f_9$         | xx000xxxxx       |               |

| 4       | $f_{10}$      | xx0xxx11x1      | $f_{10}$      | xx0xxx11x1       | xx0xxx11x1    |

Table III. Example test vectors and their components.

#### Algorithm Iter\_IFC

**Input:** A test set T of size |T| and fault coverage  $FC_T$ . **Output:** A new test set  $T^*$  such that  $|T^*| \leq |T|$  and  $FC_{T^*} \geq FC_T$ .

1. Randomly fill the unspecified bits in T.

2.  $T^* = IFC(T)$

3. If  $|T^*| < |T|$ , copy  $T^*$  to T and go to Step 1. Else If  $|T^*| == |T|$ , return  $T^*$ . Else return T.

Fig. 5. The iterative IFC algorithm.

the components in each cluster. Since the number of clusters obtained is four, the compacted test set is of size four. Hence, two test vectors were eliminated.

3.1.4 Iterative IFC. The level of compaction achievable by our IFC algorithm can be improved in two ways. First, after a component is generated for a fault, the component is fault simulated and the faults detected by it are marked as detected. In this way, a large portion of the faults will not be considered subsequently since they are already detected. Based on our experimental investigations, we noticed that this extra step increases the runtime and improves the results very little. Secondly, the IFC algorithm can be called on a test set iteratively. Basically, the new test set generated is treated as the test set to be compacted. Therefore, IFC is carried out iteratively until the length of the test set cannot be reduced any more. This process is called *iterative* IFC and is shown in Figure 5. Unspecified bits in the test set T are assigned random values before every call to the IFC algorithm.

It should be pointed out that any static compaction algorithm can be used after our IFC algorithm. In fact, given a test set T, the IFC algorithm will generate a new test set  $T^*$  whose characteristics are different from the characteristics of T. Thus, a static compaction algorithm that cannot compact T may manage to compact  $T^*$ .

#### 3.2 Class-based Clustering

3.2.1 *Preliminaries.* Given the set of components of every test vector in a test set, a test vector can be eliminated if its components can be all moved to other test vectors. Moving a component to a test vector is implemented by merging the

component with the destination test vector. Even though the idea is very simple, it is not always possible to move a component to a new test vector. This is because of two problems: (1) blocking and (2) conflicting components. In the former, a component  $c_i$  is blocked from being moved to a test vector t when it becomes incompatible with it.  $c_i$  becomes incompatible with t when another component  $c_j$  that is incompatible with  $c_i$  is moved to t. In the latter, however, a test vector is uneliminatable if it contains at least one conflicting component. A conflicting component cannot be moved to any other test vector in the given test set.

Definition 1. (Conflicting Component). A component c of a test vector t belonging to a test set T is called a Conflicting Component (CC) if it is incompatible with every other test vector in T.

The number of CCs in a test vector determines its degree of hardness. The degree of hardness of a test vector is basically a measure of how much hard a test vector is to eliminate. Test vectors can be classified based on their degree of hardness.

Definition 2. (Degree of Hardness of a Test Vector). A test vector is at the  $n^{th}$  degree of hardness if it has n CCs.

Definition 3. (Class of a Test Vector). A test vector belongs to class k if its degree of hardness is k.

A CC can be moved to a test vector t if the characteristics of t are changed. That is, a CC  $c_i$  is movable to a test vector t, if the components in t incompatible with  $c_i$  can be moved to other test vectors. The set of test vectors to which  $c_i$  can be moved is referred to as the set of candidate test vectors of  $c_i$ . A test vector whose CCs are all movable is referred to as a potential test vector.

Definition 4. (Movable CC). Let  $c_i$  be a CC in a test vector  $t_s$ ,  $\beta$  be a set of components in a test vector  $t_d$  such that  $c_i$  is incompatible with every component  $c_j$  in  $\beta$ ,  $S_j$  be the set of test vectors compatible with  $c_j$ . Then,  $c_i$  is movable to  $t_d$  if and only if  $S_j \neq \phi$  for every  $c_j$  in  $\beta$ .

Definition 5. (Set of Candidate Test Vectors of a CC). The set of candidate test vectors of a CC  $c_i$ , denoted by  $S_{cand}(c_i)$ , contains all test vectors to which  $c_i$  can be moved.

Definition 6. (Potential Test Vector). Let  $\alpha$  be the set of CCs in a test vector t. t is a potential test vector that belongs to class  $|\alpha|$  if and only if for every CC  $c_i$  in  $\alpha$ ,  $c_i$  is movable.

3.2.2 Algorithm Description. After stating the necessary definitions, we now describe our Class-Based Clustering (CBC) algorithm. The CBC algorithm is based on the idea of dividing test vectors into classes and then heuristically processing test vectors of every class. A test vector is eliminated if its components can be all moved to other test vectors. Eventually, in the final test set, every test vector represents a cluster whose components originally belong to test vectors in different classes. This is why the technique is called CBC.

The CBC algorithm is shown in Figure 6 and proceeds as follows. First, the given test set is fault simulated without fault dropping. This step is performed

Test Vector Decomposition Based Static Compaction Algorithms for Combinational Circuits · 13

#### Algorithm CBC

**Input:** A test set T of size |T| and fault coverage  $FC_T$ . **Output:** A new test set  $T^*$  such that  $|T^*| \leq |T|$  and  $FC_{T^*} \geq FC_T$ .

1. Fault simulate T without fault dropping.

2. Sort test vectors in increasing order of their number of faults.

3. Generate atomic components (see Figure 7).

- 4. Sort test vectors in decreasing order of their number of components.

- 5. Remove redundant components using fault dropping simulation.

- 6. For every test vector, merge its components together.

- 7. Classify test vectors.

- 8. Process class zero test vectors (see Figure 8).

- 9. For every test vector, merge its components together.

- 10. Reclassify test vectors.

- 11. Process class one test vectors (see Figure 9).

- 12. For every test vector, merge its components together.

- 13. Reclassify test vectors.

- 14. Process class i test vectors, where i > 1 (see Figure 11).

Fig. 6. The CBC algorithm.

#### Algorithm Gen\_Comp

1. For every test vector t: 1.1. For every fault f detected by t: 1.1.1. If f is essential: a. Extract the atomic component  $c_f$ from t. Else b. Decrement the number of test vectors detecting f by one.

Fig. 7. Algorithm for generating components.

to find the number and set of test vectors that detect every fault. Secondly, test vectors are sorted in increasing order of their number of faults. Then, atomic components of test vectors are generated. Component generation is performed such that components are extracted from essential test vectors. An essential test vector is a test vector that detects at least one essential fault. The component generation algorithm is shown in Figure 7 and proceeds as follows. For every fault f detected by t, if the number of test vectors that detect f is one, i.e. f is an essential fault, the component of f is extracted from t; otherwise, the number of test vectors that detect f is reduced by one. Therefore, a test vector that detects no essential faults is eliminated. The sorting step preceding component generation improves the number of eliminated test vectors. Note that a component of a fault is extracted from a test vector that detects a large number of faults.

After obtaining the set of components of every test vector, test vectors are sorted in decreasing order of their number of components. This helps maximize the number of redundant components. Redundant components are dropped using fault simulation with dropping. After that, every test vector is reconstructed by merging its components together. Then, test vectors are classified and processed.

Class zero test vectors are processed as shown in Figure 8. First, test vectors are

14 • El-Maleh and Osais

#### Algorithm Proc\_Class\_0\_TVs

- 1. Sort class zero test vectors in increasing order of their number of components.

- 2. For every class zero test vector, compute its blockage value.

- 3. For every class zero test vector t whose blockage value is zero: 3.1. Move components of t to appropriate test vectors.

- 3.2. Eliminate t.

- 3.3. Update  $S_{comp}$  of components belonging to other class zero

- test vectors

- 3.4. Update the blockage values of other class zero test

- vectors. 4. Sort class zero test vectors in increasing order of their number

- of components.

- 5. For every remaining class zero test vector t:

- 5.1. If components of t can be all moved:

- 5.1.1. Move components of t to appropriate test vectors.

- 5.1.2. Eliminate t.

- 5.1.3. Update  $S_{comp}$  of components belonging to other

- class zero test vectors.

## Fig. 8. Algorithm for processing class zero test vectors.

sorted in increasing order of their number of components. This way a test vector with a small number of components has a higher chance of getting eliminated. After that, for every test vector, its blockage value is computed. The blockage value of a test vector t, denoted by TVB(t), can be defined as the sum of the blockage values of the individual components making up t. This can be shown mathematically as follows.

$$TVB(t) = \sum_{i=1}^{NumComp} CB(c_i),$$

where  $CB(c_i)$  is the blockage value of component  $c_i$  belonging to the set of components of t and NumComp is the number of components making up t.

$CB(c_i)$  is mathematically defined as follows.

$$CB(c_i) = Min\{CB(c_i, t_j)\},\$$

where  $CB(c_i, t_j)$  is the number of class zero test vectors that will be blocked when component  $c_i$  is moved to test vector  $t_j$ ,  $t_j$  belongs to  $S_{comp}(c_i)$ , and  $S_{comp}(c_i)$  is the set of test vectors compatible with  $c_i$ . Note that when computing  $CB(c_i, t_j)$ only components  $c_k \in t_j$  such that  $S_{comp}(c_k) = 1$  and  $c_k$  is in conflict with  $c_i$  needs to be considered.

Components of a test vector whose blockage value is zero can be moved without blocking any class zero test vector. Therefore, for any class zero test vector whose blockage value is zero, its components are moved to appropriate test vectors and then it is eliminated. A component  $c_i$  is moved to a test vector  $t_j$  in  $S_{comp}(c_i)$  such that  $CB(c_i, t_j) = 0$ . If there is more than one test vector, a test vector with the smallest number of components is selected. This is based on the assumption that a test vector with a small number of components has a smaller probability of

ACM Transactions on Design Automation of Electronic Systems, Vol. V, No. N, July 2003.

15

Table IV. Example test vectors showing that although  $v_1$  has a zero blockage value, it blocks  $v_2$ .

| Test   | Component | $Set \ of \ Compatible$ |

|--------|-----------|-------------------------|

| Vector |           | Test  Vectors           |

| $v_1$  | $c_{11}$  | $\{v_3\}$               |

|        | $c_{12}$  | $\{v_4\}$               |

| $v_2$  | $c_{21}$  | $\{v_3, v_4\}$          |

conflicts with other components. The blockage values of the other class zero test vectors must be updated after merging the components of a class zero test vector. Note that the blockage value of a class zero test vector t needs to be updated if t has at least one component  $c_i$  whose  $S_{comp}$  has been modified or t receives new components. Besides, the blockage value needs to be updated if t has at least one component  $c_i$  in conflict with another component  $c_j$  such that  $S_{comp}(c_j)$  has been modified and  $S_{comp}(c_j) = 1$ .

Next, remaining class zero test vectors, having non-zero blockage value, are sorted in increasing order of their number of components. A remaining test vector t can be eliminated if for every component  $c_i$  in t,  $S_{comp}(c_i) \neq \phi$ . A component is heuristically moved to a test vector with the smallest number of components.  $S_{comp}$ of every component must be updated after eliminating every test vector.

It is worth mentioning that the technique we use for computing the blockage value of a class zero test vector is not exact. Consider for example the two test vectors shown in Table IV. Both vectors are in class zero. Suppose that  $c_{21}$  is in conflict with both  $c_{11}$  and  $c_{12}$ . Our technique will compute the blockage value of  $v_1$  as zero although it will block  $v_2$ . The correct blockage value of  $v_1$  is one.

After processing class zero test vectors, every test vector is reconstructed by merging its components together. Then, test vectors are reclassified. After that, class one test vectors are processed as shown in Figure 9. Basically, for every class one test vector,  $S_{cand}$  of the CC is found and potential test vectors are marked. Then, for every test vector in  $S_{cand}$ , the number of class one potential test vectors whose CCs can be moved to it is found. Besides, test vectors in  $S_{cand}$  of every class one potential test vector are sorted according to their types, i.e. a non-potential test vectors have the same type, they are sorted in decreasing order of the number of CCs that can be moved to every one of them.

After processing the  $S_{cand}$  of the CC of every class one potential test vector, class one potential test vectors are sorted in decreasing order of the number of non-potential test vectors in  $S_{cand}$ . This is done to reduce the number of CCs that may be moved to potential test vectors. After that, for every class one potential test vector  $t_p^1$ , its CC is moved to a test vector selected from  $S_{cand}$ , call it  $t_d$ , remaining components making up  $t_p^1$  are moved to appropriate test vectors, and test vectors are reclassified (see Figure 10). Before moving a remaining component, test vectors in its  $S_{comp}$  are sorted in decreasing order of their degree of hardness. This is to avoid increasing the number of components of test vectors having lower degrees of hardness since they have better chances of getting eliminated. After  $t_p^1$ is eliminated, for every test vector  $t_p^2$  whose CC can be moved to  $t_d$ ,  $t_p^2$  is processed in the same way as  $t_p^1$ .

#### Algorithm Proc\_Class\_1\_TVs

- 1. For every class one test vector t:

- 1.1. Find  $S_{cand}$  of the CC.

- 1.2. If  $S_{cand} \neq \phi$ , mark t as potential.

- 2. For every class one potential test vector t: 2.1. For every test vector in  $S_{cand}$ , find the number of class one potential test vectors whose CCs can be moved to it.

- 2.2. Sort test vectors in  $S_{cand}$  according to their types.

- 3. Sort class one potential test vectors in decreasing order of the

- number of non-potential test vectors in  $S_{cand}$ .

- 4. For every unprocessed class one potential test vector  $t_p^1$ : 4.1. Merge  $t_p^1$  (see Figure 10). Denote by  $t_d$  the test vector to which the CC of  $t_p^1$  has been moved.

- 4.2. If  $t_p^1$  has been eliminated, then for every class one potential test vector  $t_p^2$  whose CC can be moved to  $t_d$ , merge  $t_p^2$ .

Fig. 9. Algorithm for processing class one test vectors.

#### Algorithm Merge\_Class\_1\_Potential\_TV Input: A class one potential test vector $t_p$ .

- 1. If the CC in  $t_p$  is movable:

- 1.1. Move the CC to an appropriate test vector selected from  $S_{cand.}$

- 1.2. Move the remaining components to appropriate test vectors.

- 2. Reclassify test vectors.

Fig. 10. Algorithm for merging class one potential test vectors.

After processing class one test vectors, test vectors are reconstructed and then reclassified. Next, test vectors in class i, where i > 1, are processed as shown in Figure 11. Basically, for every class, if the number of potential test vectors is greater than zero, potential test vectors are marked. Then, if all the CCs of a potential test vector t can be moved, t is marked eliminated and its components are moved to other test vectors. If at least one CC of t cannot be moved, t is skipped. Several heuristics can be tried when moving a component. In our case, before moving a CC  $c_i$ , test vectors in  $S_{cand}(c_i)$  are sorted in decreasing order of the number of components incompatible with  $c_i$ . Besides, before moving a component  $c_j$  that is not CC, test vectors in  $S_{comp}(c_i)$  are sorted in decreasing order of their degree of hardness. Note that test vectors are reclassified after moving every CC and set of remaining components.

3.2.3 Illustrative Example. We now illustrate the application of the CBC algorithm on the example given in Table II. Table V shows the test vectors and their components after the component generation phase. In the example, redundant components are not dropped for simplicity. The second column shows the class of each test vector. The third and fourth columns show the faults detected by each test vector and their components, respectively. The last column shows the set of compatible test vectors with each component.

We first consider test vectors in class zero with the smallest number of compo-

#### Algorithm Proc\_Remaining\_Classes

- 1. For every class i, where i > 1:

- 1.1. Find the set of class i potential test vectors.

- 1.2. For every class *i* potential test vector  $t_p$ : 1.2.1. For every CC in  $t_p$ :

- a. Move the CC to an appropriate test vector; otherwise, go to Step 1.2.

b. Reclassify test vectors.

- 1.2.2. If all CCs in t<sub>p</sub> have been moved:a. Move remaining components.b. Reclassify test vectors.

| TP: 11    | A 1 • . 1      | C   |            |           | 1        |

|-----------|----------------|-----|------------|-----------|----------|

| Fig. 11.  | Algorithm      | tor | nrococcing | romaining | 000000   |

| 1 15, 11, | 7 ingoi i unni | 101 | processing | romanning | crasses. |

| Test   | Class | Fault    | Component  | $Set \ of \ Compatible$ |

|--------|-------|----------|------------|-------------------------|

| Vector |       |          |            | Test  Vectors           |

| $v_1$  | 0     | $f_3$    | 0xxxxx0x10 | $\{v_6\}$               |

| $v_2$  | 0     | $f_1$    | x0x1xxxxxx | $\{v_1, v_5\}$          |

|        |       | $f_4$    | 1xxxxxx00  | $\{v_4\}$               |

|        |       | $f_5$    | 10x1xxxxxx | $\{v_5\}$               |

| $v_3$  | 0     | $f_6$    | 0xx0xxxxxx | $\{v_1, v_5, v_6\}$     |

|        |       | $f_7$    | xxxxxxx00x | $\{v_2, v_4\}$          |

| $v_4$  | 1     | $f_2$    | x11xxxxxx0 | $\{v_1, v_3\}$          |

|        |       | $f_8$    | 11xxxxx0xx | {}                      |

| $v_5$  | 0     | $f_{10}$ | xx0xxx11x1 | $\{v_6\}$               |

| $v_6$  | 0     | $f_9$    | xxx0xxxx1x | $\{v_1, v_4, v_5\}$     |

|        |       | $f_{11}$ | x0x01xxxxx | $\{v_1,v_3,v_5\}$       |

Table V. Test vectors and their generated components.

| Table VI.       | Test vectors | and t | their | components | after | elim- |

|-----------------|--------------|-------|-------|------------|-------|-------|

| inating $v_1$ . |              |       |       |            |       |       |

| Test   | Class | Fault    | Component  | Set  of  Compatible |

|--------|-------|----------|------------|---------------------|

| Vector |       |          |            | Test  Vectors       |

| $v_2$  | 0     | $f_1$    | x0x1xxxxxx | $\{v_5\}$           |

|        |       | $f_4$    | 1xxxxxxx00 | $\{v_4\}$           |

|        |       | $f_5$    | 10x1xxxxxx | $\{v_5\}$           |

| $v_3$  | 0     | $f_6$    | 0xx0xxxxxx | $\{v_5, v_6\}$      |

|        |       | $f_7$    | xxxxxxx00x | $\{v_2, v_4\}$      |

| $v_4$  | 1     | $f_2$    | x11xxxxxx0 | $\{v_3\}$           |

|        |       | $f_8$    | 11xxxxx0xx | {}                  |

| $v_5$  | 1     | $f_{10}$ | xx0xxx11x1 | {}                  |

| $v_6$  | 1     | $f_9$    | xxx0xxxx1x | $\{v_4, v_5\}$      |

|        |       | $f_{11}$ | x0x01xxxxx | $\{v_3, v_5\}$      |

|        |       | $f_3$    | 0xxxxx0x10 | {}                  |

nents. We choose to eliminate  $v_1$  by moving its component to  $v_6$ . Table VI shows the test vectors and their components after eliminating  $v_1$ . We next eliminate  $v_3$  by moving the component of  $f_6$  to  $v_6$  and the component of  $f_7$  to  $v_4$ . Table VII shows the test vectors and their components after eliminating  $v_3$ . We next eliminate  $v_2$ by moving the components of  $f_1$  and  $f_5$  to  $v_5$  and the component of  $f_4$  to  $v_4$ . Table VIII shows the test vectors and their components after eliminating  $v_2$ .

Table VII. Test vectors and their components after eliminating  $v_3$ .

| eliminat | $\operatorname{mg} v_3.$ |          |            |                     |

|----------|--------------------------|----------|------------|---------------------|

| Test     | Class                    | Fault    | Component  | Set  of  Compatible |

| Vector   |                          |          |            | Test  Vectors       |

| $v_2$    | 0                        | $f_1$    | x0x1xxxxxx | $\{v_5\}$           |

|          |                          | $f_4$    | 1xxxxxxx00 | $\{v_4\}$           |

|          |                          | $f_5$    | 10x1xxxxxx | $\{v_5\}$           |

| $v_4$    | 2                        | $f_2$    | x11xxxxxx0 | {}                  |

|          |                          | $f_8$    | 11xxxxx0xx | {}                  |

|          |                          | $f_7$    | xxxxxxx00x | $\{v_2\}$           |

| $v_5$    | 1                        | $f_{10}$ | xx0xxx11x1 | {}                  |

| $v_6$    | 1                        | $f_9$    | xxx0xxxx1x | $\{v_5\}$           |

|          |                          | $f_{11}$ | x0x01xxxxx | $\{v_5\}$           |

|          |                          | $f_3$    | 0xxxxx0x10 | {}                  |

|          |                          | $f_6$    | 0xx0xxxxxx | $\{v_5\}$           |

Table VIII. Test vectors and their components after eliminating  $v_2$ .

| Test   | Class | Fault    | Component  | Set  of  Compatible |

|--------|-------|----------|------------|---------------------|

| Vector |       |          |            | Test  Vectors       |

| $v_4$  | 4     | $f_2$    | x11xxxxxx0 | {}                  |

|        |       | $f_8$    | 11xxxxx0xx | {}                  |

|        |       | $f_7$    | xxxxxxx00x | {}                  |

|        |       | $f_4$    | 1xxxxxxx00 | {}                  |

| $v_5$  | 3     | $f_{10}$ | xx0xxx11x1 | {}                  |

|        |       | $f_1$    | x0x1xxxxxx | {}                  |

|        |       | $f_5$    | 10x1xxxxxx | {}                  |

| $v_6$  | 4     | $f_9$    | xxx0xxxx1x | {}                  |

|        |       | $f_{11}$ | x0x01xxxxx | {}                  |

|        |       | $f_3$    | 0xxxxx0x10 | {}                  |

|        |       | $f_6$    | 0xx0xxxxxx | {}                  |

At this stage, none of the test vectors can be eliminated. So, the resulting compacted test set is obtained by merging the components in each test vector. The final test set is of size three and is {111xxxx000,1001xx11x1,00x01x0x10}.

# 3.3 Worst-Case Analysis

We analyze here the worst-case storage and runtime requirements of our algorithms. In the analysis, we assume that the test set, fault list, and circuit structure are given as inputs. Therefore, their memory and time requirements are not considered. Throughout the analysis, the number of test vectors in a test set will be denoted by  $N_T$ , size of a test vector will be denoted by  $N_{PI}$ , and the number of faults and gates in a circuit will be denoted by  $N_F$  and  $N_G$ , respectively.

3.3.1 Space Complexity. The space complexity of the IFC algorithm is analyzed as follows. In Step 1, a memory space of size  $O(N_F N_T)$  is required for storing the indexes of test vectors detecting every fault. In Step 2, a memory space of size  $O(N_{PI})$  is required for storing a component when it is generated. Besides, a memory space of size  $O(N_T N_{PI})$  is required for storing test vectors of compatibility sets. In Step 3, the memory space required for building IFSs is  $O(N_F)$ . Finally, in Step 6, a memory space of size  $O(N_{PI})$  is required for storing a component when it

is generated. Besides, a memory space of size  $O(N_T N_{PI})$  is required for storing test vectors of compatibility sets. Hence, the IFC algorithm has the space complexity  $O(N_T(N_F + N_{PI}))$ .

The space complexity of the CBC algorithm is analyzed as follows. In Step 1, a memory space of size  $O(N_F N_T)$  is required for storing the set of faults detected by every test vector. In Step 3, a memory space of size  $O(N_F N_{PI})$  is required for storing all the components. For every component, a list of size  $O(N_T)$  is required for storing the indexes of compatible/candidate test vectors. The complexity of this step is  $O(N_F N_T)$ . Furthermore, for every component belonging to class zero test vector, a list of size  $O(N_T)$  is required for storing the blockage values. The complexity of this step is  $O(N_F N_T)$ . Hence, the CBC algorithm has the space complexity  $O(N_F(N_T + N_{PI}))$ .

3.3.2 Time Complexity. The analysis of time complexity is based on the following two assumptions. First, logic simulation of a test vector requires  $O(N_G)$  basic operations. Secondly, fault simulation of a test vector for a single fault requires  $O(N_G)$  basic operations.

The time complexity of the IFC algorithm is analyzed as follows. In Step 1, the cost of fault simulation without fault dropping is  $O(N_F N_T N_G)$ . In Step 2, the cost of finding essential faults is  $O(N_F)$ . Besides, the costs of extracting a single component and mapping it are  $O(N_G)$  and  $O(N_T N_{PI})$ , respectively. Therefore, the overall complexity of Step 2 is  $O(N_F(N_T N_{PI} + N_G))$ . In Step 3, the cost of computing IFSs is  $O(N_F^2 N_T^2)$ . In Steps 4 and 5, the costs of sorting IFSs and test vectors detecting every fault are  $O(N_F \log_2 N_F)$  and  $O(N_F N_T \log_2 N_T)$ , respectively. In Step 6, the complexity of component extraction is  $O(N_F N_T N_G)$ . This is because a component is extracted a number of times  $O(N_T)$  if it is incompatible with existing compatibility sets. However, from our experimental results the average number of times a component is extracted for a fault is one. The complexity of mapping components of remaining faults to existing compatibility sets is  $O(N_F N_T^2 N_{PI})$ . Therefore, the overall complexity of Step 6 is  $O(N_F N_T (N_T N_{PI} + N_G))$ .

Based on our experimental analysis of the different phases of IFC (see Table XI), we noticed that most of the runtime of IFC is spent in computing the IFSs and matching the remaining faults. Hence, Steps 3 and 6 are the dominating sources of time consumption.

The time complexity of the CBC algorithm is computed as follows. In Step 1, the cost of fault simulation without fault dropping is  $O(N_F N_T N_G)$ . The cost of sorting test vectors in Step 2 is  $O(N_T log_2 N_T)$ . In Step 3, the cost of component generation is  $O(N_F N_G)$ . The cost of sorting test vectors in Step 4 is  $O(N_T log_2 N_T)$ . In Step 5, the cost of dropping redundant components using fault simulation with dropping is  $O(N_F^2 N_G)$ . The cost of merging components in Step 6 is  $O(N_F)$ . In Step 7, the cost of classifying test vectors is  $O(N_F N_T N_P I)$ .

Computing the cost of processing class zero test vectors involves the following steps (see Figure 8). In Step 1, the cost of sorting class zero test vectors is  $O(N_T log_2 N_T)$ . In Step 2, the cost of computing blockage values for all class zero test vectors is  $O(N_F^2 N_T N_{PI})$ . In Step 3, the cost of moving components to appropriate test vectors is  $O(N_F N_T)$  and the cost of updating  $S_{comp}$  for all components belonging to class zero test vectors is  $O(N_F N_T N_{PI})$ . Note that only components

ACM Transactions on Design Automation of Electronic Systems, Vol. V, No. N, July 2003.

whose  $S_{comp}$  contains eliminated and/or modified test vectors should be updated. The cost of updating blockage values for all class zero test vectors is  $O(N_F^2 N_T^2 N_{PI})$ . The cost of sorting test vectors in Step 4 is  $O(N_T log_2 N_T)$ . Finally, the cost of processing remaining class zero test vectors is  $O(N_F N_T^2 N_{PI})$ .

Based on our experimental analysis of the class zero algorithm (see Table XV), we noticed that most of the runtime of the algorithm is spent in computing class zero test vector blockage values and updating  $S_{comp}$  and blockage values of components. Hence, Steps 2, 3.3, and 3.4 are the dominating sources of time consumption.

After processing class zero test vectors, components of test vectors are merged and test vectors are reclassified. The costs of merging components and reclassifying test vectors are  $O(N_F)$  and  $O(N_F N_T N_{PI})$ , respectively. After that, class one test vectors are processed as shown in Figure 9. In Step 1, the complexity of finding class one test vectors is  $O(N_T)$ . Besides, the complexity of computing  $S_{cand}$  of a CC belonging to class one test vector is  $O(N_F N_{PI})$ . This process costs  $O(N_T N_F N_{PI})$  for all CCs. Thus, the complexity of Step 1 is  $O(N_F N_T N_{PI})$ . In Step 2, the cost of finding class one potential test vectors is  $O(N_T)$ . Furthermore, the cost of Step 2.1 is  $O(N_T^3)$ . The cost of sorting test vectors in Step 2.2 is  $O(N_T^2 \log_2 N_T)$ . Therefore, the time complexity of Step 2 is  $O(N_T^3)$ . In Step 3, the cost of sorting class one potential test vectors is  $O(N_T log_2 N_T)$ . Computing the complexity of merging a class one potential test vector in Step 4 involves the following steps. First, the complexity of moving the CC to an appropriate test vector is  $O(N_T)$ . Secondly, the complexity of moving remaining components to appropriate test vectors is  $O(N_F N_T)$ . Thirdly, the complexity of reclassifying test vectors is  $O(N_F N_T N_{PI})$ . Therefore, the complexity of Step 4 is  $O(N_F N_T^2 N_{PI})$ . Hence, from the above analysis, it can be seen that the complexity of processing class one test vectors is  $O(N_F N_T^2 N_{PI})$ .

After processing class one test vectors, components of test vectors are merged and test vectors are reclassified. The costs of merging components and reclassifying test vectors are  $O(N_F)$  and  $O(N_F N_T N_{PI})$ , respectively. After that, class *i* test vectors, where i > 1, are processed. As can be seen from the algorithm in Figure 11, the complexity of processing remaining classes is  $O(N_F N_T^2 N_{PI})$ .

Based on our experimental analysis of the different phases of CBC (see Table XV), we noticed that the CBC algorithm spends most of its runtime in the component generation, component elimination, and blockage value computation phases. Hence, Steps 3 and 5 in Figure 6 and Step 2 in Figure 8 are the dominating sources of time consumption.

# 4. EXPERIMENTAL RESULTS

In order to demonstrate the effectiveness of the IFC and CBC algorithms, we have performed experiments on a number of the ISCAS85 and full-scanned versions of ISCAS89 benchmark circuits. The experiments were run on a SUN Ultra60 (UltraSparc II-450 MHz) with a RAM of 512 MB. We have used test sets generated by HITEC [Niermann and Patel 1991]. In addition, we have used the fault simulator HOPE [Lee and Ha 1996] for fault simulation purposes and the test relaxation algorithm in [El-Maleh and Al-Suwaiyan 2002] for component generation.

Table IX summarizes the features of benchmark circuits we have used in our

|           |           | Table IX.  | Benchma | rk circui | ts.   |       |        |

|-----------|-----------|------------|---------|-----------|-------|-------|--------|

| Cct       | #  Inputs | #  Outputs | #Gates  | # TVs     | #CFs  | # DFs | FC     |

| c2670     | 233       | 140        | 1193    | 154       | 2747  | 2630  | 95.741 |

| c3540     | 50        | 22         | 1669    | 350       | 3428  | 2895  | 84.452 |

| c5315     | 178       | 123        | 2307    | 193       | 5350  | 5291  | 98.897 |

| s13207.1f | 700       | 790        | 7951    | 633       | 9815  | 9664  | 98.462 |

| s15850.1f | 611       | 684        | 9772    | 657       | 11725 | 11335 | 96.674 |

| s208.1f   | 18        | 9          | 104     | 78        | 217   | 217   | 100    |

| s3271f    | 142       | 130        | 1572    | 256       | 3270  | 3270  | 100    |

| s3330f    | 172       | 205        | 1789    | 704       | 2870  | 2870  | 100    |

| s3384f    | 226       | 209        | 1685    | 240       | 3380  | 3380  | 100    |

| s38417f   | 1664      | 1742       | 22179   | 1472      | 31180 | 31004 | 99.436 |

| s38584f   | 1464      | 1730       | 19253   | 1174      | 36303 | 34797 | 95.852 |

| s4863f    | 153       | 120        | 2342    | 132       | 4764  | 4764  | 100    |

| s5378f    | 214       | 228        | 2779    | 359       | 4603  | 4563  | 99.131 |

| s6669f    | 322       | 294        | 3080    | 138       | 6684  | 6684  | 100    |

| s9234.1f  | 247       | 250        | 5597    | 620       | 6927  | 6475  | 93.475 |

Table IX. Benchmark circuits.

Table X. Results by the RM, GC, and IFC algorithms.

| Cct       | ROF | RM  |       | G   | C           |     | IFC            |  |  |

|-----------|-----|-----|-------|-----|-------------|-----|----------------|--|--|

|           | #   | #   | #     | #   | Time (sec.) | #   | $Time\ (sec.)$ |  |  |

|           | TVs | TVs | Comp  | TVs | Total       | TVs | Total          |  |  |

| c2670     | 106 | 100 | 761   | 99  | 8.03        | 96  | 6.95           |  |  |

| c3540     | 83  | 80  | 657   | 83  | 9.08        | 83  | 8.98           |  |  |

| c5315     | 119 | 106 | 1491  | 117 | 34.95       | 103 | 31             |  |  |

| s13207.1f | 476 | 252 | 3516  | 248 | 339.93      | 243 | 169            |  |  |

| s15850.1f | 456 | 181 | 4135  | 169 | 463.95      | 144 | 249            |  |  |

| s208.1f   | 33  | 33  | 94    | 33  | 0.009       | 32  | 0.93           |  |  |

| s3271f    | 115 | 76  | 1212  | 69  | 14.97       | 61  | 7.02           |  |  |

| s3330f    | 277 | 248 | 1263  | 233 | 11.01       | 208 | 9              |  |  |

| s3384f    | 82  | 75  | 1048  | 73  | 15.01       | 72  | 7.97           |  |  |

| s38417f   | 822 | 187 | 12215 | 173 | 5327.3      | 145 | 2072           |  |  |

| s38584f   | 819 | 232 | 16086 | 210 | 9250        | 145 | 2590           |  |  |

| s4863f    | 65  | 59  | 607   | 52  | 24.01       | 49  | 25.96          |  |  |

| s5378f    | 252 | 145 | 1460  | 130 | 34.95       | 123 | 23             |  |  |

| s6669f    | 52  | 42  | 1286  | 40  | 60.01       | 35  | 37.91          |  |  |

| s9234.1f  | 375 | 202 | 2093  | 185 | 104.01      | 172 | 68.06          |  |  |

experiments. The first column gives the circuit name. Columns two through eight give the number of primary inputs, number of primary outputs, number of gates, number of Test Vectors (TVs), number of Collapsed Faults (CFs), number of Detected Faults (DFs), and Fault Coverage (FC), respectively.

In Table X, we report the results of applying the Random Merging (RM), Graph Coloring (GC), and IFC algorithms on the test sets after they are compacted by ROF. The first column gives the circuit name. The second and third columns give test set sizes after applying ROF and RM, respectively. Columns four through six give the results of the GC algorithm. The number of components obtained after dropping redundant ones is given under the column headed #Comp. Test set sizes are given under the column headed #TVs. The total time required by the GC algorithm is given under the column headed Total. Columns seven to eight give the results of the IFC algorithm. Test set sizes are given under the column headed

| $Cct \qquad \# \ \# \ CSs \ \# \ Size \ Avg. \# TVs \ Max. \# \ Time (sec.)$ |      |       |       |      |        |       |            |       |       |        |        |

|------------------------------------------------------------------------------|------|-------|-------|------|--------|-------|------------|-------|-------|--------|--------|

| Cct                                                                          | #    | #CSs  |       | Size | 0 1    |       | Max. #     |       |       |        |        |

|                                                                              | EFs  | After | IFSs  | of   | Per    | Tried | TVs        | FS    | Mat.  | Build. | Mat.   |

|                                                                              |      | Mat.  |       | Max. | Fault  | Per   | Tried  Per | ND    | EFs   | IFSs   | Rem.   |

|                                                                              |      | EFs   |       | IFS  |        | Fault | Fault      |       |       |        | Faults |

| c2670                                                                        | 269  | 91    | 787   | 26   | 22.2   | 1     | 2          | 0.95  | 0.06  | 1.96   | 3.96   |

| c3540                                                                        | 343  | 74    | 665   | 22   | 13.62  | 1.1   | 3          | 0.95  | 0.07  | 0.97   | 7      |

| c5315                                                                        | 302  | 85    | 1206  | 19   | 18.6   | 1.2   | 10         | 1.93  | 1.03  | 4      | 24.1   |

| s13207.1f                                                                    | 1153 | 208   | 2906  | 63   | 106.8  | 1.03  | 12         | 15    | 10.06 | 61.97  | 75     |

| s15850.1f                                                                    | 982  | 125   | 3301  | 62   | 95.61  | 1.04  | 16         | 23    | 15    | 56.05  | 151    |

| s208.1f                                                                      | 59   | 32    | 64    | 7    | 7.48   | 1.01  | 2          | 0.005 | 0.9   | 0.003  | 0.01   |

| s3271f                                                                       | 170  | 49    | 985   | 19   | 22.3   | 1.07  | 8          | 0.05  | 0.93  | 1.06   | 5      |

| s3330f                                                                       | 358  | 198   | 730   | 37   | 51.6   | 1.04  | 4          | 1.04  | 0.96  | 3      | 3.94   |

| s3384f                                                                       | 135  | 70    | 1221  | 10   | 25.93  | 1     | 4          | 0.95  | 0.02  | 1.97   | 5      |

| s38417f                                                                      | 1913 | 106   | 9466  | 107  | 176    | 1.1   | 51         | 87    | 74    | 753    | 1133   |

| s38584f                                                                      | 1670 | 126   | 10405 | 129  | 189.23 | 1.02  | 51         | 89.04 | 66    | 1212   | 1189   |

| s4863f                                                                       | 227  | 36    | 1473  | 14   | 15.16  | 1.16  | 6          | 0.96  | 0.98  | 2.05   | 21.95  |

| s5378f                                                                       | 320  | 109   | 1341  | 37   | 55.32  | 1.02  | 9          | 2.04  | 1.01  | 5.96   | 14     |

| s6669f                                                                       | 100  | 23    | 2340  | 12   | 15.94  | 1.1   | 6          | 0.96  | 0.95  | 8.02   | 27.04  |

| s9234.1f                                                                     | 722  | 157   | 1439  | 66   | 61.33  | 1.03  | 18         | 9     | 5.06  | 11     | 42.02  |

Table XI. Analysis of the different phases of IFC.

Table XII. Results by the Iter\_IFC algorithm.

| Cct       | IFC  | $Iter\_IFC$ |               |                |  |  |

|-----------|------|-------------|---------------|----------------|--|--|

|           | #TVs | #TVs        | #  Iterations | $Time\ (sec.)$ |  |  |

| c2670     | 96   | 85          | 6             | 42.07          |  |  |

| c3540     | 83   | 75          | 3             | 26.95          |  |  |

| c5315     | 103  | 86          | 4             | 88.04          |  |  |

| s13207.1f | 243  | 238         | 2             | 473.12         |  |  |

| s15850.1f | 144  | 129         | 1             | 374.95         |  |  |

| s208.1f   | 32   | 32          | 1             | 0.01           |  |  |

| s3271f    | 61   | 60          | 2             | 18.98          |  |  |

| s3330f    | 208  | 196         | 3             | 30.02          |  |  |

| s3384f    | 72   | 72          | 1             | 7.07           |  |  |

| s38417f   | 145  | 120         | 2             | 3775.06        |  |  |

| s38584f   | 145  | 124         | 3             | 8217.08        |  |  |

| s4863f    | 49   | 42          | 3             | 70.88          |  |  |

| s5378f    | 123  | 117         | 6             | 109            |  |  |

| s6669f    | 35   | 30          | 4             | 175.01         |  |  |

| s9234.1f  | 172  | 155         | 4             | 200.93         |  |  |

#TVs. The total time required by the IFC algorithm is given under the column headed *Total*.

The GC algorithm is called the Brelaz Color-Degree algorithm and is explained in [Mchugh 1990]. It proceeds as follows. First, an incompatibility graph is built. In this graph, nodes correspond to components and an edge exists between two nodes if their corresponding components are incompatible. Secondly, as long as the number of uncolored nodes is not zero, a node  $n^*$  is selected such that it has the maximum number of adjacent nodes. Now,  $n^*$  is colored with the current color  $c_k$ . Then, for every node  $n_i$  that is compatible with  $n^*$  and can be colored with  $c_k$ , it is colored with  $c_k$ . After that, the incompatibility graph is updated.

As can be seen from Table X, for most of the circuits, the GC algorithm is able

to compute test sets whose sizes are smaller than the sizes of the test sets obtained by RM. This observation reveals the potential of the TVD technique. Test sets computed by the GC algorithm are as much as 11.9% smaller than those computed by RM, e.g. 1% smaller for c2670, 9.5% smaller for s38584f, and 11.9% smaller for s4863f.

It can be seen that the results obtained by the IFC algorithm are better than those obtained by the RM and GC algorithms. The percentage improvement over the RM algorithm varies between 3% for s208.1f and 37.5% for s38584f. On the other hand, the percentage improvement over the GC algorithm varies between 1.4% for s3384f and 31% for s38584f. The runtime of the IFC algorithm is better than that of the GC algorithm.