| A                | ΓL           | J     | ١   | (          | 3   | 5 |

|------------------|--------------|-------|-----|------------|-----|---|

|                  |              |       |     | <b>.</b> . |     |   |

| 1 <i>2</i> 1 1 - | 1.1.1.1      | · . · | · : |            |     |   |

|                  | -41.8        |       | •   | ÷ •        |     |   |

| . 177. 11.       |              | L     |     |            |     |   |

|                  |              |       | •   |            |     |   |

| - 1995 h         |              | •••   | ••• |            |     |   |

|                  |              |       |     |            |     | - |

| 1                | 10 B R F     | ••    | •   | •          | • • |   |

| · · · •          |              |       | •   |            |     |   |

|                  |              |       | •   | • •        | ••• |   |

|                  |              | •••   | •   | •          | ••• |   |

|                  | <b>6</b> - 1 | •••   | •   | •          | ••• |   |

|                  | N 19         |       | • • |            |     |   |

|                  |              |       |     | •          | ••• | - |

|                  |              | •••   | . • | <u>.</u>   | ::: |   |

|                  | 2            |       |     | • •        |     |   |

| · · · ·          | 2            |       | ۰.  |            | ::  |   |

|                  |              | · · . | . : | ÷ .        | ••• |   |

|                  |              |       | 1   |            |     | 1 |

|                  |              |       | · · |            |     | _ |

# ATLAS High-Level Triggers, DAQ and DCS

# **Technical Proposal**

Issue: Revision: Reference: Created: Last modified: **Prepared by:**

0 CERN/LHCC/2000-17 31 March 2000 19 September 2000 ATLAS HLT/DAQ/DCS Group

1

All trademarks, copyright names and products referred to in this document are acknowledged as such.

# **ATLAS Collaboration**

### Armenia

Yerevan Physics Institute, Yerevan

### Australia

Research Centre for High Energy Physics, Melbourne University, Melbourne University of Sydney, Sydney

Austria

Institut für Experimentalphysik der Leopold-Franzens-Universität Innsbruck, Innsbruck

### Azerbaijan Republic

Institute of Physics, Azerbaijan Academy of Science, Baku

### **Republic of Belarus**

Institute of Physics of the Academy of Science of Belarus, Minsk National Centre of Particle and High Energy Physics, Minsk

### Brazil

Universidade Federal do Rio de Janeiro, COPPE/EE/IF, Rio de Janeiro

### Canada

University of Alberta, Edmonton Department of Physics, University of British Columbia, Vancouver University of Carleton/C.R.P.P., Carleton Group of Particle Physics, University of Montreal, Montreal Department of Physics, University of Toronto, Toronto TRIUMF, Vancouver University of Victoria, Victoria

### CERN

European Laboratory for Particle Physics (CERN), Geneva

### China

Institute of High Energy Physics, Academia Sinica, Beijing, University of Science and Technology of China, Hefei, University of Nanjing and University of Shandong

### **Czech Republic**

Academy of Sciences of the Czech Republic, Institute of Physics and Institute of Computer Science, Prague

Charles University, Faculty of Mathematics and Physics, Prague

Czech Technical University in Prague, Faculty of Nuclear Sciences and Physical Engineering, Faculty of Mechanical Engineering, Prague

### Denmark

Niels Bohr Institute, University of Copenhagen, Copenhagen

### Finland

Helsinki Institute of Physics, Helsinki

### France

Laboratoire d'Annecy-le-Vieux de Physique des Particules (LAPP), IN2P3-CNRS, Annecy-le-Vieux Université Blaise Pascal, IN2P3-CNRS, Clermont-Ferrand

Institut des Sciences Nucléaires de Grenoble, IN2P3-CNRS-Université Joseph Fourier, Grenoble Centre de Physique des Particules de Marseille, IN2P3-CNRS, Marseille Laboratoire de l'Accélérateur Linéaire, IN2P3-CNRS, Orsay LPNHE, Universités de Paris VI et VII, IN2P3-CNRS, Paris CEA, DSM/DAPNIA, Centre d'Etudes de Saclay, Gif-sur-Yvette

### Republic of Georgia

Institute of Physics of the Georgian Academy of Sciences and Tbilisi State University, Tbilisi

### Germany

Physikalisches Institut, Universität Bonn, Bonn Institut für Physik, Universität Dortmund, Dortmund Fakultät für Physik, Albert-Ludwigs-Universität, Freiburg Institut für Hochenergiephysik der Universität Heidelberg, Heidelberg Institut für Physik, Johannes-Gutenberg Universität Mainz, Mainz Lehrstuhl für Informatik V, Universität Mannheim, Mannheim Sektion Physik, Ludwig-Maximilian-Universität München, München Max-Planck-Institut für Physik, München Fachbereich Physik, Universität Siegen, Siegen Fachbereich Physik, Bergische Universität, Wuppertal

### Greece

Athens National Technical University, Athens Athens University, Athens High Energy Physics Department and Department of Mechanical Engineering, Aristotle University of Thessaloniki, Thessaloniki

### Israel

Department of Physics, Technion, Haifa Raymond and Beverly Sackler Faculty of Exact Sciences, School of Physics and Astronomy, Tel-Aviv University, Tel-Aviv

Department of Particle Physics, The Weizmann Institute of Science, Rehovot

### Italy

Dipartimento di Fisica dell' Università della Calabria e I.N.F.N., Cosenza Laboratori Nazionali di Frascati dell' I.N.F.N., Frascati Dipartimento di Fisica dell' Università di Genova e I.N.F.N., Genova Dipartimento di Fisica dell' Università di Lecce e I.N.F.N., Lecce Dipartimento di Fisica dell' Università di Milano e I.N.F.N., Milano Dipartimento di Scienze Fisiche, Università di Napoli 'Federico II' e I.N.F.N., Napoli Dipartimento di Fisica Nucleare e Teorica dell' Università di Pavia e I.N.F.N., Pavia Dipartimento di Fisica dell' Università di Pisa e I.N.F.N., Pisa Dipartimento di Fisica dell' Università di Roma 'La Sapienza' e I.N.F.N., Roma Dipartimento di Fisica dell' Università di Roma 'Tor Vergata' e I.N.F.N., Roma Dipartimento di Fisica dell' Università di Roma 'Roma Tre' e I.N.F.N., Roma Dipartimento di Fisica dell' Università di Udine, Gruppo collegato di Udine I.N.F.N. Trieste, Udine

### Japan

Department of Information Science, Fukui University, Fukui Hiroshima Institute of Technology, Hiroshima Department of Physics, Hiroshima University, Higashi-Hiroshima KEK, High Energy Accelerator Research Organisation, Tsukuba Department of Physics, Faculty of Science, Kobe University, Kobe Department of Physics, Kyoto University, Kyoto Kyoto University of Education, Kyoto-shi Department of Electrical Engineering, Nagasaki Institute of Applied Science, Nagasaki Naruto University of Education, Naruto-shi Department of Physics, Okayama University, Okayama Department of Physics, Faculty of Science, Shinshu University, Matsumoto International Center for Elementary Particle Physics, University of Tokyo, Tokyo Physics Department, Tokyo Metropolitan University, Tokyo Department of Applied Physics, Tokyo University of Agriculture and Technology, Tokyo Institute of Physics, University of Tsukuba, Ibaraki

### Morocco

Faculté des Sciences Aïn Chock, Université Hassan II, Casablanca, and Université Mohamed V, Rabat

### Netherlands

FOM - Institute SAF NIKHEF and University of Amsterdam/NIKHEF, Amsterdam University of Nijmegen/NIKHEF, Nijmegen

#### Norway

University of Bergen, Bergen University of Oslo, Oslo

#### Poland

Henryk Niewodniczanski Institute of Nuclear Physics, Cracow Faculty of Physics and Nuclear Techniques of the University of Mining and Metallurgy, Cracow

#### Portugal

Laboratorio de Instrumentação e Física Experimental de Partículas (University of Lisboa, University of Coimbra, University Católica-Figueira da Foz and University Nova de Lisboa), Lisbon

#### Romania

Institute of Atomic Physics, National Institute of Physics and Nuclear Engineering, Bucharest

### Russia

Institute for Theoretical and Experimental Physics (ITEP), Moscow P.N. Lebedev Institute of Physics, Moscow Moscow Engineering and Physics Institute (MEPhI), Moscow Moscow State University, Institute of Nuclear Physics, Moscow Budker Institute of Nuclear Physics (BINP), Novosibirsk Institute for High Energy Physics (IHEP), Protvino Petersburg Nuclear Physics Institute (PNPI), Gatchina, St. Petersburg

### JINR

Joint Institute for Nuclear Research, Dubna

### **Slovak Republic**

Bratislava University, Bratislava, and Institute of Experimental Physics of the Slovak Academy of Sciences, Kosice

### Slovenia

Jozef Stefan Institute and Department of Physics, University of Ljubljana, Ljubljana

### Spain

Institut de Física d'Altes Energies (IFAE), Universidad Autónoma de Barcelona, Bellaterra, Barcelona

Physics Department, Universidad Autónoma de Madrid, Madrid Instituto de Física Corpuscular (IFIC), Centro Mixto Universidad de Valencia - CSIC, Valencia

### Sweden

Fysiska institutionen, Lunds universitet, Lund Royal Institute of Technology (KTH), Stockholm University of Stockholm, Stockholm Uppsala University, Department of Radiation Sciences, Uppsala

### Switzerland

Laboratory for High Energy Physics, University of Bern, Bern Section de Physique, Université de Genève, Geneva

Taiwan

Institute of Physics, Academia Sinica, Taipei

Turkey

Department of Physics, Ankara University, Ankara Department of Physics, Bogaziçi University, Istanbul

### **United Kingdom**

School of Physics and Astronomy, The University of Birmingham, Birmingham Cavendish Laboratory, Cambridge University, Cambridge Department of Physics and Astronomy, University of Edinburgh, Edinburgh Department of Physics and Astronomy, University of Glasgow, Glasgow Department of Physics, Lancaster University, Lancaster Department of Physics, Oliver Lodge Laboratory, University of Liverpool, Liverpool Department of Physics, Queen Mary and Westfield College, University of London, London Department of Physics, Royal Holloway and Bedford New College, University of London, Egham Department of Physics and Astronomy, University College London, London Department of Physics and Astronomy, University of Manchester, Manchester Department of Physics, Oxford University, Oxford Rutherford Appleton Laboratory, Chilton, Didcot

Department of Physics, University of Sheffield, Sheffield

### **United States of America**

State University of New York at Albany, New York Argonne National Laboratory, Argonne, Illinois University of Arizona, Tucson, Arizona Department of Physics, The University of Texas at Arlington, Arlington, Texas Lawrence Berkeley Laboratory and University of California, Berkeley, California Department of Physics, Boston University, Boston, Massachusetts Brandeis University, Department of Physics, Waltham, Massachusetts Brookhaven National Laboratory (BNL), Upton, New York University of Chicago, Enrico Fermi Institute, Chicago, Illinois Nevis Laboratory, Columbia University, Irvington, New York Department of Physics, Duke University, Durham, North Carolina Department of Physics, Hampton University, Virginia Department of Physics, Harvard University, Cambridge, Massachusetts Indiana University, Bloomington, Indiana Department of Physics and Astronomy, Iowa State University, Ames, Iowa University of California, Irvine, California Massachusetts Institute of Technology, Department of Physics, Cambridge, Massachusetts University of Michigan, Department of Physics, Ann Arbor, Michigan Michigan State University, Department of Physics and Astronomy, East Lansing, Michigan University of New Mexico, New Mexico Center for Particle Physics, Albuquerque Physics Department, Northern Illinois University, DeKalb, Illinois Ohio State University, Columbus, Ohio Department of Physics and Astronomy, University of Oklahoma Department of Physics, University of Pennsylvania, Philadelphia, Pennsylvania University of Pittsburgh, Pittsburgh, Pennsylvania Department of Physics and Astronomy, University of Rochester, Rochester, New York Institute for Particle Physics, University of California, Santa Cruz, California Department of Physics, Southern Methodist University, Dallas, Texas State University of New York at Stony Brook, Stony Brook, New York Tufts University, Medford, Massachusetts High Energy Physics, University of Illinois, Urbana, Illinois Department of Physics, Department of Mechanical Engineering, University of Washington, Seattle, Washington Department of Physics, University of Wisconsin, Madison, Wisconsin

# Acknowledgments

The authors would like to thank Mario Ruggier for preparing the FrameMaker template upon which this document is based. The authors also warmly thank the CERN Desktop Publishing Service for their professional help in the organization of publishing the document, as well as the CERN Printshop staff for their helpful, friendly and efficient service.

# **Table Of Contents**

|   | ATL   | AS Col      | laboratio          | m                                                    | iii  |

|---|-------|-------------|--------------------|------------------------------------------------------|------|

|   | Ackr  | nowledg     | gments             |                                                      | viii |

| 1 | Intro | ductio      | n                  |                                                      | 1    |

|   | 1.1   | Purpo       | se and Se          | cope of the Technical Proposal                       | 1    |

|   | 1.2   | -           |                    | f the Technical Proposal                             |      |

|   |       | 1.2.1       |                    | Requirements of Physics and External Systems         |      |

|   |       | 1.2.2       |                    | Summary of work done in the HLT/DAQ/DCS Comm         |      |

|   |       | 1.2.3       |                    | Architecture Proposal and Issues for Further Work .  | U    |

|   | 1.3   | Refere      |                    | · · · · · · · · · · · · · · · · · · ·                |      |

|   |       |             |                    |                                                      |      |

| 2 | •     | -           | -                  | ts                                                   |      |

|   | 2.1   | 0           |                    | LHC                                                  |      |

|   | 2.2   |             |                    | etector                                              |      |

|   | 2.3   | Physic      | -                  | ements on the High-Level Triggers                    |      |

|   |       | 2.3.1       | Physics            | Process Signatures                                   | 4    |

|   |       | 2.3.2       | Definiti           | on of the Key Characterizations                      | 4    |

|   |       | 2.3.3       | Other P            | hysics-Related Requirements.                         | 5    |

|   | 2.4   | Summ        | nary               |                                                      | 5    |

|   | 2.5   | Refere      | ences .            |                                                      | 5    |

| 3 | Dete  | ctor Re     | quireme            | nts                                                  | 7    |

|   | 3.1   | Introd      | uction .           |                                                      | 7    |

|   | 3.2   | Functi      | ional Reg          | uirements                                            | 8    |

|   |       | 3.2.1       | Data A             | equisition.                                          | 8    |

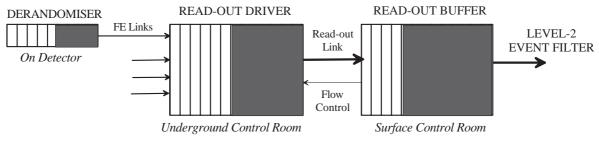

|   |       |             | 3.2.1.1            | -                                                    |      |

|   |       |             | 3.2.1.2            | Normal Running                                       | 9    |

|   |       |             | 3.2.1.3            | Standalone Running                                   | 9    |

|   |       |             | 3.2.1.4            | Test Beam                                            |      |

|   |       |             | 3.2.1.5            | DAQ-DCS Interface                                    |      |

|   |       |             |                    | Interface between the DCS and Detector Configuration |      |

|   |       | 3.2.2       |                    | ing Aspects                                          |      |

|   |       | 01212       | 3.2.2.1            | Introduction                                         |      |

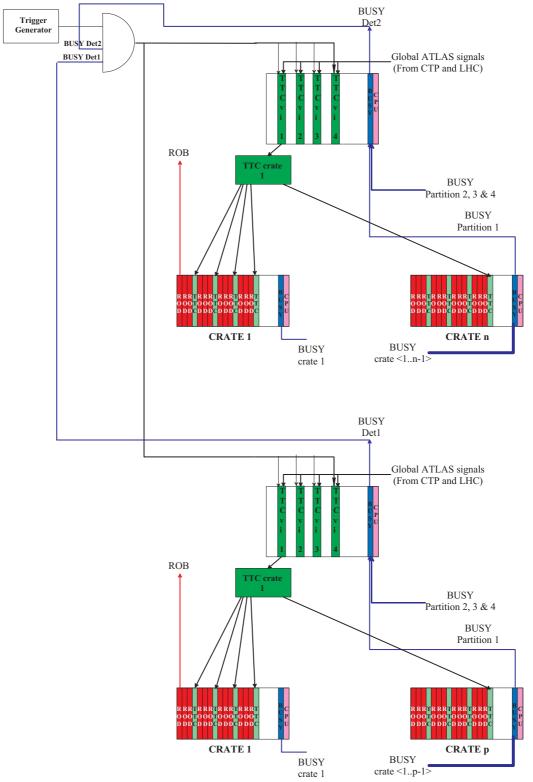

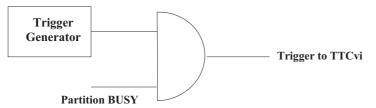

|   |       |             |                    | Dead-Time Handling in the RODs and ROBs              |      |

|   |       |             | 3.2.2.3            | ROD_BUSY Module                                      |      |

|   |       |             | 3.2.2.4            |                                                      |      |

|   | 3.3   | Interfa     |                    | irements                                             |      |

|   | 0.0   | 3.3.1       | -                  | nd Interfaces                                        |      |

|   |       | 3.3.2       |                    | t Links                                              |      |

|   |       | 5.5.2       | 3.3.2.1            |                                                      |      |

|   |       |             |                    | Prototype Work                                       |      |

|   |       |             | 3.3.2.2<br>3.3.2.3 | User Requirements of the Readout Link.               |      |

|   |       | <b>99</b> 9 |                    | -                                                    |      |

|   |       | 3.3.3       |                    | ormat                                                |      |

|   |       | 3.3.4       | Data M             | apping into the Readout Drivers                      | 16   |

|   | 3.4        | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | Exter      | rnal Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 4.1        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

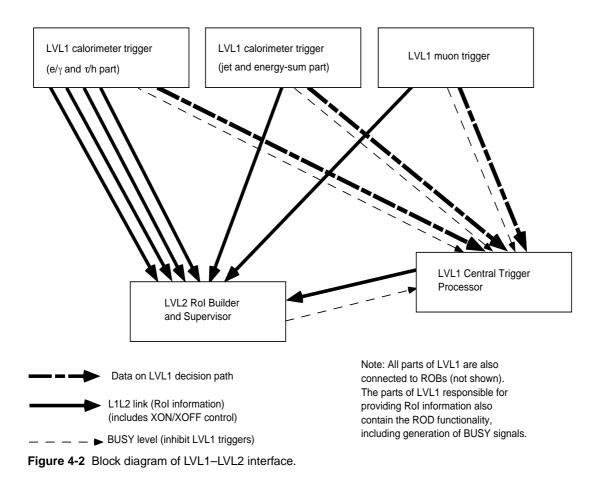

|   | 4.2        | LVL1-LVL2 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |            | 4.2.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |            | 4.2.2 LVL1 Trigger System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |            | 4.2.3 RoI Builder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |            | 4.2.4 LVL1-to-LVL2 Links                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |            | 4.2.4.1 Event Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |            | 4.2.4.2 Status Words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |            | 4.2.4.3 RoI Data Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 4.3        | LVL1-ROB Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 4.4        | Interface to the Offline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |            | 4.4.1 Software Architectural Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |            | 4.4.2 Software Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 4.5        | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| F |            | VEE 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

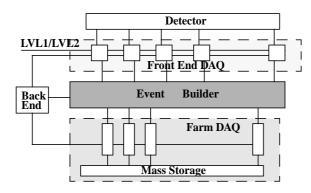

| 5 | DAQ<br>5.1 | 0/EF -1         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . </td |

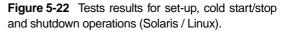

|   | 5.1<br>5.2 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

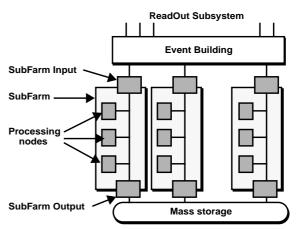

|   | 3.2        | DataFlow System         28           5.2.1         Introduction         28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |            | 5.2.1.1 DataFlow Factorization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |            | 5.2.2 The DAQ-Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |            | 5.2.2.1 Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |            | 5.2.2.2 Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

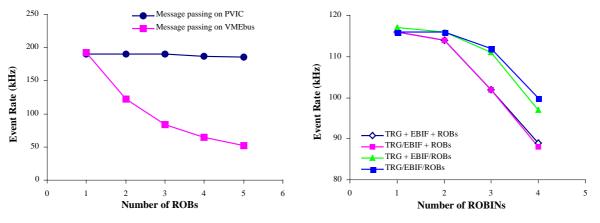

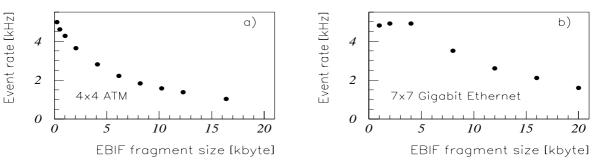

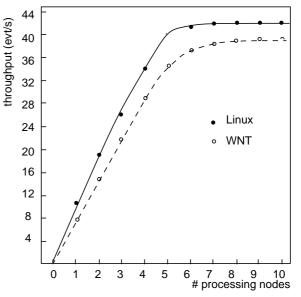

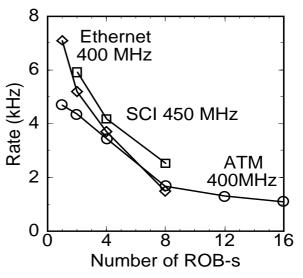

|   |            | 5.2.2.3 Performance Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |            | 5.2.3 Event Builder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

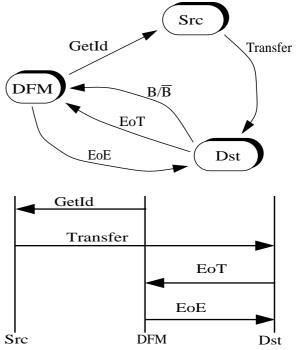

|   |            | 5.2.3.1 Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

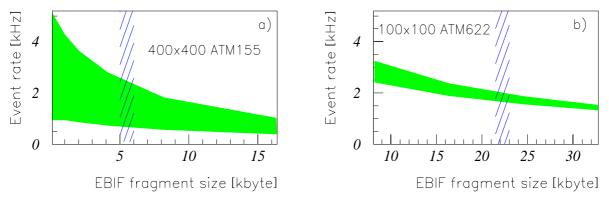

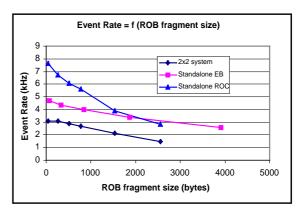

|   |            | 5.2.3.2 Prototype Implementation and Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |            | 5.2.3.3 Scalability Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |            | 5.2.4 LDAQ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $34$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |            | 5.2.4.1 Introduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $34$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |            | 5.2.4.2 Design $\ldots$ $\ldots$ $\ldots$ $\ldots$ $34$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |            | 5.2.4.3 Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

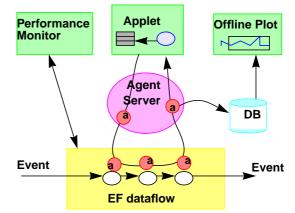

|   |            | 5.2.5Integrated DataFlow365.2.6DataFlow System Assessment36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

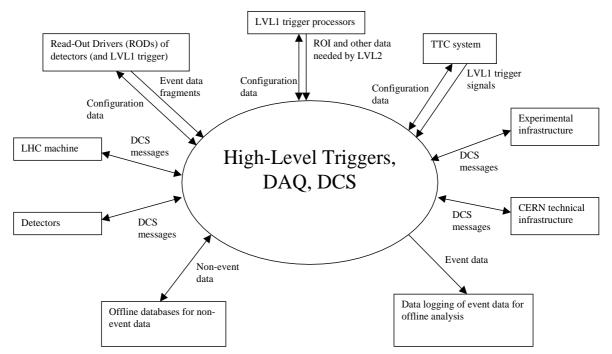

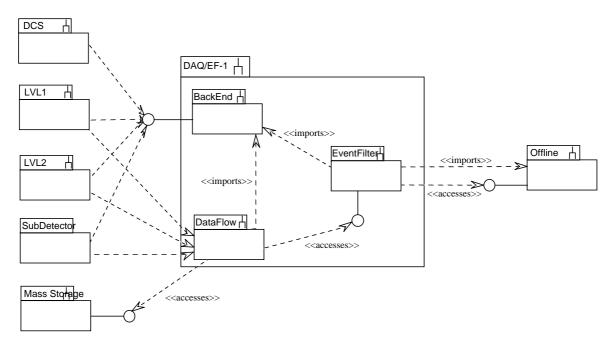

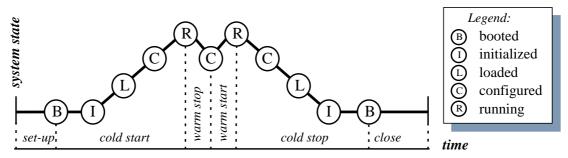

|   | 5.3        | 5.2.6.3       ATLAS HLT/DAQ view.       38         Back-End DAQ System.       38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

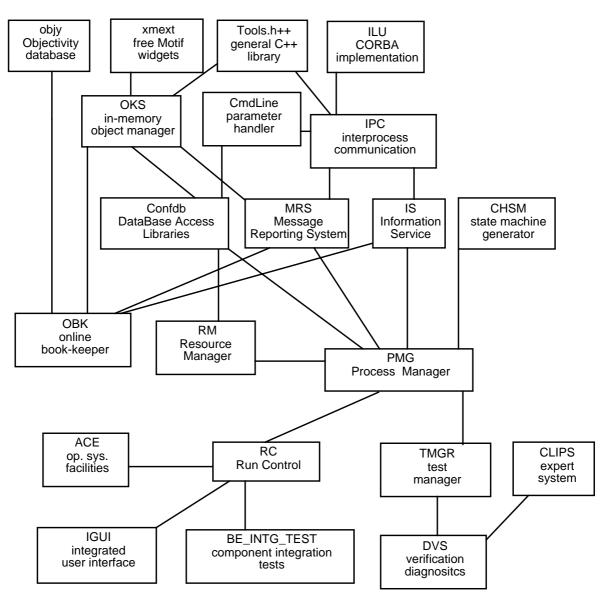

|   | J.J        | 5.3.1 The Software Component Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |            | 5.3.1 The Software Component Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |            | 5.3.1.1 Core Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |            | 5 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

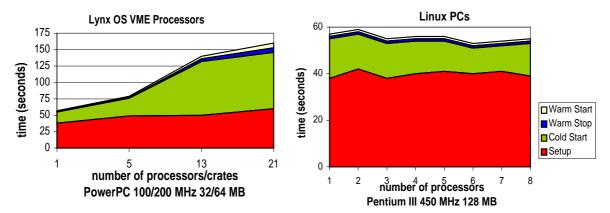

|   |            | 5.3.3 Integrated Back-End DAQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |     | 5.3.3.1 Component Tests                                      | 0 |

|---|-----|--------------------------------------------------------------|---|

|   |     | 5.3.3.2 Integration Tests.                                   |   |

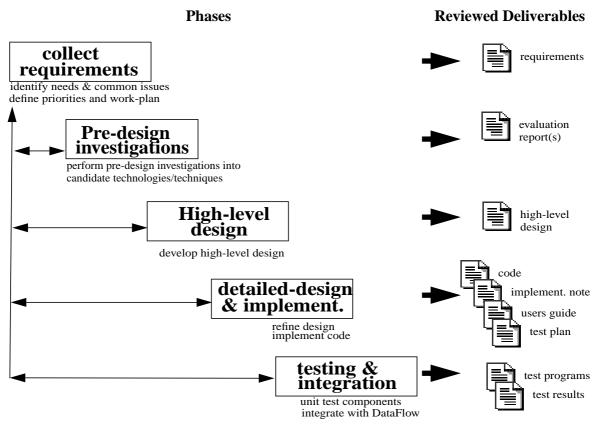

|   |     | 5.3.4 Software Process and Inspection                        |   |

|   | 5.4 | Event Filter System                                          |   |

|   |     | 5.4.1 Prototypes                                             |   |

|   |     | 5.4.2 Commodity PC Prototype                                 |   |

|   |     | 5.4.3 Symmetric Multi-Processor Prototype                    |   |

|   |     | 5.4.4 Intel Commodity Multiprocessor Prototype               |   |

|   |     | 5.4.5 Results and Comparison of the Prototypes               |   |

|   |     | 5.4.5.1 Data Redundancy and Robustness                       |   |

|   |     | 5.4.5.2 Data Communication Mechanisms                        | 6 |

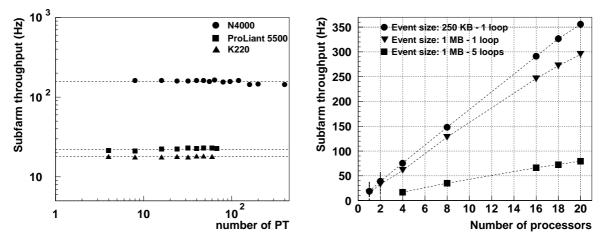

|   |     | 5.4.5.3 Throughput and Scalability 4                         | 7 |

|   |     | 5.4.5.4 SubFarm Configuration and Monitoring                 |   |

|   |     | 5.4.6 Event Filter System Assessment                         |   |

|   | 5.5 | Detector Interface System                                    |   |

|   | 5.6 | Global System Performance                                    |   |

|   |     | 5.6.1 Introduction                                           |   |

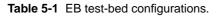

|   |     | 5.6.2 Configuration and Environment                          |   |

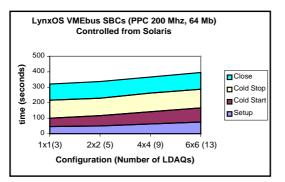

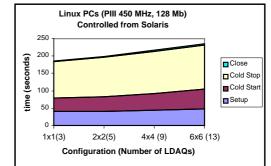

|   |     | 5.6.3 Tests and Results                                      |   |

|   |     | 5.6.3.1 Functionality                                        |   |

|   |     | 5.6.3.2 Performance                                          |   |

|   |     | 5.6.3.3 Scalability                                          |   |

|   | 5.7 | Conclusions                                                  |   |

|   | 5.8 | References                                                   |   |

| • |     |                                                              |   |

| 6 |     | LVL2 Pilot Project                                           |   |

|   | 6.1 | Introduction                                                 |   |

|   |     | 6.1.1 Principles of the Scheme in the ATLAS TP               |   |

|   |     | 6.1.2 Studies Prior to the LVL2 Pilot Project                |   |

|   |     | 6.1.3 The LVL2 Pilot Project                                 |   |

|   | 6.2 | Reference Software   6                                       |   |

|   |     | 6.2.1 Software Process, Requirements and Design              |   |

|   |     | 6.2.2 Implementation                                         |   |

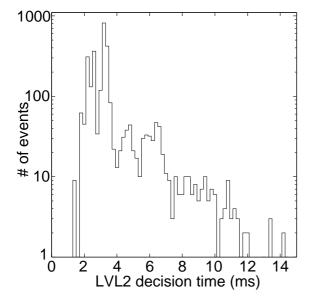

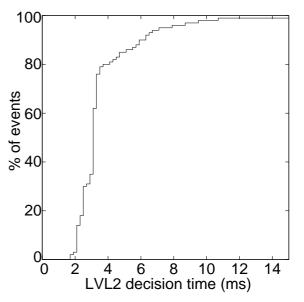

|   |     | 6.2.3 Results                                                |   |

|   |     | 6.2.4 Conclusions for the Reference Software                 |   |

|   | 6.3 | The Testbeds                                                 |   |

|   | 6.4 | Requirements of the ROB Complex and Implementation Studies 6 |   |

|   |     | 6.4.1 Operation of a ROB Complex                             |   |

|   |     | 6.4.2 ROB Complex Conclusions                                |   |

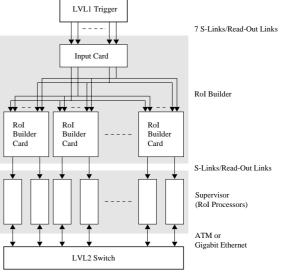

|   | 6.5 | The Supervisor and RoI Builder    6                          |   |

|   |     | 6.5.1 Overview                                               |   |

|   |     | 6.5.2 Design and Implementation of the RoI Builder 6         |   |

|   |     | 6.5.3 RoI Builder Tests                                      |   |

|   |     | 6.5.4 Integration into Testbeds                              |   |

|   |     | 6.5.5 Conclusions                                            |   |

|   | 6.6 | Processor Requirements and Measurements                      | 1 |

|   | 6.7   | Use of FPGAs as Co-Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

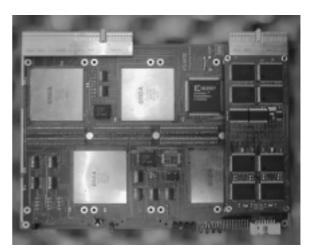

|   |       | 6.7.1 The ATLANTIS Processor System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |       | 6.7.2 Implementation of the TRT Full-Scan Algorithm in ATLANTIS . 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |       | 6.7.3 Prospects for FPGA Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |       | 6.7.4 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |