# Analog Readout for the ATLAS Semiconductor Tracker

**Christoph POSCH**

DISSERTATION

submitted to obtain the academic degree of Doktor der technischen Wissenschaften

prepared at

CERN, European Laboratory for Particle Physics, CH-1211 Geneva 23, Switzerland

and

Vienna University of Technology, Institute for Applied Electronics and Quantum Electronics, Gußhausstraße 25-29, A-1040 Vienna, Austria

supervised by

Prof. F. SEIFERT, Vienna University of Technology, Vienna, AustriaProf. W. DABROWSKI, University of Mining and Metallurgy, Cracow, PolandDr. P. WEILHAMMER, CERN/EP-ATT, Geneva, Switzerland

Geneva, January 1999

## Abstract

The context of the work, described in this document, is the development of electronic components for future high-energy physics experiments.

The first part deals with design and evaluation of an electronic device for reading and processing the signals, created by charged elementary particles in solid state detectors. This device has to work within an experimental environment, which imposes very rigorous requirements in terms of signal processing speed, noise performance, power dissipation, radiation hardness and size as well as in terms of system complexity. These constraints force its realization as a VLSI integrated circuit. An emphasis is put on the major problem, which occurs when dealing with extremely small signals, as the ones produced by a semiconductor detector. This problem concerns the low-noise operation of the front-end amplifiers.

The second part contends with the transmission of the data from this read-out devices to the first data buffer, which is located outside the detector about 50 to 100 m apart. It describes a device, which main task is the synchronization of these data to an external timing reference. Again, system and performance conditions urge the implementation as an integrated circuit.

- Chapter 1 gives a brief introduction to the context and the motivation for building this new high-energy physics experiments and describes the boundary conditions and the environment, the devices will have to work in.

- Chapter 2 reviews the fundamentals of semiconductors, relevant for its use as radiation detectors, and looks into the generation of signal charge, created by a traversing particle and the properties of the signal as seen by the readout amplifier. The chapter concludes with the characteristics of silicon strip detectors, significant for the design of the front-end electronics.

- Chapter 3 describes the requirements for an electronic device to deal with the signal delivered by a Silicon strip detector in terms of electrical properties of the signal itself and of the detector. In this context, we emphasize on the crucial problem of the noise performance of an amplifier to be used with semiconductor detectors.

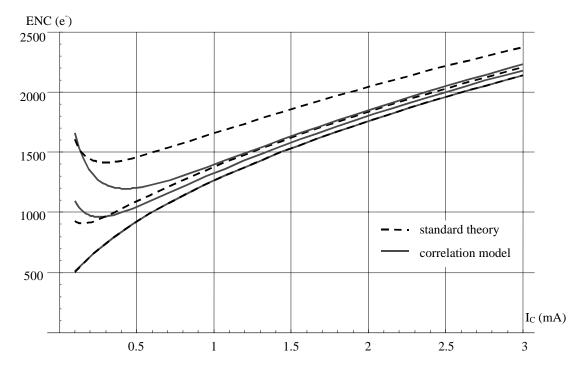

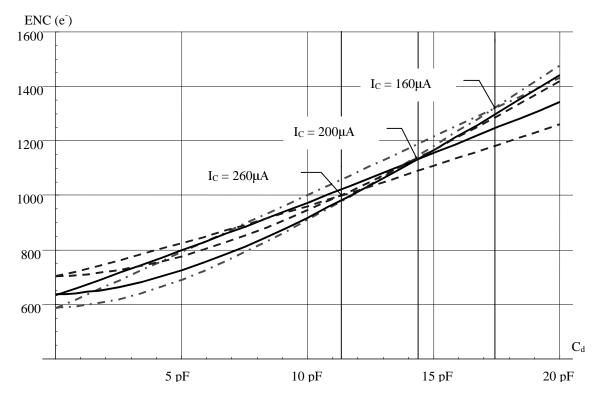

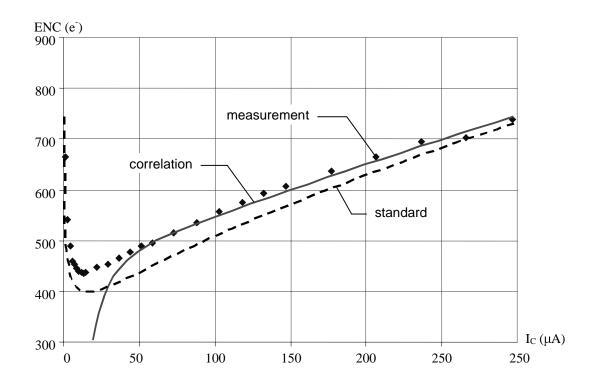

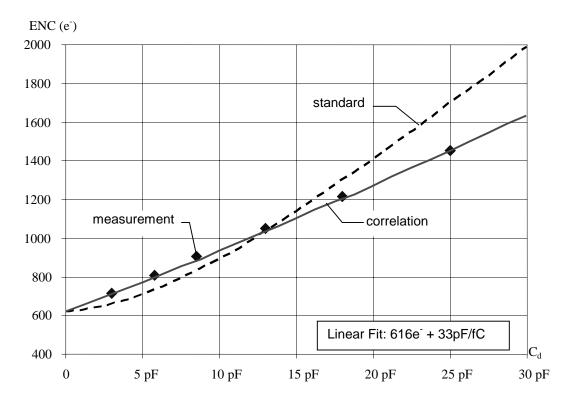

A derivation of a complete expression for the electronic noise of a charge-sensitive amplifier including noise filtering, starting from the basic noise mechanisms, is presented. In order to improve the accuracy of this model, the theory of noise correlation in bipolar junction transistors, first predicted by A. Van der Ziel in 1955 [57], is adapted. Comparisons with experimental results confirm the quality of the derived model.

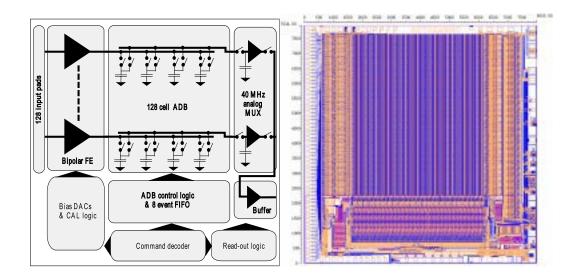

Chapter 4 deals with the requirements and the specifications for the on-detector electronics in terms of environmental and system conditions concerning the use of the device within a large experiment like ATLAS/LHC. Subsequently, a 128-channel analog readout ASIC for semiconductor detectors (SCT128A) is presented and architecture and functionality described in detail.

Results of functionality tests and performance measurements, carried out on the chip in a laboratory environment as well as using CERNs particle beam facilities, demonstrate that the SCT128A meets all specifications to be a feasible candidate for analog readout in LHC experiments. An absolute calibration of the front-end amplifier with monochromatic photons allows an accurate determination of the signal charge, released by a minimum ionizing particle (MIP) in the silicon strip detectors foreseen to be used within the ATLAS Inner Tracker.

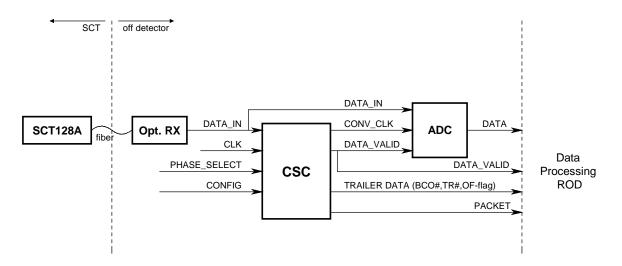

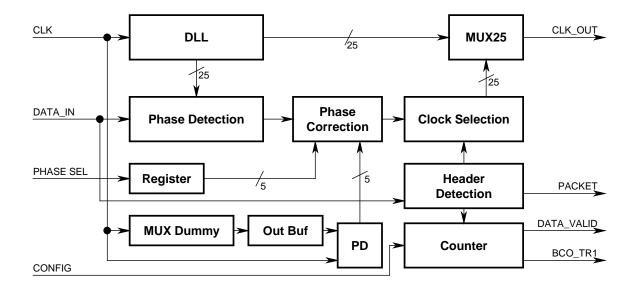

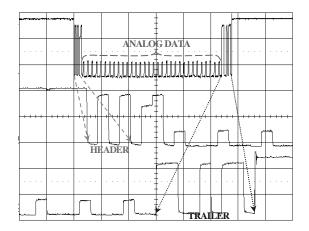

• Chapter 5 describes the conception, establishing of the specifications, and implementation of a mixed-signal data receiver/synchronizer ASIC. The main task of the device is the synchronization of the data stream, sent by the readout chips, to an external time reference and the controlling of the A/D conversion of the analog data in the stream.

The functionality requires an accurate Phase-to-Digital conversion with a resolution of 1 nano second. The demands on the nonlinearity of the converter and the jitter of the output signal (in the range of tens of pico seconds) are accordingly strict. In order to achieve the required performance independently of process variations, operating temperature and load capacitance, an auto-calibration circuit was implemented in the chip. The entire design flow from the concept to the final product is documented. Results of functionality tests and performance measurements on the prototype verify the design.

# Kurzfassung

Den Rahmen der vorliegenden Arbeit stellt die Entwicklung elektronischer Komponenten für zukünftige Hochenergiephysik-Experimente dar.

Der erste Teil beschäftigt sich mit dem Entwurf und der Realisierung einer elektronischen Einheit zur Detektion, Verarbeitung und Zwischenspeicherung von Signalen, die durch geladene Elementarteilchen in Halbleiterdetektoren hervorgerufen werden. Einsatzgebiet und Arbeitsumgebung stellen sehr rigorose Anforderungen an die Schaltung in Bezug auf Schnelligkeit, Rauschverhalten, Leistungsverbrauch, Strahlungshärte und Größe sowie bezüglich der Systemkomplexität. Diese Rahmenbedingungen erzwingen eine Realisierung als integrierte Schaltung.

Eines der Hauptprobleme, das in diesem Zusammenhang auftritt, betrifft die extrem kleinen Signale, die ein Elementarteilchen in einem Halbleiterdetektor produziert. Ein Schwerpunkt in der Entwicklung liegt daher auf der Optimierung der Schaltung in Bezug auf ihr Rauschverhalten.

Der zweite Teil der Arbeit behandelt Probleme mit der Übertragung der Daten von diesen Zwischenspeichern zum ersten Datenbuffer außerhalb des eigentlichen Experimentes. Es beschreibt eine Einheit, deren Hauptaufgabe die Synchronisierung dieser Daten zu einer externen Taktreferenz darstellt. Wiederum drängen Leistungs- und Systemanforderungen auf die Implementierung als integrierte Schaltung.

- Kapitel 1 gibt eine kurzen, einleitenden Überblick und behandelt die Beweggründe für den Aufbau neuer Hochenergiephysik-Experimente. Weiters werden die Eigenheiten und Rahmenbedingungen der Arbeitsumgebung beschrieben, die für die Entwicklung der elektronischen Komponenten maßgeblich sind.

- Kapitel 2 wiederholt die Grundlagen der Halbleiter, relevant f

ür ihren Einsatz als Teilchendetektoren. Behandelt wird die Erzeugung der Signalladung, ausgel

öst von einem, den Detektor durchquerenden Teilchen, und die Eigenschaften dieses Signals aus der Sicht des Ausleseverst

ärkers. Das Kapitel schlie

ßt mit den f

ür die Entwicklung der Auslese-Elektronik bedeutenden Eigenschaften der Silizium-Streifendetektoren.

Kapitel 3 beschreibt die Anforderungen an die Auslese-Elektronik, betreffend die elektrischen Eigenschaften des Signals und des Detektors. In diesem Zusammenhang wird auf das wichtige Problem des Rauschverhaltens eines Verstärkers für die Auslese von Halbleiterdetektoren detailiert eingegangen.

Die Ableitung eines kompletten Ausdruckes für das elektrische Rauschen eines ladungsempfindlichen Verstärkers mit Bandpaß-Filter wird dargestellt. Um die Genauigkeit dieses Modells zu verbessern, wird die Theorie der Rauschkorrelation in bipolaren Sperrschicht-Transistoren, bereits im Jahre 1955 vorausgesagt von A. Van der Ziel [52], benutzt. Vergleiche mit experimentellen Resultaten bestätigen die Qualität des berechneten Modells.

Kapitel 4 beschäftigt sich mit Anforderungen und Spezifikationen für die Auslese Elektronik in Hinblick auf ihren Einsatz innerhalb eines großen Experimentes wie ATLAS/LHC. Anschließend wird ein 128-Kanal Analog-IC für die Auslese von Halbleiterdetektoren vorgestellt und Architektur und Funktionalität im Detail beschrieben. Das Kapitel schließt mit Resultaten von Funktionalitätstests und Messungen, die an dem fertigen Chip durchgeführt wurden,.

Eine absolute Kalibrierung des Verstärkers mit monochromatischen Photonen erlaubt eine genaue Ermittlung der Signalladung, die von einem minimal ionisierenden Teilchen (MIP) in den, für den Einsatz im ATLAS Spurendetektor vorgesehenen Silizium-Streifendetektoren freigesetzt wird.

Kapitel 5 beschreibt Konzept, Spezifizierung und Implementierung eines Empfängers und Takt-Synchronisierers für gemischt analog-digitale Datenpakete. Die Hauptaufgabe der Einheit ist die Synchronisierung des Datenstromes, kommend von den Auslesesystemen, auf eine externe Zeitreferenz, und die Steuerung der Digital-Wandlung der analogen Daten.

Für die angestrebte Funktionalität wird eine hoch-genaue Phasen-Digital-Wandlung mit einer Auflösung von 1 Nanosekunde benötigt. Die Anforderungen an die Nichtlinearität des Wandlers und den Zeit-Jitter der Ausgangssignale (in der Größenordnung von einigen 10 Picosekunden) sind entsprechend hoch. Um die angestrebten Leistungsdaten unabhängig Prozeßparametervariationen, von Umgebungstemperatur Lastkapazität sicherzustellen, wurde und eine Selbstkalibrierung in den Chip integriert. Der gesamte Designfluß vom Konzept zum fertigen Prototyp ist dokumentiert. Resultate der Messungen und Tests an dem Prototyp demonstrieren die korrekte Funktion und die Einhaltung der angestrebten Spezifikationen.

# **Table Of Contents**

| INTRODUCTION                                                                 | 1         |

|------------------------------------------------------------------------------|-----------|

| SIGNALS FROM SEMICONDUCTOR PARTICLE DETECTORS                                | 5         |

| SIGNAL GENERATION IN SEMICONDUCTORS                                          | 5         |

| CHARGE COLLECTION                                                            | 9         |

| LEAKAGE CURRENT AND DETECTOR CAPACITANCE                                     | 10        |

| THE SIGNAL CURRENT AT THE ELECTRODES                                         | 11        |

| THE SILICON STRIP DETECTOR                                                   | 14        |

| PROCESSING THE SIGNALS FROM SILICON STRIP DETECTORS - THE FRONT-EN           | D17       |

| THE PREAMPLIFIER                                                             | 18        |

| FEEDBACK CONFIGURATIONS                                                      | 18        |

| NOISE SOURCES IN BIPOLAR JUNCTION TRANSISTORS                                | 20        |

| Amplifier Noise Model                                                        | 22        |

| EQUIVALENT INPUT NOISE SPECTRAL DENSITY                                      | 25        |

| EQUIVALENT NOISE CHARGE (ENC) AND THE SHAPER CIRCUIT                         | 28        |

| COMPARISON OF BIPOLAR AND MOS INPUT DEVICE                                   | 36        |

| A BICMOS FRONT-END FOR SILICON STRIP DETECTORS                               | 39        |

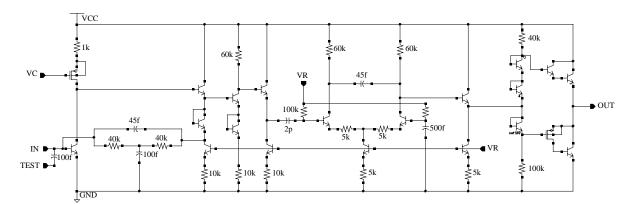

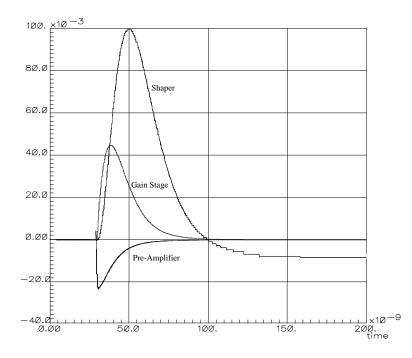

| CIRCUIT DESCRIPTION                                                          | 39        |

| THE INPUT TRANSISTOR                                                         | 41        |

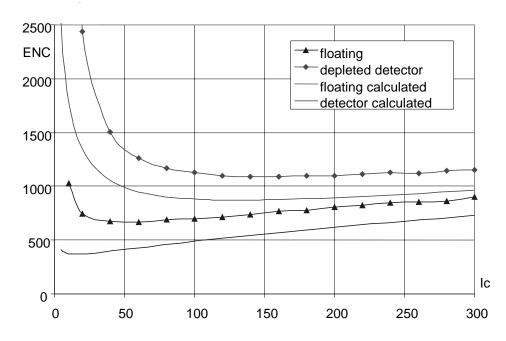

| NOISE PERFORMANCE OF THE SCT32A FRONT-END                                    | 41        |

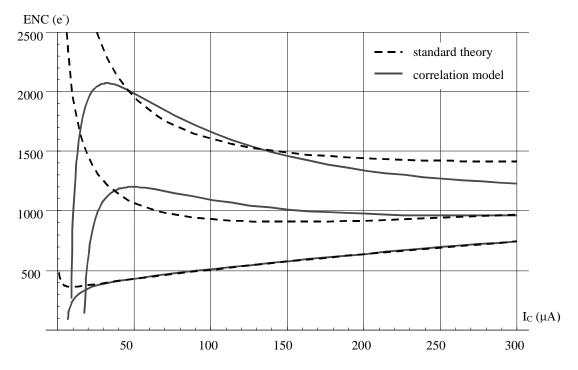

| NOISE CORRELATION IN FRONT END CIRCUITS WITH BJT INPUT DEVICE                | 43        |

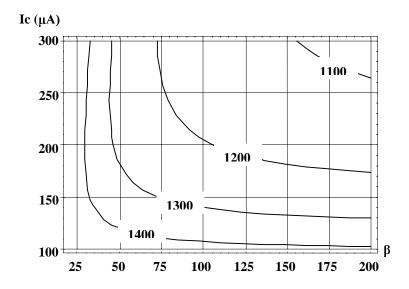

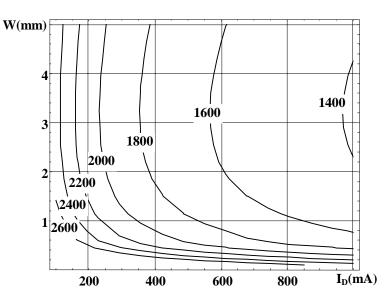

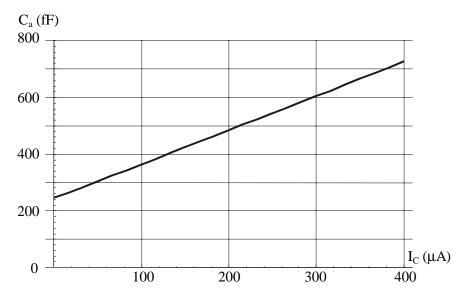

| JUNCTION CAPACITANCES AND CURRENT GAIN AS FUNCTIONS OF THE COLLECTOR CURRENT | 47        |

| ENC CONSIDERING NOISE CORRELATION AND CAPACITANCE SCALING                    | 49        |

| COMPARISON WITH EXPERIMENTAL RESULTS                                         | 51        |

| A READOUT ASIC FOR SILICON STRIP DETECTORS IN LHC EXPERIMENTS                | <u>55</u> |

| <b>READ OUT ELECTRONICS FOR LHC EXPERIMENTS - SYSTEM ASPECTS</b>             | 55        |

| BASIC READOUT ARCHITECTURES PROPOSED FOR ATLAS                               | 57        |

| THE BINARY READOUT ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                             | 57                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| THE ANALOG READOUT ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                             | 58                                                                                                                                                         |

| AN ANALOG READOUT ASIC FOR LHC: SCT128A                                                                                                                                                                                                                                                                                                                                                                     | 60                                                                                                                                                         |

| SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                              | 60                                                                                                                                                         |

| ARCHITECTURE AND BASIC PRINCIPLES                                                                                                                                                                                                                                                                                                                                                                           | 63                                                                                                                                                         |

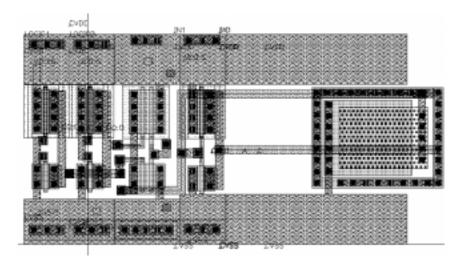

| LAYOUT                                                                                                                                                                                                                                                                                                                                                                                                      | 64                                                                                                                                                         |

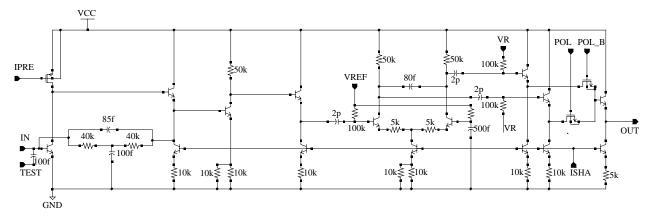

| THE SCT128A FRONT - END                                                                                                                                                                                                                                                                                                                                                                                     | 64                                                                                                                                                         |

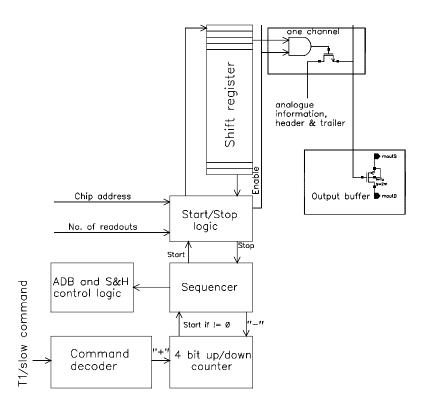

| DESCRIPTION OF THE READOUT LOGIC                                                                                                                                                                                                                                                                                                                                                                            | 65                                                                                                                                                         |

| CALIBRATION CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                         | 66                                                                                                                                                         |

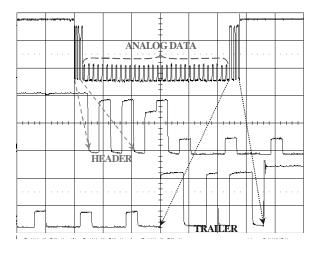

| READOUT PROTOCOL                                                                                                                                                                                                                                                                                                                                                                                            | 67                                                                                                                                                         |

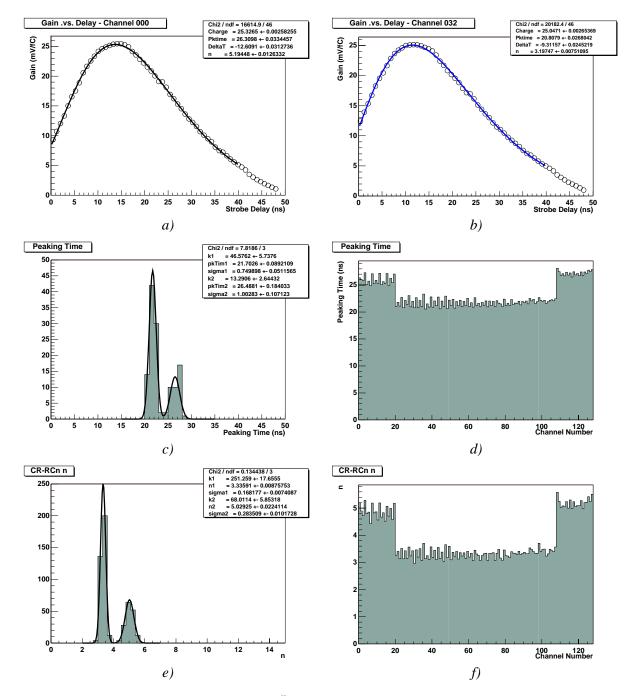

| LAB TESTS AND MEASUREMENTS ON THE SCT128A                                                                                                                                                                                                                                                                                                                                                                   | 68                                                                                                                                                         |

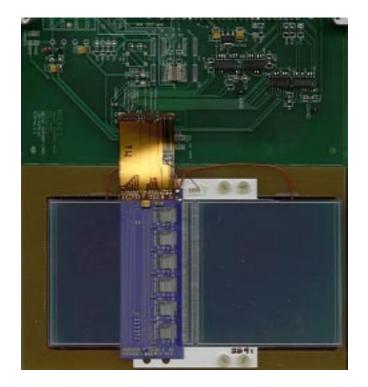

| TEST AND DATA ACQUISITION SETUP                                                                                                                                                                                                                                                                                                                                                                             | 68                                                                                                                                                         |

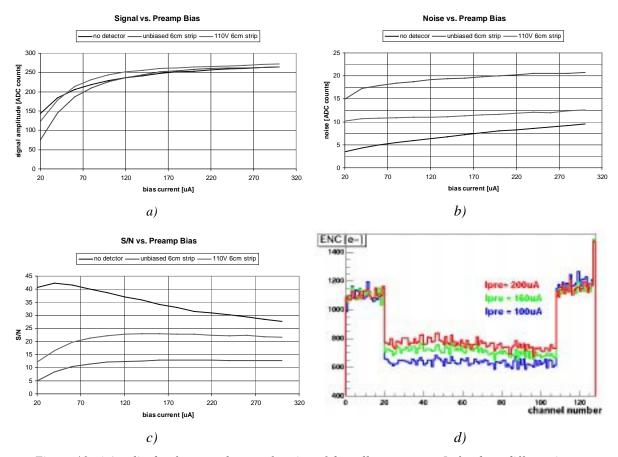

| READOUT OF SILICON DETECTORS                                                                                                                                                                                                                                                                                                                                                                                | 70                                                                                                                                                         |

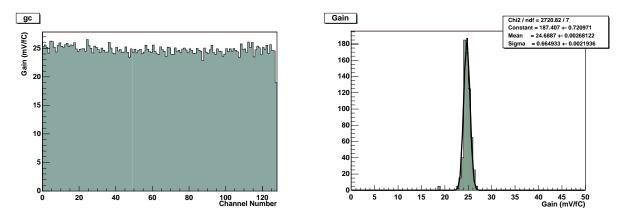

| TEST PULSE MEASUREMENTS: NOISE PERFORMANCE, GAIN AND TIMING SCANS                                                                                                                                                                                                                                                                                                                                           | 70                                                                                                                                                         |

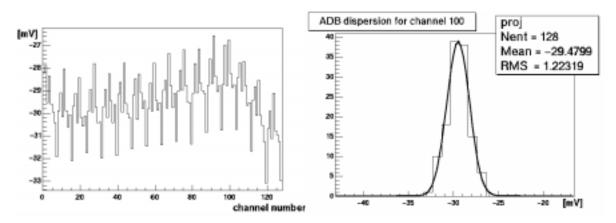

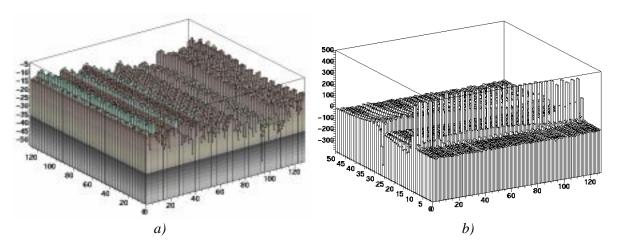

| PERFORMANCE OF THE ANALOG MEMORY (ADB)                                                                                                                                                                                                                                                                                                                                                                      | 72                                                                                                                                                         |

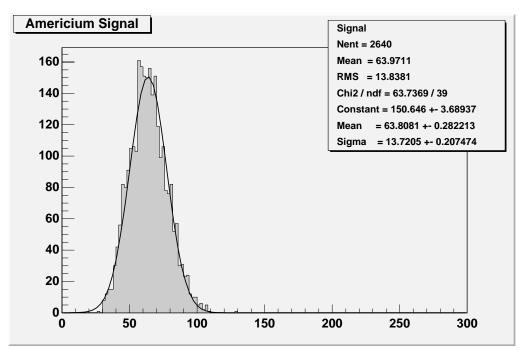

| CALIBRATION WITH GAMMAS FROM A <sup>241</sup> AMERICIUM SOURCE                                                                                                                                                                                                                                                                                                                                              | 73                                                                                                                                                         |

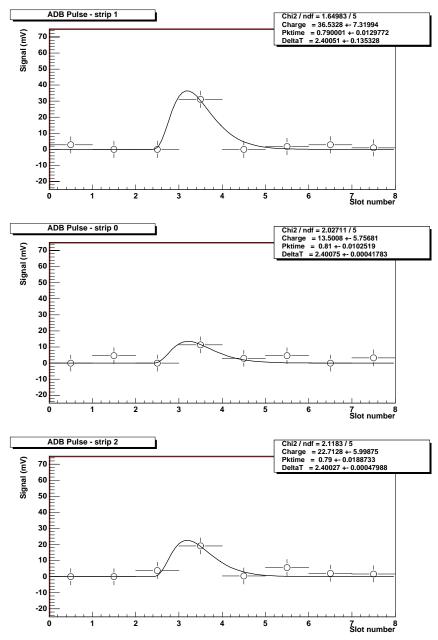

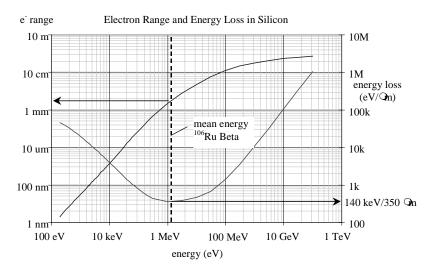

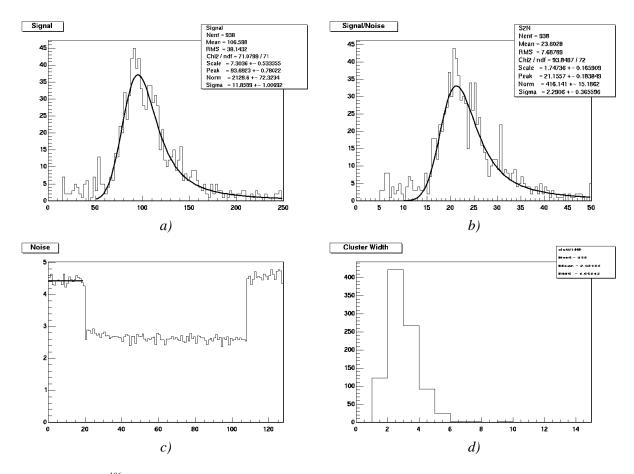

| Readout The Signals From $\beta$ - Particles In Silicon Detectors                                                                                                                                                                                                                                                                                                                                           | 77                                                                                                                                                         |

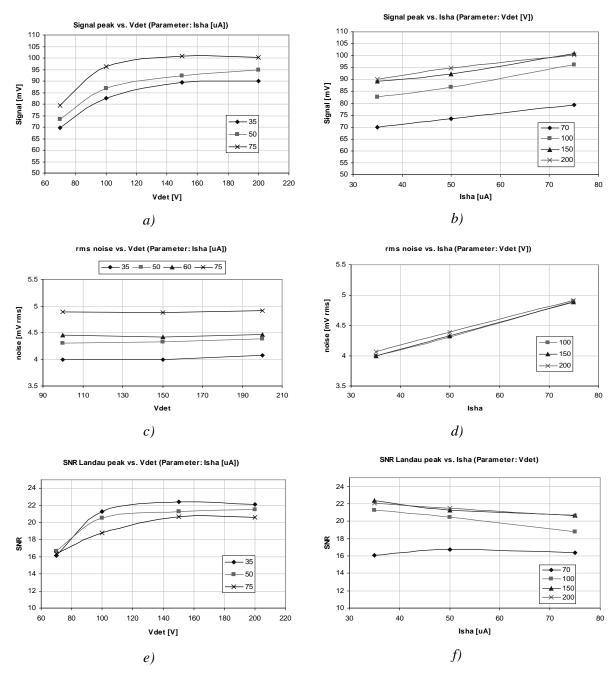

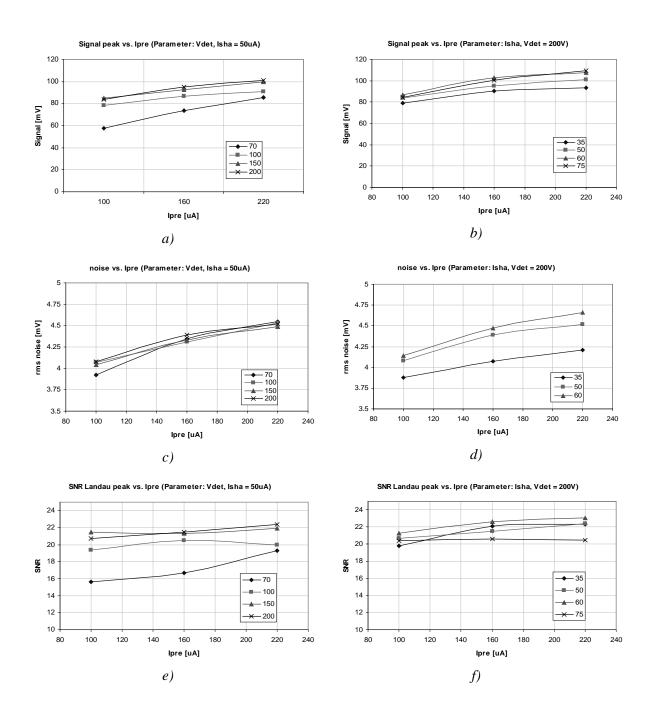

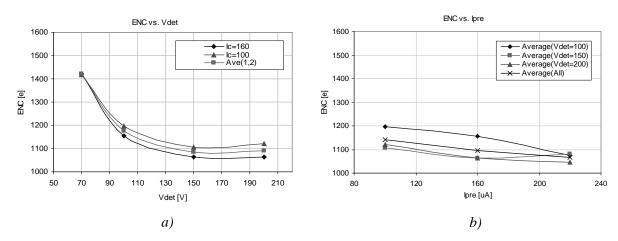

| THE SCT128A-HC PERFORMANCE AT VARYING BIAS AND DETECTOR SETTINGS                                                                                                                                                                                                                                                                                                                                            | 80                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                            |

| A/D CONVERSION FOR THE ATLAS ANALOG READOUT SCHEME                                                                                                                                                                                                                                                                                                                                                          | 84                                                                                                                                                         |

| A/D CONVERSION FOR THE ATLAS ANALOG READOUT SCHEME<br>Requirements And Specifications For A Mixed Signal Data Receiver/Clock                                                                                                                                                                                                                                                                                | 84                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                             | <u>84</u><br>84                                                                                                                                            |

| REQUIREMENTS AND SPECIFICATIONS FOR A MIXED SIGNAL DATA RECEIVER/CLOCK                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                            |

| REQUIREMENTS AND SPECIFICATIONS FOR A MIXED SIGNAL DATA RECEIVER/CLOCK<br>Synchronizer                                                                                                                                                                                                                                                                                                                      | 84                                                                                                                                                         |

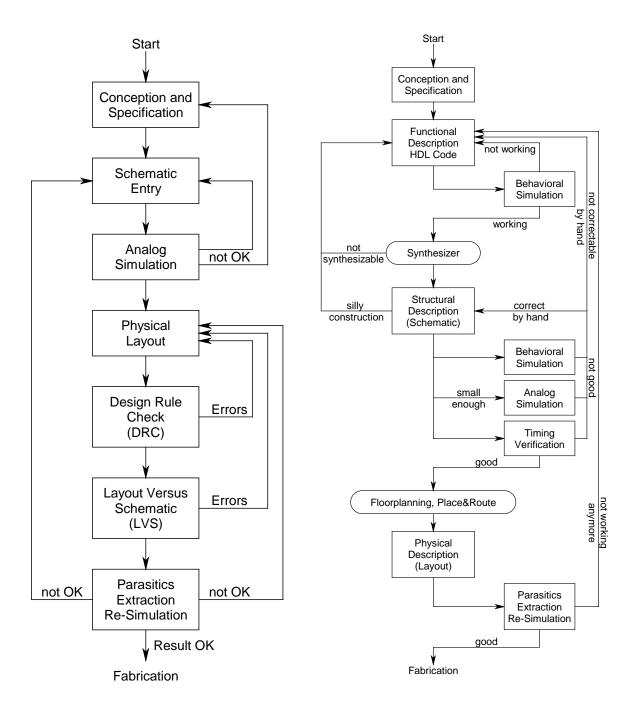

| REQUIREMENTS AND SPECIFICATIONS FOR A MIXED SIGNAL DATA RECEIVER/CLOCK<br>Synchronizer<br>VLSI Design Methods                                                                                                                                                                                                                                                                                               | 84<br>87                                                                                                                                                   |

| REQUIREMENTS AND SPECIFICATIONS FOR A MIXED SIGNAL DATA RECEIVER/CLOCK<br>Synchronizer<br>VLSI Design Methods<br>Full Custom Design                                                                                                                                                                                                                                                                         | <b>84</b><br><b>87</b><br>87                                                                                                                               |

| REQUIREMENTS AND SPECIFICATIONS FOR A MIXED SIGNAL DATA RECEIVER/CLOCK<br>Synchronizer<br>VLSI Design Methods<br>Full Custom Design<br>Semi Custom Design                                                                                                                                                                                                                                                   | <b>84</b><br><b>87</b><br>87<br>87                                                                                                                         |

| REQUIREMENTS AND SPECIFICATIONS FOR A MIXED SIGNAL DATA RECEIVER/CLOCK<br>SYNCHRONIZER<br>VLSI DESIGN METHODS<br>FULL CUSTOM DESIGN<br>SEMI CUSTOM DESIGN<br>HIGH LEVEL DESIGN AND SYNTHESIS                                                                                                                                                                                                                | <b>84</b><br><b>87</b><br>87<br>87<br>87<br>88                                                                                                             |

| REQUIREMENTS AND SPECIFICATIONS FOR A MIXED SIGNAL DATA RECEIVER/CLOCK<br>SYNCHRONIZER<br>VLSI DESIGN METHODS<br>FULL CUSTOM DESIGN<br>SEMI CUSTOM DESIGN<br>HIGH LEVEL DESIGN AND SYNTHESIS<br>CSC ARCHITECTURE                                                                                                                                                                                            | <b>84</b><br><b>87</b><br>87<br>87<br>88<br><b>90</b>                                                                                                      |

| REQUIREMENTS AND SPECIFICATIONS FOR A MIXED SIGNAL DATA RECEIVER/CLOCK         SYNCHRONIZER         VLSI DESIGN METHODS         FULL CUSTOM DESIGN         SEMI CUSTOM DESIGN         HIGH LEVEL DESIGN AND SYNTHESIS         CSC ARCHITECTURE         THE BUILDING BLOCKS                                                                                                                                  | <ul> <li>84</li> <li>87</li> <li>87</li> <li>87</li> <li>88</li> <li>90</li> <li>91</li> </ul>                                                             |

| REQUIREMENTS AND SPECIFICATIONS FOR A MIXED SIGNAL DATA RECEIVER/CLOCKSYNCHRONIZERVLSI DESIGN METHODSFULL CUSTOM DESIGNSEMI CUSTOM DESIGNMIGH LEVEL DESIGN AND SYNTHESISCSC ARCHITECTURETHE BUILDING BLOCKSPHASE DETECTION (PHASE-TO-DIGITAL CONVERTER)                                                                                                                                                     | <ul> <li>84</li> <li>87</li> <li>87</li> <li>87</li> <li>88</li> <li>90</li> <li>91</li> </ul>                                                             |

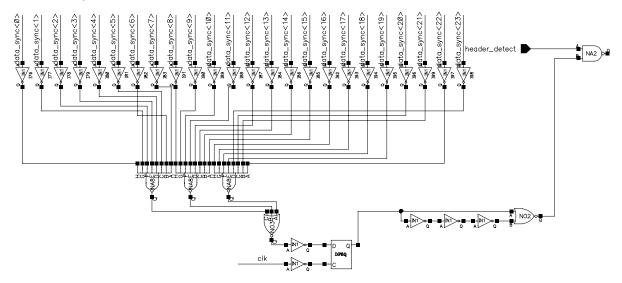

| REQUIREMENTS AND SPECIFICATIONS FOR A MIXED SIGNAL DATA RECEIVER/CLOCKSYNCHRONIZERVLSI DESIGN METHODSFULL CUSTOM DESIGNSEMI CUSTOM DESIGNSEMI CUSTOM DESIGNHIGH LEVEL DESIGN AND SYNTHESISCSC ARCHITECTURETHE BUILDING BLOCKSPHASE DETECTION (PHASE-TO-DIGITAL CONVERTER)HEADER IDENTIFICATION                                                                                                              | <ul> <li>84</li> <li>87</li> <li>87</li> <li>88</li> <li>90</li> <li>91</li> <li>91</li> </ul>                                                             |

| Requirements And Specifications For A Mixed Signal Data Receiver/ClockSynchronizerVLSI Design MethodsFull Custom DesignSemi Custom DesignHigh Level Design And SynthesisCSC ArchitectureThe Building BlocksPhase Detection (Phase-to-Digital Converter)Header IdentificationGeneration Of Control Signals                                                                                                   | <ul> <li>84</li> <li>87</li> <li>87</li> <li>87</li> <li>88</li> <li>90</li> <li>91</li> <li>91</li> <li>91</li> <li>92</li> </ul>                         |

| Requirements And Specifications For A Mixed Signal Data Receiver/ClockSynchronizerVLSI Design MethodsFull Custom DesignSemi Custom DesignHigh Level Design And SynthesisCSC ArchitectureThe Building BlocksPhase Detection (Phase-to-Digital Converter)Header IdentificationGeneration Of Control SignalsThe Timing Reference: Delay Locked Loop (DLL)                                                      | <ul> <li>84</li> <li>87</li> <li>87</li> <li>87</li> <li>88</li> <li>90</li> <li>91</li> <li>91</li> <li>91</li> <li>92</li> <li>93</li> </ul>             |

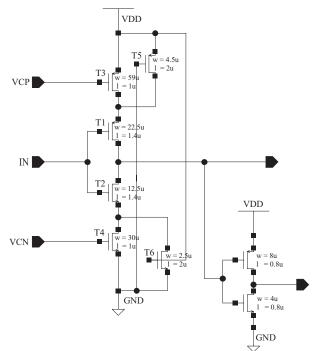

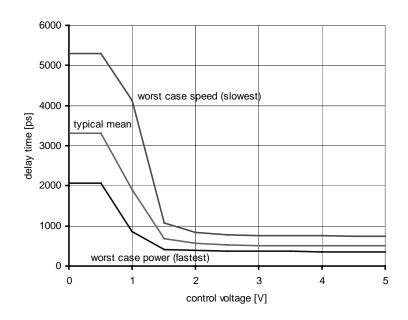

| Requirements And Specifications For A Mixed Signal Data Receiver/ClockSynchronizerVLSI Design MethodsFull Custom DesignSemi Custom DesignHigh Level Design And SynthesisCSC ArchitectureThe Building BlocksPhase Detection (Phase-to-Digital Converter)Header IdentificationGeneration Of Control SignalsThe Timing Reference: Delay Locked Loop (DLL)Delay Line Architecture                               | <ul> <li>84</li> <li>87</li> <li>87</li> <li>88</li> <li>90</li> <li>91</li> <li>91</li> <li>91</li> <li>92</li> <li>93</li> <li>94</li> </ul>             |

| Requirements And Specifications For A Mixed Signal Data Receiver/ClockSynchronizerVLSI Design MethodsFull Custom DesignSemi Custom DesignHigh Level Design And SynthesisCSC ArchitectureThe Building BlocksPhase Detection (Phase-to-Digital Converter)Header IdentificationGeneration Of Control SignalsThe Timing Reference: Delay Locked Loop (DLL)Delay Line architecturePhase Detector and charge pump | <ul> <li>84</li> <li>87</li> <li>87</li> <li>88</li> <li>90</li> <li>91</li> <li>91</li> <li>91</li> <li>92</li> <li>93</li> <li>94</li> <li>95</li> </ul> |

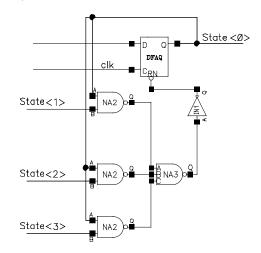

| AUTO RESET OF THE STATE MACHINE                                 | 99  |

|-----------------------------------------------------------------|-----|

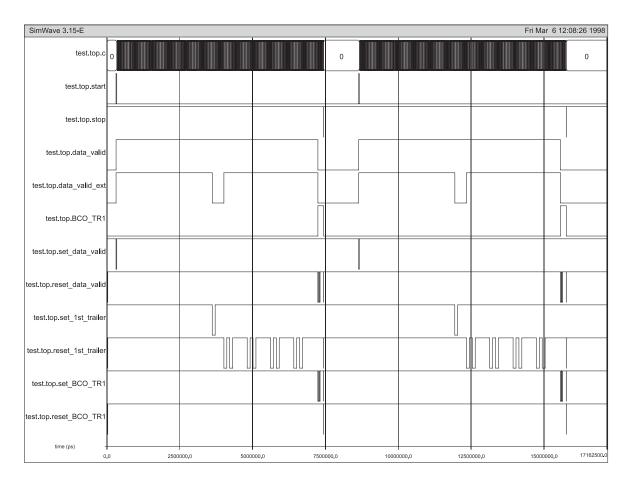

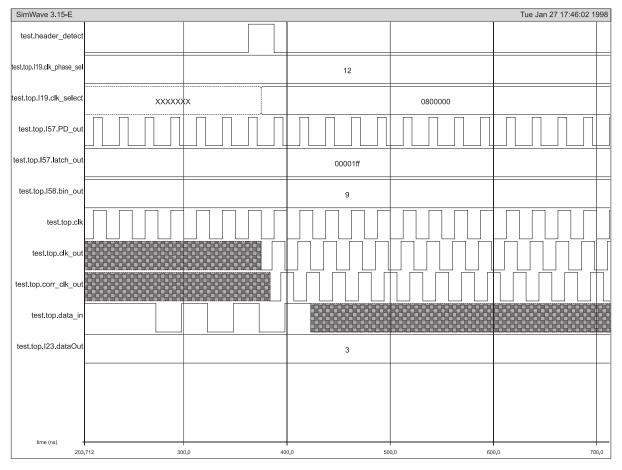

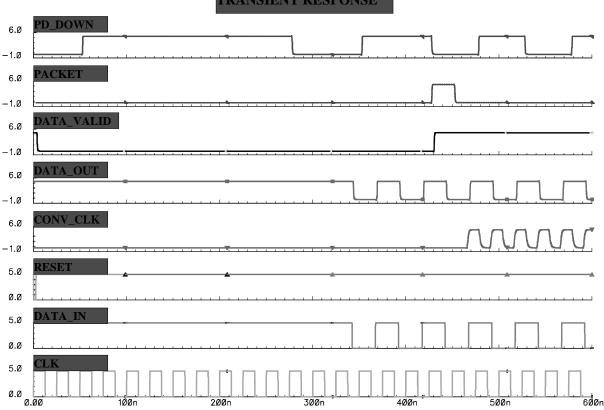

| SYSTEM SIMULATION                                               | 100 |

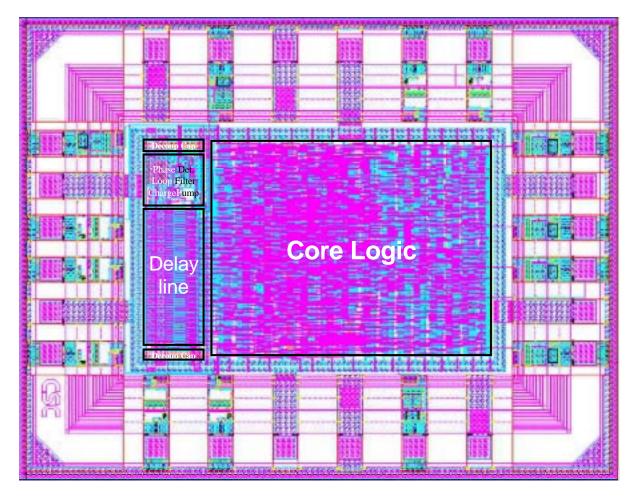

| LAYOUT                                                          | 102 |

| TESTING AND MEASUREMENT RESULTS                                 | 103 |

| FUNCTIONALITY                                                   | 103 |

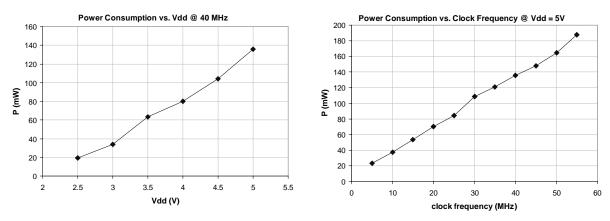

| POWER CONSUMPTION, POWER SUPPLY RANGE AND CLOCK FREQUENCY RANGE | 104 |

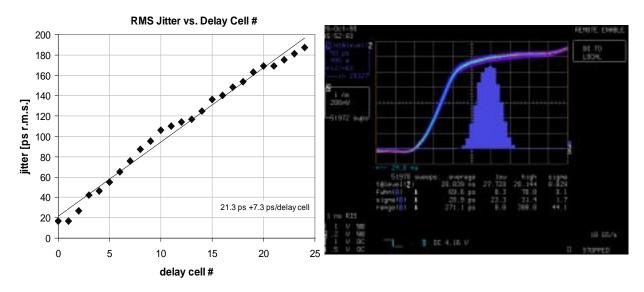

| CLOCK JITTER AND PHASE-TO-DIGITAL CONVERTER PERFORMANCE         | 104 |

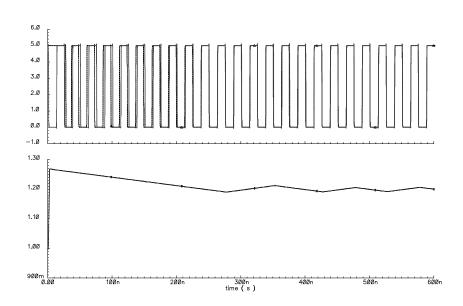

| BEHAVIOR OF THE AUTO CALIBRATION LOOP                           | 106 |

| SUGGESTIONS FOR THE REDESIGN                                    | 107 |

| IMPROVED HEADER DETECTION                                       | 107 |

| ADDITIONAL FUNCTIONALITY                                        | 107 |

| REFERENCES                                                      | I   |

| LIST OF FIGURES                                                 | V   |

| LIST OF TABLES                                                  | VII |

# Chapter 1

## Introduction

The origin of mass is one of the most fundamental topics in modern physics. In the Standard Model (SM), which is the theoretical foundation of high energy physics (HEP), elementary particles acquire their mass through spontaneous symmetry breaking. This process is known as the Higgs-mechanism and gives rise to the existence of a new massive particle, the Higgs boson, which has not yet been observed experimentally. Although the SM does not predict the mass of the Higgs boson, theoretical arguments indicate that either one or more Higgs bosons with a mass below about 1TeV should exist, or that a more complex scenario of new physics will be found at the TeV energy scale.

In current HEP experiments, sub atomic particles are accelerated to energies of hundreds of billions of electronvolts (>100 GeV), corresponding to velocities very close to the speed of light, and than brought to collision either with each other or with fixed targets. When such a collision takes place, a part of the particle's kinetic energy may convert into mass according to the Einstein relation, creating numerous particles of mostly very short lifetime. CERN, the European Center for Nuclear Research, houses the world's largest particle accelerator complex. LEP, the biggest machine at CERN at present, is a 27 km circular electron-positron collider that reaches a center-of-mass collision energy of 200 GeV. This value constitutes probably an upper limit for circular electron storage rings of that size due to synchrotron radiation energy loss from the circulating beams. Since the radiation losses decrease with the fourth power of the mass of the particles<sup>1</sup>, one possible solution to overcome this limitation and push the collision energy into the TeV range, is to accelerate particles with higher rest mass, like hadrons. A proton - proton collider offers a feasible possibility of exploring this energy range in the nearer future.

In order to gain new experimental insight and to test and enlarge our understanding of elementary particle physics at the TeV scale, CERN approved in 1994 the proposed Large Hadron Collider (LHC). Scheduled to be operational by the year 2005, this new machine is a proton - proton collider with a projected center - of - mass collision energy of 14 TeV. The collisions between the bunches of

<sup>&</sup>lt;sup>1</sup> Emitted SR power *P* per turn for a given radius *R*:  $P = (4\pi E_0 r_e I/3eR)(E/E_0)^4$ , with energy of the particle *E*, rest energy  $E_0$ , electron radius  $r_e$ , electron current *I*.

protons will recreate the state of the very early universe just  $10^{-12}$  seconds after the "Big Bang", the beginning of space and time, when the temperature was  $10^{16}$  degrees.

The energy available for acceleration of the particles is mainly limited by the strength of the bending magnets. With the radius being fixed by the LEP tunnel, LHC needs a bending field of 8.36T, delivered by 1232 superconducting dipole magnets operating at 1.9 K. In addition to p-p operation, the LHC will be able to collide heavy nuclei (Pb-Pb) produced in the existing CERN accelerator complex, resulting in an energy of 1150 TeV in the center of mass.

The accelerating RF system consists of eight single-cell cavities per beam. Each cavity is driven by a separate 400 MHz klystron rated at 300 kW. The maximum operating voltage is 2 MV per cavity, thus leading to an overall RF voltage of 16 MV during the ramping up phase. The energy gain equals to 485 keV per turn, the stored beam energy will be 334 MJ. The wavelength corresponding to a RF frequency of 400 MHz is 0.75 m or 2.5 ns. Every tenth RF bucket will be filled obtaining bunches separated by 25 ns. This value of the bunch separation is well suited for the experiments and at the same time gives the optimum overall performance of the machine for two high-luminosity experiments taking data at the same time.

Four different experiments are currently planned for LHC. Two of them, ATLAS and CMS, are general purpose proton-proton experiments and are designed to exploit the full LHC physics potential. The other two experiments, LHC-B and ALICE, are dedicated to B-physics and to heavy ion (Pb-Pb) physics, respectively.

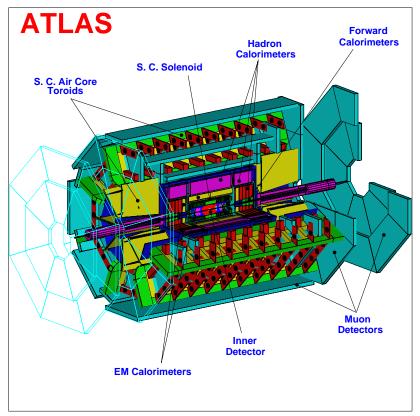

Figure 1. Cut view of the ATLAS detector

ATLAS, <u>A</u> <u>T</u>oroidal <u>L</u>HC <u>ApparatuS</u>, is one of the two general-purpose proton-proton collider experiments foreseen for LHC. A design description is presented in the ATLAS Technical Proposal [1]. The detector geometry follows the common tracker-calorimeter-muon chamber configuration. A three-dimensional view of the ATLAS detector installed in the underground hall is shown in Figure 1. With an overall length of 42 m (including the third layer of the forward muon chambers mounted on the cavern wall), a diameter of 22 m and a weight of 7000 tons, the ATLAS detector is enormous even if compared to the largest of today's high energy physics collider experiments.

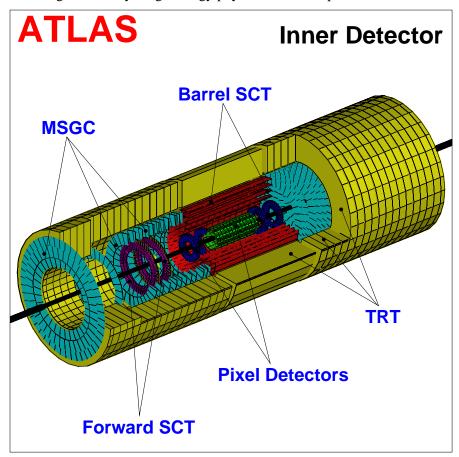

Figure 2. ATLAS inner detector

The purpose of the Inner Detector is to track the particle from the collision point to the electromagnetic calorimeter. Pattern recognition, momentum and vertex measurements, and enhanced electron identification are achieved with a combination of discrete high-resolution pixel and strip detectors (Semiconductor Tracker, SCT) in the inner part and continuous straw-tube tracking detectors with transition radiation capability (Transition Radiation Tracker, TRT) in the outer part of the tracking volume. The Inner Detector is housed in a 6.8 m long cavity of radius 1.15 m within the barrel cryostat of the electromagnetic calorimeter, which contains also the superconducting solenoid providing the axial 2 T field for the tracking. The large track density expected at LHC and the momentum and spatial resolution targets require the use of precision tracking layers with a fine

granularity. However, the number of such layers is constrained by the tolerable amount of material, and their granularity is limited by the power consumption and by the high cost of the readout electronics.

Depending on the required radiation hardness, which is determined primarily by the distance from the beam pipe, different detector technologies are used, namely silicon pixel detectors at the lowest radii and in the forward direction, where highest radiation hardness is required, and silicon strip detectors above a radius of 30 cm. The barrel SCT consists of two silicon pixel detector layers at radii of 11.5 cm and 16.5 cm, complemented by eight pixel disks for the forward direction and of four silicon strip detector layers at radii of about 30 cm, 40 cm, 50 cm, and 60 cm. Since material in the inner detector degrades the momentum, the amount of material is another important performance criteria.

The LHC bunch crossing frequency of 40 MHz, combined with the large number of  $10^8$  electronics channels in the ATLAS detector, results in a very large data rate: All subdetectors together produce data at a rate of ~ 50 – 100 TB/s, which are written into the detector's front-end pipeline memories. This data rate must be reduced to about 10 MB/s to 100 MB/s before being recorded for the subsequent offline analysis. This challenging task will be taken on by the three-level trigger architecture. The level-1 (L1) trigger accepts data from the calorimeter and the muon trigger chambers at the full LHC bunch-crossing rate (BCO) of 40 MHz. During the L1 latency (i.e. the time required to collect and process the data, and to distribute the trigger decision) of 2.5  $\mu$ s, the data from all subdetectors are stored in the pipeline memories. Upon reception of a positive L1 trigger decision, which occurs at a maximum rate of 100 kHz, the full event data are transferred from the pipeline memories to the L2 buffers, which corresponds to a data rate of about 130 GB/s.

The work described in this document deals with the design and evaluation of an electronic device for reading, processing and storing the signals, provoked by the traversing particles in the strip detectors of the SCT. This device has to work within the above described environment, which imposes very rigorous requirements in terms of data processing speed, noise performance, power dissipation, radiation hardness and size as well as in terms of system complexity (Chapter 4). An emphasis is put on the major problem, which occurs when dealing with extremely small signals, like the ones produced by a semiconductor detector (Chapter 2). This problem concerns the low-noise operation of the front-end amplification (Chapter 3). The last section deals with the transmission of the data from this read-out devices to the first data buffer outside the detector. It describes a device that takes care of the synchronization of these data to an external timing reference (Chapter 5). Test and measurement results are presented in order to demonstrate the functionality and performance of both devices.

# Chapter 2

## **Signals From Semiconductor Particle Detectors**

The nature and properties of semiconducting materials, as silicon, germanium, gallium-arsenide or diamond, allow them to being used as active components in particle detectors.

As described in the previous chapter, the ATLAS Semiconductor Tracker SCT will use silicon strip and pixel detectors in the barrels as well as in the forward regions. This section discusses the generation of signal charge by a traversing particle and the properties of the signal as seen by the readout amplifier. The characteristics of silicon strip detectors, significant for the design of the frontend electronics, will be reviewed

## **Signal Generation In Semiconductors**

As an energetic particle traverses through a semiconductor, it continuously looses fractions of its kinetic energy via several kinds of interactions. The predominant type is the electromagnetic interaction with the electrons of the lattice atoms. As a result, electrons are excited and raised from the valence band to the conduction band, ionizing the lattice atoms and creating excess charge concentration. These additional charge carriers can be detected under certain circumstances.

The mean energy loss dE of a moderately relativistic particle over a path length dx can be calculated according to the Bethe-Bloch formula

$$-\frac{dE}{dx} = k \cdot z^2 \frac{Z}{A} \frac{1}{\beta^2} \left[ \frac{1}{2} \ln \left( \frac{2 \cdot m_e \cdot v^2 \cdot \gamma^2}{I^2} \varepsilon_{\max} \right) - \beta^2 - \frac{\delta}{2} \right]$$

(2.1)

using the following symbols:

$\beta$  relative speed

v velocity of the incident particle

c light speed in vacuum

$$\gamma \qquad = \sqrt{\frac{1}{1 - \beta^2}}$$

- *k* parameter, proportional to the properties of the target material

- m<sub>e</sub> electron rest mass

$\mathcal{E}_{\text{max}}$  maximum transferable energy, proportional to the mass of the incident particle

- *I* excitation potential per atomic electron

- Z atomic number of target material

- *A* atomic mass of target material

- *z* charge of incident particle

- $\delta$  density effect correction

The parameter k calculates to  $4\pi \cdot N_A r_e^2 m_e c^2 = 0.307 MeV g^{-1} cm^2$  with  $r_e$  being the classical electron radius<sup>1</sup>, the maximum transferable energy is determined using the relation

$$\varepsilon_{\rm max} = \frac{2m_e c^2 \beta^2 \gamma^2}{1 + 2\gamma m_e / M + (m_e / M)^2}$$

(2.2)

with M being the mass of the incident particle. The relative speed is the velocity of the incident particle divided by the speed of light in vacuum ( $\beta = v/c$ ). The parameter  $\delta$  corrects for the density effect: The electric field of the incoming particle modifies the field present in the semiconductor. This results in a weakening of the oncoming interactions, hence reducing the transferred energy. The density effect becomes especially important for ultra relativistic particles. A general expression for  $\delta$  as a function of the particle momentum has been given in [54].

<sup>&</sup>lt;sup>1</sup>  $r_e = (2.817940 \cdot 10^{-10} \text{ m}).$

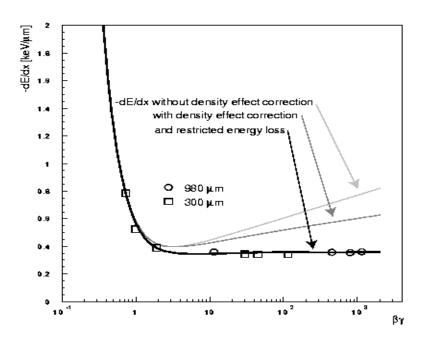

Figure 3. Mean energy deposition in silicon as a function of particle energy. The density effect correction and the restriction of the energy loss to 0.5 MeV become important at high energies. The circular data were taken with a 980  $\mu$ m thick detector and are reported in [31], the rectangular are calculated from measurements of the most probable energy with a 300  $\mu$ m thick detector[9].

dE/dx initially falls with  $1/\beta^2$ , then reaches a broad minimum at  $\gamma = 3.2$  almost independently of the material. Particles with energy losses close to this minimum are called minimum ionizing particles (MIPs). The number of created, electron-hole pairs equals to the deposited energy divided by the ionizing energy of the material. This charge concentration in excess of the equilibrium  $(n \cdot p > n_i^2)$  represents the detectable signal. It returns to thermal equilibrium through recombination of the charge carrier pairs with a time constant equal to the minority carrier lifetime.

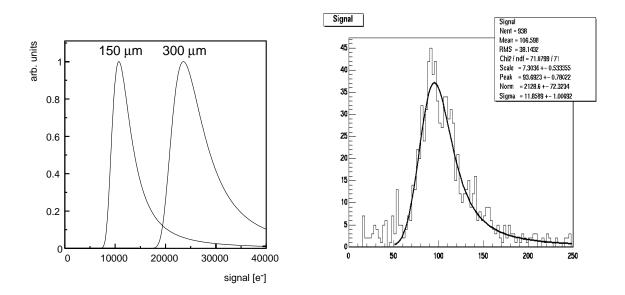

The mean energy deposition according to (2.1) is equivalent to the most probable energy deposition for relatively thick layers of absorber material where the number of collisions is large. Here the energy loss is *Gaussian* distributed. This follows directly from the *Central Limit Theorem* for a large number of statistically distributed events. In the case of thin<sup>2</sup> layers, the probability of interactions with high energy-transfer is highly reduced. Consequently, the most probable energy deposition is smaller than the mean deposition and the distribution function shows a long tail towards higher energies due to these rare events. *Landau* [36] established a theory for the energy deposition in thin layers, hence the energy loss of this type is designated as being *Landau*-distributed. All semiconductor detectors relevant for this work can be classified 'thin'.

$<sup>^{2}</sup>$  A layer of a thickness for which the mean energy loss is small (less than 1%) compared to the maximum energy loss allowable in a single collision are considered as 'thin' in this context [36].

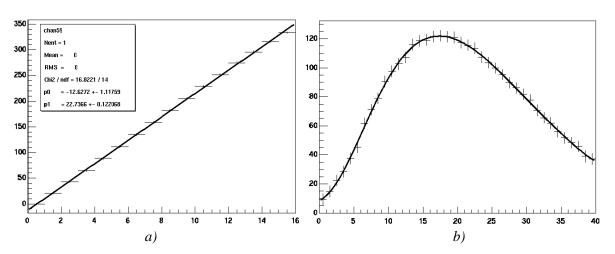

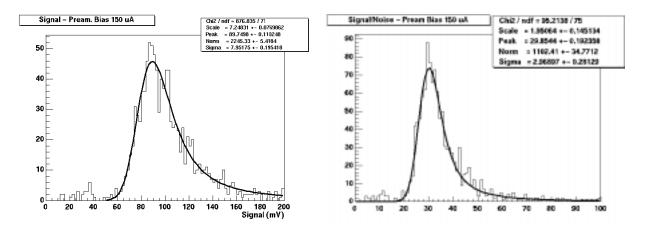

Figure 4. Landau distribution, approximated with equation (2.7) for a 300  $\mu$ m and a 150  $\mu$ m thick silicon detector, and measured for a 300  $\mu$ m silicon strip detector and <sup>109</sup>Ru beta particles. A convolution of a Landau and a Gauss distribution is used as the fit function rather than a pure Landau due to the imperfections of the measurement process like for example the electronics noise of the readout amplifier. The vertical scale is the number of events for the given energy, the horizontal scale is in mV for an amplifier of a gain of about 25mV/fC.

The number of created charge carrier pairs can be calculated in a straightforward way from the deposited energy as the predominant interaction is the ionization of the atom resulting in the creation of an electron-hole pair. The *Landau*-distribution can be approximated by the following normalized distribution of the number of created carrier pairs:

$$\phi(\lambda) = \frac{1}{2\pi i} \int_{-i\infty}^{i\infty} \exp(\lambda s + s \cdot \ln s) ds$$

(2.3)

The parameter  $\lambda$  takes the most probable charge generation  $q_{mp}$  and the *FWHM*<sup>3</sup> of the experimentally measured distribution into account and has the following relation with the generated charge *q*:

$$\lambda = \frac{q - q_{mp}}{FWHM} \tag{2.4}$$

Figure 4 shows the *Landau* distribution derived according to the equations above using experimental data from [30] for  $q_{mp}$  and *FWHM* for 150 µm and 300 µm thick silicon.

<sup>&</sup>lt;sup>3</sup> Full-Width-Half-Maximum (FWHM) denotes the full width of the distribution function at 50% of the peak value.

## **Charge Collection**

In order to use semiconductor material as particle detectors, the excess charge created by the traversing particle has to be collected and measured. This charge collection can be done by applying an electrical field via electrodes across the bulk of the semiconductor. The electron-hole pairs will separate and start drifting towards their respective electrodes, thereby exciting mirror charges at the electrodes, which can be detected and measured. Applying an appropriate field across the semiconductor does not raise a problem in case of high-band gap material like diamond or for usual semiconductors (Si, GaAs) at cryogenic temperatures where practically no free charge carriers are available. Operating semiconductors like silicon at room temperature in this configuration requires the removal of nearly all free charge carriers from the bulk by other means in order to prevent the flow of a substantial DC current. The necessity for this precaution can be illustrated by the following consideration: A 1 cm<sup>2</sup> large and 300  $\mu$ m thick silicon detector made of pure intrinsic silicon contains in total about  $4.4 \cdot 10^8$  free electron-hole pairs. This number is further increased by the unavoidable presence of impurities in the crystal lattice. A traversing MIP looses an average of 116 keV of its energy in such a detector. Together with an ionization energy of 3.62 eV per carrier pair in silicon, this results in a total detectable signal of 32000 electron-hole pairs. The most probable energy loss corresponds to ~24000 electron hole pairs. This, in comparison with the total amount of free charge carriers, very small signal would sink into insignificance besides the fluctuation of the current through the detector. One possible and feasible method of removing the free charge carriers from the silicon bulk is, to use doped silicon in a reverse biased pn-junction-diode configuration. The junction of a reverse biased diode allows applying an electric field for the charge collection and creates a blocking barrier against the flow of majority carriers. Carrier diffusion establishes a region around the junction, which becomes depleted of free charge carriers. The depth of this so-called space charge region increases with the reverse bias voltage. For detector applications, it is desirable to extend the depletion region over the entire device depth, thus increasing the sensitive volume for radiation detection. Moreover, the higher electrical field across the bulk also provides a more efficient charge collection due to increase of the drift velocity. The maximum voltage, which can be applied, is given by the breakdown point of the junction.

## Leakage Current And Detector Capacitance

The DC current flowing through a reversed biased pn-junction, called diode leakage current, is a sum of several effects, among which the most important are thermal generation of minority carriers in the depletion region, diffusion of minority carriers from the neutral region and surface effects. For planar silicon pn-junctions, the surface leakage current is generally much smaller than the generation current in the depletion region. A simplified expression for the generation current density can be obtained [55]

$$J_{gen} = \frac{qn_iW}{\tau_e}$$

(2.5)

where W is the depletion-layer width and  $\tau_e$  the effective carrier lifetime. At a given temperature, the current density is proportional to the depletion-layer width, which is itself dependent on the applied reverse bias. The diffusion current for a fully depleted silicon detector is negligible. The leakage current through a semiconductor detector constitutes a significant source of noise for the readout electronics. Therefore, the mastering of the leakage current is one of the major issues in detector design.

Another source of noise is the effect of the capacitance of the detector seen by the input amplifier of the readout electronics. The equation for the capacitance of a reverse biased planar pn-junction is equivalent to the equation for the capacitance of a parallel plate capacitor, where the distance is replaced by the depth of the depletion layer [36]:

$$C_{\rm det} = \varepsilon \varepsilon_0 \frac{A}{d} \tag{2.6}$$

This expression, however, is only accurate for capacitors where the depletion depth is much smaller then the lateral extension of the implant. For highly segmented detectors like that will be described in the following section, also the capacitance between two adjacent implants has to be taken into account. Depending on the layout the contribution of this capacitance can even become dominant.

## The Signal Current At The Electrodes

The drifting charge carriers in the detector bulk induce image charges at the electrodes [25]. The resulting signal current is a function of the motion of the charge carriers from their point of generation to the respective electrode. The resulting current is the sum of two components, originating from the motion of the two charge carrier types, electrons and holes, respectively. For a planar junction and assuming constant carrier mobility and constant charge generation per unit length, the total current can be denoted as [53]:

$$i(t) = Q_{gen} \cdot \frac{v_n}{2} \left[ \left( 1 + \frac{V_{od}}{E_{\max} \cdot d} \right) \cdot \exp\left(\frac{-v_n t}{d}\right) - \frac{V_{od}^2}{E^2_{\max} \cdot d^2} \cdot \exp\left(\frac{v_n t}{d}\right) \right] \cdot \sigma(t_{n\max}) + Q_{gen} \cdot \frac{v_p}{2} \left[ \left( 1 + \frac{V_{od}}{E_{\max} \cdot d} \right) \cdot \exp\left(\frac{-v_p t}{d}\right) - \frac{V_{od}^2}{E^2_{\max} \cdot d^2} \cdot \exp\left(\frac{v_p t}{d}\right) \right] \cdot \sigma(t_{p\max})$$

(2.7)

with

$$t_{n \max} = \frac{d}{v_n} \cdot \ln\left(1 + \frac{E_{\max} \cdot d}{V_{od}}\right) > V_{od} > 0$$

$$t_{p \max} = \frac{d}{v_p} \cdot \ln\left(1 + \frac{E_{\max} \cdot d}{V_{od}}\right)$$

(2.8)

and the unit step function

$$\sigma(t_{n \max}) = 1 \quad 0 \le t \le t_{n \max}$$

$$\sigma(t_{p \max}) = 1 \quad 0 \le t \le t_{p \max}$$

$$\sigma(t) = 0 \quad elsewhere.$$

$Q_{gen}$  is the total charge per unit length, generated by the traversing particle in the bulk,  $E_{max}$  represents the maximum electric field at full depletion,  $v_n$  and  $v_p$  are the charge carrier drift velocities, d is the detector thickness.  $V_{od}$ , the over depletion voltage, is the voltage in excess of the voltage necessary for full detector depletion.  $t_{nmax}$  and  $t_{pmax}$  denote the total charge collection time for electron and holes respectively. It has to be mentioned here, that the diffusion of the carriers is neglected in this approximation and only the drift component due to the electric field is taken into account.

The two terms are nonzero only for the time where moving charge carriers are present in the bulk, which is accounted for by the unit step functions  $\sigma(t)$ . Hence, the detectable output signal is a current pulse with a rise time of typically a few pico seconds<sup>4</sup>. This is the time, the incident particle

<sup>&</sup>lt;sup>4</sup> In case of a usual detector thickness of a few hundred micrometers. The traverse time calculates from the detector thickness divided by the speed of light in the medium (detector material) for relativistic particles.

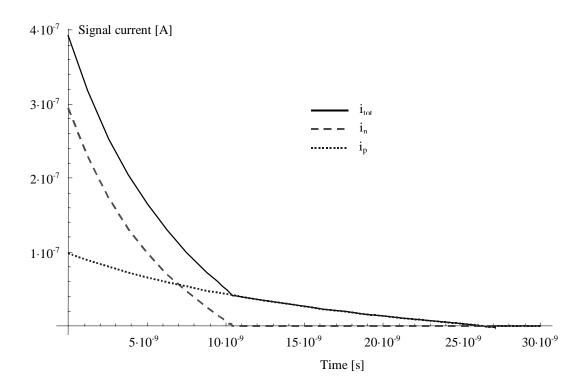

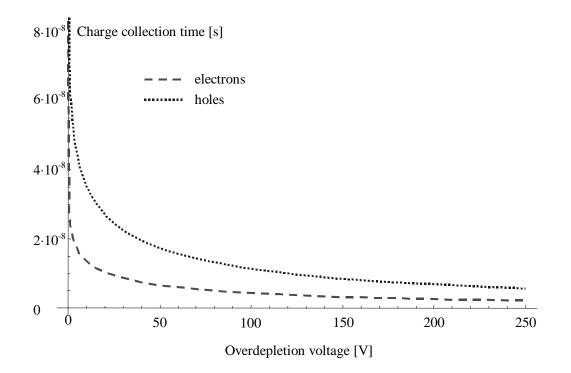

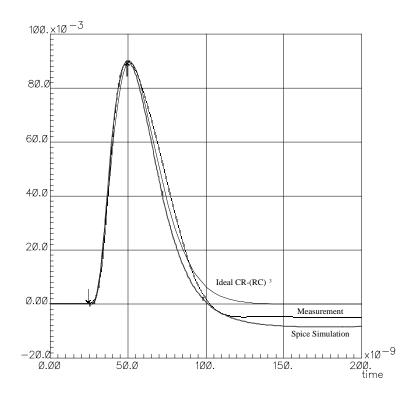

needs to traverse through the entire detector bulk and to create the maximum number of electron-hole pairs. Immediately after their creation, the charge carriers start drifting in the electric field towards their respective electrodes, where they are absorbed on arrival. At the time when the last carrier reaches its electrode, the current becomes zero. Thus, the fall time of the signal pulse is proportional to the drift velocities of the charge carriers and therefore dependent on the electric field across the detector bulk and the mobilities of the electrons and holes in the semiconductor. As holes have usually a different (lower) mobility than electrons, the falling edge of the pulse signal is divided into two parts. After the last hole has reached its electrode, the output current becomes zero. The length of the falling edge for a moderately overdepleted 300  $\mu$ m silicon detector is in the range of 25 ns (see Figure 7 for the charge collection time versus overdepletion voltage). Figure 5 shows the pulse shape according to (2.11).

Figure 5. Current vs. time for 300 µm substrate doped at 10<sup>12</sup> cm<sup>-3</sup> with an overdepletion of 20 V. The total charge generated was assumed 24000 electron-hole pairs (1 MIP), the carrier mobilities 1300 and 500 cm/Vs respectively.

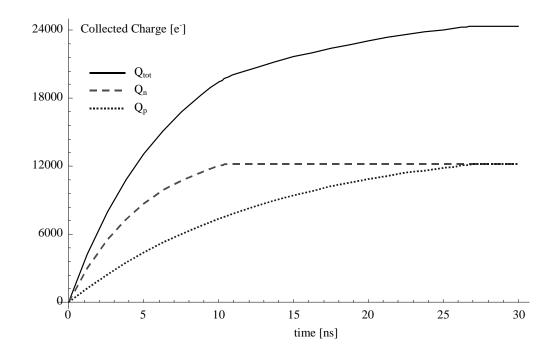

The contribution of each charge carrier to the total detectable charge in the output pulse depends on the place of its creation inside the detector, hence the further it travels before it reaches the electrode, the more it contributes. For that reason, a certain number of electron-hole pairs induce only half of the charge they carry themselves on the electrodes. The contribution as a function of the drift distance can be denoted as an infinite sum, which converges to one half for each of the charge carrier types [2]. A traversing MIP, creating 24000 electron-hole pairs in 300 µm silicon, gives rise to 24000 q of signal charge. Integrating (2.11) with respect to time yields the collected charge as a function of time [53], (Figure 6).

Figure 6. Collected charge as a function of time for the same conditions as in Figure 5.

Figure 7. Charge collection time versus overdepletion voltage according to equation (2.12) for 300  $\mu$ m silicon substrate doped at 10<sup>12</sup> cm<sup>-3</sup>.

## **The Silicon Strip Detector**

The following list summarizes the desirable characteristics of a semiconductor particle detector material:

14

- Efficient energy to charge conversion

- Long charge carrier lifetimes for low leakage current and high charge collection efficiency

- High charge carrier mobilities for large signal amplitude and short signal pulse decay time

- High resistivity to enable full detector depletion

- Surface quality to minimize surface leakage

In current high-energy physics experiments, tracking detectors use mainly silicon as the detecting material, but also different semiconductors like germanium, gallium-arsenide or diamond are presently under investigation for their application as active substrates in radiation detectors. The main advantage of silicon is, besides its attractive characteristics (Table 1), that it has the most advanced techniques for the production of high quality crystals and is the most commonly used semiconductor material for various electronics application and for integrated circuits. The choice of other semiconductor materials might be motivated by special requirements, but their superiority over silicon has rarely been proven in practice. Table 1 summarizes some important properties of silicon [36].

#### Table 1. Some physical properties of silicon:

| Atomic number                      | 14                  |                     |

|------------------------------------|---------------------|---------------------|

| Atomic weight                      | 28.09               |                     |

| Density                            | 2.328               | g/cm <sup>3</sup>   |

| Dielectric constant (relative)     | 11.9                |                     |

| Intrinsic resistivity              | 235                 | kΩcm                |

| Energy gap E <sub>G</sub> (300K)   | 1.12                | eV                  |

| Electron mobility (300K)           | 1350                | cm <sup>2</sup> /Vs |

| Hole mobility (300K)               | 480                 | cm <sup>2</sup> /Vs |

| Carrier saturation velocity (300K) | $8 \cdot 10^{6}$    | cm/s                |

| Intrinsic carrier density          | $1.5 \cdot 10^{10}$ | cm <sup>-3</sup>    |

| Breakdown field                    | $3 \cdot 10^{5}$    | V/cm                |

| Energy per electron-hole pair      | 3.62                | eV                  |

| Minimum dE/dx                      | 1.66                | $MeV \cdot g/cm^2$  |

Position sensitive detectors for multi particle tracking usually consist of one or two-dimensional arrays of detection elements. This is obtained by dividing the p-n diode into smaller segments that act as individual independent electrodes. Besides pad and pixel structures, the microstrip detector is the most widely used architecture in modern tracking devices.

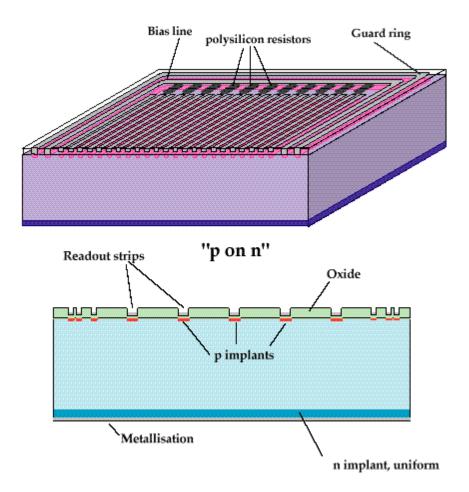

Microstrip detectors are segmented in 10 to 50  $\mu$ m wide parallel diode strips, which can be several centimeters long. Every strip can be connected to its own readout channel or intermediate strips can be left floating and only capacitively coupled to the readout strips. Depending on the precise geometry and signal processing the spatial resolution can be as good as < 1  $\mu$ m in one dimension [15]; there is no sensitivity along the strip. A schematic view of a microstrip detector is shown in Figure 8. To achieve a two dimensional position information two microstrip detectors are mounted back to back rotated against each other. Only single tracks are unambiguously reconstructed. For n tracks, the n<sup>2</sup> possible combinations of the hits in the individual planes introduce considerable ambiguities called ghost hits. Combining several of these double microstrip planes and an iterative track finding program can partially or fully resolve the ambiguities and reconstruct the real tracks.

Figure 8. Cut views of a single sided p-on-n microstrip detector with capacitive (AC) coupled aluminum readout strips. The p-type implants are isolated from the readout strips through silicon oxide.

In addition to segmenting one side of the detector, the backplane can be segmented as well. This allows two dimensional position information from one silicon plane, hence reducing the material the particles have to traverse and can help to resolve the ambiguities by correlating the signal heights in the strips on the front and the back side.

For the ATLAS tracker, single sided p-on-n silicon strip detectors are foreseen. Each detector has an active area of approximately 6 cm by 6 cm, containing 768 strips. All strips are read out. The implant strip dimensions are 20  $\mu$ m width, 62 mm length and 80  $\mu$ m pitch<sup>5</sup>. A bias resistor supplies a DC path from each implant strip to the bias line allowing all strips to be held at the same potential. The resistor value should be large in order to achieve a maximum isolation between the individual strips and to keep its contribution to the system noise low (Chapter 3). On the other hand, the resistors cannot be made arbitrarily large as the inevitable variation of the actual resistor values would cause a too big variation of voltage drop, influencing the potential of the individual strips. The readout strips are AC coupled aluminum lines deposited on top of the oxide layer. The backplane consists of a metallized n<sup>+</sup>-layer. The detector bias voltage is applied between the bias line and the backplane. The detector bulk thickness is 300  $\mu$ m.

Table 2 summarizes some important electrical properties of the ATLAS prototype strip detector, which are crucial for the design of the read out electronics.

| Resistivity p-implant             | <200    | $k\Omega/cm$ |

|-----------------------------------|---------|--------------|

| Resistivity aluminum strip        | <15     | Ω/cm         |

| Bias resistors (polysilicon)      | 1.5±0.5 | MΩ           |

| Load capacitance per strip        | <1.2    | pF/cm        |

| Coupling capacitance              | >20     | pF/cm        |

| Depletion voltage                 | <100    | V            |

| Initial leakage current @ 20°C    | <6      | μA @ 150 V   |

| (no irradiation)                  | <20     | μA @ 300 V   |

|                                   | <100    | μA @ 500 V   |

| Leakage current after irradiation | <1.5    | mA @ 500 V   |

#### Table 2. ATLAS strip detector electrical properties

<sup>&</sup>lt;sup>5</sup> The pitch denotes the distance between the centers of two adjacent strip implants.

## Chapter 3

# **Processing The Signals From Silicon Strip Detectors - The Front-End**

In order to utilize the information of the signal induced by traversing particles on the readout electrodes of a silicon strip detector, it needs to be taken care of by some signal-processing unit.

The following section describes the requirements for an electronic device to deal with the signal delivered by a Silicon strip detector in terms of electrical properties of the signal itself and of the detector. In this context, we emphasize on the crucial problem of the noise performance of an amplifier to be used with silicon detectors.

In integrated signal processing systems such as detector readout systems, electrical noise is a fundamental limiting factor. It represents a lower limit to the size of the electrical signal that can be handled by an electronic circuit without significant deterioration in signal quality. In position sensitive detector systems, the ratio between signal charge and noise determines the position resolution and even the detectability of the signals and indirectly determines the readout speed and the number of readout channels required. For a silicon strip detector and using pulse height readout, the position resolution at a given strip distance is directly proportional to the system's signal-to-noise ratio [47].

For the design of such a system, it is of crucial importance to optimize the noise performance of the preamplifier or input stage, as in a well designed systems the overall noise performance is always dominated by the preamplifier noise. The signal source in semiconductor detector systems is of a reactive rather than a resistive type, which means that the signal source at the input of the preamplifier can be represented by a capacitance in parallel with a current source. In order to achieve wideband noise matching, this fact has to be taken into account.

Unfortunately, noise is not the only performance parameter to be optimized for wideband amplifiers matching reactive sources. In addition, there are many other constraints to be met such as precise gain, bandwidth, power dissipation, distortion, stability, dynamic range, etc. For the application of the semiconductor detector readout, some of those, like low power dissipation are crucial, while others, such as large dynamic range or precise gain are less important.

The goal of this section is, to derive a complete expression for the noise performance of an entire detector readout system in terms of design parameters and conditions imposed by the environment.

The front-end for the readout of signals from silicon strip detectors, as well as from other types of particle detectors, can be divided into three sub-blocks: The input stage or preamplifier, which is the main source of electronics noise, the shaper, a bandpass filter to reduce the noise bandwidth, and some type of output buffer, that drives the signal from the shaper into subsequent stages.

The first step in the design of a preamplifier is the choice of the appropriate input device, which dominates the noise performance of the entire system. Possible candidates for this type of application are bipolar-junction-transistors (BJT) and the field-effect-transistors (MOSFET and JFET). There is only one noise source for each device type, which is related to the amplification mechanism and determined uniquely by the fundamental parameters of the device. This is thermal noise in the case of FETs and collector current shot noise for the BJT, which can be represented as an equivalent white noise voltage generator in series with the control electrode (base, gate). All other noise sources (for example "parallel" sources such as resistors at the input and leakage current into the input) are a result of imperfections. This type of noise can be reduced by improvements in technology and circuit design. The superiority of one device over the others in terms of noise performance depends on the selected amplifier configuration as well as on the requirements of the application. In the following, the noise performance of the BJT as the input device for a charge sensitive preamplifier will be derived and compared with the performance of a MOSFET transistor.

#### **Feedback Configurations**

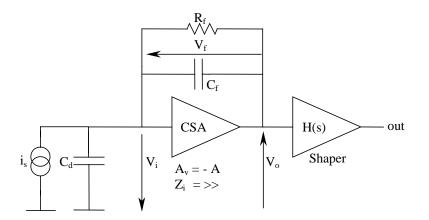

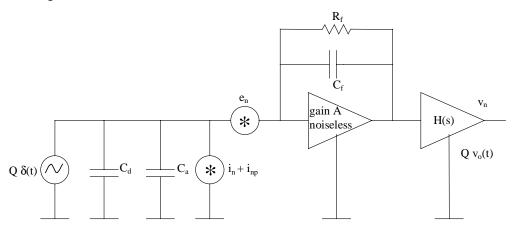

There are three types of preamplifier configurations commonly used for the amplification of charge signals from particle detectors. Those are the integrating transimpedance amplifier with capacitive feedback ("charge sensitive amplifier", CSA), the current amplifier configuration and the voltage amplifier configuration. A detailed description of those architectures as charge amplifiers and a performance comparison are given in [27]. Subsequently, only the transimpedance configuration will be studied.

As discussed in Chapter 2, pp. 11, the detector output signal can be represented as a short current pulse, for a thin silicon detector in the range of up to 30 ns. The total charge  $Q_s$  contained in this pulse  $i_s$  is proportional to the energy deposited in the detector.

$$E \propto Q_s = \int i_s dt \tag{3.1}$$

This charge is integrated onto a small feedback capacitor  $C_f$  by means of a low noise transimpedance amplifier, giving rise to a voltage step at the output with an amplitude  $Q_s/C_f$ . The step signal is fed into another integrating amplifier, which performs the pulse shaping, respectively noise filtering, primarily to optimize the signal-to-noise ratio of the readout system. The pulse shaper is being investigated in the section "Equivalent Noise Charge (ENC) And The Shaper Circuit", pp. 28.

Figure 9 shows the block diagram of a charge-sensitive transimpedance amplifier configuration (CSA). With the amplifier voltage gain  $V_o/V_i = -A$ , the voltage across  $C_f$  becomes  $V_f = (A + 1) \cdot V_i$ . The charge integrated onto  $C_f$  can be written as  $Q_f = C_f \cdot V_f = C_f \cdot (A + 1) \cdot V_i$ . Assuming the charge into the amplifier  $Q_i \cong Q_f$ , the charge gain  $A_Q$  calculates to:

$$A_{\underline{Q}} = \frac{V_o}{Q_i} = \frac{V_o}{C_f (A+1) \cdot V_i} = -\frac{A}{A+1} \cdot \frac{1}{C_f} \approx -\frac{1}{C_f}$$

(3.2)

The effective ("dynamic") input capacitance is  $C_i = Q_i / V_i = C_f (A + 1)$ . The amount of signal charge which actually flows into the amplifier input and the fraction which remains on  $C_d$  is determined by the ratio  $C_d / C_i$ :

$$\frac{Q_i}{Q_s} = \frac{Q_i}{Q_d + Q_i} = \frac{C_f V_f}{C_d V_i + C_f V_f} = \frac{C_f (A+1)}{C_d + C_f (A+1)} = \frac{C_i}{C_d + C_i} = \frac{1}{1 + \frac{C_d}{C_f (A+1)}}$$

(3.3)

For example, assuming a feedback capacitance of 100 fF, a detector capacitance of 10 pF and a voltage gain of 1000, the fraction of signal charge that actually flows into the amplifier is 91%.

The feedback resistor  $R_f$  serves to discharging the capacitor  $C_f$ . It has to be large enough to minimize its contribution to the amplifier noise and small enough to discharge  $C_f$  fast enough to prevent tail pile-up.

Figure 9. Block diagram of the charge sensitive amplifier (CSA) configuration.

#### **Noise Sources In Bipolar Junction Transistors**

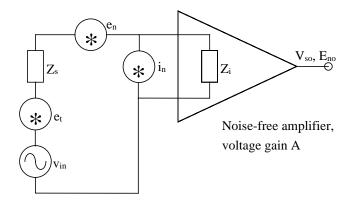

In the following sections, the noise sources which appear with the use of a BJT as the input device for a CSA, will be revisited and the noise behavior of the whole system, from the detector to the shaper output, derived. Subsequently, the noise performance will be compared to the noise performance of a similar system, using a FET as the input device.

First, the basic noise mechanisms will be summed up, for a detailed discussion refer to excellent sources like [13], [39] or [46]. Noise can be characterized by its frequency spectrum, its amplitude distribution, and the physical mechanism responsible for its generation. There are two irreducible forms of noise which are generated according to physical principles, *shot noise* and *thermal* (or *Johnson*) *noise*. Real devices (transistors, resistors) in addition show various sources of "excess noise". This excess noise often exhibits a *1/f* spectrum, therefore called *1/f-noise*. Measured noise voltage (or current) depends on the measurement bandwidth, thus it is convenient to define a RMS noise voltage (current) spectral density:

• *Thermal noise* is generated by random thermal movement of the charge carriers in any conductive material. The noise voltage spectrum of a resistor, for example, is proportional to its resistance and to the absolute temperature and is frequency independent, thus showing a "white" noise spectrum:

$$v_t = \sqrt{4kTR\Delta f} \tag{3.4}$$

A noisy resistor can be represented by an equivalent circuit, composed of a noise-free resistor and a noise voltage source in series<sup>1</sup> with a noise voltage density according to (3.4).

• *Shot noise* occurs due to the fact that an electric current is the flow of discrete electrical charges. Any current flowing across a potential barrier, like for example a pn-junction, shows a statistical fluctuation, giving rise to a random pulse train of current pulses of unit charge. The spectrum is, like for thermal noise, white:

$$i_n = \sqrt{2qI_{DC}\Delta f} \tag{3.5}$$

The equivalent circuit representation for a shot noise source is a current generator according to (3.5).

• *1/f noise* in the case of the BJT manifests itself only in a frequency region that can be several orders of magnitude lower than that in MOSFET transistors. Therefore, from a practical low-noise design point of view, *1/f noise* in bipolar transistors has only little significance.

20

<sup>&</sup>lt;sup>1</sup> According to Norton's Theorem, this series arrangement can be replaced by a current generator in parallel to the ideal resistor, with a noise current density of  $i_t = \sqrt{4kT\Delta f/R}$ .

In a bipolar transistor in the forward-active region, minority carriers diffuse and drift across the base region to be collected at the collector-base junction. Minority carriers entering the collector-base depletion region, are accelerated by the field existing in this region, and swept across into the collector. The time of arrival of the drifting carriers at the collector base junction is a purely random process and hence the BJT's collector current consists of a random series of current pulses, therefore showing *shot noise* behavior.

$$i_{nc}^2 = 2qI_c\Delta f \tag{3.6}$$

The base current  $I_b$  appears due to recombination in the base and base–emitter depletion regions and due to carrier injection from the base into the emitter.  $I_b$  exhibits *shot noise*.

$$i_{nb}^2 = 2qI_b\Delta f \tag{3.7}$$

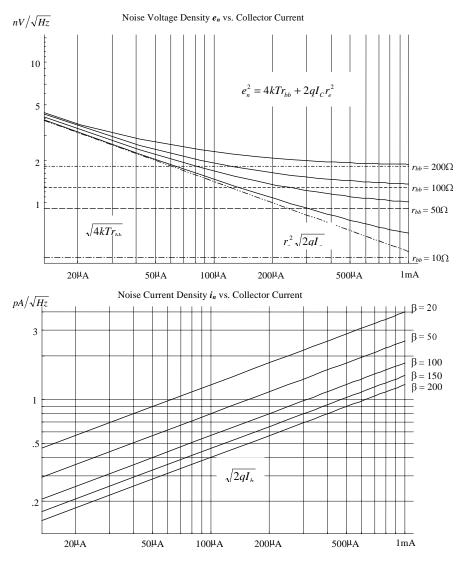

In addition to the shot noise sources, associated with the terminal currents, BJTs show also *thermal noise* due to series resistances at each terminal. Among the three resistances  $r_{bb}$ ,  $r_c$  and  $r_e$ , the base-spread resistance  $r_{bb}$  is the most important one, because it appears at the input terminal for most cases. The noise voltage caused by the base resistance is

$$v_{nb}^2 = 4kTr_{bb}\Delta f \tag{3.8}$$

Although there is no exact theoretical description of *1/f noise* in BJTs, it was shown [39] that the appropriate power spectrum can be expressed as

$$i_{nf}^2 = \frac{2qf_L I_B^{\gamma}}{f} \tag{3.9}$$

with the technology dependent parameters  $f_L$  and  $\gamma$ . The parameter  $f_L$  stands for the noise corner frequency of the specific device, while  $\gamma$  is a constant factor between 1 and 2, usually close to 1.

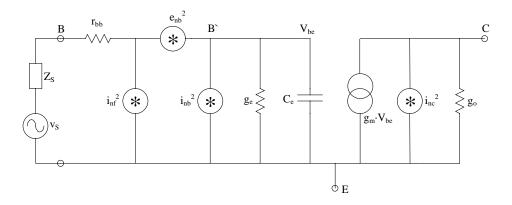

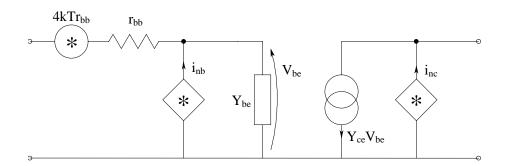

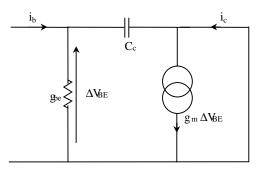

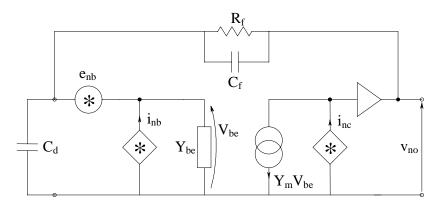

Figure 10. Hybrid- $\pi$  small signal model of a BJT transistor, modified to include noise sources.

Figure 10 shows the hybrid- $\pi$  small signal model of a BJT transistor, including the above described noise sources. The two elements  $g_e$  and  $C_e$  represent the significant portion of the transistor input impedance. The amplification property of the device is represented by the dependent current generator  $g_m V_{be}$ , where  $V_{be}$  is the signal potential between B` and the emitter terminal E, the element  $g_o$ represents the dynamic output resistance of the transistor. The short-circuit current gain  $\beta$  can be derived from the model. Assuming a short circuit between C and E and considering low-frequency operation,  $\beta$  can be expressed as

$$\beta = \frac{g_m V_{be}}{g_e V_{be}} = \frac{g_m}{g_e},$$

(3.10)

22

with  $g_m$  derived from the diode equation relating  $I_c$  and  $V_{be}$ :

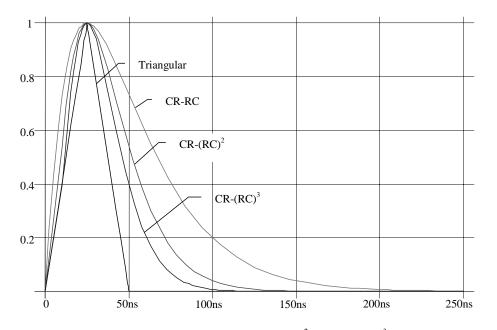

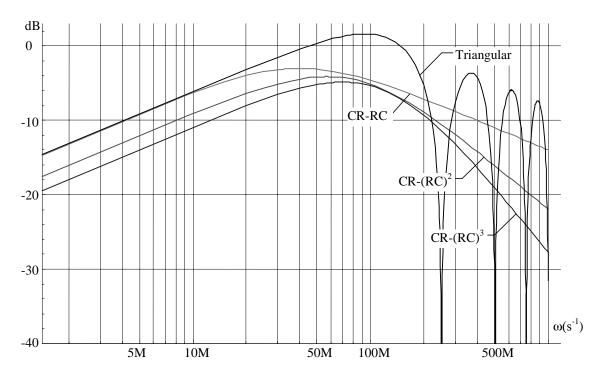

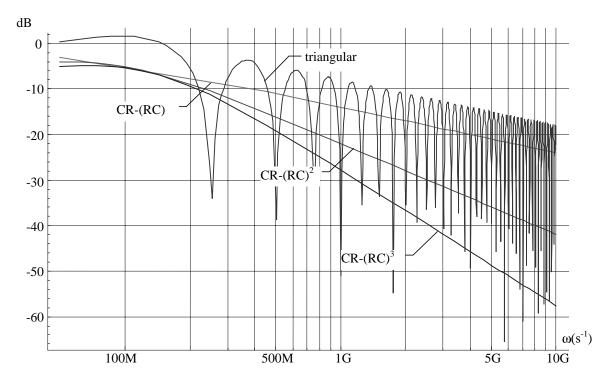

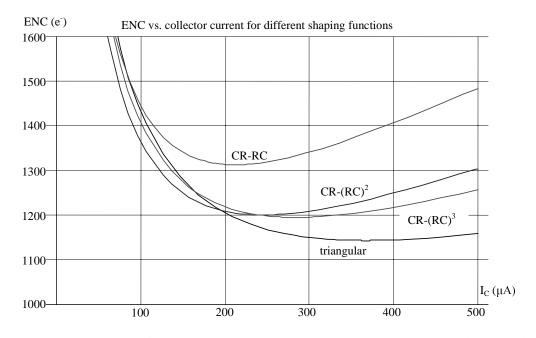

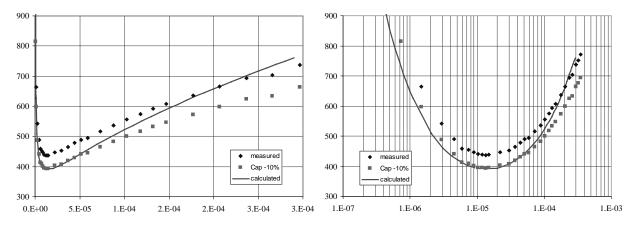

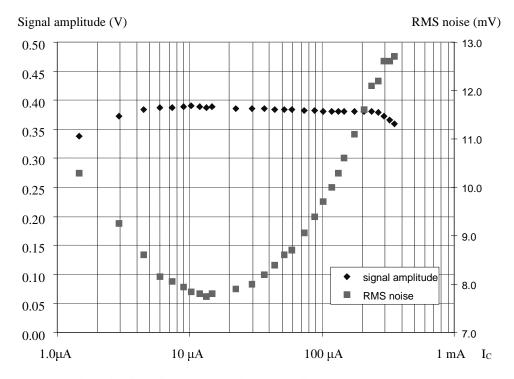

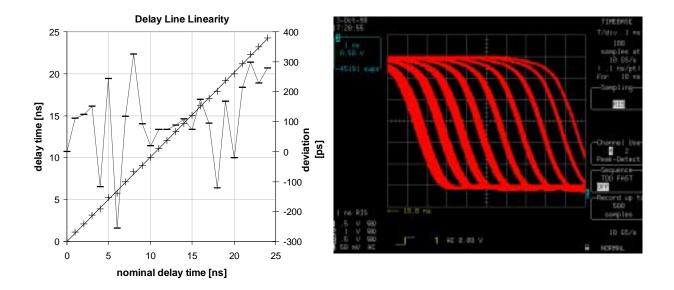

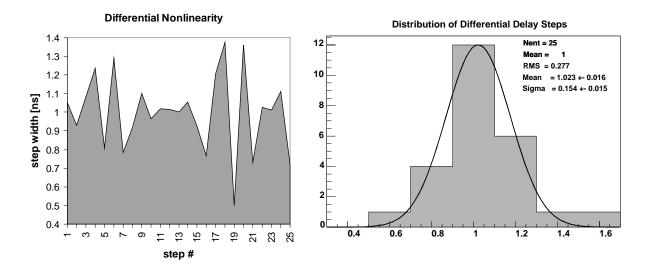

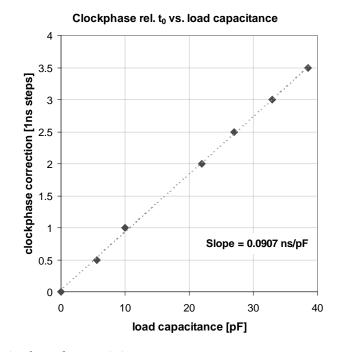

$$g_m = \frac{qI_C}{kT} \tag{3.11}$$