LHCb 99-004, TRIG 17 February 1999

## LHCb BASE-LINE LEVEL-0 TRIGGER 3D-FLOW IMPLEMENTATION

## Dario B. Crosetto

900 Hideaway Pl. DeSoto, TX 75115 Crosetto@vxcern.cern.ch; Crosetto@physics.rice.edu

Original version 17 February 1999; added Appendix upon request by L0 trigger group 2 June 1999

#### Abstract

The LHCb (Large Hadron Collider Beauty Experiment at CERN, Geneva, Switzerland) Level-0 trigger implementation with the 3D-Flow system is described in detail using components and technology available today. It offers full programmability, allowing it to adapt to unexpected operating conditions and enabling new, unforeseen physics.

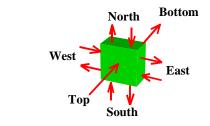

The 3D-Flow Processor system is a new, technology-independent concept in very fast, real-time system architectures. Based on the replication of a single type of circuit of approximately 100K gates, which communicates in six directions: bidirectional with North, East, West, and South neighbors, unidirectional from Top-to-Bottom, the system offers full programmability, modularity, ease of expansion and adaptation to the latest technology.

A complete study of its applicability to the LHCb Calorimeter triggers is presented. Full description of the input data handling, either in digital or mixed digital-analog form, of the data processing, and the transmission of results to the global level-0 trigger decision unit are provided.

Any level-0 trigger algorithm (2x2, 3x3, 4x4, etc.) with up to 20 steps, can be implemented with zero dead time, while sustaining input data rate (up to 32-bit per input channel, per bunchcrossing) at 40 MHz. For each step, each 3D-Flow processor can exchange up to 26 operation, inclusive of compare, ranging, finding local maxima, and efficient data exchange with neighboring channels. (One to one correspondence between input channel and trigger tower).

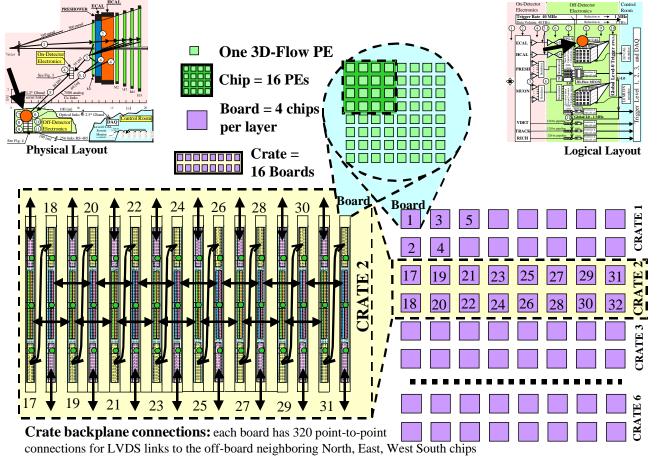

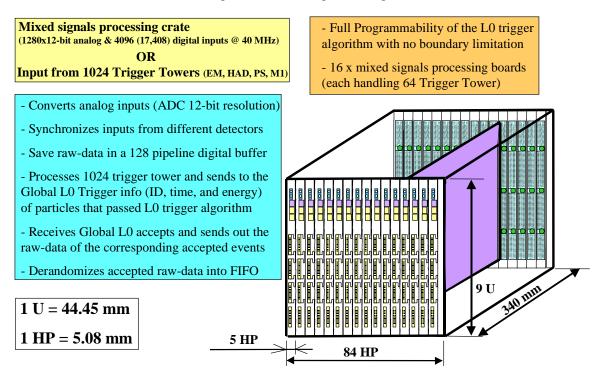

It is shown how the whole Level-0 calorimeter trigger can be accommodated into 6 crates (9U), each containing 16 identical boards carrying only two main types of components, front-end FPGAs (Field Programmable Gate Array) and 3D-Flow processors.

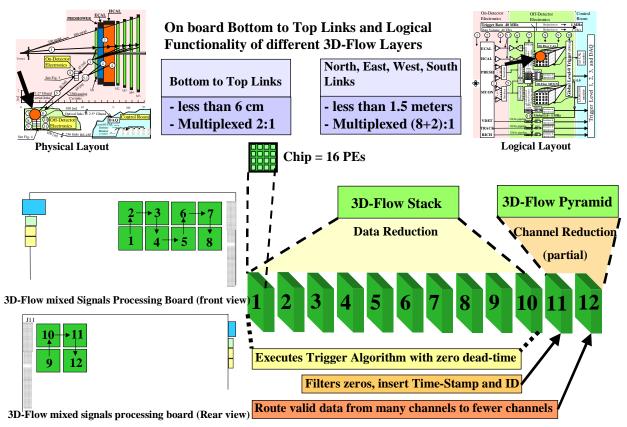

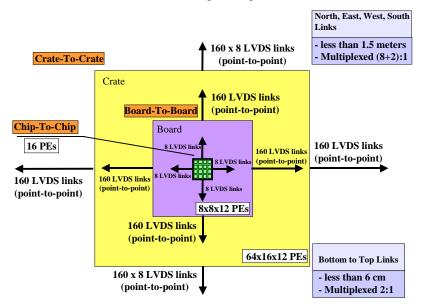

All 3D-Flow inter-chip Bottom-to-Top port connections are all contained on the board (data are multiplexed 2:1, printed circuit board (PCB) traces are shorter than 6 cm); all 3D-Flow inter-chip North, East, West, and South port connections between boards and crates are multiplexed (8+2):1 and are shorter than 1.5 meters.

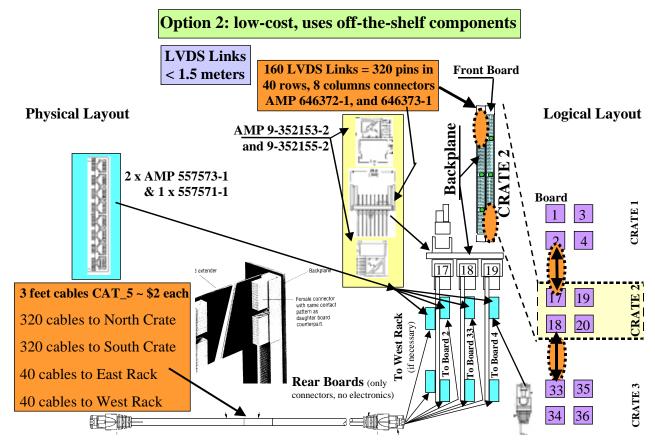

Full implementation of a 3D-Flow system, for the most complex trigger algorithm, requires 320 cables to North and South crates and 40 cables to East and West crates (cable cost =\$2 each).

For applications requiring a simpler real-time algorithm (e.g., requiring less then 20 steps, which is equivalent to 10 layers of 3D-Flow processors), the number of connections for the inter-boards (North and South), and inter-crates (East and West) will also be reduced to the number of layers used by the simpler algorithm, thus not requiring all cables to be installed (e.g., applications requiring only 9 layers of 3D-Flow processors will save 32 cables to the North, 32 to the South, 4 to the East, and 4 to the West crates).

Details are also given on timing and synchronization issues, ASIC (Application Specific Integrated Circuit) design verification, real time performance monitoring and design (software and hardware) development tools.

This material is based upon work partially funded by the Department of Energy under Grant No. DE-FG03-95ER81905.

## TABLE OF CONTENTS

| 1 INTRODUCTION                                                                          | 4  |

|-----------------------------------------------------------------------------------------|----|

| 2 THE 3D-FLOW: A SINGLE TYPE OF CIRCUIT FOR SEVERAL ALGORITHMS                          | 4  |

| 2.1 System level                                                                        |    |

| 2.2 System architecture                                                                 |    |

| 2.3 PROCESSOR ARCHITECTURE                                                              |    |

| 2.4 INTRODUCING THE THIRD DIMENSION IN THE SYSTEM                                       |    |

| 2.5 THE 3D-FLOW ARCHITECTURE OPTIMIZED FEATURES FOR THE FIRST LEVELS OF TRIGGERS.       |    |

| 3 A SINGLE TYPE OF COMPONENT FOR SEVERAL ALGORITHMS                                     |    |

| 3.1 The evolution of IC Design                                                          |    |

| 3.2 TECHNOLOGY-INDEPENDENT 3D-FLOW ASIC                                                 |    |

| 4 FIRST-LEVEL TRIGGER ALGORITHMS                                                        | 9  |

| 5 LHCB LEVEL-0 TRIGGER OVERVIEW                                                         | 10 |

| 5.1 Physical Layout                                                                     | 10 |

| 5.2 Logical Layout                                                                      |    |

| 5.3 Electronic Racks (Functions/Locations)                                              | 12 |

| 6 A SINGLE TYPE OF BOARD FOR SEVERAL ALGORITHMS                                         | 13 |

| 6.1 3D-FLOW MIXED-SIGNAL PROCESSING BOARD (OPTION 1)                                    | 13 |

| 6.2 3D-FLOW DIGITAL PROCESSING BOARD (OPTION 2)                                         |    |

| 6.3 FRONT-END SIGNAL SYNCHRONIZATION/PIPELINING/DERANDOMIZING/TRIGGER WORD FORMATTER    |    |

| 6.3.1 Level-0 front-end, VHDL coding of the I/O and signals definition                  |    |

| 6.3.2 Level-0 front-end, VHDL coding of registering the input data on rising edge       |    |

| 6.3.3 Level-0 front-end, VHDL coding of the updating contents of variable delays        |    |

| 6.3.4 Level-0 front-end, VHDL coding of selecting a variable delay                      |    |

| 6.3.6 Level-0 front-end, VHDL coding for the 128 pipeline buffer                        |    |

| 6.3.7 Level-0 front-end, VHDL coding of moving accepted L-0 event from 128 pipe to FIFO |    |

| 6.3.8 Mapping the Level-0 front-end circuits into ORCA OR3T30 FPGA                      | 24 |

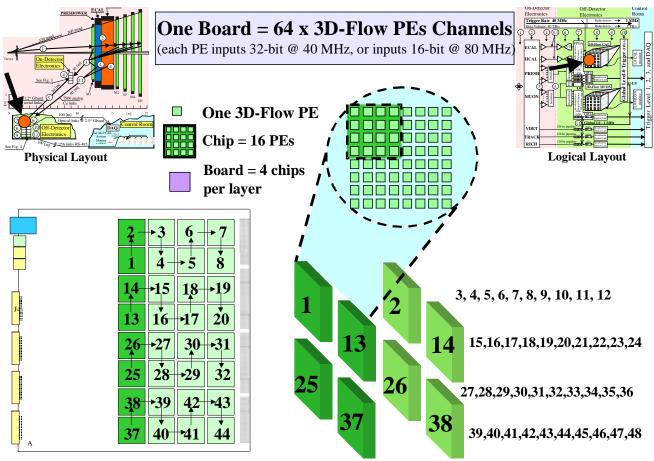

| 6.3.9 Front-end circuits 'Real-Estate' and cost considerations                          | 24 |

| 6.4 LOGICAL-TO-PHYSICAL LAYOUT OF 64 CHANNELS/10 LAYERS ON THE 3D-FLOW BOARD            |    |

| 6.5 ON-BOARD DATA-REDUCTION, CHANNEL-REDUCTION AND BOTTOM-TO-TOP LINKS                  |    |

| 6.6 DETAILS OF THE ON-BOARD BOTTOM-TO-TOP LINKS (6 CM)                                  |    |

| CRATE(S) FOR 3D-FLOW SYSTEMS OF DIFFERENT SIZES                                         | 28 |

| 7.1 CRATE BACKPLANE LVDS LINKS NEIGHBORING CONNECTION SCHEME                            |    |

| 7.2 NUMBER OF NEWS LINKS FOR THE CHIP-TO-CHIP, BOARD-TO-BOARD, CRATE-TO-CRATE           |    |

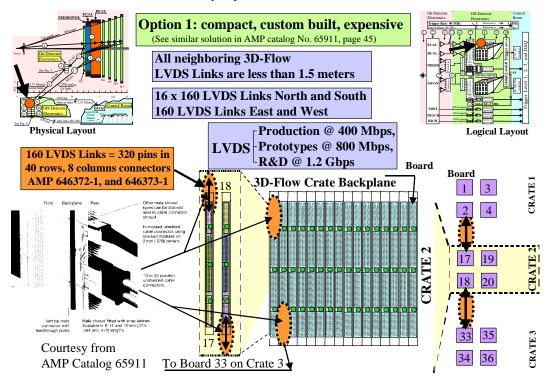

| 7.3 IMPLEMENTATION OF THE BACKPLANE CRATE-TO-CRATE LVDS LINKS (OPTION 1)                |    |

| 7.4 IMPLEMENTATION OF THE BACKPLANE CRATE-TO-CRATE LVDS LINKS (OPTION 2)                |    |

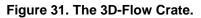

| 7.5 THE 3D-FLOW CRATE                                                                   |    |

| 8 GLOBAL LEVEL-0 TRIGGER                                                                | 32 |

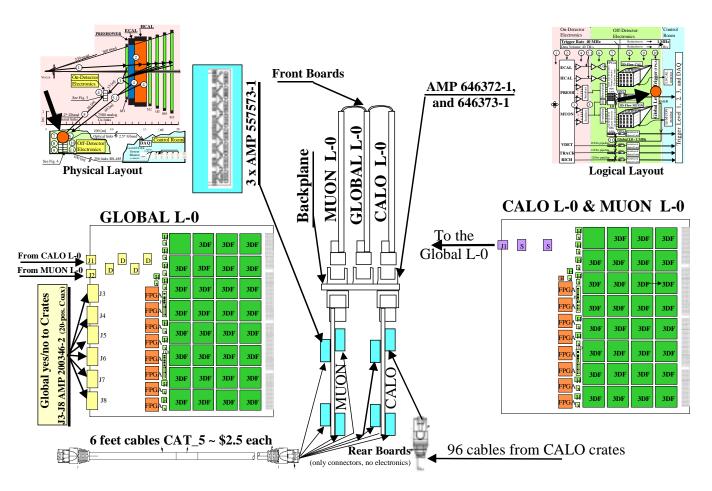

| 9 TIMING AND SYNCHRONIZATION ISSUES OF CONTROL SIGNALS                                  |    |

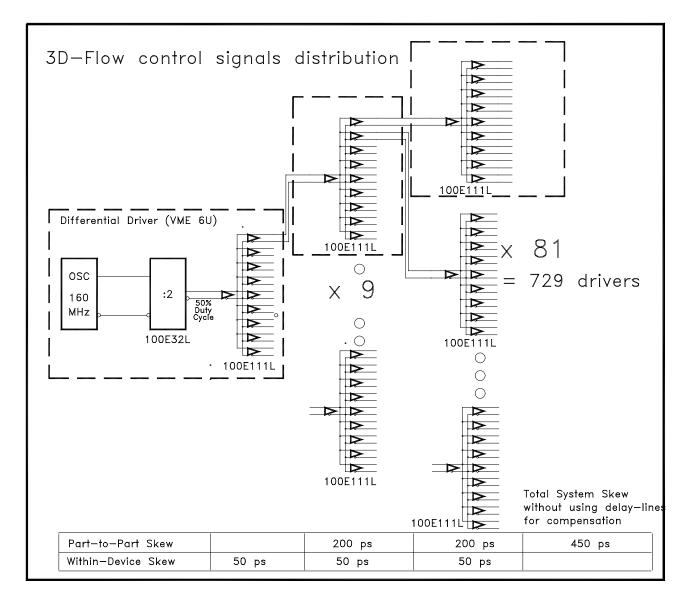

| 10 ASIC DESIGN VERIFICATION                                                             | 34 |

| 11 HOST COMMUNICATION AND MALFUCTIONING MONITOR                                         | 35 |

| 12 SOFTWARE TOOLS                                                                       |    |

| APPENDIX A: COST/PERFORMANCE COMPARISON OF THE CALORIMETER FRONT-END AND L              |    |

| IGGER                                                                                   |    |

| APPENDIX B: FRONT-END ELECTRONICS FOR THE PRESHOWER DETECTOR                                                                                      | 41 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| APPENDIX C: HIGH SPEED BACKPLANES                                                                                                                 | 41 |

| Figure 1. The 3D-Flow Processing Element (PE) or "logical unit."                                                                                  | 5  |

| Figure 2. One layer (or stage) of 3D-Flow parallel processing                                                                                     |    |

| Figure 3. General scheme of the 3D-Flow pipeline parallel-processing architecture.                                                                |    |

| Figure 4. The evolution of IC design.                                                                                                             |    |

| Figure 5. Technology-independent 3D-Flow ASIC.                                                                                                    |    |

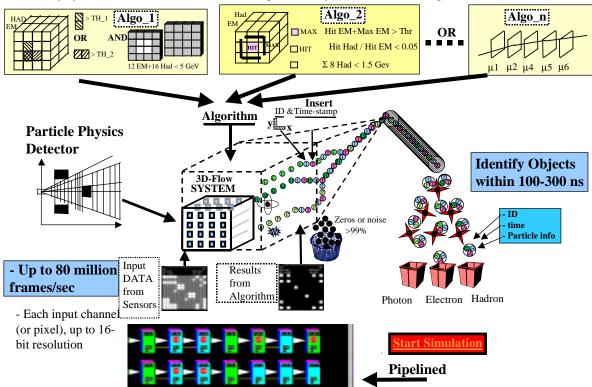

| Figure 6. Overview of the use of the 3D-Flow System in particle identification in HEP.                                                            |    |

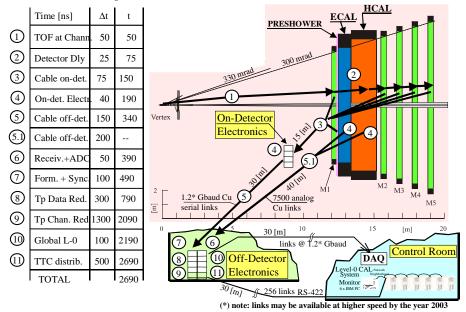

| Figure 7. LHCb Level-0 Trigger - Physical Layout.                                                                                                 |    |

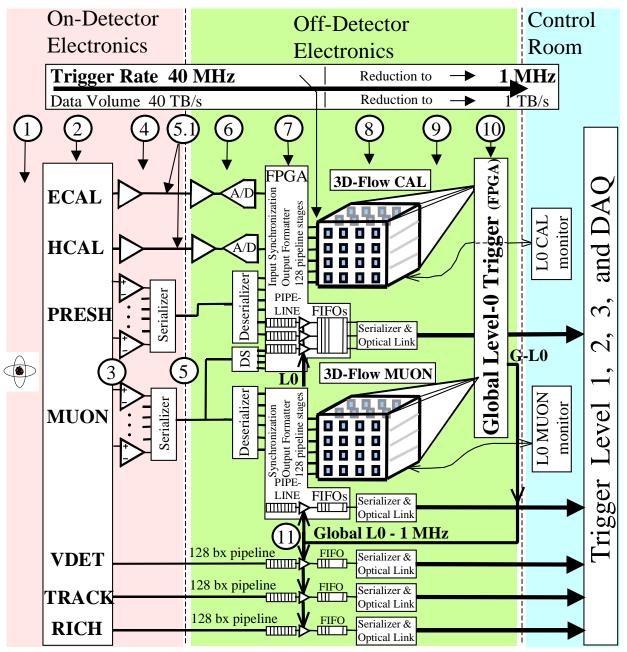

| Figure 8. LHCb Level-0 Trigger - Logical Layout.                                                                                                  |    |

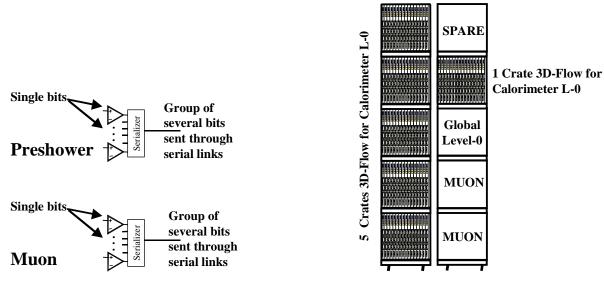

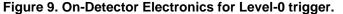

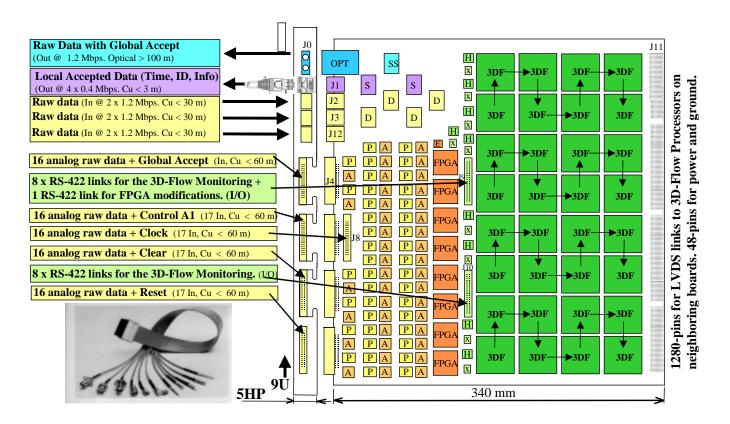

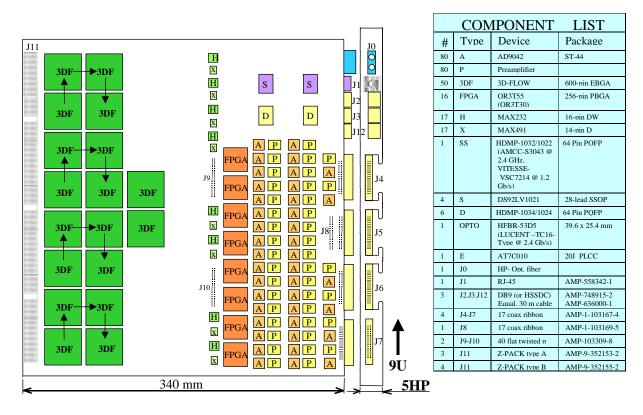

| Figure 9. On-Detector Electronics for Level-0 trigger                                                                                             |    |

| Figure 10. Off-Detector Electronics for level-0 trigger.                                                                                          |    |

| Figure 11. Electronics in the Control Room for the Calorimeter Level-0 Trigger Monitoring                                                         |    |

| Figure 12. Mixed-signal processing board (front view)                                                                                             | 14 |

| Figure 13. Mixed-signal processing board (rear view).                                                                                             | 14 |

| Figure 14. Digital processing board (front view)                                                                                                  | 17 |

| Figure 15. Digital processing board (rear view).                                                                                                  |    |

| Figure 16. Front-end signal synchronization, pipelining, derandomizing, and trigger word formatting                                               |    |

| Figure 17. VHDL code and graphical representation of registering input data.                                                                      |    |

| Figure 18. VHDL code and graphical representation for the updating of the variable delays                                                         |    |

| Figure 19. VHDL code and graphical representation for the selection of the variable delays                                                        |    |

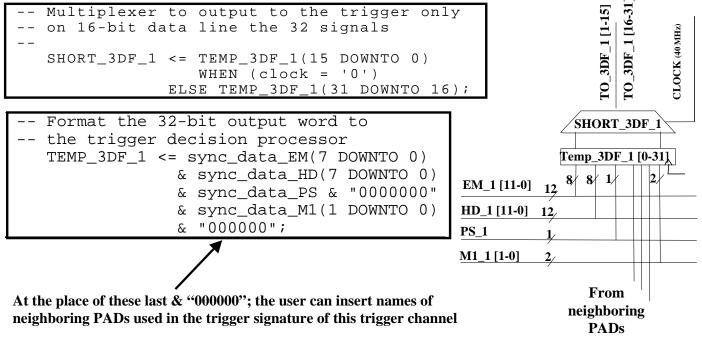

| Figure 20. VHDL code and graphical representation for formatting and multiplexing the trigger word                                                |    |

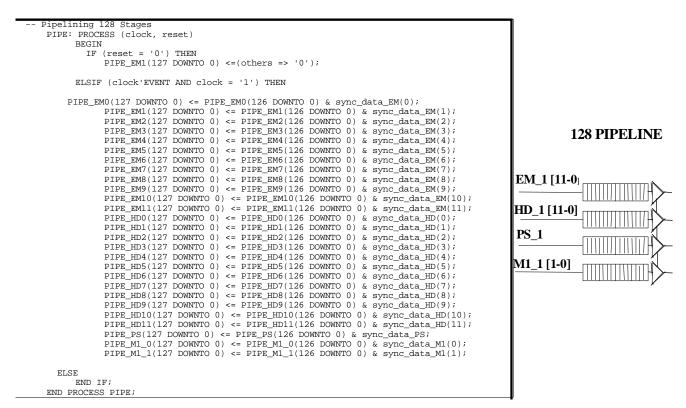

| Figure 21. VHDL code and graphical representation of the 128 pipeline buffer                                                                      | 23 |

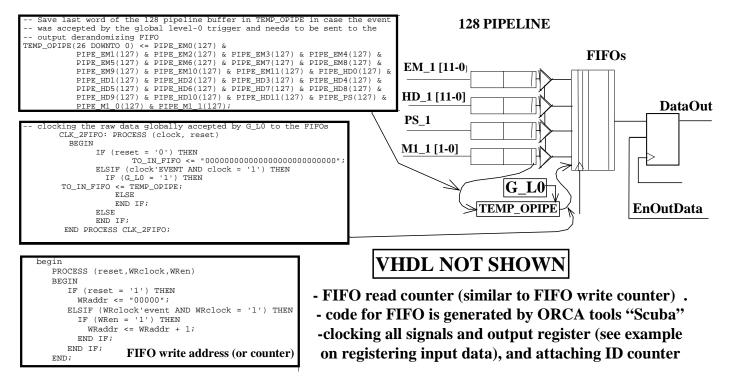

| Figure 22. VHDL code and graphical representation for moving accepted data from the pipeline to the FIFO                                          | 23 |

| Figure 23. 3D-Flow layer interconnections on the PCB board.                                                                                       |    |

| Figure 24. Bottom-to-Top Links on the PCB board.                                                                                                  |    |

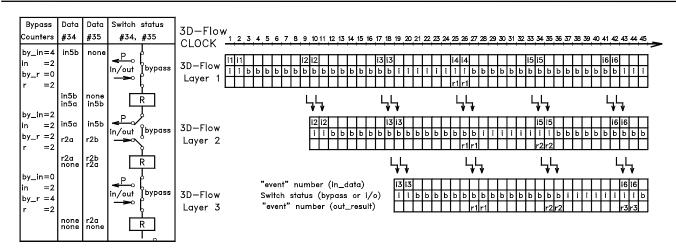

| Figure 25. Position of the bypass switches for the data flow (Input/Output) from Top-to-Bottom ports.                                             |    |

| Figure 26. Bottom-to-Top Links on the PCB (details).                                                                                              |    |

| Figure 27. 3D-Flow System LVDS Links Neighboring Connection Scheme.                                                                               |    |

| Figure 28. 3D-Flow North, East, West, and South LVDS Links.                                                                                       |    |

| Figure 29. Crate-To-Crate Backplane LVDS Links (Option 1)                                                                                         |    |

| Figure 30. Crate-To-Crate Backplane LVDS Links (Option 2).                                                                                        |    |

| Figure 31. The 3D-Flow Crate                                                                                                                      |    |

| Figure 32. LHCb Programmable Global Level-0 Trigger Decision Units.                                                                               |    |

| Figure 33. Scheme of the control signal distribution with minimum skew.                                                                           |    |

| Figure 34. ASIC design verification. From user's system algorithm down to the gate-level circuit.                                                 |    |

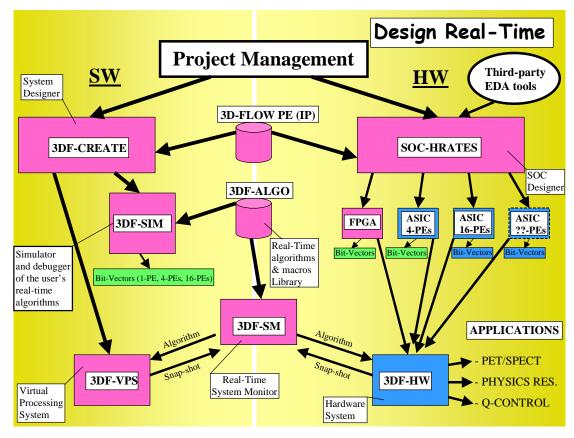

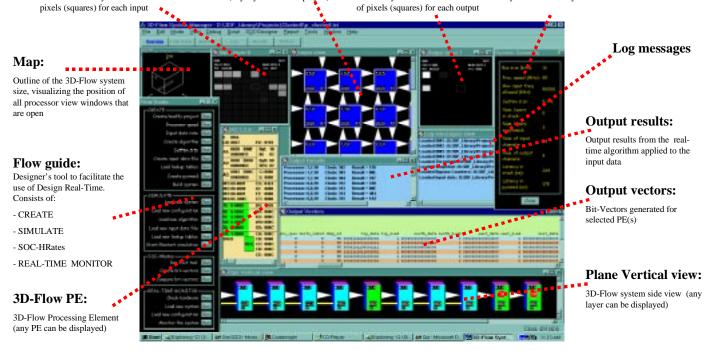

| Figure 35. Demostrator of a System Monitor for 128 3D-Flow Channels<br>Figure 36. Interrelation between entities in the Real-Time Design Process. |    |

| Figure 36. Interretation between entities in the Real-Time Design Process                                                                         |    |

|                                                                                                                                                   |    |

| Table 1. The 3D-Flow architecture optimized features for first-level trigger algorithms                                    | 7      |

|----------------------------------------------------------------------------------------------------------------------------|--------|

| Table 2. VHDL code for the definition of the architecture of the front-end circuit                                         |        |

| Table 3. Mapping the Level-0 front-end circuit into ORCA OR3T55 FPGA.                                                      | 24     |

| Table 4. System Monitor Demonstrator test results for 128 channels.                                                        | 36     |

| Table 5. System Monitor estimated timing for 1024 channels                                                                 | 36     |

| Table 6. Calorimeter Front-end and Level-0 trigger cost implementation comparison (the cost of the front-end electronics o | of the |

| PreShower and of the Pad Chamber are not included in this table).                                                          | 38     |

| Table 7. Cost comparison of the Preshower Front-end electronics                                                            | 39     |

| Table 8. Calorimeter Level-0 Trigger Features/Performances.                                                                | 40     |

|                                                                                                                            |        |

## **1 INTRODUCTION**

The importance of flexibility and programmability for the trigger systems of today's sophisticated High Energy Physics (HEP) experiments has been recognized repeatedly. As a recent example, in an article presented at the 1998 workshop on electronics for LHC experiments<sup>1</sup>, Eric Eisenhandler states that "Triggering of LHC experiments presents enormous and unprecedented technical challenges [and that].... first level or two of these trigger systems must work far too fast to rely on general-purpose microprocessors... Yet at the same time must be programmable. ... This is necessary in order to be able to adapt to both unexpected operating conditions and to the challenge of new and unpredicted physics that may well turn up."

The 3D-Flow system was conceived to satisfy exactly such stringent requirements. The result was a system suitable for application to a large class of problems, extending over several fields in addition to HEP, for which it was originally devised.

In the following, after a description of the general architecture and properties of the 3D-Flow concept, all the aspects of its application to LHCb Level-0 trigger are discussed in detail. In particular, all the details of the circuits, components and assembly, as they can be achieved with today's technology, are provided. When compared with competing proposals, the 3D-Flow solution offers system sizes and costs at least 50% lower than the alternatives, while maintaining the important advantages of full programmability, modularity, scalability and ease of monitoring.

The style of the description is in a bottom-up fashion: circuit, architecture vs. trigger needs (see Table 1), chip, board, crate, system, global trigger decision unit, timing and synchronization of control signals, real-time malfunctioning monitor, development and design verification tools.

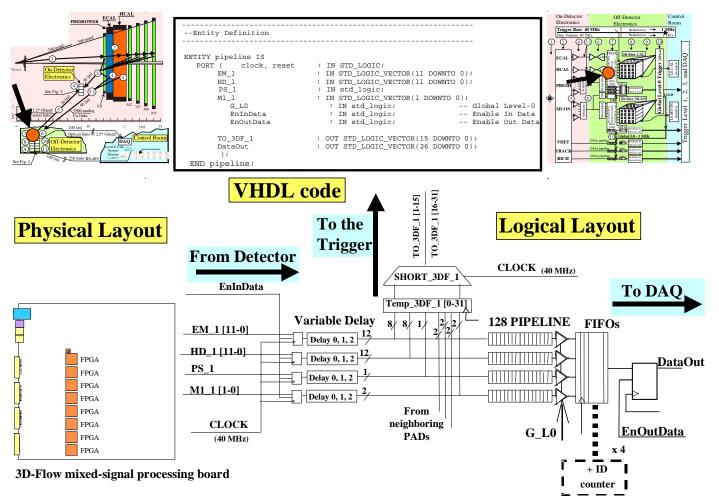

All sections and figures are related to Figure 8 in the following manner:

- Figures 9, 10, and 11: physical aspects of the logical elements shown in Figure 8.

- Section 2: functional information on the conceptual architecture of the 3D-Flow indicated by 8 in Figure 8.

- Section 3: physical implementation of the basic element 3D-Flow that was conceptually described in Section 2.

- Section 4: general information on fully programmable first level triggers as the part indicated by 8 in Figure 8.

- Section 6.1: physical implementation in 9U boards of what is indicated by the numbers 6, 7, 8, and 9 in Figure 8.

- Section 6.2: alternative detailed implementation of Section 6.1 with the information of the physical implementation in 9U boards of what is indicated by the numbers 7, 8, and 9 in Figure 8.

- Section 6.3: logical functions indicated by 7 in Figure 8.

- Sections 6.4, 6.5 and 6.6: relationship between physical and logical layout of what is indicated by 8 in Figure 8.

- Section 7: physical implementation in 9U crates of what is indicated by the numbers 6, 7, 8, 9, and 10 in Figure 8.

- Section 8: logical function indicated by 10 in Figure 8.

- Section 9: control signals distribution among what is indicated by 6, 7, 8, 9, and 10 in Figure 8.

- Section 11: description of the box to the right of Figure 8, L0 CAL (Level-0 Calorimeter real-time monitoring system). The other box, L0 MUON has the same functionality and implementation.

- Section 12: tools which allow simulation of the programmable system indicated in Figure 8 by 8, 9, and the L0 Calorimeter and Muon monitor.

# 2 THE 3D-FLOW: A SINGLE TYPE OF CIRCUIT FOR SEVERAL ALGORITHMS

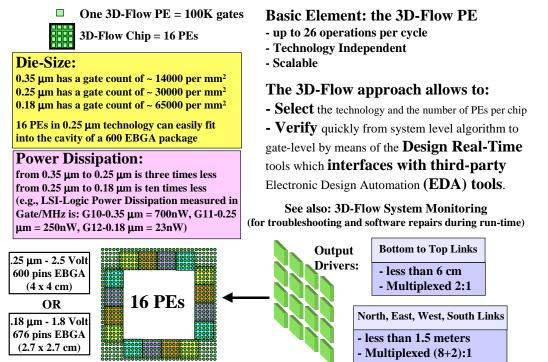

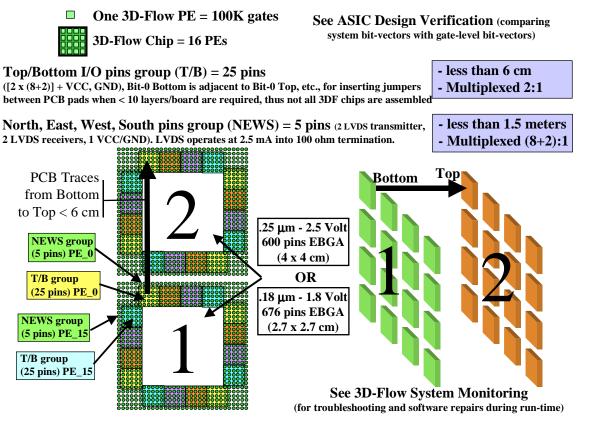

The system is based on a single type of replicated circuit called 3D-Flow processing element<sup>2</sup> (PE) consisting of about 100K gates. Several PEs can be put into a single component. The 3D-Flow PE circuit is technology-independent. Implementation with the current technology of 0.25  $\mu$ m which has a gate count of ~30K gates per mm<sup>2</sup> requires about 3 mm<sup>2</sup> of silicon per PE. A chip accommodating 16 PEs requires a silicon area of about 50 mm<sup>2</sup> in 0.25  $\mu$ m technology (leading to a chip @ 2.5 Volt, 600-pin EBGA, 4 cm x 4 cm) and about 25 mm<sup>2</sup> in 0.18  $\mu$ m technology available next year (leading to a chip @ 1.8 Volt, 676-pin EBGA, 2.7 cm x 2.7 cm). However, the later technology dissipates ten times less power with respect to the 0.25  $\mu$ m.

The main characteristics of the 3D-Flow<sup>3</sup> system architectures based on a single 3D-Flow component are the following:

#### 2.1 System level

#### Objective:

Oriented toward data acquisition, data movement, pattern recognition, data coding and reduction.

#### Design considerations:

- Quick and flexible acquisition and exchange of data, bi-directional with North, East, West, and South neighbors, unidirectional from Top-to-Bottom.

- Small on-chip area for program memory in favor of multiple processors per chip and multiple execution units per processor, data-driven components (FIFOs, buffers), and internal data memory. (Most algorithms that this system aims to solve are short and highly repetitive, thus requiring little program memory.)

- Balance of data processing and data movement with very few external components.

- Programmability and flexibility provided by download of different algorithms into a program RAM memory.

- Strong emphasis on modularity and scalability, permitting solutions for many different types and sizes of applications using regular connections and repeated components.

#### 2.2 System architecture

The goal of this parallel-processing architecture is to acquire multiple data in parallel (up to the maximum clock speed allowed by the latest technology) and to process them rapidly, accomplishing digital filtering on the input data, pattern recognition, data moving, and data formatting.

The system is suitable for "particle identification" applications in HEP (calorimeter data filtering, processing and data reduction, track finding and rejection).

The compactness of the 3D-Flow parallel-processing system in concert with the processor architecture (its I/O structure in particular) allows processor interconnections to be mapped into the geometry of sensors (such as detectors in HEP) without large interconnection signal delay, enabling real-time pattern recognition. This work originated by understanding the requirements of the first levels of triggers for different experiments, past, present, and future. A detailed study of each led to the definition of system, processor, and assembly architecture suitable to address their recognized common features. To maintain scalability and simplify the connectivity, a three-dimensional model was chosen, with one dimension essentially reserved for the unidirectional time axis and the other two as bi-directional spatial axes (Figure 1).

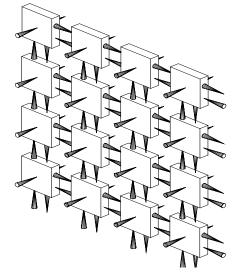

The system architecture consists of several processors arranged in two-orthogonal axes (called layers; see Figure 2), assembled one adjacent to another to make a system (called a stack; see Figure 3). The first layer is connected to the input sensors, while the last layer provides the results processed by all layers in the stack.

Data and results flow through the stack from the sensors to the last layer. This model implies that applications are mapped onto conceptual two-dimensional grids normal to the time axis. The extensions of these grids depend upon the amount of flow and processing at each point in the acquisition and reduction procedure as well as on the dimensionality of the set of sensors mapped into the processor layers.

Four counters at each processor arbitrate the position of the bypass/in-out switches (Top-to-Bottom ports. See Figure 25) responsible for the proper routing of data. Higher-dimensional models were considered too costly and complex for practical scalable systems, mainly due to interconnection difficulties.

#### 2.3 Processor architecture

The 3D-Flow processor is a programmable, data-stream pipelined device that allows fast data movements in six directions with digital signal-processing capability. Its cell input/output is shown in Figure 1.

#### Architecture (processor and system)

- Modularity (the same "logical unit," the 3D-Flow PE, replicated several times -- in a chip, on a board, or on a system)

- Powerful I/O

"logical unit" = 3D-Flow Processing Element (PE)

#### Figure 1. The 3D-Flow Processing Element (PE) or "logical unit."

The 3D-Flow can operate on a data-driven, or synchronous mode. In data-driven mode, program execution is controlled by the presence of the data at five ports (North, East, West, South, and Top) according to the instructions being executed. A clock synchronizes the operation of the cells. With the same hardware one can build low-cost, programmable first levels of triggers for a small and low-event-rate detector, or high-performance, programmable higher levels of triggers for a large detector. The multi-layer architecture and automatic by-pass feature from Top-to-Bottom ports allow for event input to be sustained at the processor clock rate, even if the actual algorithm execution requires many clock cycles, as described below.

The 3D-Flow processor is essentially a Very Long Instruction Word (VLIW) processor. Its 128-bits-wide instruction word allows for concurrent operation of the processor's internal units: Arithmetic Logic Units (ALUs), Look Up Table memories, I/O busses, Multiply Accumulate and Divide unit (MAC/DIV), comparator units, a register file, an interface to the Universal

Asynchronous Receiver and Transmitter (UART) used to preload programs and to debug and monitor during execution, and a program storage memory.

The high-performance I/O capability is built around four bi-directional ports (North, East, South, and West) and two monodirectional ports (Top and Bottom). All of the ports can be accessed simultaneously within the same clock cycle. N, E, W, and S ports are used to exchange data between processors associated with neighboring detector elements within the same layer. The Top port receives input data and the Bottom port transmits results of calculations to successive layers.

A built-in pipelining capability (which extends the pipeline capability of the system) is implemented using a "bypass mode." In bypass mode, a processor will ignore data at its Top port and automatically transmit it to the Top port of the processor in the next layer. This feature thus provides an automatic procedure to route the incoming events to the correct layer. Several 3D-Flow processing elements, shown in Figure 1, can be assembled to build a parallel processing system, as shown in Figure 2.

Figure 2. One layer (or stage) of 3D-Flow parallel processing.

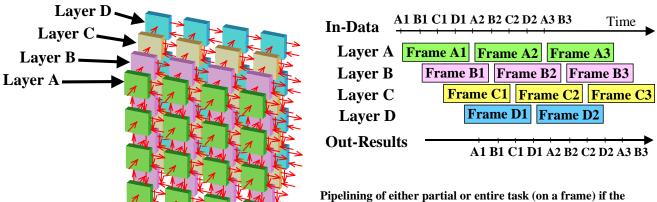

#### 2.4 Introducing the third dimension in the system

In applications where the processor algorithm execution time is greater than the time interval between two data inputs, one layer of 3D-Flow processor is not sufficient.

The problem can be solved by introducing the third dimension in the 3D-Flow parallel-processing system, as shown in Figure 3.

In the pipelined 3D-Flow parallel-processing architecture, each processor executes an algorithm on a set of data from beginning to end (e.g., the event in HEP experiments, or the picture in graphics applications).

Data distribution of the information sent by the external data sources as well as the flow of results to the output are controlled by a sequence of instructions residing in the program memory of each processor.

Each 3D-Flow processor in the parallel-processing system can analyze its own set of data (a portion of an event or a portion of a picture), or it can forward its input to the next layer of processors without disturbing the internal execution of the algorithm on its set of data (and on its neighboring processors at North, East, West, and South that are analyzing a different portion of the same event or picture. The portion of event or picture is called "Frame A1, Frame A2, etc.," in Figure 3.).

The programming of each 3D-Flow processor determines how processor resources (data moving and computing) are divided between the two tasks or how they are executed concurrently.

A schematic view of the system is presented in Figure 3, where the input data from the external sensing device are connected to the first layer of the 3D-Flow processor array.

The main functions that can be accomplished by the 3D-Flow parallel-processing system are:

- Operation of digital filtering on the incoming data related to a single channel;

- Operation of pattern recognition to identify events of interest; and

- Operations of data tagging, counting, adding, and moving data between processor cells to gather information from an area of processors into a single cell, thereby reducing the number of output lines to the next electronic stage.

In calorimeter trigger applications, the 3D-Flow parallel-processing system can identify patterns of energy deposition characteristic of different particles type, as defined by more or less complex algorithms, so reducing the input data rate to only a subset of candidates.

In real-time tracking applications, the system can perform pattern recognition, calculate track slopes, and intercepts total and transverse momenta as well.

No glue logic interface or MUX I/Os needed between SOC components

Pipelining of either partial or entire task (on a frame) if the algorithm cannot be partitioned (essential when the task needs to communicate with neighboring processors or due to the nature of the algorithm [e.g., presence of branches])

Figure 3. General scheme of the 3D-Flow pipeline parallel-processing architecture.

#### 2.5 The 3D-Flow architecture optimized features for the first levels of triggers.

The following list of Table 1 shows the most important features of the 3D-Flow that make it very efficient to solve algorithms of the first level of triggers in High Energy Physics.

| A Typical Level-0 Algorithm Requires:                                                                               | The 3D-Flow Architecture Offers:                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100% of the time during algorithm execution it is required to input data and output results.                        | Top and Bottom ports are: multiplexed only 2:1, propagating, by means of the by-pass switches, either input data or output results at each cycle. Outputs are required to drive only up to 6 cm.                   |

| Only 10% of the time of the algorithm execution it is required to exchange data with neighbors.                     | North, East, West, and South ports are: multiplexed 10:1, do not require many cables, have very low power consumption with LVDS (Low Voltage Differential Signaling) I/O requiring to drive only up to 1.5 meters. |

| Operation of comparing with different thresholds, finding local maximum.                                            | A special unit with 32 registers/comparators can compare 4 values, find their range, or find the local maximum, or the greater between pairs, all in one cycle.                                                    |

| Short programs.                                                                                                     | 128 words of program memory.                                                                                                                                                                                       |

| Lookup table to convert ADC values.                                                                                 | Four data memories, each for lookup tables of 256 locations of 16-bit, or for buffering.                                                                                                                           |

| Arithmetic and Logic operations<br>(multiplying by calibration constants,<br>adding to calculate cluster energies). | All Arithmetic, Logical and data move operations are provided by parallel<br>units executing up to 26 operations per cycle. (Including Multiply-<br>Accumulate and Divide at variable precision).                  |

Table 1. The 3D-Flow architecture optimized features for first-level trigger algorithms

## **3 A SINGLE TYPE OF COMPONENT FOR SEVERAL ALGORITHMS**

The fundamental concept of the 3D-Flow system, based upon the replication of a single, interconnecting component, can be maintained in spite of the rapid advances in Integrated Circuits technology. For this purpose, the 3D-Flow "System on a Chip" (SOC) complete circuit description is provided in generic VHDL in  $IP^4$  form, so that it can be implemented at any time using the technology of the day. This in turn will allow to achieve, at any moment in time, the best performance in terms of power dissipation, size, speed, and, consequently, cost.

SOCs (System On a Chip) utilizing IPs (Intellectual Property) Virtual-Components (VC) are redefining the world of electronics. A catalog<sup>5</sup>, of 200 VC IP's was introduced at DAC '98.

#### 3.1 The evolution of IC Design

The evolution of ICs is illustrated in Figure 4. All current indications and projections confirm that the evolution will continue to increase rapidly in the years to come. Furthermore, the traditional way of designing systems will change: the current productivity of about 100 gates per day (*EE Times, Oct. '98*) will need to improve substantially, in order to resist competition. The evolution of ICs reflects what is illustrated in Figure 4. Many statements in this regard have been reported by specialized

magazines. Using today's methodology, a 12-million-gate ASIC would require 500 person-years to develop, at a cost in excess of \$75M. Companies will not be able to afford this cost, unless one develops IP blocks in order to build System-On-a-Chip. Analog design retains its investment for several years, while digital design becomes outdated in about one year.

The 3D-Flow System digital design based on a single replicated circuit

- allows for implementation of the user's conceptual algorithm, at the gate circuit level, into the fastest High-Speed, Real-Time programmable system.

- retains its value because of its powerful 'Design Real-Time' tools that allow the user to quickly design, verify, and implement a System-On-a-Chip (SOC) based on a single replicated circuit (the 3D-Flow processing element [PE] in IP form [C++, VHDL, and netlist]), that can be targeted to the latest technology at any time.

| IC Design Complexi | ty (average co   | mponent size) |               |             |

|--------------------|------------------|---------------|---------------|-------------|

|                    | Current Industry |               | Forec         | cast        |

|                    | 1997             | 1998          | 1999          | 2001        |

| Logic Gates        | 300K             | 1M            | 5M            | 12M         |

| Technology         | $0.5\mu_m$       | $0.35\mu_{m}$ | $0.25\mu_{m}$ | $0.18\mu_m$ |

| Speed              | 1.4 x '96        | 1.4 x '97     | 1.4 x '98     | 1.4 x '2000 |

| Cost/100K gates    | \$25             | \$5           | ~ \$2         | ???         |

| <b>3D-Flow SOC</b> | 450K             | 1.7M          | 6.5M          | 13M         |

| (100K gates/PE)    | (4-PEs)          | (16-PEs)      | (64-PEs)      | (128-PEs)   |

#### Figure 4. The evolution of IC design.

#### 3.2 Technology-independent 3D-Flow ASIC

Figure 5 shows the main characteristics of the 3D-Flow chip that is technology-independent. As the technological performance increases<sup>6</sup>, the multiplexing of the I/O can also increase. For example the (8+2):1 of the LVDS (Low Voltage Differential Signaling) serial links can increase to 16:1 or (16+2):1 when the LVDS serial link speed reaches 1.2 Gbps or higher. (16 PEs, for example, requires a silicon area of about 50 mm<sup>2</sup> in 0.25  $\mu$ m technology, leading to a chip @ 2.5 Volt, 600-pin EBGA, 4 cm x 4 cm, while it requires about 25 mm<sup>2</sup> in 0.18  $\mu$ m technology that will be available next year, and it will lead to a chip @ 1.8 Volt, 676-pin EBGA, 2.7 cm x 2.7 cm. Please see the Web site of LSI-Logic<sup>6</sup> as an example of technology currently available).

Figure 5. Technology-independent 3D-Flow ASIC

## 4 FIRST-LEVEL TRIGGER ALGORITHMS

Typical first-level trigger algorithms at LHC<sup>7</sup> experiments need to sustain the input data rate at 40 MHz with zero dead time, providing a yes/no global level-0 (or level-1) trigger output at the same rate; need to exchange --for about 10% of the duration of the algorithm-- data with neighboring elements; need to find clusters with operations of multiply/accumulate; and need to have a special unit that should be a combination of registers/comparators capable of executing in one cycle operations such as ranging, local maximum, and comparing different values to different thresholds. While short, the first-level trigger algorithms need a good balance between input/output operation and several other operations of moving data, data correlation, arithmetic, and logical operation performed by several units in parallel. Typical operations also include converting ADC values into energies or a more expanded 16-bit nonlinear function that is quickly accomplished by lookup tables. The internal units of the 3D-Flow have all these capabilities, including powerful I/O.

The desired performance, programmability, modularity, and flexibility of the 3D-Flow<sup>8</sup> are represented schematically in Figure 6. With a 3D-Flow processor running an 80 MHz clock speed, it has been shown that the calorimeter trigger requirements can be met by a 3D-Flow system of 10 layers, each layer comprising about 6000 Processing Elements (PEs), one element per ECAL block (sometimes referred to as "trigger tower," that is corresponding to all signals from ECAL, HCAL, PreShower and Muon detectors contained in a specific view angle from the interaction pointEach PE executes the user's defined trigger algorithm on the information received from the detector, at the bunch crossing 40 MHz rate (requiring a time interval ranging from 100 ns to 300 ns, depending on the complexity of the algorithm.). The ten-layer stack is then followed by a data collection "pyramid," where the information from any trigger tower (3D-Flow input channel) where an event of interest was found is routed to a single exit point. The data routing that provides channel reduction is accomplished via the NEWS ports within a time of the order of a microsecond, depending on the size and number of channels in the system.

The details of algorithms devised to perform the selection process, schematically shown in Figure 6, and their realization within the 3D-Flow systems have been described elsewhere<sup>2, 9, 10, 11</sup>. The present document provides a detailed description of all the components, and their layout, required to build the 3D-Flow system appropriate for the implementation of the calorimeter trigger (the muon trigger implementation details cannot yet be fully defined, since the actual detector configuration is still under discussion, and it will be the subject of a future paper).

While utilizing existing technology in each individual step, the resulting system is very compact in the total number of crates (e.g., 6 crates for the calorimeter trigger) and is less costly than other proposed solutions <sup>12, 13</sup>. And this, while conserving the intrinsic properties of full programmability and ease of expansion.

The full simulation of the algorithm can be verified from the system level to each component gate level by comparing the bitvectors generated by system simulation tools and the tools provided by the Electronic Design Automation (EDA).

Figure 6. Overview of the use of the 3D-Flow System in particle identification in HEP.

## 5 LHCb LEVEL-0 TRIGGER OVERVIEW

#### 5.1 Physical Layout

The preferred layout for the LHCb<sup>11</sup> level-0 trigger is to have all decisions made in electronics racks located on the "balcony" at some 40 meters from the detector. In this configuration, the only link from the control room, located about 70 meters from the detector, to the level-0 trigger electronics is given by the trigger monitor, operating through slow control on RS-422 links. Figure 7 shows the path of the signals from the different sub-detectors to the electronics, and the corresponding time delays (the numbers identifying each step in Figure 7 correspond to the same numbers in Figure 8).

An alternative scheme would call for locating all the level-0 trigger electronics in the control room. This scheme would have the advantage of easier access for maintenance; its disadvantage is that it would be necessary to run longer cables which will require longer latency. What Follows is the first option having the level-0 trigger electronics on the balcony.

Another choice has to be made on whether to convert the signals from analog-to-digital on-detector or off-detector. The selection of one scheme instead of another will consequently require some changes in the electronics. The current preferred solution among the LHCb collaboration it seems to be the one which foresees a mixture of analog and digital signals to be received from the detector; however, for maximum flexibility, a 3D-Flow level-0 trigger system that foresees receiving signals from the detector solely in digital form is also reported (see Section 6.2 --3D-Flow digital processing board-- Option 2). LHCb current approach is more similar to that used in the Atlas<sup>14</sup> experiment, in which the analog signals are transported for about 60 meters and are converted to digital in a low-radiation area. On the contrary, the first-level trigger of the CMS experiment receives all digital information. The conversion is being made on-detector by means of the radiation-resistant QIE analog-to-digital converter (Q for charge, I for integrating, and E for range encoding), which was developed at Fermi National Laboratory.

After the particles have traveled from the interaction point to the calorimeter, and the signal is formed by the photomultipliers (steps 1 and 2), a minimum of analog electronic circuit with line driver will be installed close to the photomultiplier. The signal is then transported through a coaxial 17 position ribbon cable (part number AMP 1-226733-4) to the 3D-Flow mixed-signals processing board (shown in figure 12).

These analog signals are foreseen to be converted to 12-bit digital form with standard components such as Analog Device AD 9042<sup>15</sup>. For the analog signals available at the PreShower sub-detector it will be desirable, because of lower cost, to use a shorter cable set from the different sensors to a location where the signals can be grouped together in sets of 20 bits or more. The above analog signals, as well as the ones from the muon stations, are foreseen to be converted to only one-bit digital value. Once the digital signals have been grouped, they can be sent in digital form on standard copper cables (e.g. equalized cables AMP 636000-1), through one of the available serializers at 1.2 Gbps. (Serializers at 2.4 Gbps are also available; however, they are limited to 10 meters in copper or at longer distances in optical fiber and are more expensive). In case the radiation is too high where the transmitter (or serializer) has to be installed, radhard components<sup>16</sup> should be considered.

In the event the preferred solution by LHCb would be that of keeping the analog cables shorter than 10 meters (see Figure 7), since in LHCb there is a very low radiation (fewx100 rad/year @ 10m), than the entire 6 racks of front-end and level-0 calorimeter trigger can be moved to the top of the detector.

Figure 7. LHCb Level-0 Trigger - Physical Layout.

## 5.2 Logical Layout

The scheme of the entire Level-0 trigger system for the event selection ("trigger") for the LHCb<sup>11</sup> High Energy Physics experiment is summarized in Figure 8.

Figure 8 shows the logical function performed by the different signals and electronics previously shown in Figure 7 (see also the timing information indicated by the number inside the circle in Figure 7). It is divided into three sections. The section at the left shows the electronics and signals on the detector. The center section shows the electronics and signals in the racks located off-detector (where all decision electronics for the level-0 trigger are located). The section on the right shows the cables/signals carrying the information to the DAQ and higher-level triggering system that are received at the control room. In this scheme, only the monitoring electronics of the level-0 trigger is located in the control room.

In regard to the analog-to-digital front-end electronics for the preshower detector, the design assumes to receive 1-bit digital information from each preshower detector channel. Since the baseline solution described in the TP (see TP Chapter 10.2.3) foresees this electronics accommodating close to the multi-anode PMTs, a printed circuit board with the size of 9 cm x 9 cm is estimated to be used for each 16-channels PMT, on each of the 375 PMT installed on the preshower detector. The design of this section of electronics is described briefly in Appendix B.

Figure 8. LHCb Level-0 Trigger - Logical Layout.

The LHCb detector, consisting of several sub-components (ECAL, HCAL, PreShower, Muon, VDET, TRACK and RICH) monitors the collisions among proton bunches occurring at a rate of 40 MHz (corresponding to the 25 nsec bunch crossing rate). At every crossing, the whole information from the detector (data-path) is collected (indicated in the figure by the number 4), digitized (indicated by the number 6), synchronized and temporarily stored (indicated by 7) into digital pipelines (conceptually similar to 128 deep, 40 MHz shift registers), while the Trigger Electronics (indicated by 8 and 9), by examining a subset of the whole event data (trigger path), decides (indicated by 10) whether the event should be kept for further examination or discarded. In the LHCb design, the input rate of 40 Tbytes per sec<sup>11</sup> (see top of the figure), needs to be reduced, in the first level of triggering, to 1 Tbytes/sec, i.e. a 1 MHz rate of accepted events. The selection is performed by two trigger systems (indicated by 8) running in parallel, the Calorimeter Trigger, utilizing mainly the information from the ElectroMagnetic and Hadronic Calorimeters (ECAL and HCAL) to recognize high transverse momentum electrons, hadrons and photons; and the Muon Trigger, utilizing the information from five planes of muon detectors to recognize high transverse momentum muons.

The resulting global level-0 trigger accept signal (indicated by 10 in the figure) enables the data in the data-path to be stored first into a derandomizing FIFO and later to be sent through optical fiber links to the higher-level triggers and to the data acquisition (see in Figure 8 the signal Global L0 distributed to all front-end 128 bunch crossing "bx" pipeline buffers). Real-time monitoring systems (L0 CAL monitor and L0 MUON monitor) supervise and diagnose the programmable level-0 trigger from the distant control room.

#### 5.3 Electronic Racks (Functions/Locations)

Figure 9 shows the estimate of the type of electronics that will be needed on-detector for Level-0 trigger. Figure 10 shows the number and functionality of the crates and racks located off-detector that will be required to accommodate the level-0 electronics. A fully programmable calorimeter Level-0 trigger implemented with the 3D-Flow requires 6 crates (9U). This is to be compared with the, less flexible 2x2 trigger implementation option<sup>12</sup>, requiring 20 crates (9U), or with a third, HERA-B like solution<sup>13</sup> requiring 40 crates (9U). Figure 11 shows the monitoring system for the 3D-Flow calorimeter trigger. This, together with any other monitoring of the level-0 muon trigger and of the global level-0 decision unit, should be accommodated in the control room

Figure 10. Off-Detector Electronics for level-0 trigger.

Figure 11. Electronics in the Control Room for the Calorimeter Level-0 Trigger Monitoring.

## 6 A SINGLE TYPE OF BOARD FOR SEVERAL ALGORITHMS

The modularity, flexibility, programmability, and scalability of the 3D-Flow system is kept all the way from the component to the crate(s). This is valid also for the type of board used in the system. Only a single type of board is needed in a 3D-Flow system of any size. This board can change for each application from mixed signals analog and digital to a purely digital board, depending on the nature of the input signals received from the sensors.

Following are described a mixed-signal 3D-Flow processing board (option 1), and a purely digital processing board (option 2. The only difference among the two boards is the front-end electronics. In one case, there are preamplifiers and analog-todigital converters, in the second case there are high-speed optical fiber links.

The board design presented here, based upon an 80 MHz processor, accommodates 64 trigger towers and 10 processing layers. With a 16-bit wide word processor, such a board can sustain an input bandwidth of 10.24 Gbyte/s (80 MHz x 2 bytes x 64) and process the received information on each of the 64 channels with zero dead time and a real-time algorithm of the complexity up to 20 steps. (It should be considered that up to 26 different operations can be executed at each step, including efficient operations of data exchange with neighboring channels).

With today's technology, it is not a problem to feed a 9U x 5HP board from the front panel with digital information at 10.24 Gbyte/s, e.g., the information could be received by the board using currently available deserializer/receiver links from several vendors at 1.2 GHz. Possible choices for such deserializer devices include Hewlett Packard HDMP-1024<sup>17</sup>, HDMP-1034 @ 1.2 Gbps, AMCC quad serial backplane serializer/deserializer device with single and dual I/O S2064<sup>18</sup>/S2065 @ 1.25 GHz, and from VITESSE<sup>19</sup>). Alternatively, using the deserializer from AMCC-S3044<sup>20</sup>. @ 2.4 GHz (this device requires a minimum network interface processor that can be implemented in FPGA), Lucent Technologies<sup>21</sup> TC16-Type 2.5 Gb/s optical transmitter/receiver with 16 channels 155 Mb/s serializer/deserializer, or using links soon to become available for the short range at 10 GHz that are already available for the long range in telecommunications (see Lucent Technologies<sup>22</sup> and . or Nortel<sup>23</sup>) may also solve this problem.

Should the transmission distance exceed 30 meters @ 1.2 GHz (only 10 meters can be achieved with acceptable Bit Error Rate –BER-- for transmission over copper @ 2.4 Gbps), then the more expensive optical fiber receivers should be coupled to the components mentioned above. As one can notice from the type of components listed above, non all vendors provide devices with functions of deserializing/receiving/demultiplexing, separated from the functions of serializing/transmitting/multiplexing. The same situation occur when one of the above components has to be coupled with a fiber optic receiver. Also in this case we may find vendors that offer both functions (optical fibers receiver/transmitter) in a single component at a lower cost in some cases then the price of a component with a single functions. Some example of matching the previous deserializer/receiver with optical fiber receivers (or receiver/transmitter) are: Hewlett Packard HDMP-1024 with the optical transreceiver HFCT-53D5<sup>24</sup>, AMCC-S3044<sup>20</sup> with the fiber optic receiver SDT8408-R<sup>25</sup>, and Lucent Technologies deserializer TRCV012G5 with the optical fiber transreceiver Netlight1417JA. Connectors carrying several fibers are provided by many vendors (e.g. from Methode<sup>26</sup>).

The above deserializing/receiving components have matching components that can be supplied by the same vendors, which have the function of serializing/transmitting/multiplexing and optical fiber transmitter that are needed for transmission of the input data from the front-end electronics, or for the transmission of the output results from the 3D-Flow digital (or mixed-signal) processing board to the data acquisition system and higher-level triggers. A few examples are: deserializer HDMP-1034, matched with serializer HDMP-1032, deserializer HDMP-1024, matched with serializer HDMP-1022, deserializer AMCC-S3044<sup>20</sup>, coupled with the fiber optic receiver SDT8408-R<sup>25</sup>, matched with the serializer AMCC-S3043<sup>27</sup>, coupled with the fiber optic requires a minimum network interface processor that can be implemented in FPGA).

In the mixed signal application (option 1), only 80 analog signals (64 ECAL + 16 HCAL, since each HCAL is equivalent to an area of 4 ECALs), converted to digital with 12-bit resolution in addition to 192 bits (1 PreShower + 2 Pads from muon station 1 x 64) are received by each board every 25 ns. This is not saturating the bandwidth of the 32-bit x 64 channels = 2048 bits every 25 ns bunch crossing that the 3D-Flow system could sustain.

However, the front-end electronic FPGA chips on the same board described in detail in Section 6.3 (see Figure 16) increase the input bandwidth to the 3D-Flow system by formatting and generating the input trigger word to be sent to each of the 64 channels. More precisely, the FPGA trigger word formatter (see Section 6.3.5 and Figure 20) reduces the ECAL information from 12-bit to 8-bit, and increases by duplicating information to different channels (e.g. sending the same 8-bit HCAL information to each of the 4 subtended ECAL blocks, and sending the same 2-bit Pads to 4 neighboring blocks), in order to save some bit-manipulation instructions to the 3D-Flow processors.

#### 6.1 3D-Flow mixed-signal processing board (Option 1)

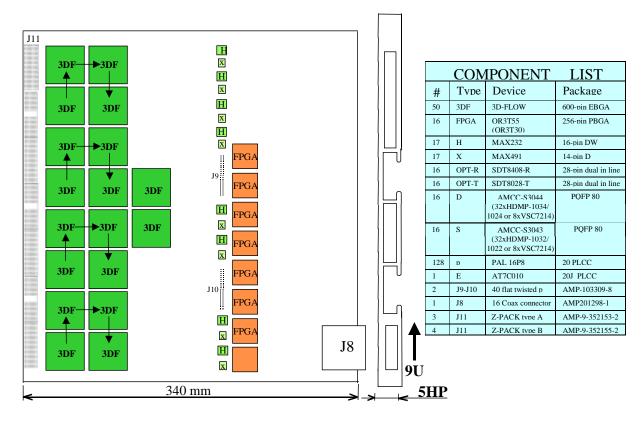

Features of the 3D-Flow mixed-signal processing board built-in standard 9U x 5HP x 340 mm dimensions (see Figures 12, and 13):

- Converts 80 analog inputs (ADC 12-bit resolution), and produce 4 copies of each HCAL digitized value;

- synchronizes 1152 inputs (16 x 4 x 12 bits ECAL, 16 x 12 bits HCAL, 16 x 4 x 1 PreSh, 16 x 4 x 2 Pads) every 25 ns;

- saves 1152 raw-data every 25 ns in a 128x1152 pipeline-stage digital buffer;

Figure 12. Mixed-signal processing board (front view).

Figure 13. Mixed-signal processing board (rear view).

- processes data received from 64 trigger towers (or data received at a continuous input data stream of 10 Gbyte/s) and sends to the global level-0 trigger the information (tower ID, bunch crossing ID, and energy) of the clusters that passed the level-0 trigger algorithm;

- receives the global level-0 trigger accepts and sends out the raw data of the corresponding accepted events;

- derandomize accepted raw data into a FIFO;

- all 3D-Flow inter-chip Bottom-to-Top port connection are within the board (data are multiplexed 2:1, PCB traces are shorter than 6 cm); all 3D-Flow inter-chip North, East, West, and South port connections between boards and crates are multiplexed (8+2):1 and are shorter than 1.5 meters;

- communicate with the host monitoring/control system via 16 RS-422 links to downloads user's algorithms into the processors and upload performance data (the status of all processors during 8 consecutive cycles) for monitoring purposes;

- communicates with the host monitoring/control system to download the FPGA programming, to adjust signal synchronization, pipeline stages, FIFO buffer, and trigger word formatter;

- communicates through 160 LVDS<sup>28</sup> links to North, East, West, and South neighboring boards.

What follows is a description of the board with its component list and assembly information.

The 3D-Flow mixed-signal processing board has on the front panel:

- three connectors for receiving digital raw data from the PreShower and muon M1 detectors through six copper twisted pair links at 1.2 Gbps. The receiver from Hewlett Packard HDMP-1034 (or HDMP-1024, dimension: 23 mm x 17 mm) could be used;

- five 17-conductor coaxial ribbon cables<sup>29</sup> for analog input (see Figure 12) from the electromagnetic, hadronic calorimeter, and from the control signal (reset, control A1, clear, clock, and global level-0 accept);

- 17 bidirectional RS-422 links for monitoring the on-board 3D-Flow system and loading different circuits into the FPGA;

- one RJ45 connector carrying four high-speed LVDS output signals to the global level-0 trigger decision unit;

- one optical fiber carrying out raw data relative to the event accepted by the level-0 trigger decision unit (e.g., Hewlett Packard transmitter at 1.2 Gbps HDMP-1022 (dimension: 23 mm x 17 mm) coupled with the fiber optic transreceiver HFBR-53D5 (dimension: 39.6 mm x 25.4 mm).

On the rear of the board are assembled alternately four 200-pin AMP-9-352153-2<sup>30</sup> connectors with three 176-pin AMP-9-352155-2<sup>30</sup> connectors. The latter connectors have a key for mechanical alignment to facilitate board insertion. Of these, 1280 pins carry LVDS signals to neighboring 3D-Flow chips residing off-board in the North, East, West, and South direction; 48 pins are used for power and ground.

Starting from the left of the board, we have 80 analog preamplifiers P (half of the components are on the rear of the board as shown in Figure 13), 80 analog-to-digital converters A (e.g., Analog Device<sup>15</sup> AD9042 converting each analog input channel to 12-bit at 40 MHz). The converted data are then combined with the other digital information received from the other detectors (PreShower and muon stations) into 16 FPGAs (4 channels fit into an ORCA<sup>31</sup> 256-pin BGA OR3T30) for the purpose of synchronization, pipelining, derandomizing, and trigger word formatting.

Formatted data are then sent to the processor stack (see Figures 23, and 24), to be picked by the first available layer, according to the setting of the bypass switches (see Figure 25), where the trigger algorithm is then executed.

At the bottom of the stack (see Figure 24), the first layer of the pyramid checks whether a valid particle (electron, hadron, or photon) was found.

The entire board (64 channels) is designed to send to the global trigger decision unit an average of 40-bits of information of clusters validated by the trigger algorithm (tower ID, time stamp, and energies) at each bunch crossing, through four LVDS<sup>6</sup> links at 400 Mbps on the J1 connector.

If the detector has higher occupancy so that any region of 64 channels could be expect to transmit to the global level-0 decision unit more than 40-bit per bunch crossing, then it would be sufficient to select a higher-speed link (e.g., 1.2 Gbps). If the occupancy is still higher, the number of output links to the global trigger decision unit can be increased to the required level.

If, on the other hand, 40-bit per bunch crossing per group of 64 were sufficient, then it would be simpler not to use the National Semiconductor serializer DS92LV1021, but rather have the North, East, West, or South ports of the 3D-Flow chip driver send the information directly to the global level-0 decision unit. In the present board, these serializer chips from National Semiconductor have been considered in order to make a conservative choice in terms of driving capabilities to three meters, while the 3D-Flow chip is required to drive only 1.5 meters on the LVDS I/O.

The board consist of surface-mounted devices assembled on both sides, with some free space not covered by components.

#### 6.2 3D-Flow digital processing board (Option 2)

The digital processing board carries on the motherboard 16 high-speed receiver links at 2.4 Gbps (e.g., the set from AMCC- $S3044^{20}$  and the SDT8408- $R^{23}$  optical fiber receiver, which contains 16 sockets for mezzanine boards with the same set of

components, or with the transmitter set AMCC-S3043<sup>24</sup> and the SDT8028-T<sup>23</sup> (these devices require a minimum network interface processor that can be implemented in FPGA).

The user can install as many mezzanines as required (up to 16) for the application in order to optimize the cost. For example, one could use 16 x receivers set on the mother board to sustain a rate of data input to the board of 5 Gbyte/s, and install 16 x transmitter mezzanine boards that provide 5 Gbyte/s output. Another application may need instead to install 15 x receiver mezzanine boards that together with the 16 on-board receivers provide 9.92 Gbyte/s input bandwidth, and only one transmitter mezzanine board for 320 Mbyte/s output data. This configuration will satisfy many high-energy physics experiments where the real-time trigger algorithm achieves a substantial reduction.

As another example, the CMS calorimeter level-1 trigger<sup>32</sup> (currently implemented in 19 crates (9U) using a different approach, while it will require only 5 crates (9U) if the 3D-Flow approach would be used), requires to receive only 18-bits from each trigger tower (electromagnetic, hadronic, fine grain, and characterization bit). Thus only 5 additional mezzanine fibers and receiver modules must be installed. One board can process 64 trigger towers and send to the global level-1 trigger decision unit the particles ID, time stamp, and energy information of the particles validated locally by the trigger algorithm. Subsequently, it can provide the raw-data of the particles validated by the global level-1 trigger. This scheme has the advantage of flexibility: if the experiment later requires not only changing the level-0 (or level-1) trigger algorithm, but also increasing the number of bits (information) used in the level-0 (or level-1) trigger algorithm, this can be done without redesigning the hardware. In the case of the CMS calorimeter trigger algorithm, by using the digital processing board of the 3D-Flow approach, the user can in the future increase the number of bits from each trigger tower from 18 to 31 before being required to redesign the hardware.

Features of the 3D-Flow digital processing board, built-in standard 9U x 5HP x 340 mm size (see Figures 14 and 15):

- Inputs 1024 digital inputs and outputs 1024 digital outputs every 25 ns, or any combination of I/O having a total of 2048 I/Os and a minimum of 1024 inputs every 25 ns;

- synchronizes up to 2048 inputs every 25 ns from different detectors (electromagnetic, hadronic, PreShower, and M1)

- saves up to 2048 raw-data every 25 ns in a 128 x 2048 pipeline-stage digital buffer;

- processes data received from 64 trigger towers (or data received at a continuous input data stream of 9.92 Gbyte/s) and sends to the global level-0 (or level-1) trigger the information (trigger tower ID, time-stamp, and energies) of particles that passed the level-0 trigger algorithm;

- receives the global level-0 trigger accepts and sends out the raw data of the corresponding accepted events;

- derandomizes accepted raw data into FIFO;

- all 3D-Flow inter-chip Bottom-to-Top port connection are within the board (data are multiplexed 2:1, PCB traces are shorter than 6 cm); all 3D-Flow inter-chip North, East, West, and South ports connections between boards and crates are multiplexed (8+2):1 and are shorter than 1.5 meters;

- communicate with the host monitoring/control system via 16 RS-422 links to download user's algorithms into the processors and upload performance data (the status of all processors during 8 consecutive cycles) for monitoring purposes

- communicates with the host monitoring/control system to download the FPGAs programming, to adjust signals synchronization, pipeline stages, FIFO buffer and trigger word formatter;

- communicates through 160 LVDS links to North, East, West, and South neighboring boards.

What follows is a description of the board with its component list and assembly information.

- The 3D-Flow digital processing board has on the front panel:

- 16 optical fibers of receivers, each at 2.4 Gbps installed on the mother board and 16 optional optical fibers (transmitter or receiver) installed on the mezzanine boards. (receiver SDT8408-R<sup>25</sup>, dimension: 15.24 mm x 36.4 mm, with the deserializer AMCC-S3044<sup>20</sup>, dimension: 17 mm x 17 mm, both at 2.5 Gbps and transmitter SDT8028-T<sup>25</sup>, dimension: 15.24 mm x 36.4 mm, with the serializer AMCC-S3043<sup>27</sup>, 17 mm x 17 mm. (These devices require a minimum network interface processor that can be implemented in FPGA).

- 17 bidirectional RS-422 links for monitoring the on-board 3D-Flow system and loading different circuits into the FPGAs;

- one RJ45 connector carrying four high-speed LVDS output signals to the global level-0 trigger decision unit.

On the rear of the board are assembled alternately four 200-pin AMP-9-352153-2<sup>30</sup> connectors with three 176-pin AMP-9-352155-2<sup>30</sup> connectors. The latter connectors have a key for mechanical alignment to facilitate board insertion. Of these, 1280 pins carry LVDS signals to neighboring 3D-Flow chips residing off-board in the North, East, West, and South direction; 48 pins are used for power and ground.

The mezzanine board is built with four PAL16P8 (high-speed, 5n pin-to-pin, or fast PLD) for the purpose of demultiplexing the 16-bit at 155 MHz provided by the AMCC-S3044<sup>20</sup> into 32-bit at 77.5 MHz. This additional PALs are needed at least until next year when the FPGAs at 160 MHz will become available and the signals from the AMCC chip could be sent directly to the

Figure 14. Digital processing board (front view).

Figure 15. Digital processing board (rear view).

FPGA chip. The reason for installing the 4 PAL on the mezzanine board is to lower the high frequency through connectors (77.5 MHz instead of 155 MHz). This will allow to use lower cost connectors to be used.

The digital data (from the electromagnetic and hadronic calorimeter, preshower, and muon) are sent into 16 FPGAs (4 channels fit into an ORCA<sup>31</sup> 256-pin BGA OR3T30) for the purpose of synchronization, pipelining, derandomizing, and trigger word formatting.

Formatted data are then sent to the processor stack (see Figures 23, and 24), to be picked by the first available layer, according to the setting of the bypass switches (see Figure 25), where the trigger algorithm is then executed. At the bottom of the stack, the first layer of the pyramid checks whether a valid particle (electron, hadron, or photon) was found.

The output of the particle found locally by the trigger algorithm (tower ID, time stamp, and energies) are sent out to the global level-0 decision unit through an RJ45 connector carrying four  $LVDS^6$  links at 400 Mbps. The same consideration applies to this board that was made for the mixed-signal processing board described in Section 6.1 on the number of bits sent to the global level-0 decision unit that is related to the detector occupancy.

The raw data of the events validated by the global level-0 trigger are sent out to the higher-level trigger system and DAQ, through the installed transmitter mezzanine boards. The necessary number of transmitter mezzanine boards should be installed in order to sustain the volume of raw data information to be sent out.

Boards contain surface-mounted devices assembled on both sides, with some free space not covered by components.

#### 6.3 Front-end Signal Synchronization/pipelining/derandomizing/trigger word formatter

The complete detailed study for the overall level-0 front-end electronics has been performed and described elesewhere<sup>33</sup>. Detailed circuits that can be downloaded in the ORCA OR3T30 FPGA are provided in the above referenced document, together with testbenches for easy verification of the correlation between signals and their timing performance.

For the mixed-signal processing board, after the task of amplification and conversion of analog signals to digital by means of an ADC such as Analog Devices AD9042<sup>15</sup> converting to 12-bit at 40 MHz, all digital information is sent to 16 FPGAs. Each FPGA can implement all functions described below for four channels out of 64 channels in a board. The study has been made referring to the component from Lucent Technologies ORCA OR3T55<sup>31</sup> with 256-pin BGA, dimension 27 mm x 27 mm.

The digital information relative to four trigger towers is sent to the input of one FPGA. If a PAD from the muon station is used by more than one trigger tower, it will be sent to all the appropriate FPGA units.

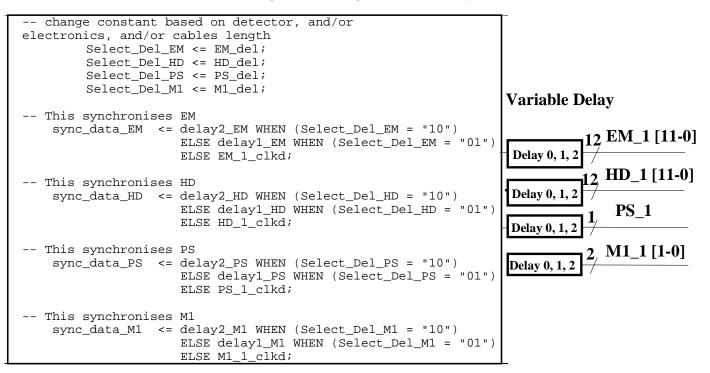

All data are strobed into a register inside the FPGA at the same time; however, the present design allow for the possibility that data from different detectors (e.g., muon Pad vs. ECAL) be out of phase by one or two bunch crossings.

Next, a delay from 0 to 2 clock counts at each bit received at the input of the FPGA needs to be inserted. This function, called "variable delay," is shown in Figures 16, 18, and 19.

For each channel we have, then, 12-bit information from the electromagnetic calorimeter, 12-bit information from the hadronic calorimeter, 1-bit information from the preshower, and 2-bit information from the muon pad chamber, for a total of 27-bits per input channel.

The above 27-bits input channels need to be stored into a level-0 pipeline buffer of 128 clocks (or bunch crossings) while the trigger electronics verifies whether the event should be retained or rejected. This function is called "128 pipeline." (See Figure 21)

When an event is accepted, the global level-0 trigger decision unit sends a signal to all the "128 pipeline" bits buffer to move the accepted bit (corresponding to an accepted event) to a derandomizing FIFO buffer (see Figure 22). This function is called "FIFO." For each channel we will have a 27-bit FIFO containing the full information relative to the accepted event. Even though the whole process is synchronous, it is safer to extend the width of the FIFO in each FPGA. At present, 8-bit has been reserved for the time-stamp bunch-crossing counter, however, the length of this field is defined in the configuration file, and can be changed at any time

Each FPGA handles the information of four trigger tower channels, memorizes the information for 128 clock cycles, stores the information relative to the accepted events (at an average of 1 MHz) into 32-bit deep (this parameter can be changed at any time), 80-bit wide FIFO. The width of the output FIFO in each FPGA is calculated as follows:  $4 \times 12$ -bit electromagnetic, 12-bit hadronic,  $4 \times 1$ -bit preshower,  $4 \times 2$ -bit PADs of muon station, and 8-bit time-stamp from a bunch crossing counter that will allow one to verify partial event information at different stages of the data transmission (optical fibers, deserializer, etc.). Thus for each accepted event, each FPGA will send 80-bit through the serializer and the optical fiber to the upper level trigger and DAQ.

A strobe signal received from the upper level decision units and DAQ (called EnOutData in Figures 16 and 22) will read all output FIFOs from the FPGAs at an estimated rate of 1 MHz.

Besides the synchronization, 128-pipeline storage, and derandomization of the full data path, it is also necessary to generate the trigger word to be sent to the 3D-Flow trigger processor. In order to save some 3D-Flow bit-manipulation instruction, the function of formatting the input trigger word can also be implemented into the FPGA (see Figure 20).

- At present, the input trigger word is defined as:

- 8-bit electromagnetic calorimeter

- 8-bit hadronic calorimeter

- 1-bit preshower

- 8-bit Pad from muon station M1.

Obviously, the format could be redefined at any time by reprogramming the FPGA through the RS-422 link. Following are the details of the functions listed above written in "generic VHDL" code suitable to several FPGAs or ASICs. Likewise a breakdown of the above functions mapped to the ORCA<sup>31</sup> Programmable Function Units (PFUs) is also provided.

#### Figure 16. Front-end signal synchronization, pipelining, derandomizing, and trigger word formatting.

#### 6.3.1 Level-0 front-end, VHDL coding of the I/O and signals definition

For each of the units shown in Figure 16, its corresponding excerpt of the VHDL code is provided as follows (the complete VHDL code with the equivalent synthetized version for FPGA OR3T30 and the relative test bench are provided in reference 33)..

The design is synchronous. All inputs and outputs are registered with the clock (to avoid code repetition the registering of input and output are not shown for all I/Os in this document; however, there are two examples, one registering the input data on the rising edge, another registering the output data).

This code is implementing one out of the 64 trigger tower channels on the board. The other channels will be identical except for the change of the signal name. In addition, there is the extension of the time-stamp bunch crossing counter to the raw-data output FIFO accepted by the global trigger decision unit. The trigger word is going out of the FPGA as 8-bit every 6.25 ns, since the Top port of the 3D-Flow is multiplexed 2:1.

Table 2. VHDL code for the definition of the architecture of the front-end circuit.

```

_____

-- file name : lhcb_FE.vhd

___

author : Dario Crosetto

--

-- project : LHCb

-- date

: 2/12/99

-- purpose : This file implements the front-end signals synchronization,

_ _

pipelining, derandomizing, trigger word formatter.

_ _

The initial code is for one trigger channel (4 trigger

--

channels can be accommodated into an OR3T30 FPGA)

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.std_logic_arith.ALL;

_____

--Entity Definition

-----

ENTITY pipeline IS

clock, reset : IN STD_LOGIC;

1 : IN STD_LOGIC_VECTOR(11 DOWNTO 0);

PORT (

EM_1

HD_1

: IN STD_LOGIC_VECTOR(11 DOWNTO 0);

: IN std_logic;

PS 1

: IN STD_LOGIC_VECTOR(1 DOWNTO 0);

M1 1

: IN std_logic;

-- Global Level-0

G LO

: IN std_logic;

-- Enable In Data

EnInData

: IN std_logic;

-- Enable Out Data

EnOutData

TO_3DF_1

: OUT STD_LOGIC_VECTOR(15 DOWNTO 0);

DataOut

: OUT STD_LOGIC_VECTOR(26 DOWNTO 0);

);

END pipeline;

_____

--ARCHITECTURE Definition

_____

ARCHITECTURE rtl OF pipeline IS

CONSTANT PS_del : std_logic_vector(1 DOWNTO 0) := "10"; --select delay 2

CONSTANT HD_del : std_Logic_vector(1 DOWNTO 0) := "00"; --select delay 0

CONSTANT EM_del : std_logic_vector(1 DOWNTO 0) := "00"; --select delay 0

CONSTANT M1_del : std_logic_vector(1 DOWNTO 0) := "01"; --select delay 1

SIGNAL Select_del_EM : std_Logic_vector(1 DOWNTO 0);

SIGNAL Select_del_HD : std_Logic_vector(1 DOWNTO 0);

SIGNAL

Select_del_HD

. Std_Logic_vector(1 DOWNTO 0);

SIGNAL

Select_del_PS

: std_Logic_vector(1 DOWNTO 0);

SIGNAL

Select_del_M1

: std_Logic_vector(1 DOWNTO 0);

SIGNAL

EM_1_clkd

: STD_LOGIC_VECTOR(11 DOWNTO 0);

SIGNAL

HD_1_clkd

: STD_LOGIC_VECTOR(11 DOWNTO 0);

SIGNAL

PS_1_clkd

: STD_LOGIC_VECTOR(11 DOWNTO 0);

SIGNAL

M1_1_clkd

: STD_LOGIC_VECTOR(1 DOWNTO 0);

SIGNAL

M1_1_clkd

: STD_LOGIC_VECTOR(11 DOWNTO 0);

SIGNAL

Delay1_EM

: STD_LOGIC_VECTOR(11 DOWNTO 0);

: STD_LOGIC_VECTOR(11 DOWNTO 0);

: STD_LOGIC_VECTOR(11 DOWNTO 0);

: STD_LOGIC_VECTOR(11 DOWNTO 0);

: STD_LOGIC_VECTOR(11 DOWNTO 0);

: STD_LOGIC;

: STD_LOGIC;

: STD_LOGIC / VECTOR(1 DOWNTO 0);

: STD_LOGIC_VECTOR(1 DOWNTO 0);

SIGNAL Delay2_EM

SIGNAL Delay1_HD

SIGNAL Delay2_HD

SIGNAL Delay1_PS

SIGNAL Delay2_PS

SIGNAL Delay1_M1

STD_LOGIC_VECTOR(1 DOWNTO 0);

STD_LOGIC_VECTOR(31 DOWNTO 0);

STD_LOGIC_VECTOR(15 DOWNTO 0);

STD_LOGIC_VECTOR(11 DOWNTO 0);

STD_LOGIC_VECTOR(11 DOWNTO 0);

SIGNAL Delay2_M1

SIGNAL TEMP_3DF_1

SIGNAL SHORT_3DF_1

SIGNAL sync_data_EM

SIGNAL sync_data_HD

STD_LOGIC;

STD_LOGIC;

STD_LOGIC_VECTOR(1 DOWNTO 0);

STD_LOGIC_VECTOR(127 DOWNTO 0);

STD_LOGIC_VECTOR(127 DOWNTO 0);

SIGNAL sync_data_PS

SIGNAL sync_data_M1

SIGNAL PIPE_EMO

SIGNAL PIPE_EM1

. . . .

SIGNAL PIPE_EM11

: STD_LOGIC_VECTOR(127 DOWNTO 0);

: STD_LOGIC_VECTOR(127 DOWNTO 0);

: STD_LOGIC_VECTOR(127 DOWNTO 0);

SIGNAL PIPE_HD0

SIGNAL PIPE_HD1

```

| SIGNAL | PIPE_HD11  | : STD_LOGIC_VECTOR(127 DOWNTO 0); |

|--------|------------|-----------------------------------|

| SIGNAL | PIPE_PS    | : STD_LOGIC_VECTOR(127 DOWNTO 0); |

| SIGNAL | PIPE_M1_0  | : STD_LOGIC_VECTOR(127 DOWNTO 0); |

| SIGNAL | PIPE_M1_1  | : STD_LOGIC_VECTOR(127 DOWNTO 0); |

| SIGNAL | TEMP_OPIPE | : STD_LOGIC_VECTOR(26 DOWNTO 0);  |

| SIGNAL | TO_IN_FIFO | : STD_LOGIC_VECTOR(26 DOWNTO 0);  |

|        |            |                                   |

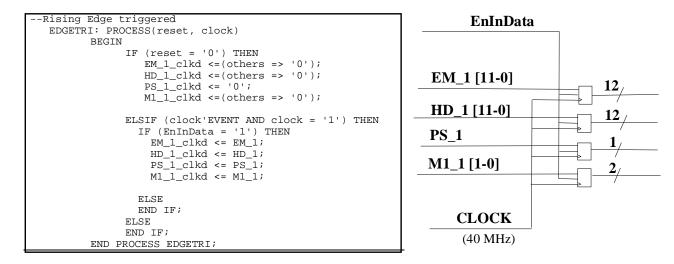

#### 6.3.2 Level-0 front-end, VHDL coding of registering the input data on rising edge

Figure 17. VHDL code and graphical representation of registering input data.

#### 6.3.3 Level-0 front-end, VHDL coding of the updating contents of variable delays

| adding delays<br>ADD_DLY: PROCESS (clock, reset)<br>BEGIN<br>IF (reset = '0') THEN<br>delay1_EM <=(othe<br>delay2_EM <=(othe<br>delay2_HD <=(othe<br>delay2_HD <=(othe<br>delay1_PS <= '0';<br>delay2_PS <= '0';<br>delay2_PS <= '0';<br>delay2_M1 <= "00"<br>ELSIF (clock'EVENT AND co<br>delay1_EM <= EM_1<br>delay2_EM <= dela<br>delay1_HD <= HD_1<br>delay2_HD <= dela<br>delay1_PS <= PS_1<br>delay2_PS <= dela<br>delay1_M1 <= M1_1<br>delay2_M1 <= dela | rs => '0');<br>rs => '0');<br>rs => '0');<br>;<br>;<br>clock = '1')<br>_clkd;<br>y1_EM;<br>_clkd;<br>y1_HD;<br>_clkd;<br>y1_PS;<br>_clkd; |