## DISSERTATION

## ON A MULTIPROCESSOR COMPUTER FARM FOR ONLINE PHYSICS DATA PROCESSING

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

> eingereicht an der Technischen Universität Wien Technisch-Naturwissenschaftliche Fakultät

> > von

# Nikolaos J. Sinanis

24 Les Erables, F-01710 Thoiry, Frankreich

Matrikelnummer: 9327425

geboren am 27 Mai 1965 in Athen, Griechenland

Genf, im 23 März 1999

# Contents

|   | Contents                                        | 1  |

|---|-------------------------------------------------|----|

|   | Kurzfassung                                     | 5  |

|   | Abstract                                        | 7  |

|   | Preface                                         | 9  |

|   | Acknowledgements                                | 13 |

| 1 | Physics Experiments and Data Acquisition        | 14 |

|   | 1.1 Elementary Particles and Their Interactions | 14 |

|   | 1.2 Particle Physics Experiments                | 15 |

|   | 1.3 The Large Hadron Collider (LHC).            |    |

|   | 1.4 The CMS Detector                            | 18 |

|   | 1.5 The CMS Trigger and DAQ System              | 19 |

|   | 1.5.1 The Level-1 Trigger (LV1)                 |    |

|   | 1.5.2 Data Acquisition Architecture             | 22 |

|   | 1.5.3 Event Builder Architecture                |    |

|   | 1.5.4 High-level Triggers                       |    |

|   | 1.5.5 On-line Computing Services                |    |

|   | 1.6 Summary of CMS DAQ Parameters               | 24 |

| 2 | <b>Event Building and Filtering Systems</b>     | 26 |

|   | 2.1 Event Builder                               | 26 |

|   | 2.1.1 Read-out Dual Port Memories (RDPM)        | 27 |

|     | 2.1.2   | Event Builder Communication Network | 29 |

|-----|---------|-------------------------------------|----|

|     | 2.1.3   | The Switch-to-Farm Interface (SFI)  | 33 |

|     | 2.1.4   | Event Manager (EVM)                 | 34 |

| 2.2 | The E   | vent Filter Farm (EFF)              | 35 |

|     | 2.2.1   | Architecture                        | 35 |

|     | 2.2.2   | Scheduling                          | 36 |

|     | 2.2.3   | Control and Management              | 36 |

|     | 2.2.4   | Alternative Solutions               | 37 |

| 2.3 | The E   | vent Filter Unit (EFU)              | 37 |

|     | 2.3.1   | Architecture                        | 38 |

|     | 2.3.2   | I/O Interfaces                      | 38 |

| 2.4 | Filteri | ng Software                         | 39 |

## **3** System Architectures

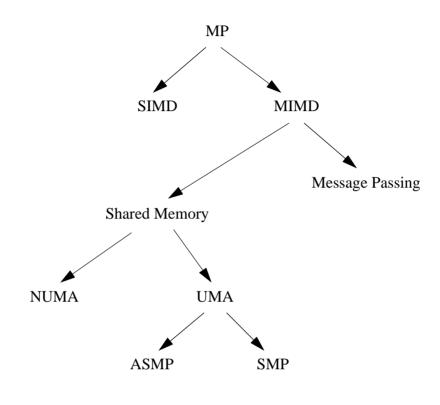

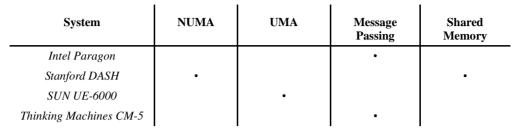

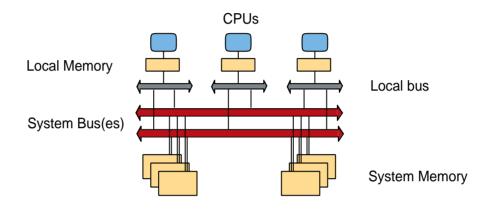

| 3.1 Multiprocessor Architectures |

|----------------------------------|

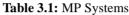

| 3.1.1 Symmetric Multiprocessors  |

| 3.2 Microprocessors              |

| 3.3 Memories                     |

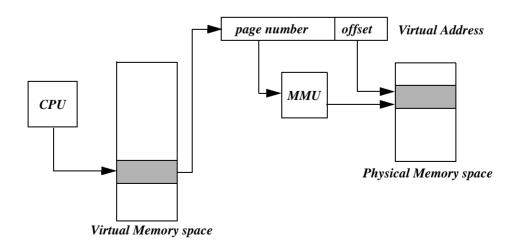

| 3.3.1 Virtual Memory             |

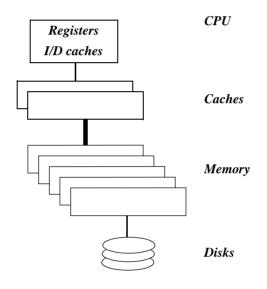

| 3.3.2 Memory Hierarchies 47      |

| 3.3.3 Cache Memory Systems       |

| 3.3.4 Memory Models 50           |

| 3.4 System Networks              |

| 3.4.1 Bus Interconnections       |

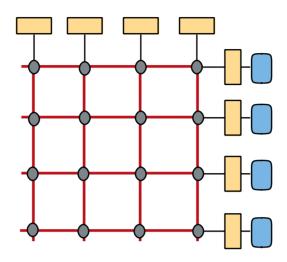

| 3.4.2 Cross-bar Interconnections |

# 4Performance Aspects and Evaluation Methods544.1 Performance of SMP Systems54

| 4.1.1     | Interconnection Performance    | . 55 |

|-----------|--------------------------------|------|

| 4.1.2     | SMP Operating Systems Aspects  | . 58 |

| 4.2 Perfo | rmance Modeling and Evaluation | . 61 |

| 4.2.1     | Mathematical Modeling          | . 62 |

| 4.2.2     | Simulations                    | . 64 |

| 4.2.3     | Benchmarks and Measurements    | . 66 |

| 4.3 Summ  | nary                           | . 68 |

# 5Farm Simulations695.1 DAQ Simulation Model Description69

41

| 1  |

|----|

| 73 |

| 74 |

| /4 |

| 75 |

| 6  |

| 6  |

| 8  |

| 8  |

| 8  |

| 9  |

| 9  |

| 80 |

| 80 |

| 31 |

| 32 |

| 33 |

| 39 |

|    |

# EFU Prototype Environment

| 6.1 | SFI E  | mulation                               |

|-----|--------|----------------------------------------|

|     | 6.1.1  | Network layer                          |

|     | 6.1.2  | Fragment Management Layer              |

|     | 6.1.3  | Filter API Layer                       |

| 6.2 | Setup  | Description                            |

|     |        | Event Fragment Data Model              |

|     | 6.2.2  | SFI Emulator Implementation            |

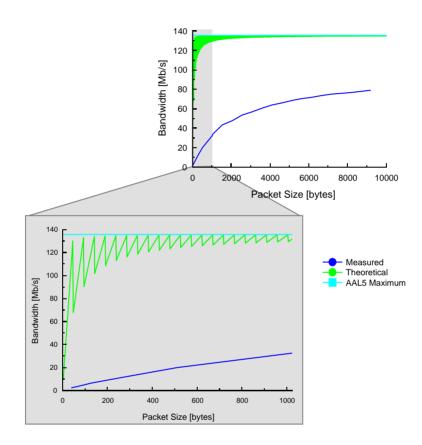

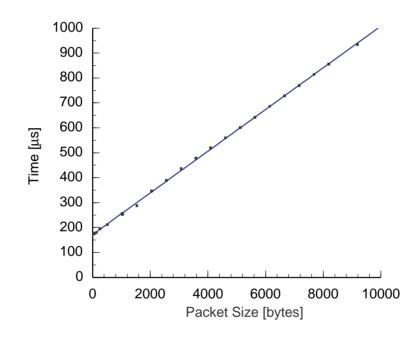

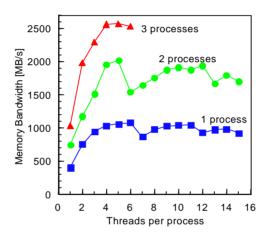

| 6.3 | ATM    | Performance                            |

|     | 6.3.1  | NIC Performance                        |

|     | 6.3.2  | Host Hardware and Software Performance |

| 6.4 | SFI E  | mulator Performance Measurements       |

|     | 6.4.1  | Contention Analysis 104                |

| 6.5 | Perfor | mance Considerations                   |

|     | 6.5.1  | NIC and Host Related                   |

|     | 6.5.2  | SFI Emulator                           |

| 6.6 | Summ   | nary                                   |

|     |        |                                        |

# 7 Farm Scaling 113 7.1 Scaling Parameters 113

|   | 7.1.1<br>7.1.2<br>7.1.3<br>7.1.4 | Event Builder SizeNumber of EFU and ProcessorsI/O BandwidthProcessor Performance                         | 115<br>116 |

|---|----------------------------------|----------------------------------------------------------------------------------------------------------|------------|

|   | 7.2 Scalir<br>7.2.1<br>7.2.2     | Ing Scenarios         LV1-trigger Maximum Rate         Effect of the LV2 Rejection Factor         lusion |            |

| 8 | Conclus                          | ions and Prospects                                                                                       | 124        |

|   | 8.1 Impac                        | ct on the CMS DAQ Architecture                                                                           |            |

|   | 8.2 Impac                        | ct on the EFU                                                                                            |            |

|   | 8.3 Future                       | e Work                                                                                                   |            |

|   | List of F                        | igures                                                                                                   | 128        |

|   | List of T                        | ables                                                                                                    | 130        |

|   | List of A                        | cronyms                                                                                                  | 131        |

|   | Reference                        | ces                                                                                                      | 134        |

|   | Curricu                          | lum Vitae                                                                                                | 140        |

# Kurzfassung

In dieser Arbeit wird eine Untersuchung des Verhaltens von großen Multiprozessor (MP) Computerfarmen für die on-line Datenverarbeitung des Compact Muon Solenoid (CMS) Experiments vorgestellt. CMS ist einer der großen Teichendetektoren am Large Hadron Collider (LHC) am Europäischen Laboratorium für Teilchenphysik (CERN) in Genf, der im Jahre 2005 den Betrieb aufnehmen wird.

Die CMS Computerfarm soll aus 1,000 MP Computersystemen und einem  $1,000 \times 1,000$ Schaltnetzwerk bestehen. Thema der vorliegenden Arbeit ist es mit Hilfe von Simulationsstudien und durch das Erstellen von kleinen Prototypensystemen das Verhalten dieser Computerfarm zu untersuchen.

Für die Simulationsstudien wurde ein einzelereignisgetriebenes Simulationsprogramm entwickelt, welches eine Beschreibung der 'high-level' Architektur der Farm, sowie eine Leistungsabschätzung derselben ermöglicht. Die modulare Struktur des Simulationsprogramms erleichtert die Entwicklung verschiedener Module, die das Verhalten der Einzelbausteine in einem gewünschten Detail zu modellieren erlauben. Mit Hilfe dieses Simulationsprogrammes wird eine spezielle Untersuchung über das 'scheduling' der Farmknoten durchgeführt, die nachweist, daß ein vorausschauendes 'scheduling' die Leistungsfähigkeit der Computerfarm erhöht.

Ein Prototyp eines Farmknotens wurde entwickelt ('event filter unit' EFU). Ein System, bestehend aus einem hochleistungs-MP System (dem Farmknoten), verbunden mit einem zweiten Computersystem (die Datenquelle emulierend) über ein ATM Netzwerk wurde erstellt. Das Leistungsverhalten des Anwendungsprogramms im Farmknoten betreffend die Benutzung eines Netzwerk Schnittstellencontrollers ('network interface controller' NIC) wird untersucht. Es wird gezeigt, daß ein speziell gebautes Modul zwischen dem Schaltnetzwerk und einem Farmknoten ('switch-to-farm interface' SFI) vermieden werden kann durch die Emulation der Funktionen in Software. Darüber hinaus wird ausgeführt, daß eher Aufmerksamkeit erfordert wird für die NIC Hardware, Software und Schnittstelle zum Anwendungsprogramm, als dem Erstellen eines speziell gebauten Moduls für den Aufbau der Ereignisdaten.

Außerdem wird das Erweiterungsverhalten der Farm untersucht. Es wird versucht, bei gegebenen Farm Konfigurationen mögliche Arbeitsbereiche in Abhängigkeit von verschiedenen Netzwerkgeschwindigkeiten zu ermitteln. Analytische Ergebnisse werden vorgestellt, die durch das Simulationsprogramm überprüft wurden. Schlußendlich wird die Abhängigkeit der Anforderungen an die einzelnen Bausteine der Farm von den der Farm eigenen Parametern aufgezeigt.

# Abstract

The topic of this thesis is the design-phase performance evaluation of a large multi-processor (MP) computer farm intended for the on-line data processing of the Compact Muon Solenoid (CMS) experiment. CMS is a high energy Physics experiment, planned to operate at CERN (Geneva, Switzerland) during the year 2005.

The CMS computer farm is consisting of 1,000 MP computer systems and a  $1,000 \times 1,000$  communications switch. The followed approach to the farm performance evaluation is through simulation studies and evaluation of small prototype systems—building blocks of the farm.

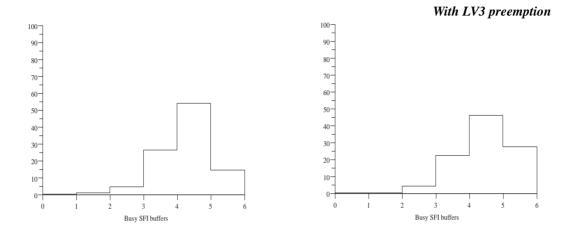

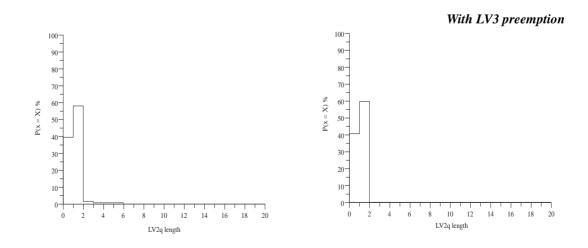

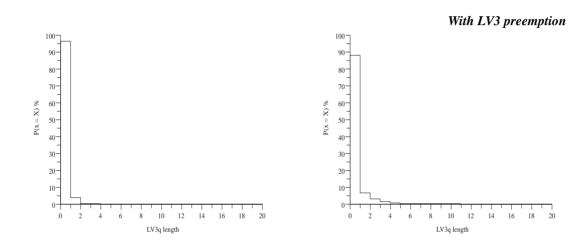

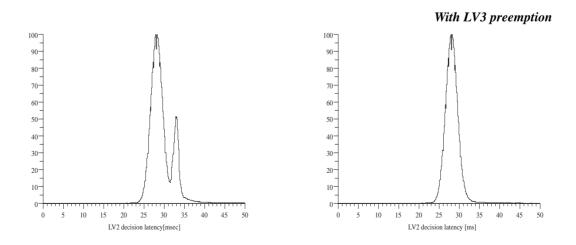

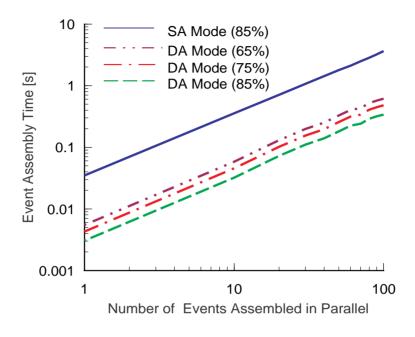

For the purposes of the simulation studies, we have developed a discrete-event, eventdriven simulator that is capable to describe the high-level architecture of the farm and give estimates of the farm's performance. The simulator is designed in a modular way to facilitate the development of various modules that model the behavior of the farm building blocks in the desired level of detail. With the aid of this simulator, we make a particular study on the scheduling of the nodes of the farm, showing that a preemptive scheduling can increase farm's throughput.

We have developed a prototype setup of a farm node —an event filter unit. The setup consists of a high performance MP system (the farm node) connected to a second computer system (used to emulate the data sources) through an ATM network. The performance issues of interfacing a network interface controller (NIC) to the application running in the farm node, are explored. It is shown with the aid of this setup, that the switch-to-farm interface (SFI) —a device used to put together the incoming data fragments into a single entity— can be entirely avoided by emulating its function in software. We show that in order to meet the required event assembly performance in the filter node inputs, the development effort has to concentrate on the NIC hardware, software and its interface to the application, rather than building a custom designed device specialized to perform the task of event assembly.

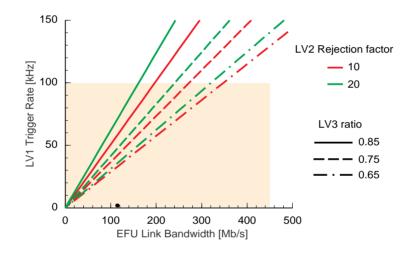

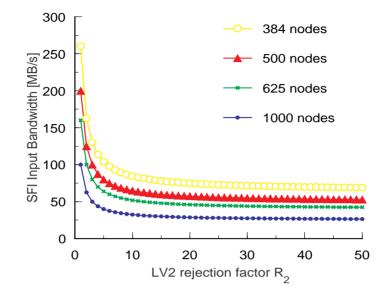

Finally, the farm scaling issues are investigated. Our aim is to obtain an "operational region" inside the farm configuration space, when the various networking speeds are taken into account. Analytically obtained results that have been confirmed with the above mentioned simulator, are discussed. We present also results showing the influence

of the inherent to the farm parameters (like the algorithm rejection factor) on the requirements for the farm building blocks (sustained I/O bandwidth).

# Preface

The quest of the elementary building blocks of matter and their interactions is the research topic of high energy physics (HEP). To find new particles and prove existing theories, one has to collide particles at higher and higher energies. To increase the probability of observing new phenomena, high interaction rates of particles are required. Any evidence of new particles has to be picked out of an extremely large amount of data, recorded during the operation of the physics experiments.

A new generation of HEP experiments at the future Large Hadron Collider (LHC) at the European Laboratory for Particle Physics (CERN), is currently designed and expected to start operating in the year 2005. The LHC is designed to collide protons with interaction energy of 14 TeV, every 25 ns. The LHC experiments have set the objective of investigating the Higgs sector of the Standard Model —the today's theory describing best the microcosm's particles behavior. The Higgs particle according to the Standard Model is the missing piece of the puzzle that explain how particles acquire their mass.

The Compact Muon Solenoid (CMS) experiment at the LHC, besides its many physics and construction challenges, has also an immense on-line data processing challenge. The data acquisition system (DAQ) of CMS is designed to be able to process quickly the detector data produced by the approximately 100 million detector channels after each particle collision, discarding less interesting events and analyzing the most interesting ones. This event selection is achieved by different selection mechanisms, called triggers. The first level trigger selection is expected to reduce the data rate, down to 100 thousand events per second, with an event size of 1 MB. After that first selection, the data of an event must be collected together from the 1,000 read-out units to a single location where further selection will take place. At that high event data rate, many locations where further processing can take place simultaneously, are required. A 1000  $\times$  1000 switching communication network with an aggregate bandwidth of 500 Gb/s is foreseen for that purpose. It will interconnect the 1,000 read-out units with a computer farm consisting of 1,000 multi-processor (MP) computer systems.

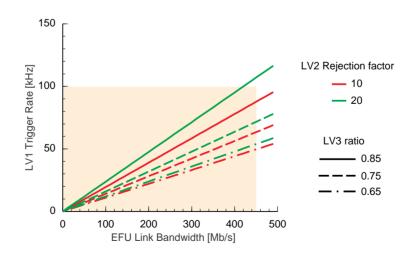

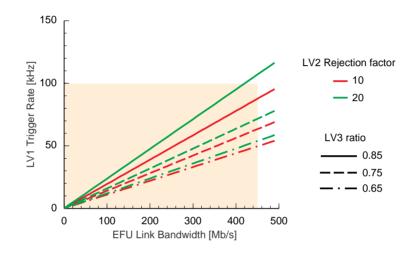

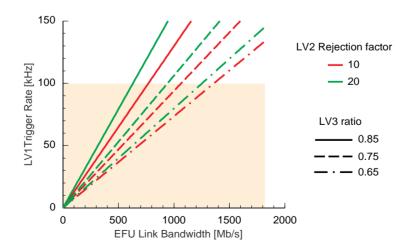

In the event filter farm (EFF) of the CMS DAQ system, the final steps of the event selection will take place before the data can be recorded to permanent storage. For that purpose, the EFF has to provide an estimated total processing capacity of approximately 5 TIPS (5 million MIPS), so that sufficient processing can be done before an event is accepted or rejected. Each of the farm nodes, the event filter unit (EFU), is designed to process an independent stream of events with an average arrival rate of 100 events per second. After a two level processing, the resulting average output rate will be approximately 0,1 events per second. To achieve this high reduction of the event rate, a novel idea of a two-steps data selection has been adopted. At the first step of the selection, called Level-2 (LV2) trigger, only a small part of the processed event (~ 25% of the full event) is forwarded through the switch to an EFU. If the selection algorithm decides that it is an interesting event, the rest of the event will be forwarded to the same EFU for additional processing, the Level-3 (LV3) trigger. This two-steps event selection results in decreased bandwidth requirements for the switch and makes more economic use of both the switch and EFF resources.

Today's computer performance is not sufficient to build such a farm in an economic way. It is expected however, that prior to the start of operation of the experiment in the year 2005, it will become affordable to build a farm whose performance is very close to the requirements. In that respect a farm approach for the on-line data processing of the CMS experiment, has the advantage of easily adjusting the farm performance, either by selecting more powerful nodes, or by adding more nodes to it. This flexibility offered by a farm design, will ease the building, tuning and upgrade of the CMS on-line event filter farm.

#### Motivation and Problem Statement

The advent of powerful, yet affordable computer systems, has a tremendous impact also in the data processing required by modern HEP experiments. Building a farm of MP systems for the on-line filtering purposes of CMS is a very challenging task. Design issues, as the number of the event filter units (EFU), the number of processors in each EFU, must be well understood for the various scenarios of the farm operation. These issues are a function of many parameters of the data acquisition system, *e.g.*, the arrival rate of data from the detector, the processing time needed for deciding whether an event will be recorded or not, etc. All that suggests, that a thorough understanding of the farm behavior under many different assumptions is required, before important design decisions are taken.

Specific characteristics of the EFU like their I/O bandwidth and throughput, need also special attention. They are important in order to ensure that the communication requirements with the event builder switch through the switch–to–farm interface (SFI) are satisfied for the given event rates. Given an MP system for the EFU, the available processing capacity must be accommodated with sufficient memory and I/O bandwidth in order to sustain an incoming events stream up to 100 MB/s. More powerful MP systems will require even higher I/O bandwidth, hence a balance of the computing with the I/O capacity is required. Therefore, the impact of MP systems on the total farm size (i.e. the number of EFU) and the ability of MP systems to deliver sufficient I/O bandwidth to the event filtering applications are very important design issues.

Therefore, it is crucial to study in the above context, the functional behavior of the event filter farm foreseen by the CMS DAQ system. In particular, the relations of the farm size with the required processing time relatively to the computer performance, the event filter unit scheduling for the two-steps event selection and the I/O requirements relatively to the farm size.

#### Thesis approach

In this thesis the above problems are studied in a twofold way. Firstly, for the investigation of the farm behavior under the different assumptions, simulations are used. A simulation tool is developed for that purpose that is able to describe the behavior of the major parts of the DAQ system related to the EFF. With the aid of this tool, a wide variety of scaling scenarios of the farm can be investigated. A particular study of the scheduling behavior of the EFU is done, in order to improve system performance.

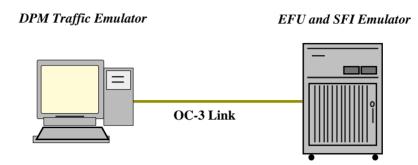

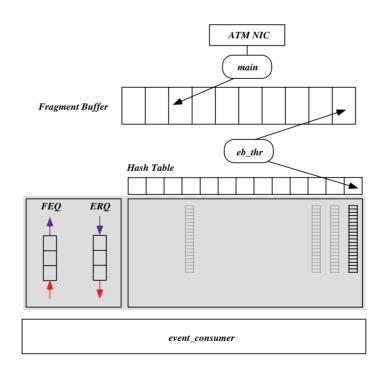

Secondly, a study of the performance of an MP system used for an EFU, is done using a prototype setup. A small EFU prototype environment is built using a modern symmetric multiprocessor system and an asynchronous transfer mode (ATM) communication network. An emulation environment of an EFU is developed. With the aid of the setup, the aspects of MP-based EFU can be analyzed.

#### Thesis layout

In Chapter 1 the concepts of the high energy physics and the modern experimental approach, are introduced. Chapter 2 introduces the domain of this work, describing the various parts of the currently designed data acquisition system of the CMS experiment.

In Chapter 3 we describe the principles of modern MP computer system architectures. In Chapter 4 we analyze the MP performance issues related to the MP architecture, processor-memory interconnection, I/O and the operating system, in order to identify corollaries to the farm performance. A description of the methods used for the MP systems performance analysis and evaluation, is following. We focus on the method of event-driven simulations as the tool for the performance evaluation of the event filter farm.

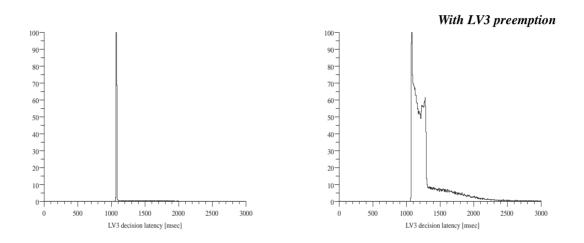

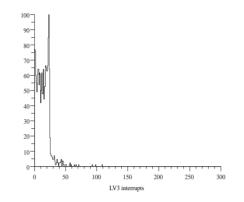

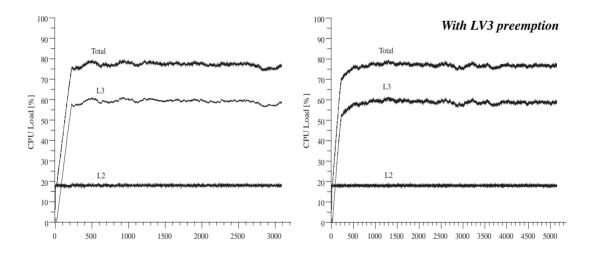

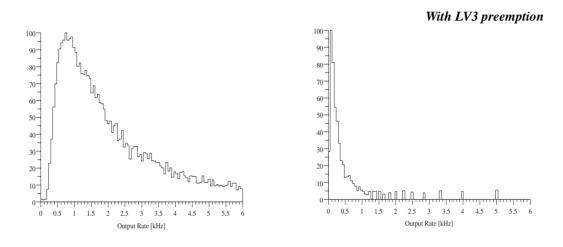

In Chapter 5 the development of a simulation tool used for the design and evaluation of the CMS event filter farm is described. Based on a simple behavioral simulation model and a set of identified parameters describing the farm, it is able to give the performance parameters of the various components of the farm and of the data acquisition system. The results of a preemptive scheduling are discussed.

Chapter 6 contains a case study of using a modern high-end commercial computer system as the event filter farm node. The interaction between the computer hardware, the

operating system and the communications network, is studied in the framework of an SFI emulator running into the system.

In Chapter 7, we investigate various scaling scenarios of the farm. An assessment of the farm performance scaling is done, for a farm with many but less powerful processing nodes and a farm with more powerful, but fewer processing nodes. The merits of these two possible approaches are studied and compared.

Finally, in Chapter 8 the conclusions of this work are presented. Prospects and future work are discussed at the end.

#### Achievements of the Presented Work

With the aid of the event filter farm simulator, it is shown that when scheduling of the event filtering jobs is done, the throughput of the farm can be improved. In particular, if preemption of LV3 jobs is adopted when LV2 jobs arrive and the EFU processors are busy processing LV3 jobs, the farm throughput is increased.

The developed simulator also sets the framework for further, more detailed, investigations on the farm architecture. In particular, it can be very useful to extrapolate the performance of prototype systems built during the design phase of the farm, up to the expected performance of a full sized farm.

The EFU prototype setup has given valuable insight on the usability of MP systems for the EFU. In particular, it is shown that an MP system can also be used to perform the functions of the last stage of the event assembly, prior to the event processing. This task, done by the SFI in the original DAQ design, can be effectively emulated in an MP-based EFU. It is shown that the potential performance bottlenecks might appear in the I/O subsystem of an MP system and not related to any limitations of the SFI-emulator's event assembly throughput. While a custom designed SFI may guarantee the necessary event assembly throughput, the possible I/O performance bottlenecks are still not addressed. The experience gained with this EFU prototype, suggests that in both cases of a custom designed SFI system, or an emulated one, the available application interfacing to the I/O through the operating system, requires a significant improvement. Possible ways of how this could be done are proposed.

# Acknowledgements

This thesis would never have been finished without the support of many friends and colleagues. Foremost, I wish to thank my Supervisor, Univ. Prof.-Dr. Günter Haring, for his tolerance and comprehension. He has been extremely supportive throughout this work and through the difficulties I have encountered.

I am grateful to Werner Jank, Sergio Cittolin and Martti Pimiä of CERN, for their continuous encouragement and giving me the opportunity to start the work on this dissertation.

I am obliged to the Institut für Hochenergiephysik der Österreichische Akademie der Wissenshaften in Vienna, for offering me the first opportunity to work at CERN on the CMS project.

I am indebted also to Jean-Pierre Porte for his continuous support and the numerous helpful discussions, to Norbert Neumeister for his help with German and for his friend-ship.

Special thanks go to Dirk Samyn, who kindly provided me the original version of the event filter farm simulator, to Gerhard Walzel for the many fruitful discussions, Paul Porth for his hospitality, Joop Joosten for the enlightening discussions on ATM and George Smyris for his help on proofreading.

This dissertation has been made possible by the generous Doctoral Students program of CERN, from 1994 to 1997. My work and stay at CERN has been also supported by the management of the CMS experiment, to whom I am very thankful.

The Interphase Corporation has kindly provided the sources of their ATM driver, giving invaluable insight for the ATM implementation of the SFI emulator.

My fiancée Tina, was a source of continuous encouragment and silently provided the necessary understanding for the endless hours in front of the computer.

To all those that helped me, a big thank you!

# **1** Physics Experiments and Data Acquisition

The mankind endeavor to understand the fundamental laws and principles of Nature dates back to the days of Democritus, Aristotle and Pythagoras. The dramatic evolution of technology and the remarkable intellectual progress of Science, especially in the last century, still suggest that Nature is governed by simple laws, even though the complexity of the observed phenomena might imply the opposite.

The modern science of elementary particles is concerned with the identification of the fundamental building blocks of matter and their interactions. In numerous achievements it has revealed a fascinating harmony of Nature, is it at the macrocosm or at the microcosm, which today is very well described by the *Standard Model* (SM) of elementary particles and their interactions.

## **1.1** Elementary Particles and Their Interactions

The different forces of Nature as described by the field theory, are four: the *electromagnetic*, the *weak*, the *strong* and the *gravitational* force. Each fundamental interaction has its own field and one or more mediator particles, responsible for the exchange of the interaction. These fundamental forces and their mediator particles are summarized in Table 1.1, together with their relative strength and effective range.

| Force           | Mediator          | Relative Strength | Range             |

|-----------------|-------------------|-------------------|-------------------|

| Electromagnetic | γ                 | 1                 | ∞                 |

| Strong          | g                 | ~ 20              | $\sim 10^{-15} m$ |

| Weak            | $W^{\pm}$ , $Z^0$ | 10-7              | $\sim 10^{-18} m$ |

| Gravity         | graviton?         | 10 <sup>-36</sup> | ∞                 |

Table 1.1: Fundamental forces and their characteristics

The remarkable success of the SM is that it can describe the interactions of the various particles discovered in the numerous physics experiments during the last century, making use of only three families of pairs of elementary particles (leptons and quarks) and their anti-particles, by unifying the electromagnetic and weak forces into the *electroweak* force. Those two groups of three families of particles are summarized in Table 1.2.

|         | Family                                   |                                                  |                                                    |

|---------|------------------------------------------|--------------------------------------------------|----------------------------------------------------|

| Leptons | $\begin{pmatrix} e \\ v_e \end{pmatrix}$ | $\begin{pmatrix} \mu \\ \nu_{\mu} \end{pmatrix}$ | $\begin{pmatrix} \tau \\ \nu_{\tau} \end{pmatrix}$ |

| Quarks  | $\begin{pmatrix} u \\ d \end{pmatrix}$   | $\begin{pmatrix} c\\s \end{pmatrix}$             | $\begin{pmatrix} t \\ b \end{pmatrix}$             |

Table 1.2: Fundamental elementary particles

In order to explain the spontaneous symmetry breaking in the electroweak force, into what is observed today as electromagnetic and weak forces, the SM introduces a mechanism which also gave masses to the light and heavy particles and to the vector bosons  $W^{\pm}$  and  $Z^{0}$ . This mechanism requires the introduction of another particle; the *Higgs boson*. In further extensions of the SM as in the *Minimal Supersymmetric SM*, the Higgs boson is replaced by a set of five bosons  $H^{\pm}$ , h,  $H^{0}$  and A.

## **1.2** Particle Physics Experiments

The SM has successfully predicted the existence of the  $W^{\pm}$  and  $Z^{0}$  intermediate bosons, with a remarkable precision of their masses. For their discovery, the collision products of protons *p* and anti-protons  $\bar{p}$  had to be registered, identified and analyzed. In 1981 at the European Center for Particle Physics (CERN) in Geneva, Switzerland, the Super proton anti-proton collider (Sp $\bar{p}$ S) was constructed, and the detectors UA1 and UA2 built around it confirmed the SM predictions.

To study further the properties of the intermediate bosons  $W^{\pm}$  and  $Z^{0}$ , another generation of physics experiments were constructed at CERN at the beginning of 90's. Four worldwide collaborations were formed and a new collider of electrons and positrons (LEP) was built, together with four experiments (L3, ALEPH, OPAL and DELPHI) around it. Other experiments (CDF, D0) have been setup at the Tevatron collider at Fermilab, in the United States. It was the LEP experiments that confirmed the assumption of the SM that the leptonic families are exactly three. Also, the CDF experiment [CDF96] at Fermilab, has recently provided evidence of the existence of the last quark remained not detected; the *t*-quark.

All these searches of rare interactions of particles, able to prove the existence of one or another particle, are not only major scientific and engineering challenges, but also enormous data processing and analysis projects. High-speed electronics hardware and sophisticated physics software, are all put together to select only the interesting candidates of the registered interactions (from now on referred to as events), out of a huge number of background and uninteresting events. There is an immense need in High Energy Physics experiments, of high performance computing resources and communication systems.

## **1.3** The Large Hadron Collider (LHC)

The existence of the Higgs boson still remains unconfirmed in the theory of the SM. For that purpose, at CERN, the physics community has proposed to build the Large Hadron Collider (LHC) [LHC95].

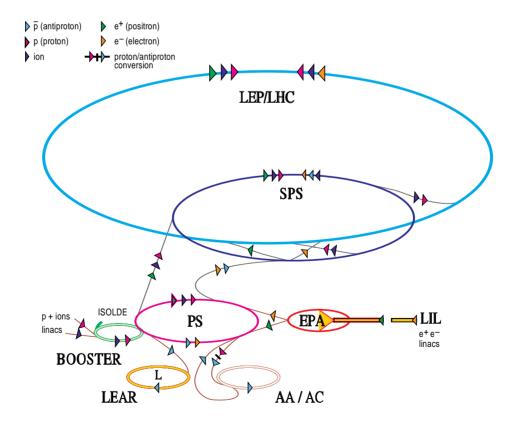

Figure 1.1: CERN accelerator complex

The LHC will accelerate two beams of protons in opposite directions and collide them at a center of mass energy of 14  $\text{TeV/c}^2$ . The construction of LHC was approved in 1994 and it will be operational in 2005.

Two general purpose experiments, CMS [CMS94] and ATLAS [ATLA94], have been proposed to be built at the LHC, to search for the Higgs boson and any other interesting physics phenomena that might emerge at the unprecedented energy levels of LHC. Two other more specialized experiments, LHC-B and ALICE are also proposed.

The LHC will be built in the same tunnel where the LEP collider is located now. It will have a circumference of 27.5 km. In order to achieve the required collision energy at LHC, the existing accelerator complex of CERN consisting of the LINAC, the Booster, the Proton Synchrotron (PS) and the Super Proton Synchrotron (SPS), will be utilized to gradually accelerate the collision particles and finally inject them into LHC (Figure 1.1).

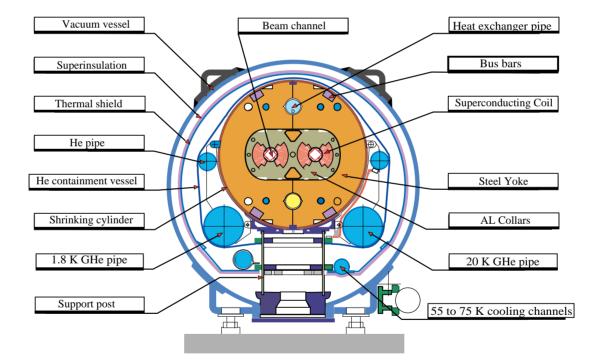

Figure 1.2: Cross-section of the LHC dipole

The maximum energy that LHC can achieve, depends on how strong the magnetic field that holds on trajectory the collision particles can be made. In order to achieve the required energy of 7 TeV for each beam, some 1300 dipoles (Figure 1.2) with superconductive magnets generating a magnetic field of 8.4 T strength, will be utilized.

At normal operation, LHC will collide bunches of protons every 25 ns, each bunch crossing producing approximately 20 proton interactions. Two periods of operation are foreseen for LHC. LHC will provide also the capability of colliding heavy-ions at lower energies, and the ALICE experiment is specially designed to observe these collisions.

## **1.4 The CMS Detector**

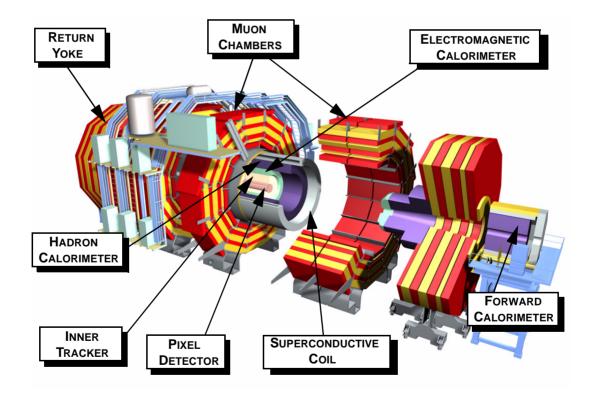

The Compact Muon Solenoid (CMS) detector, depicted in Figure 1.3, was first proposed in 1990. Its basic concept for detecting the Higgs boson, is a compact detector with optimized muon identification and the best possible electromagnetic calorimeter.

The CMS detector consists of the pixel detector, the inner tracker, the electromagnetic and hadron calorimeters and the muon detectors. A solenoidal magnet generating a field of 4 T intensity, surrounds the central detectors and the calorimeters.

Figure 1.3: Perspective view of the CMS detector

The CMS detector has a total length of 21.60 m, a diameter of 14.60 m and it weighs 14,500 tons.

Until the beginning of construction of CMS, several research and development projects on detector technology are taking place, in order to evaluate the different choices for each sub-detector system. In addition, the requirement for an affordable detector will lead to two designs, a full-fledged and a staged design, with the option of future upgrades. The CMS detector performance and objectives are such, that it can provide a rich physics research program for at least 15 years.

Today the CMS project is supported by a world-wide collaboration, consisting of 1760 scientists in 145 universities and research organizations, from 31 countries. The CMS project was approved in December 1996, with a construction budget not exceeding 475 million swiss francs. Its targeted completion date is in year 2005.

## **1.5 The CMS Trigger and DAQ System**

The LHC experiments' objective of detecting the Higgs boson, raises the requirement of operating the LHC at high luminosity *i.e.*, the LHC provides a high number of interactions per unit of time, so that rare phenomena can be detected.

With bunch collisions occurring every 25 ns, the CMS detector will record the traces of approximately 20 proton–proton interactions at a frequency of 40.8 MHz. A large number of sub-detector channels are therefore required, to keep the number of "fired" detector channels (referred here as occupancy) at a reasonable level. For every occurring proton collision, the particles produced will be detected by the individual sub-detector systems. The output data of each sub-detector, after a collision has taken place, will add up to the full event describing the results of the interaction. In Table 1.3 are summarized the contributions of each sub-detector system to the full event, together with their estimated occupancy. The total size of one event is expected to be around 1 MB of compressed (zero suppressed) data.

| Detector      | Channels     | Occupancy | Event Size [KB] |

|---------------|--------------|-----------|-----------------|

| Pixel         | 80,000,000   | 0.01      | 100             |

| Inner tracker | 16,000,000   | 3.0       | 700             |

| Preshower     | 512,000      | 10.0      | 50              |

| Calorimeters  | 125,000      | 5.0       | 50              |

| Muons         | 1,000,000    | 0.1       | 10              |

|               | Trigger data | •         | 10              |

Table 1.3: CMS detector channels and event sizes

If we assume that each one of the detector channels carries binary information and multiply the interaction rate by the resulting (from the detector channels) number of bytes, we reach to an estimate value of 400 TB/s for the required data throughput. The effect of using an event size of 1 MB reduces the above figure by an order of magnitude only (40 TB/s). Therefore, before the event rate can be handled for storage, a multi-stage event selection and rate reduction mechanism is required to reduce the data rate to reasonably lower figures. This selection however, must not compromise the interesting physics events that can occur. These event selection mechanisms are commonly referred to in the physics experiments, as *triggers*. Their implementation is usually based on specialized, custom-made hardware.

The CMS DAQ system implements three logical levels of triggering. The first data selection is carried out from the LV1 trigger devices. Two additional stages of event selection will be implemented by the LV2 and LV3 triggers respectively, before the resulting event rate becomes low enough for data storage.

#### **1.5.1** The Level-1 Trigger (LV1)

The LV1 trigger [Lack95] consists of specialized hardware, able to process each subdetector's data in a very limited time interval (few bunch-crossing periods each of 25 ns), and provide an indication if the occurred event is interesting or not. Every sub-detector participating in the LV1-trigger has its own trigger devices because of the peculiarity of their signals and the different logic needed for a trigger decision. Because the varying response time of the different sub-detectors, not all of them are suitable for LV1 triggering. There are also specialized sub-detectors that have a fast response time and are used only for triggering.

When the various LV1 trigger devices have finished processing, a global decision must be taken to forward the event for further processing or not, according to the result of the individual LV1 triggers. This decision is taken by the Global Trigger System (GTS) [Neum97]. Among its tasks of combining the triggers, the GTS must be able to pace the resulting event rate. The average rate of events accepted from LV1 is fixed today to a maximum value of 100 kHz. The exact characteristics of this event rate are not currently well known. The regional LV1 triggers may result to accepted events in subsequent bunch-crossings *i.e.*, 25 ns. The GTS is expected to minimize such cases to not more than three triggers in consecutive bunch-crossings.

The GTS is designed to be programmable in order to accommodate unforeseen physics rates and to operate in a pipeline mode due to the high speed and data-flow requirements. The acceptance of an event by the GTS, will be communicated by the timing, trigger and control (TTC) system [Tay195] to the front-end detector electronics, to initiate the detector read-out.

The identification of the event that a Higgs boson might have occurred, is done through the various signatures of the typical Higgs production decays. Each decay, leaves to the sub-detectors distinct signatures that can be identified. These signatures are summarized in Table 1.4 together with their contribution to the total LV1-trigger event rate.

Each trigger condition might occur not only due to a Higgs boson decay, but also from other uninteresting interactions. In a 25 ns time interval, not enough processing can be done to decide whether a Higgs boson was present or not. Therefore, the LV1 trigger will fire only when a particular trigger condition has been detected, while detailed processing that might reveal interesting physics events will be done at the later LV2 and LV3 trigger stages. This way, fast selection of potentially interesting events can be done, resulting in highly reduced selected event rates.

| Trigger<br>Condition | E <sub>t</sub> cut-off<br>[GeV] | Rate<br>[kHz] |

|----------------------|---------------------------------|---------------|

| $E_t sum$            | 400                             | 6             |

| $E_t$ miss           | 80                              | 4             |

| e single             | 25                              | 6.84          |

| e double             | 12                              | 1.45          |

| l jet                | 100                             | 2.06          |

| 2 jet                | 60                              | 2.17          |

| 3 jet                | 30                              | 3.16          |

| 4 jet                | 20                              | 2.96          |

| jet + e              | 50 + 12                         | 1.35          |

| Single µ             | 20                              | 7.8           |

| Double µ             | 4                               | 1.6           |

| $\mu + e$            | 4 + 8                           | 5.5           |

| $\mu + jet$          | 4 + 40                          | 0.3           |

| $\mu + E_t miss$     | 4 + 60                          | 1.0           |

| $\mu + E_t sum$      | 4 + 250                         | 0.2           |

| SUM                  | •                               | 20            |

Table 1.4: LV1 trigger rate break-down

The detector front-end electronics, the LV1 trigger and the event readout units, are designed for parallel and pipeline operation. The TTC system is used for their synchronization. It provides a reliable means of signal and short message distribution, between the various stages of the front-end electronics and the LV1-trigger devices.

The TTC system employs a time division multiplexing of two data channels at 160.32 MBaud. One channel is used to communicate the LV1 trigger acceptance and the other for broadcasts and individually addressed commands. TTC offers a high precision clock of 160.32 MHz (four times the LHC bunch-crossing rate), distributed to the various detector destinations with an output jitter of less than 10 ps RMS.

### 1.5.2 Data Acquisition Architecture

The GTS acceptance of an event starts the read-out of the detectors into some 1,000 front-end buffers. The task of the data acquisition system (DAQ) is to move the data fragments from these front-end buffers, to a single location in the event filter farm (EFF), where the LV2 and LV3 triggers will be executed.

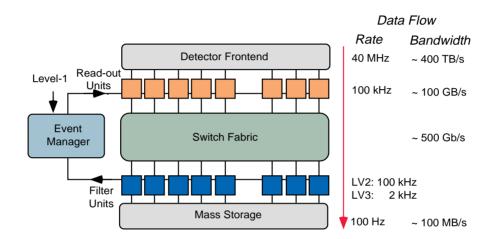

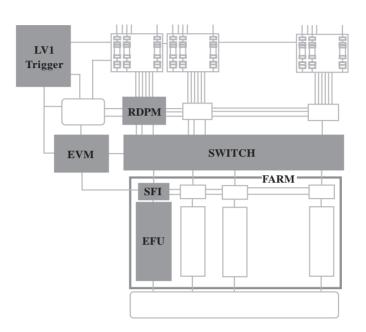

Figure 1.4: Architecture of the CMS DAQ system

The management of the readout buffers is done by the read-out units (RU) which comprise a set of front-end drivers (FED) connected to a read-out dual port memory (RDPM) [Citt95]. The RU will be coordinated by the event manager (EVM) in order to send the data fragments of an event to a single event filter unit (EFU). The task of putting together event data fragments into full events is called *event building*.

This architecture of the CMS DAQ system is shown in Figure 1.4. It is estimated that some 1,000 EFU will be required to handle the LV1 event rate, providing sufficient computing resources to execute the physics algorithms of the LV2 and LV3 triggers.

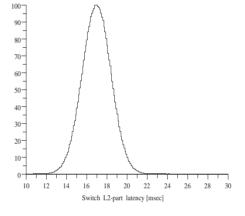

#### 1.5.3 Event Builder Architecture

The crucial part of the CMS DAQ system is its event building architecture. It is foreseen to incorporate a high performance communication network of 1,000 inputs and 1,000 outputs. However, the bandwidth requirements for such a communications network are very high due to the LV1-trigger data rate and the average event size. The product of the event size times the LV1-trigger rate, gives the bandwidth that the event builder will have to sustain. With a LV1 trigger rate of 100 kHz and an event size of 1 MB (as shown in Figure 1.4), one can see that an aggregate bandwidth around 800 Gb/s will have to be sustained by the event builder.

To require the existence of such a high performance for the event builder, well in advance of the start-up of the CMS experiment, is a very risky assumption. Therefore, in order to reduce the required bandwidth, the event builder architecture is based on a two steps event building, otherwise called *virtual-LV2* trigger strategy. For the LV2 trigger, the physics algorithms will be given to process only a fraction (~ 25%) of the full event. Only in the case of an event accepted by the LV2 trigger the rest of the event (~ 75%) will be forwarded to the same destination, so that the LV3 trigger processing can start. The LV3-trigger will have available the full event for processing.

Given a relatively high rejection rate of the LV2 trigger, significant bandwidth reduction can be achieved. For instance, given that the rate of events accepted by the LV2-trigger will be on average 2,000 events per second, for the above mentioned event fractions the resulting bandwidth that the event builder will have to sustain is around 250 Gb/s. With a safety factor of two the required bandwidth is set to be around 500 Gb/s (Table 1.5). The virtual-LV2 strategy assumes that with the data of the muon detectors and the calorimeters, an efficient decision (without missing interesting events) can be taken by the LV2 trigger.

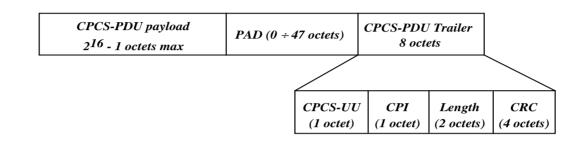

Constructing a switched, non-blocking and a packet-loss free communication network of the size required by the CMS DAQ architecture is a difficult task. The required performance and the cost considerations suggest that widely-available, highly-scalable commercial solutions are the best candidates for the event builder. Standardized communication technologies as Asynchronous Transfer Mode (ATM), Fibre Channel (FC), Scalable Coherent Interface (SCI) are among the candidates considered today. It remains to be seen which technology will be the market's choice, eventually offering the best price performance, before a decision is taken for the implementation of the event builder in CMS.

#### **1.5.4 High-level Triggers**

In addition to the LV1 trigger, CMS foresees two more levels of event processing (the LV2 and LV3 triggers) in order to select only the interesting physics candidates. The high-level triggers will not be executed in specialized hardware devices as in the LV1-trigger case, but in one of the EFU of the event filter farm which consists of computer systems made of general purpose processors.

The LV2 trigger, in more time-relaxed conditions, will be able to refine the LV1 decision identifying the interesting physics events and discarding the less interesting. The LV2 trigger must have bounded execution time, because a timely decision for each event will be required to release the pending event part in the RDPM.

The LV3 trigger, will make an even narrower event selection based on data from all the sub-detectors. The origins of the tracks left by particles that so far have triggered an interesting event, will be identified among the tracks of many thousand other particles. If there is still an indication that an interesting event has happened, the full event together

with the individual trigger data will be stored into permanent storage for later detailed analysis.

The flexibility of general purpose computer systems in the EFF, will help for the tuning of the high-level trigger algorithms. The algorithms' performance and efficiency will be crucial for the operation of the detector. It is not desired that interesting events will be rejected, due to any algorithm inefficiencies. On the other hand, the limitations of the storage devices will set an upper limit to the amount of data that will be possible to be stored.

Today's estimates of the combined processor performance that will be available when CMS will start operating and the amount of processor time needed for the high level triggers, suggest that around 10ms for LV2 and around 1s for LV3 will be sufficient.

#### 1.5.5 On-line Computing Services

At the endpoint of the DAQ system, the events that passed all the triggering stages will be recorded to permanent storage, so that later can be carefully analyzed and the underlying physics interaction studied. The output event streams from all the EFU will terminate at a buffering device. Estimates show that with an output event rate around 100 Hz, a minimum of 10 TB buffer storage capacity will be required. A short *quasi on-line processing* will follow immediately after and prior to the recording [CMS96]. The task of the quasi on-line processing will be to tag the events in the event database used for the off-line analysis.

Other tasks performed by the on-line computing services are the DAQ control and monitoring and detector calibration. The control system supervises the operation of the entire trigger hierarchy and the DAQ system. It will monitor and record the configuration and operation parameters, including initialization and dynamic reconfiguration, and accordingly launch and terminate the DAQ tasks. Failure detection is a crucial task of the control system. Some additional monitoring will be also provided sampling the detector physics performance and detecting error conditions.

### **1.6 Summary of CMS DAQ Parameters**

In Table 1.5 we summarize the main parameters of the CMS DAQ system, as they are assumed today. The value for the bandwidth of the event builder switch is calculated by adding the needed bandwidths for LV2 and LV3, in order to sustain the transfers of a LV2 (LV3) event at a LV2 (LV3) rate and taking into account a 50% switch efficiency. The assumed value for the LV2 rejection rate is set to be 50. One could argue that this is a rather optimistic value. For the performance evaluation studies of Chapter 6 and Chapter 7 we consider worst cases of the LV2 rejection factor value.

| Number of RDPM              | 1,000     |

|-----------------------------|-----------|

| Number of EFU               | 1,000     |

| Maximum LV1 trigger rate    | 100 kHz   |

| Average total event size    | 1 MB      |

| Size of data used in LV2    | 250 KB    |

| Size of data used in LV3    | 750 KB    |

| LV2 trigger rejection rate  | 20 to 100 |

| LV3 trigger rate            | 2 kHz     |

| Aggregate switch bandwidth  | 250 Gb/s  |

| Accepted events output rate | 100 Hz    |

| Typical LV2 processing time | 1 ms      |

| Typical LV3 processing time | 1 s       |

Table 1.5: Summary of the CMS DAQ parameters

# **2** Event Building and Filtering Systems

The event filtering and the event building are the main tasks of the CMS DAQ system in order to accomplish the acquisition of the detector data at a reasonably low rate. Both together, set the domain of this work.

In this chapter, the functionality of the various units comprising the event building and filtering system is described. The basic concepts guiding the design of the CMS event builder and event filter are analyzed. Similarities of the DAQ sub-systems with those used in computer and communication industry, are identified.

## 2.1 Event Builder

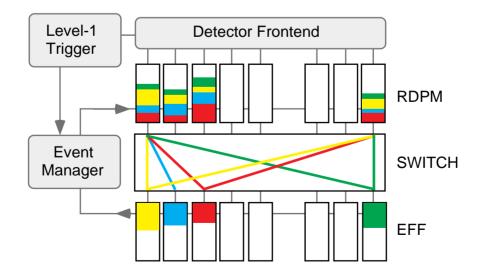

The event builder (EVB) has to assemble the data fragments constituting an event, as recorded by the different sub-detectors, into a single destination—location— in the event filter farm (EFF). This functionality is depicted in Figure 2.1.

Figure 2.1: Event building using a switch network

The pieces with different shades at the switch inputs (the top side), are representing fragments belonging to different events. The fragments of each event (those with the same shade and spread over the switch sources), will have to be forwarded to a previously defined destination in the EFF.

The event builder has always been the principle component in most DAQ systems of HEP experiments, due to the nature of the data produced by the particle detectors. The generation of the LHC experiments however, due to the high interaction rates and massive data flows, has requirements on the EVB that have not been previously met. A large number of EVB input sources (~1,000) are required for reading-out the detector data. A similar number of destinations or event filter units are needed to handle the resulting event rate.

### 2.1.1 Read-out Dual Port Memories (RDPM)

The RDPM [Citt95] are hardware devices that interface the EVB with the detector readout electronics and their front-end drivers (FED). They have as their task the read-out of FED connected to each of them and on request inject the fragments of an event into the EVB switch.

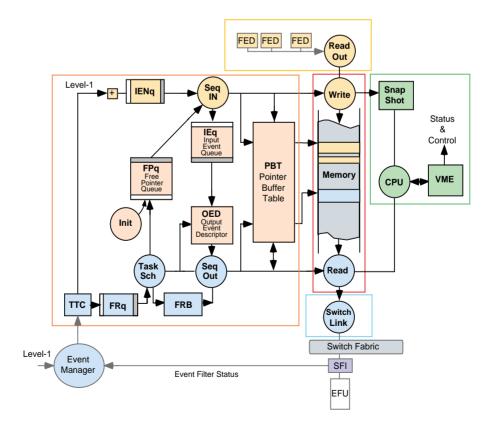

Figure 2.2: RDPM functional diagram

The RDPM essentially represents a large storage device with two simultaneously accessed ports, one used for input and the other for output. The RDPM it is connected also to the LV1-trigger signal distribution network (TTC) and the event manager (EVM). Figure 2.2 shows a block diagram of an RDPM based on FPGA logic [Fucc95].

The RDPM data memory is partitioned into fixed-size pages. A list of pointers to the free memory pages is maintained in the free pointer queue (FPq). The input part of the data stream is handled by the input sequencer (SeqIN) and the output part, by the output sequencer (SeqOUT).

The LV1-trigger sends to the RDPM the event numbers of the accepted events. The RDPM store the incoming event numbers in the input event number queue (IENq). Once data are available in the FED, the RDPM will be notified and the SeqIN will pick an entry from the IENq. The FPq FIFO-organized queue is read to obtain a pointer to a free memory page. The read-out of the FED is then initiated and the incoming data are stored into one or more memory pages. At the end of the read-out an event descriptor consisting of the pointer to the first memory page, the event number and the total word count, is written to the input event queue (IEq). Finally, the SeqIN writes into the pointer buffer table (PBT) a linked list of pointers to the memory pages occupied by the event fragment.

The RDPM output is driven by the EVM. The EVM sends to each of the RDPM event filter requests (EFR). An EFR consists of a filter resource (FRS), the event number assigned to it and a command specifying the action to be performed for that event. Each RDPM will store incoming EFR in its farm request queue (FRq).

When an EFR becomes available, the task scheduler (TS) copies an available event descriptor from the IEq to a free location in the output event descriptor (OED). The TS will also decode the command contained in the EFR and will initiate an action taken by the SeqOUT, depending on the decoded command.

The commands that are envisaged to be encoded in an EFR are READ-data, CLEARdata or both READ and CLEAR. The CLEAR-only command will be executed immediately, while the other two commands will be written to the filter request buffer (FRB). The SeqOUT on a reception of a command will read the pointer to the first memory page and the word count from the event descriptor contained in the OED. It will then initiate the transfer of the data referenced by the pointers, to the data-link device.

The presence of the FRB is to allow for a higher level of traffic-shaping of the RDPM output data stream to the EVB switch. We will examine how this might be implemented in the next paragraph.

| Total number of RDPM               | up to 1,000       |

|------------------------------------|-------------------|

| FED per RDPM                       | up to 6           |

| Minimum I/O bandwidth              | 100 MB/s          |

| Maximum I/O bandwidth              | 400 MB/s          |

| Average event-fragment size        | 1024 ÷ 4096 bytes |

| Number of buffered event fragments | ≈ 100,000         |

| Internal memory size               | ≈ 100 MB          |

Table 2.1: RDPM main characteristics

The characteristics of the RDPM as included in their current specifications, are summarized in Table 2.1 The maximum figures for the I/O bandwidth are set to enable the RDPM to operate in event builder environments with eventually smaller switch configurations *e.g.*,  $512 \times 512$  ports.

Similarly to the FPGA based RDPM, there exist proposals of building it with specialized processor boards built around the TMS 320C80 digital signal processor. Such a system is VORTEX [Bran95]. Prototypes of such systems are already built, which come very close to meeting the RDPM requirements.

For the purposes of the virtual-LV2 trigger operation, the RDPM will be grouped in those holding event fragments to be used for the LV2 trigger and those that hold event fragments that will be requested in the case of LV3 trigger. Both groups will get data from their attached FED simultaneously and at a maximum rate of 100 kHz.

The LV2 group of RDPM will receive EVM requests to send data at an average rate of 100 kHz. The LV3 group will receive the read requests from the EVM at an average rate which will be determined, by the average number of accepted events at the LV2 trigger stage in one unit of time. On the other hand, the RDPM of both types (LV2 and LV3) are designed with a predefined memory size. Hence, the amount of time that an event fragment is kept in the RDPM is very critical for their stable operation. Evidently, this hold time is even more crucial for the LV3 group of the RDPM, as it in addition includes the time necessary for the LV2 trigger processing.

The RDPM need to be monitored to ensure their normal operation. This will be done through a VME interface. The same interface will be used for their control and initialization, as well as for any other signalling, required by the DAQ architecture.

### 2.1.2 Event Builder Communication Network

The heart of the event building task is the communication network that interconnects the read-out units with the event filter units. The CMS DAQ architecture, foresees a large switching network to accomplish this task. However, the number of needed ports, the

LV1-trigger rate and the average event size, result in non-trivial requirements on the EVB network.

Preliminary estimates indicate that around 1,000 input ports will need to be connected to a 1,000 output ports. The number of the input ports is determined by the number of the read-out units that are necessary to handle the detector data. Consequently, the number of the output ports is determined by the number of the required EFU, in order to provide sufficient event processing resources, to handle the LV1 and LV2 event streams and rates. As was discussed in paragraph 1.5.3, the EVB switch will have to sustain an aggregate bandwidth of 500 Gb/s.

There are many similarities between an EVB switch and those used in telecommunications and high-speed networking [Bars90]. The switch design will benefit a lot if commercially available equipment can be used. This will lead to much more economical solutions than in the case of a custom design. The main differences between a switch suitable for event building and a telecommunication switch, are on the assumed patterns of traffic. In telecommunications, random input–output interconnection patterns are assumed usually. Traffic models for high-speed data networking assume random traffic, or data arriving in packet trains. In event building however, the interconnection patterns are a sequence of input-output combinations that might be known beforehand or can be calculated. This is because, consecutive events will be destined to different outputs in a predetermined way, so that the load of the EFU can be balanced.

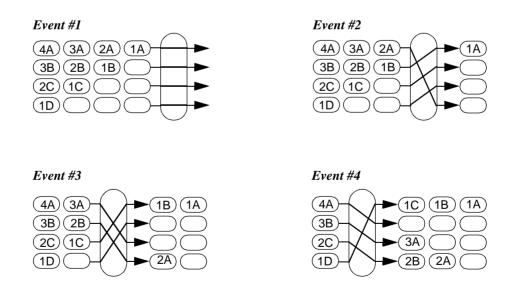

Figure 2.3: Barrel shift network

All the fragments of an event will always be addressed to the same destination. Next events, will be forwarded to different destinations, depending on the way the EFU scheduling is done. This rather simple traffic pattern may lead to serious competition for the same output of the switch, commonly referred to as output blocking. Because of this high traffic predictability, techniques like *barrel shifting* or more generally, *input traffic shap-ing* [Bars90] can be implemented to minimize the output-port blocking.

Figure 2.3 illustrates the operation of a simple barrel shift network. Each of the sources transmits event fragments to different destinations in each time slot. After a full cycle of input-output interconnections has taken place, all the fragments of the first event will have arrived to a destination and so on. The barrel shift network of Figure 2.3 assumes event fragments of equal size. Its operation can be further extended to the more general case when the event fragments are of non-equal size. The barrel shift network requires an external control to synchronize the transmission of the sources (or the connection configuration of the switch) in isochronous intervals. Building such a control for a switch with a relatively high number of ports can be a difficult task and be a potential bottleneck in the overall event builder performance. The barrel shift networks have been successfully deployed in event building systems with a relatively small number of switch ports.

Another possible way to reduce the output blocking is traffic shaping of the sources. The RDPM are designed to have the capability to randomize the order of injecting event fragments to the EVB network, relatively to the arrival order of requests from the EVM. This can be achieved by some logic built into the RDPM that will implement a randomization algorithm to selectively pick entries from the FRB and transmit the appropriate fragment.

Common to telecommunications and data networking, the event builder sources can implement the rate division technique, for traffic shaping. Using rate division, each source will transmit to a destination only a fraction of the link bandwidth, so that the sum of the individual rates reaching a destination is less or equal to the full link bandwidth. Rate division is mostly applicable to ATM networks, were each virtual connection can have its own specified sending rate. A survey of representative ATM switching techniques, is done in [Pryc94]. Recent work with  $4 \times 4$  and  $8 \times 8$  ATM event builders for the CDF experiment, has shown superior performance when rate division is implemented [Baue96].

The approach of rate division is particularly interesting, when parallel event building is adopted—the destinations assemble several events simultaneously—because the unused bandwidth during a fragment transmission is used for transmitting fragments to other destinations.

To construct a switch network with the number of ports envisaged in the CMS DAQ system, smaller switches can be connected together. The switches comprising the network can be arranged in a single or in multiple stages. A simple interconnection topology with a single stage is that of the cross-bar switch.

One major issue when smaller switches are cascaded together to form a larger network is the potential internal blocking that may occur under certain load conditions. This can happen when two different sources send to two different (or the same) destinations, but the messages must cross the same internal node of the network. The cross-bar switch offers several paths between two different end-points, hence internally has non-blocking properties. Output port contention can still occur, in particular when they are used for event building without any traffic shaping.

The cross-bar network fully interconnects N sources to N destinations and therefore it scales as  $O(N^2)$  when new nodes are added. This scaling property of the cross-bar network makes it impractical for constructing large scale networks.

Better scaling behavior can be achieved with multi-stage interconnection networks (MIN). In a MIN, the path from a source to a destination can traverse one or several intermediate switches, assembled into stages. For that reason, a MIN can be more prone to internal blocking than a cross-bar switch. MIN interconnection topologies and their properties have been investigated since very early for telecommunications and data networking purposes [Ahma89]. Their blocking properties and scaling characteristics are very well understood today [Fahm95] [Turn97].

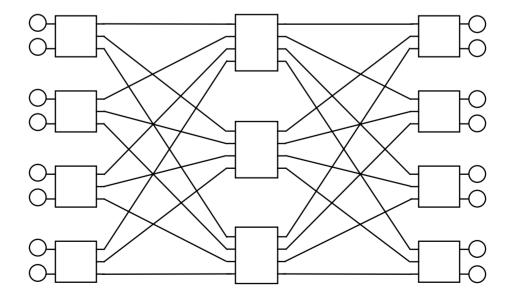

The main advantage of MIN that makes them more attractive than cross-bars, despite their inherent complexity, is their scaling behavior. They can be constructed with less crossing points than the cross-bar network and provide essentially the same non-block-ing characteristics. The Clos network illustrated in Figure 2.4, has a third stage that provides at least one more path between any source and destination. A three-stage, *N*-port Clos network can be built by smaller switching elements of size  $n \times m$  for the first switch stage,  $p \times p$  for the second stage and  $m \times n$  for the third stage, where the values for p, m and n are given as  $p = \frac{N}{n}$ , m = 2n-1 and  $n \approx \sqrt{\frac{N}{2}}$

Figure 2.4: Clos network with 3 stages

The Clos network scales as  $O(N\sqrt{N})$ , hence for large number of input–output ports *N*, the total number of crossing points can be several times smaller than in a cross-bar switch. From the connectivity point of view, it can be seen that when m > 2n - 1 the Clos network can be internally non-blocking. However, it is much more difficult to obtain a similar non-blocking condition in cases like the ATM networks, where the individual virtual channels may vary their bandwidth requirements with time. More relaxed non-blocking conditions can be obtained by limiting the blocking probability to a sufficiently low value. Those types of networks are referred to as rearrangeably non-blocking.

Other types of MIN like Banyan [Goke73] and Benes [Turn97] have been investigated. Although they are internally blocking, they have a considerably better scaling behavior *e.g.*,  $O(N\log N)$ . An enormous amount of research work in the MIN area, has provided a lot of insight in their blocking characteristics. Under certain assumptions on the input traffic and the switch organization, Benes networks can have very low congestion probability [Bian93]. There is evidence that this non-blocking behavior can be expected also when the switch size reaches the size of the switch needed by the CMS DAQ system [Chan96].

Inherently blocking networks can be made non-blocking with appropriate time-ordering of the data entering the network. This is more difficult to achieve in a telecommunications or data network, were the traffic is assumed to be of random nature. It is however much easier in the event building case where the connection patterns are well defined.

The fault tolerance of the switch fabric is another important issue in the event builder design. Depending on the switch architecture, a single link failure in the switch may disable several destinations in the EFF. A switch with a large number of ports, as it is considered here, can be particularly prone to failures. Careful selection of the switch interconnection topology and its technology can minimize the effects of possible failures.

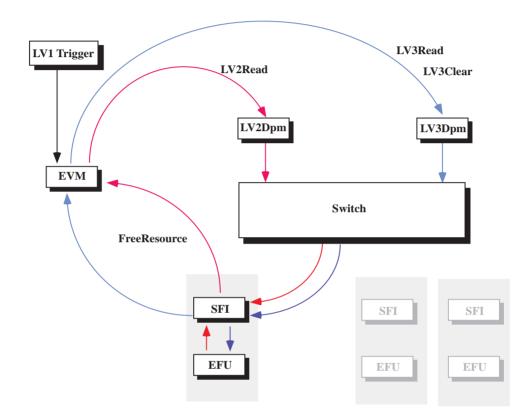

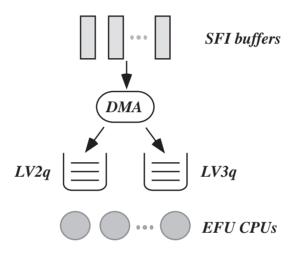

## 2.1.3 The Switch-to-Farm Interface (SFI)

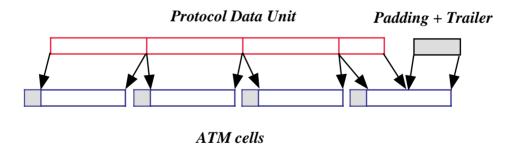

The SFI is the connection point between the EVB switch fabric and the EFU. The last stage of the event building is carried out by the SFI. Each switch output has its own SFI, which is attached to one EFU. Each SFI has to assemble the incoming fragments belonging to the same event into separate entities of sub-events (for the LV2-trigger) or full events (for the LV3-trigger).

The SFI operation has many similarities with that of the RDPM. Its function can be conceived as that of an inverted RDPM. It has a network interface to connect to the switch fabric and an I/O bus to connect to the EFU. Its internals are essentially the same with the RDPM, with the main difference that its output is not driven by the EVM. Instead, it is driven from the EFU that sends requests for the next assembled event to be processed. The current design of the CMS DAQ architecture, foresees a slightly modified version of the RDPM to be used for the SFI. It will be enhanced with the necessary logic to communicate to the EVM the EFU requests for reading a new event, clearing a processed event or discarding a LV3-part of an event.

Alternative ways to implement the SFI functionality are considered also. One is the use of a modified version of the DSP-based RDPM (VORTEX) [Bran95]. This alternative is attractive mostly because of the simplicity and versatility of the VORTEX design, that makes it more easy to adapt from operating as RDPM, to the SFI operation. It also requires additional logic to interface to the EVM network.

A second alternative is to emulate the operation of the SFI, in software that is running on the EFU. This idea of an emulated SFI is particularly attractive, because it eliminates any hardware design, construction and maintenance as required for a custom designed system. An emulated SFI is much simpler to build, provided that the EFU that can have the required additional resources to assemble the incoming event-fragments into events. As the previous SFI candidates, the interface to the EVM is not addressed either. It can be thought however that this task can be easily handled from the EFU itself because very few additional resources will be required. The software emulated alternative is extensively studied in Chapter 6.

The SFI has to be capable to handle the incoming event-fragment rate, resulting from the requests of its attached EFU. The same requirement is valid also for the network interface controller that connects to the switch fabric. Estimated values of the incoming event rate are approximately 100 new events per second for a farm of 1,000 EFU. The arrival rate of individual fragments however, is much higher. The bursty nature of the incoming traffic of the SFI, can have severe implications on the SFI performance. The effects of this on the network interface controller will be studied in Chapter 6, together with the implications on the overall SFI performance.

## 2.1.4 Event Manager (EVM)

The event manager is the key component for the synchronization of the event builder. It is a custom made hardware device that has the necessary logic to associate each LV1-trigger event to a destination in the EFF.

The EVM is notified by the different EFU for their availability, by messages containing filter resources (FRS). Each FRS, points to an available buffer in one EFU. It is expected that the EFU independently from the occurrence of the LV1 triggers, will send to the EVM such messages. The EVM will hold the FRS in a queue or a table. At a LV1-trigger, occurrence, the EVM will pick an FRS, it will assign to it an event number and broadcast it to the LV2 or the LV3 group of RDPM. Another function of the EVM is to forward to the LV3 group of RDPM, the CLEAR messages for the sub-events that failed to pass the LV2 trigger.

The functionality of the EVM is rather simple. However, in order to minimize the event building latency, the requirements on its response time are quite high. Ideally the EVM could provide an FRS to the RDPM in a time interval equal to the FED read-out latency of the RDPM. The EVM is also the place where the EFF scheduling can be done. With some intelligence added to the EVM, it can order the broadcasts of FRS according to a given scheduling policy. Such scheduling policy could be based for instance on the frequency of arrivals of the FRS from each of the EFU. This can be particularly useful in the case of a heterogeneous EFF *i.e.*, not all the EFU have the same capacity.

The communication media used between the EVM with the RDPM and between the EVM and the EFU, is an important design issue. Between the EVM and the RDPM, a multicast type of communications seems appropriate. It has relatively modest bandwidth requirements but the type of the expected traffic will be very bursty. More complicated is the case of the network utilized between the EFU and the EVM. It will also have modest bandwidth requirements, but it may be severely congested due to the high number of sources sending to a single destination.

Equally important to the functional design of the EVM, is its tolerance to failures. The EVM, in the current event building architecture has a prominent function from the reliability point of view. Failures of the EVM, will prohibit any event building to take place. A redundant design seems appropriate to reduce to a minimum the time that the DAQ system is unavailable due to EVM failures.

## **2.2** The Event Filter Farm (EFF)

The concept of using a farm of computer systems for the event selection and processing, is a common practice in HEP experiments. With the advent of powerful workstations and personal computers, farms of commodity equipment have become very attractive solutions for the on-line purposes of HEP experiments like in HERA-B [Gell95]. The main reason for that is to provide enough capacity to cope with the LV1-trigger rates. The different events accepted from the LV1-trigger, are not correlated by each other. Hence, the idea of filtering events into several independent nodes, that do not require any kind of interaction seems appropriate. To satisfy the physics requirements of the LHC experiments, a high LV1-trigger rate must be accommodated. The CMS DAQ system is designed to be able to operate at a maximum sustained LV1-trigger rate of 100,000 events per second (Table 1.5).

#### 2.2.1 Architecture

The CMS EFF, consists of some 1,000 EFU connected to the EVB switch through the SFI. It must provide a sufficient amount of processing power to accommodate the maxi-

mum LV1-trigger rate and the load of the LV2 and LV3 filtering processes. Such a design of the event filtering part of the DAQ system, has the advantage of a very flexible scaling behavior. Depending on the processing power of the EFU deployed in the EFF, their number can be reduced or increased. Also, due to the nature of the event filtering —nonrelated events— multiprocessor systems can be easily assumed. Again the aggregate computing power required by the EFF can be achieved by adding more processing units in the EFU, given sufficient expansion capability.

The current construction schedule of LHC, envisages a period of a few years of operation at lower luminosity. During that period, the expected physics event rate will be much lower than that of nominal luminosity operation. A flexible EFF, can be initially built with either less powerful EFU or with a smaller number of EFU that will be sufficient for the low-luminosity period and later can be upgraded to its nominal power.

The ability to design a flexible event filtering system is of utmost importance for the success of the CMS DAQ system. With a relatively long design and construction phase until the year 2005, and the immense progress of the computer industry, it is very difficult to make precise predictions of the technology and the computing power that will be economically available at that time. Additionally, unexpected physics phenomena may need to be studied, resulting in event rates higher than what the current physics simulations suggest.

#### 2.2.2 Scheduling

A farm with the size needed by the CMS DAQ architecture, must also employ a flexible scheduling of its resources. A simple approach could be the EVM to allocate EFU to new LV2 and LV3 triggers in a round-robin manner. However, a more sophisticated farm scheduling seems to have some obvious advantages. Firstly, EFU fault isolation will be straightforward. The faulty EFU can be removed immediately from the list of available destinations, thus preventing events to be forwarded to a non-functioning EFU. Secondly, during the lifetime of the CMS experiment, several upgrades of the EFU may take place. This will result into a non-homogeneous EFF consisting of EFU with very different performance and capacity. A dynamically scheduled farm, can better balance the event filtering load amongst different EFU. A possible way to implement dynamic EFU scheduling could be based on monitoring the rate of requests arriving from each of the EFU. The EFF scheduling policies can be implemented by the EVM.

#### 2.2.3 Control and Management

Besides the main control exercised by the EVM for scheduling purposes of the EFF, functions like EFU initialization and restart, status monitoring and alarm condition detection must also be carried out. This type of control, will be part of the general detector control system (DCS) that will command all crucial DAQ sub-systems.

Alarm conditions and EFU failures together with diagnostics information will be communicated to the operators, so that the necessary actions can be taken. Data collected from the EFU status monitors, will be analyzed continuously to ensure the correct EFF operation.

The initialization of the EFF and management of its resources into smaller partitions is also relevant. This can be particularly useful for testing new event selection algorithms, or during periods of lower luminosity, some of the EFF resources can be allocated for tasks related to the off-line data analysis.

#### 2.2.4 Alternative Solutions

There are also several alternative ways to build the EFF. They can be more generally classified into custom and commercial alternatives. For the purposes of the CMS DAQ system, building a custom designed EFF may have a tremendous financial impact. The design, construction and maintenance costs of an EFF consisting of custom made EFU (*e.g.*, based on DSP) may quickly become dominant to any advantages gained by such a design.

From the commercially available alternatives, the massive parallel processing (MPP) systems seem very close to the EFF and EVB architectures. The high speed communication network, the large amount of computing power and sometimes the scaling flexibility are their more prominent resemblances. The MPP systems are not considered because most of them are proprietary products and their integration (even though sometimes it is based on commercially available systems) follows a different and slower path than that of the widely commercialized systems. For the lifetime of the CMS experiment, the MPP market is considered too small to offer economical solutions and upgrades.

Another possible alternative could be the use of embedded systems, adapted to the EFF requirements. For instance, a farm consisting of digital signal processors could be constructed to offer the required performance. This possibility is not considered for the same arguments of wide commercial availability and proprietary origins. In addition, the adoption of an on-line computing system used for event filtering that is entirely different from that used for the off-line analysis, is not very attractive as it will make more difficult the development of the event filtering algorithms.

## **2.3** The Event Filter Unit (EFU)

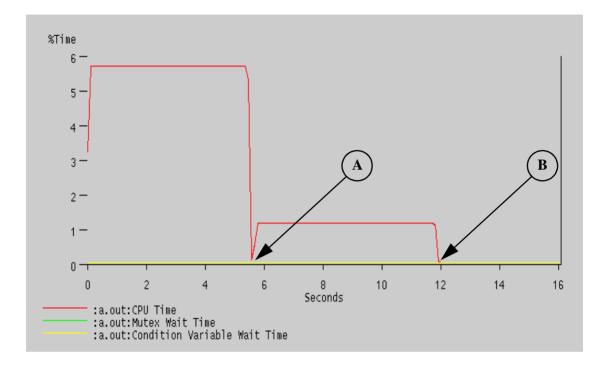

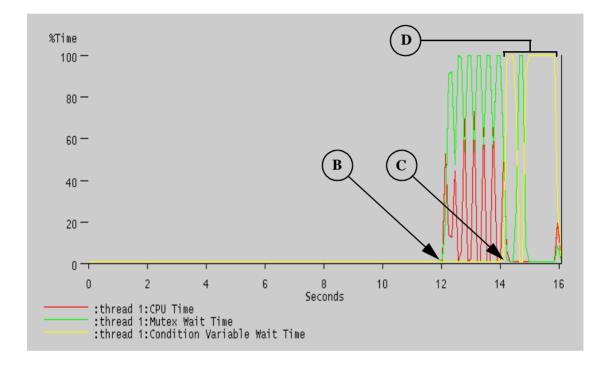

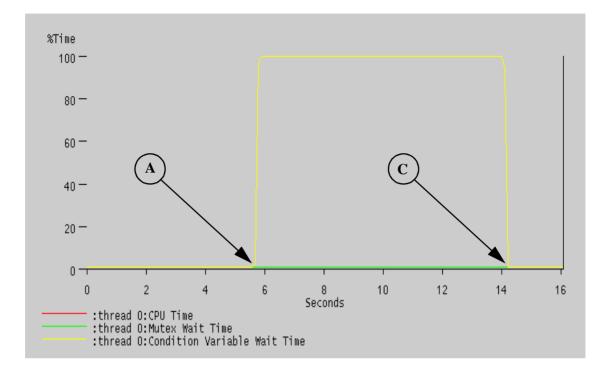

The EFU is a computer system, where assembled sub-events or full events will be processed by the LV2 and LV3 filtering processes, respectively. It has to provide sufficient computing power to ensure that the rate of filtering events is higher than the rate of event arrivals. Also it must have the necessary memory and I/O bandwidth to handle the incoming (and to a less extent the outgoing) event data-stream and also the needs of the filtering processes themselves.