## DISSERTATION

# The Hardware Track Finder Processor in CMS at CERN

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

eingereicht an der Technischen Universität Wien Fakultät Elektrotechnik

von

Alexander Kluge, CERN/PPE, CH-1211 Genf, Schweiz geb. 15. April 1968, Wien

Wien, im Juli 1997

## Begutachter

Prof. Dr. techn. Franz Seifert

Prof. Dr. techn. Christian Fabjan

### Kurzfassung

Für das für 2005 geplante Hochenergiephysikexperiment CMS (Compact Muon Solenoid) am CERN in Genf wurde ein Myon-Trigger- und Impulsmeßsystem (Track Finder Processor) entwickelt. Der 'Track Finder Processor' gestattet es, die physikalische Relevanz von hochenergetischen Kollisionen abzuschätzen und nur die Messdaten von interessanten Ereignissen den entsprechenden Analyseeinheiten zuzuführen.

Die Daten von mehr als 200000 Detektorzellen werden benutzt, um den Ort, bzw. die Spur von Myonen aufzufinden und deren Transversalimpuls zu messen. Alle 25 ns wird ein neuer Spurensatz generiert. Die Bestimmung von Flugbahn und Transversalimpuls der Myonen am Wechselwirkungspunkt benötigt insgesamt 350 ns. Die 'pipeline'-Architektur verarbeitet neue Spurensätze mit der geforderten Rate von 40 MHz, um das Gesamtsystem totzeitlos betreiben zu können.

Im Rahmen dieser Arbeit wurden die Spezifikationen und das Gesamtkonzept des Prozessors detailliert ausgearbeitet. Simulationen wurden ausgeführt, um die am einsetzbare Meßmethode und Implementierungstechnologie effizientesten auszuwählen. Zusätzlich wurden schon existierende Systeme bewertet und deren Spezifikationen mit denen des 'Track Finder Processors' verglichen. Die klassische Methode bei Hochenergiephysikexperimenten ist, nach vorgegebenen Spurensätzen bzw. Bitmustern in den Meßdaten zu suchen und deren Eigenschaften zu bestimmen, wobei vordefinierte Muster mit den tatsächlich auftretenden verglichen werden (Mustervergleich). Die hohe Zahl der Datenkanäle des 'Track Finder Processors' und die komplexen Anforderungen an die örtliche Detektorauflösung erlauben es jedoch nicht. diese Methode zur Anwendung zu bringen. Ein sogenannter Spurverfolgungsalgorithmus wurde entworfen, der ausgehend von einzelnen Spurelementen ganze Spuren durch den Detektor zusammenzusetzen vermag. Anstatt große, vorsimulierte Vergleichsdatensätze zu speichern, wird ein Algorithmus zur Spurensuche und Impulsbestimmung direkt angewandt. Dadurch wird die Umsetzung in Hardware ermöglicht, womit die für das Gesamtexperiment vorgegebenen Anforderungen erfüllt werden. Der Meßalgorithmus wurde in digitaler Logik implementiert. Ausführliche VHDL-Hardware Simulationen wurden durchgeführt, um den Algorithmus und seine Hardware-Repräsentation zu optimieren. Ein FPGA (Field Programmable Gate Array)-Prototyp und ein Testsystem wurden entwickelt. Eine Machbarkeitsstudie wurde durchgeführt, um zu zeigen, daß der Prozessor mittels heute erhältlicher Technologie als 'Application Specific Integrated Circuits' (ASICs) realisiert werden kann und den technischen Anforderungen durch das Experiment gewachsen ist.

## Abstract

The work covers the design of the Track Finder Processor in the high energy experiment CMS (Compact Muon Solenoid, planned for 2005) at CERN/Geneva. The task of this processor is to identify muons and measure their transverse momentum. The track finder processor makes it possible to determine the physical relevance of each high energetic collision and to forward only interesting data to the data analysis units.

Data of more than two hundred thousand detector cells are used to determine the location of muons and measure their transverse momentum. Each 25 ns a new data set is generated. Measurement of location and transverse momentum of the muons can be terminated within 350 ns by using an ASIC (Application Specific Integrated Circuit). A pipeline architecture processes new data sets with the required data rate of 40 MHz to ensure dead time free operation.

In the framework of this study specifications and the overall concept of the track finder processor were worked out in detail. Simulations were performed in order to select the most appropriate measurement method and implementation technology. Already existing systems were evaluated and their specifications were compared with those of the track finder processor's. The classic method in high energy physics experiments is to search for predefined tracks or bit patterns in the measurement data and to determine their properties. The predefined patterns are compared to the found patterns. The high number of data channels of the track finder processor and the complex requirements to the spatial detector resolution do not permit to employ a pattern comparison method. A so called track following algorithm was designed, which is able to assemble complete tracks through the whole detector starting from single track segments. Instead of storing a high number of track patterns an algorithm for track finding and momentum measurement is employed directly. This enables to realize a hardware implementation within the requirements given by the experiment. The algorithm was translated to the level of digital electronics. Comprehensive simulations, employing the hardware simulation language VHDL, were conducted in order to optimize the algorithm and its hardware implementation. An FPGA (field programmable gate array)-prototype and a test system was designed. A feasibility study to implement the track finder processor employing ASICs was conducted. The study proves that the track finder processor can be implemented using today's technology.

## Acknowledgements

#### This dissertation is dedicated to my parents, Irene and Kurt.

I would like to thank Professor Franz Seifert for supervising my dissertion.

Professor Christian Fabjan I wish to thank for his advice and for being co-supervisor.

I want to thank Dr. Friedrich Szoncso and Dr. Claudia Wulz for entrusting me the task to plan an important part of the experiment and for giving me autonomy during this work.

I owe Dr. Friedrich Szoncso thanks for reading and criticizing my dissertation.

To Dr. Norbert Neumeister and Dipl.-Ing. Torsten Wildschek I express my thanks for many valuable suggestions and the repeated assistance in Physics.

I especially appreciated the teamwork with Dipl. Ing. Torsten Wildschek.

The seemingly insurmountable problems with the operation of VHDL simulators I could only solve with the help of Serge Brobecker.

When it was necessary to prove that the VHDL simulations could also be transformed into hardware, a prototype was built and I relied on numerous pieces of advice by Dipl.-Ing. Anton Taurok.

The collaboration with Stefan Puttinger during the trigger test was of decisive significance for success.

To my whole family, especially to my parents, Irene and Kurt, I am thankful for having had the chance to carry out my studies. For this reason my dissertation is dedicated to my parents.

My special thanks certainly goes to the Austrian Nation for making my stay at CERN possible by the doctoral scholarship which I received.

## **CARPE DIEM**

Usually scientific papers are comprehensible only to a small readership. In order to serve also readers not familiar with physics or electronics an additional feature is provided in the next pararaph. Like the 'Hitchhiker's Guide to the Galaxy' this document contains a very important phrase printed in large capital letters on one of the first pages.

## **'DO NOT PANIC'**

## **Table of Contents**

| Kurzfassu    | ing                                                                                                                   | i |

|--------------|-----------------------------------------------------------------------------------------------------------------------|---|

| Abstract     | ii                                                                                                                    | i |

| Acknowle     | dgements                                                                                                              | 7 |

| Table of C   | Contents iz                                                                                                           | ζ |

| СНАРТЕН      | <b>R 1. Introduction</b>                                                                                              | L |

| 1.1.<br>1.2. | Short introduction to high energy physics experimental methods<br>Data acquisition in high energy physics experiments |   |

| СНАРТЕН      | R 2. Track finder processor environment                                                                               | ) |

| 2.1.         | Experiment CMS - Compact muon solenoid                                                                                | ) |

| 2.2.         | Trigger and data acquisition of CMS                                                                                   |   |

| 2.3.         | CMS first level trigger 13                                                                                            |   |

| СНАРТЕН      | <b>R 3.</b> Track finder processor overview 20                                                                        | ) |

| 3.1.         | Track finder processor specifications                                                                                 | ) |

| 3.2.         | Trigger environment and implementation in other high energy physics<br>experiments                                    |   |

| СНАРТЕН      | R 4. Evaluating the CMS track finder processor 30                                                                     | 5 |

| 4.1.         | Feasibility study: Feature extraction methods                                                                         | 5 |

| 4.2.         | Implementation technologies                                                                                           |   |

| 4.3.         | Extrapolation method - Feasibility from physics point of view 59                                                      | ) |

| СНАРТЕН      | R 5. Detailed architecture and functionality of the CM                                                                | 5 |

|              | track finder processor 69                                                                                             | ) |

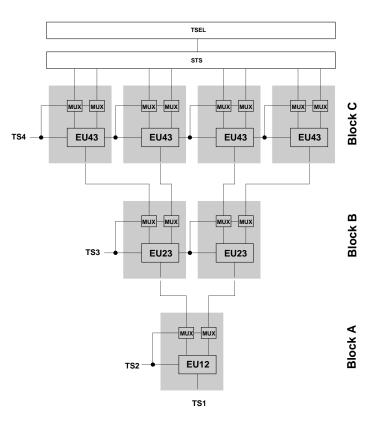

| 5.1.         | Logic segmentation                                                                                                    | ) |

| 5.2.         | Track finder processor algorithm                                                                                      | l |

| 5.3.         | Conclusion: Processor architecture and simulation                                                                     | 5 |

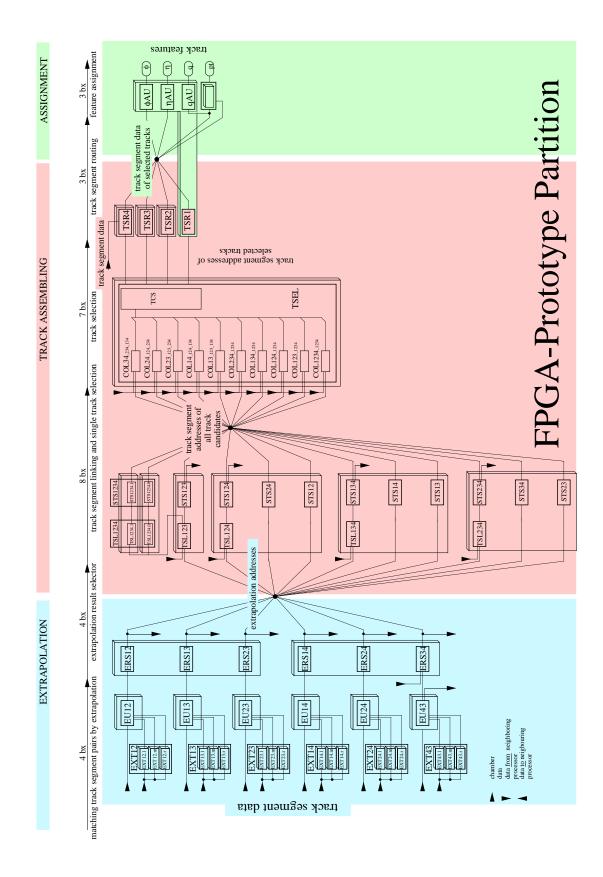

| CHAPTER              | <b>6. FPGA prototype layout and test</b>                                                   | 88    |

|----------------------|--------------------------------------------------------------------------------------------|-------|

| 6.1.<br>6.2.<br>6.3. | Implementation strategy<br>Block diagram of implementation<br>Test configuration           | 89    |

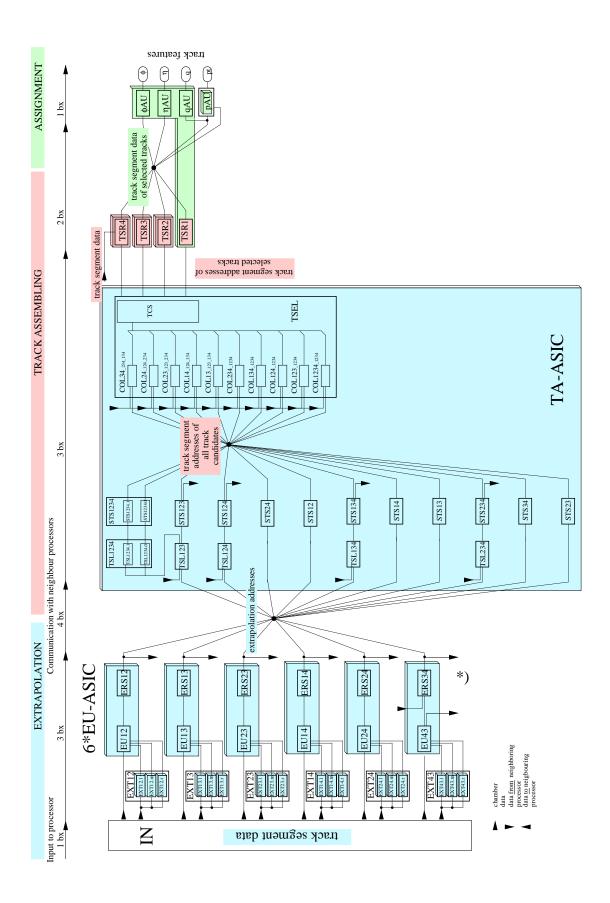

| CHAPTER              |                                                                                            |       |

|                      | CMS track finder processor                                                                 | 93    |

| 7.1.<br>7.2.         | Implementation strategy and problems<br>System partition, gate count and timing estimation |       |

| CHAPTER              | 8. Error detection and location                                                            | . 102 |

| 8.1.<br>8.2.         | Error detection<br>Error location                                                          |       |

| CHAPTER              | <b>9.</b> Conclusion and further perspectives                                              | . 108 |

|                      |                                                                                            | 108   |

| Appendix             | A                                                                                          | . 111 |

| A.1.<br>A.2.         | Hardware simulations<br>VHDL-VHSIC hardware description language                           |       |

| Appendix 1           | В                                                                                          | . 117 |

| B.1.                 | Example of the hardware implementation of the track segment lir modules.                   | 117   |

| B.2.                 | Several cancel out schemes                                                                 | 118   |

| Appendix             | C                                                                                          | . 120 |

| C.1.                 | Alternatives to the base line ASIC-system partitioning                                     | 120   |

| Appendix 3           | D                                                                                          | . 124 |

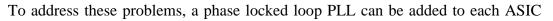

| D.1.                 | System solutions for high speed multi ASIC systems                                         | 124   |

| Bibliograp           | hy                                                                                         | . 127 |

| LEBENSL              | AUF: Dipl. Ing. Alexander Kluge                                                            | . 135 |

| CURRICU              | JLUM VITAE:<br>Dipl. Ing. Alexander Kluge                                                  | . 137 |

#### Structure of this work:

Chapter 1 gives a short introduction to high energy physics and the applied data acquisition methods.

Chapter 2 covers the environment of the track finder processor. The experiment setup is explained shortly and the data acquisition of the system is described in more detail.

Chapter 3 deals with track finder processor specifications. The system requirements are compared to previously implemented systems.

In chapter 4 both the realisation methods and the implementation technology possibilities for the track finder processor are discussed and the most suitable are selected. At the end of the chapter the realisation feasibility of the chosen realisation method is proven.

In chapter 5 the algorithm and its implementation in hardware is discussed comprehensively.

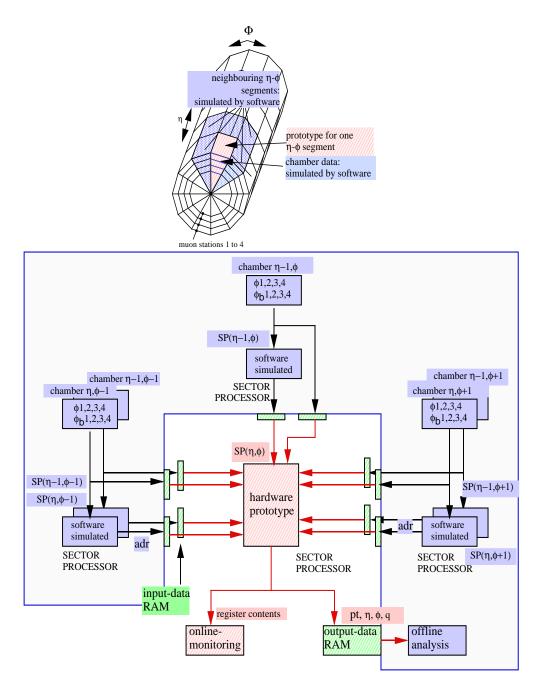

Chapter 6 deals with the design of a FPGA (field programmable gate array) prototype.

Chapter 7 covers the problem of final implementation employing ASICs (Application Specific Integrated Circuit). A feasibility study is presented where system partitioning and timing analysis show that the system is implementable within the given requirements even with today's technology.

Chapter 8 presents an error detection and location scheme for the entire track finder processor system.

Chapter 9 concludes the work and gives further perspectives of the track finder processor project.

The research and development work for the track finder processor project has mainly been conducted by a physicist, Dipl-Ing. Torsten Wildschek, and me. The responsibilities for the project were shared between the two of us. Torsten Wildschek was responsible for the physics aspects of the processor while my duty was to carry out research and development regarding the hardware aspects of the processor. Since this document concludes the results concerning the hardware aspects of the track finder processor special emphasis has been given to the description of the hardware. However, in order to understand the entire project also physics studies (see chapter 4.3., "Extrapolation method - Feasibility from physics point of view") and the design of the surrounding environment (see chapter 2, "Track finder processor environment") are described, although, only to a certain minimum expense. Of course the design of the track finder processor also influenced the general concept of the first level muon trigger (see chapter 2.3., "CMS first level trigger"). For further information on topics not directly related to the hardware of the track finder processor refer to the literature given in the descriptions.

Of course in some aspects of the design process a close team work was established between Torsten Wildschek and me. This is especially true for working out the specifications of the track finder processor, described in chapter 3.1., and finding a appropriate track finding strategy which fulfils the needs from physics point of view and is found to be implementable in hardware (chapter 4.1.). However, once the requirements from physics point of view were understood the hardware design process was carried out rather independently by me.

This included

- to perform simulations in order to support chosing the implementation methodology,

- to work out a suitable implementation technology,

- to work out a track finding algorithm implementable in hardware,

- to design the overall concept of the processor,

- to design the detailed architecture of the processor and components,

- to simulate the behavior and optimize the hardware architecture and algorithm,

- to design a FPGA-prototype,

- to design a trigger test bench,

- and to perform a feasibility study for a final implementation.

(see chapters 4.1., "Feasibility study: Feature extraction methods", 4.2., "Implementation technologies", 5, "Detailed architecture and functionality of the CMS track finder processor", 6, "FPGA prototype layout and test", 7, "Feasibility study for ASIC implementation of the CMS track finder processor", 8, "Error detection and location").

## **1** Introduction

In the following chapters a short overview of techniques in experimental high energy physics is given. The chapter is aimed at readers not familiar with high energy physics experiments. Chapter 1.1. gives a short introduction to high energy physics experimental methods. In chapter 1.2. methods for data acquisition are described.

## **1.1. Short introduction to high energy physics experimental methods**

At CERN (European Laboratory For Particle Physics) in Geneva a new particle collider LHC (Large Hadron Collider) has been designed and is going to be built. The LHC project [1] consists primarily of the addition to the already existing LEP (Large electron positron collider) tunnel of a superconducting magnet system with two beam channels. While the LEP collides electrons and positrons with an centre of mass energy of up to 200 GeV, the LHC is designed to bring two proton beams into collision resulting in 14 TeV centre of mass collisions.

Given the size of the beam and the number of particles within the beam a probability of their collision can be given. However, not all collisions occur with the same impact. The transverse momentum  $p_t$  (momentum perpendicular to the beam direction) of the particles emerging from a collision is a measure for the power of the impact. Thus one wants to observe as many collisions with a high number of particles having as high a transverse momentum as possible.

At one of the experimental areas the experiment CMS (Compact Muon Solenoid) [2] is planned to be installed (see fig. 2.2). The aim when designing detectors for collider experiments is to cover a full  $4\pi$ -area around the interaction point, in order to ensure the detection of all produced particles. As constructing a ideal sphere-shaped detector system poses problems, a cylindrical shaped form is realized to cover the interaction point.

Generally seen two types of detectors exist. One type are detectors which measure the energy of particles and are called calorimeters [3]. The second type of detectors measures the position of charged particles. Wire chambers belong to this type. They are described shortly as they are used by the track finder processor. Wire chambers are based on the principle of ionisation. The basic configuration consists of a container with conducting walls. It is filled with a gas. Along the axis of the cylinder a conducting wire is suspended to which a positive voltage relative to the walls is applied. When charged particles traverse the chamber volume, gas molecules are ionized and electron-ions pairs are being created. Under the action of the electric field, the electrons will be accelerated towards the anode and the ions towards the cathode. Is the applied electric field high enough, an ionisation avalanche is triggered. Thus the deposited charge on the wire is amplified and can be detected by the read out electronics.

A multi wire proportional chamber comprises a number of single wire chambers arranged next to each other. It allows to cover a large measurement area.

Drift tubes are wire chambers where the drift time of the electron avalanche is used to determine the exact position of incident. The drift time is the time difference between the arrival of a particle at the chamber and the deposit of the charge at the wire. It depends on many parameters (gas, field). The resulting drift speed is in the order of 50  $\mu$ m/ns.

Applying drift tubes allows to determine the position of particles with a resolution in the order of 100  $\mu$ m. However, a typical problem of drift tubes is the so called left-right ambiguity of the position measurement. A single drift cell does not give any information if the particle crossed on the left or right hand side of the wire.

## **1.2.** Data acquisition in high energy physics experiments

In the first section basic structures of data acquisitions are described, as they are used for the experiment CMS.

The second section covers basic track finding methods.

#### **1.2.1. Data acquisition architectures**

When colliding protons against each other only a small fraction of occurring interactions involve high energy quark-quark collisions. There will be a large number of so called soft collisions which are of no particular interest.

In LHC some type of interactions are supposed to be examined which have a probability to occur once in  $10^{11}$  interactions. As experiments become more and more complex the amount of data taken for one interaction is very large. In case of CMS the number of channels is about  $10^8$ . The resulting compressed data stream has a size of 1 MByte per event. Recording all events on a permanent storage device and performing off-line analysis at a later time to evaluate interactions of physical relevance is out of question. The data amount per second produced by CMS yields 1 MByte  $\cdot$  40 MHz =

$4 \cdot 10^{14}$  bit·s<sup>-1</sup>. Thus it is obvious that a selection of interesting events has to be performed prior to writing the data to a permanent storage device such as a tape drive.

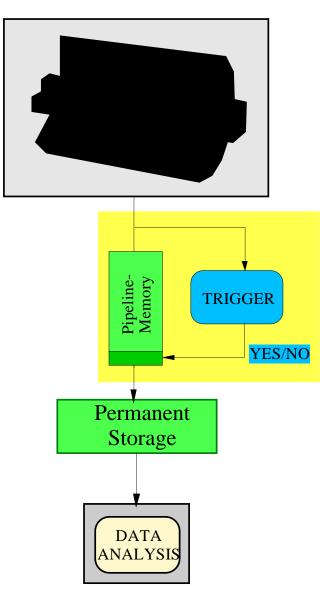

Fig. 1.1.: Data Acquisition using a trigger to select interesting data on-line.

Trigger devices evaluate the occurring interactions. Thev select all good event candidates and reject most of the back ground events. Features are extracted from each event. Features are variables containing the relevant physics message that can be used for the final decision of the trigger. When a decision based on the extracted features is positive the events are recorded, otherwise discarded. Features for trigger decisions can be, for example:

•track multiplicity of an event,

direction of particles,

deflection or curvature of particles to measure momentum,

type of particles,

• deposited energy in the detector,

•missing energy to detect particles which leave the detector without interaction with matter (as neutrinos), but also

• event topology for expected interactions.

During the processing time of the trigger all detector data are stored in a pipeline memory. If the trigger decision is positive the data will be extracted from

the buffer and written onto the permanent storage device. There it is available for off-line analysis (see fig. 1.1).

However, in modern high energy physics experiments the number of read-out channels and the complexity of the ongoing interactions do not allow to perform a trigger decision in one go using all available data in a reasonable amount of time. In CMS the number of channels is  $10^8$  and the required reduction rate of the trigger is as high as  $10^7$ . That means in average only one event out of  $10^7$  is considered worth being stored. However, the dead time, where a trigger processes data from an event and thus is not able to evaluate subsequent events, must not occur.

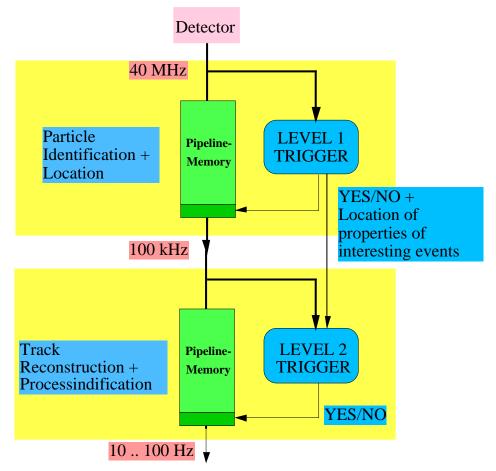

Fig. 1.2.: Two level trigger architecture.

Hence a two or more level trigger scheme is applied (see fig. 1.2). A first level trigger performs an event evaluation based on a subset of all available data. If the first level trigger releases a positive trigger decision, the event data is forwarded to the next trigger stage. In this way the event rate is reduced for the subsequent trigger level offering more decision time for this level. The higher the trigger level the more complex but also time consuming the algorithms become. However, as long as the processing time for a certain level is smaller than the corresponding bunch crossing period, no dead time is introduced to the data read-out. Deviations from the medium event rate must be compensated for by buffers between the various trigger levels.

When the bunch crossing period for a certain trigger level is smaller than the processing time, data from the subsequent interaction arrive at the inputs of the trigger before the previous event was processed. That means the trigger introduces dead time and cannot evaluate each subsequent event. In proton-proton colliders, as the LHC, where the possibility of interactions during a bunch crossing is very high, dead time of the trigger inevitably introduces inefficiencies. For lepton colliders, as the  $e^+e^-$  collider LEP/CERN, where the probability of collisions in a bunch crossing is far below 1, dead times of the trigger system usually do not cause severe inefficiencies. This is because the probability of a second interaction within the trigger processing time is low.

In case of LHC it is vital to avoid any dead time. However, the bunch crossing (bx) period is 25 ns and it is obvious that no decision, even not on the first level, can be found during that time. Two architectures are possible to come by this problem:

- 'Round Robin'- architecture and

- pipeline architecture.

The 'Round Robin' architecture employs a number of parallel running processors. Each processor executes the entire algorithm for one single event. After each occurring event the data is sent to another processor which happens to be idle. When a processor finished its task it puts out the calculated data and is free to obtain the next data set. The number of processors necessary equals the execution time for one event divided by the bunch crossing period. This scheme has the advantage that commercial processors may be employed. However, the hardware effort is high, since the architecture foresees parallel running identical processors. Moreover routing the data stream into the corresponding processor again introduces propagation time and hardware effort.

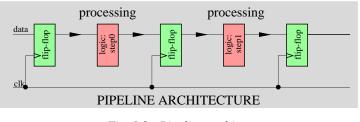

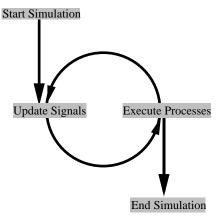

A more elegant solution, especially when employing custom designed digital circuits, is the pipeline architecture. The implementation of the algorithm is partitioned in small calculation steps. The processing time of each step

Fig. 1.3.: Pipeline architecture.

does not exceed the bunch crossing period. The intermediate results of each step are stored in flip-flops. When applying a central synchronous clock to the circuit equal to the bunch crossing rate (see fig. 1.3) the data stream proceeds though the structure accepting a set of input data each clock cycle and outputting a result each clock cycle. The processing time corresponds to the number of processing steps times the clock period. Most algorithms implemented in custom designed digital circuits can be splitted into sufficiently small steps. The advantage is the reduced hardware amount. No processor duplication must be performed. Higher processing times might be a result of storing the intermediate results in the latches.

#### 1.2.2. Track finding in high energy physics

The decision finding process of a trigger can be based on several features. However, here only the methodologies for track finding in position measuring detectors are shortly described. For more detailed information refer to [4].

A large number of methods is known and has been applied in software implementations. Only a few have been realized in hardware applications. The different methods can be classified as global or local. When comparing the available methods to each other one should consider the advantages of a hardware implementation compared to a software application. The obvious advantage is the possible processing speed of any given logic or arithmetic operation. However, the other advantage is that in hardware systems the processor architecture can be adapted exactly to the required needs. In other words one can take advantage of parallel working units. This again reduces the overall computing time. It is obvious that not all track finding methods can be implemented in hardware in an efficient way.

A local method evaluates a subset of the entire data set first and attempts to find a correlation to the remaining data. Local methods often have to make fruitless attempts in order to find track candidates and thus use the same data entity in different combinations. When used in software applications the computing time increases more rapidly than linearly with the number of data entries. However, when implemented in hardware different combinations can be evaluated in parallel. This requires to foresee a number of parallel working hardware blocks. The number of hardware blocks also increases more rapidly than linearly with the number of data entries. Since different combinations are processed in parallel computing time does not increase necessarily with the number of data entries.

A global algorithm evaluates the entire data set at once. The computing time of a global method should be proportional to the number of data entities (points) in the event. Applied in a hardware application a global method is very efficient as long the data set is reasonable small. However, as data set size increases due to the high number of inputs and the necessary interconnect within processing units a global method requires a high number of processing units.

#### 1.2.2.1. Local methods

#### Track following method

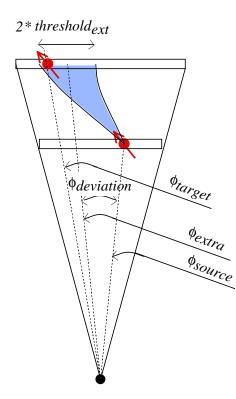

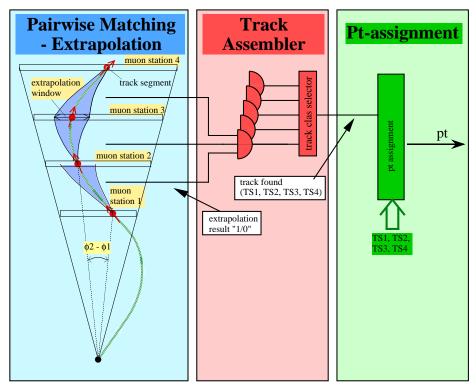

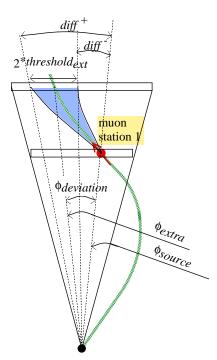

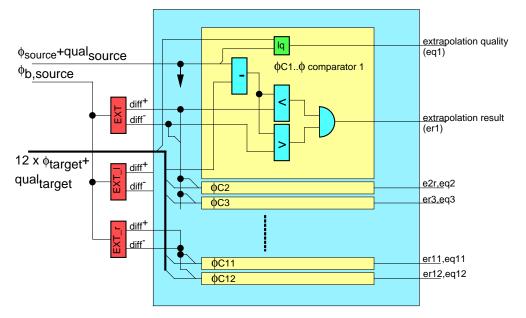

An initial track segment is selected. The next step is to predict a point by extrapolation into the next chamber. The extrapolation may be of zero order simply by choosing the nearest neighbour, first order (straight line), second order (parabola), and possibly higher orders, or other track forms such as circles or helices.

In high resolution detectors where a large number of possible points may occur applying this method in hardware can be time consuming or requires a high number of processing units. In a hardware implementation two options are given. Either one attempts to extrapolate from one point to the points in the adjacent chamber one after the other (in the same way as it is done in software) or one attempts to extrapolate from one point to all other points at the same time in parallel. In the first case the advantage of parallelisation is entirely lost and thus a higher processing time will be the result. In the latter case the possibility must be provided to extrapolate from one point to all other points at the same time. However, if the number of possible extrapolation target points exceeds a reasonable amount a combination of the two options might have to be considered.

#### Track road method

An interpolation between points is used to predict extra points on the track. By using initial points at both ends of a track - and possibly in the centre of curved tracks - a simple model of the track is used to predict the positions of further points on the track, by defining a road around the track model. If a sufficient number of hits is going to be found to be within this road a track is considered to be formed.

The track road method is slower than the track following method. Sometimes it is the only workable method available, particularly in the case of widely spaced detector planes, where the redundancy in the coordinate measurement can be very low. However, even when there is sufficient redundancy the road method can sometimes be superior in performance and speed when compared with the track following method, for example in drift chambers with left-right ambiguity.

However, parallelisation of hardware processing units may prove to be cumbersome when the maximum number of possible reference points from which the track model is derived from exceeds a certain limit. The track road method can be applied efficiently in hardware when points in a reference plane with a low multiplicity are available. For instance this could be the outermost plane and the interaction point. However, being dependent on the proper functionality of a specific detector plane is a severe restriction to the track finding performance.

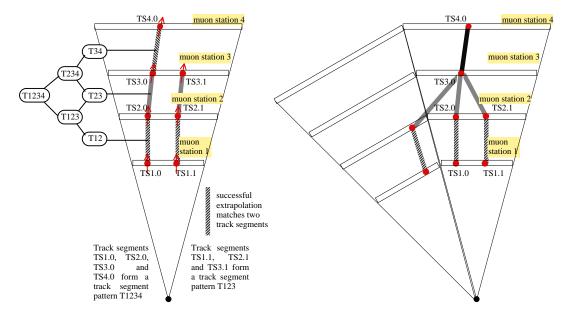

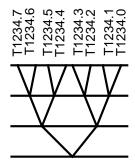

#### Track segment method

The track candidates are formed in two steps. Short track segments are built from points, normally inside sub divisions of the detector. As a result one obtains the position of the cluster and a direction value (track segment). Several track segments are connected to each other using track following or track road methods.

The great advantage of this method is its speed, compared to using all points per track directly. It is therefore appropriate for detectors with a very high point density. In addition, the left-right ambiguity of drift chambers can be resolved at the track segment level.

From point of view of hardware implementation the track finding method has an important feature, namely reducing the data set size (by creating a fixed number of track segments) while maintaining the full detector resolution. As a result the number of points to be processed for the actual track finding algorithm is reduced. Track segments in different detector regions can be formed in parallel. Then a track following or track road method is applied on the reduced data set.

#### 1.2.2.2. Global methods

#### Combinatorial method

All measurements giving a possible track candidate are fitted to a track model. If the requirements for a valid track are met, a track is found. This method is very time consuming. Applied in a hardware system this is only a viable solution when the maximum number of possible points is low.

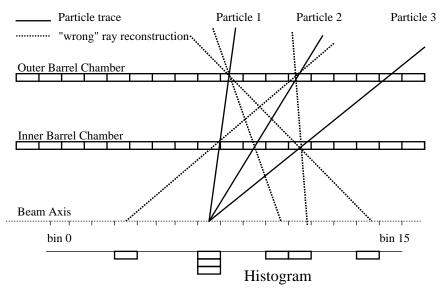

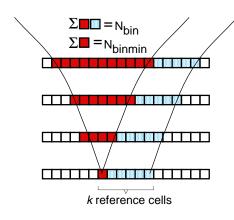

#### Histogramming method

A set of n functions of the measured hit coordinates is defined. The function is chosen in a way that, applied to hit coordinates of the same track, it delivers identical (or at least similar) values. In most times it is attempted to define functions which directly yield the desired property of the track. The function values are entered in a n-dimensional histogram. Hit coordinates triggered by one track will cause a peak in the histogram.

This method is known to be used intensively in software applications. Serially the software processes count the entries into the histogram. Afterwards the filled histogram is evaluated. Employing this method in hardware using parallelisation proves cumbersome when the dimensions of the histogram and the maximum number of

entries get too large. Assuming a two dimensional histogram of the size 20 times 20 with a maximum number of entries of 16 already requires 400 counters each accepting up to 16 entries at the same time.

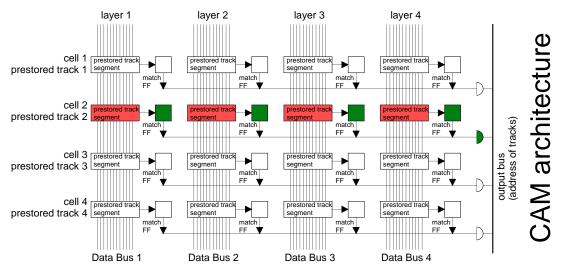

#### Pattern matching

A predefined set of valid track patterns is compared to measured values. If a match is detected a valid track is found. The method can only be applied if the number of patterns to be stored and compared can be kept within reasonable limits.

In hardware applications this method is known to be applied intensively. It is a fast and efficient method. However, as detector resolution and number of detector cells get too high the number of necessary inputs of the hardware system and the number of patterns too store can get prohibitively high.

#### Neural artificial networks

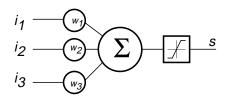

Fig. 1.4.: Block diagram of a neuron.

The sensory and cognitive abilities of biological neural networks, like the human brain, are still not reached by even the most powerful electronic systems. However, recently more and more applications to implement neural networks are being undergone. The neuron is an information processing unit that is fundamental to the operation of a neural network. Fig. 1.4 shows the

model of a neuron: Input signals are fed to a set of synapses or connecting links, each of which is characterized by a weight of its own. An adder sums up the weighted input signals and provides it to the activation function. This limits the amplitude of the output of a neuron. A layered neural network is a network of neurons organized in the form of layers. [5,6]

## **2** Track finder processor environment

### 2.1. Experiment CMS - Compact muon solenoid

In this chapter the experiment is described in a simplified way in order to support understanding of the environment and specifications of the track finder processor. More detailed information about the detector may be found in [2, 7, 8].

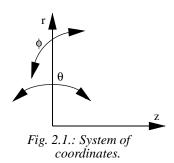

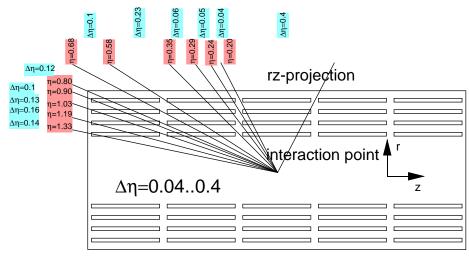

Fig. 2.1 illustrates the system of coordinates for the detector used in the following chapters. The angle  $\theta$  frequently is replaced by the pseudo rapidity  $\eta$ . Equation 2.1 shows the definition for  $\eta$ . For directions perpendicular to the beam axis  $\eta$  equals 0. Directions parallel to the beam axis have a pseudo rapidity  $\eta$  of  $+\infty$  or  $-\infty$ .

$\eta = -\ln\left(\tan\left(\frac{\theta}{2}\right)\right)$  (Eqn. 2.1.)

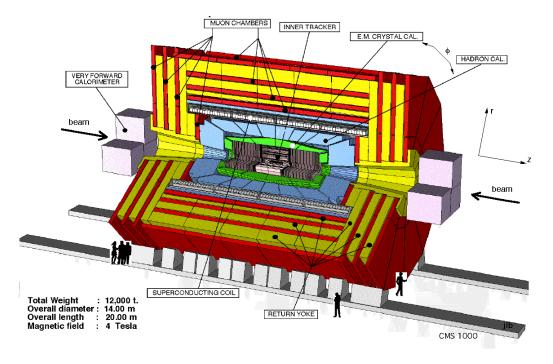

The detector will be built around a high-field superconductive solenoid leading to a compact design for the muon spectrometer, hence the name Compact Muon Solenoid (CMS). The solenoid has an inner radius of 3 m generating a uniform magnetic field of 4 T parallel to the beam axis. The magnetic flux is returned through a 1.8 m thick iron yoke instrumented with muon chambers. The magnetic field in the return yoke is 1.8 T. Fig. 2.2 shows a three-dimensional view of CMS. The overall dimensions of the detector are: a length of about 20 m, a diameter of 14 m and a total weight of 12000 tons. The total number of measurement channels is about 10<sup>8</sup>.

From the inside of the detector at the interaction point to the outside particles traverse

- the beam pipe,

- the inner tracker,

- the crystal electromagnetic calorimeter,

- the hadronic calorimeter,

- the superconductive coil, and

- muon chambers and return yoke.

Fig. 2.2.: Three dimensional view of the detector CMS (Compact Muon Solenoid).

The inner tracker provides accurate position information of all charged particles. The number of particles and superimposed tracks close to the interaction point require the inner tracker to have a high granularity in order to be able to ensure pattern recognition. The three employed detector systems, silicon pixel detectors, microstrip detectors and micro strip gas chambers, achieve a spatial resolution in the order of 15 to  $40 \,\mu\text{m}$ .

The electromagnetic calorimeter measures the energy of photons and electrons. It is built using lead tungsten (PbWO<sub>4</sub>) crystals arranged in a projective geometry with respect to the interaction point. The crystals have a physical size of 23 cm length and 20.5 x 20.5 mm<sup>2</sup> square section on the front face. The size of the front face corresponds to the spatial granularity of the detector.

The hadronic calorimeter surrounds the electromagnetic calorimeter and acts in conjunction with it to measure the energies and directions of hadrons and to help measuring the missing energy. The active elements of the calorimeter consists of plastic scintillator tiles. Layers of these tiles alternate with layers of copper absorber to form the sampling calorimeter structure. The tiles are arranged in projective towers with fine granularity. The granularity is  $160 \times 160 \text{ mm}^2$ .

The muon detector fulfils three basic tasks: muon identification, trigger, and momentum measurement. The muon detector is placed behind the calorimeters and the magnet coil. It consists of four muon stations interleaved with the iron return yoke plates. A system of drift tubes (DT) is applied in the barrel region, while cathode strip chambers (CSC) cover the forward region. In addition resistive plate chambers (RPC) cover the entire muon detector.

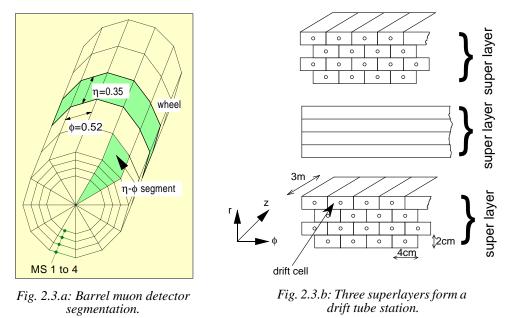

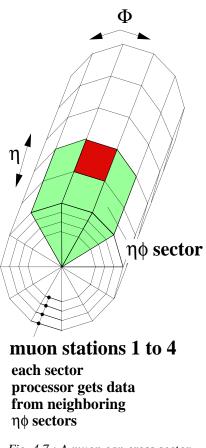

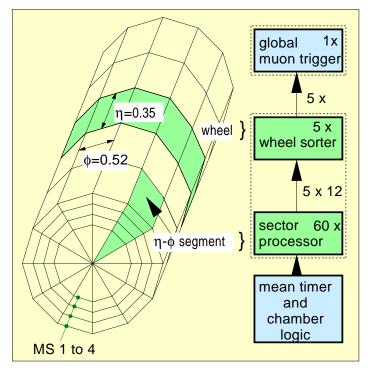

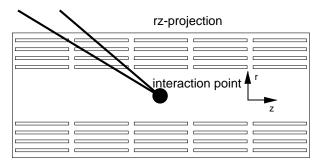

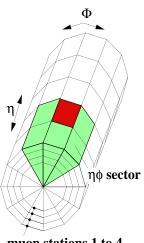

The barrel part of the detector is divided in five wheels z-direction and twelve  $30^{\circ}$  sectors, resulting in 60 ( $\eta\phi$ ) detector segments (see fig. 2.3.a). Each sector comprises four measuring stations, MS1 to MS4. Every station contains a module of drift tubes.

A drift tube cell has a cross section of  $4 \times 1.1 \text{ cm}^2$ . The drift time is about 400 ns. A spatial resolution of about 200 µm is achieved. The total number of drift wires is about 200000. Fig. 2.3.b illustrates the arrangement of the drift tubes. The chambers consists of twelve layers of drift tubes arranged in three superlayers of four planes each. The outer two superlayers (r $\phi$ ) measure the  $\phi$ -coordinate in the bending plane. The middle superlayer (rz) measures the z-coordinate along the beam line. The chambers are 2.56 m long and the width increases from 2 m in the inner station to 4 m in the outer station. The tubes within a superlayer are staggered by half the width of a tube.

In the endcap regions the muon detector comprises four muon stations. Muon stations are mounted vertically (fig. 2.3). Each muon station contains cathode strip chambers. The cathode strip chambers contain six layers with cathode strips oriented radially to measure the azimuthal coordinate. The wires are strung perpendicular to the central radial line. [2]

## 2.2. Trigger and data acquisition of CMS

The LHC environment presents challenges to the trigger and data acquisition which are far more demanding than those encountered by the past and present experiments at other facilities. [9]

These advanced demands arise because of a

| high bunch crossing rate,   | 40 MHz                    |

|-----------------------------|---------------------------|

| high channel number in CMS, | >10 <sup>8</sup> channels |

•

| ٠ | high collision rate (up to 18 interactions per crossing), | 10 <sup>9</sup> Hz |

|---|-----------------------------------------------------------|--------------------|

| • | high complexity of the events                             | overlap and pileu  |

overlap and pileup 10<sup>7</sup> high complexity of the events, • and high reduction rate of the trigger.

The bunch crossing (bx) rate in LHC is 40 MHz, corresponding to 25 ns between two subsequent crossings. On average there will be 18 interactions per bunch crossing, causing overlap of the interactions within one bunch crossing, but also interfering with subsequent interactions (pileup). Thus the resulting interaction rate is about  $10^9$ interactions per second. The trigger and data acquisition must reduce the input rate by a factor of  $10^7$  to 100 Hz. This is the rate permanent storage devices, such as tape drives, are able to cope with. [2]

CMS has more than  $10^8$  channels. Considering the raw data from all the detectors and the bunch crossing rate of 40 MHz the resulting data rate for the entire experiment is in the order of  $10^{15}$  bit s<sup>-1</sup>. This data rate corresponds to an amount of data processed by  $2 \cdot 10^9$  simultaneous playing compact disc players. Assuming a large music store has 100000 compact discs in stock 80000 stores would have to play all their discs at the same time to generate an equal data rate as caused by the detector CMS [10]. Table 2-1 shows the number of channels and the resulting amount of data after zero suppression for each of the detector systems. Even after zero suppression the data size for one crossing is still 1 MByte, resulting in a compressed data rate of  $3.4 \cdot 10^{14}$  bit s<sup>-1</sup>. The occupancy gives the average fraction of detector channels whose detector cells are being hit.

| Detector      | No. of channels     | Occupancy<br>[%] | Event size<br>[kB] |

|---------------|---------------------|------------------|--------------------|

| Pixel         | 8·10 <sup>7</sup>   | 0.04             | 100                |

| Inner Tracker | 1.6·10 <sup>7</sup> | 0.8              | 700                |

| Calorimeters  | $6.4 \cdot 10^5$    | 5-10             | 100                |

| Muons         | 10 <sup>6</sup>     | 0.1              | 10                 |

| total         | 9.8·10 <sup>7</sup> | -                | ~1000              |

Table 2-1: Number of channels, occupancy and zero suppressed events size of detectors.

The data reduction rate is performed in three steps. The three steps form a series of progressively more complex, but also more time consuming levels. By reducing the event rate, each level offers the subsequent level more time for its decision. Although the data rate is reduced in three steps, only two physical units (physical levels) are employed. The first level is based on custom, pipelined hardware processors. The second and third level are based on network switches and processor farms.

The level-1 trigger comprises the front-end electronics which generates the trigger primitives (detector data for the trigger decision). The level-1 trigger operates on a subset of data (muon detector and calorimeters). The event rate is reduced to 100 kHz. The entire trigger system operates dead time free. That means the first level trigger generates a decision for each event every 25 ns. Due to the limited storage capacity of detector read-out the decision must be available 3.2 µs after the corresponding bunch crossing.

The level-2 trigger is provided by an on-line processor farm and reduces the trigger rate by a factor of 10 to 10 kHz. After a positive Level-2 decision, the remainder of the full crossing data is requested for further processing by this farm for the final (Level-3) decision, which puts out a positive decision with a frequency of up to 100 Hz. [2]

In the first level trigger only a subset of data is used to identify the particles and perform an energy evaluation on a macro-granular detector information. In level two the information about location and type of particle is known from level-1 and a finer granularity is used to refine the level-1 measurements. Employing track reconstructions and more precise energy measurements permits evaluating the event topology. In level-three a full process identification is conducted.

No high energy physics experiment in the past had as many channels as CMS. Moreover, none of the previous experiments worked at a bunch crossing frequency of 40 MHz. See table 2-2 for a comparison of the channel number, event rate, bunch crossing rate, event size, and data rate for the experiment UA1 (SPS/CERN), H1 (HERA/DESY), and CMS (LHC/CERN) [10,12].

| Experiment                           | UA1             | H1                | CMS               |

|--------------------------------------|-----------------|-------------------|-------------------|

| Tracking [channels]                  | 10 <sup>4</sup> | 10 <sup>4</sup>   | 10 <sup>8</sup>   |

| Calorimeter [channels]               | 10 <sup>4</sup> | $5.10^4$          | 6·10 <sup>5</sup> |

| Muons [channels]                     | 10 <sup>4</sup> | $2 \cdot 10^5$    | 10 <sup>6</sup>   |

| Bunch crossing rate [ns]             | 3400            | 96                | 25                |

| Raw data rate [bit·s <sup>-1</sup> ] | 10 <sup>9</sup> | $3 \cdot 10^{11}$ | $4 \cdot 10^{15}$ |

| Tape write rate [Hz]                 | 10              | 10                | 100               |

| Event size [byte]                    | 100k            | 125k              | 1M                |

Table 2-2: Data acquisition parameters for UA1 (1982), H1 (1992) and CMS. [10]

## 2.3. CMS first level trigger

The task of the CMS first level trigger is to release the L1 accept signal. In case of a positive decision the detector data are extracted from the data pipeline and forwarded to the second level trigger. In case of a negative decision they are discarded. The requirements on the hardware implementation are severe. Every 25 ns another event has to be evaluated. The L1 trigger processing time is limited to 128 bx.

The CMS First Level (L1) Trigger has to reduce the data rate from 40 MHz to less than 100 kHz. This yields a rejection rate of 400. The data reduction is based on the recognition of primitive physical objects such as leptons, hadrons and photons. The final decision is made as a function of the event topology and cuts on the kinematical parameters transversal Energy  $E_t$  and transversal momentum  $p_t$ . The L1 trigger has to process its algorithms in a fixed time. The processing time must be independent of the occurring event. The large amount of data to be processed by the L1 trigger requires more time than one bunch crossing. Moreover the L1 trigger must not introduce dead time to the trigger system. Hence the trigger has to operate in a pipelined way. In order to render the size of the data pipeline within reasonable limits the calculation time of the L1 trigger is limited to 128 bunch crossings (bx) or  $3.2 \,\mu$ s. The strict requirements on L1 trigger latency do not permit to use tracker information in the L1 trigger. Hence only muon detectors and calorimeter data participate in this system. Still the number of channels to be processed in each crossing is higher than  $10^6$ .

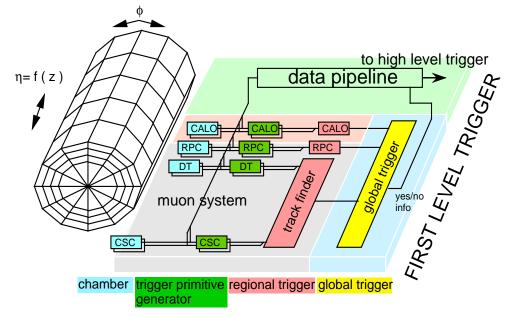

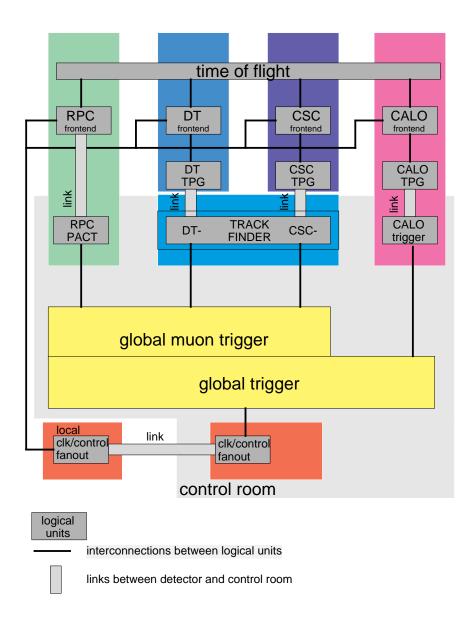

Fig. 2.4.: Block diagram of CMS First Level Trigger.

The complexity of the events does not allow to process all the input data in one logical unit. Fig. 2.4 shows a block diagram of the CMS L1 trigger. Four main blocks can be seen, the calorimeter trigger, the muon trigger, the global trigger and the data pipeline. The calorimeter trigger measures the energy of hadrons, electrons and photons. The muon trigger determines the location and the transverse momentum  $p_t$  of muons. The main principle of the L1 trigger is that none of the sub triggers (muon, calorimeter) applies any cuts on the detector data. It is the global trigger which combines the sub trigger information and finds a final decision.

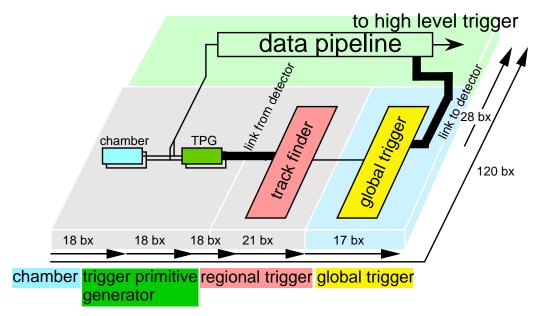

Both sub trigger systems have a common structure. They can be subdivided into three groups; the trigger primitive generators (TPG), the regional triggers, the global trigger. The trigger primitive generator processes the digitized chamber raw data. It performs zero suppression and forwards the data to the regional triggers. These units attempt to find particles and perform energy or momentum measurements. The information of both sub triggers is combined in the global trigger. It releases the 'level 1 accept' signal.

#### 2.3.1. CMS global trigger

The global trigger combines the information from the calorimeter trigger and the muon trigger and delivers the final trigger decision (L1 accept signal). The L1 accept signal is transmitted to the data pipeline in order to discard the data of the corresponding event or to forward all detector information to the higher level triggers. Additionally the

information which the L1 trigger decision is based on, including all sub trigger output data and trigger settings, is made available to the second level trigger. This information serves the second level trigger to identify regions of interest.

#### 2.3.2. CMS level 1 trigger latency

The level 1 trigger latency is a basic parameter of CMS. It determines the amount of data storage that must be provided in the front end electronic systems, which are located near the detector. Specification of an unnecessarily long latency can make the design of the data pipeline more complex and costly. Specification of too short a time can make it impossible for some detector system to contribute fully to the trigger, or, even worse, can mean that the data from some detector cannot be captured for subsequent read-out.

There are many contributions the to latency. These include time of the flight of the particles to the detector this number can be as high as 30 ns; propagation of signals within the sensitive elements of the detector in case of drift tubes up to 400 ns; signal processing and trigger primitive generation times; cable runs within the detector hall and from the detector hall to the control room the longest expected cable run is as long as 90 m

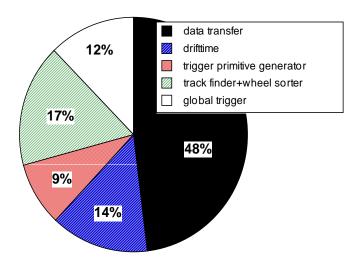

Fig. 2.5.: Latency distribution of the drift tube muon trigger system and global trigger.

(450 ns); time to process regional trigger algorithms; time to make the global trigger decision; time to distribute the L1 trigger accept signal back to the crates in the front end - 90m (450 ns); and time to distribute the signal to the relevant locations within the crates. Fig. 2.5 shows the distribution of the latency caused by processing time, cable delay and synchronization for the track finder system and global trigger. 48 % of the latency is due to cable delays, synchronization and the transmission from the detector to the processing units in the electronics barracks and vice versa. The charts show that an appreciable portion of the latency is in fixed cable delays.

#### 2.3.3. CMS muon trigger

The muon trigger performs only measurements on the particles found in the muon system. It does not make a decision whether the detector data of a given event is to be discarded or to be retained. The tasks of the CMS muon trigger are to identify muons, determine their location, determine the bunch crossing in which they occurred and measure the transverse momentum. The system is based on dedicated trigger detectors (resistive plate chambers) and precision muon chambers (drift tubes and cathode strip

Fig. 2.6.: Detailed first level trigger block diagram

chambers). The RPC system as well as the muon chamber trigger system are designed to work independently of each other. In most large scale high energy physics experiments fast dedicated trigger chambers recognize a muon and precise muon chambers provide a sharp momentum cut. The possible difference in CMS is that often in other experiments muon chambers are used in the second level trigger whereas in CMS the chamber information is already used in the first level trigger. This is well suited to the overall concept of the CMS trigger which does not have a dedicated level two hardware. This is possible due to high integration of logic processing units and fast calculation speed of today's electronic components. Since the two trigger components work in the same level one can take advantage of their complementarity with respect to their measurement performance. For further information about advantages of the two component muon trigger system refer to [11]. The system has to cover the entire geometrical range of the muon system of up to  $|\eta|=2.4$ . The latency of the system must not exceed 128 bunch crossings. The system must not introduce any dead time to the detector read-out. Both systems put out information about muons with the highest transverse momentum  $p_t$  in the entire detector. [13]

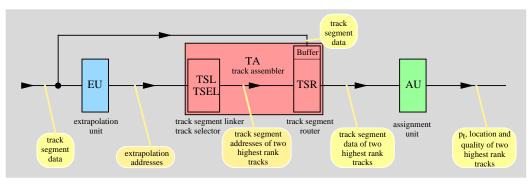

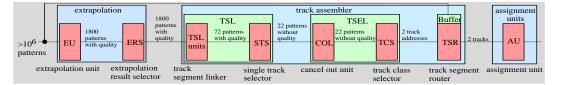

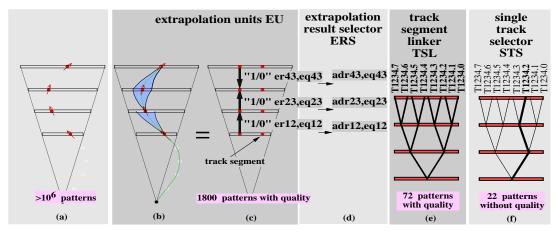

The CMS muon trigger comprises three main components; the pattern comparator trigger (PACT) [2,14,15] based on resistive plate chambers (RPC), track finder processor (TF) based on drift tube chambers (DT) and cathode strip chambers (CSC) and the global muon trigger. A detailed block diagram of the L1 trigger is shown in fig. 2.6. All blocks on the shaded background are located in the control room 90 m apart from the detector.

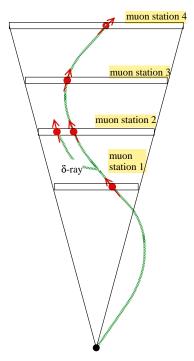

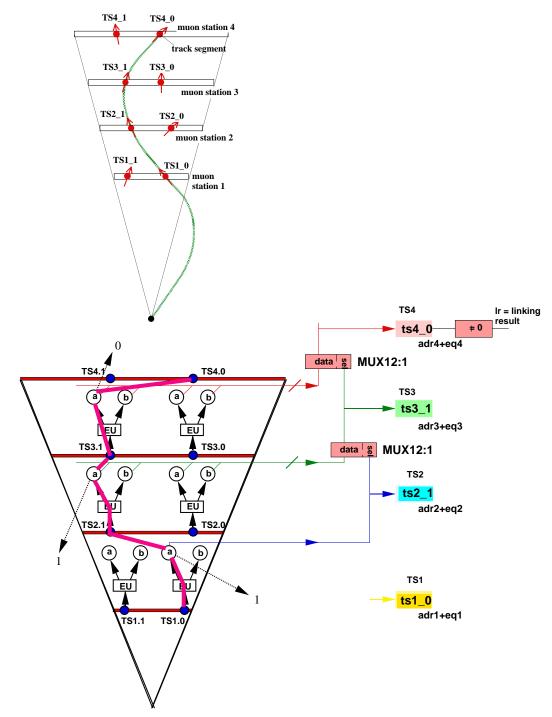

DT- and CSC-trigger primitive generators first process the information of the chamber locally. As a result up to two vectors per muon station, the track segment (position and angle) is delivered. Track segments from different stations are collected by the track finder which combines them to form muon tracks. The transverse momentum  $p_t$  is assigned. The track information is forwarded to the wheel sorter which selects the four highest  $p_t$  muons in each detector wheel.

#### 2.3.3.1. Drift tube trigger primitive generator (DT-TPG)

The task of the drift tube trigger primitive generator is to perform a data compression

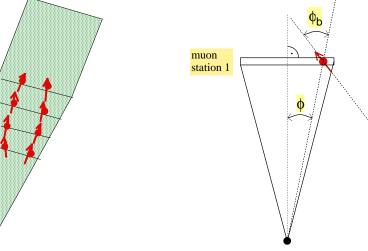

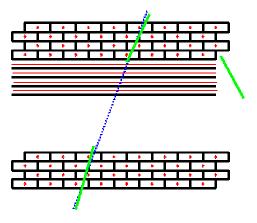

Fig. 2.7.a: Two track segments per chamber are given out.

Fig. 2.7.b: A track segment consists of the spatial coordinate  $\phi$  and the crossing angle  $\phi_b$ .

for further processing by the track finder. Since the probability to find more than two tracks in a detector segment is negligible [16] the primitive generator suppresses data from all drift cells which are not hit (zero suppression) and puts out information of up to two track segments per chamber in each detector segment (see fig 2.7.a). A track segment consist of a position and an angle measurement. The position gives the location of the hit in the chamber. The angular value is the angle of the crossing track with respect to the detector radius (see fig. 2.7.b).

In case more than two track segments are found in a chamber the drift tube electronics selects those two track segments with angles closest to the radial direction (muons with high momentum have a low bend angle).

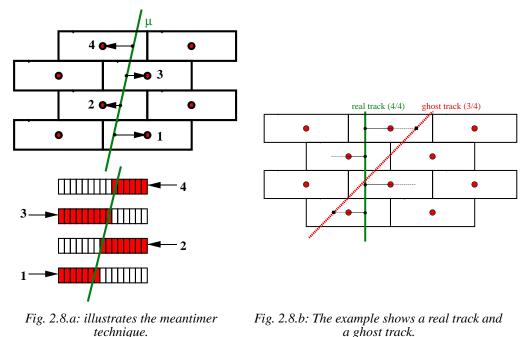

The maximum drift time of the drift tube chambers in CMS is about 400 ns or 16 bx. Thus a single drift cell does not allow to identify the bunch crossing in which a particle crossed the muon detector. This problem is solved by applying the so called mean timer method:

Each of the four muon stations in the barrel is equipped with twelve layers of drift tubes [2]. They are arranged in quartets called superlayers SL. Two of the superlayers measure the ro-coordinate, one measures the z-coordinate. The drift tubes of a superlayer are staggered (see fig. 2.3.b). The tracks in each superlayer are identified by bunch and track identifier BTI [17]. The signals from four drift tube layers are each connected to a register. They are clocked with the bunch crossing frequency and have a depth equal to the maximum drift time  $T_{max}$ . The wire signals are shifted in the same direction as the electrons drift in the chamber. The hits will be aligned in the shift register at the time T<sub>max</sub> after the corresponding bunch crossing. The aligned 'shift register images' reflect the images of the tracks (see fig. 2.8.a). Thus the track position and direction is given and can be calculated. The position resolution is 1.25 mm and the angular resolution 60 mrad. However, possible inefficiencies in the chamber system require to accept track images consisting of only three out of four hits. This and the 'left-right' ambiguity of drift tubes makes it possible to find ghost tracks. In fig. 2.8.b such a ghost track is illustrated. Both the real 4 out of 4 track and a ghost 3 out of 4 track will be found. 4 out of 4 hits are marked as high quality triggers (HTRG). Conservatively a low quality trigger (LTRG) indicates 3 out of 4 tracks.

BTIs find track segment candidates. The track correlator TC attempts to form a correlation between the track segments of the inner and outer superlayer. Amongst all track segments the track server TS finds the ones exhibiting the lowest angle closest to the radial direction.

The BTI is used in both chamber views, ro and rz, to find track segments giving at least three out of four hits. A wire cluster of nine wires is connected to the BTI. The principle of correlation is shown in fig. 2.9. The angles of track segments in the outer and in the inner superlayer are compared to the computed value using the positions of the two found track segments. If the angles are found to be equal programmable within a tolerance the correlation will be considered successful and the correlation quality bit of the track segment will be activated. Only one track segment (position and angle) is given out. Due to the correlation the track angle can be calculated

Fig. 2.9.: Correlation between track segments in the inner and outer superlayer of a station.

with a more accurate precision of 10 mrad using the spatial coordinates of the correlated track segments.

If the track segments cannot be correlated the track segment with the higher quality will be given out. Uncorrelated high quality triggers are forwarded without any filtering. Low quality triggers are filtered, because ghost tracks belong to this class. The ghost suppression is performed by making a time coincidence with the track segment from the r $\phi$ -plane and the track segment of the rz-plane.

The last stage is the trigger server. Amongst all track segments the trigger server finds the ones exhibiting two track segments with angles closest to the radial direction again. The track segments are sent to the track finder. The spatial value is transmitted in an eleven bit word. Eight bits are reserved for the angle.

The DT-chamber system is divided into twelve  $\phi$ -segments, five wheels in z-direction and four stations in r-direction, see fig. 2.2. Thus the entire system comprises 12 x 5 x 4 = 240 stations. Hence 480 track segments are delivered to the regional trigger, the track finder.

#### 2.3.3.2. Cathode strip chamber trigger primitive generator (CSC-TPG)

A description of the CSC-TPG cannot be given at the present moment. Design is not advanced sufficiently. However, output format (track segments) is identical to the drift tube trigger primitive generator. Baseline information can be found in [18,19].

## **3** Track finder processor overview

In chapter 3.1. the track finder specifications are discussed.

Chapter 3.2. gives an introduction to previously implemented and planned first level triggers in comparable experiments in the whole world. Comparisons between the track finder specifications and the features of other first level trigger systems are conducted.

### **3.1. Track finder processor specifications**

In this chapter the track finder processor specifications are discussed. Although they are listed here one after the other the process of optimizing the appropriate features was determined by a long adaptation phase. Some of the requirements and parameters influenced each other. Some of the specifications had to be refined in a later design phase.

$p_t = 3.5, 4.0, 4.5, 6.0 \text{ GeV}$

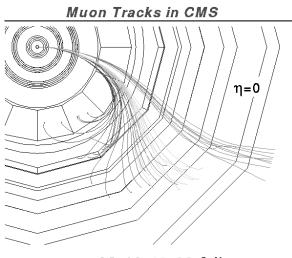

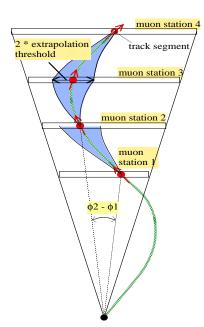

Fig. 3.1.: Muon tracks with different  $p_t$ -values in the magnetic field of CMS. Due to the change of magnetic field direction in the return yoke of the magnet the curvature of muon tracks changes.

The task of the track finder processor is to find muon tracks originating from the interaction point and to measure transverse momentum  $p_t$  and their location in  $\phi$  and  $\eta$ . The system is based on the drift tube chamber system in the barrel of the detector. However, it must be designed as flexible as possible in order to allow an application in the forward region, where CSC deliver the hit information.

In fig. 3.1 muon tracks are illustrated. As shown muons with a transverse momentum of as low as 3.2 GeV/c (for  $\eta=0$  and c velocity of light) reach the muon detector. In the forward region

even muons with transverse momenta of 2.0 GeV/c penetrate the muon stations. Clearly

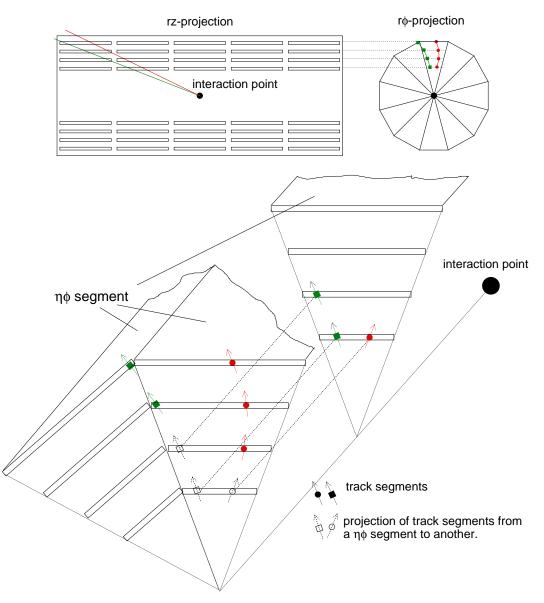

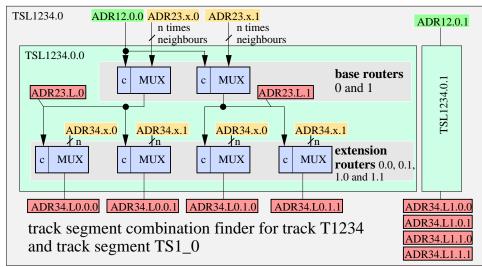

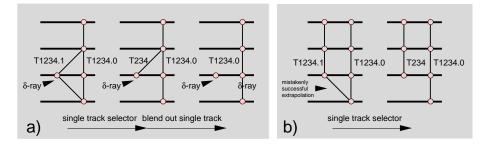

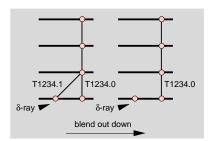

Fig. 3.2.: shows muons in the detector crossing segment boundaries in  $\phi$  as well as in  $\eta$ . The three dimensional view of the detector segments and the track segments illustrates that the track finder processor first has to generate the projection of the track, respective its track segments, onto the  $r\phi$ -plane in order to obtain all track segment data of a certain track. This includes merging neighboring  $\phi$ -segments as well as neighboring  $\eta$ -wheels.

one can see that low momentum muons are deviated very strongly by the magnetic field and thus cross detector segment boundaries quite regularly. On the other hand high  $p_t$ muons resemble almost a straight line and thus pose a challenge to the track finder to determine the track's curvature and its momentum. As illustrated in fig. 3.2 the track finder has to find matching track segments, link them together to a full track and measure their momentum. Hereby only muons emerging from the interaction point should be taken into account.

#### P<sub>t</sub>-measurement

The second level trigger of CMS is designed to process events with a rate of 100 kHz at the maximum. If the first level trigger output rate exceeds this rate the second level trigger will fail to process events. As a consequence it is vital to be able to limit the first level muon trigger rate. Simulations for physics events producing muons have been

conducted. They allow to estimate the rate of muons in the detector in dependence of their transverse momentum  $p_t$  [2, 22].

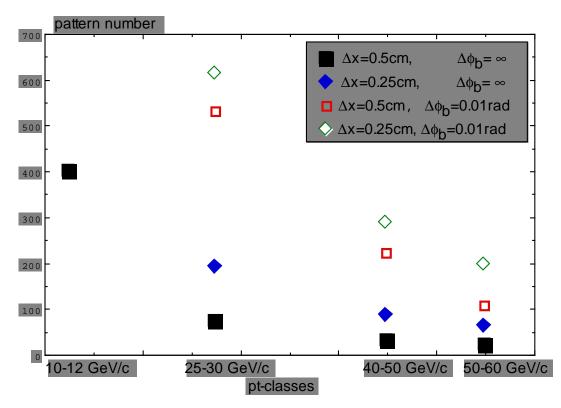

Approximately one half of the level one trigger bandwidth is expected to be filled by triggers involving the calorimeter system and the other half is expected to be filled by triggers involving the muon trigger system. However, since an even division of level one bandwidth among sub triggers is not anticipated, flexibility to accommodate for variations in rates of the sub triggers is planned. In order not to exceed the maximum output rate foreseen for the muon sub triggers one selects only high transverse momentum muons and cuts off low transverse momentum muons just to obtain the required rate. Due to uncertainties of the estimates, changing beam conditions and different trigger settings it is necessary to be able to set a muon transverse momentum threshold in a range between 2.0 GeV/c and 140 GeV/c. The rates are also dependent on the beam condition. One expects the rate estimations to be accurate by a factor of two. The  $p_t$ -range between 2.0 GeV/c and 140 GeV/c is divided into 25  $p_t$ -classes (see table 3-1). The step from one  $p_t$ -class to the next corresponds to a change in output rate of factor 1.5 [23,24]. This factor is quite well suited to accommodate the rate estimation uncertainties. A factor exceeding the value two would cause inefficiencies in output rate adaptations. The  $p_t$ -value is given out in a 5 bit number. A sixth bit indicates the charge of the particle.

As the number of events to be recorded is limited one wants to capture only those events containing high transverse momentum muons. This requirement corresponds to a sharp cut off at the momentum threshold. That means one wants to record only a little number of muons with transverse momentum lower than the threshold and vice versa. In other words one wants to have a transverse momentum measurement resolution as good as possible.

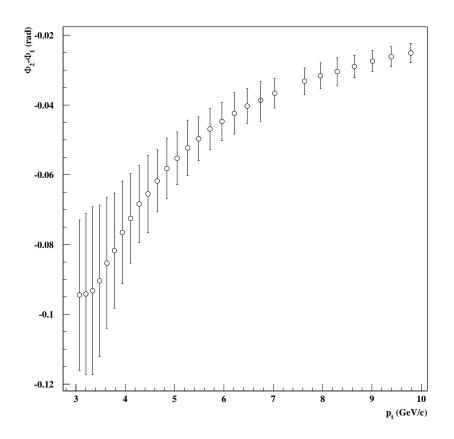

The relative measurement resolution (standard deviation)  $\sigma_{pt}/p_t$  of the transverse momentum measurement is a trade-off between technical feasibility and physics requirements. The transverse momentum  $p_t$  is derived from the curvature  $\kappa_c$  of the muon tracks. The resolution of  $\kappa_c$  is directly proportional to the resolution of the measured bend angle derived from the track segment coordinates [20, 21]. The chamber can deliver a resolution of as low as 200 µm [2]. Obviously this accuracy cannot be used in the trigger level. A spatial measurement resolution  $\sigma_{ts}$  of 0.3 mrad is considered implementable in hardware [16,17] and is provided for the track segment measurements by the trigger primitive generators. 0.3 mrad corresponds to approximately 1.25 mm in station one and two and 2.5 mm in station three and four. Using a spatial resolution of  $\sigma_{ts}$  enables to achieve a  $p_t$  measurement resolution  $\sigma_{pt}/p_t$ in the order of 35 %. For further details refer to [22, 25, 26].

####

Measurement in  $\phi$  can be given out very accurately since the position of the track segments in  $\phi$  is known well. The 1.25 mm binning of the track segments corresponds to a  $\phi$ -resolution in the first station of 0.018° or 0.3 mrad. That means the track position in  $\phi$  can be given in the same resolution. The first level global trigger cannot process the sub trigger data with such a good resolution. Thus the track finder processor partitions the total of twelve detector segments into 256 bins using an eight bit number. Hereby a  $\phi$ -resolution of 1.4° or 25 mrad is provided.

| $p_t$ range | 5 bit-p <sub>t</sub><br>code | $p_t$ range | 5 bit-p <sub>t</sub><br>code | $p_t$ range | 5 bit-p <sub>t</sub><br>code | $p_t$ range | 5 bit- <i>p<sub>t</sub></i><br>code |

|-------------|------------------------------|-------------|------------------------------|-------------|------------------------------|-------------|-------------------------------------|

| no muon     | 0                            | 4.0-5.0     | 8                            | 17.0-20.0   | 16                           | 70.0-80.0   | 24                                  |

| reserved    | 1                            | 5.0-6.0     | 9                            | 20.0-25.0   | 17                           | 80.0-100.0  | 25                                  |

| reserved    | 2                            | 6.0-7.0     | 10                           | 25.0-30.0   | 18                           | 100.0-120.0 | 26                                  |

| reserved    | 3                            | 7.0-8.0     | 11                           | 30.0-35.0   | 19                           | 120.0-140.0 | 27                                  |

| 2.0-2.5     | 4                            | 8.0-10.0    | 12                           | 35.0-40.0   | 20                           | 140.0-∞     | 28                                  |

| 2.5-3.0     | 5                            | 10.0-12.0   | 13                           | 40.0-50.0   | 21                           | reserved    | 29                                  |

| 3.0-3.5     | 6                            | 12.0-14.0   | 14                           | 50.0-60.0   | 22                           | reserved    | 30                                  |

| 3.5-4.0     | 7                            | 14.0-17.0   | 15                           | 60.0-70.0   | 23                           | reserved    | 31                                  |

Table 3-1: p<sub>t</sub>-classes [23].

#### <u>n-measurement</u>

The non-projective chamber geometry with respect to the rz-view does not allow a precise measurement of the  $\eta$ -coordinate of the track. The only information the  $\eta$ -coordinate can be derived from is the place where a particle crossed detector wheel boundaries. The  $\eta$ -value is given in a 2 bit code.

#### Quality

Due to inefficiencies not all chambers deliver track information at all times. Then a track must be identified and the transverse momentum measured using only the available data. Obviously the measurement resolution is impaired and measurement errors are higher. Thus the track finder has to give information about the quality of the data the track measurement is based to the global trigger. This is done by a two bit number.

#### Dead time free

The first level trigger architecture must permit a dead time free operation. That means that even in case of a positive level accept signal release the processor must stay operational for the subsequent events. The trigger system must be capable of accepting data of each single event, with a data repetition rate of 40 MHz. It is obvious that the trigger cannot perform its task on a data set of one event within one bunch crossing.

#### Processing time - latency

It is important to keep the processing time of the track finder processor as low as possible, because during the time an event is evaluated in the level one trigger all corresponding detector data must be stored in the data pipeline. In CMS the number of detector channels is as high as  $10^8$ . Most of them belong to the tracker. The tracker signals are analogue and are only converted into a digital number after a positive level one trigger accept signal. Thus the tracker data is going to be stored in an analogue memory. Since they are expensive the storage depth is limited to 128 steps. As thoroughly discussed earlier the level one trigger latency is dominated by transmission of signals from and to the detector and by signal propagation between processing units. Thus only a smaller part is left over for the execution of the algorithms. Fig. 3.3 shows the latency distribution between the different system components. For the track finder

processor 21 bunch crossings or 525 ns are foreseen. The first level trigger decision must be provided within 128 bunch crossings. Obviously one cannot design a first level trigger system for exact this latency number. Changes at a later time as adaptations to newly found requirements or changes of detector geometry and the resulting changes in cable length cannot be accounted for. Thus a contingency of about eight bunch crossings is foreseen.

Fig. 3.3.: Latency of drift tube trigger components.

#### **Programmability**

The trigger system must be flexible enough to permit changes in the algorithm and changes in the detector geometry. In order to optimize the track finding and measurement algorithm simulations have to be employed. Obviously they are based on several assumptions. Simulation results may be refined in a later phase of optimization or at the time beam data will be available.

Another point is the detector geometry. Even if the designed chamber geometry is not going to be changed misalignment of the chambers must be accounted for. The trigger uses a resolution of 1.25 mm. However, it is impossible to install all chambers (of the dimensions 2.56 m x 2 m) within an accuracy of 1.25 mm with respect to each other. The chambers are installed within a coarser accuracy and a laser based alignment system provides information to the trigger electronics how much each chamber is displaced from the nominal position.

#### Output segmentation

The trigger system must output the information about four muons with the highest  $p_t$  in a detector wheel.

The mapping of the detector geometry onto the hardware level must be realized in a way where information exchange between processing units is minimized. This is especially vital with respect to latency but also to the physical dimensions of interconnections. Although the number of channels to evaluate exceeds 200000 in the

barrel the hardware expense of the track finder system must be kept as small as possible. Table 3-2 concludes all track finder processor specifications.

| track finder processor specifications                                     |  |  |  |  |  |

|---------------------------------------------------------------------------|--|--|--|--|--|

| outputs the four highest $p_t$ muons per wheel: $p_t$ , location, quality |  |  |  |  |  |

| $p_t$ measurement range: 2.0 - 140 GeV/c; resolution: ~ 35 %              |  |  |  |  |  |

| φ-measurement: 2 mrad                                                     |  |  |  |  |  |

| η-measurement: as good as possible                                        |  |  |  |  |  |

| dead time free                                                            |  |  |  |  |  |

| programmability: algorithm settings and chamber alignment                 |  |  |  |  |  |

| modular and flexible for use in the CSC and overlap region                |  |  |  |  |  |

| processing time: < 21 bunch crossings or 525 ns.                          |  |  |  |  |  |

Table 3-2: Track finder processor specifications.

| output         | number<br>of bits |

|----------------|-------------------|

| $p_t$ + charge | 5 + 1             |

| φ              | 8                 |

| η              | 2                 |

| quality        | 2                 |

Table 3-3: Output format.

Compatibility to forward and overlap region between cathode strip chambers CSC and

#### drift tube chambers DT

The track finder is supposed to be applied in the barrel region (equipped with drift tube chambers) but also in the forward region (equipped with cathode strip chambers) and in the resulting overlap region between the two systems. This requires the cathode strip primitive generator to deliver the same output format as the drift tube trigger primitive generator. However, as the design of the cathode strip chamber electronics is not evolved yet to a satisfying extent, in this work only the barrel drift tube track finder processor is described. However, from point of view of hardware it can be extended into the forward region of the detector.

# **3.2.** Trigger environment and implementation in other high energy physics experiments

This chapter deals with previously implemented trigger systems in modern high energy physics experiments. Focus is given to muon and track finding systems in similar detector and accelerator environments. The features of the

# systems are discussed in the following chapters. At the end of each description the systems are compared to the track finder processor. Chapter 3.2.6. concludes all systems and differences.

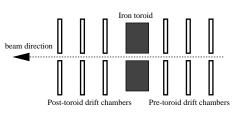

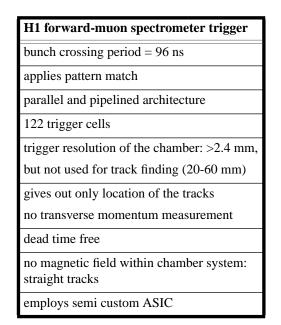

A large number of previously implemented trigger systems in high energy physics experiments exist. However only those are described which are similar to the drift tube track finder in a way. Small fixed target experiments are ruled out. Moreover only experiments at accelerators with requirements to the data acquisition similar to those of LHC are regarded. These are colliders with a high bunch crossing frequency. The most recently implemented trigger systems at large scale experiments at modern colliders whose requirements are in some way similar to those of the track finder processor are at the:

- Experiment D0 at the collider Tevatron (FERMILAB),

- Experiment CDF at the collider Tevatron (FERMILAB), and

- Experiment H1 at the collider HERA (DESY).

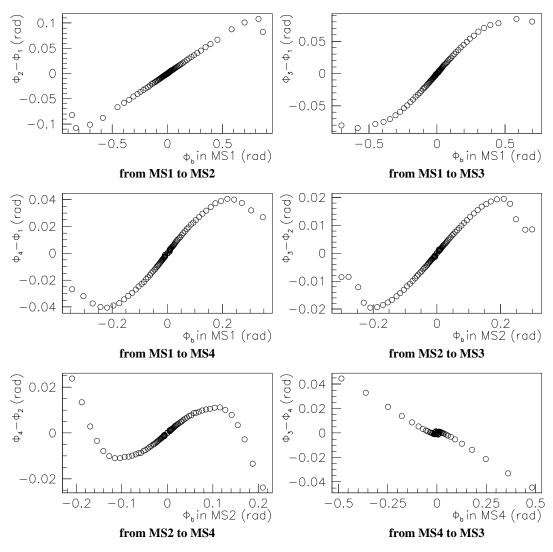

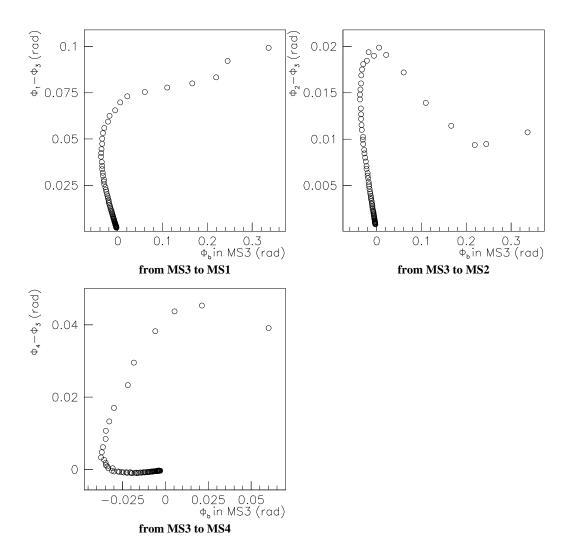

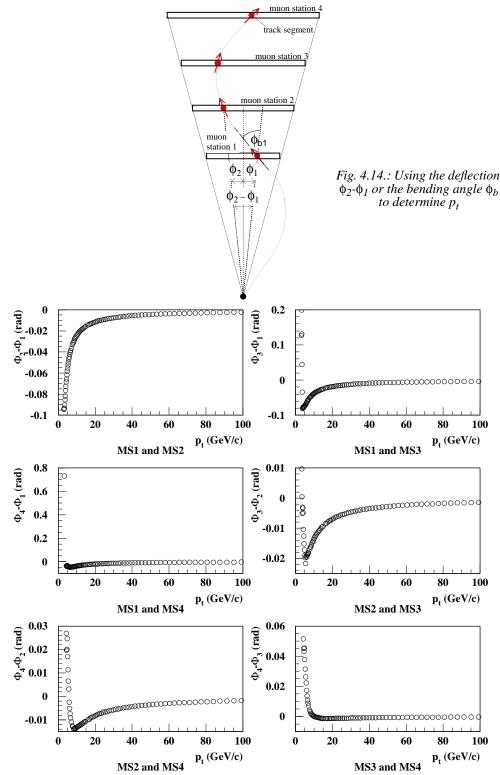

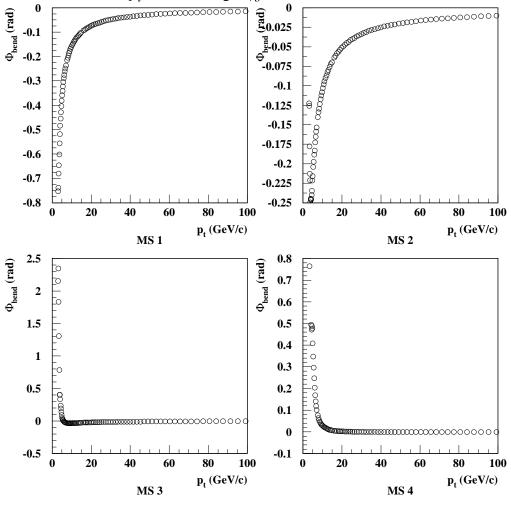

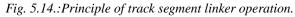

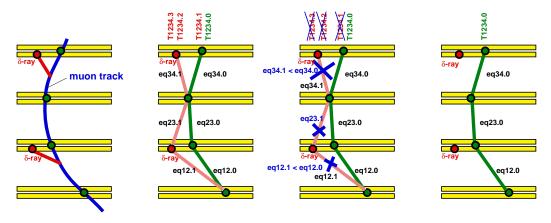

Tevatron [27] is a high-energy colliding beam accelerator operating at Fermilab, Batavia (Illinois). It collides 900 GeV protons with 900 GeV antiprotons accelerated on a 6.3 km circular path. At the collision points the experiments D0 [28] and CDF [29] are located. The bunch crossing period is  $3.5 \,\mu$ s.