# Evaluation and Simulation of Event Building Techniques for a Detector at the LHC

Dissertation zur Erlangung des Grades eines Doktors der Naturwissenschaften der Abteilung Physik an der Universität Dortmund

vorgelegt von Diplomphysiker Ralf Spiwoks aus Duisburg

- Dortmund, Oktober 1995 -

Gutachter:

Prof. Dr. C. Gößling Universität Dortmund

> Dr. L. Mapelli CERN

# Abstract

The main objectives of future experiments at the Large Hadron Collider are the search for the Higgs boson (or bosons), the verification of the Standard Model and the search beyond the Standard Model in a new energy range up to a few TeV. These experiments will have to cope with unprecedented high data rates and will need event building systems which can offer a bandwidth of 1 to 100 GB/s and which can assemble events from 100 to 1000 readout memories at rates of 1 to 100 kHz. This work investigates the feasibility of parallel event building systems using commercially available high speed interconnects and switches. Studies are performed by building a small-scale prototype and by modelling this prototype and realistic architectures with discrete-event simulations.

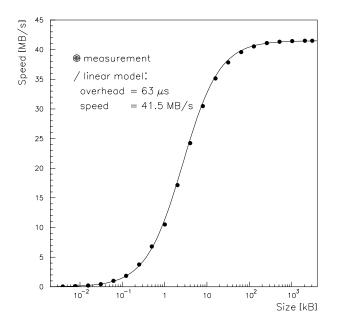

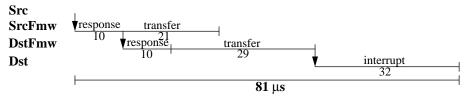

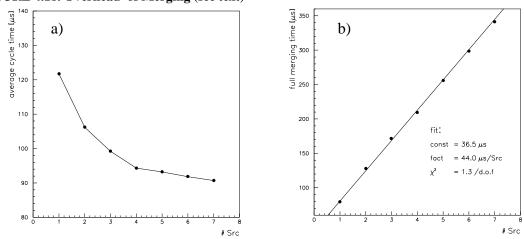

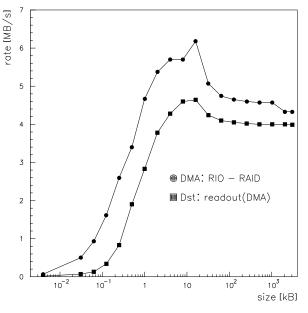

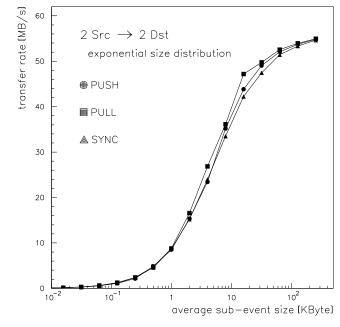

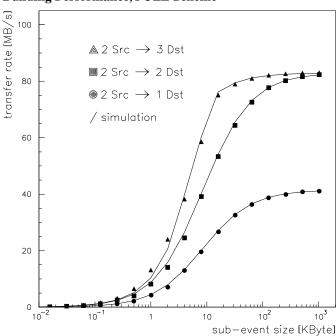

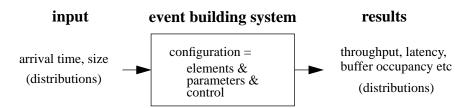

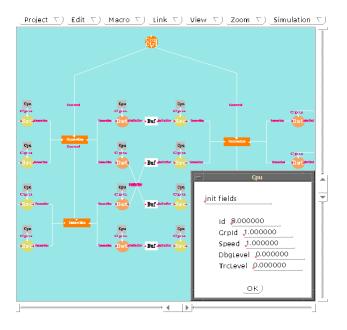

The prototype is based on the HiPPI standard and uses commercially available VME-HiPPI interfaces and a HiPPI switch together with modular and scalable software. The setup operates successfully as a parallel event building system of limited size in different configurations, with different input data and different data flow management schemes. Realistic parameters of 40 MB/s for the link speed and of 100 µs for the overhead have been measured and the total throughput is scalable with the number of destinations. The prototype measurements lead to a parametrized model of a parallel event building system which is implemented in a simulation program. This is used to simulate large-scale systems including a realistic model of the ATLAS event building system with realistic event size distributions from off-line simulations. The influence of different parameters and the scaling behaviour are investigated. Different data flow management schemes for destination assignment and traffic shaping are studied as well as a two-stage event building system.

## Acknowledgements

I would like to thank my supervisor Prof. Dr. C. Gößling for his support and guidance over the last few years. I am also very grateful to Dr. L. Mapelli for his support and supervision of this work which was started at his suggestion. I am indebted to both for their help to obtain a CERN doctoral fellowship without which this work would not have been possible.

My stay at CERN has been of immense worth to me and I am in particular grateful to all members of the RD13 collaboration for the friendly atmosphere and the many fruitful discussions. I would especially like to thank Dr. G. Mornacchi for his competent help and advice in all questions of data acquisition and event building systems, Dr. S. Buono for helping to begin with the HiPPI standard and modules, Dr. R. Jones for his help in questions of computing and I. Gaponenko for the many discussions on event building and modelling.

I would like to thank Drs. E. v.d. Bij and R. McLaren from CERN/ECP for their advice with the HiPPI hardware and software and for the loan of some of the modules. I am also indebted to Dr. W. Greiman from LBL for the original version of the simulation program and to K. Djidi from Saclay for the collaboration on DSL and its GUI. I am very grateful to Dr. R. Hawkings from CERN/PPE for his help with the ATRIG program and for providing the trigger events. I would also like to thank Dr. T. Hansl from Saclay for making the ATRIG program run.

I would like to thank all of the people in RD11, RD24, RD31 and the ATLAS DAQ groups for the friendly atmosphere and the fruitful discussions. In particular, am I very grateful to Dr. A. Bogaerts, D. Calvet, Dr. F. Harris, S. Hunt, W. Iwanski, Dr. K. Korcyl, Dr. M. Letheren, Dr. I. Mandjavidze and Dr. J. Vermeulen.

I am also indebted to D. Klein for her support with many organizational aspects of the work, in particular in helping to print it. I would like to thank Dr. E. Tsesmelis for proof-reading this work and for the good company over the last few years. I am also indebted to D. Hearty for looking through this work and for being a good friend.

I would like to warmly thank Keiwan Fakhr-Soltani for his understanding and patience without which this work could not have been finished.

# Table of Contents

| 2.0       ATLAS Experiment       2         2.1       Large Hadron Collider       2         2.1.1       Machine       2         2.1.2       Magnets       3         2.2       Physics Issues at the LHC       3         2.2.1       Standard Model       4         2.2.2       Physics Potential       4         2.2.2       Physics Potential       4         2.2.3       Higgs Boson       5         2.3       ATLAS Detector       7         2.3.1       Overview       7         2.3.2       Inner Detector       8         2.3.3       Calorimetry       80         2.3.4       Muon Spectrometer       12         2.4       ATLAS Trigger and Data Acquisition System       14         2.4.1       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger.       19         3.0       Event Building Systems       21         3.1       Definition       22         3.1.2       Elements       23         3.1.3       Performance luides       24         3.2.1       Strend Bua Architectures       25         3.2.2       Mutiphe Port                                                                                       | 1.0 | Intro                  | duction.                 |                                       | 1  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|--------------------------|---------------------------------------|----|--|--|

| 2.1.1       Machine       2         2.1.2       Magnets       3         2.2       Physics Issues at the LHC       3         2.2.1       Standard Model       4         2.2.2       Physics Potential       4         2.2.3       Higgs Boson       5         2.3       ATLAS Detector       7         2.3.1       Overview       7         2.3.2       Inner Detector       8         2.3.3       Calorimetry.       10         2.3.4       Muon Spectrometer       12         2.4       ATLAS Trigger and Data Acquisition System       14         2.4.1       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger.       17         2.4.4       Level-1 Trigger.       19         3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2.1       Shared Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.1       Shared Archi                                                                                      | 2.0 | ATL                    | ATLAS Experiment         |                                       |    |  |  |

| 2.1.1       Machine       2         2.1.2       Magnets       3         2.2       Physics Issues at the LHC       3         2.2.1       Standard Model       4         2.2.2       Physics Potential       4         2.2.3       Higgs Boson       5         2.3       ATLAS Detector       7         2.3.1       Overview       7         2.3.2       Inner Detector       8         2.3.3       Calorimetry.       10         2.3.4       Muon Spectrometer       12         2.4       ATLAS Trigger and Data Acquisition System       14         2.4.1       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger.       17         2.4.4       Level-1 Trigger.       19         3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2.1       Shared Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.1       Shared Archi                                                                                      |     | 2.1                    | Large                    | Hadron Collider                       | 2  |  |  |

| 2.2       Physics Issues at the LHC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |                        | 2.1.1                    | Machine                               | 2  |  |  |

| 2.2.1       Standard Model       4         2.2.2       Physics Potential       4         2.2.3       Higgs Bosn       5         2.3       ATLAS Detector       7         2.3.1       Overview       7         2.3.2       Inner Detector       8         2.3.3       Calorimetry       10         2.3.4       Muon Spectrometer       12         2.4       ATLAS Trigger and Data Acquisition System       14         2.4.1       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger       17         2.4.4       Level-1 Trigger       18         2.4.5       Event Building Systems       21         3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Shitches       29         3.3       High Speed Data Links       30         3.3.1 <td< td=""><td></td><td></td><td>2.1.2</td><td>Magnets</td><td>3</td></td<>                |     |                        | 2.1.2                    | Magnets                               | 3  |  |  |

| 2.2.1       Standard Model       4         2.2.2       Physics Potential       4         2.2.3       Higgs Bosn       5         2.3       ATLAS Detector       7         2.3.1       Overview       7         2.3.2       Inner Detector       8         2.3.3       Calorimetry       10         2.3.4       Muon Spectrometer       12         2.4       ATLAS Trigger and Data Acquisition System       14         2.4.1       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger       17         2.4.4       Level-1 Trigger       18         2.4.5       Event Building Systems       21         3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Shitches       29         3.3       High Speed Data Links       30         3.3.1 <td< td=""><td></td><td>2.2</td><td>Physic</td><td>s Issues at the LHC</td><td></td></td<> |     | 2.2                    | Physic                   | s Issues at the LHC                   |    |  |  |

| 2.2.2       Physics Potential.       4         2.2.3       Higgs Boson       5         2.3       ATLAS Detector       7         2.3.1       Overview       7         2.3.2       Inner Detector.       8         2.3.3       Calorimetry.       10         2.3.4       Muon Spectrometer       12         2.4       ATLAS Trigger and Data Acquisition System       14         2.4.1       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger.       17         2.4.4       Level-2 Trigger.       18         2.4.5       Event Building and Level-3 Trigger.       19         3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       30         3.3.1       High Performance Parallel Interface       30 <tr< td=""><td></td><td></td><td>•</td><td></td><td></td></tr<>          |     |                        | •                        |                                       |    |  |  |

| 2.2.3       Higgs Boson                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |                        | 2.2.2                    |                                       |    |  |  |

| 2.3.1       Overview       7         2.3.2       Inner Detector       8         2.3.3       Calorimetry       10         2.3.4       Muon Spectrometer       12         2.4       ATLAS Trigger and Data Acquisition System       14         2.4.1       Trigger and Data Acquisition Architecture       15         2.4.2       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger       17         2.4.4       Level-2 Trigger       18         2.4.5       Event Building and Level-3 Trigger       18         3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2       Interconnecting Networks and Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.1       Shared Bus Architectures       26         3.2.4       Integrated Architectures       28         3.2.5       Examples       27         3.2.6       Fibre Channel       30         3.3.1       High Perf                                          |     |                        | 2.2.3                    | •                                     |    |  |  |

| 2.3.1       Overview       7         2.3.2       Inner Detector       8         2.3.3       Calorimetry       10         2.3.4       Muon Spectrometer       12         2.4       ATLAS Trigger and Data Acquisition System       14         2.4.1       Trigger and Data Acquisition Architecture       15         2.4.2       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger       17         2.4.4       Level-2 Trigger       18         2.4.5       Event Building and Level-3 Trigger       18         3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2       Interconnecting Networks and Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.1       Shared Bus Architectures       26         3.2.4       Integrated Architectures       28         3.2.5       Examples       27         3.2.6       Fibre Channel       30         3.3.1       High Perf                                          |     | 2.3                    | ATLAS                    | S Detector                            | 7  |  |  |

| 2.3.3       Calorimetry       10         2.3.4       Muon Spectrometer       12         2.4       ATLAS Trigger and Data Acquisition System       14         2.4.1       Trigger Tarategy       14         2.4.2       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger.       17         2.4.4       Level-2 Trigger.       18         2.4.5       Event Building and Level-3 Trigger.       19         3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model.       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2       Interconnecting Networks and Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Switches       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.4       Scalable Coherent Interface       32         3.4       Data Flow Man                                          |     |                        |                          |                                       |    |  |  |

| 2.3.4       Muon Spectrometer       12         2.4       ATLAS Trigger and Data Acquisition System       14         2.4.1       Trigger and Data Acquisition Architecture       15         2.4.2       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger       17         2.4.4       Level-2 Trigger       18         2.4.5       Event Building and Level-3 Trigger       19         3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2       Interconnecting Networks and Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Switches       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       31         3                                 |     |                        | 2.3.2                    | Inner Detector                        | 8  |  |  |

| 2.4       ATLAS Trigger and Data Acquisition System       14         2.4.1       Trigger and Data Acquisition Architecture       15         2.4.2       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger       17         2.4.4       Level-2 Trigger       18         2.4.5       Event Building and Level-3 Trigger       19         3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2       Interconnecting Networks and Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Switches       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.4.4       Conteriton Resolution       34                                     |     |                        | 2.3.3                    | Calorimetry                           |    |  |  |

| 2.4.1       Trigger Strategy       14         2.4.2       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger       17         2.4.4       Level-2 Trigger       18         2.4.5       Event Building and Level-3 Trigger       19         3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2       Interconnecting Networks and Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Switches       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.3       Asynchronous Transfer Mode       31         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destinat                                          |     |                        | 2.3.4                    | Muon Spectrometer                     |    |  |  |

| 2.4.1       Trigger Strategy       14         2.4.2       Trigger and Data Acquisition Architecture       15         2.4.3       Level-1 Trigger       17         2.4.4       Level-2 Trigger       18         2.4.5       Event Building and Level-3 Trigger       19         3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2       Interconnecting Networks and Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Switches       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.3       Asynchronous Transfer Mode       31         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destinat                                          |     | 2.4                    | ATLAS                    | S Trigger and Data Acquisition System | 14 |  |  |

| 2.4.3       Level-1 Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |                        |                          |                                       |    |  |  |

| 24.4       Level-2 Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |                        | 2.4.2                    |                                       |    |  |  |

| 2.4.5       Event Building and Level-3 Trigger.       .19         3.0       Event Building Systems       .21         3.1       Definition       .22         3.1.1       Data model       .22         3.1.2       Elements       .23         3.1.3       Performance Indices       .24         3.2       Interconnecting Networks and Architectures       .25         3.2.1       Shared Bus Architectures       .25         3.2.2       Multiple Port Memories       .27         3.2.3       Switches       .27         3.2.4       Integrated Architectures       .28         3.2.5       Examples       .29         3.3       High Speed Data Links       .30         3.3.1       High Performance Parallel Interface       .30         3.3.2       Fibre Channel       .30         3.3.3       Asynchronous Transfer Mode       .31         3.4       Data Flow Management       .32         3.4.1       Data Flow Management       .32         3.4.2       Contention Resolution       .34         3.4.3       Destination Assignment       .34         3.4.4       Configuration       .35         3.4.5       Error                                           |     |                        | 2.4.3                    | Level-1 Trigger                       | 17 |  |  |

| 3.0       Event Building Systems       21         3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2       Interconnecting Networks and Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Switches       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.4       Scalable Coherent Interface       32         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       32         3.4.4       Configuration       35         3.4.5       Error Handling       35                                                   |     |                        | 2.4.4                    | Level-2 Trigger                       |    |  |  |

| 3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2       Interconnecting Networks and Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Switches       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.3.4       Scalable Coherent Interface       32         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         3.4.5       Error Handling       35         3.4.1       Hardware       37                                                                       |     |                        | 2.4.5                    | Event Building and Level-3 Trigger    |    |  |  |

| 3.1       Definition       22         3.1.1       Data model       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2       Interconnecting Networks and Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Switches       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.3.4       Scalable Coherent Interface       32         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         3.4.5       Error Handling       35         3.4.1       Hardware       37                                                                       | 3.0 | Event Building Systems |                          |                                       |    |  |  |

| 3.1.1       Data model.       22         3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2       Interconnecting Networks and Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Switches       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.3.4       Scalable Coherent Interface       32         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         3.4.5       Error Handling       35         4.1       Hardware       37         4.1.1       HiPPI Standard       38                                                                  |     |                        |                          | •••                                   |    |  |  |

| 3.1.2       Elements       23         3.1.3       Performance Indices       24         3.2       Interconnecting Networks and Architectures       25         3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Switches       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.3.4       Scalable Coherent Interface       32         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         3.4.5       Error Handling       35         3.4.1       Hardware       37         4.1       Hardware       37         4.1.1       HiPPI Standard       38                                                                     |     | 5.1                    |                          |                                       |    |  |  |

| 3.1.3       Performance Indices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |                        |                          |                                       |    |  |  |

| 3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Switches       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.3.4       Scalable Coherent Interface       32         3.4       Data Flow Management       32         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         3.4.5       Error Handling       37         4.1       Hardware       37         4.1.1       HiPPI Standard       38         4.1.2       VME-HiPPI Interface       40         4.1.3       HiPPI Switch       40                                                                                                                             |     |                        | 3.1.3                    |                                       |    |  |  |

| 3.2.1       Shared Bus Architectures       25         3.2.2       Multiple Port Memories       27         3.2.3       Switches       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.3.4       Scalable Coherent Interface       32         3.4       Data Flow Management       32         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         3.4.5       Error Handling       37         4.1       Hardware       37         4.1.1       HiPPI Standard       38         4.1.2       VME-HiPPI Interface       40         4.1.3       HiPPI Switch       40                                                                                                                             |     | 3.2                    | Interco                  |                                       |    |  |  |

| 3.2.2       Multiple Port Memories       27         3.2.3       Switches       27         3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.3.4       Scalable Coherent Interface       32         3.4       Data Flow Management       32         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         3.4.5       Error Handling       37         4.1       Hardware       37         4.1.1       HiPPI Standard       38         4.1.2       VME-HiPPI Interface       40         4.1.3       HiPPI Switch       40                                                                                                                                                                                   |     | 0.2                    |                          | •                                     |    |  |  |

| 3.2.3       Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                        | 3.2.2                    |                                       |    |  |  |

| 3.2.4       Integrated Architectures       28         3.2.5       Examples       29         3.3       High Speed Data Links       30         3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.3.4       Scalable Coherent Interface       32         3.4       Data Flow Management       32         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         4.0       Event Building Prototype       37         4.1       Hardware       37         4.1.1       HiPPI Standard       38         4.1.2       VME-HiPPI Interface       40         4.1.3       HiPPI Switch       40                                                                                                                                                                                                                                                                     |     |                        | 3.2.3                    | 1                                     |    |  |  |

| 3.3High Speed Data Links303.3.1High Performance Parallel Interface303.3.2Fibre Channel303.3.3Asynchronous Transfer Mode313.3.4Scalable Coherent Interface323.4Data Flow Management323.4.1Data Flow Processes333.4.2Contention Resolution343.4.3Destination Assignment343.4.4Configuration343.4.5Error Handling354.0Event Building Prototype374.1Hardware374.1.1HiPPI Standard384.1.2VME-HiPPI Interface404.1.3HiPPI Switch40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |                        | 3.2.4                    |                                       |    |  |  |

| 3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.3.4       Scalable Coherent Interface       32         3.4       Data Flow Management       32         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         4.0       Event Building Prototype       37         4.1       Hardware       37         4.1.1       HiPPI Standard       38         4.1.2       VME-HiPPI Interface       40         4.1.3       HiPPI Switch       40                                                                                                                                                                                                                                                                                                                                                                                                                  |     |                        | 3.2.5                    |                                       |    |  |  |

| 3.3.1       High Performance Parallel Interface       30         3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.3.4       Scalable Coherent Interface       32         3.4       Data Flow Management       32         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         4.0       Event Building Prototype       37         4.1       Hardware       37         4.1.1       HiPPI Standard       38         4.1.2       VME-HiPPI Interface       40         4.1.3       HiPPI Switch       40                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 3.3                    | High S                   | Speed Data Links                      |    |  |  |

| 3.3.2       Fibre Channel       30         3.3.3       Asynchronous Transfer Mode       31         3.3.4       Scalable Coherent Interface       32         3.4       Data Flow Management       32         3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         3.4.6       Event Building Prototype       37         4.1       Hardware       37         4.1.1       HiPPI Standard       38         4.1.2       VME-HiPPI Interface       40         4.1.3       HiPPI Switch       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |                        | -                        |                                       |    |  |  |

| 3.3.4Scalable Coherent Interface323.4Data Flow Management323.4.1Data Flow Processes333.4.2Contention Resolution343.4.3Destination Assignment343.4.4Configuration353.4.5Error Handling354.0Event Building Prototype374.1Hardware374.1.1HiPPI Standard384.1.2VME-HiPPI Interface404.1.3HiPPI Switch40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |                        | 3.3.2                    | 6                                     |    |  |  |

| 3.4       Data Flow Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |                        | 3.3.3                    | Asynchronous Transfer Mode            |    |  |  |

| 3.4.1       Data Flow Processes       33         3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         4.0       Event Building Prototype       37         4.1       Hardware       37         4.1.1       HiPPI Standard       38         4.1.2       VME-HiPPI Interface       40         4.1.3       HiPPI Switch       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |                        | 3.3.4                    | Scalable Coherent Interface           |    |  |  |

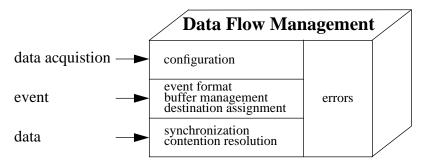

| 3.4.2       Contention Resolution       34         3.4.3       Destination Assignment       34         3.4.4       Configuration       35         3.4.5       Error Handling       35         4.0       Event Building Prototype       37         4.1       Hardware       37         4.1.1       HiPPI Standard       38         4.1.2       VME-HiPPI Interface       40         4.1.3       HiPPI Switch       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 3.4                    | Data F                   | low Management                        |    |  |  |

| 3.4.3       Destination Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |                        |                          | •                                     |    |  |  |

| 3.4.4       Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                        | 3.4.2                    | Contention Resolution                 |    |  |  |

| 3.4.5Error Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |                        | 3.4.3                    | Destination Assignment                |    |  |  |

| 4.0 Event Building Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |                        | 3.4.4                    | e                                     |    |  |  |

| 4.1       Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |                        | 3.4.5                    | Error Handling                        |    |  |  |

| 4.1.1       HiPPI Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.0 | Even                   | Event Building Prototype |                                       |    |  |  |

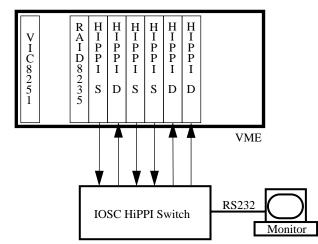

| 4.1.1       HiPPI Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 4.1                    | Hardw                    | /are                                  |    |  |  |

| 4.1.3 HiPPI Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |                        | 4.1.1                    | HiPPI Standard                        |    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |                        | 4.1.2                    | VME-HiPPI Interface                   | 40 |  |  |

| 4.1.4 RAID Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                        | 4.1.3                    | HiPPI Switch                          |    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |                        | 4.1.4                    | RAID Processor                        |    |  |  |

|     | 4.2  | Software                           | e                                              |    |  |  |  |

|-----|------|------------------------------------|------------------------------------------------|----|--|--|--|

|     |      | 4.2.1                              | HiPPI Firmware                                 |    |  |  |  |

|     |      | 4.2.2                              | Event Handling                                 |    |  |  |  |

|     |      | 4.2.3                              | Data Flow Processes                            |    |  |  |  |

|     |      | 4.2.4                              | Destination Assignment                         |    |  |  |  |

|     |      | 4.2.5                              | Configuration                                  |    |  |  |  |

|     | 4.3  | Simple I                           | Data Transfers                                 |    |  |  |  |

|     |      | 4.3.1                              | Data Path                                      |    |  |  |  |

|     |      | 4.3.2                              | Method of Measurement                          |    |  |  |  |

|     |      | 4.3.3                              | Minimum Latency                                |    |  |  |  |

|     |      | 4.3.4                              | Other Overheads                                |    |  |  |  |

|     |      | 4.3.5                              | Data Moving                                    |    |  |  |  |

|     | 4.4  | Parallel                           | Event Building                                 |    |  |  |  |

|     | 4.4  | 4.4.1                              | Fixed Event Sizes                              |    |  |  |  |

|     |      | 4.4.1                              | Event Size Variations                          |    |  |  |  |

|     |      | 4.4.2                              |                                                |    |  |  |  |

|     |      | 4.4.5                              | Destination Assignment                         |    |  |  |  |

|     |      |                                    | Fault Tolerance                                |    |  |  |  |

|     | 4.5  | Conclus                            | ions                                           | 63 |  |  |  |

| 5.0 | Simu | lation Pro                         | ogram                                          | 65 |  |  |  |

|     | 5.1  | 6                                  |                                                |    |  |  |  |

|     | 5.2  |                                    | Event Simulation                               |    |  |  |  |

|     | 5.2  | 5.2.1                              |                                                |    |  |  |  |

|     |      | 5.2.1                              | Definition                                     |    |  |  |  |

|     |      |                                    | MODSIM II                                      |    |  |  |  |

|     | 5.3  | -                                  | mulation Library (DSL)                         |    |  |  |  |

|     |      | 5.3.1                              | Elements                                       |    |  |  |  |

|     |      | 5.3.2                              | Graphical User Interface                       |    |  |  |  |

|     |      | 5.3.3                              | Tracing Facility                               |    |  |  |  |

|     |      | 5.3.4                              | Example                                        | 69 |  |  |  |

|     | 5.4  | Simulati                           | ion Program for Event Building Systems (SIMEB) |    |  |  |  |

|     |      | 5.4.1                              | Elements                                       | 70 |  |  |  |

|     |      | 5.4.2                              | Configuration                                  | 71 |  |  |  |

|     |      | 5.4.3                              | Collection of Statistics                       | 72 |  |  |  |

| 6.0 | Simu | lation of                          | Event Building Systems                         | 73 |  |  |  |

| 0.0 |      |                                    | Model                                          |    |  |  |  |

|     | 6.1  | -                                  |                                                |    |  |  |  |

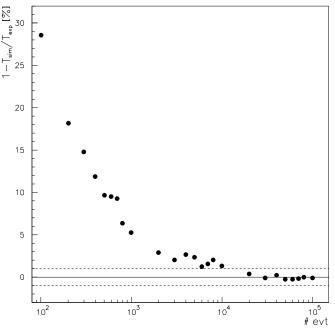

|     |      |                                    | Warm-up and Convergence                        |    |  |  |  |

|     | 6.2  |                                    | vent Building System                           |    |  |  |  |

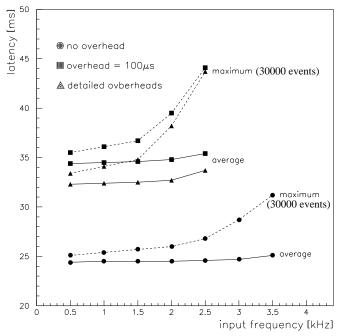

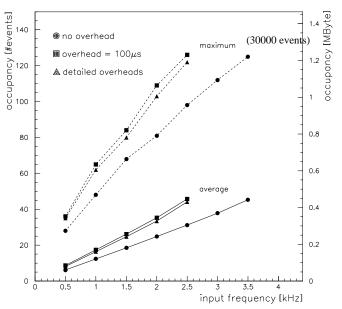

|     |      | 6.2.1                              | Overhead and Processing Times                  |    |  |  |  |

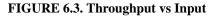

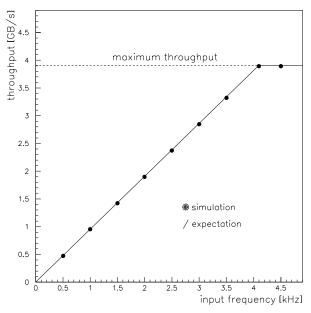

|     | 6.3  | Event Si                           | ize Variations and Correlations                |    |  |  |  |

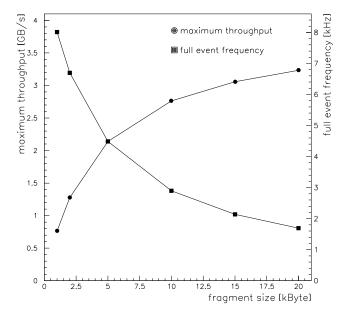

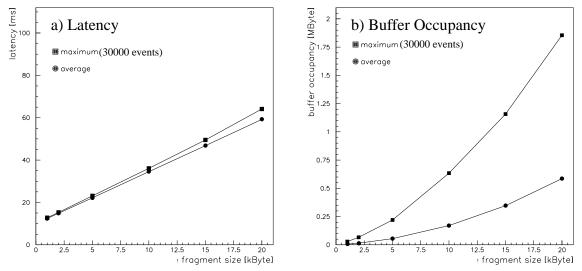

|     |      | 6.3.1                              | Full Event Size                                |    |  |  |  |

|     |      | 6.3.2                              | Event Size Distributions                       |    |  |  |  |

|     |      | 6.3.3                              | Event Size Correlations                        |    |  |  |  |

|     |      | 6.3.4                              | Link Speed                                     |    |  |  |  |

|     |      | 6.3.5                              | Scaling Behaviour                              |    |  |  |  |

|     | 6.4  | ATLAS                              | Model                                          |    |  |  |  |

|     | 5.1  | 6.4.1                              | Off-line Simulations                           |    |  |  |  |

|     |      | 6.4.2                              | Readout Buffer Mapping                         |    |  |  |  |

|     |      | 6.4.3                              | Event Size Distributions                       |    |  |  |  |

|     |      | 6.4.4                              | Results                                        |    |  |  |  |

|     | 6.5  |                                    | ions                                           |    |  |  |  |

|     |      |                                    |                                                |    |  |  |  |

| 7.0 | Simu | Simulation of Data Flow Management |                                                |    |  |  |  |

|     | 7.1                     | Contention Resolution                  |  |

|-----|-------------------------|----------------------------------------|--|

|     | 7.2                     | Destination Assignment Schemes         |  |

|     |                         | 7.2.1 Random Destination Assignment    |  |

|     |                         | 7.2.2 Destination-Initiated Assignment |  |

|     |                         | 7.2.3 Data Flow Manager                |  |

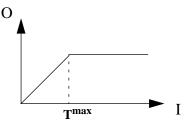

|     | 7.3                     | Traffic Shaping                        |  |

|     |                         | 7.3.1 Definition                       |  |

|     |                         | 7.3.2 A Possible Algorithm             |  |

|     |                         | 7.3.3 Performance                      |  |

|     |                         | 7.3.4 Summary and Outlook              |  |

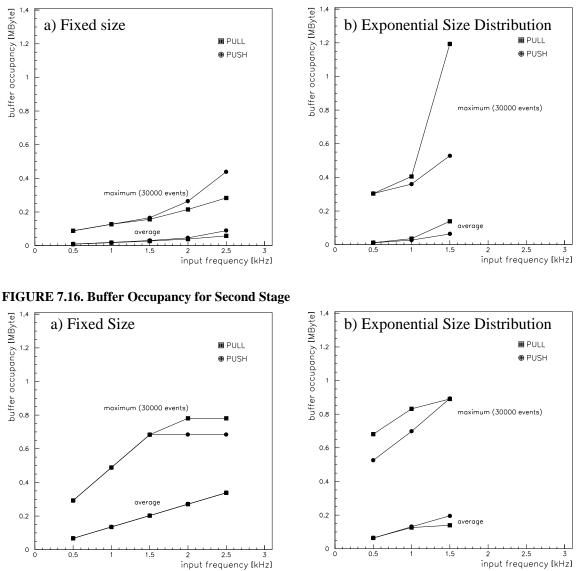

|     | 7.4                     | Two-Stage Event Builder                |  |

|     |                         | 7.4.1 Model                            |  |

|     |                         | 7.4.2 Performance                      |  |

|     | 7.5                     | Conclusions                            |  |

| 8.0 | Conclusions and Outlook |                                        |  |

|     | Refer                   | rences                                 |  |

# **1.0 Introduction**

The Standard Model (SM) is a description of all elementary particles and their interactions known today. Its biggest successes are the predictions of phenomena which could subsequently be discovered and measured in experiments, like the intermediate vector bosons [Arn83] and the top-quark [Abe95].

But there are also still open questions: the Higgs boson which explains the spontaneous breaking of symmetry in the electroweak sector of the SM has not yet been discovered. Its existence is closely related to a very fundamental question, namely: what is the origin of the different particle masses? And furthermore, when searching at ever higher energies there is always the possibility to discover new physics which could change the understanding of particle physics.

In order to research in this direction the Large Hadron Collider (LHC) [Eva95] was proposed as a hadron collider with unprecedented high energies and high luminosity. General-purpose experiments at this collider will be able to explore a new field of particle physics with high precision measurements. They will have to cope with high data rates which require sophisticated trigger and data acquisition systems to observe and select the rare and interesting phenomena.

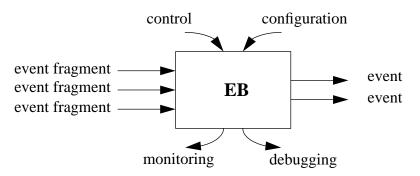

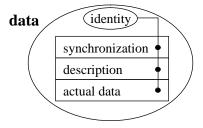

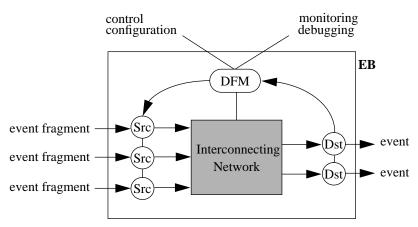

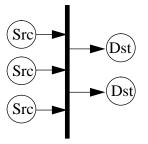

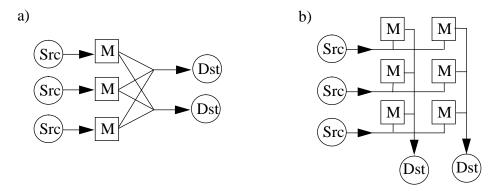

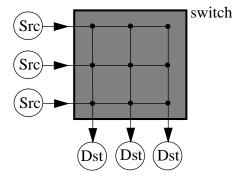

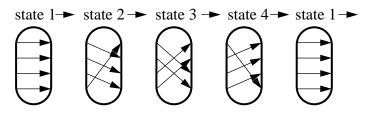

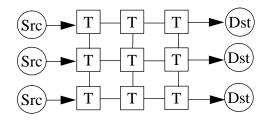

An event building system is a part of the trigger and data acquisition system where data from events belonging to the same interaction are assembled. It has to match with the trigger rates up-stream and down-stream, must not introduce deadtime and not lose event data. Its performance is determined by the input rate and the event fragment size distributions and their correlations. Future experiments at the LHC [ATL94][CMS94] will need event building systems with a bandwidth of 1 to 100 GB/s and which will be able to assemble events from 100 to 1000 data sources at rates of 1 to 100 kHz. Bus based systems are not appropriate to fulfill this task and parallel event building based on high speed interconnects with switching elements has to be envisaged.

This work presents studies carried out to prepare a future experiment at the LHC. The feasibility of event building systems using commercial high speed interconnect standards and commercially available communication switches is investigated in two complementary ways: by building a prototype and by simulations. A small-scale prototype has been built to adapt a given technology to the task of event building and to obtain a realistic model of the switch. Simulations, on the other hand, use the model and the parameters measured in the prototype and extrapolate to full-scale systems as needed in a future experiment. Realistic event size distributions can be studied as well as different data flow managment schemes.

In chapter 2 this work presents an overview of the LHC, its physics issues and one of the general-purpose experiments with its detector lay-out and its trigger and data acquisition system. Chapter 3 defines the components needed in an event building system and discusses different architectures and high speed interconnect standards available. The prototype and its measurements are presented in chapter 4. Chapter 5 presents the simulation program used. And simulations of realistic event building systems are discussed in chapter 6. Different control schemes of event building systems are compared in chapter 7.

# 2.0 ATLAS Experiment

# 2.1 Large Hadron Collider

The LHC [Eva95] is a future proton-proton collider at CERN operating at a centre-ofmass energy of  $\sqrt{s} = 14$  TeV and at a nominal luminosity of L =  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. The LHC will reach higher energies than ever achieved before and thus open a new field of research in particle physics, in particular for the search for the Higgs boson.

# 2.1.1 Machine

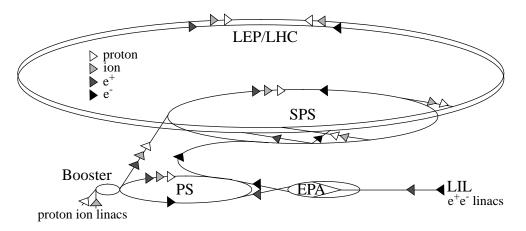

The LHC, approved in 1994, will be operational in 2004. It will be accommodated in the LEP tunnel. The existing accelerator complex at CERN consisting of the 50 MeV linac, the 1 GeV booster, the 26 GeV Proton Synchrotron (PS) and the 450 GeV Super Proton Synchrotron (SPS) constitute an excellent injection complex for the LHC as shown in figure 2.1.

### FIGURE 2.1. LHC and Injection Complex at CERN

Furthermore, constructing the LHC in the LEP tunnel opens up the possibility of having electron-proton collisions of a centre-of-mass energy up to  $\sqrt{s} = 1.7$  TeV. The LHC can further be used for heavy ion collisions and reaches for lead ions a centre-of-mass energy of up to  $\sqrt{s} = 1312$  TeV. Two general-purpose pp experiments (ATLAS [ATL94] and CMS [CMS94]) and one heavy ion experiment (ALICE [ALI93]) are proposed.

#### TABLE 2.1. Parameters of the LHC

| Circumference | 27 km                                     |

|---------------|-------------------------------------------|

| Proton Energy | 7.0 TeV                                   |

| Luminosity    | $10^{34} \mathrm{cm}^{-2}\mathrm{s}^{-1}$ |

| Bunch Spacing | 25 ns                                     |

### 2.1.2 Magnets

A technical challenge which must be overcome at the LHC is the realization of the superconducting dipole magnets [Eva95] providing a field of 8.4 T. Figure 2.2 shows a crosssection of the magnets with two counter-rotating proton beams in one device. This design uses copper-clad niobium-titanium windings and operates at a temperature of 1.9 K. Some other parameters are listed in table 2.2. A total of 1,296 dipole magnets are needed, plus 2,500 other magnets ranging from normally conducting bending magnets to large superconducting focusing quadrupoles. The cryogenics system for the magnets will contain some 700,000 l of liquid helium and have a power consumption of about 140 kW.

#### FIGURE 2.2. LHC Magnets

| Sc. Bus-Bars                    | Heat Exchanger Pipe                   |

|---------------------------------|---------------------------------------|

| Iron Yoke                       | Superconducting Coils                 |

| Shrinking Cylinder              | Beam Screen                           |

| Thermal Shield<br>2.2 K He Pipe | 4.5 K He Pipe<br>Non-Magnetic Collars |

| Radiative Insulation            |                                       |

| Vacuum Vessel                   | Beam Pipe                             |

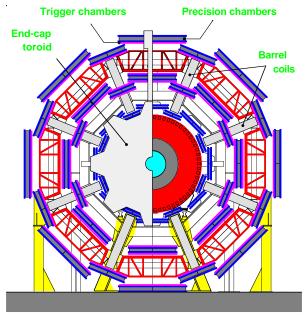

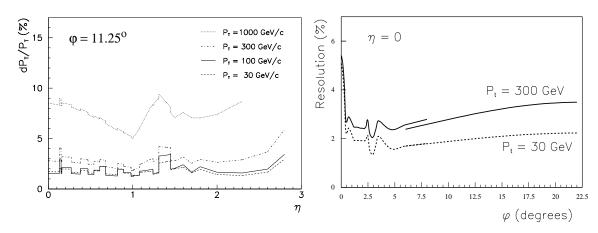

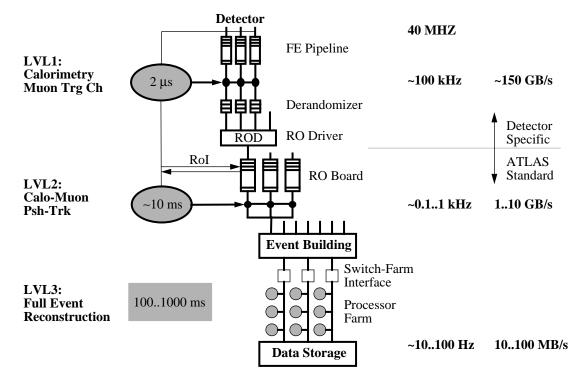

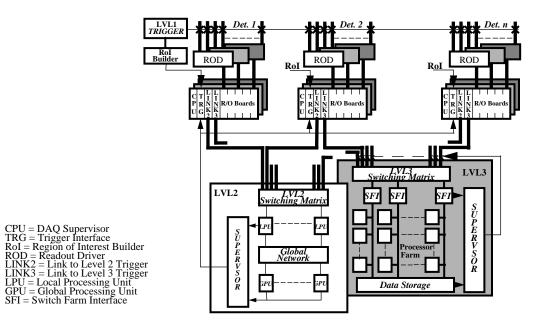

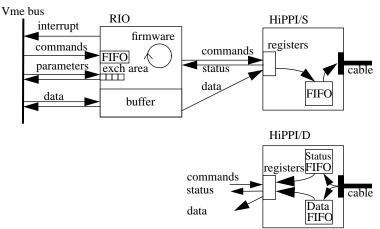

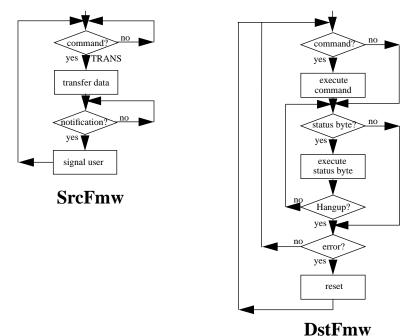

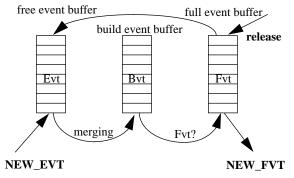

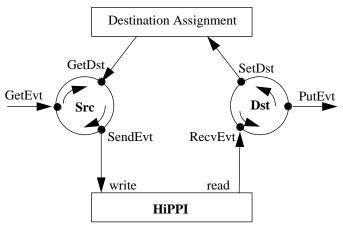

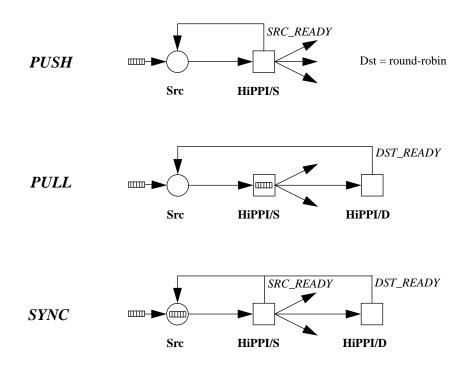

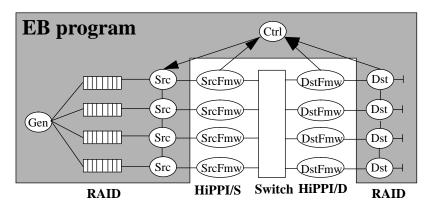

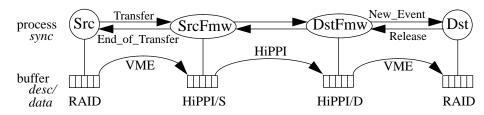

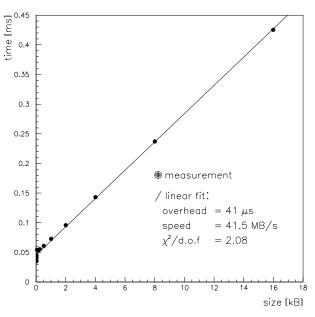

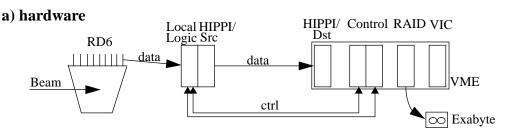

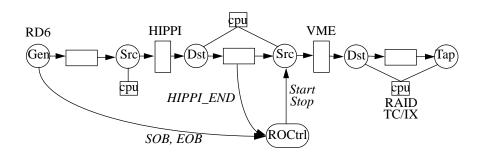

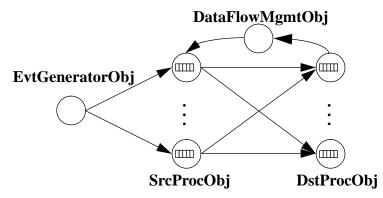

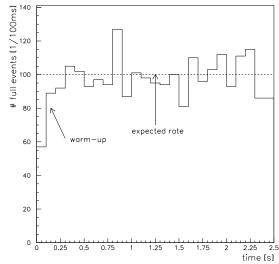

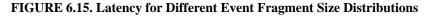

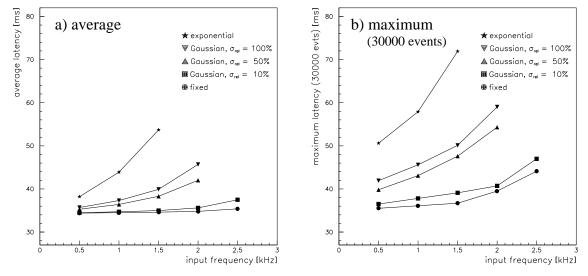

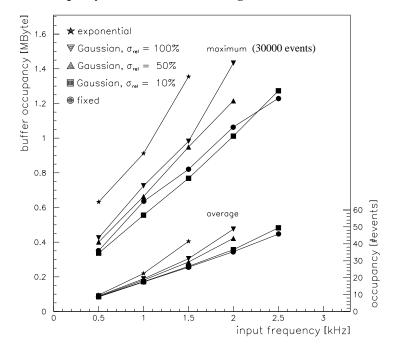

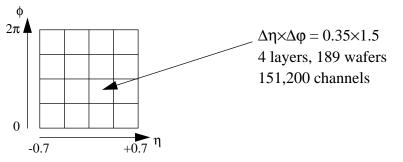

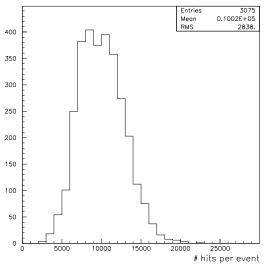

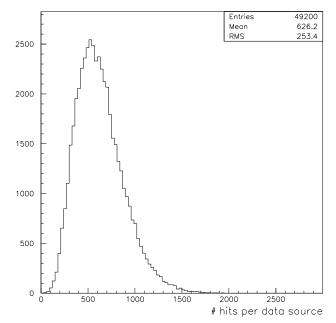

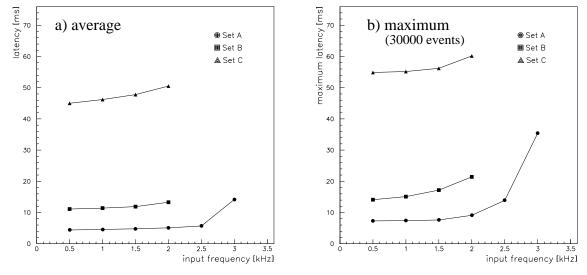

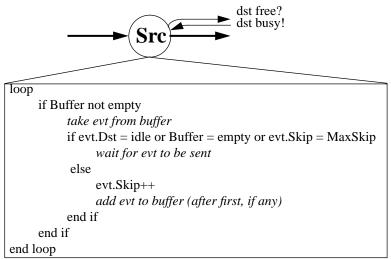

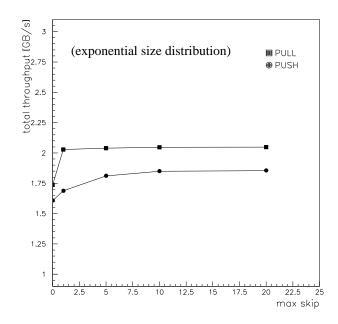

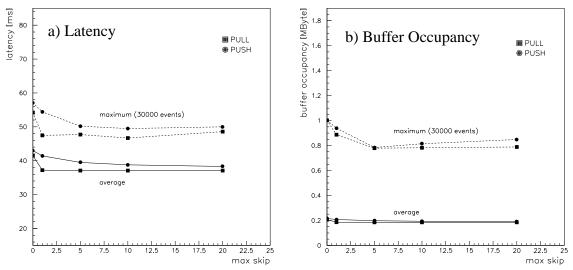

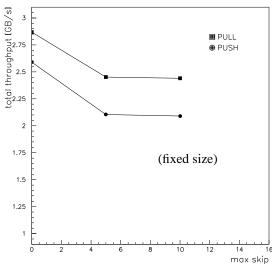

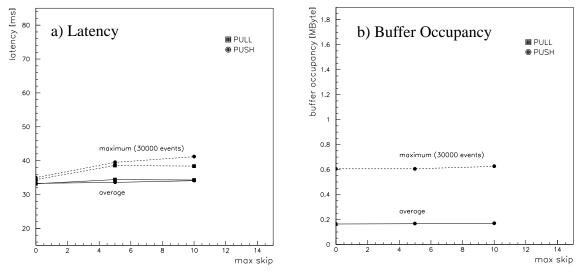

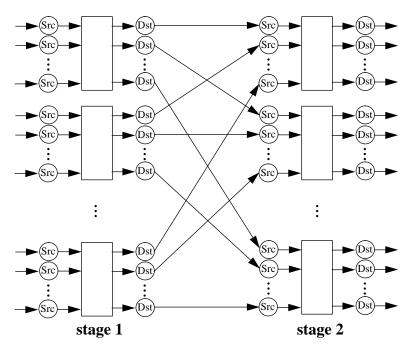

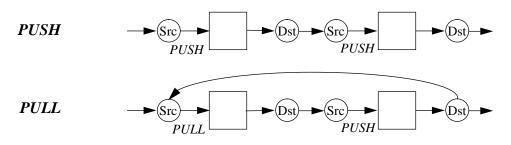

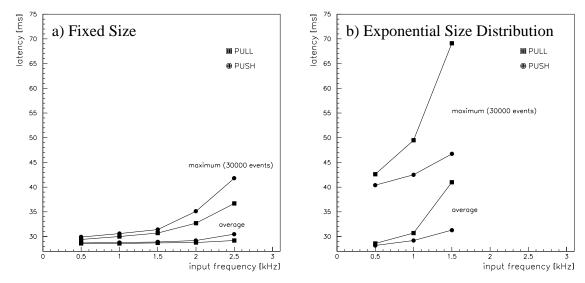

| 1.8 K He Pipe                   | 20 K He Pipe<br>Support Post          |