CERN/DRDC 93-32

**RD-27 Status Report**

11 August 1993

CERN DADC 93-32

# FIRST-LEVEL TRIGGER SYSTEMS FOR LHC EXPERIMENTS

I. Brawn, R.E. Carney, Y. Ermoline<sup>1</sup>, J. Garvey, D. Grant, P. Jovanovic, I. McGill, R. Harris, R. Staley, A. Watson

School of Physics and Space Research, University of Birmingham, UK

N. Ellis\*), C. Jacobs, B.G. Taylor, J.-P. Vanuxem, H. Wendler *CERN*, *Geneva*, *Switzerland*

P. Hanke, M. Keller, E.-E. Kluge, K. Schmitt, M. Wunsch Institut für Hochenergiephysik der Universität Heidelberg, Germany

P. Böd, H. Hentzell, C. Svensson, J. Yuan Linköping University, Sweden

J. Fent, W. Froechtenicht, C. Kiesling, H. Oberlack, P. Schacht

Max-Planck-Institut für Physik, Munich, Germany

E. Eisenhandler, M. Landon, G. Thompson

Queen Mary and Westfield College, University of London, UK

J. Dowdell, C.N.P. Gee, A. Gillman, R. Hatley, V. Perera, S. Quinton Rutherford Appleton Laboratory, UK

B. Green, D. Johnson, J. Strong

Royal Holloway and Bedford New College, University of London, UK

E. Gennari, A. Nisati, E. Petrolo, M. Torelli, S. Veneziano, L. Zanello Intituto Nazionale di Fisica Nucleare and Universita La Sapienza, Rome, Italy

G. Appelquist, C. Bohm, S. Hellman, B. Hovander, N. Yamdagni, X. Zhao Stockholm University, Sweden

(\*) Spokesman

<sup>&</sup>lt;sup>1</sup> Visitor from Institute for High Energy Physics, Russia, 142284, Moscow region, Protvino.

# **Summary**

The RD27 project was approved in June 1992 with the following milestones:

- design outline of a first level trigger system

- · detailed design studies and beam tests of a prototype calorimeter trigger

- · detailed design studies of a muon trigger, including several detector options

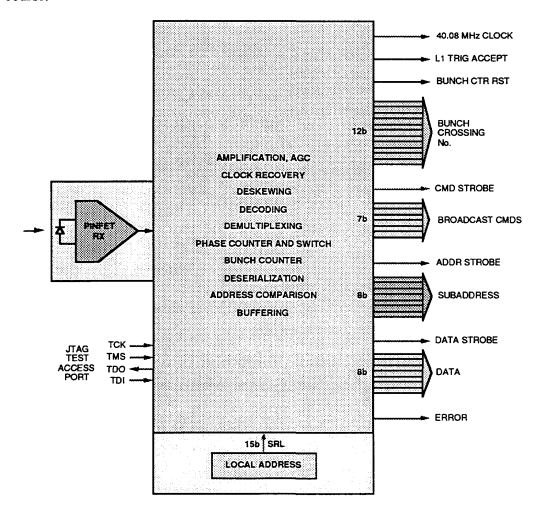

Design studies have been performed for all parts of the level-1 trigger system, which consists of subtrigger processors associated with the calorimeters and muon detectors, a central trigger processor that combines the subtrigger results and makes the overall yes/no decision, and a trigger, timing and control distribution system which distributes the trigger decision to the front-end systems. Our design studies also include the interface to the level-2 trigger which makes use of region-of-interest information provided by the level-1 system. Our design studies are described briefly in the main body of this status report and in more detail in RD27 internal notes.

Detailed design studies have been made for the calorimeter trigger processor, where we are investigating two architectures based on bit-parallel and bit-serial digital processors respectively. In the case of the bit-parallel approach, we have constructed a first prototype processor and successfully tested it in real time at test beams in conjunction with the Accordion and TGT liquid-argon calorimeters. This prototype processor is based on an Application-Specific Integrated Circuit (ASIC) which was produced for the project. The beam tests were carried out at the full LHC clock speed of 40 MHz; tests were also made at the originally envisaged frequency of 67 MHz.

Our calorimeter trigger design studies result in rather compact processor systems occupying only a few electronic crates. We believe that such processors could be constructed based on technology that is currently available. However, more work is required to validate these designs, particularly in relation to data transmission into the processor where the total data rate is several hundred Gbytes per second. We plan to build further technical demonstrators to address this issue.

Extensive simulation work has been performed for the calorimeter trigger. The algorithms that are included in the processors were selected on the basis of these studies. Our efficiency and rate calculations were used in the letters of intent of ATLAS and CMS. Where comparison is possible, our predictions have been found to agree well with our test-beam measurements.

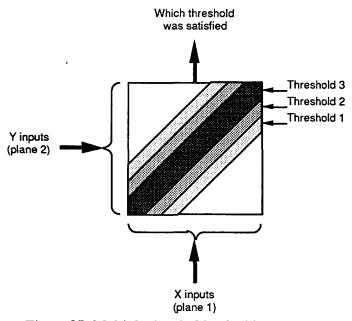

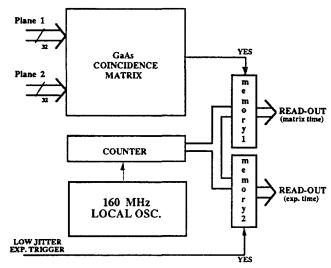

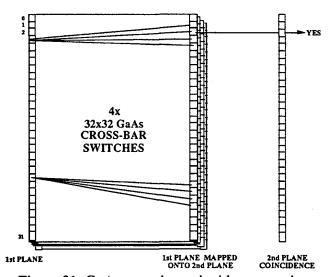

A detailed design study has been performed for a muon trigger based on Resistive Plate Chamber (RPC) detectors and a first demonstrator system is under construction in preparation for tests with RD5 later this year using large-area RPCs. The initial prototype is based on coincidence matrices made from expensive commercial GaAs products. We hope to develop a second prototype based on custom programmable coincidence-array circuits with LHC performance.

We are actively working on simulation studies to evaluate the physics requirements and the backgrounds for the muon trigger. The implications of the high rate of "random" hits in the muon detectors, due to the enormous flux of low-energy photons and neutrons in the experimental areas, are still being evaluated.

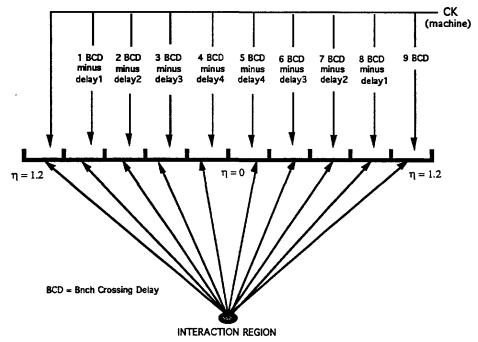

The possibility of making a level-1 muon trigger using the precision drift-chamber detectors is being studied. Conceptual design studies for various chamber geometries have been performed, taking into account the need to trigger at relatively low  $p_T$  ( $p_T \approx 6$  GeV) for B physics analyses. We have also performed an initial investigation of the feasibility of bunch-crossing identification logic based on programmable coincidence arrays, extending ideas used by members of our collaboration in the forward-muon trigger of the H1 experiment at HERA.

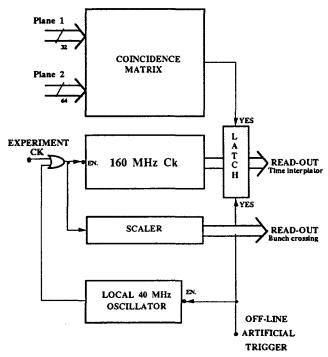

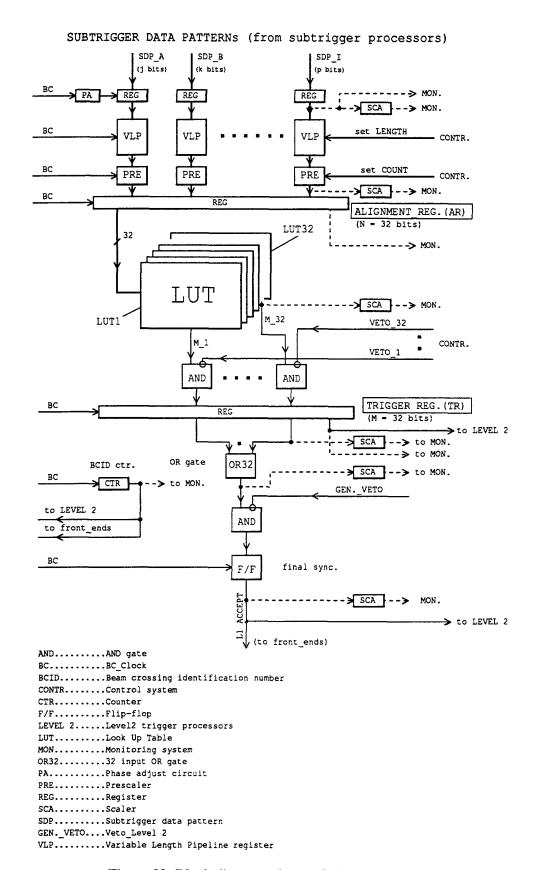

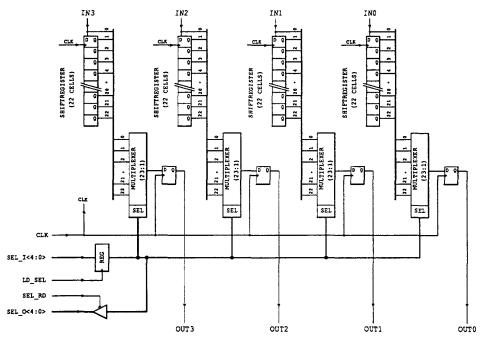

Initial design studies have been made for the central trigger processor. This receives information from the subtrigger processors, allowing for differences in latency, and makes the overall level-1 decision. Facilities to prescale high-rate triggers are included, and extensive monitoring is provided with the provision of scalers to record trigger rates. We plan to make more detailed design studies and to perform modelling using VHDL. Several key components – a variable length pipeline, a scaler and a prescaler – will be studied in more detail, initially using a field-programmable gate array test bench.

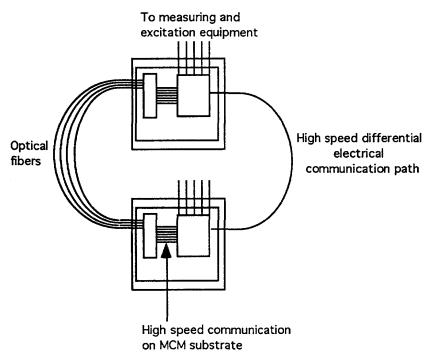

In conjunction with RD12, we have studied a range of technologies for the optical transmission of timing, trigger and control signals from a single node at the central trigger processor to large numbers of front-end electronics locations. Using currently available components, we have demonstrated the capability of time-division multiplexing the required signals and broadcasting them over an entirely passive all-glass distribution network to 1024 receivers per laser transmitter. The recovered clock jitter is less than 100 ps rms, compatible with foreseen LHC experiment requirements. We plan to pursue this development using such higher-power lasers and new optoelectronic technologies as become available in the future.

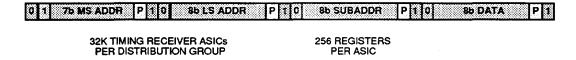

In the next phase, in conjunction with RD12, RD16, CERN Microelectronics Group and interested users, we plan to develop a demonstrator timing receiver ASIC which could be incorporated in the front-end electronics of detector prototypes in future beam tests. In addition to the clock, the receiver would deliver a unique bunch crossing number synchronously with each level-1 trigger decision, with programmable compensation for detector, electronics, time-of-flight and signal propagation delays. The receiver ASIC would also be able to transmit to the front-end electronics separately deskewed broadcast and individually-addressed commands and data.

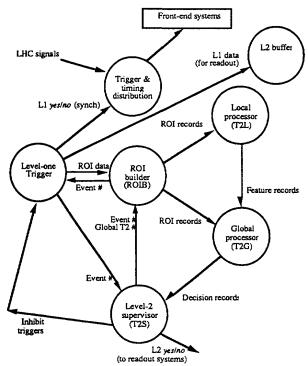

Initial studies have been made for the level-1/level-2 interface system, including first timing measurements. This work will be extended in the second year of the project.

A list of suggested milestones for the second year of the RD27 project and the funding request to CERN can be found in Sections 8 and 10 of this status report.

#### 1. Introduction

The RD27 project is a broad study of level-1 trigger systems for LHC experiments. The work includes level-1 subtrigger processors based on calorimetry and muon detectors, the central trigger processor that combines the results from different subtriggers, the timing, trigger and control distribution system that delivers the trigger decision to the front-end electronics, and the interface to the level-2 trigger. Monte Carlo simulation plays an essential role in our studies, for algorithm optimisation (rate and efficiency calculations for background and signal processes) and for comparison with test-beam data (single particle simulation).

The challenges of triggering in LHC general-purpose experiments are formidable, especially at level-1 [1]. At high luminosity, the proton-proton interaction rate will be  $\sim 10^9$  Hz, with a bunch-crossing rate of 40 MHz. The readout time for subdetectors is typically 10  $\mu$ s, limiting the rate into the level-2 system to 100 kHz. Hence, a very large rejection power is required from the level-1 trigger. The cross-sections for many of the physics processes that are sought at LHC are very small, so high trigger efficiency is mandatory, in some cases with rather complex signatures. Furthermore, LHC trigger systems should be flexible, allowing one to react to new physics or to unforeseen background conditions.

Issues that affect the design of the level-1 trigger system are the following:

- The readout of LHC detectors is pipelined because of the short (25 ns) bunch-crossing period. The length of these readout pipelines, which may be analogue or digital, depends on the level-1 trigger latency which should be as short as possible.

- The trigger must uniquely identify the bunch crossing containing the interaction of interest. This is especially challenging in the case of triggers based on detectors with a signal collection time longer than 25 ns.

- The calorimeter trigger must be able to operate at high luminosity in the presence of pileup from many overlapping events.

- Muon detectors will be exposed to a high flux of low-energy photons and neutrons

which can produce "noise" hits; the muon trigger must be able to operate under these

conditions.

- The physical size of LHC detectors and their large numbers of readout channels require a complex system for establishing and maintaining synchronisation, and for distributing the trigger decision to the front-end electronics which will, in most cases, be on the detector.

- Information from the level-1 trigger can be used to guide the level-2 trigger, for example by indicating the location of electron/photon candidates.

- It is essential to foresee extensive test and monitoring facilities, especially in the case of on-detector electronics.

- Facilities for maintaining the calibration and synchronisation of the trigger processors must be included in the design.

- Parameters such as transverse momentum  $(p_T)$  thresholds should be programmable, requiring a control system.

The design studies and demonstrator prototypes being developed in RD27 take into account all the above issues.

The RD27 collaboration maintains close contact with other R&D groups and with both ATLAS and CMS. We collaborate informally with RD11 (EAST) in the study of the interface to the level-2 trigger. Work on the timing, trigger and control distribution system is performed jointly with RD12. For the calorimeter trigger work, we have made beam tests with the RD3 Accordion calorimeter and with the RD33 TGT calorimeter; close contact is maintained with RD16 (FERMI). For the muon trigger, beam tests will be performed with RD5. Members of RD27 participate strongly in trigger-related activities within ATLAS. Members of CMS attend RD27 meetings as observers and RD27 work is presented to the CMS collaboration on request.

The RD27 project was approved in June 1992 [2] with the following milestones:

- design outline of a first level trigger system

- · detailed design studies and beam tests of a prototype calorimeter trigger

- detailed design studies of a muon trigger, including several detector options

In this report we describe the work that we have done so far, and propose a continued programme of work for the coming year.

### Outline of Level-1 Trigger System

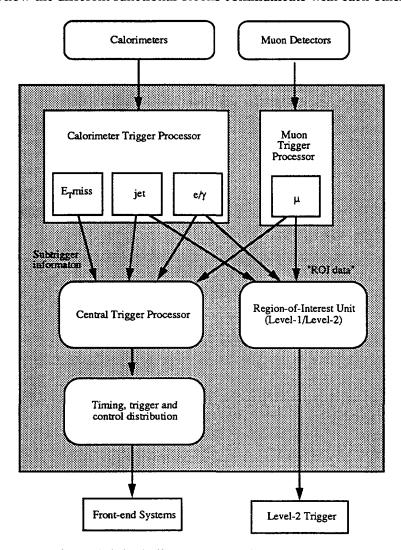

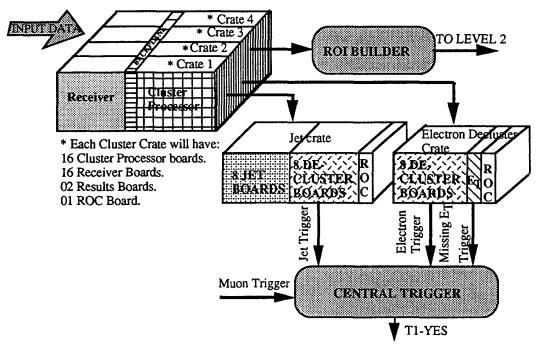

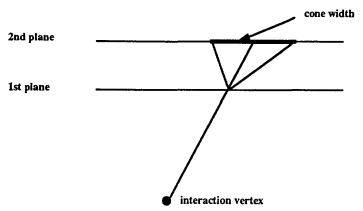

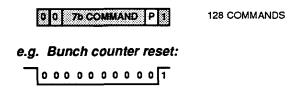

In Figure 1 we show a block diagram of a level-1 trigger system based on calorimetry (electron, photon, jet, missing transverse energy triggers) and on muon detectors. The subtrigger processors work independently and in parallel to summarise the characteristics of the event:

- information on multiplicity of electrons/photons for several thresholds with various isolation requirements

- information on multiplicity of jets for several thresholds

- information on missing transverse energy for several thresholds

- information on multiplicity of muons for several thresholds

These data are transmitted to the central level-1 trigger processor that makes the overall yes/no trigger decision, based on combinations of trigger requirements, with the possibility of prescaling high-rate triggers. The central trigger processor is in turn connected to the timing, trigger and control distribution system that broadcasts the trigger decision to the front-end electronics, much of which is on the detector.

Region-of-interest information from the level-1 subtrigger processors is sent to the level-2 trigger system, which only needs to acquire and process data from regions of the detector in the vicinity of (electron, photon, jet or muon) candidates flagged by the level-1 system.

The trigger system is based on purpose-built digital hardware processors and makes extensive use of micro-electronics. The processing is pipelined and many operations are performed in parallel. Such processors have a fixed set of algorithms, but are programmable at the level of parameters. In practice considerable flexibility can be provided. The trigger processors themselves are synchronous with the LHC clock. However, we are considering using asynchronous transmission of zero-suppressed data to reduce bandwidth requirements where necessary, notably at the input to the calorimeter trigger processor.

In the following sections, we describe the functional blocks of Figure 1 in detail and comment on how the different functional blocks communicate with each other.

Figure 1: Block diagram of level-1 trigger system.

# 2. Calorimeter Trigger

#### Introduction

Several possibilities have been suggested for level-1 calorimeter triggering at future hadron colliders. ATLAS [3], CMS [4] and SDC [5] propose to use purpose-built digital processors, while GEM [6] considers a mixed analogue/digital system as its baseline option, with a programmable digital processor as an alternative.

In RD27 we are studying purpose-built, synchronous digital processors for the level-1 calorimeter trigger. Strong points of this approach are the following:

• It is possible to implement relatively complicated algorithms that optimise the trigger performance in terms of efficiency and rejection power. Many different sets of thresholds can be provided, and (optional) criteria such as electron/photon isolation can be implemented.

- A large degree of flexibility can be provided through programmable parameters (thresholds and control words).

- A programmable threshold can be applied at the cell level, suppressing contributions from electronic noise and pileup. The threshold can be increased for high-luminosity running (more pileup) or in case of unforeseen problems such as coherent noise.

- Ease of calibration the trigger ADC system (if separate) can be cross-calibrated against the precision readout.

- Ease of monitoring intermediate results from the calculation can be read out and checked against values calculated from the input data, requiring an exact match.

- Ease of testing and diagnostics test patterns can be played through the processor, localising faults.

- The processing latency can be minimised using hardwired algorithms and fixed routing of the data by direct links.

- The interface between the digitisation system and the trigger processor can be optimised to cope with the extremely high bandwidth, for example by exploiting the low detector occupancy (using zero-suppression).

- It is relatively easy to equalise the phase of digital signals relative to one another, for example using programmable delays or FIFOs.

- Extensive use of Application Specific Integrated Circuits (ASICs) allows costeffective implementations. Commercial CAD tools provide an easy route to a wide

range of products from different vendors. Hence, one can exploit new technology as it

becomes available and select among manufacturers to obtain the best price. Our

preliminary studies suggest that ASIC products that are already available are adequate

for our needs; we can exploit future developments to add functionality or reduce the

system cost.

We are following two calorimeter trigger design schemes in RD27, based respectively on bit-parallel and bit-serial operations (addition, comparison, etc.), as described below. These design studies are complementary and substantial "cross-fertilisation" has already occurred. They could be combined in the future into a hybrid design; many features are common to the two designs as described below.

The calorimeter trigger processor acts on reduced granularity data from the electromagnetic and hadronic calorimeters (ECAL and HCAL), with a typical trigger cell size of  $\Delta\eta \times \Delta\varphi = 0.1 \times 0.1$  in pseudorapidity – azimuth space, and with just one sampling in each of the ECAL and HCAL. Simulation studies (described below) suggest that 8-bit or 9-bit linear data with a least count of about  $E_T = 1$  GeV are adequate for the level-1 trigger calculation. These data can be obtained from an independent trigger ADC system, using analogue summation over trigger cells before the ADC, and a look-up table after the ADC to apply calibration constants. Alternatively, if a digital front-end system such as FERMI [7] is adopted for the calorimeter readout, the data for the level-1 trigger can be derived from the precision ADCs. Beam tests performed so far by RD27 have used dedicated trigger ADC systems. However, we are in close contact with the FERMI collaboration, who have included in their design a level-1 trigger sum that could be interfaced to either the bit-parallel or the bit-serial processor design.

The signals from calorimeters proposed for LHC experiments, such as the Accordion liquid argon calorimeter, are slow compared to the 25 ns bunch-crossing interval. Hence, if the

raw digitised signals are used, large energy deposits would be seen by the trigger processor for several consecutive bunch-crossings. This problem can be overcome by using signal processing techniques, which can be integrated with the ADC system. We have studied simple digital filter algorithms, applying them to data collected with the Accordion calorimeter. Analogue signal processing, as demonstrated by GEM [6], is an alternative under consideration.

The transmission of data into the trigger processor system is a major issue. For a pseudorapidity coverage of  $|\eta| < 3$  and a trigger cell size of  $\Delta \eta \times \Delta \varphi = 0.1 \times 0.1$  in each of the ECAL and HCAL, one has  $\approx 8000$  trigger cells. Assuming 8-bit data with a sampling rate of 40 MHz, the total data rate is 320 Gbytes/s. Furthermore, the two-dimensional nature of cluster-finding algorithms requires that each processing element knows about its environment. Hence one has to fan-out data between processing elements, increasing the overall bandwidth. (While one could instead make use of additional connections between processing elements, we do not find this alternative attractive.) During the next year, RD27 plans to address this difficult problem, verifying our detailed design studies using demonstrator prototypes as described in detail below.

We have already shown that complex trigger algorithms can be implemented on ASICs. A first demonstrator trigger processor for isolated electrons has been built and tested with the Accordion and TGT liquid-argon calorimeters at test beams. Building on this experience, we have made detailed design studies for a bit-parallel and a bit-serial trigger processor system.

The rest of this section is organised as follows. Physics simulation studies, which were used to optimise and evaluate trigger algorithms, are presented<sup>1</sup>. Next, we explain the differences between the bit-parallel and bit-serial processing architectures. We then describe the bit-parallel trigger processor demonstrator, the beam tests performed with RD3 (Accordion) and with RD33 (TGT), and present results of off-line analysis of the test beam data. Finally, we present the two detailed design studies that have been performed for calorimeter trigger processors, using bit-parallel and the bit-serial architectures, and propose a programme of work for the coming year.

# Algorithms and simulation studies

The essential requirements for a first-level trigger system are that it should reduce the event rate in an LHC detector from the bunch-crossing frequency of 40 MHz with about 25 events per bunch crossing to a rate that can be accepted by the next stage in the trigger chain (at most  $\sim 100 \text{ kHz}$ ), while maintaining high efficiency for interesting physics processes. Physics simulations, that is the simulation of possible LHC events and detector response, are needed to determine whether or not a proposed trigger algorithm can meet these goals. Such simulations are used to optimise algorithms and their parameters, and to determine requirements such as the dynamic range for calorimeter signals used in the trigger. Members of our collaboration have performed extensive simulation studies that build on earlier work performed for the Aachen workshop [8] and within the LHC experimental collaborations [9]. Here we briefly describe a few examples of simulations performed, mainly in relation to the electron/photon trigger. A more detailed description of this work, which includes studies of jet and missing  $E_T$  triggers, can be found in Ref. [10].

<sup>&</sup>lt;sup>1</sup>Our predictions for trigger rates were used by both ATLAS and CMS in their letters of intent.

# Physics processes simulated

For the electromagnetic (e.m.) cluster trigger, the efficiency of the algorithms was studied using events containing single electrons of different energies and rapidities. Minimum-bias events, generated using PYTHIA, were superimposed to simulate the effects of pileup. Real events are more complex than this, containing in addition to the electrons or photons an underlying event from the residual proton—proton system and possibly also hadronic jets. In order to study the performance of the e.m. cluster trigger in more realistic circumstances three examples of possible physics processes were simulated using PYTHIA:

- $H^0 \rightarrow \gamma \gamma$ ,  $m_H = 120 \text{ GeV}$

- $H^0 \rightarrow Z Z^* \rightarrow e^+e^-e^+e^-$ ,  $m_H = 130 \text{ GeV}$  and 150 GeV

- Top events where the top quarks decayed to electrons

The rate for the first-level e.m. cluster trigger will be dominated by backgrounds from high- $p_T$  jet events. Jets may mimic the signature for electron or photon production if they contain one or more high- $p_T$   $\pi^0$ s or an early-showering high- $p_T$  hadron. In order to study the background rates for this trigger, a large-statistics sample of jet events was simulated using PYTHIA.

#### **Detector** simulation

A number of detector models of different degrees of complexity and realism were used in these studies. The choice of model was determined by the degree of detail needed to adequately answer the question posed and by the computer resources available.

For many of the studies, simple models based on parameterisations of detector response were used. The four-vectors of final-state particles were smeared with the resolutions of a "typical" LHC detector, namely  $\Delta E/E = 10\%/\sqrt{E}$  for electromagnetic particles and  $\Delta E/E = 50\%/\sqrt{E}$  for hadrons. Longitudinal sharing of hadronic showers between e.m. and hadronic calorimeters was parameterised; no transverse shower width was simulated. Electronic effects and event pileup were included in the simulation. Such models were used for studies of jet trigger rates, the required ADC range in jet and missing- $E_T$  triggers, and for fast studies of many effects in the electron/photon trigger.

More complex detector simulation was also used, based on the GEANT simulation package [11]; the detector model was that of ATLAS [12]. This simulated in detail the material in the tracking system, magnet and cryostat as well as the calorimeters<sup>2</sup>, and also the effects of magnetic fields. This model was used for all efficiency studies in the electron/photon trigger, where these effects are most important. We have so far concentrated on the trigger for  $|\eta| \approx 0$ , but studies of the variation in jet rejection with angle are planned for the coming year.

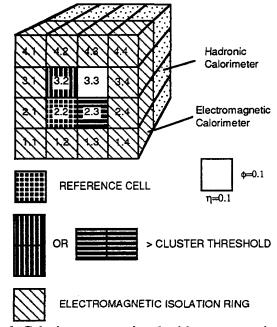

# E.M. cluster algorithms

In all of the algorithms studied here, it is assumed that the calorimeter trigger will work with a reduced detector granularity of  $\Delta\eta \times \Delta\phi \approx 0.1 \times 0.1$  with one depth sampling in each of the ECAL and HCAL. This granularity was chosen on the basis of simulation studies. A threshold is applied to the  $E_T$  in each trigger cell and only the cells above this threshold

<sup>&</sup>lt;sup>2</sup> To economise on computer time, a somewhat simplified calorimeter model was used in the simulation of the jet background to the electron/photon trigger.

contribute to the trigger. This reduces the sensitivity of the trigger to electronic noise and pileup.

The electron/photon trigger is based upon a localised deposit of energy in the ECAL. This cluster should ideally contain fully the energy of an e.m. shower while being small compared with the size of a jet core. Several cluster definitions have been studied (see below) to find the best compromise between sharpness of threshold and background trigger rate. Many of the physics processes sought at the LHC result in isolated leptons or photons, i.e. not associated with jets, while the dominant background to the electron/photon trigger comes from jets containing high- $p_T \pi^0$ s or early-showering hadrons. Thus a further trigger rate reduction can be achieved using isolation requirements.

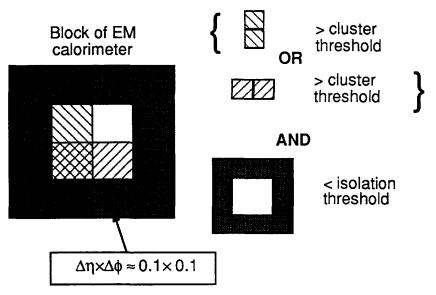

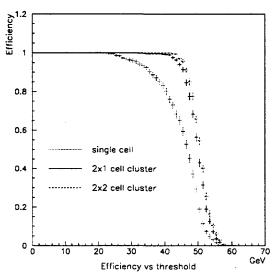

### Electromagnetic cluster definition

The figures of merit for the electromagnetic cluster algorithm are the sharpness of the trigger threshold and the trigger rate for a threshold which is efficient for the desired physics. The sharpness of the threshold is affected by the resolution of the calorimeter and the digitisation system for the level-1 trigger, the degree of containment of e.m. showers within the cluster, and by the pileup and electronic noise in the cluster window. Rate is primarily determined by the area of the cluster window. Three cluster definitions were considered:

- A threshold was applied to the  $E_{\rm T}$  in a single e.m. trigger cell

- The  $E_{\rm T}$  sums of pairs of trigger cells adjacent in azimuth or rapidity were compared with a threshold (Figure 2) this is selected as our standard algorithm

- The summed  $E_T$  of a 2 × 2 trigger cell cluster was compared with a threshold

Figure 2: EM cluster algorithm.

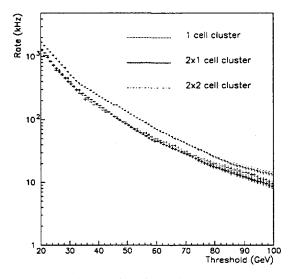

The efficiency as a function of threshold for these three cluster definitions is shown in Figure 3 for 50 GeV electrons at  $|\eta| \approx 0$ . The single-cell algorithm exhibits a significantly softer threshold than the two-cell and four-cell clusters due to shower leakage at the edges of the cell. For this granularity the two-cell cluster threshold is almost as sharp as that of the four-cell cluster. These simulation results have been confirmed by test-beam measurements. The corresponding trigger rates are shown in Figure 4 as a function of threshold. Since the

two-cell algorithm gives a much sharper threshold than the single-cell one, and has a significantly lower rate than the four-cell one, it is taken as our standard algorithm. The question of the optimum trigger algorithm for large rapidity requires further study, but it is worth noting that the single-cell algorithm is particularly badly affected by the small physical size of the trigger cells at large rapidity.

Figure 3: Efficiency for 50 GeV electrons at  $|\eta| \approx 0$  versus cluster threshold for various cluster algorithms.

Figure 4: Trigger rate versus cluster threshold for various cluster algorithms for  $|\eta| \approx 0$ . Here the "threshold" corresponds to 95% efficiency for electrons.

# Isolation requirements

The  $E_{\rm T}$  sums in the ring of e.m. cells surrounding the cluster and in the hadronic window behind it provide extra rejection against jet backgrounds. The effectiveness of the isolation cuts is determined by the area of the isolation window and by the tightness of the cuts which can be applied while retaining high efficiency for isolated e.m. showers. The latter is

limited by electronic noise, pileup and by leakage of the shower into the isolation regions. Electronic noise and pileup are suppressed by applying an  $E_{\rm T}$  threshold to the individual trigger cells, but this also reduces the sensitivity to low- $p_{\rm T}$  jet fragments and hence the effectiveness of the isolation requirement. This trigger cell threshold parameter is crucial to the performance of the isolation veto.

Table 1 shows the mean and rms  $E_T$  values for different-sized regions in the calorimeter due to electronic noise and two levels of pileup. The level of electronic noise used corresponds to 400 MeV energy in a trigger cell, which is approximately the level seen in tests with RD3 [13]. The effect of the cell  $E_T$  threshold in suppressing these noise contributions is shown in Table 2. In most of the studies described here a threshold of 1 GeV per trigger cell was applied.

In addition to inclusive e.m. cluster triggers, it is foreseen to trigger on pairs of electrons and photons at lower thresholds. Here it is reasonable to use less restrictive isolation requirements, since both the rejection power of the isolation cut and the loss in efficiency due to it are squared. We have checked, for example, that high (>95%) isolation-cut efficiency for  $H^0 \rightarrow \gamma\gamma$  can be retained while obtaining an order-of-magnitude reduction in trigger rate, even in the presence of pileup at the highest LHC luminosity.

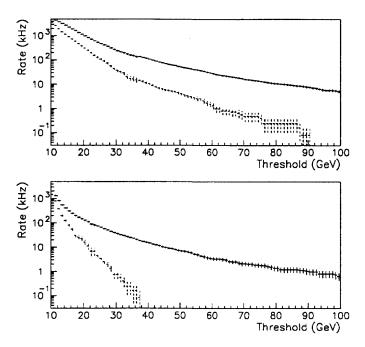

# Estimated trigger rates

We have estimated trigger rates for the most difficult case, where the peak LHC luminosity is taken as  $1.7 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. We aim for an inclusive e.m. cluster threshold of  $\approx 40$  GeV and a trigger on pairs of clusters with thresholds of  $\approx 20$  GeV, as suggested in the ATLAS letter of intent [3]. The e.m. cluster trigger rates obtained are shown in Figure 5 for single-cluster and two-cluster triggers, with and without isolation requirements. It is worth noting that the isolation requirement reduces the background rate by an order of magnitude, while giving excellent efficiency for isolated electrons.

| Noise Sources         | Single em<br>trigger cell | two-cell em<br>cluster | em isolation<br>ring of 12 em<br>trigger cells | hadronic isolation 4 × 4 hadronic trigger cells |

|-----------------------|---------------------------|------------------------|------------------------------------------------|-------------------------------------------------|

| Electronic noise only | $0.32 \pm 0.24$           | $0.51 \pm 0.36$        | 1.12 ± 0.95                                    | $1.23 \pm 0.93$                                 |

| Plus 19 events pileup | $0.36 \pm 0.30$           | $0.60 \pm 0.46$        | $1.49 \pm 1.15$                                | $1.30 \pm 1.01$                                 |

| Plus 38 events pileup | $0.41 \pm 0.35$           | $0.68 \pm 0.54$        | 1.90 ± 1.40                                    | 1.34 ± 1.04                                     |

Table 1: Mean and rms noise levels (transverse energy in GeV) in different-sized regions of the calorimeters. The results are for  $|\eta| \approx 0$  which gives the worst-case contribution from electronic noise.

| Noise sources         | No threshold    | 0.5 GeV         | 1.0 GeV         | 1.5 GeV         |

|-----------------------|-----------------|-----------------|-----------------|-----------------|

| Electronic noise only | 1.68 ± 1.26     | 1.98 ± 0.99     | $0.35 \pm 0.54$ | $0.06 \pm 0.12$ |

| Plus 19 events pileup | $2.10 \pm 1.58$ | $2.32 \pm 1.22$ | $0.56 \pm 0.85$ | $0.15 \pm 0.50$ |

| Plus 38 events pileup | 2.51 ± 1.84     | 2.66 ± 1.37     | $0.76 \pm 1.03$ | $0.24 \pm 0.68$ |

Table 2: Mean and rms noise levels ( $E_T$  GeV) in the e.m. plus hadronic isolation region as a function of the trigger cell threshold.

Figure 5: Trigger rate for  $L = 1.7 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> versus threshold with (lower curves) and without (upper curves) isolation. (a) Single e.m. cluster rates, (b) Two e.m. cluster rates.

## ADC resolution and dynamic range

Together with the trigger cell granularity and occupancy, the resolution and dynamic range of the ADC system affect the input bandwidth to the first-level trigger. The requirement on the resolution is that it should not degrade the sharpness of the trigger thresholds significantly. For a threshold of 20 GeV a calorimeter with a "typical" performance of  $\Delta E/E = 10\%/\sqrt{E} \oplus 1\%$ , would have a resolution of 0.5 GeV. However, many currently-suggested designs include a preshower detector for  $\gamma/\pi^0$  separation, and if the energy from the preshower detector is not included in the trigger this resolution is degraded by about a factor of two. Thus a least count of  $E_T \approx 1$  GeV is well matched to the physics requirements.

A finer resolution is desirable in setting the trigger cell threshold. This is determined by a balance between suppressing noise in the electron/photon isolation region and retaining sensitivity of the isolation test to jet fragments. Since the contributions from electronic noise and pileup are typically in the region of 0.25–0.4 GeV per trigger cell, the ability to tune the cell threshold with a step size of 0.25–0.5 GeV is desirable. There is, however, no need for these least significant bits to be transmitted to the trigger processors.

The dynamic range requirements are determined by the resolution for high- $E_T$  jets and missing  $E_T$ . Comparing with a system with infinite dynamic range, it is found that a maximum count of 255 GeV/cell leads to a slight softening (few percent loss of events) at jet or missing- $E_T$  thresholds of 300 GeV, becoming significant (20% loss) at 400 GeV. A maximum count of 511 GeV/cell was found to be practically indistinguishable from infinite range.

# Trigger cell occupancy

The trigger-cell occupancy has been studied using a detailed GEANT simulation of minimum-bias events. The number of events per beam crossing was conservatively taken to be 38. It was assumed that bunch-crossing identification will not be possible for low-energy signals, and signals from successive bunch crossings were added with weights 0.5, 1.0 and 0.5 respectively, corresponding approximately to the shape of pulses observed in beam tests. Electronic noise was added with a gaussian distribution of 0.35 GeV rms. Under these very conservative assumptions, the occupancy for an  $E_T$  threshold of 1 GeV was found to be 6%.

#### Hardware architectures

### Systolic arrays

The most efficient way to implement synchronous level-1 triggers with fixed algorithms is by using systolic arrays (processing pipelines). Here the hardware is tailored to the algorithm in question, which is broken up into its most basic arithmetic and logical components. These are allocated to compute stations which are connected via data paths and delays so that all arguments arrive in the same clock period. The clock frequency must be chosen so that all basic calculations can finish in one cycle. Data entered at the input nodes at each clock period will thus flow through the structure in a wave-like motion, ending in one destination which provides the final result.

The clock frequency will determine the processing capacity of the systolic array while the number of pipeline steps will define the latency.

### Bit-parallel or bit-serial data representations

In a bit-parallel systolic array, the data are entered, processed and presented in a parallel form. The data will flow uniformly through the computation structure. Successive data will be completely independent since the components are without memory.

With a bit-serial data representation the process is carried one step further. Here the data are inserted into the system one bit at a time. Corresponding bits will then reach the compute stations where they are processed at the same clock cycle, presenting the corresponding result bit after a certain latency. The data flow in a bit-serial processing pipeline is usually not memory-less since consecutive bits will influence each other (e.g. via carry bits). It is not uniform since a reset signal must accompany the first, least-significant bits, clearing the memory functions so that consecutive data will stay independent. Formally this means that the bit-serial processing pipeline no longer satisfies the definition of a systolic array.

Before entering a bit-serial processing pipeline the data must be zero-extended by adding zeros after the most significant bit so that the word length is equal to that of the most precise intermediate result (n bits). Otherwise bits will be lost as the words overflow their allotted time frame. This means that full operations will take at least n clock cycles instead of one for the parallel case. However, the basic bit-serial operations are in most cases faster than corresponding bit-parallel ones, allowing an increased clock rate (e.g. bit-serial addition is not hampered by carry propagation like bit-parallel is). The bit-serial speed gain may, in favourable cases, be a factor  $\approx 2-4$  depending on the word width. Multiple bit-serial calculation blocks (farms) can then be used to obtain the required throughput.

A bit-serial farm with n/2 to n/4 pipelines must be used to achieve the same throughput as for a single bit-parallel processor. This increased circuit complexity is acceptable since the

gate counts of the basic bit-serial processing elements are much smaller than their bit-parallel counterparts. In the case of additions and comparisons, the reduction factor is approximately n. Thus, with algorithms predominantly composed of additions and comparisons, the overall gate count saving of bit-serial architectures is considerable.

The latency of each full operation depends on the clock rate and the type of operation performed. Additions can in both cases be cascaded with a latency of one clock period. This means a considerably shorter latency for bit-serial additions due to higher clock frequency. Bit-serial comparisons will require all bits before delivering the result, i.e. a latency of n clock periods, which is slower than for the bit-parallel case. To these latencies one has to add the overhead of serialisations and parallelisations. Thus the total latency effect depends very much on the algorithm.

### Bit-parallel processor demonstrator

We have constructed and tested a first-prototype bit-parallel calorimeter trigger system. Its aim was to test the efficiency and rejection power of the e.m. cluster-finding algorithm described above, running at full LHC speed and using affordable present-day electronics, with real signals from prototype LHC calorimeters in test beams. The core of this system is a custom-made integrated circuit (ASIC) that implements the algorithm.

# Description of the ASIC

The ASIC implements most of the features of our trigger algorithm. Referring to Figure 6, it carries out the operations needed for one e.m. trigger channel. This means that it must work on the 8-bit energies from 16 trigger channels. It forms separate energy sums with one horizontal and one vertical neighbour to find potential e.m. clusters. It also sums the energy in the outer 12 e.m. cells to examine isolation. A cluster is found if the vertical sum or the horizontal sum is greater than a programmable cluster threshold, and the sum of the outer 12 cells is less than a programmable isolation threshold. This logic is duplicated, so that two pairs of programmable threshold values allow for two different cluster conditions. In addition, the sum of the energies of all 16 input channels is formed.

In this first prototype chip, no attempt is made to handle hadronic trigger information.

To implement the algorithm on an ASIC, the logic was broken down into 15 ns pipelined steps since that was the initially proposed LHC bunch-crossing period. Further details of the ASIC design are given in [14]. The ASIC uses a 0.8 µm CMOS gate array and was produced by Fujitsu. The cluster-finding results are available within 7 clock cycles, and the 12-bit 16-cell total energy sums within 6 clock cycles. The package is a 179-pin ceramic pin grid array. Tests at the full design frequency of 67 MHz have been successful.

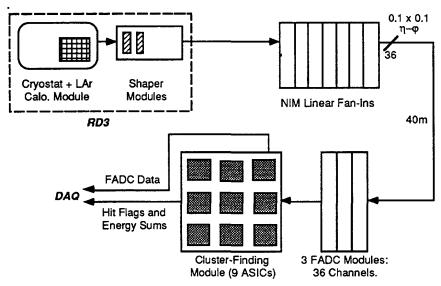

# Description of processor hardware

The prototype trigger processor is designed to trigger on a  $3 \times 3$  area of calorimeter trigger cells. It must first digitise the signals, then pass them to a cluster-finding module (CFM) containing nine ASICs. A clock module is needed to distribute clock signals to the ADCs and the cluster-finding module.

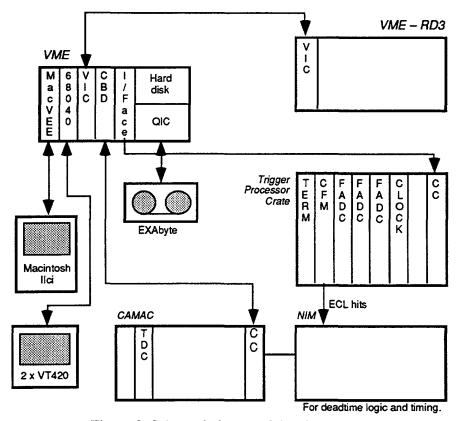

A block diagram of the system is shown in Figure 7, while the layout of the electronics is shown in Figure 8. The configuration shown is the one used for tests in conjunction with RD3, described below. Although VMEbus is used for computer interfacing and control, the trigger modules needed to be larger in size so we modified some crates originally developed for UA1. Modules for these crates are 9U high and 40 cm deep (1U = 1.75 inch). At the

rear the modules plug into two backplanes. The lower one is a printed circuit carrying TTL-compatible signals that uses 96-way connectors and provides a simple control and addressing system. This is organised by a crate controller module which is in turn controlled by a VME interface module. The upper backplane allows wire-wrap connections between modules and uses Teradyne connectors with 320 active pins and 80 grounds. We use this to transmit fast ECL signals. The wire-wrap backplane minimises the amount of cabling on the front panels of the various modules.

Figure 6: Calorimetry associated with one e.m. trigger cell.

Figure 7: Block diagram of the calorimeter and trigger system.

Calorimeter signals are digitised by three flash-ADC modules (FADC), each having 12 channels. The FADC hybrids were of the type used in the ZEUS experiment at HERA, and are 8-bit devices that can run at up to 104 MHz. The modules are simple, with no on-board memory, since we rely on the input memories of the cluster-finding module to monitor and record the FADC data.

Figure 8: Schematic layout of the electronics.

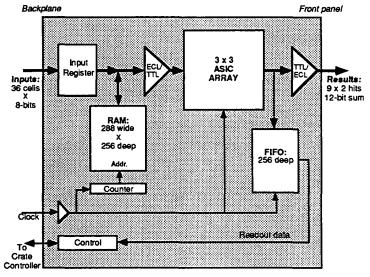

The prototype trigger system is built around a single cluster-finding module, which incorporates nine cluster-finding ASICs. A block diagram of this module is given in Figure 9. The module was developed in order to attack the problems of using the ASICs under realistic conditions at full speed. Therefore, in addition to control facilities, it includes fast memories on the inputs for capturing and reading out the FADC input data and FIFOs on the outputs for reading out the hit results and energy sums from the ASICs. The memories on the inputs can also be loaded with test data that can then be clocked through the logic. The module has been successfully tested at speeds up to 70 MHz.

Figure 9: Block diagram of the cluster-finding module.

Synchronisation of modules within the trigger crate was under the control of a clock module, which distributed correctly phased clock signals to the three 12-channel FADCs and to the cluster-finding module. A system clock frequency of 40 MHz was used for most data collection, corresponding to the anticipated 25 ns bunch-crossing period of the LHC, although data were also taken at 67 MHz.

On each system clock, digital data from the 36 FADCs were transferred in parallel to the cluster-finding module and inserted into a pipeline running at the system clock frequency. Trigger bits resulting from the cluster-finding algorithm emerged seven clock cycles later from the ASICs and were available as prompt front-panel outputs.

Copies of the incoming FADC information, output trigger hits and ASIC energy sums were saved on the cluster-finding module in high-speed memories, allowing up to 256 time slices to be recorded. During data-taking, the system clock was normally free-running, and the memories scrolled continuously at the system clock frequency. At any instant, therefore, the memories contained a history of the preceding 256 FADC samples and the corresponding trigger algorithm analysis results from the nine ASICs. The phase of the event trigger (see below) with respect to the system clock was recorded using a CAMAC time-to-digital converter.

A fast event trigger signal was derived from a coincidence of beam scintillation counters. Gating and monitoring of event signals, and various other control functions, were done using a combination of standard NIM and CAMAC modules, with the CAMAC connected via a VME-based branch driver.

On receipt of the event signal, the clock module counted a further set number of system clocks before generating a stop signal to freeze the cluster-finding module memories. The event signal was also sent to a VME-based data acquisition system, running a variant of the CERN Spider suite [15] adapted for RD27 and running on an MVME167 (68040-based) processor. This selectively read out and recorded the memory contents of the cluster-finding module, and performed on-line analysis on a sample of the data. A copy of the data was transmitted in real time over a VME-VME link to the RD3 data acquisition system, where a duplicate recording was made together with complementary information from the RD3 calorimeter. On completion of data readout, the trigger crate was restored under software control to the initial free-running state.

An Apple Macintosh application developed specially for RD27 was used to set the contents of programmable registers on modules in the trigger crate. Parameters controlled in this way included the ASIC cluster and isolation thresholds, clock frequency and phase, and the number of system clocks preceding the stop signal generation. In addition, the Macintosh was used to run various diagnostic test programs.

# Tests with the RD3 "Accordion" calorimeter

We have now had two periods of running together with the RD3 prototype liquid-argon Accordion calorimeter [16] in an SPS test beam in the North Area at CERN. In order to form trigger cells of the desired granularity, analogue signals from the calorimeter were added both laterally and in two  $9 X_0$  depth samples using LeCroy 428F NIM linear mixers, as shown in Figure 7.

The full trigger processor system was not ready in time for our first tests in November 1992. We therefore chose simply to digitise the data using FADCs and record them for later analysis and off-line "playback" to the trigger processor. We digitised the data from a  $4 \times 4$

region of the calorimeter using a 16-channel F1001 FADC module borrowed from the H1 experiment at HERA. The FADCs were 8-bit and could sample at rates up to 104 MHz. The data acquisition system (VME and CAMAC) was independent of RD3 and simply ran asynchronously. Control and monitoring were done by software running in a Macintosh, and data recording was done onto a hard disk. The analysis of these data is described in Ref. [17].

In April—May 1993 we ran with our prototype trigger processor installed. The configuration is shown in Figures 7 and 8 and was as described above. We recorded a total of 446 data runs, where a "run" means a unique combination of beam particle, beam energy, beam position in the calorimeter, and cluster energy and isolation thresholds in the trigger.

### Analysis of test-beam data from the RD3 calorimeter

At the time of writing this report, data from the two test-beam periods with the RD3 calorimeter prototype are being analysed [17, 13]. As has been described above, the equipment used in the two periods differed greatly. For both periods we recorded the signals from an area of the e.m. calorimeter. These data enable us to study, with two different FADC systems, the expected performance of the trigger algorithm with real calorimeter data, including the effects of electronic noise. In addition, these data are being used for studies [18] of algorithms to identify the bunch-crossing to which a calorimeter signal belongs. In the second period we also have the results of the real-time processing of the calorimeter data performed by the demonstrator trigger system, which, combined with the stored FADC signals, enables us to study thoroughly the performance of the demonstrator hardware.

It should be noted that the analysis, particularly of the data from the second period, is still under way and results shown below should be considered as preliminary. We include here only a brief review of our initial studies.

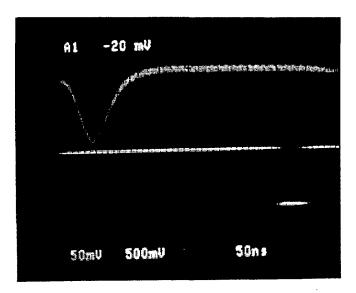

In the beam tests the trigger system had its own free-running clock. Since the clock period was short compared with the pulse width, the signal from a single shower is sampled over several clock cycles. A typical pulse sampled at a frequency of 40 MHz is shown in Figure 10. The significant differences in the pulse heights measured in consecutive digitisations offer the possibility of unambiguously associating a calorimeter pulse with a single bunch crossing, as discussed in more detail below.

Figure 10: Pulse from the Accordion calorimeter sampled at 40 MHz by an FADC.

Pedestals were measured for each channel in each run, using the ADC values measured in digitisings prior to the arrival of the pulse. Typical pedestal values and rms widths of 10 and 0.4 counts respectively, were found for the F1001 system used in the first test-beam period, and 26 and 0.6 counts for the purpose-designed ADC system used in the second period. We have checked that, with both ADC systems, the pedestal values were stable over periods of several days. The observation of low rms values is important because the amount of noise seen in unoccupied channels has a considerable impact on the performance of the trigger, especially in the isolation veto.

Calibration of the ADCs was performed using various methods, using electron beam data of several different energies, test pulse data and cross calibration against the precision ADCs of RD3. A typical calibration constant close to our design aim of 1 GeV per count was obtained.

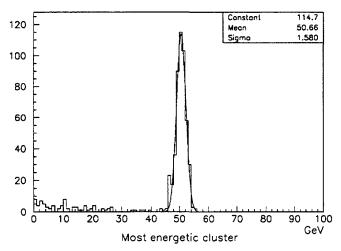

We have used electron beam data of different energies to measure the energy resolution of the trigger. Clusters are formed from the sum of energy in two adjacent cells, and the cluster energy distribution fitted with a gaussian. An example of the distribution observed is shown in Figure 11. The long tail below the peak, due to pion contamination of the beam, is ignored in the fit. The resolutions obtained from the two beam tests are summarised in Table 3, together with the expectation for an intrinsic calorimeter resolution of  $10\%/\sqrt{E} \oplus 1\%$ .

Figure 11: Distribution of energy measured by trigger in cluster window.

The two-cell cluster algorithm is proposed in order to maintain an acceptably sharp trigger threshold in the presence of sharing of energy between cells in the calorimeter. This sharing is illustrated in Figure 12, which shows the energies measured in two cells as the beam was scanned across the boundary between them. As can be seen, the sum of the two energies remains constant across the boundary.

| Beam Energy | 10 GeV   | 20 GeV   | 50 GeV   | 100 GeV  |

|-------------|----------|----------|----------|----------|

| Nov. 1992   | 0.77 GeV | 1.06 GeV | 1.24 GeV | 1.81 GeV |

| April 1993  | 1.54 GeV | 1.65 GeV | 1.53 GeV |          |

| 10%/√E ⊕ 1% | 0.33 GeV | 0.49 GeV | 0.87 GeV | 1.41 GeV |

Table 3: Cluster energy resolution of the trigger ADC system, compared with pure calorimeter resolution. The somewhat larger values for the 1993 data are due to the wider pedestal distribution of the FADCs.

Figure 12: Sharing of energy of shower between trigger cells (data from November 1992).

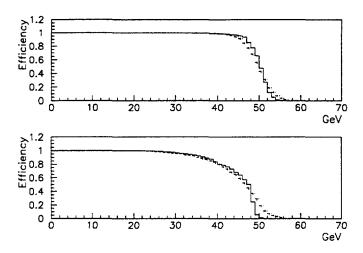

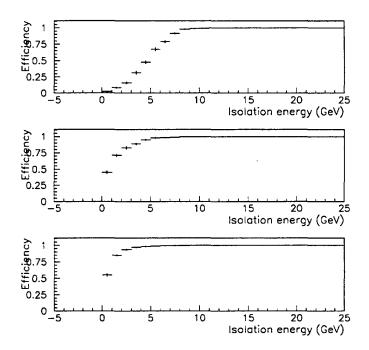

The beam spot in these tests was of about the size of a single calorimeter cell, whereas a trigger cell was the lateral sum of  $4 \times 4$  calorimeter cells. In a real experiment the electrons will be evenly distributed over the trigger acceptance, so in order to study the trigger threshold sharpness one needs a number of data samples taken over a range of points within a trigger cell. Since a trigger cell contains four calorimeter cells in the central core, four at the corners and eight along the edges, a "representative" distribution can be obtained from one data point taken in the core, one in a corner and two along an edge. Such a group of four runs was recorded during the 1993 beam test with a 50 GeV electron beam. The data from the four runs were combined, and the efficiency of the cluster algorithm as a function of threshold computed. This is shown in Figure 13a, with the Monte Carlo expectation for a similar calorimeter geometry shown for comparison. Figure 13b shows the corresponding threshold curves for a trigger based on a single cell, which has much less sharp threshold behaviour. In both cases there is reasonable agreement between the data and the simulation.

The other element of the e.m. cluster algorithm is the isolation requirement. This is primarily designed to reject jets mimicking the electron/photon signature, and thus the data taken during these tests tell us little about its performance. However, the efficiency of the requirement for isolated electrons and its dependence on noise suppression can be studied. Figure 14 shows the efficiency versus threshold on the energy measured in the isolation ring with and without a trigger cell threshold, in events containing a 50 GeV electron cluster. Requiring that the pedestal-subtracted cell energy be greater than twice the pedestal rms is extremely effective in suppressing noise, giving an efficiency of 95% for a requirement that the isolation energy be less than 5 GeV. The corresponding distribution from the simulation is shown for comparison. This was calculated assuming a noise level equivalent to 360 MeV in a  $\Delta\eta \times \Delta\phi \approx 0.1 \times 0.1$  trigger cell area in the calorimeter, which is consistent within 10% with the noise contribution measured in earlier RD3 tests and slightly lower than used in the simulation studies described above.

Figure 13: Efficiency versus threshold (a) for two-cell algorithm, (b) for single-cell algorithm. In each plot the test-beam result is shown as the solid line and the Monte Carlo result is shown as the dashed line.

Figure 14: Measured and simulated efficiency versus isolation threshold: (a) Pedestal-subtracted data with cell threshold = 0, (b) Pedestal-subtracted data with cell threshold = 2  $\sigma$ , (c) Monte Carlo.

A final test of the trigger algorithm is its ability to distinguish electrons from pions. Cluster and isolation thresholds were chosen to achieve a high efficiency (>95%) for electrons with energies of 10, 20, 30 and 50 GeV, and these were applied to data taken with a pion beam. The rejection power of these selections is summarised in Table 4. As expected, the e.m. isolation requirement contributes little to the rejection power against single particles. Nevertheless a significant rejection is obtained from the cluster threshold alone, and

hadronic isolation, not included in the demonstrator system, would increase this significantly.

| Beam energy | Cluster threshold | Cluster plus Isolation |

|-------------|-------------------|------------------------|

| 10 GeV      | 14 ± 4            | 15 ± 4                 |

| 20 GeV      | 42 ± 9            | 45 ± 10                |

| 30 GeV      | $260 \pm 130$     | $340 \pm 190$          |

Table 4: Estimated rejection power of the trigger algorithm against pion beams of different energies. Trigger thresholds chosen to give 95% efficiency for electrons of the same energy. As the pion beam contains a significant muon contamination these numbers can only be taken as indicative.

During the beam test in April–May 1993, using our demonstrator system of nine cluster-finding ASICs, both the FADC data and the ASIC outputs were recorded. Thus it is possible to determine with precision whether the system behaves as expected, and to study in detail any problems which we encounter. In the following, a clock period of 25 ns was used unless stated otherwise.

Each cluster-finding ASIC accepts 16 8-bit energy values every clock cycle. It calculates the sum of all 16 inputs, the sums of the two cluster options (horizontal and vertical) and the 12-cell isolation sum. The 16-cell energy sum, which in a full system would form an input to the jet trigger, is available on the front panel of the trigger module after six clock cycles. The cluster and isolation sums are compared with thresholds, and if either of the two clusters is greater than the cluster threshold and the isolation sum is less than the isolation threshold a trigger hit is generated. There are two combinations of cluster and isolation threshold, so two different trigger bits may be set. The trigger hit results are available on the front panel of the trigger module after seven clock cycles. The demonstrator system includes no calibration, pedestal subtraction or zero suppression facilities, and so the raw ADC counts form the input to the algorithm.

During the design of the ASICs an error was made in the connection of the input signals, so that instead of vertical and horizontal sums being formed for the clusters, vertical and diagonal sums were instead formed. This effect was included in the simulation of the trigger algorithm in the study of the demonstrator performance. While it would have been straightforward to correct this hardware error by making a second prototype cluster board, we did not consider that the expense was justified.

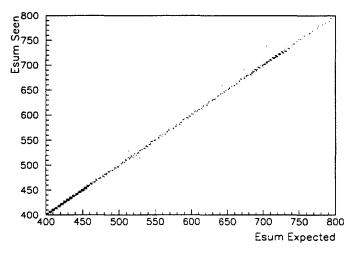

We have compared the energy sums read out from the ASICs with the expectation from the FADC signals. In about 80% of events there is exact agreement between the ASIC results and expectation, with the ASIC result appearing correctly with a latency of six clock cycles. In almost all of the remaining events exact agreement is still found, but with the ASIC result appearing one cycle late in the readout pipeline. We are optimistic that this problem will be resolved for future beam tests by re-adjusting the clock phases used to strobe the readout pipelines. In Figure 15 we show the correlation between the real-time calculation and the prediction after correcting in the analysis for this readout problem.

To avoid confusion due to the readout timing problems described above, only events in which all ASIC energy sums appeared "in-time" were used in the following analysis.

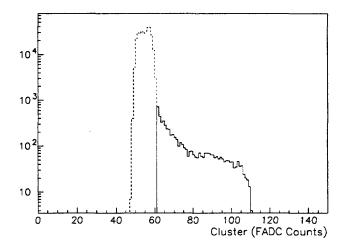

In the e.m. cluster logic there are two requirements – that one of the two (horizontal/vertical) cluster windows lie above the cluster threshold and that the sum from the isolation ring lie below the isolation threshold. In order that these two operations could be tested separately, in many runs the isolation requirement was disabled. The affect of the

cluster threshold is illustrated in Figure 16. In this particular run, one cluster threshold was set at the value of 60 counts, only a few counts above the pedestal sum for two channels. In all the events examined the cluster threshold test worked perfectly.

Figure 15: ASIC output versus expected value after correcting for readout problem described in the text.

Figure 16: Energy in the cluster window for events with (solid line) and without (dashed line) a "hit" from the trigger processor.

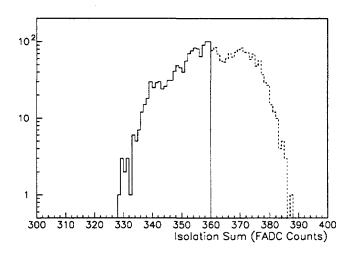

We have also analysed runs in which one of the isolation thresholds was set close to the expected 12-trigger-cell pedestal sum. Choosing events and ASICs for which one of the clusters should be above the cluster threshold, one can compare the isolation sums in events for which the trigger hit was or was not set. The isolation requirement worked as expected as shown in Figure 17.

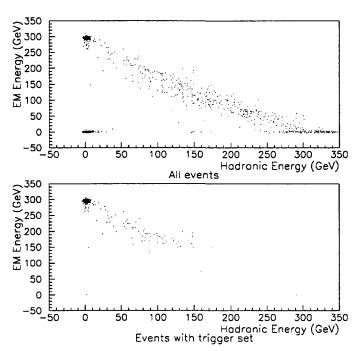

The ability of the trigger processor to separate electrons from pions and muons in real time can be demonstrated by using RD3 data tapes, which included a copy of the RD27 data. Figure 18a plots the energies observed in the RD3 e.m. and hadronic calorimeters against each other. Three distinct types of event can be seen – events with a large deposit of energy in the e.m. calorimeter and none in the hadronic calorimeter (electrons), events with little or

no energy in either calorimeter (muons), and events in which energy is shared between the two calorimeters (pions). Figure 18b shows the same distribution for events in which the RD27 e.m. cluster trigger was fired. The trigger threshold in this run, 200 counts, corresponds to approximately 150 GeV (after pedestal subtraction).

Figure 17: Energy in isolation window for events with (solid line) and without (dashed line) a "hit" from the trigger processor.

The pulses from many proposed LHC calorimeters are longer than the bunch-crossing period, as shown in Figure 10. The unambiguous association of such signals to a unique bunch crossing simplifies the trigger, since otherwise a large pulse would cause the trigger to be fired for a number of consecutive bunch crossings. It may also reduce the data rate to the trigger processors, since the signal need only be transmitted for one bunch crossing. Investigations are therefore being made into bunch-crossing identification using digital signal processing algorithms. These algorithms have been simulated in software and tested with the data recorded in the November 1992 and April 1993 beam tests, with both 25 ns and 15 ns sampling periods. The studies using the November 1992 data are described in detail in Ref. [18].

Algorithms studied include a peak-finding algorithm, a zero-crossing identifier, a constant-fraction discriminator and a deconvolution filter. Very encouraging results have been obtained, even for relatively small deposited energies. For example, using data from the November 1992 tests with a 25 ns bunch-crossing period, a simple peak-finding algorithm was able to correctly identify the bunch crossing in > 99 % of cases for energies as low as 4 GeV in a single trigger cell.

In addition to the off-line studies described above, a single-channel bunch-crossing identification module is currently under construction. This will be able to apply any of the above algorithms to calorimeter data in real-time. This demonstrator prototype makes extensive use of static RAM look-up tables.

Although analogue signal processing has not yet been investigated in RD27, it is still being considered as an alternative method of bunch-crossing identification.

Finally, to demonstrate real-time operation of the processor, in Figure 19 we show an oscilloscope photograph of calorimeter pulses at the input to the FADC system and the trigger processor output which follows after the expected latency, including cable delays.

Figure 18: Energy in ECAL versus HCAL (a) for all events and (b) for events with e.m. cluster "hit".

Figure 19: Oscilloscope photograph showing calorimeter pulse at input to trigger FADC (upper trace) and the output of the trigger processor (lower trace).

# Tests with the RD33 TGT calorimeter

A prototype TGT calorimeter [19] was installed in an SPS test beam in late June 1993. In parallel with the RD33 calorimeter performance measurements, a test of its features for triggering was performed by RD27.

The TGT prototype contains electronics in which readout cells are summed to form trigger towers of area  $6 \times 5$  cm<sup>2</sup>. The trigger signals from the calorimeter are delivered to the external electronics separately for the five layers in depth, requiring further analogue

summation before digitisation. The total number of trigger towers is  $4 \times 4$ , which is the minimum number needed to feed one of the cluster-finding ASICs including the isolation window.

We built VME boards which receive the five analogue signals from a TGT tower. Summing and shaping is performed before the signal is digitised by an 8-bit FADC sampling the analogue-sum signal at 40 MHz produced by a free-running clock. A fast memory stores the FADC digitisations in a 256-word circular buffer until the content is frozen by an external STOP signal. The memory serves as a debugging aid for the apparatus by showing the digitisation history back to triggering pulse and beyond. The complete FADC system consists of a VME crate housing eight FADC modules (two channels per module). Interface boards to the special backplane of the trigger processor demonstrator, on which signal distribution to the cluster-finding modules is performed, were also built for these tests.

A Macintosh software package was used for data acquisition in the RD33/RD27 joint test. All components of the trigger system were tested in the laboratory prior to installation at the test beam. Analogue trigger signals from the TGT were simulated with a pulse generator. Digitisation and transmission to the cluster finder showed satisfactory results.

The full trigger system was installed in the North Area at CERN for the TGT test-beam period at the end of June 1993. The analysis of the data which were collected is in progress.

### Bit-parallel processor design study

We briefly describe here a preliminary, but fairly complete, design for a bit-parallel first-level calorimeter trigger processor; more detail is given in [20]. This design will, of course, evolve as our studies and prototype work progress and also as new technology becomes available. However, it should be stressed that the present design looks feasible and is based on technology available now or in the near future.

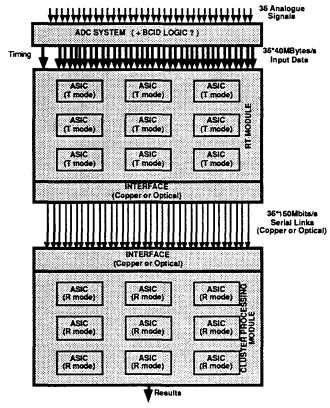

The processor consists of e.m. cluster logic, jet logic and missing- $E_T$  logic. The e.m. cluster logic is the most demanding part of the system, and will consist of four crates of electronics. The remaining electronics will be housed in two further crates. The processor will use four different ASIC designs and seven different circuit board designs. Figure 20 shows a block diagram of the trigger processor system. The total latency of this processor will be under 500 ns.

#### Receiver module

A receiver module will take in digitised, serialised, zero-suppressed data at 160 Mbits/s from the ADC system. If the connections are optical, the receiver module must convert them to electrical signals. There is one receiver module per cluster processor module, so there would be 64 in total (see below).

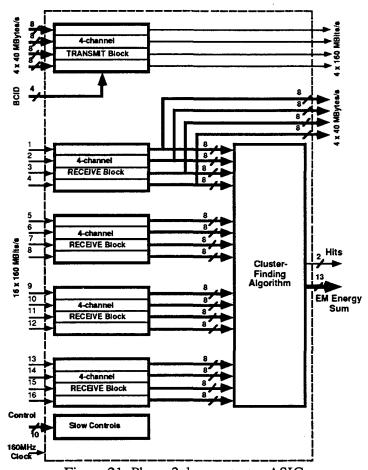

# E.M. cluster-finding ASIC

The cluster-finding ASIC will do the required processing for 16 e.m. trigger channels, including hadronic information. This means that it must examine the transverse energy in a total of 98 channels ( $7 \times 7$  trigger cells for each of the e.m. and hadronic calorimeters). To reduce the number of input/output (I/O) pins and the bandwidth, the information for each channel will be sent as a single, zero-suppressed 160 Mbits/s serial stream. Thus serial-to-parallel conversion and tag-matching are required. With derandomizing buffers at each end of the asynchronous link four words deep, the fraction of data which are lost can be reduced

to a negligible level<sup>3</sup> for a zero-suppression threshold of  $E_{\rm T}=1$  GeV even at the highest LHC luminosity; the fact that this threshold is programmable gives additional safety.

The ASIC will produce results for eight sets of threshold values (cluster threshold, isolation threshold) as hits and as a "region-of-interest" array for the level-2 trigger. A 160 MHz clock is needed for the serial input and output links, but the internal logic will probably run at 40 MHz. We anticipate using a 0.5  $\mu$ m CMOS gate array with up to 820k gates. A total of 256 ASICs would be needed to process the entire calorimeter.

The trigger latency could be reduced by either running the cluster-finding ASICs at 80 MHz (the first prototype already runs at more than 67 MHz) or by reducing the number of pipeline stages and so doing more processing per stage.

Figure 20: First-level calorimeter trigger system.

# E.m. cluster processor module

The cluster processor module will contain four cluster-finding ASICs and one adder ASIC to combine the  $E_T$  sums from the ASICs, as well as look-up tables to convert  $E_T$  to its components,  $E_x$  and  $E_y$ . A total of 64 such modules would be required.

#### Results module

The results module will receive  $E_x$  or  $E_y$  values from 16 cluster processor modules and carry out addition using adder ASICs. The twos-complement results of this adding process will be sent to the missing- $E_T$  module. A total of eight such modules would be required.

<sup>&</sup>lt;sup>3</sup> The fraction of data which are lost under the very pessimistic assumptions discussed in the simulation section is 0.2%.

### Missing-E<sub>T</sub> module

The function of the missing- $E_T$  module is to receive the partial  $E_x$  and  $E_y$  sums from the eight results modules and carry out further addition using the adder ASICs before finally testing the missing transverse energy  $E_T = (E_x^2 + E_y^2)^{1/2}$  against four thresholds using look-up tables. Only one such module would be required.

### Jet processor module

The jet algorithm will be performed using the 13-bit  $E_T$  sums calculated over  $4 \times 4$  trigger-channel areas of the calorimeter that are available from the cluster processor modules. These areas will be further summed into  $2 \times 2$  sliding windows, each of which will be compared to eight threshold values. A jet ASIC will be designed to perform this algorithm using data from  $4 \times 4$  of the 13-bit sum areas, i.e. a total of nine jet windows. Approximately 30 of these jet ASICs are needed in the system, mounted on about eight jet-processor modules.

#### Cluster-counting module

Simply counting e.m. or jet hits would result in an overestimate due to double-counting of contiguous hits. Therefore a "veto" procedure to look for "corners" will be used. The cluster-counting, or "declustering", electronics for jets and e.m. clusters will be identical. The module will examine a 256-pixel array of hits from either the e.m. cluster-processor modules<sup>4</sup> or the jet-processor modules and count non-vetoed pixels. It will then compare the multiplicity with eight multiplicity-threshold values. Part of the vetoing and counting logic will be implemented on a veto ASIC, and to complete the counting an adder ASIC will be used. Each veto ASIC will process 16 pixels, so each module will have 16 ASICs. A total of eight e.m. and eight jet cluster-counting modules would be required.

### Readout and crate controller module

Each crate will be organised by a readout and crate controller module to allow communication with the trigger modules and to provide an interface to the level-2 trigger. A built-in CPU might be used to control and format the data and to provide test facilities.

#### System crates

The four e.m. cluster-processor crates will each process 1024 e.m. and 1024 hadronic trigger cells. In each crate there will be 16 cluster processor modules and 16 receiver modules. The receiver modules and the cluster processor modules will be plugged back-to-back via the backplane connectors<sup>5</sup>. There will also be two results modules.

The jet processor crate will include eight jet-processor modules and the eight cluster-counting modules needed for jets.

The e.m. cluster-counting crate will include eight cluster-counting modules and the missing- $E_{\rm T}$  module.

<sup>&</sup>lt;sup>4</sup> For the e.m. cluster counting, the declustering logic acts on a granularity of 4 × 4 trigger cells, corresponding to the OR of hits from an ASIC for a given threshold. Simulation has shown that this gives satisfactory performance, at least for high-luminosity physics.

<sup>&</sup>lt;sup>5</sup> Such back-to-back connections are possible using commercial technology such as Molex Omnigrid 2.5 connectors.

The crates will be 450 mm high (18SU) with 20 slots.

# Proposal for future work

We have identified several key areas of the bit-parallel processor that require further study before a full level-1 system could be designed and constructed. We therefore propose building a phase-2 bit-parallel demonstrator system. This would be based on a new, high-speed ASIC together with associated support modules. The aims are:

- To demonstrate our data sparsification scheme, using zero-suppression and asynchronous serial data transfer to reduce the number of interconnections required.

- To include a custom digital signal processor in order to implement and test bunchcrossing identification using various algorithms.

- To address the question of whether the high-speed links between the front-end digitisation electronics and the level-1 processors should be electrical or optical.

Figure 21: Phase-2 demonstrator ASIC.

The new ASIC would be designed explicitly as a test bench. We feel that our e.m. clustering algorithm has been adequately demonstrated by the existing prototype system, and we believe that putting more channels onto one ASIC in order to reduce the overall size of the system and its interconnections is a relatively straightforward task. Thus, in order to minimise the cost of the new ASIC we will stay with one channel per chip, and also put onto the same type of chip other functions that we want to test but which would not be located there in the final design. This is illustrated in Figure 21.

The critical functions that we would like to test are:

- "Transmit" block: receive and buffer (FIFO) 8-bit wide data at 40 Mbytes/s, perform zero suppression, tag, do parallel-to-serial conversion, and transmit serial data at 160 Mbits/s. This section would actually be part of the ADC system in an LHC experiment.

- "Receive" block: receive data at 160 Mbits/s, perform serial-to-parallel conversion, buffer (FIFO) and tag-match.

- "Algorithm" block: receive data as above for 16 e.m. trigger channels and perform cluster-processing for a 4 × 4 area as in the first prototype system.

- If gate counts permit, we might also include bunch-crossing identification logic, at least for one channel.

This ASIC requires about 63 inputs and 51 outputs. By using bi-directional pins and sharing pins (the transmit block and receive block would not be used at the same time on the same ASIC) the I/O pin count could be reduced by 36. We are considering implementing the ASIC on a 34k, 0.5 µm CMOS gate array.

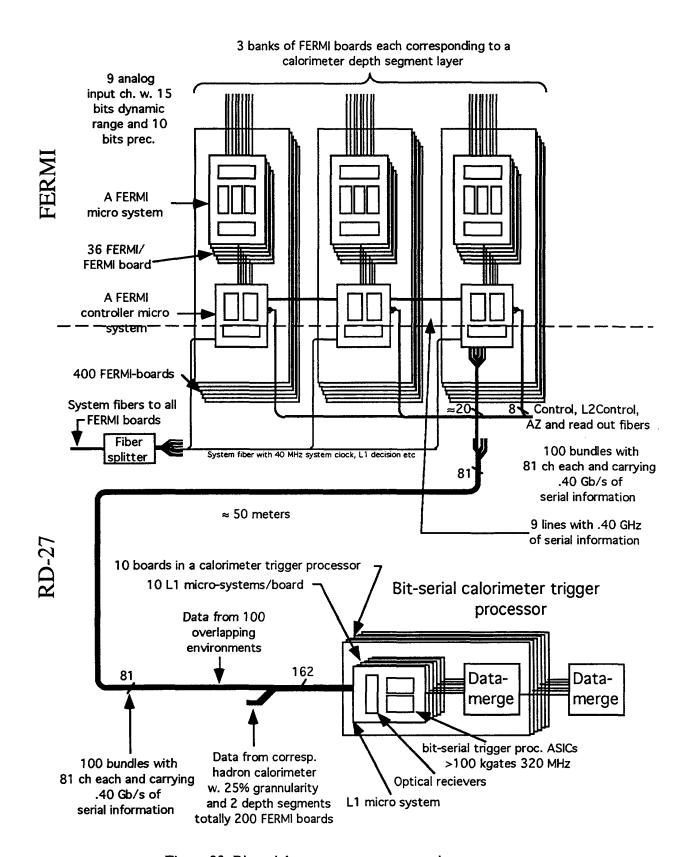

Figure 22. Phase-2 demonstrator trigger processor system.

The demonstrator system would be similar to the existing one, which fully processes a  $3 \times 3$  area of the calorimeter using nine ASICs. Figure 22 shows a block diagram of the new system. The receiver/transmitter (RT) module will have nine of the ASICs in transmit (T) mode, which will only use the transmit block of the ASICs. It will receive 8-bit parallel data from the 36 FADC channels and will transmit the processed data via a transmit interface module on 36 serial links at 160 Mbits/s/link; these links could be optical or electrical. The cluster processor module will receive the serial data via a receive interface

module and will have nine ASICs in receive (R) mode, which means that they will use the receive block and the cluster algorithm block to carry out the cluster-finding algorithm. The design of the interface modules will depend on whether the links are optical or electrical. Look-up tables may be included between the FADC system and the RT module to subtract the pedestals before zero suppression.

# Bit-serial processor design study

Advantages and disadvantages of a bit-serial calorimeter trigger processor

The calorimeter trigger algorithms are such that most parts benefit from the use of a bit-serial data representation, both with respect to the gate count and the overall latency. However, some operations (e.g. table look-ups) are, for practical reasons, best performed in a bit-parallel mode. A hybrid solution with serial-to-parallel and parallel-to-serial conversions is therefore necessary. Since these conversions introduce latency, the system should be partitioned to minimise the number of transitions between representations.

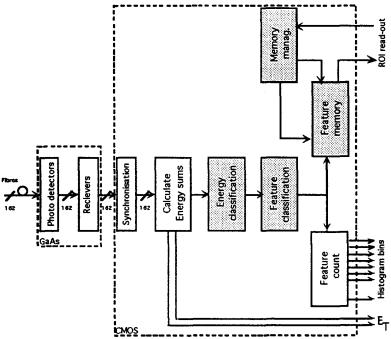

Most of the electron identification processing occurs in the initial calculations of "environment sums" – two 2-cell e.m. cluster sums, one 12-cell e.m. sum and one 16-cell hadronic sum for each trigger cell. The results of these operations are placed in categories by comparisons to fixed limits. The compound category codes are then converted into a trigger cell classification, e.g. representing high-energy electrons with good isolation, high-energy electrons with medium isolation, etc. The final operation is to count the global number of different classification instances. These numbers are then fed to the central trigger processor for evaluation. Of these operations only the classification has to be done in bit-parallel mode, using table look-up.

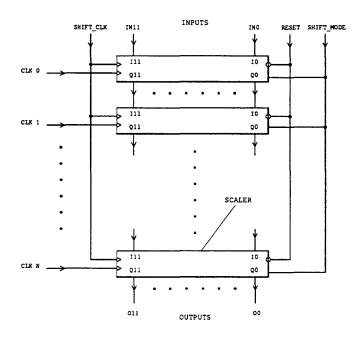

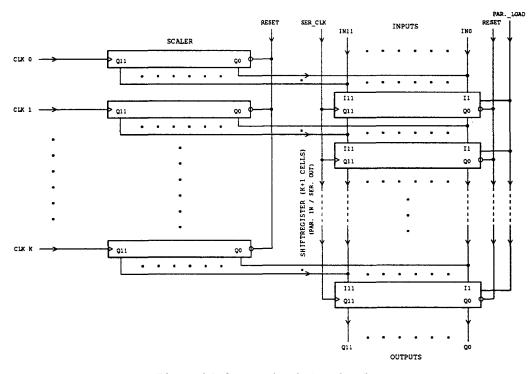

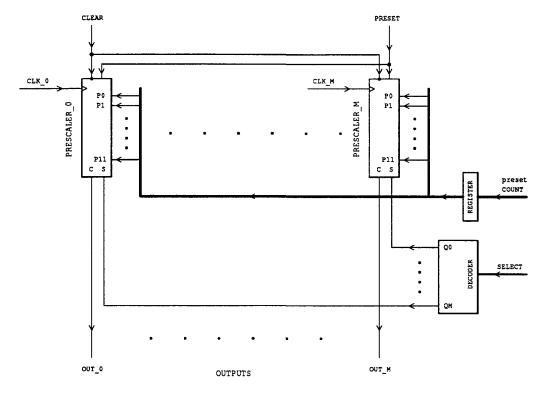

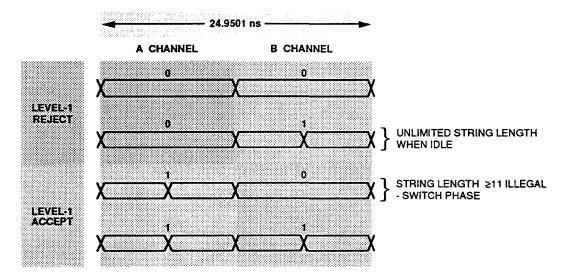

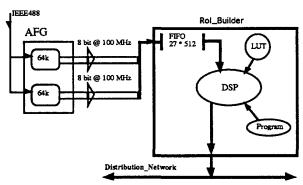

The missing- $E_T$  calculation is also made up mostly of additions. The logic can be arranged so that the bulk of this processing is in initial additions of transverse energies from trigger cells along the axial ( $\eta$ ) direction, well suited for bit-serial operations. These partial sums can then be converted to bit-parallel representation for multiplication with sin $\varphi$  and cos $\varphi$  and for the final vectorial addition. The jet algorithm can similarly be factorized into a main part suitable for bit-serial operations and a bit-parallel part for the remainder.