# The Kiel Esterel Processor: A Multi-Threaded Reactive Processor

## Dissertation

zur Erlangung des akademischen Grades Doktor der Ingenieurwissenschaften (Dr. -Ing.)

der Technischen Fakultät der Christian-Albrechts-Universität zu Kiel

## Xin Li

Kiel 2007

1. Gutachter

Reinhard von Hanxleden

2. Gutachter

Michael Mendler

Datum der mündlichen Prüfung

23. Juli 2007

## Acknowledgements

This thesis would not have been possible without the support of many people. My deepest gratitude is to my supervisor, Professor Reinhard von Hanxleden, for his precious suggestions, friendly advice, and giving me the freedom to pursue a research topic. Most of all, for his patience with my mistakes and extreme generosity with his time. His scientific vision, high standards, detailed comments and discussions, and solid insight into embedded system design have given me guidance to follow throughout my research efforts. I am also grateful to him for having provided me chances to attend many conferences, which have expanded my horizon and inspired me to conduct this research work.

Furthermore, my special thanks go to Prof. Michael Mendler at the Universität Bamberg, Prof. Stephen A. Edwards at Columbia University, Dr. Stavros Tripakis and Dr. Claudio Pinello at Cadence Berkeley Labs, and Prof. Alberto Sangiovanni-Vincentelli at the University of California Berkeley for their inspiring talks, suggestions and advice which were very helpful for my work.

Claus Traulsen and Malte Tiedje read a draft version of this thesis and gave me lots of helpful comments, I really appreciate their help. I thank also Marian Andreas Boldt for his discussions and collaboration. In addition to this, I am grateful for all the discussions with Steffen Prochnow, Jan Lukoschus, and Sascha Gädtke. I further thank my colleagues Gesa Walsdorf, Isabella Cembrowski, Maren Lutz, Hauke Fuhrmann, and Tim Grebien for their kind help during my study in the Real-time and Embedded Systems group.

I acknowledge the DAAD and DFG for giving me the financial support for this work.

Last, but not least, I would never have finished this work without the moral support and encouragement of my parents (Zhenhua Li and Sujiao Wu), my wife (Di Zang) and my daughter (Luopian Li) to whom I dedicated this dissertation.

## Abstract

Many embedded systems belong to the class of reactive systems, which continuously react to inputs from the environment by generating corresponding outputs. The programming of reactive systems typically requires the use of non-standard control flow constructs, such as concurrency or exception handling. Most programming languages do not support these constructs at all, or their use induces non-deterministic program behavior. To address these difficulties, the synchronous language Esterel has been developed to express reactive control flow patterns in a concise manner, with a clear semantics that imposes deterministic program behavior under all circumstances.

There are different options to synthesize an Esterel program into a concrete system, e. g., software, hardware, and HW/SW co-design implementations. However, these classical synthesis approaches suffer from the limitations of traditional processors, with their instruction set architectures geared towards the sequential von-Neumann execution model, or they are very inflexible if HW synthesis is involved.

Recently, another alternative for synthesizing Esterel has emerged, the *reactive processing* approach. Here the Esterel program is running on a processor that has been developed specifically for reactive systems. However, the main challenge when designing a reactive architecture is the handling of control.

This thesis presents the Kiel Esterel Processor (KEP). In the KEP, the multi-threaded reactive architecture is responsible for managing the control flow of all threads. The KEP Instruction Set Architecture is *complete* in that it allows a direct mapping of all Esterel statements onto KEP assembler. It supports Esterel's concurrency operator || in a very precise, direct and efficient way. It also supports full Esterel preemptions, i. e., the delayed and immediate strong/weak abortion and suspension. All other Esterel kernel statements, e. g., the Esterel exception, delay, and signal emission, etc., are also implemented directly and semantically accurate by the KEP.

As the experimental comparison with a 32-bit commercial RISC processor indicates, the KEP has advantages in terms of memory use, execution speed, and energy consumption. Another advantage is the predictability of its timing behavior at the program level.

# Contents

| $\mathbf{C}$ | Contents |        |                                     | V    |

|--------------|----------|--------|-------------------------------------|------|

| Li           | st of    | Figur  | es                                  | ix   |

| Li           | st of    | Table  | ${f s}$                             | xiii |

| 1            | Intr     | oduct  | ion and Motivation                  | 1    |

|              | 1.1      | Introd | luction                             | . 1  |

|              | 1.2      | Motiv  | ation                               | . 2  |

|              | 1.3      | Resea  | rch Contribution                    | . 3  |

|              | 1.4      | Thesis | s Organization                      | . 5  |

| <b>2</b>     | Bac      | kgrou  | nd and Related Work                 | 7    |

|              | 2.1      | Imple  | mentation Technologies              | . 7  |

|              | 2.2      | Comp   | ilation Approaches                  | . 9  |

|              | 2.3      | Handl  | ing Esterel via Reactive Processors | . 12 |

| 3            | The      | KEP    | Instruction Set Architecture        | 17   |

|              | 3.1      | The E  | Esterel Language                    | . 18 |

|              |          | 3.1.1  | Esterel Statements                  | . 20 |

|              |          | 3.1.2  | An Example Program                  | . 28 |

|              | 3.2      | Design | n of the Esterel-type Instructions  | . 30 |

|              |          | 3.2.1  | Handling Concurrency                | . 30 |

|              |          | 3.2.2  | Handling Preemption                 | . 32 |

|              |          | 3.2.3  | Handling Exceptions                 | . 35 |

|              |          | 3 2 4  | Handling Signal and Schizophrenia   | 35   |

vi CONTENTS

|   |     | 3.2.5 Handling Delays                                             | 36  |

|---|-----|-------------------------------------------------------------------|-----|

|   |     | 3.2.6 Summary of Esterel-type Instructions                        | 37  |

|   | 3.3 | Further Instructions                                              | 39  |

|   | 3.4 | From Esterel to KEP Assembler                                     | 42  |

|   |     | 3.4.1 Code Generation for the KEP – The Compiler's Perspective $$ | 42  |

|   |     | 3.4.2 EXAMPLE: Code Translation                                   | 44  |

|   | 3.5 | Encoding KEP Instructions                                         | 47  |

|   | 3.6 | Summary                                                           | 51  |

| 4 | The | e KEP Architecture                                                | 53  |

|   | 4.1 | The KEP Architecture Overview                                     | 53  |

|   | 4.2 | The Reactive Core                                                 | 55  |

|   |     | 4.2.1 The Thread Block                                            | 56  |

|   |     | 4.2.2 The Reactive Block                                          | 60  |

|   |     | 4.2.3 Decoder & Controller                                        | 90  |

|   | 4.3 | The Interface Block                                               | 91  |

|   | 4.4 | The Data Handling Block                                           | 96  |

|   | 4.5 | The Tick Manager and Energy Saving                                | 98  |

|   | 4.6 | Putting It All Altogether                                         | 101 |

|   | 4.7 | Summary                                                           | 104 |

| 5 | Exp | perimental Results                                                | 107 |

|   | 5.1 | The KEP Evaluation Platform                                       | 107 |

|   |     | 5.1.1 Compilation                                                 | 108 |

|   |     | 5.1.2 Implementation                                              | 108 |

|   |     | 5.1.3 Validation                                                  | 110 |

|   | 5.2 | Comparison with Other Execution Platforms                         | 110 |

|   | 5.3 | Evaluation Results                                                | 113 |

|   | 5.4 | Summary                                                           | 121 |

| 6 | Cor | nclusion and Outlook                                              | 123 |

|   | 6.1 | Conclusion                                                        | 123 |

|   | 6.2 | Recommendations for Further Research                              | 125 |

|          | ••  |

|----------|-----|

| CONTENTS | V11 |

| $\mathbf{A}$ | KE    | P Inst  | ruction Set                                   | 129 |

|--------------|-------|---------|-----------------------------------------------|-----|

|              | A.1   | Estere  | el-type Instructions                          | 129 |

|              |       | A.1.1   | Preemption                                    | 129 |

|              |       | A.1.2   | Exception                                     | 132 |

|              |       | A.1.3   | Concurrency                                   | 132 |

|              |       | A.1.4   | Delay                                         | 134 |

|              |       | A.1.5   | Signal Emission and Testing                   | 136 |

|              |       | A.1.6   | Others                                        | 140 |

|              | A.2   | Classic | cal Instructions                              | 142 |

|              |       | A.2.1   | Program and Machine Control                   | 142 |

|              |       | A.2.2   | Boolean Variable Manipulation                 | 146 |

|              |       | A.2.3   | Data Transfer                                 | 148 |

|              |       | A.2.4   | Arithmetic Operations                         | 149 |

|              |       | A.2.5   | Logical Operations                            | 153 |

| В            | An    | Introd  | luction to the KEP Evaluation Platform        | 157 |

|              | B.1   | Functi  | ion Description of the KEP Assembler Compiler | 157 |

|              |       | B.1.1   | Options of the KEP Assembler Compiler         | 157 |

|              |       | B.1.2   | The KEP Configuration File                    |     |

|              |       | B.1.3   | The Further Configuration                     |     |

|              | B.2   | Functi  | ion Description of the TestDriver             | 161 |

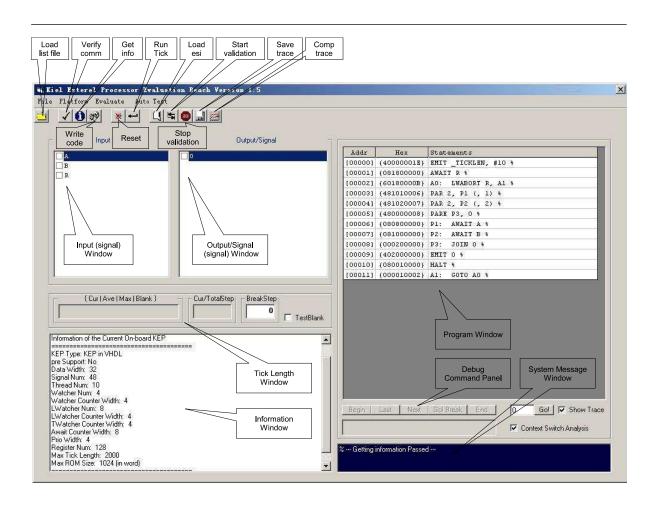

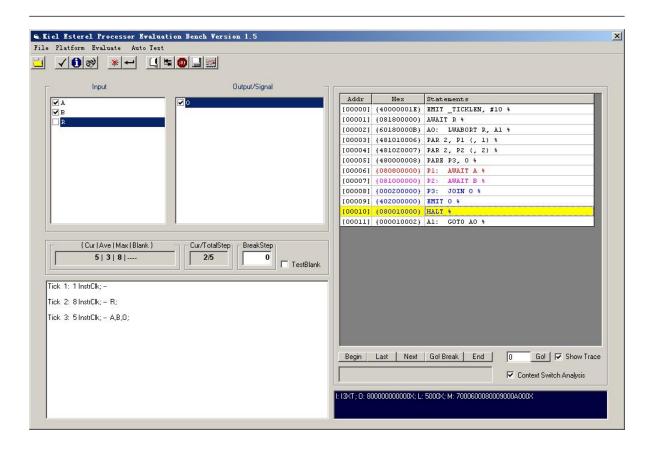

|              | В.3   |         | ion Description of the KEP Evaluation Program |     |

|              |       | B.3.1   | Starting an Evaluation                        |     |

|              |       | B.3.2   | Debugging a Program                           |     |

|              |       | B.3.3   | Validating a Program                          |     |

| Bi           | bliog | graphy  |                                               | 173 |

viii CONTENTS

# List of Figures

| 2.1  | The schizophrenia problem (a) and the typical solution (b)                                                                                                                                                                                     | 11 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

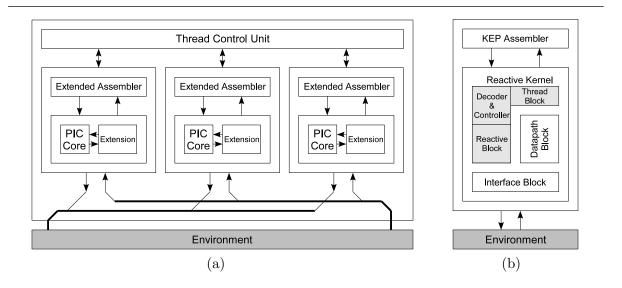

| 2.2  | The architecture overview of multi-processing (a) and multi-threaded (b).                                                                                                                                                                      | 15 |

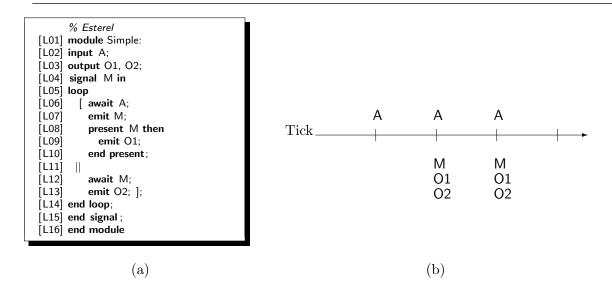

| 3.1  | Simple: a module illustrating the structure of the Esterel program (a), and a possible execution trace (b)                                                                                                                                     | 18 |

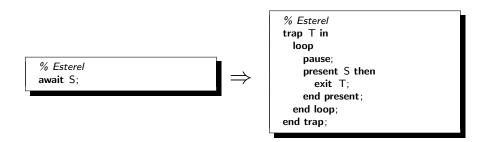

| 3.2  | The equivalent expression of the $await$ statement by kernel statements                                                                                                                                                                        | 23 |

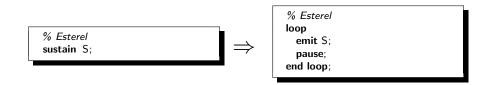

| 3.3  | The equivalent expression of the $sustain$ statement by kernel statements                                                                                                                                                                      | 24 |

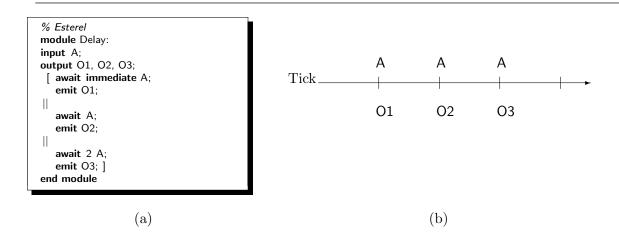

| 3.4  | Delay: an Esterel module illustrating the difference of Esterel delay expressions (a), and a possible execution trace (b)                                                                                                                      | 24 |

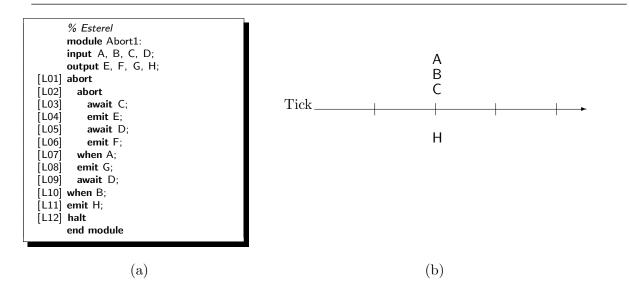

| 3.5  | Abort1: an Esterel module illustrating the strong abort nest (a), and a possible execution trace (b)                                                                                                                                           | 26 |

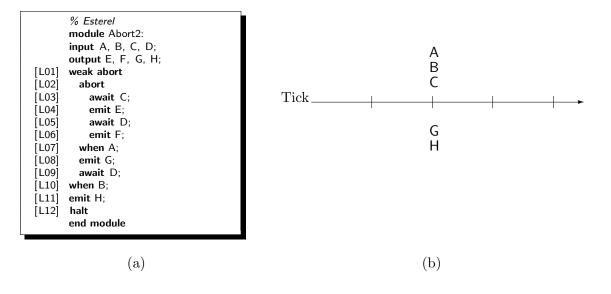

| 3.6  | Abort2: an Esterel module illustrating the mixed abort/weak abort nest (a), and a possible execution trace (b). $\dots$                                                                                                                        | 26 |

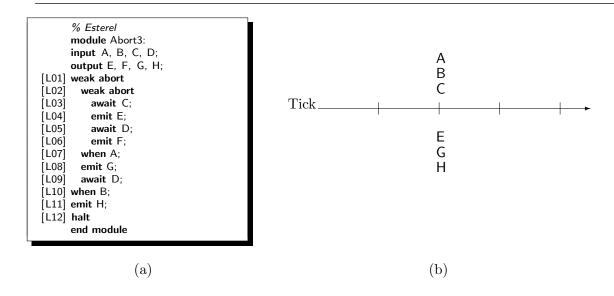

| 3.7  | Abort3: an Esterel module illustrating the weak abort nest (a), and a possible execution trace (b)                                                                                                                                             | 27 |

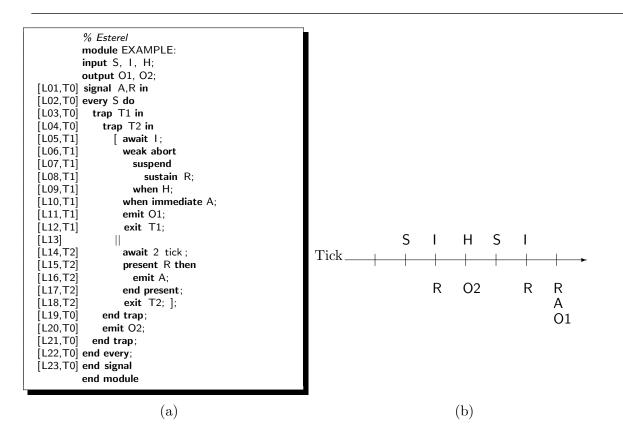

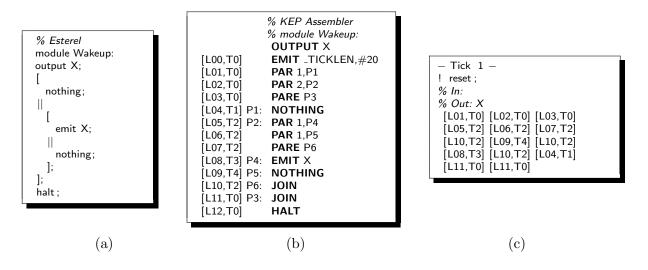

| 3.8  | EXAMPLE: an Esterel module illustrating Esterel parallel, preemption, and exception statements (a), and a possible execution trace (b). The KEP assembler includes labels (in brackets) that list the line number ("Lxx") and thread id ("Tx") | 28 |

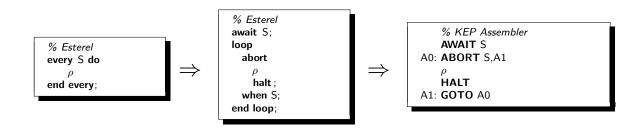

| 3.9  | Translation rules of the every statement                                                                                                                                                                                                       | 30 |

| 3.10 | The KEP instructions for handling concurrency                                                                                                                                                                                                  | 31 |

| 3.11 | The KEP instruction for handling preemption                                                                                                                                                                                                    | 33 |

| 3.12 | Translating the Esterel RUNNER module (a) to the KEP assembler program (b) with refined instructions employed                                                                                                                                  | 34 |

| 3.13 | KEP instruction for handling exception                                                                                                                                                                                                         | 35 |

| 3.14 | REINC: Translation of the Esterel signal declaration (a) into to the KEP SIGNAL instruction (b)                                                                                                                                                | 36 |

x LIST OF FIGURES

| 3.15 | The KEP instruction for handling multiple signal awaiting                                                                                                              | 37 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.16 | Translating the Esterel variable declaration to the KEP instructions. $$ . $$ .                                                                                        | 39 |

| 3.17 | Translating the Esterel interface declaration to the KEP instructions                                                                                                  | 41 |

| 3.18 | Translating the Esterel COUNT module (a) to the KEP assembler program (b)                                                                                              | 42 |

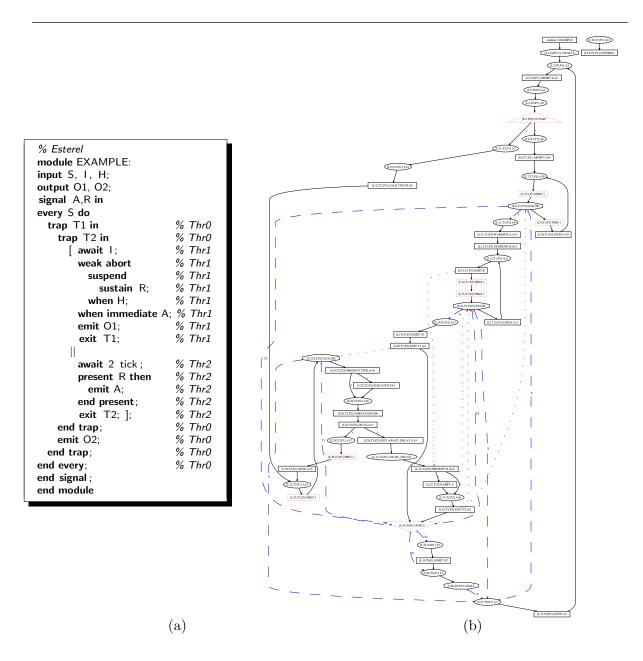

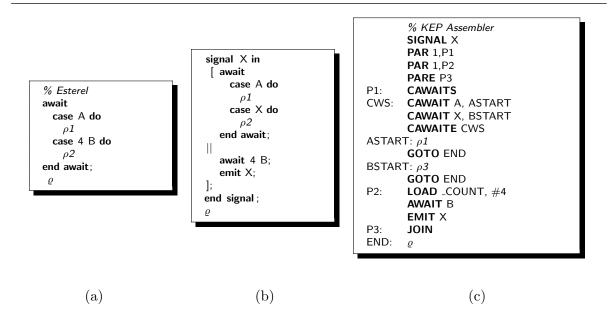

| 3.19 | The EXAMPLE: (a) Esterel; (b) Concurrent KEP Assembler Graph (CKAG), where rectangles are transient nodes, octagons are delay nodes, and triangles are fork/join nodes | 45 |

| 3.20 | Translating the Esterel EXAMPLE module (a) to the KEP assembler program (b) by KEP compiler, or manually (c)                                                           | 46 |

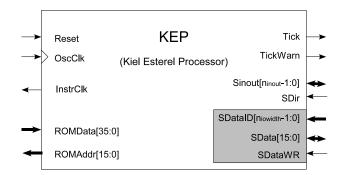

| 4.1  | The interface connections of the KEP                                                                                                                                   | 54 |

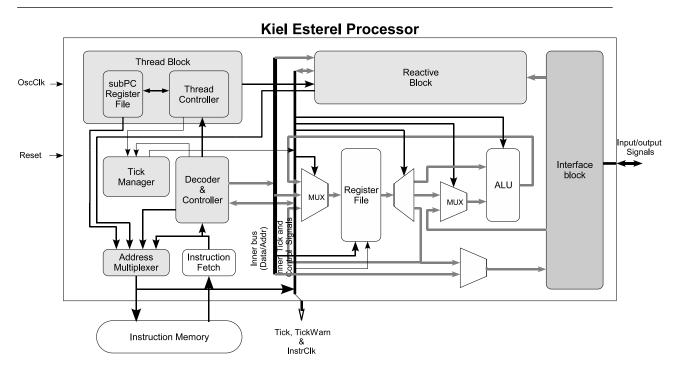

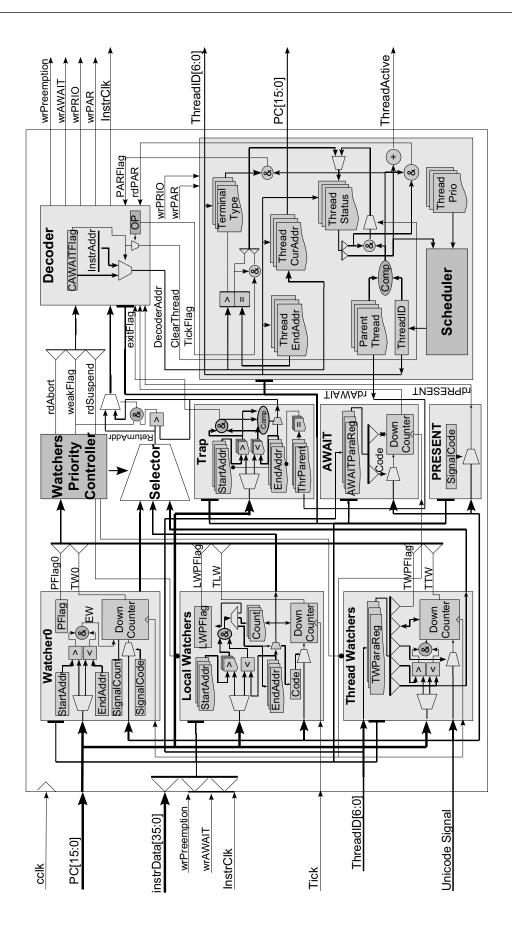

| 4.2  | Overview of the architecture of the KEP                                                                                                                                | 55 |

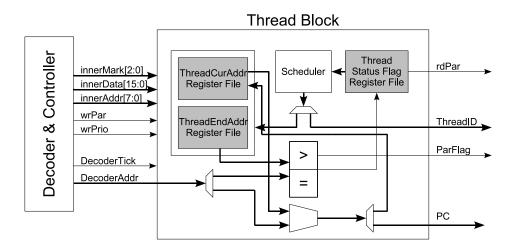

| 4.3  | Architecture of the Thread Block                                                                                                                                       | 56 |

| 4.4  | Algorithm for creating KEP threads                                                                                                                                     | 58 |

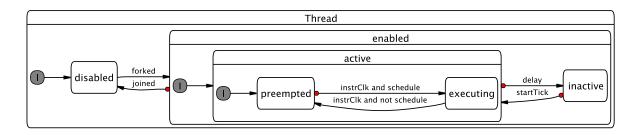

| 4.5  | Execution status of a single thread                                                                                                                                    | 59 |

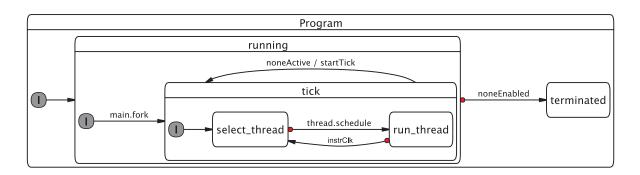

| 4.6  | The status of the whole program, as managed by the Thread Block                                                                                                        | 59 |

| 4.7  | Algorithm for running threads                                                                                                                                          | 59 |

| 4.8  | Algorithm for managing thread status (1)                                                                                                                               | 61 |

| 4.9  | Algorithm for managing thread status (2)                                                                                                                               | 62 |

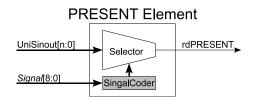

| 4.10 | Architecture of the Present Element                                                                                                                                    | 62 |

| 4.11 | Algorithm for handling signal test                                                                                                                                     | 63 |

| 4.12 | Executing an AWAIT instruction twice in a tick                                                                                                                         | 64 |

| 4.13 | Algorithm for handling the delay instructions (Decoder & Controller)                                                                                                   | 65 |

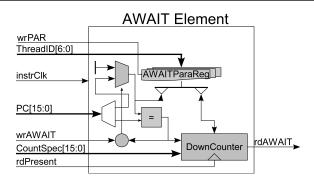

| 4.14 | Algorithm for handling the delay instructions (AWAIT Element)                                                                                                          | 66 |

| 4.15 | Architecture of the AWAIT Element                                                                                                                                      | 67 |

| 4.16 | Translation of concurrent Esterel await case statements (a) into to an equivalent Esterel program without concurrent await case statements (b).                        | 68 |

| 4.17 | Algorithm for handling the parallel await                                                                                                                              | 69 |

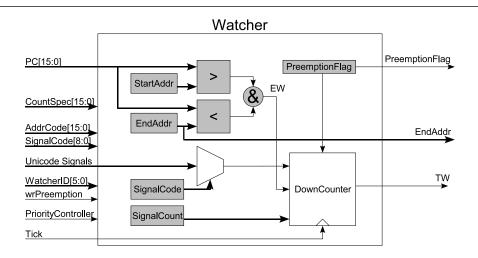

| 4.18 | Architecture of the Watcher.                                                                                                                                           | 71 |

| 4.19 | Algorithm for configuring watchers                                                                                                                                     | 72 |

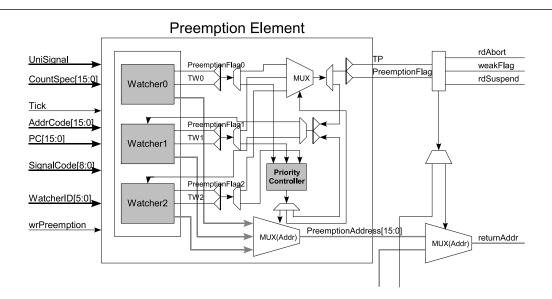

| 4.20 | Architecture of a Reactive Block with three Watchers                                                                                                                   | 73 |

| 4.21 | NESTED: the Esterel module illustrating the preemption statements (a), the KEP assembler program (b).                                                                  | 74 |

LIST OF FIGURES xi

| 4.22 | A possible execution trace of the NESTED module                                                                              | 74  |

|------|------------------------------------------------------------------------------------------------------------------------------|-----|

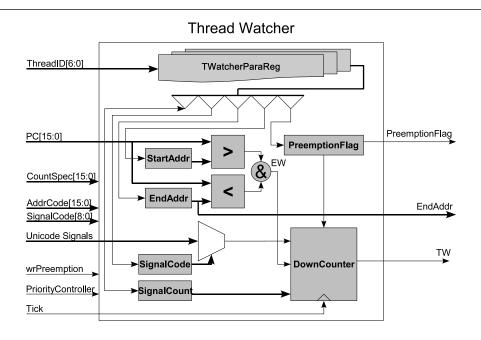

| 4.23 | Architecture of the Thread Watcher (TWatcher)                                                                                | 76  |

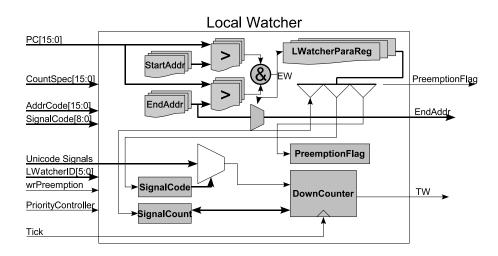

| 4.24 | Architecture of the Local Watcher (LWatcher)                                                                                 | 77  |

| 4.25 | Algorithm for indexing the LWatcher and the TWatcher                                                                         | 78  |

| 4.26 | Algorithm for triggering Watchers                                                                                            | 80  |

| 4.27 | Algorithm for triggering the LWatcher and the TWatcher                                                                       | 81  |

| 4.28 | Algorithm for handling all watchers                                                                                          | 82  |

| 4.29 | Esterel modules illustrating the trap nest, and possible execution trace. T0 denotes the initial thread, T1 is thread 1, etc | 83  |

| 4.30 | The KEP programs corresponding to the Trap1 and Trap2 modules (Figure 4.29)                                                  | 85  |

| 4.31 | Algorithm for setting and clearing an exception                                                                              | 87  |

| 4.32 | Algorithm for covering and handling exceptions                                                                               | 88  |

| 4.33 | Algorithm for Join Review mechanism for handling exception                                                                   | 89  |

| 4.34 | The example of waking up a thread                                                                                            | 91  |

| 4.35 | Algorithm for the Decoder & Controller                                                                                       | 92  |

| 4.36 | Architecture of the Reactive Core of the KEP                                                                                 | 93  |

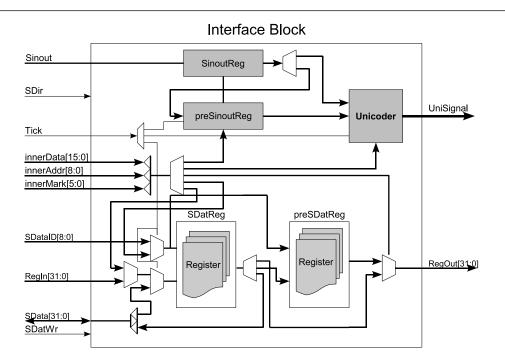

| 4.37 | Architecture of an Interface Block                                                                                           | 94  |

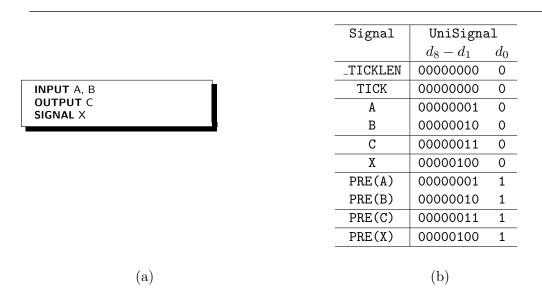

| 4.38 | The signal definition of an module (a), and the corresponding $UniSignal$ codes of the signals (b)                           | 94  |

| 4.39 | Algorithm for building the UniSignal                                                                                         | 95  |

| 4.40 | Algorithm for handling interface signals when a tick starts/finishes                                                         | 96  |

| 4.41 | Algorithm for executing the signal emission instruction                                                                      | 97  |

| 4.42 | Translating the Esterel combined valued signal (a) to the corresponding assembler code for KEP (b)                           | 98  |

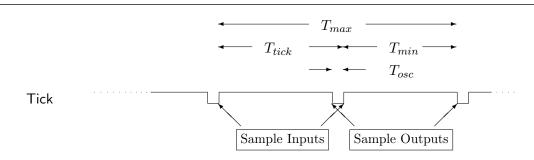

| 4.43 | A waveform of the Tick signal and derived values                                                                             | 96  |

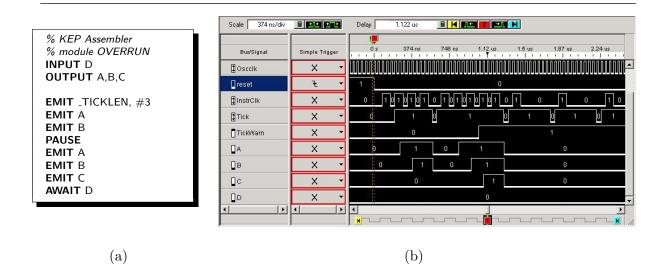

| 4.44 | An example KEP assembler code illustrating the Tick Manager (a), and a resulting timing diagram (b)                          | 100 |

| 4.45 | Execution the EXAMPLE program                                                                                                | 102 |

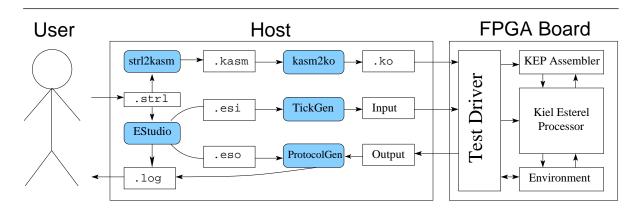

| 5.1  | Structure of the KEP evaluation platform                                                                                     | 107 |

| 5.2  | The EXAMPLE Esterel program: (a) Esterel; (b) KEP Assembler; (c) KEP Machine Code Listing.                                   | 109 |

xii LIST OF FIGURES

| A.1 | Translating an Esterel CountAwaitCase module (a) to its equivalent form (b), and the corresponding assembler code for KEP (c) | 137 |

|-----|-------------------------------------------------------------------------------------------------------------------------------|-----|

| В.1 | The ABRO KEP Machine Code Listing                                                                                             | 162 |

| B.2 | The KEP Evaluation Program                                                                                                    | 167 |

| B.3 | Debugging a Program.                                                                                                          | 169 |

# List of Tables

| 2.1  | Comparison of implementation alternatives                                                                                            | 9  |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1  | Overview of the KEP Esterel-type instruction set architecture. Esterel kernel statements are shown in <b>bold</b>                    | 38 |

| 3.2  | Overview of the KEP non-Esterel-type instruction set architecture 4                                                                  | 40 |

| 5.1  | The code size and RAM usage (in word) comparison of the CURVE implementation between KEP, MCS51, and MicroBlaze                      | 11 |

| 5.2  | Performance comparison between the KEP3 and EMPEROR 11                                                                               | 12 |

| 5.3  | Extending a KEP to different threads                                                                                                 | 13 |

| 5.4  | Concurrency analysis of benchmarks                                                                                                   | 14 |

| 5.5  | Comparison of compilation time of the benchmarks                                                                                     | 15 |

| 5.6  | Preemption character analysis of benchmarks                                                                                          | 16 |

| 5.7  | Effects on the Reactive Core's cost/performance of the various watchers architecture                                                 | 17 |

| 5.8  | Analysis of context switches (CSs), in absolute numbers and relative.  Minimal and maximal relative values are shown <b>bold</b>     | 17 |

| 5.9  | Memory usage comparison between KEP and MicroBlaze implementations. "(b)" refers to measurements in bytes, "(w)" to words            | 18 |

| 5.10 | The worst-/average-case reaction times (in clock cycles) for the KEP and MicroBlaze implementations, in absolute and relative values | 19 |

| 5.11 | The energy consumption comparison between KEP and MicroBlaze implementations                                                         | 20 |

| B.1  | The code format of the 31st char of the information string                                                                           | 33 |

| B.2  | The code format of the information string of the on-board KEP 16                                                                     | 33 |

xiv LIST OF TABLES

# Chapter 1

## Introduction and Motivation

#### 1.1 Introduction

In the past decades, computer systems have rapidly surrounded us. Nowaday, if we take a close look at applications, we will be surprised at how many computer systems can be found in our daily life, e. g., mp3 players, the computer controlled microwave ovens, washing machines, engine controllers and ABS for automobiles. Unlike a general-purpose computer, such as a computer on our desktop, these embedded systems are special-purpose systems in which computers are completely encapsulated by the devices they control. In general, an embedded system is pre-defined for very specific requirements.

Applications can be divided into one of three categories [18], i. e., the transformational systems, which compute output values from inputs values and then stop, e. g., batch processing, simulations, compilers; the interactive systems, which constantly interact with their environment in such a way that the computers can be viewed as the masters of the interaction, e. g., databases, operating systems; or the reactive systems, which continuously react to stimuli coming from their environment by sending back to stimuli, e. g., engine controllers, traffic control, microcontrollers, etc. In general, most of embedded systems are reactive systems.

Reactive systems are purely input-driven and they must react at a pace that is dictated by the environment. Any automatic control system can be classified as a reactive system, e. g., nuclear plant controllers, airplane flight systems, etc. The essential characteristics of reactive systems can be summarized as following [49]:

**Criticality** They are highly critical, just like the systems they control are critical. Failure of these systems could cause catastrophic consequences for human life.

**Parallelism** At least the parallelism between the system and its environment must be taken into account during the specification. Moreover, it is very often convenient for the designer to conceive the system as a set of parallel components, cooperating in order to achieve the desired behavior.

**Determinism** A reactive system determines a sequence of output signals from a sequence of input signals in a unique way. This determinism makes their design, analysis, and debugging much easier. Thus it must be preserved by the implementation.

For programming a reactive system, a traditional programming language, e. g., C or Java, can be employed. However, this has several shortcomings. First, classical asynchronous languages lack high-level parallel programming primitives, and asynchronous parallelism can cause an unwanted non-determinism. The correctness of a model that is directly described by common program language would be hard to certify, which is an essential requirement of a safety-critical system. Second, the classical programming languages lack statements for modelling reactive control structures. Furthermore, those languages are relatively low level, hence, the developers have to not only focus on specifying the functions of a module, but also have to implement those functions.

In the 1980s, the synchronous languages were introduced, which can cope with the above mentioned drawbacks of traditional programming language. Although several languages, e. g., Esterel [23], Lustre [65], and Signal [63], were presented for different purposes, they still have some common features [11, 10]. First, concurrency—all of these languages support functional concurrency and include that express concurrency in a user-friendly manner [55]. Second, simplicity—those languages have a simple formal model to make formal reasoning tractable, especially for clearly describing formal model as simple as possible [77]. Finally, synchronicity—they are based on the synchrony hypothesis, which states in essence that a system responds in zero time to environmental requests [23]. Gradually, the synchronous languages have attracted some leading companies which develop automatic control software for critical applications, such as Schneider, Dassault, Aerospatiale, Snecma, Cadence, Texas Instruments, and Thomson [10, 49]. The key advantage of synchronous languages is that the synchronous approach has a rigorous mathematical semantics which allows the programmers to develop critical software faster and better.

Our work focuses on the Esterel language, which currently appears to be the best-known synchronous language in industry and academia [10]. In the industry area, Esterel is used in applications such as developing DSP chips for mobile phones [30, 3], designing and verify DVD chips, and programming the flight control software of Rafale fighters [22, 49]. Although its strength has been proven, it still contains some weaknesses, for example, the comparatively inefficient implementation of Esterel modules in general [102].

#### 1.2 Motivation

Esterel is an imperative language dedicated to the programming of reactive applications [21, 19]. In contrast to many high-level languages, Esterel is both parallel and deterministic. The language is based on a formal mathematical semantics.

In Esterel, signals are used to communicate internally and with the environment. The execution of an Esterel program is divided into logical instants, or ticks. The synchrony hypothesis of Esterel implies that the outputs generated from given inputs occur at the same logical instant [23]. Signals are present or absent throughout an instant, indicating the occurrence of certain events, and they may also carry a value.

The Esterel *parallelism* is expressed by the concurrency operator ("||"). It groups statements in parallel, which also can be regarded as threads. When several threads are active concurrently, they may communicate back and forth instantaneously, that is, within the same logical tick. The communication between concurrent modules depends on local signals.

The Esterel *preemption* includes weak and strong abortion, suspension [18], and exception handling. The strong abortion kills its body immediately; the weak abortion first terminates its current reaction. On the contrary, the suspension can temporarily halt its body when the trigger occurs. The exception handling mechanism defines an exit point for a trap body. If the body exits the trap, the trap statement immediately terminates and weakly aborts the trap body.

Neither traditional processors nor classical programming languages have similar structures or statements (instructions) to handle corresponding Esterel statements efficiently. Hence, the implementation of the Esterel semantics on commercial off-the-shelf (COTS) processors is problematic since it must be simulated. Therefore, an Esterel-based design proves its efficiency on model description and validation, but can hardly enhance the implementation performance or reduce resource usage. Although researchers have studied different compiling techniques for synthesizing Esterel programs to efficient intermediate languages, the final execution code is still fairly large and has long execution times.

Since traditional processors have difficulties to handle Esterel programs efficiently, it is natural to raise the question whether a special processor can be developed for handling Esterel structure directly? In other words, whether an Application Specific Instruction-set Processor (ASIP) can be used for targeting Esterel programs? Furthermore, what benefits can result from this alternative strategy, especially compared with previous Esterel implementations?

#### 1.3 Research Contribution

The focus of this dissertation is the development of a reactive architecture. The project was driven by the desire to achieve predictable, competitive execution speeds at minimal resource usage, in terms of processor size and power usage as well as instruction and data memory. This work has resulted in the  $Kiel\ Esterel\ Processor\ (KEP)$ . It is a custom multi-threaded reactive processor, to our knowledge it is the first of this kind.

This thesis presents the architecture of the KEP. Notable features of the KEP include the following:

- 1. The KEP is the first reactive processor which employs a multi-threaded architecture for directly handling concurrency. This strategy uses resources efficiently and easily scales up to very high degrees of concurrency.

- 2. The KEP contains a full-custom *reactive core*, whose instruction set and data path have been tailored exclusively for the processing of Esterel code. Hence, all types of Esterel preemptions, delays, and exceptions, can be handled by KEP very efficiently.

- 3. The KEP also includes an interface block for handling Esterel input, output and local types of pure and valued signals. Furthermore, testing the presence and values of signals across logical instants (corresponding to Esterel's pre operator) are also directly supported.

- 4. Throughout the development of the KEP, scalability has been considered, hence the allowed number of signals, the maximum thread number, the nesting depth of preemption primitives, and other design parameters are fully configurable.

- 5. Unlike other reactive processing approaches, the KEP Instruction Set Architecture (ISA) is *complete* in that it allows a direct mapping of all Esterel statements onto KEP assembler. All the Esterel kernel statements, including delay, preemption, concurrency and exception handling, are implemented directly and semantically accurately by the KEP, and they can be freely combined and nested as defined by the Esterel semantics. However, it can also make unrefined processing approaches fairly costly. The KEP ISA therefore not only supports common Esterel statements directly, but also takes into consideration the statement context. Providing such a *refined* ISA further minimizes hardware usage while preserving the generality of the language.

Advantages of the KEP compared with traditional processors include:

**Performance** As the instruction set and data path have been developed specifically for Esterel execution, the Esterel module can be executed fairly fast on KEP. This benefits two key aspects of system performance, *i. e.*, the *Worst Case Reactive Time* (WCRT) and *Average Case Reactive Time* (ACRT).

Memory Because most typical Esterel statements can be expressed directly with just a single KEP instruction, an Esterel program executed on the KEP has very low instruction and data memory usage.

**Power Usage** For controller programming, the main goal of Esterel, the control signals tend to be more often absent than present [19]. Due to the architecture of the KEP, very few instruction cycles are needed for executing a *blank event*, which corresponds to the condition of all signals being absent.

**Logic Area** The KEP offers a novel light-weight thread model, *i. e.*, the multi-threaded architecture, to implement Esterel concurrency efficiently. This characteristic significantly reduces its logic resource usage for implementing a practical (industry scale) Esterel module.

**Predictability** The KEP is not designed to optimize (average) performance for general purpose computations, and hence does not have a hierarchy of caches, pipelines, branch predictors, etc. This leads to a simpler design and execution behavior and further implies that control-flow is preserved while compiling Esterel into machine code, and that the execution platform has a very predictable timing behavior.

In summary, the KEP is an efficient reactive processor for handing practical Esterel modules, and appears to be very competitive with other implementations.

This dissertation focuses on the KEP hardware, *i. e.*, its architecture and execution model. However, since starting the KEP project, a set of closely related activities have started, in particular considering its compiler [85, 26], timing analysis [86, 28, 27], and HW/SW Co-design [58, 57]. This dissertation will summarize these activities as is appropriate to help the understanding of the KEP itself.

## 1.4 Thesis Organization

This dissertation is composed of five main sections. The next chapter provides an overview of the Esterel language and existing Esterel implementation methods. It also reviews some previous reactive processor approaches. In Chapter 3, we give an overview of the KEP instruction set architecture (ISA) design. Chapter 4 provides the detailed descriptions of the core contributions of this research work, *i. e.*, the multi-threaded reactive processor architecture model. It is followed by a presentation of the KEP evaluation platform, which includes the KEP compiler, the evaluation hardware platform and the evaluation software. Experimental results are presented in Chapter 5, and are also compared with results of its competitors and other implementations. We finally conclude with a summary of this work, and propose considerations for future work in Chapter 6.

# Chapter 2

## Background and Related Work

Most reactive applications can be divided to the data handling part and control handling [19] part. Unlike the data handling, which continuously produces output values from input values, the control handling produces discrete output signals from input ones. For example, transportation systems, robots, communication protocols, peripheral drivers, and human-machine interface fall into this category. The Esterel language was developed to design control-dominated reactive programs as an imperative concurrent language.

There exist two major versions of Esterel language, *i. e.*, Esterel V5 [19], which most academical tools use; and the newer Esterel V7 [116], enhances some complex control description statements and new powerful hardware datapath expressions. It is currently evolving into an IEEE standard. The KEP targets Esterel V5 language.

In this thesis, we generally refer to V5 unless indicated otherwise.

## 2.1 Implementation Technologies

To build a real system for an Esterel specification, several implementation methods have been introduced, which can be distinguished by what they generate:

#### • Hardware Synthesis

Hardware implementations [14, 117, 47, 111, 110, 32], where an Esterel program is synthesized into a hardware circuit presentation (e. g. VHDL or Verilog HDL), lead to small footprints (low memory requirements) and cheap implementations. However, hardware implementations are not flexible, meaning that even a tiny modification of the program will require a re-synthesis. Furthermore, for an industry scale Esterel module, which may include some data path handling, its resourc usage may increase rapidly. In short, it can be used for implementing pure Esterel modules, e. g., a RAM controller, but is not suitable for realizing common large scale Esterel applications [38].

#### • Software Synthesis

In a software implementation [23, 44, 46, 39, 50], an Esterel program is first synthesized into sequential, lower level language codes (e. g., C or JAVA), and then compiled to codes which can be executed at a target COTS processor. See also Section 2.2. In contrast to the hardware synthesis, it is a very flexible solution, and has low costs for the data path and arithmetic operations. However, classical processor architectures cannot handle reactive control constructs, such as abortions, directly, and cannot concurrently observe multiple signals. Therefore, handling these control constructs correctly, including priority resolution, turns out to be fairly expensive on classical software implementations. Moreover, the footprint (memory requirement) can be too large for low-cost microcontrollers.

#### • Hardware/Software Co-design

A co-design implementation partitions a model into hardware and software components [7]. This implementation suits small control-dominated embedded systems, and tries to achieve a good balance of flexibility, performance and cost. It is composed of a few Application Specific Integrated Circuits (ASIC) combined with software procedures on general-purpose processors [37, 6]. The SW/HW interface is synthesized for internal communication [107, 93]. As a result, it combines the advantages of hardware and software implementation methods, but also inherits some shortages [24, 79]. The co-design approach has been explored for example by the POLIS project [6, 99].

#### • Reactive Processors

The reactive processor implementation aims to combine the advantages of custom hardware and traditional software. See also Section 2.3. It implements an Esterel program on a reactive processor whose instruction set has been tailored to Esterel. In other words, it can be viewed as the ASIP (Application Specific Instruction Processor) implementation [31, 75]. However, depending on whether a traditional processor core is used as a part of reactive processor, this approach can be further distinguished to two variants:

Patched Reactive Processor implementations combine a COTS processor core with an external hardware block, which implements additional Esterel-style instructions.

Custom Reactive Processor implementations consist of a full-custom reactive core, whose instruction set and data path have been tailored exclusively for the processing of Esterel code.

Driven by the limitations of traditional processors, the *reactive processing* approach tries to achieve a more efficient execution of reactive programs by providing an ISA that is a better match for reactive programming. The architectures proposed so far specifically support Esterel programming; however, they should be an attractive alternative to traditional processor architectures for reactive programming in general.

|                       |               | Hardware                  | Software                                       | Co-design                                                      | Patched                                                           | Custom                  |

|-----------------------|---------------|---------------------------|------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------|-------------------------|

|                       |               |                           |                                                |                                                                | Processor                                                         | Processor               |

| Architecture          |               | Hardware  Custom Hardware | Software  COTS Assembler  COTS-µC  Environment | Co-design  COTS Assembler  COTS-  COTS-  Hardware  Environment | Patched Processor  Extended Assembler  PIC Extension  Environment | Esterel-µC  Environment |

| Speed                 |               | ++                        | _                                              | +                                                              | +                                                                 | +                       |

|                       | Selected      | Berry [14],               | Berry <i>et al.</i> [23],                      | Baleani et al.                                                 | Roop et al.                                                       | Li et al.               |

| R                     | References    | Edwards [47]              | Edwards [44]                                   | [7]                                                            | [105]                                                             | [90]                    |

| F                     | Flexibility   |                           | ++                                             | _                                                              | +/-                                                               | +                       |

| Estere                | el Compliance | ++                        | ++                                             | +/-                                                            | _                                                                 | ++                      |

|                       | Logic Area    | ++/-                      | +                                              | +                                                              |                                                                   | +/-                     |

| $\operatorname{Cost}$ | Memory        | ++                        |                                                |                                                                | +                                                                 | +                       |

|                       | Power Usage   | ++                        | _                                              |                                                                |                                                                   | +                       |

| Appl. Design Cycle    |               |                           | ++                                             | +/-                                                            | ++                                                                | ++                      |

Table 2.1: Comparison of implementation alternatives.

++ represents best; -- means worst, e. g., Cost ++ means very low production costs.

Of course, each implementation has its advantages and drawbacks. Table 2.1 provides a high-level comparison of these implementation alternatives.

## 2.2 Compilation Approaches

In general, an Esterel program is first validated via a simulation-based tool set, and then compiled to an intermediate language, e. g., C or VHDL. Different technologies are used to compile the Esterel language. In the past, various techniques have been developed to synthesize Esterel into software; see [48, 10] for an overview, which also places Esterel code synthesis into the general context of compiling concurrent languages. The KEP compiler belongs to the family of simulation-based approaches, which try to emulate the control logic of the original Esterel program directly, and generally achieve compact and yet fairly efficient code. These approaches first translate an Esterel program into some specific graph formalism that represents computations and dependencies, and then generate code that schedules computations accordingly.

A nice historical overview of the original Esterel compilers can be found on the web [54]. The Esterel V1 and V2 compilers built automata for Esterel programs. Later the V3

compiler accelerated the automata-building process by simulating the intermediate code (IC) format – a concurrent control-flow graph hanging from a reconstruction tree handles Esterel's concurrency and preemption statements. However, the problem is the state explosion. As a result, although these compilers can produce very fast code, they can hardly be scaled to an industry program size [10].

To address this shortcoming, one can employ circuits to represent the intermediate code, since circuits are roughly linear while automata are exponential. The later Esterel compilers V4 and V5 adopt this idea. For example, the Esterel compiler V5, which is one of the most used Esterel compilers, translates the IC into a combinational logic network in a very direct way, and then uses a simple topological-sort-based scheduling technique to translate the logic network into sequential code [48].

However, the logic netlist representation of the V5 compiler still has some shortcomings. For example, in the circuit, every part is assumed to be always active. However, the software code which is generated via the circuit approach wastes time on evaluating idle portions of the program – a simulation of evaluating each gate in the network in every clock cycle. Obviously, the compilation technology of V5 could result in slow code [10].

The EC/Synopsys compiler first constructs a concurrent control flow graph (CCFG), which it then sequentializes [46]. Threads are statically interleaved according to signal dependencies, with the potential drawback of superfluous context switches; furthermore, code sections may be duplicated if they are reachable from different control points ("surface"/"depth" replication [17]).

The SAXO-RT compiler [39] divides the Esterel program into basic blocks, which schedule each other within the current and subsequent logical tick. An advantage relative to the Synopsis compiler is that it does not perform unnecessary context switches and largely avoids code duplications. However, the scheduler it employs has an overhead proportional to the total number of basic blocks present in the program. The grc2c compiler [100] is based on the graph code (GRC) format, which preserves the state-structure of the given program and uses static analysis techniques to determine redundancies in the activation patterns. A variant of the GRC has also been used in the Columbia Esterel Compiler (CEC) [50, 51], which again follows SAXO-RT's approach of dividing the Esterel program into atomically executed basic blocks. However, their scheduler does not traverse a score board that keeps track of all basic blocks, but instead uses a compact encoding based on linked lists, which has an overhead proportional to just the number of blocks actually executed.

On the other hand, in the POLIS project, an Esterel program will be translated to the Co-design Finite State Machines (CFSMs). The CFSM sub-network can be directly mapped into the abstract hardware description format BLIF. For the software, a Control-Data Flow Graph (CDFG) called S-GRAPH specifies the transition function of a single CFSM [6].

In summary, there is currently not a single Esterel compiler that produces the best code on all benchmarks, and there is certainly still room for improvements. For exam-

```

% Esterel

module REINC:

input S;

output O1,O2;

% Esterel

signal S in

module REINC:

present S then

input S;

emit O1;

output O1,O2;

else

emit O2:

loop

signal S in

present S then

pause;

emit O1;

emit S;

end signal;

else

emit O2:

% replicate

signal S in

end:

pause:

present S then

emit S

emit O1;

end signal

else

end loop

emit O2;

end;

pause

emit S;

end signal;

end loop

(a)

(b)

```

Figure 2.1: The schizophrenia problem (a) and the typical solution (b).

ple, the simulation-based approaches presented so far restrict themselves to interleaved single-pass thread execution, which in the case of repeated computations ("schizophrenia" [17]) requires code replications; it should be possible to avoid this with a more flexible scheduling mechanism.

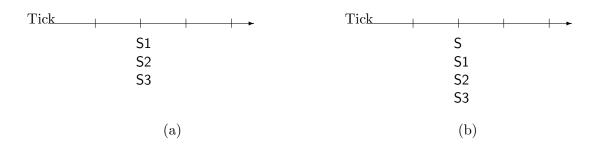

The schizophrenia problems are not only a problem of Esterel, but occur in all synchronous languages that provide local declarations as micro steps [106]. Schizophrenic programs are those compound statements which can be run and exited or terminated and reentered inside the same reaction [114]. The problem is caused because the local variables and signals involved may have two distinct occurrences in the same reaction with different values or statuses.

For example, consider the situation of a local declaration nested inside of a loop body, which is shown in Figure 2.1(a). The signal S is defined inside the loop. Each iteration refers to a fresh signal S. In a given instant two instances of S cohabit: the first being emitted at the end of the loop, and the second being tested as the loop is reentered. The problem is that these micro steps all belong to the same macro step and therefore all data values coexist at the same point of time.

The traditional solution to this problem is unrolling of loops and renaming local declarations in the different loop bodies, as shown in Figure 2.1(b). Obviously, this method will generate unnecessarily large code. Some other solutions are also discussed by Tardieu et al. [115] and by Schneider et al. [106]. In short, they all lose efficiency as the cost of curing the schizophrenia problem. However, this schizophrenia program will not bring any problem in the KEP implementation because the micro-step of the KEP execution will exactly follow the original definition of the Esterel program, see also Section 3.2.4.

## 2.3 Handling Esterel via Reactive Processors

Up to now, there are only limited and fairly recent investigations for reactive processors. Since all the introduced reactive processors are handling Esterel programs, they can also be called *Esterel Processors*. An introduction of different reactive processor implementations is presented in [119].

The first Esterel processor, called REFLIX [105], was presented by Salcic, Roop et al. in 2002. In this approach, a traditional soft microcontroller core (FLIX) is combined with a custom hardware block that extends the instruction set of the traditional microcontroller by certain new, Esterel-like instructions. Although its supported Esterel-style statements (instructions) were very limited, it performed better than its competitors, i. e., the FLIX and other microcontrollers. Another Esterel processor, which is similar to the REFLIX, was also presented by Chow et al. in 2004 [38]. In this work, the FLIX processor is replaced by the PIC processor [95], which is more popular in the industry control domain. However, both of them have to depart from the original Esterel semantics to adhere the control path of the traditional processor. For example, considering nested traps, the control path there delicately depends on address ranges and parallel relations of the traps—there is no corresponding control path for handling this situation directly in the traditional processors. This is further explained in Section 4.2.2. In 2005, Z. Salcic et al. presented the REMIC as a custom processor [104]. Since the essence of the REMIC is similar to its ancestors, it still inherits some of their limitations, e. q., the weak Esterel semantic compatibility. Both the RePIC and the REMIC were extended to multiprocessing architectures, e. q., the EMPEROR [41], to handle Esterel concurrency [103, 104].

In 2004, we have presented the first prototype of the KEP [89]. The architecture described in that paper is now referred to as the "KEP1". It represented to our knowledge the first custom-designed reactive processor, and the first reactive processor that correctly handled weak and strong abortion. However, it did not provide full concurrency, and logic and arithmetic expression were also not supported.

In the following year, the KEP2 improved over the KEP1 in that it includes an interface block that supports the PRE-operator, and can handle further Esterel-constructs such as variables and local signals [86, 88]. Furthermore, it contains an ALU and supports some classical logic and arithmetic expression. The KEP2 also includes a Tick Manager,

which can provide a constant logical tick length and detects timing overruns. We have also presented [86] an approach to analyze the Worst Case Reaction Time (WCRT) of the KEP2.

An important improvement of the next generation of the KEP is the implementation of concurrency [90] in 2006. The KEP3 was the first truly concurrent KEP. It implements Esterel's concurrency operator via multi-threading, which scales well to high degrees of concurrency with minimal resource overhead. Half a year later, the KEP3a and its compiler were presented [85, 84]. The KEP3a improves over the KEP3 in that it supports exception handling and provides context-dependent preemption handling instructions. The compiler employs a priority assignment approach that makes use of a novel concurrent control flow graph and has a complexity that in practice tends to be linear in the size of the program. Unlike earlier Esterel compilation schemes, this approach avoids unnecessary context switches by considering each thread's actual execution state at run time. Furthermore, it avoids code replication present in other approaches.

The latest version of the KEP is the KEP4, which is presented in this thesis. It enriches its control path for handling some delicate and complex mixed Esterel control structures, and supports more options for generating various configured processor series. It is the most powerful, flexible, and stable version of the KEP so far.

The KEP has also been employed as a platform for HW/SW co-design. Some extended works enrich the research of the multi-threaded reactive processor. Gädtke et al. [57, 58] presented an approach to accelerate reactive processing via an external logic block that handles complex signal expressions. An Esterel program is synthesized into a software component, running on the Kiel Esterel Processor, and a hardware component, consisting of simple combinational logic. The transformation process involves a two-step procedure, which first partitions the program at the source level and subsequently performs the synthesis. An intermediate logic minimization, at the source code level, facilitates the synthesis of compact logic blocks.

Another important part of the KEP project is the development of the KEP compiler [26, 85], including WCRT analysis [27, 28]. The analysis of the WCRT is influenced by the KEP in two ways: the exact number of instructions for each statement and the way parallelism is handled. The analysis is performed on a graph representation, the Concurrent KEP Assembler Graph (CKAG). In a first step we compute whether concurrent threads terminate instantaneously, thereafter it is able to compute for each statement how many instruction are maximally executable from it in one logical tick. The maximal value over all nodes gives us the WCRT of the program.

According to the classification method in Section 2.1, which depends on whether the processor description strategy is based on an existing COTS processor or not, the whole KEP series and the REMIC falls in the *Custom Processor* [78] implementation approach. Other Esterel processors, *i. e.*, REFLIX and RePIC, belong to the *Patched Processor* [80] implementation approach. Another classification method is based on the concurrency handling methods of these Esterel processors. Figure 2.2 compares the *multi-processing*

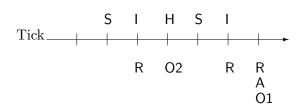

and the multi-threaded architectures. Of course it is always possible to translate an Esterel program into an equivalent program that has a flattened state space, i. e., sequentialization. The REFLIX, the RePIC, and the KEP2 and its predecessor can be classified to this type. However, to handle concurrency directly, in the multi-processing implementation approach, every Esterel thread is mapped onto an independent processor to be executed, and a thread control unit handles the synchronization and communication between processors, as is done by the EMPEROR [124]. It allows the distributed execution of Esterel programs and also handles Esterel's concurrency operator. The EMPEROR uses a cyclic executive to implement concurrency, and allows the arbitrary mapping of threads onto processing nodes. This approach has the potential to speed up execution relative to single-processor implementations. However, their execution model potentially requires to replicate parts of the control logic at each processor. The most efficient concurrency implementation approach is multi-threaded, which employs multithreading to implement concurrency. In this way, a single KEP core is extended to handle concurrency by an interleaved control flow. Each Esterel thread has an independent program counter and threads are scheduled according to their activation status and a dynamical changed priority. The KEP3 and later versions of the KEP fall into this category.

Although the multi-processing strategy seems a straightforward solution for the implementation of the Esterel language, it cannot avoid two essential limitations. First, to handle Esterel preemption and statements, it can neither support necessary Esterel-style instructions, nor follow the original Esterel semantics directly. For example, again consider the nested trap illustrated in Section 4.2.2. Since the Esterel threads are executed on different processors, when both of them throw exceptions, some complex mechanisms should be built for handling these exceptions correctly—this also degrades efficiency. Second, to handle the Esterel concurrency, such an architecture can hardly support the arbitrary nesting of concurrency and preemption. Furthermore, for a real embedded system, in particular if one wants to scale up to high degrees of concurrency and preemption nests, the multi-processor approach is relatively hardware-intensive.

Since multi-processing and multi-threaded reactive processors employ different strategies to handle Esterel concurrency, their compilers, which synthesize an Esterel program to the target reactive processor codes, also use different approaches to implement the communication between threads. For example, for multi-processing, the EMPEROR Esterel Compiler 2 (EEC2) [124] is based on a variant of the GRC, and appears to be competitive even for sequential executions on a traditional processor. However, their synchronization mechanism, which is based on a three-valued signal logic, does not seem to be able to take compile-time scheduling knowledge into account, but replaces it by repeating cycles through all threads until all signal values have been determined. Hence the compiler needs to generate sync instructions, to ensure that signals are not tested before they are emitted [41]. On the other hand, the multi-threaded implementation approach implements interleaving by inserting priority setting code at the context switch point. See also Section 3.2.1.

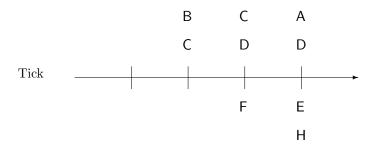

Figure 2.2: The architecture overview of multi-processing (a) and multi-threaded (b).

To give a summary review of previous Esterel processors other than the KEP series, we note that they have three significant limitations. First, the function of their Esterel style instructions is incomplete and cannot implement reactive control flow according to the original Esterel semantics. Second, it is not obvious how this design, *i. e.*, multiprocessing for handling Esterel concurrency, would support the arbitrary nesting of concurrency and preemption. Finally, for a real embedded system, in particular if one wants to scale up to high degrees of concurrency and preemption nests, the multiprocessor approach leads to relatively hardware-intensive implementations and large executables.

# Chapter 3

# The KEP Instruction Set Architecture

The development of the KEP was driven by the desire to achieve competitive execution speeds at minimal resource usage, considering processor size and power usage as well as instruction and data memory. A key to achieve this goal is the instruction set architecture (ISA) of the KEP, which allows the mapping of Esterel programs into compact machine codes while still keeping the processor light-weight. Notable features of the KEP ISA include the following:

- Unlike earlier reactive processing approaches, the KEP ISA is *complete* in that it allows a direct mapping of all the Esterel statements onto KEP assembler. All the Esterel kernel statements, including delay, preemption, concurrency and exception handling, are implemented directly and semantically accurate by the KEP, and they can be freely combined and nested as defined by the Esterel semantics. Valued signals and local variables are also supported.

- The KEP ISA is *efficient* in that most of the commonly used Esterel statements can be expressed directly with just a single KEP instruction.

- A characteristic of the Esterel language is that it provides a set of powerful control flow operators, which can be combined with each other in an arbitrary fashion. This makes the language concise and facilitates formal analysis; however, it can also make unrefined processing approaches fairly costly. The KEP ISA therefore not only supports common Esterel statements directly, but also takes into consideration the statement context. In particular, it provides preemption instructions that map onto different types of hardware units depending on whether preemptions are nested or not and whether they include single threads or multiple threads. Providing such a refined ISA further minimizes hardware usage while preserving the generality of the language.

Figure 3.1: Simple: a module illustrating the structure of the Esterel program (a), and a possible execution trace (b).

This chapter presents the KEP instruction set architecture. In Section 3.1 we introduce some chosen Esterel statements/structures. The following Section 3.2 describes the design of the KEP's Esterel-type instructions, and classical processor instructions are presented in Section 3.3. Section 3.4 illustrates how to translate an Esterel program to the KEP assembler. Finally, the method of the instruction encoding is sketched in Section 3.5.

## 3.1 The Esterel Language

Esterel is an imperative synchronous language for the development of complex reactive systems. The *module* is the basic Esterel program unit. It is composed of the module name, the description of input/output signal interfaces, and an executable body. To write an Esterel program, a designated main module is necessary, and a collection of modules can also be included and referred to in the main module.

Figure 3.1(a) shows a simple example. In this case, the name of the module is defined as Simple by module  $Simple:_{L01}^{1}$ , and the end module $_{L16}$  indicates the end of the module.

As mentioned before, the *signal* is a fundamental concept of Esterel. The *interface signals* declared in the module interface are used to communicate with the environment. For example, in Figure 3.1, line 2 defines an input signal A, and line 3 defines two output signals O1 and O2. The other signal type is *local signals*. It aims to handle the internal

<sup>&</sup>lt;sup>1</sup>To aid readability, we here use the convention of subscripting instructions with the line number where they occur.

communication of the Esterel program. The signal  $M_{L04}$  and end signal  $L_{15}$  define the scope of local signal M.

Furthermore, there is a special pure signal tick, which represents the activation clock of the reactive program. Its status is present in each instant. This signal is declared implicitly and cannot be redeclared.

Signals have a presence status, *i. e.*, *present* or *absent*. At each tick, a signal is either present (*emitted*) or absent (not emitted). By default, signals are absent except for the tick signal. The statuses of signals are instantaneously broadcast throughout the program, which implies that all statements see each of them in a consistent way. In Esterel, the broadcasting of signals is used for processing communication. It is easy to understand that the input broadcasting is implicit because concurrent statements evolve in lock step in the same input environment. Furthermore, the signal broadcasting allows that the presence status of a signal can be tested by multiple signal receivers. For example, in the second tick, the signal M is emitted by emit  $M_{L07}$ , and is tested by present M then<sub>L08</sub> and triggers await  $M_{L12}$  simultaneously. Besides, from within the programs, the input and output signals can be equally tested for presence or absence, as well as the local signals used within the program.

An Esterel module reacts to an input event by generating an output event. The reaction is conceptually considered as instantaneous, and is called an instant or tick, see also Section 4.5. It reacts to the input event sequences (input histories) repeatedly and generates output histories. An Esterel module is deterministic, i.e., the module always produces the same sequence of outputs when it is given the same sequence of inputs.

Figure 3.1(b) shows a possible execution trace of this module, with input signals shown above the time line and local and output signals below the time line. Note that the reaction is assumed to take no time because of the synchrony hypothesis. From the user's point of view, there is no need to worry about the internal reaction time, the output is considered as being generated at the same time as the input event occurrs—without logical delay.

An Esterel statement starts in some instant, remains active for a while, and may terminate in the current or some later instant. A statement is *instantaneous* if it terminates in the same instant it starts in; *e. g.*, in the second tick of the Simple module, the emit  $M_{L07}$  emits signal M, and present M then<sub>L08</sub> tests this signal immediately. Both of them are instantaneous statements. On the contrary, a non-instantaneous statement may delay some instants after it starts. For example, the delay statement await  $A_{L06}$  always takes time. It starts at the first instant, stays active, and terminates at the second instant even if A occurs at the first instant. Hence, it lasts one A.

In summary, the timing semantics of the Esterel statements relies on four structural notions. The *starting* instant of an Esterel statement is determined by the context of this statement in a program. The internal execution environment of this statement determines its *termination*. Since Esterel has block exits, the execution of a statement

can also be determined to exit a *trap* before this statement terminates. Finally, a statement can be *aborted* (killed) by some other part of the program.

The *timing* characteristic of the Esterel statements, *i. e.*, at which "instant" they are performed, is one of the key properties of Esterel statements. Furthermore, the preemption and concurrency statements provide that Esterel has more powerful control flow than traditional programming languages. Hence, to design a processor targeting the direct execution of Esterel, it is necessary to study the semantics of the Esterel statements first.

#### 3.1.1 Esterel Statements

There are dozens of Esterel statements. Hence, it seems difficult to decide which statements should be chosen as the instructions to be implemented by the processor directly. In fact, the choice of the instruction set is also a common issue in the ASIP design field [1, 62, 75].

Fortunately, there is a very small number of kernel statements in Esterel and a comparatively large number of derived statements. The derived statements can always be replaced by equivalent constructions that involve only kernel statements; the derived statements are merely syntactic sugar, i. e., convenient shorthands for the programmer. In fact, the accepted set of Esterel kernel statements has evolved over time. For example, the halt statement, which performs no action and never terminates nor exits traps [23], used to be regarded as a kernel statement [13, 11], but now is considered as the combination of the loop and the pause. We here adopt the definition of which statements are kernel statements from the v5 standard [19, 17].

The following description briefly introduces the semantics of the Esterel kernel statements. For a more detailed discussion, refer to [23, 16, 19].

#### • ||

"| " is the parallel statement. It forks control into concurrently executed threads. The two threads of a parallel immediately start when the parallel statement starts. The parallel statement will stay active whenever one of its threads remains active, unless a branch exits a trap. If both of its threads are terminated, the parallel statement will terminate instantaneously.

If a parallel's threads terminate in different instants, the parallel will wait for the last one to terminate. Furthermore, parallel threads may simultaneously exit traps. If one thread exits the trap T or both threads exit the same trap T, of course the parallel will exit T. However, if threads try to exit different traps T1 and T2 in the same instant, the parallel will exit the outermost of these traps, the other one will be discarded.

#### • suspend ... when S

The suspend statement provides a suspension mechanism. It freezes the state of a

body for the instant when the trigger event occurs. In this statement, the sensitive signal S is also called the *guard*. In the initial instant, the body of the suspension is started; and then the guard controls execution of the body in each instant. If the body of the suspension terminates or exits a trap, so does the suspend statement; if it pauses, then the suspend statement also pauses. Note the default format of this statement implies a delay. Hence, only if the body of suspension does not terminate in the first instant then the sensitive signal S will be tested for presence as long as the body of suspension remains active.

From the second tick, if signal S is present, the suspension body will not be executed in the instant and it is kept frozen for the next instant. In this case, the body of the suspension is suspended for this instant. On the other hand, if signal S is absent, then the body receives the control for this instant, *i. e.*, the body is activated for the instant.

Incidentally, the suspension statement was not a kernel statement before.

#### • trap T in ... exit T ... end trap

The trap statement expressed as trap T in ... end trap, and the exit statement expressed as exit T, are a statement pair which provides the exception mechanism. The trap statement defines a scoped exit point T for its body; and the exit statement exits from the trap.