# Technologies for the integration of Through Silicon Vias in MEMS packages

# Dissertation

zur Erlangung des akademischen Grades Doktor der Ingenieurwissenschaften (Dr.-Ing.) der Technischen Fakultät der Christian-Albrechts-Universität zu Kiel

### Stephan Warnat

Flintbek 2009

- 1. Gutachter: Prof. Dr. rer. nat. H. Föll

- 2. Gutachter: Prof. Dr.-Ing. B. Wagner

Datum der mündlichen Prüfung : 18.12.2009

## Contents

| Li | st of  | Figure   | S                                       | v   |

|----|--------|----------|-----------------------------------------|-----|

| Li | st of  | Tables   | 6                                       | vii |

| Та | able o | of Abbr  | reviations and Symbols                  | ix  |

| 1  | Inte   | gratior  | n of Through Silicon Vias (TSV) in MEMS | 1   |

| 2  | 3D     | advanc   | ced packaging                           | 9   |

|    | 2.1    | 3D pa    | ckaging                                 | 9   |

|    | 2.2    | Throu    | gh Silicon Vias                         | 11  |

|    |        | 2.2.1    | Concepts                                | 11  |

|    |        | 2.2.2    | Commercial Activities                   | 12  |

|    |        | 2.2.3    | TSV in MEMS packages                    | 16  |

|    |        | 2.2.4    | Application examples                    | 17  |

| 3  | Spe    | cificati | ons                                     | 23  |

|    | 3.1    | TSV p    | process sequences                       | 23  |

|    | 3.2    | Pad-ce   | ell requirements                        | 26  |

|    |        | 3.2.1    | CMOS pad-cell                           | 26  |

|    |        | 3.2.2    | MEMS pad-cell                           | 29  |

|    | 3.3    | TSV ł    | nole geometry                           | 30  |

|    | 3.4    | Mecha    | anical Aspects                          | 30  |

|    |        | 3.4.1    | Wafer robustness                        | 30  |

|    |        | 3.4.2    | TSV system                              | 38  |

|    |        | 3.4.3    | Hermetic criterion                      | 45  |

|    | 3.5    | Electr   | ical Specifications                     | 46  |

|    |        | 3.5.1    | Dielectric film                         | 46  |

|    |        | 3.5.2    | Metallic film                           | 50  |

|    | 3.6    | Test d   | lesign                                  | 52  |

| 4  | Key   | technologies                                                                 | 55  |

|----|-------|------------------------------------------------------------------------------|-----|

|    | 4.1   | Hole formation                                                               | 55  |

|    |       | 4.1.1 Silicon and Silicon-nitride etching                                    | 59  |

|    |       | 4.1.2 Silicon-dioxide                                                        | 68  |

|    | 4.2   | Deposition techniques                                                        | 72  |

|    |       | 4.2.1 Isolation-layer                                                        | 75  |

|    |       | 4.2.2 Metalization-layer                                                     | 86  |

|    | 4.3   | Pattern transfer                                                             | 104 |

|    | 4.4   | Technology summary                                                           | 113 |

| 5  | Proc  | cess Flow Integration                                                        | 115 |

|    | 5.1   | TSV in Test-Design                                                           | 115 |

|    | 5.2   | TSV in the David-project                                                     | 122 |

|    | 5.3   | TSV in a mass flow sensor                                                    | 123 |

| 6  | Sum   | mary and Outlook                                                             | 125 |

| 7  | Арр   | endices                                                                      | 129 |

|    | А     | Capacitance as a function of the isolation thickness gradient (linear decay) | 129 |

|    | В     | Material Data                                                                | 131 |

|    | С     | Pad-cell model                                                               | 132 |

| 8  | Pub   | lished work                                                                  | 133 |

| Re | ferer | ices                                                                         | 134 |

# List of Figures

| 1.1  | Lateral and 3D chip integration approaches.                                    | 2  |

|------|--------------------------------------------------------------------------------|----|

| 1.2  | Basic concept and elements of a Through Silicon Via                            | 3  |

| 1.3  | MEMS package of an inertial measurement unit                                   | 5  |

| 1.4  | Example of Through Silicon Vias in a MEMS package.                             | 5  |

| 2.1  | Advanced 3D stacking technologies.                                             | 10 |

| 2.2  | TSV integration approaches in IC wafers                                        | 13 |

| 2.3  | Examples of post-CMOS TSV integration approaches                               | 14 |

| 2.4  | Package examples for an integration of MEMS and ASIC $\ . \ . \ . \ . \ .$     | 19 |

| 2.5  | Finished mass flow sensor                                                      | 20 |

| 2.6  | Mass flow sensor packages                                                      | 22 |

| 3.1  | Basic process flow of a post-CMOS compatible TSV.                              | 25 |

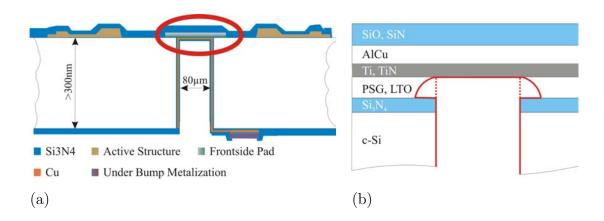

| 3.2  | Pad-cell structure of CMOS devices.                                            | 28 |

| 3.3  | Cross section of mass flow sensor.                                             | 29 |

| 3.4  | Possible TSV geometry at chip corners                                          | 31 |

| 3.5  | Simulation model for determination of wafer stability                          | 32 |

| 3.6  | Displacement and stress dependent on the external load. $\ldots$               | 34 |

| 3.7  | TSV orientations on a wafer                                                    | 35 |

| 3.8  | Principal stresses inside TSV.                                                 | 37 |

| 3.9  | Predicted principal stress for $200\mu m$ thick wafer                          | 38 |

| 3.10 | Cross section of the targeted CSP                                              | 39 |

| 3.11 | TSV model used for thermomechanical analysis                                   | 40 |

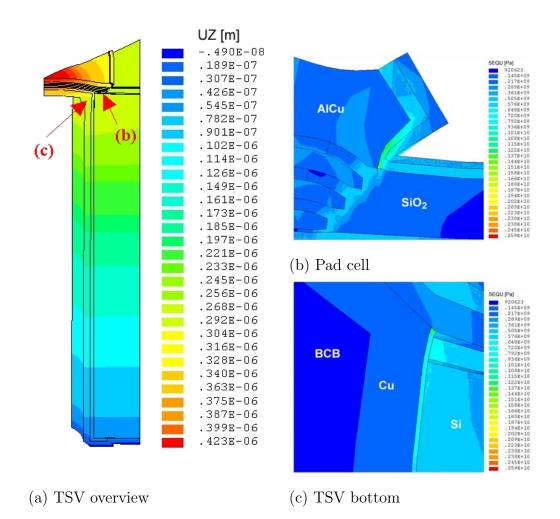

| 3.12 | Displacement and stress distribution of a TSV system during molding. $\ . \ .$ | 42 |

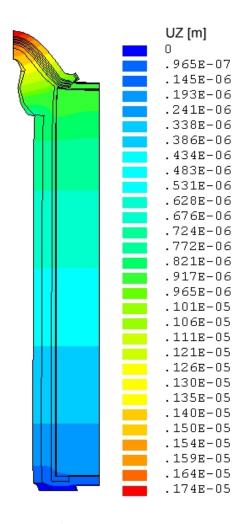

| 3.13 | Pad-cell displacement due to temperature excursion                             | 44 |

| 3.14 | Schematic of the parasitic capacitance in an insulated metal strip             | 46 |

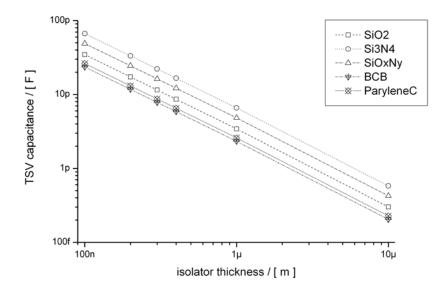

| 3.15 | TSV capacitance dependent on film thickness and isolating material             | 48 |

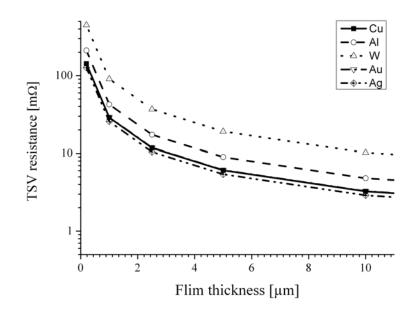

| 3.16 | Electrical resistance values for a ring metallization                          | 50 |

| 3.17 | Pad-cell film stack.                                                           | 53 |

| 3.18 | Test wafer design.                                                             | 54 |

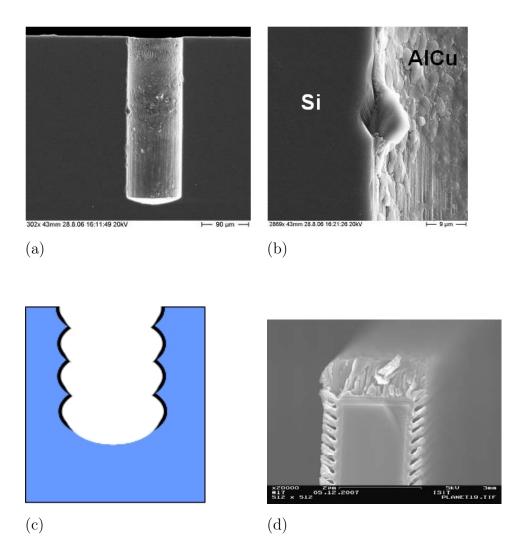

| 4.1  | TSV etch profiles                                                                       |

|------|-----------------------------------------------------------------------------------------|

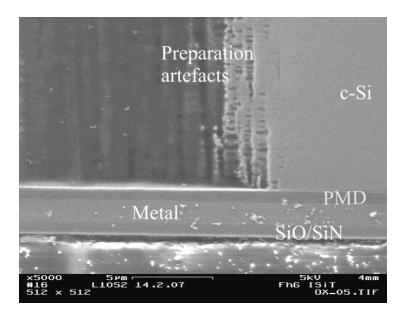

| 4.2  | Cross section of a pad cell after a plasma etch process                                 |

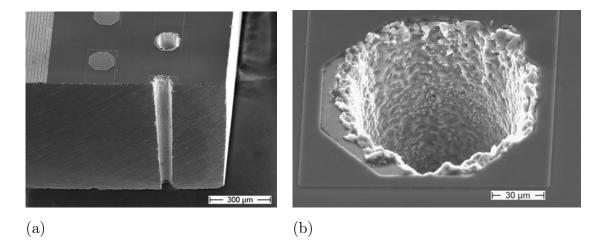

| 4.3  | TSV hole formation by laser ablation                                                    |

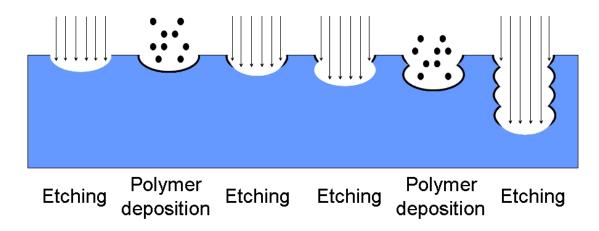

| 4.4  | Etch cycles of deep reactive ion etching (DRIE)                                         |

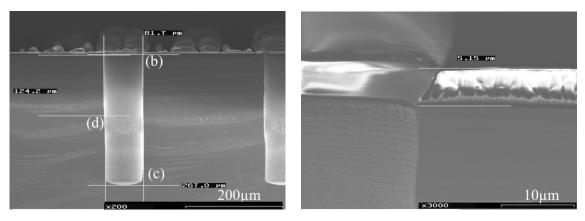

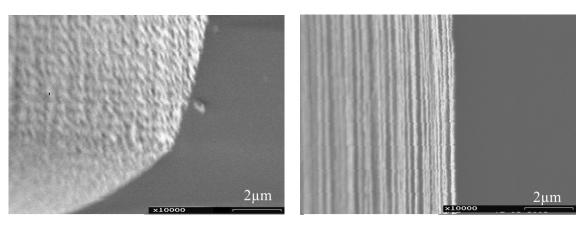

| 4.5  | TSV hole formed by DRIE                                                                 |

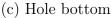

| 4.6  | Maximum possible depth of incoming $SF_6^-$ ions                                        |

| 4.7  | Etched hole from the wafer back-side                                                    |

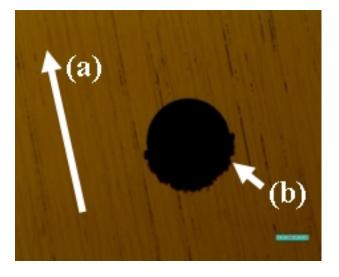

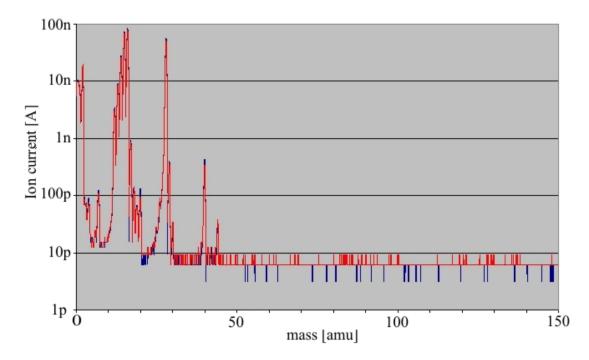

| 4.8  | Outgasing measurement                                                                   |

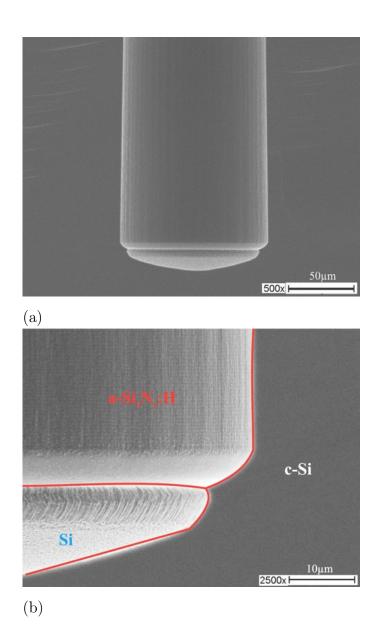

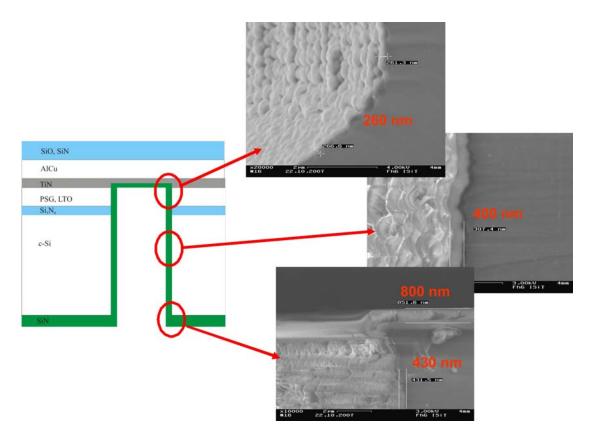

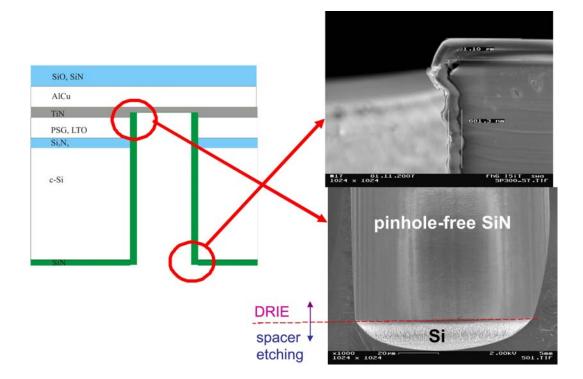

| 4.9  | TSV holes after a:Si <sub>x</sub> N <sub>y</sub> :H deposition and spacer etch          |

| 4.10 | TSV holes after a-SiN:H deposition and KOH immersion                                    |

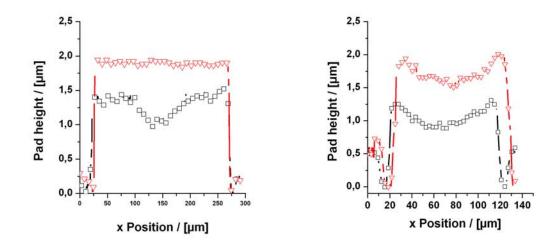

| 4.11 | Pad buckling of a $200\mu$ m and $100\mu$ m wide pad                                    |

| 4.12 | PMD etching by using BOE                                                                |

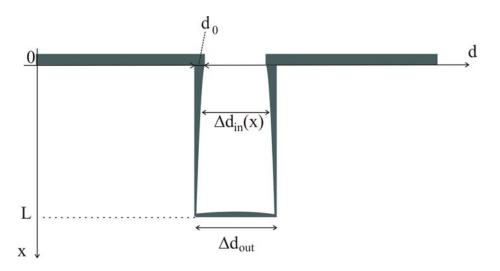

| 4.13 | Geometry aspects of TSV deposition processes                                            |

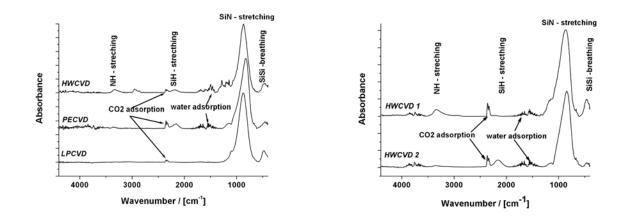

| 4.14 | IR-Spectra of silicon nitride films                                                     |

|      | Silicon nitride film thickness gradients                                                |

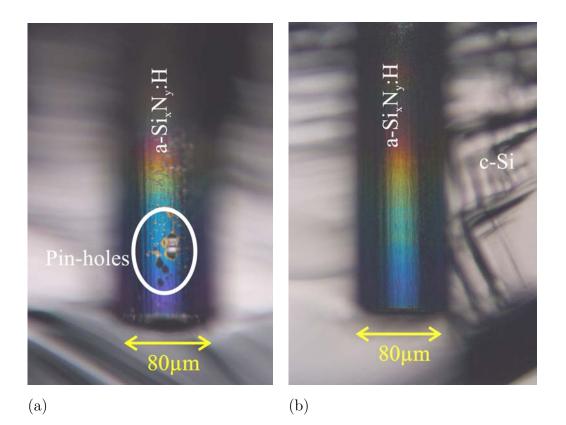

| 4.16 | a-Si <sub>x</sub> N <sub>y</sub> :H films in 300 $\mu$ m deep blind holes               |

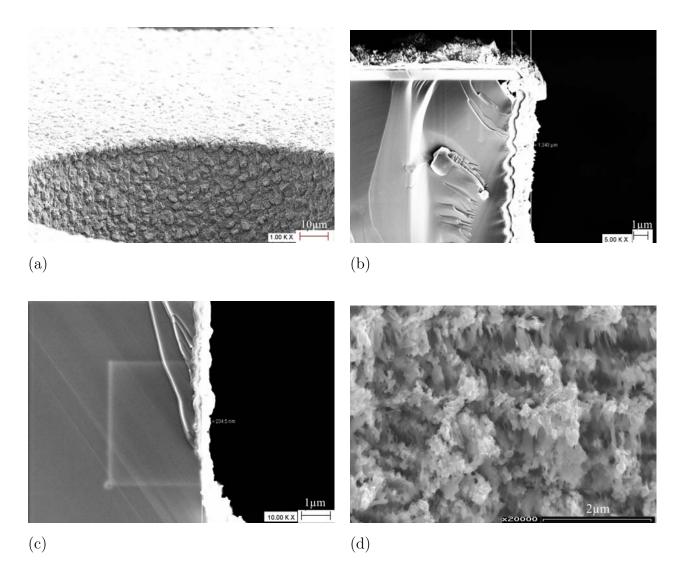

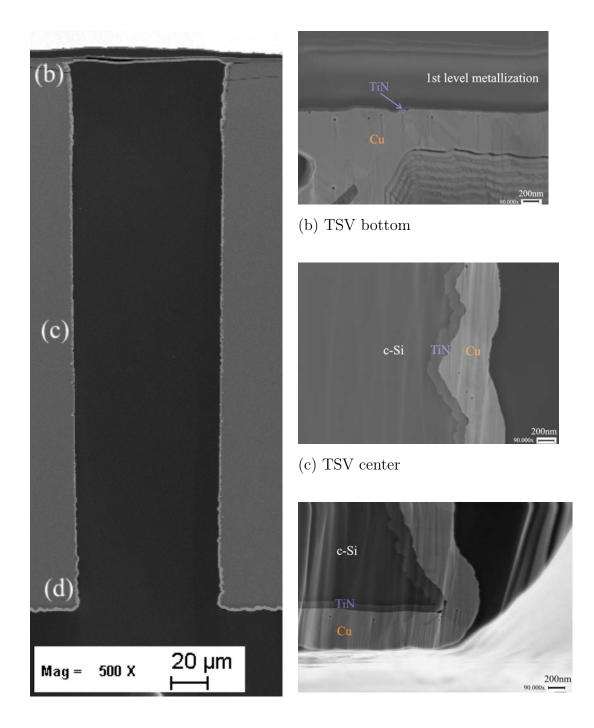

| 4.17 | Metal deposition inside $300\mu m$ deep TSV holes                                       |

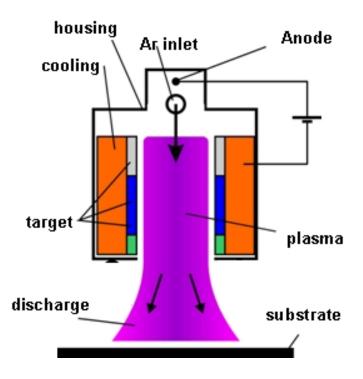

|      | Gas Flow Sputtering arrangement                                                         |

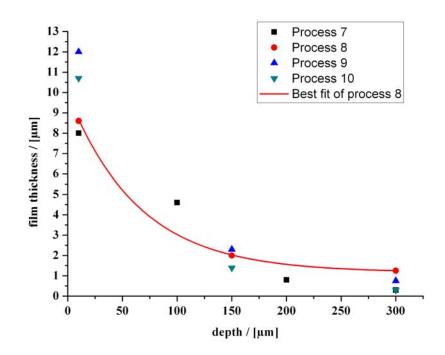

| 4.19 | Cu-film thickness gradients                                                             |

| 4.20 | Cu-film deposition inside TSV geometry by gas flow sputtering 92                        |

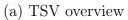

| 4.21 | Al film deposition inside TSV geometry by gas flow sputtering                           |

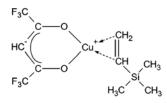

| 4.22 | Chemical structure of CupraSelect $(C_{10}H_{13}CuF_6O_2Si)$                            |

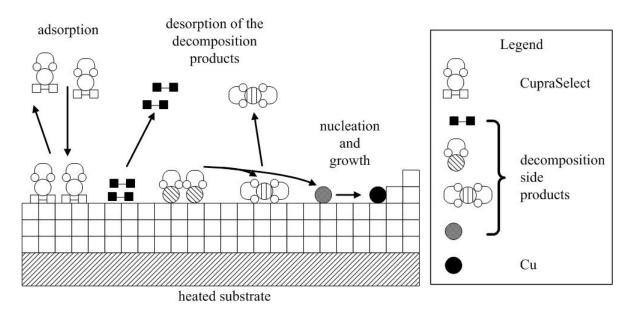

| 4.23 | Reaction model of Cu MO-CVD on surface-sides                                            |

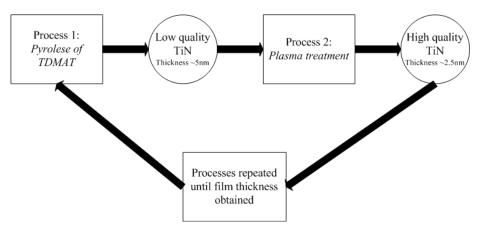

| 4.24 | Process cycle of the TiN deposition by MO-CVD                                           |

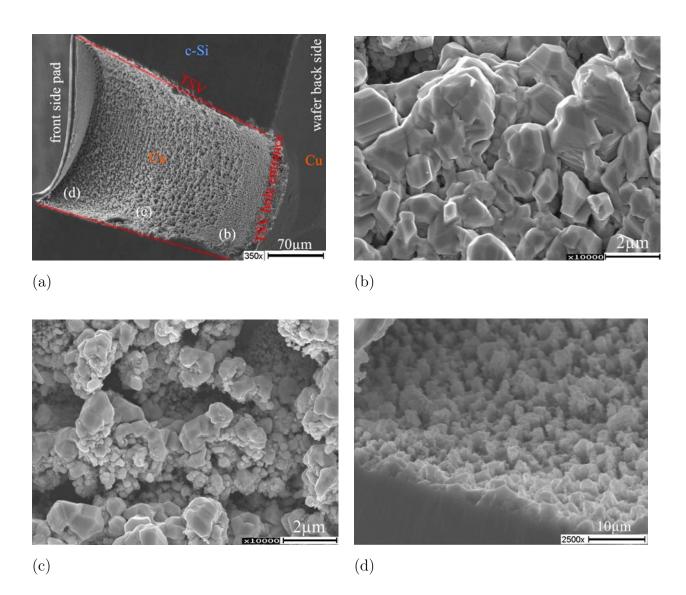

| 4.25 | Deposited Cu film inside the TSV obtained by MO-CVD                                     |

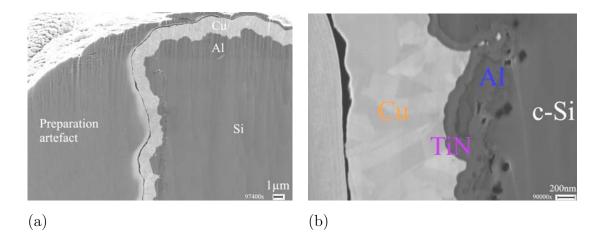

| 4.26 | Surface smoothing by Cu film deposition                                                 |

| 4.27 | Flux rates dependent on the surface location                                            |

| 4.28 | $SiO_2$ layers inside trenches obtained by using tetraethylorthosilicate precursor. 103 |

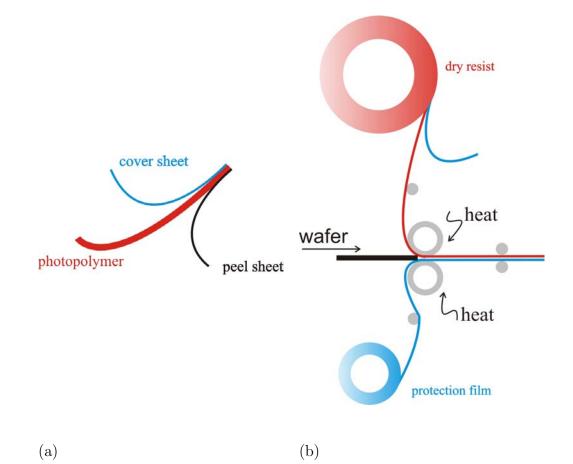

| 4.29 | Photoresist deposition by spin and spray coating                                        |

| 4.30 | Dry photoresist foil and lamination setup                                               |

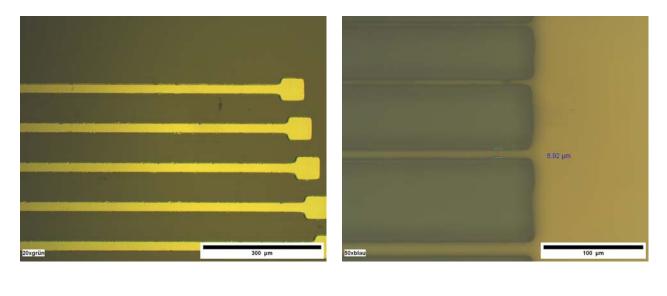

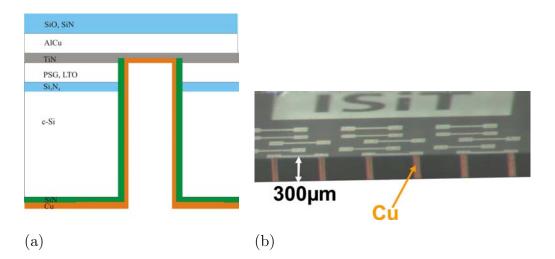

| 4.31 | Pattern transfer in Cu by using dry photoresist foils and PWS 110                       |

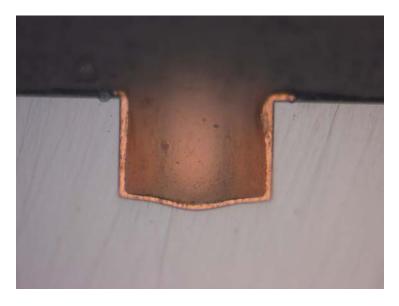

| 4.32 | Cu film inside a $50\mu$ m deep hole after Cu etching and dry photoresist removing 111  |

| 4.33 | Wafer back-side after PWS etching                                                       |

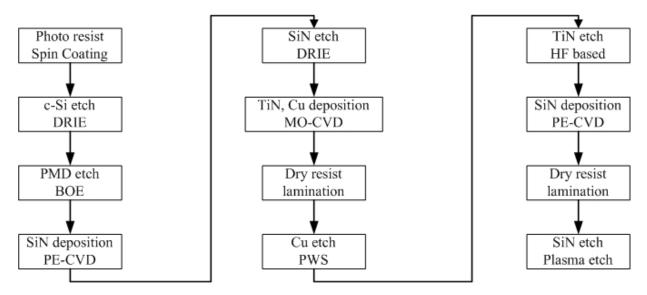

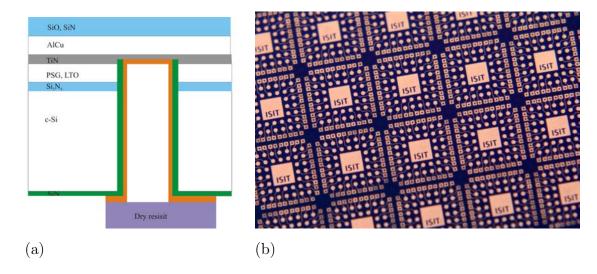

| 5.1  | post-CMOS compatible TSV process sequence                                               |

| 5.2  | Initial wafer state of TSV process flow                                                 |

| 5.3  | Hole formation by etching c-Si and $Si_3N_4$ by using DRIE                 | 116 |

|------|----------------------------------------------------------------------------|-----|

| 5.4  | PMD etching by using BOE                                                   | 117 |

| 5.5  | Isolation deposition by PE-CVD                                             | 118 |

| 5.6  | Etching of the isolation layer by DRIE                                     | 119 |

| 5.7  | Metallization of TSV by using MO-CVD                                       | 119 |

| 5.8  | Redistribution layer on wafer back-side                                    | 120 |

| 5.9  | Anisotropic etching of the isolation layer by DRIE                         | 121 |

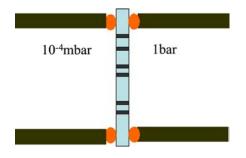

| 5.10 | Experimental setup to control the hermeticity of TSV                       | 121 |

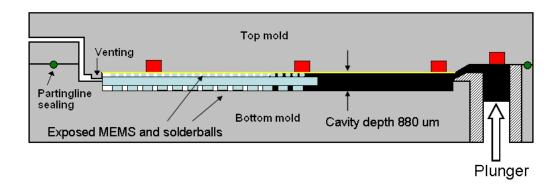

| 5.11 | Experimental Setup for wafer molding                                       | 122 |

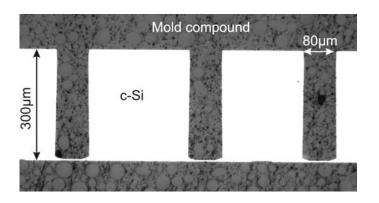

| 5.12 | TSV filled with mold compound.                                             | 123 |

| 5.13 | Redistribution of the metallization in a MEMS devices for TSV integration. | 123 |

| 5.14 | Mass flow sensor with integrated TSV                                       | 124 |

# List of Tables

| 3.2 | Possible TSV profiles                                                                | 30  |

|-----|--------------------------------------------------------------------------------------|-----|

| 3.3 | Principal stresses and z-displacements of $200\mu m$ thick wafers                    | 35  |

| 3.4 | Principal stresses at wafer center and TSV hole entrance                             | 36  |

| 3.5 | Dielectric constant values.                                                          | 48  |

|     |                                                                                      | -   |

| 4.1 | Measured breakdown voltages of isolation layers                                      | 78  |

| 4.2 | Material parameters of a-Si <sub><math>x</math></sub> N <sub><math>y</math></sub> :H | 85  |

| 4.3 | Gas flow sputtering process parameter variation                                      | 89  |

| 4.4 | Adhesion quality of a laminated photosensitive foil.                                 | 109 |

# Table of Abbreviations and Symbols

## Abbreviations

| Abbreviations        | Explanation                                                                 |

|----------------------|-----------------------------------------------------------------------------|

| ASIC                 | Application Specific Integrated Circuit                                     |

| BGA                  | Ball Grid Array                                                             |

| BKIN                 | Bilinear Kinematic Hardening                                                |

| BOE                  | Buffered Oxide Etch                                                         |

| C2C                  | Chip to Chip                                                                |

| CMLS                 | Chip multi-layer stack                                                      |

| CMOS                 | Complementary Metal Oxide Semiconductor                                     |

| CMP                  | Chemical Mechanical Polishing                                               |

| CupraSelect          | Copper-hexa fluoroacety lacetonate-thrimety lviniy lsilane                  |

|                      | $(\mathrm{C}_{10}\mathrm{H}_{13}\mathrm{CuF}_{6}\mathrm{O}_{2}\mathrm{Si})$ |

| CVD                  | Chemical Vapor deposition                                                   |

| $\operatorname{CSP}$ | Chip Scale Package                                                          |

| CTE                  | Coefficient of Thermal Expansion                                            |

| DRIE                 | Deep Reactive Ion Etching                                                   |

| EPMA                 | Electron Probe Micro-Analysis                                               |

| ESD                  | Electro-Static Discharge                                                    |

| DAVID                | Downscaled Assembly of Vertical Interconnects                               |

| GFS                  | Gas low sputtering                                                          |

| GPE                  | Gas Phase Etching                                                           |

| (hfac)Cu(TMVS)       | CupraSelect                                                                 |

| ISIT                 | Fraunhofer Institute for Silicon Technology                                 |

| HW-CVD               | Hot chemical vapor deposition                                               |

| IC                   | Integrated circuit                                                          |

| IMD                  | Inter-metallic dielectric                                                   |

| Abbreviations | Explanation                                                  |

|---------------|--------------------------------------------------------------|

| LP-CVD        | Low Pressure Chemical Vapor Deposition                       |

| LTO           | Low Temperature Oxide                                        |

| MAF           | Mass Flow Sensor                                             |

| MEMS          | Microelectro-Mechanical Systems                              |

| MO-CVD        | Metalorganic Chemical Vapor Deposition                       |

| MOS           | Metal Oxide-Semiconductor Structure                          |

| PCB           | Printed Circuit Boards                                       |

| PE-CVD        | Plasma Enhanced Chemical Vapor Deposition                    |

| PICS          | Passive Integration and Connecting Substrates                |

| PMD           | Pre Metal Dielectric                                         |

| Poly-Si       | Poly-Crystalline Silicon                                     |

| PSG           | Phosphorus Silicate Glass                                    |

| PVD           | Physical Vapor Deposition                                    |

| PWS           | 80% phosphoric acid, $16%$ water, $4%$ nitric acid + tenside |

| SPE           | Silicon Package Efficiency                                   |

| PoP           | Package on Package                                           |

| PiP           | Package in Package                                           |

| RIE           | Reactive Ion Etching                                         |

| SOI           | Silicon on Isolator                                          |

| SiP           | System in the Package                                        |

| TDMAT         | Tetrakisdimethylaminotitan                                   |

| TEOS          | Tetraethylorthosilicate $C_8H_{20}O_4Si$                     |

| TSV           | Through Silicon Vias                                         |

| W2W           | Wafer to Wafer                                               |

|               |                                                              |

## Symbols

| Symbol                   | Explanation                                                                         |

|--------------------------|-------------------------------------------------------------------------------------|

| α                        | TSV hole slope [°]                                                                  |

| $\epsilon$               | Permittivity $[F m^{-1}]$                                                           |

| $\epsilon_{Isolation}$   | Relative permetivity of the isolating material inside the TSV $[1]$                 |

| $\epsilon_0$             | Dielectric constant $8.854 \cdot 10^{-12} \mathrm{F m}^{-1}$                        |

| $\lambda$                | $\frac{1}{\tau}$ [m <sup>-</sup> 1]                                                 |

| ν                        | Vibration frequency of an atom on the surface [Hz]                                  |

| ρ                        | Specific electrical resistivity $[Sm^{-1}]$                                         |

| $\sigma$                 | Principal stress [MPa]                                                              |

| au                       | Film thickness when $63\%$ of the decay is reached [m]                              |

| $	au_s$                  | residence time [s]                                                                  |

| $\theta$                 | Angle variation of the incoming flux [°]                                            |

| ω                        | impinge rate $[m^{-2}s^{-1}]$                                                       |

| a                        | Safety distance between chip corner and TSV hole edge [m]                           |

| $A_{Isolation}$          | Surface area of the insulating material inside the TSV $[m^2]$                      |

| b                        | Backside chipping [m]                                                               |

| с                        | Distance between pad corner and dicing line [m]                                     |

| $\mathbf{C}_{Depletion}$ | Semiconductor depletion-layer capacitance [F]                                       |

| $C_{TSV}$                | TSV capacitance [F]                                                                 |

| d                        | TSV contact opening [m]                                                             |

| $d_0$                    | Initial film thickness of the isolating material at the $\mathrm{TSV}$ hole orifice |

|                          | [m]                                                                                 |

| $E_{Des}$                | Desorption energy [J]                                                               |

| $\mathbf{F}_i$           | Material flux $[m \ s^{-1}]$                                                        |

| L                        | TSV hole depth [m]                                                                  |

| $\dot{N}$                | Nucleation rate $[m^{-3} s^{-1}]$                                                   |

| $N^*$                    | Equilibrium concentration of stable nuclei $[\rm cm^{-3}]$                          |

| $N_B$                    | Bulk concentration of dopants $[cm^{-3}]$                                           |

| $\mathbf{n}_i$           | Intrinsic carrier concentration $[cm^{-3}]$                                         |

| k                        | Boltzmann constant 1.3807 $\cdot~10^{-23}~{\rm J/K}$                                |

|                          |                                                                                     |

| Symbol                 | Explanation                                                        |

|------------------------|--------------------------------------------------------------------|

| q                      | Elementary charge [C]                                              |

| $\mathbf{R}_{Barrier}$ | Barrier resistance $[\Omega]$                                      |

| $\mathbf{R}_{Bottom}$  | TSV hole bottom resistance $[\Omega]$                              |

| r <sub>in</sub>        | TSV hole radius subtracted by the isolating film thickness [m]     |

| $\mathbf{R}_{Metal}$   | TSV metallization material resistance $[\Omega]$                   |

| $R_{Ring}$             | Ring metallization resistance $[\Omega]$                           |

| r <sub>out</sub>       | TSV hole radius [m]                                                |

| r(x)                   | $\mathbf{r}_{in}$ in dependence of the film thickness gradiend [m] |

| $\mathbf{S}_C$         | Sticking coefficient [1]                                           |

| Т                      | Temperature [K]                                                    |

| $T_M$                  | Melting temperature [K]                                            |

| $t_{Isolation}$        | Isolator thickness [m]                                             |

| $\mathbf{u}_{z}$       | z-displacement [m]                                                 |

| V                      | Bias voltage [V]                                                   |

## 1 Integration of Through Silicon Vias (TSV) in MEMS

The number of electronic devices available on the market is increasing. In addition they are becoming more complex and the demand for smaller devices is increasing. For instance, a cellular phone in 1990 weighed around 2.4kg and was approximately 25cm by 17cm by 8cm. Today's smallest cellular phone weighs only 55g and is 5.7cm by 2.1cm by 1.3cm. One can perform office applications, take pictures or even browse the Internet in addition to placing a call. In order to keep the requested higher system performance the transistor density inside the electronic device must increase. Gordon Moore predicted 1965 that the implemented transistors on a chip would roughly double every two years [1], whereas the device size should remain the same. This prediction is called 'Moore's Law'.

The conduction line width and the spacing between two conduction lines are important in order to maximize the transistor density. The first integrated circuits were produced with a line width of  $25\mu m$  ( $25\mu m$  node) [2], whereas the present processor generation is fabricated in the 32nm node [3]. This change in the node allows placement of several thousand transistors effectively increasing the transistor density. The fabrication technologies used must be improved in order to realize a change between the nodes. Technological solutions to change technology nodes were found despite enormous investment cost. Nevertheless, Thompson et al. have shown that the transistor costs decreased by seven order of magnitudes from 1970 to 2000 despite an increase of the investment costs [4]. A chip production with a high throughput and yield is still economically useful in big foundries. Moore's Law can be followed up probably straight forward for another decade by decreasing the line width [5]. Physical device limits are reached if the line width size reduction is continued [6]. For instance, the electron mobility inside the metallization is reduced in smaller conduction lines due to a higher surface scattering. The device performance will be limited in the future. Other ways of increasing the transistor density must be found in order to follow the demand of higher system performances.

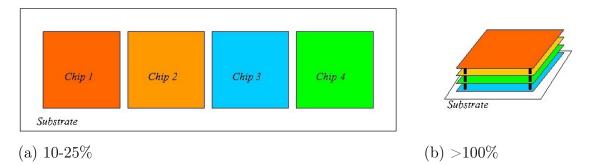

G. Moore predicted 2001 that there is certainly no end of technological creativity to follow Moore's law in the future [5]. New technologies like multi-gate transistors are under development [7], but there are still issues regarding the quality and reliability. There are so far no technological solutions to solve this problem during the chip fabrication. Therefore, the process flow must be changed after the fabrication of the chips in order to increase the transistor density. A change of the system architecture solves this problem. The electronic devices are placed next to each other in actual system designs and require a large foot print on the electronic board. A 3D integration allows a reduction of the foot print by the number of stacked devices. Memory stacks of eight dies are realized and will be commercialized in the near future [8]. A stack of different devices allows a spreading of "Moore's Law", because different devices can be placed on top of each other and improve the system performance. Figure 1.1 shows a comparison of a conventional lateral and 3D integration of four dies in respect to the required board.

Figure 1.1: Lateral and 3D integration approaches.(a) Lateral chip integration (b) 3D integration approach of four electronic chips on a substrate. The given SPEs are typical values of each approach.

The silicon packaging efficiency (SPE) describes quantitatively how many chips are placed on a certain board area. The SPE is given by the ratio of the silicon area used for all implemented chips in respect to the required board area

$$SPE = \frac{\sum_{i} Si \, Area_{i}}{Board \, Area} \tag{1.1}$$

Figure 1.1 shows typical SPE values of the integration approaches. This definition allows SPE-values above 100% for multi stacks. Different integration approaches are possible with vertical interconnects. The Chip-to-Chip technology (C2C) describes a stacking of two or more distinct chips. High system flexibility is possible, because different chips can be assembled at certain stack levels. This technology is called Chip-to-Wafer (C2W), if the first layer is replaced by a wafer. A high yield processing is possible for C2C and C2W, because only functional chips or wafers are used. International research projects like the European Union founded project "Downscaled Assembly of Vertical Interconnect Devices" [9] are developing key technologies for these stacking approaches. A stacking of complete wafers (W2W) is an other way to increase the system density. The system flexibility is limited, because only wafers of the same size and chip type are possible to stack with this W2W technology. Samsung has shown stacks of eight memory dies with this technology [8] as mentioned before.

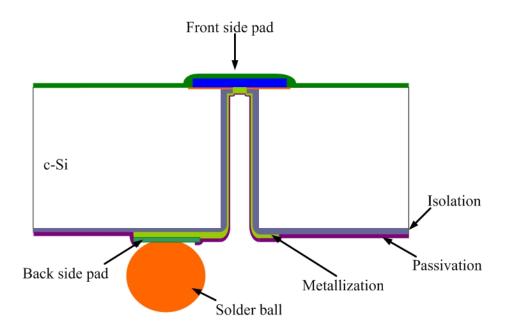

Vertical interconnects, also called through silicon vias (TSV) [10], are the key element in all described 3D integration approaches. TSV connect the front-side and back side of a wafer by a hole etched through the wafer and subsequent deposition and structuring of suitable films (isolation, metallization and passivation) as shown in figure 1.2. This configuration allows not only better SPE values, but improvements in the

- Electrical performance

- Power consumption

- Noise generation

- Functionality

Figure 1.2: Basic concept and elements of a Through Silicon Via.

The electrical resistance, capacitance and inductance (parasitic effects) of TSVs are lower compared to wire bond based packages. For instance, the electrical resistance of the wire bond is ten times higher than comparable TSV [11]. The signal propagation time between two devices such as a microprocessor and a memory is shorter in vertical stacks. In addition, systems with a high data transfer between components can change from sequential (through bond wires) to a parallel (through TSV) signal processing and improve the real time performance of the system [12]. Camera sensors (imagers) and memory devices are the drivers for TSV development, because both applications require fast processing of numerous data. Both devices allow a wafer thinning, which reduces also the parasitic effects and simplifies the TSV fabrication. The required technologies for the TSV fabrication like etching or metal deposition are easier to perform for  $<50\mu$ m deep TSVs compared to TSV for full thick wafers.

Micro-electro-mechanical systems (MEMS) gain also from TSV integrated inside their packages. The MEMS concept is based on the realization of devices in which electrical and mechanical components are integrated within a single silicon chip. Systems like sensors, actuators, power producing devices, chemical reactors and biomedical devices are realized on this concept by using a high volume production based on established technologies of the microelectronics industry. Actual MEMS packages like shown in Figure 1.3 are based on wire bond processes between the MEMS, ICs and lead frames, respectively. This arrangement consumes large areas on electronic boards. A preferable approach is a direct placement of the MEMS on top of the IC. Figure 1.3 shows that the sensor chip is much smaller then the IC. This size mismatch allows a placement of several sensor chips on top of the IC, if the IC operating capacity is large enough to handle several sensor signals. A maximum number of MEMS is placeable if TSV are integrated inside MEMS. The placing accuracy of the bond tool defines the distance between two MEMS and therefore the package density or the SPE value. A proper connection between all MEMS and the IC requires a planarization of the IC topography and an implemented redistribution layer. An additional TSV integration inside the IC increases also the SPE value. A solder ball process on the IC wafer back-side and a molding process create a compact ball grid array package (BGA) of an multi sensor module. Literature calls this stacking approach also "More than Moore" [13].

In addition, TSV enhance MEMS performance in several designs. For instance, capacitive operating devices like accelerometers are sensitive for parasitic effects caused by connection wires. The electrical parasitics are minimized by a TSV implementation as mentioned earlier [11]. Mass flow sensors for liquid or gaseous medias are a second example which implies a better system performance by a TSV implementation. The flow sensor functionality is described in chapter 2.2.4. The actual sensor design from the Fraunhofer Institute for Silicon Technology is connected by wire bonds with the electronics. Wires and the complete interconnect area are covered by an organic protection material (globtop). Sensor structures and the protected interconnect area are in a direct connection with the media investigated during measurements. A diffusion of the media investigated between

Figure 1.3: MEMS package of an inertial measurement unit (Source: SensorDynamics).

the globtop and the substrate was observed during field tests resulting in bond pad corrosion. Thus, measurements of liquid and gaseous media prefer a separation of active MEMS sides and interconnect areas [14]. Connection pads formed on the wafer back-side are protected from the media investigated and a possible corrosion is eliminated. Figure 1.4 shows schematically a TSV integration in mass flow sensor.

Figure 1.4: Example of Through Silicon Vias in a MEMS package, which allows an operation in harsh environments without a direct contact of the interconnects with the media investigated.

Wafer thicknesses of  $<50\mu$ m would change the performance of MEMS significantly due to their high sensitivity to bending stress effects . These effects will even increase with decreasing the wafer thickness. Thus, MEMS require a TSV implementation in thick wafer (> 300 $\mu$ m). Different fabrication technologies and process sequences are necessary for a TSV integration in MEMS packages compared to TSV for electronic devices like memories.

### Aim of the thesis

The previous paragraph showed the requirements of new packaging technologies in order to follow the demand of higher transistor densities in new devices. 3D stacking and thinning of chips allow an integration of several devices by using small foot prints. Through Silicon Vias (TSV) are key elements inside these new technologies. Several approaches were developed or investigated for integrated circuits (IC). The functionality of MEMS is increasing by TSV integration inside MEMS-packages. The challenges of TSV integration approaches in MEMS packages are different compared to TSV in IC and can be summarized as followed:

- MEMS are stress sensitive. Wafer thinning changes the MEMS device performance. Thus, TSV must be integrated inside wafer with a full wafer thickness or in moderately thinned wafers (>  $300\mu m$ ), whereas pad sizes of  $100\mu m$  are common. The required processes or process parameters for these TSV geometries in MEMS are not comparable to processes used in TSV approaches for IC. In addition, TSV integrated in hybrid chip scale packages (CSP) of MEMS chips and ASIC wafer require a TSV implementation in IC wafer. Wafer molding of the CSP must be performed during the assembly and puts the system under high pressures. TSV structures inside the IC must resist these forces. Thus, thick IC wafers should be targeted in order to increase the reliability of TSV and consequently of the CSP.

- Several MEMS like resonant sensors require vacuum environments for their proper functionality. The process flow must be designed in such a way that no open holes are created during processing. TSV formed in MEMS packages must show a hermetic barrier against several gases or liquids during device lifetimes.

Some requirements for TSV in IC are also valid for MEMS packages. The core challenges are:

- Maximum process temperatures used are limited by the IC itself. IC metalization layers are commonly AlCu or AlSiCu. A chemical reaction between theses materials and the Si substrate can arise at process temperatures above 400°C. A development of a post-CMOS compatible TSV process sequence results from this temperature specification.

- Some devices are sensitive regarding parasitics effects like the electrical resistance of the TSV formed. A small electrical resistance of the TSV should be targeted for MEMS.

These specific requirements for a TSV integration in MEMS packages define the aim of the thesis:

Development and characterization of fabrication technologies for an integration of hermetic Through Silicon Vias in MEMS packages where post-CMOS compatible processes are used.

### Structure of the thesis

The thesis is divided in four major parts. The first part explains basic concepts for a 3D integration of chips based on existing packaging technologies and possible TSV implementation in IC. Existing TSV approaches in MEMS packages are presented and possible TSV approaches for MEMS packages at the Fraunhofer Institute for Silicon Technology are discussed.

The second part shows specification for the TSV targeted. Functional elements of the TSV are discussed and a test design for the TSV development is presented.

The third part evaluates fabrication technologies required for the TSV development. Common IC and MEMS technologies are shown and their applicability for post-CMOS compatible TSV is evaluated.

The fourth part shows a process sequence for a TSV integration in MEMS packages. Implementation aspects of TSV in a CSP package and in a mass flow sensor are discussed. Lastly the thesis is summarized and an outlook of further work for a TSV implantation in MEMS packages is given.

## 2 3D advanced packaging

### 2.1 3D packaging

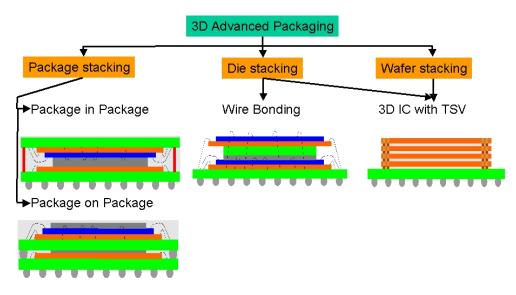

Packaging is an key technology in all fields of micro-electronics and MEMS. Devices need always an electrical connection path to other elements. Different techniques like wire or flip chip bonding were developed and are commercially used. These techniques are based on a lateral device placement on substrates. The combination of devices placed and the electrical connection paths between these devices form functional systems. This arrangement is characterized by silicon package efficiencies (SPE) of  $10\% \dots 25\%$ . A 3D placement of chips on top of each other allow higher SPE values.

Chip stacking began with mounting of smaller chips onto larger chips. This first approach of increasing SPE-values on chip level was limited due to system and tool complexity. Bond wires provide the electrical paths between chips and boards. Routing of these bond wires between chip levels is challenging especially for those chips with high interconnect densities. In addition, chip sizes in higher levels must be smaller compared to lower levels. Thus, the system flexibility is limited by chip geometries. Chip arrangements like shown in Figure 2.1 (Die stacking) are not always possible for systems targeted. A placement of larger chips on top of smaller chips requires an implementation of passive chips (interposer chips). The vertical distance between two chips increases by the implementation of these interposer chips, which allows the use of bond wires for interconnect purposes between two layers. This 3D integration approach needs larger interposer chip thicknesses compared to bond loop heights. Chip multi-layer stacks (CMLS) have been archived using these variations and are now available in high-volume productions.

Package stacking is a second way to increase SPE-values. Two or more CMLS are stacked on top of each other and form a new package in this 3D stacking technology. Connectors recognize the electrical conduction paths between stacking level. Each CMLS is tested before finally assembled. This testing allows high system yields and low cost production of high-volume products even when additional costs for connectors increase. Figure 2.1 shows two different package assembly methods. Package in a package (PiP) assemblies use a face to face orientation between two CLMS and a back to face orientation is used for package on package (PoP) architectures. The described approaches have the following disadvantages:

- All presented 3D stacks are based on wire bonds. Typical electrical resistances of bond wires are in the range of  $150m\Omega$ . This value is too high for several modern systems. It is not possible to obtain a fast signal propagation.

- Final packages are molded before they are used as an electronic device on electronic boards. Package molding introduces stress to wire bonds and the reliability risk increases during the device life time.

- Chips (silicon) and adhesive bond materials (organic based) have linear thermal expansion coefficients of  $2 \cdot 10^{-6} K^{-1}$  and  $60 \dots 100 \cdot 10^{-6} K^{-1}$ , respectively. This mismatch puts thermal stress on the system and operating temperatures are limited.

Figure 2.1: Advanced 3D stacking technologies. The text describes the technologies in detail.

### 2.2 Through Silicon Vias

Vertical interconnects through chips, also called Through Silicon Vias (TSV), can overcome the described problems in chapter 2.1. Basic concepts for packages with TSV will be discussed in chapter 2.2.1. However, TSV must have simultaneously several advantages over CMLS and package stacking technologies before semiconductor vendors change their chip assembly. Key factors for a possible technology change are summarized below and the advantages of TSV are discussed [12].

- The electrical performance is driven by the gate and interconnect delay at chip level. Interconnect delays (RC-delay), which are given by interconnect wires between transistors, device pads and bond wires, dominate in actual technology nodes used compared to transistor gate delays due to small gate dimensions of modern technology nodes. RC-delays decrease by TSV integration, because the interconnect length is shorter in TSV based packages compared to wire bond based packages. Linder showed that electrical resistances of TSV are 10 times smaller compared to similar wire bonds [11].

- Interconnect wires consume a significant portion of the electrical power. The power loss is reduced by TSV, since TSV shortens interconnect lengths. In addition, shorter wires reduce noise, which allows handling of low signal levels.

- Modern applications have a higher demand to integrate more functions in one device. In addition, package footprints should not be changed or even be reduced. Stacked chips reduce foot prints on boards by the number of stacked levels. The SPE increases to values above 100% by TSV integration.

- The access time between logic devices and memories is the bottleneck in several modern devices. The limited number of bond wires does not allow a parallel processing of all data between these two devices. The sequential data transmission, which is alternatively used, reduces the system performance. TSV allow a parallel processing between the two devices and the system gains functionality.

#### 2.2.1 Concepts

TSV based 3D-integration approaches are divided in a prearrangement of the substrate, the TSV fabrication itself and a final assembly in a package. Technologies used are mostly independent from the developed concepts. First, wafer thinning is performed depending on the concept after the TSV formation or beforehand (wafer prearrangement). A hole is formed inside the wafer and is followed by a subsequent deposition of an isolation and metallization layer. Processes needed are discussed in chapter 4. Wafers or chips with integrated TSV are aligned to each other and bonded in a final assembly step.

Developed TSV concepts use different process flows. A simultaneous processing of TSV and IC structures is a first method of TSV integration. No temperature limits arise for processes used, because TSV are integrated before metallic layers are present. Process temperatures above 400°C result in a reaction of the metal used (mostly Al) and the substrate (Si). Fabricated TSV with a maximum process temperature used of 400°C are also called *post-CMOS TSV*. Thus, the electrical conducting material is doped poly-crystalline silicon (Poly-Si). Poly-Si shows a higher electrical resistance compared to metals, which limits the application area of this technology. However, research groups and companies have developed process flows for this TSV technology.

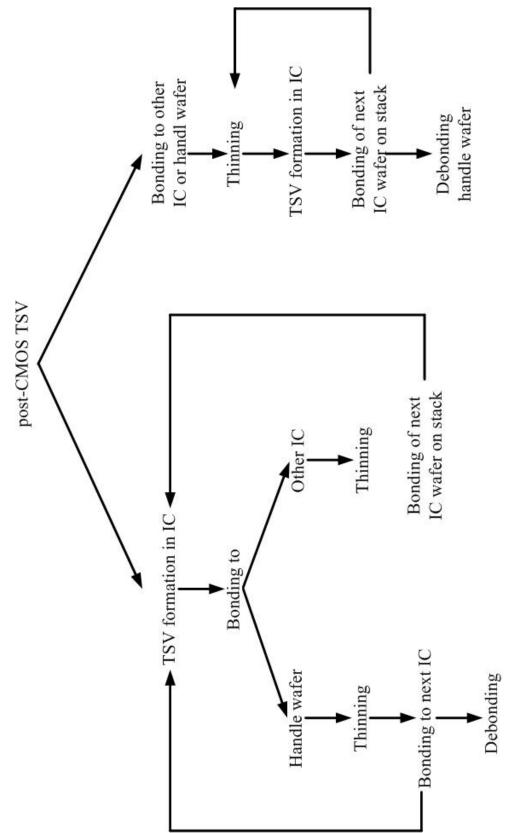

Garrou and Bower [15] discuss several post-CMOS TSV process sequences. They divided the technologies in "pre via" and "post via" sequences. TSV are formed in IC wafer before a thinning and bonding to other IC or handle wafer in "pre via" approaches. Wafers are first bonded to handle wafers and thinned before TSV are implemented in "post via" flows. Figure 2.2 shows an overview of different TSV technologies. Detailed process flows are shown in figure 2.3. Garrou and Bower show a total of nine different TSV approaches. Kröninger [16] and Joly [17] show summaries about wafer thinning and bonding technologies, respectively. These processes are not in the scope of this thesis.

#### 2.2.2 Commercial Activities

Imager chips and memories are key drivers of TSV developments. The demand of imaging devices (imager) has increased during the last decade due to the integration of cameras in cellular phones. Only conventional CMLS packages are used in camera packages so far, because the sensing side of imagers must be oriented to the outside of the package. Sanyo and Toshiba introduced a glass wafer bonding to the active imager side [18]. The glass wafer was used as a handle wafer during TSV processing and was afterwards a part of the camera package.

First, Toshiba bonded imager wafers to glass wafers by using organic adhesives. Then, imager wafers are thinned with standard back-grinding and polishing processes to thicknesses around  $100\mu m$ . TSV holes were formed by laser ablation. A  $15\mu$ m thick organic isolation was deposited and opened only at the hole bottom also by laser ablation.  $10\mu$ m thick Cu liners formed the metalization layer.

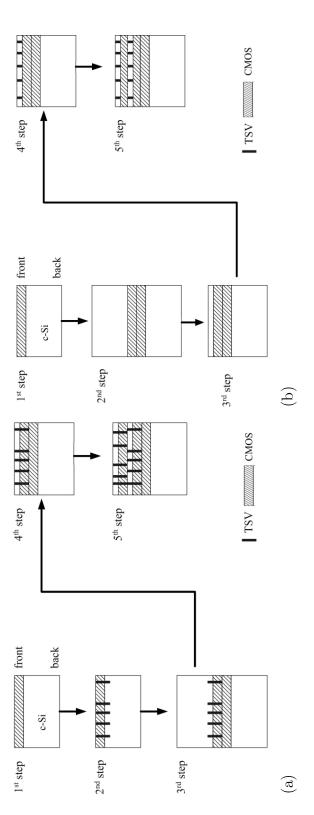

Figure 2.3: Examples of post-CMOS TSV integration approaches (redrawn from [15]).

Face to face bonding to a second IC;  $4^{th}$  step: wafer thinning and back side processing;  $5^{th}$  step: Back to Face (a)  $1^{st}$  step: The sequence starts with a fabricated IC;  $2^{nd}$  step: TSV are formed from the front side;  $3^{rd}$  step: bonding of other IC like  $3^{rd}$  and  $4^{th}$  step.

(b)  $1^{st}$  step: The sequence starts with a fabricated IC;  $2^{nd}$  step: Face to Face bonding to other IC;  $3^{rd}$  step: wafer thinning and back side processing;  $4^{th}$  step: TSV fabrication from wafer back side. This approach stops at the first metalization level of the IC;  $5^{th}$  step: Back to Face bonding of other IC like  $3^{rd}$  and  $4^{th}$  step. Sanyo used different technologies and materials for a similar TSV process sequence. Wafer thinning was performed in the same way as the Toshiba's approach. Holes were formed by physical etching of Si. An inorganic isolator  $(SiO_x)$  was deposited twice in order to maintain the required film thickness. The isolator was opened by an anisotropic etching of the isolator. A seed and barrier layer was deposited inside the holes and on wafer backsides followed by a  $5\mu$ m thick Cu-liner. Other companies have developed similar sequences for TSV in imager wafer [19][20].

The space is limited in new applications like cellular phones, whereas the same or even more data must be processed. Several memory producers develop memory stacks based on TSV in order to solve this problem. Samsung was the first company which announced in 2006 that they had developed a TSV technology for NAND flash memories. A memory stack of eight memories was shown in [8]. They showed in 2007 that their TSV technology was transferable to DRAM memories [21]. The foot print of TSV based memory stacks is 15% smaller compared to conventional packages and the stacks are 30% thinner compared to wire bond solutions [18]. Cellular phones are potential markets for these memory stacks made to height limitations inside the phone. Holes were formed by laser ablation and completely filled with Cu. Wafers were bonded to a carrier wafer before thinned to  $50\mu$ m and an etch back exposed the deposited Cu. Wafers with the same dimensions and chip sizes were bonded on top of the exposed Cu.

Other companies like Tezzaron & Chartered, Micron and NEC are also developing TSV technologies [18]. NEC used a via first technology. A passivation and Poly-Si were deposited in holes with diameters of  $2\mu$ m and a depth of  $50\mu$ m. This hole dimensions allowed a fast and complete filling with Poly-Si. Chemical mechanical polishing (CMP) provided a smooth surface for subsequent memory fabrication.

IBM [22] and INTEL [23] introduce TSV in their next generation of microprocessors or wireless communication devices. Latency times between microprocessors and memories was Intel's driver for their TSV development. TSV reduce this time as mentioned before. Their approach was based on a via last sequence. Intel's TSV have a diameter of approximately  $5\mu$  and a depth of  $10\mu$ m. Lower power consumption in TSV based packages is a driver for IBM. A detailed TSV process flow of IBM is up to now not known.

NXP implemented TSV in passive integration and connecting substrates (PICS) [24]. Different devices were bonded in a C2W process on both sides of PICS in order to overcome size mismatches. Signal routing between devices was achieved through lateral and vertical (TSV) interconnections. This 3D integration approach was also called interposer-wafer approach. PICS allowed also an integration of passive components like resistors and capacitors (RC-elements) close to devices like microprocessors by forming these elements directly on the interposer wafer. RC-elements are required to stabilize device functionalities or set certain device parameters. The interconnect length in CMLS architectures is much longer compared to these interposer solution. In addition, the fabrication technologies of available SMD RC-elements show variances up to 20%. IC technology processes have a much better process robustness and minimize the value variation. Thus, systems based on this PICS technology gain performance and the SPE value increases.

#### 2.2.3 TSV in MEMS packages

Micro-electromechanical systems (MEMS) benefit from TSV, too. Several MEMS devices measure capacitance variations. The signal level is relatively low and is noise sensitive. The parasitic capacitance resulting from interconnects is reduced by using TSV. In addition, a better signal to noise ratio is predicted [12]. Process sequences for TSV in MEMS devices are not comparable to TSV in IC devices like shown in previous chapters. Wafer thinning during the TSV fabrication is limited due to the stress sensitivity of MEMS. The MEMS functionality changes by stress introduced by wafer thinning.

SINTEF introduced TSV in cap-wafers, which are mandatory for resonant working MEMS due to their vacuum requirement (see also chapter 2.2.4). Holes were formed through the entire wafer and a 1 $\mu$ m thick thermal oxide was grown afterwards. Poly-Si was deposited by LP-CVD on both wafer sides simultaneously and doped in the gas phase with phosphorus. The electrical resistance of these TSV formed were in the order of 5 to 15  $\Omega$ . Deposited Al on both wafer sides improved the contact to the Poly-Si. Al and Poly-Si are patterned by dry etching using dry resists. This process sequence of a TSV formation in a cap wafer allowed a hermetic capsulation of the MEMS [25]. In addition, they placed a logic device on top of the cap wafer by conventional wire bond processes.

Heschel et al formed only one hole by wet etching (KOH) and patterned Al inside this cavity. He called this Si-wafer an intermediate structure. MEMS and IC's were bonded to this intermediate structure subsequently [26]. Kutchoukov et al presented a similar intermediate structure [27]. Linder showed the capability of wet etched cavities for TSV and presented a comparison between wire bond based packages with equivalent TSV [11]. Silex prearranged Si-wafers before MEMS are fabricated. Highly doped Si wafers were used as substrates. Dry etched cylindrical or rectangular rings defined the TSV structure. The rings formed were completely filled with an isolator. A final CMP process defined the Si surface on which MEMS can be fabricated. A metallic redistribution layer on the MEMS wafer back-side allowed solder balling to substrates or bonding directly on top of logic devices [28]. The doping level defines the electrical resistance of the TSV formed. Lin et al presented TSV in silicon on isolator (SOI) MEMS. MEMS layers were deposited and structured but not yet released. Holes of a diameter up to  $300\mu$ m were formed by laser ablation through the entire wafer. A thermal oxide was grown for isolation purposes. This SOI wafer was glued to a handle wafer, on which a metallic seed layer was already deposited. Then the hole was completely filled by a metal electroplating process in a so called bottom up process. A back-side contact was also formed by electroplating after the handle wafer was removed [29]. This approach allows similar to the Silex approach a high SPE value and short interconnects. A value of the electrical TSV resistance was not reported.

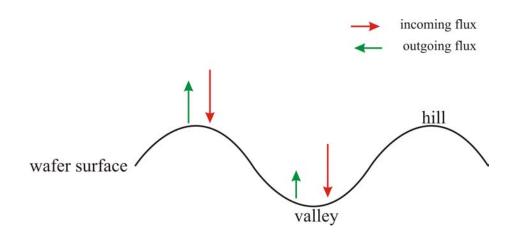

Rasmussen presented a TSV process flow for use in hearing aids [30].  $100\mu$ m wide and  $380\mu$ m deep holes were formed through the entire wafer by wet etching or dry etching.  $5\mu$ m of Parylene was deposited in the gas phase and was used as isolation material. A TiN (200nm), Cu (1 $\mu$ m) metalization was deposited by metal organic CVD and patterned by wet etching using electrophoretic resists. An electrical resistance value of 160m $\Omega$  was obtained. TSV formed by this process flow are not hermetic.

#### 2.2.4 Application examples

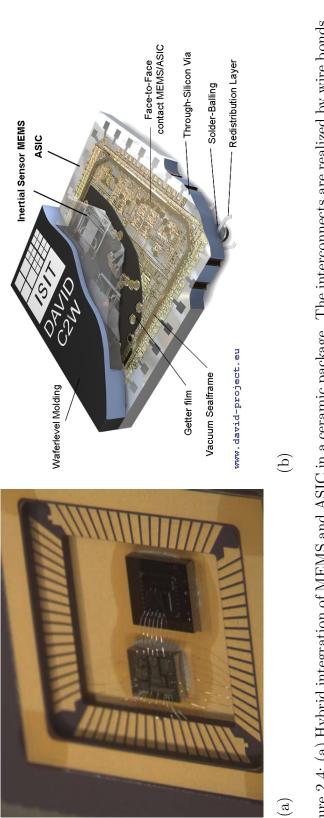

**Example A** Several MEMS modes of operation require vacuum environments. Resonant oscillating structures do not work under ambient atmosphere due to a high damping of the sensor structure. Therefore, an encapsulation of these MEMS structures is mandatory to achieve proper device function. Encapsulation processes on wafer-level are developed and several MEMS products using this technology are commercially available [31]. A MEMS wafer is bonded to a cap-wafer in this technology, whereas standard cap-wafers are electrically passive. They protect the MEMS structures during the following processes like dicing and maintain vacuum levels inside the cavity formed during the device lifetime. Detailed explanations of bond processes are presented in [32]. Bond wires form the electrical contacts between MEMS, ICs and lead frames. Figure 2.4(a) shows an actual design realized at Fraunhofer ISIT. Interconnect lengths and SPE-values are critical for several new applications planned.

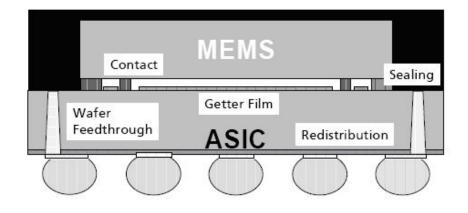

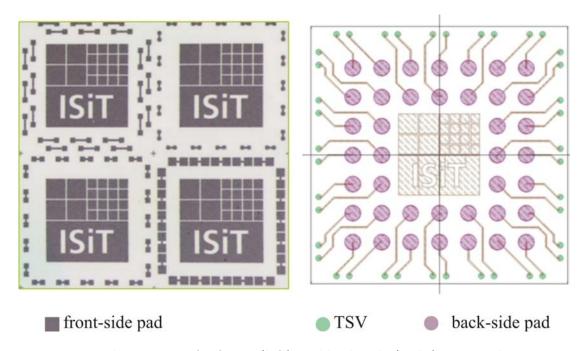

The Fraunhofer Institute for Silicon Technology (ISIT) develops new processes in order to improve MEMS functionalities. The project Downscaled Assembly of Vertical Interconnect Devices (DAVID) [33], which is founded by the European Union, targets a direct placement of MEMS devices on top of an application specific integrated circuit (ASIC). This direct stacking allows a realization of short interconnects between MEMS and ASIC. The capwafer is not passive anymore, which results in a higher SPE value. A direct bonding of a MEMS wafer to an ASIC wafer (W2W) is a promising process for high volume products due the fully developed bonding process. Costs of this process are manageable for new devices, because wire bonds are replaced and the system gains performance. A bonding of MEMS chips to ASIC wafer in a C2W process is very challenging. The technologies required are still under research [9]. However, C2W technology is an interesting technique to bond MEMS and ASIC wafer in prototype phases, low volume products or for costly MEMS. Electrical testing of MEMS and ASIC before bonding allows a 100% production yield.

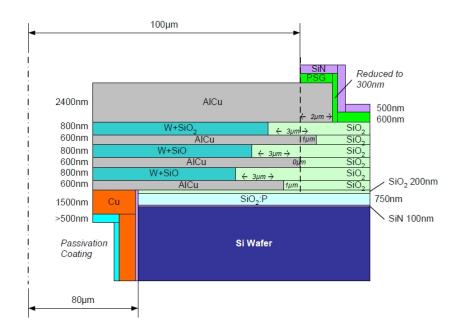

In addition, TSV integration inside ASICs improves the performance for systems creating using the DAVID approach. The TSV formation must be performed before MEMS chips are bonded to ASICs. A signal redistribution on the ASIC back allows an integration of solder balling processes. Wafer molding [34] and device separation allow an integration of this so called *system in the package (SiP)* in printed circuit board designs. Figure 2.4(b) shows a scheme of the DAVID approach for the C2W approach. Functional elements presented in figure 2.4(b) are discussed in [35].

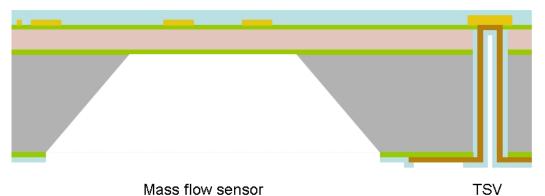

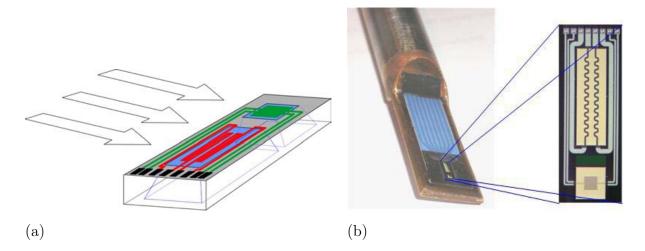

**Example B** ISIT has developed a mass flow sensor for gaseous and liquid media. The sensor operates on the hot wire anemometer principle combined with calorimetric principles. The primary sensor of this mass flow sensor is a heated wire that is exposed in a media flow (either gas or fluid). A second sensor is used to measure the ambient (media) temperature. The heating sensor shows a low electrical resistance (50-90  $\Omega$ ) and the reference sensor shows a high value (2 k $\Omega$ ). As the flow passes over the hot wire, it carries away heat. The heat loss depends on the mass flow rate, the heat capacity of the media, and the temperature difference between the wire and the media. Since the heat capacity of the media is known and the temperatures are monitored in real-time, the mass flow rate can be determined from the heat loss (related to the electric resistance of the wire via Ohm's law) and the temperature coefficient  $\alpha$  of the wire. The sensor principle is shown in detail by [36]. Figure 2.5(a) illustrates a sketch of the sensor and (b) shows a sensor setup used in field tests for water flow monitoring.

Figure 2.5: (a) Sketch of an anemometric mass flow sensor developed at ISIT. (b) MAF measurement setup used for water flow monitoring.

Field tests showed that corrosion of bond pads can occur after long measurement times even though organic protection layers (glob top) were applied on top of bond wires and pads like it is shown in figure 2.6(a). Water infiltration between the glob top interface area and the substrate was observed. A good example of a better performance of an TSV integration in MEMS is the mass flow sensor for two reasons

- to avoid the observed corrosion and

- to prevent micro-turbulences.

TSV fed the sensor signal to the wafer back-side. Redistribution layers on the wafer backside allow an electrical contact between the mass flow sensor and a substrate by solder ball or bump technologies. Pads on the wafer front can be protected by inorganic films deposited by standard LP- or PE-CVD techniques. Films deposited by these techniques show a good chemical resistance against various media that were investigated. Therefore, mass flow sensors with integrated TSV allow measurements of gaseous and fluid media even in harsh environments [14]. In addition, the measurement performance of the sensor is improved by TSV implementation. The media investigated flows homogeneously over the sensor using TSV, because turbulences of flowing medias caused by the bulky glob top in the actual system integration approach can not occur by a TSV integration. The signal to noise ratio and the sensitivity is thus enhanced by TSV integration in mass flow sensors. Figure 2.6(b) illustrates a mass flow sensor with integrated TSV which prevents corrosion and micro-turbulences.

- (b)

- Figure 2.6: Conventional mass flow sensor package after field test and mass flow sensor with TSV. (a) Mass flow sensor after field test and glob top removal. Corroded bond pads were observed due to water infiltration at the glob top interface to the sensor. (b) TSV integration in mass flow sensors developed at the Fraunhofer Institute for Silicon Technology.

# 3 Specifications of TSV in MEMS-packages at Fraunhofer ISIT

## 3.1 TSV process sequences

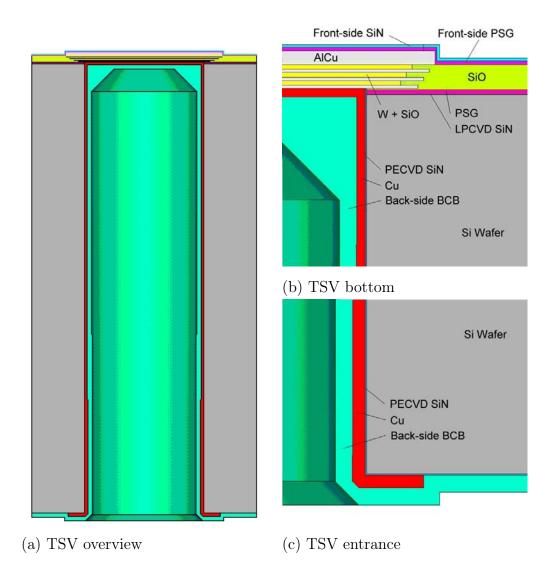

TSV carry electric signals from the wafer front- to back-side. Thus, electric conducting films must connect electrical connection points (pads) of IC or MEMS front-sides with pads on wafer back-sides. A direct connection of front-side pads from the wafer back-side by using:

• a hole etched through the wafer,

and subsequently a deposition and structuring of,

- an electrical isolating material,

- an electrical conducting material and

- a protection material

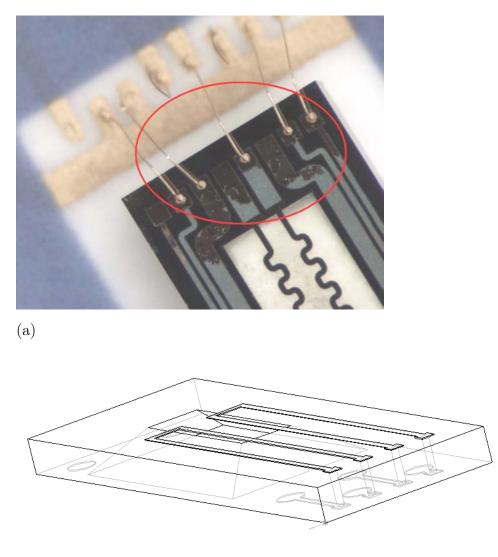

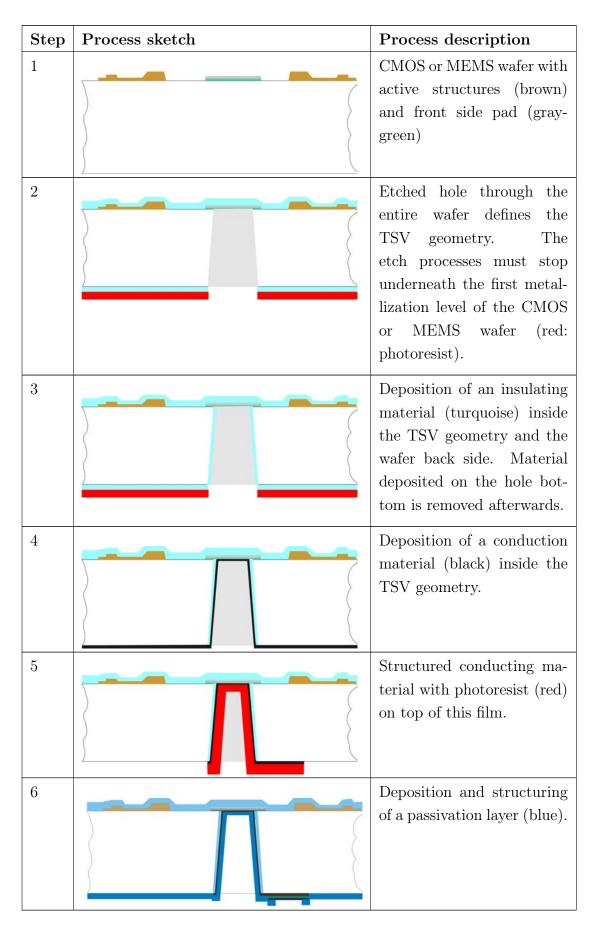

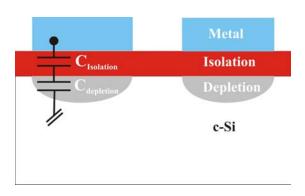

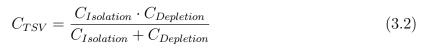

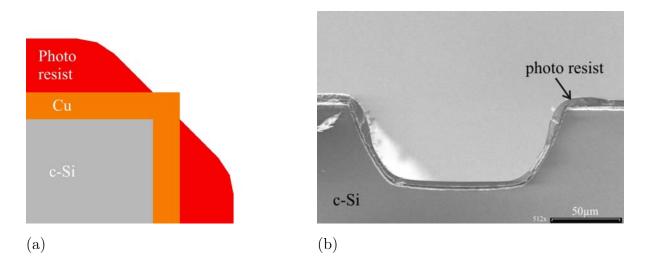

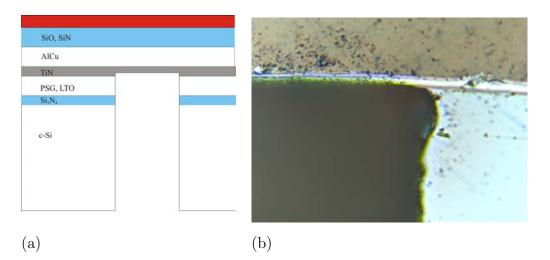

is an appropriate TSV solution for MEMS packages. TSV etch processes required must stop underneath the first metallization layer of the front-side pad in order to realize a good electrical contact between deposited electrical conducting material and the front-side metallization. In addition, hermetic TSV require stable pad-cells after TSV processing. ASIC and MEMS pad-cell specifications have to be taken into account regarding these two aspects. Pad-cell structures are discussed in sections 3.2.1 and 3.2.2. Electrical potentials of metallization films deposited must be separated from the substrate by an electrical isolating material in order to avoid cross talking between TSV and other functional elements on the wafer. Thus, organic or inorganic films have to be deposited inside the holes etched and on wafer back-sides. A structural dense film composition is necessary in order to avoid leakage currents during the device lifetime. Isolating material deposited covers the TSV hole bottom and hole sidewalls simultaneously and an anisotropic etching only at the hole bottom opens again front-side pad structures. An appropriate electrical conducting film, in general a metal, is deposited inside TSV geometries and on wafer back-sides for electrical conduction purposes. Conventional metal deposition techniques does not allow a void free filling of the TSV techniques. Electroplating is often used to fill holes completely with metals. However, a complete TSV filling inside the TSV holes with a depth of  $>300\mu$ m is economically and technologically not useful. First, Dixit et al have shown that a complete filling of  $400\mu m$  deep holes takes 20 hours, which is economically unacceptable [37]. Second, c-Si and the metal used (often Cu) have a coefficient of thermal expansion of 4.2 ppm/K and 20 ppm/K, respectively. This mismatch introduces a large stress inside the TSV system under any thermal treatment during TSV processing and is larger for complete filled TSV structures. Thus, a ring metallization like shown in figure 3.1 step 4 should be targeted for a TSV implementation inside MEMS packages with wafer thicknesses  $>300\mu$ m. This deposited film is the base material for the back-side pad-cell. Thus, a structuring of the material deposited is necessary. Metallic films deposited inside the TSV can not be structured in order to minimize the electrical TSV resistance. This requirement creates a high challenge for the deposition of photoresists, because standard resist deposition processes are not developed for this high topography challenge. The deposition and partial opening of a passivation layer are final process steps of this TSV flow. Figure 3.1 shows schematically the described TSV fabrication flow.

This TSV solution requires direct access to front side pads from wafer back sides. This is sometimes, especially for ASIC pads, hard to achieve due to implemented electrical protection structures next or underneath the pad, see chapter 3.2.1. A redistribution of pads on wafer front sides overcomes this challenge. A second pad which is electrically connected to the original pad must be implemented which fulfills requirements of a TSV implementation inside CMOS or MEMS wafer.

Figure 3.1: Basic process flow of a post-CMOS compatible TSV.

## 3.2 Pad-cell requirements

#### 3.2.1 CMOS pad-cell

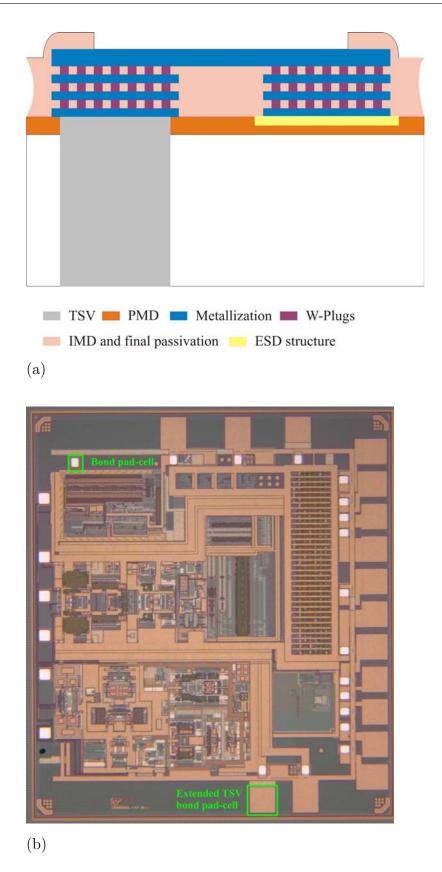

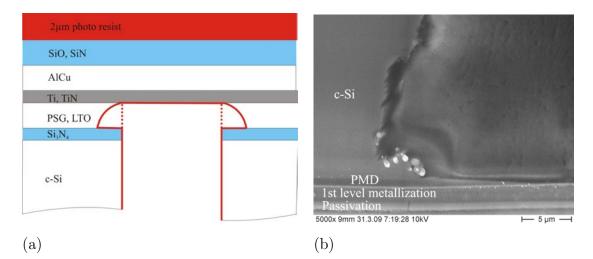

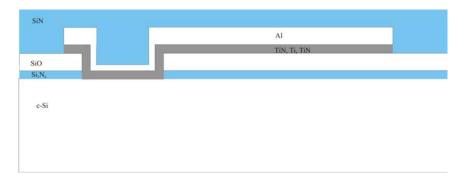

CMOS pad-cell architectures are not standardized. Electrical device performance defines pad-cell layouts. For instance, pads in high frequency application devices require much thicker isolation layers between two metal layers in order to avoid cross talking compared to direct or low frequency signal devices. In addition, pad-cells used must withstand mechanical forces during subsequent processes like wire bonding or soldering. Broken pads reduce system yields and this results in higher production costs. Thus, all CMOS wafer vendors have developed their own pad-cell designs. Design rules used are confidential. However, all pad architectures are based on the same functional elements and fabrication technologies.

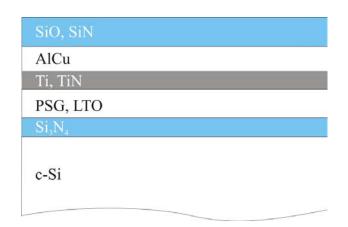

First, isolating materials are deposited onto wafers in order to isolate the silicon wafer electrically from pad structures or other functional elements. These layers or layer stacks are called pre-metal dielectric (PMD) and are based on silicon oxide or nitride variations like un-doped or doped silicate glasses. Metallic films are deposited on top of the PMD in order to connect functional elements on the wafer. These films must fulfill the following criteria due to reliability issues:

- Materials deposited must show good adhesion.

- Diffusion of any material inside other structures or functional elements must be avoided.

- The electrical conductivity must be minimized in order to reduce parasitic effects.

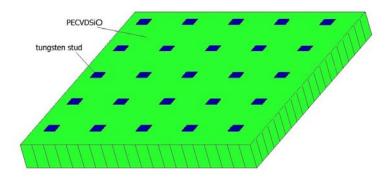

Thus, transition metals like Ti are deposited on top of the PMD and react with the surface. Ti does not diffuse through the PMD or other isolating materials. The electrical conductivity of Ti is not high enough for conduction purposes in CMOS devices. Therefore, high electrical conducting metals preferred Al, Cu or AlCu alloys, are integrated. The adhesion of these metals is good on Ti, but their diffusion inside oxides is not negligible. Diffusion barriers like TiN or TaN are deposited between adhesion promoters and metallization layers to avoid material transport. All three different films are sputtered. This film stack made out of an adhesions promoter, a diffusion barrier and a metallization is called  $1^{st}$  level metallization. Pad-cell specifications defines the pattern of the metal deposited. High transistor densities in modern CMOS devices need more than only one metallization level to make the system function. A passivation layer, also called inter metallic dielectric

(IMD), is deposited on top of the  $1^{st}$  level metallization. A planarization of this film is performed by chemical mechanical polishing in order to define a planar level for the next process. Via holes are etched inside the IMD and then filled with W completely. These Wplugs allow an electrical connection between the  $1^{st}$  and  $2^{nd}$  metallization level. The process sequence for the deposition of the  $2^{nd}$  metallization level is the same as described above for the  $1^{st}$  level metallization. These processes are repeated until the last metallization level is reached. Some CMOS devices need six to nine metallization levels.

TSV implemented in CMOS devices require a planar  $1^{st}$  level metallization surface in order to achieve a defined etch stop at the adhesion promoter. A mosaic design, which is sometimes used in RF-applications, does not allow a defined etch stop, because oxides are deposited between metal structures. These oxides will be removed during the PMD etching. The metal remaining is possibly not mechanically stable after the oxides are removed.

Several functional elements on wafers are electrostatic sensitive and require protection structures due to possible short electrical current pulses during testing or assembly. Thus, electrical protection structures are sometimes implemented underneath the  $1^{st}$  metallization level. These structures must remain stable during TSV processing. A placing of these structures around pad cells allows a TSV process as described before. This is often not possible due to design aspects. A pad extension like the one shown in figure 3.2 is otherwise required for a TSV integration. A complete chip re-design is not necessary in this case. Figure 3.2 shows also a top view of an ASIC design with an extended TSV pad-cell.

TSV implementation in CMOS devices limits the processes that can be used. For instance, the thermal process budget is limited due to already implemented metallic films like Al. Higher temperatures cause a diffusion of Al into the Si substrate even if a diffusion barrier is present. This diffusion can cause non-functional electrical circuits.

Alkali ions contamination may occur during an exposure of the wafer with etchants such as KOH or photo-resist developers like NaOH. The main concern of alkali ion contamination is the probability of positive alkali ions to diffuse to functional elements and change physical parameters such as the threshold voltage of transistors. Suitable cleaning procedures are necessary in order to remove all ions after wet etching processes. In addition, Al is etched by some wet chemical processes. Process flows must be chosen in such a way that no contamination and destruction of pad-cells appear.

Figure 3.2: Pad-cell structure of CMOS devices. (a) Extended pad-cell allows an integration of TSV in standardized Pad cells without a re-design of ESD structures.(b) Topview of an ASIC by ST Microelectronics with conventional bond and extended TSV pads.

#### 3.2.2 MEMS pad-cell

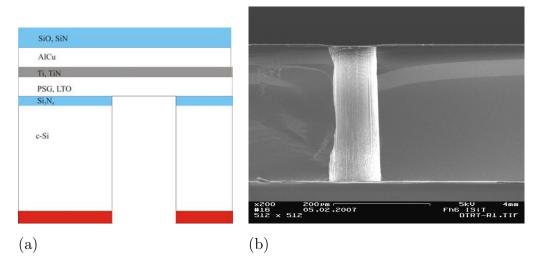

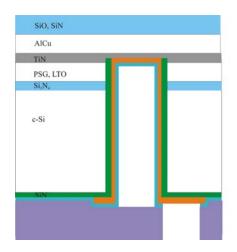

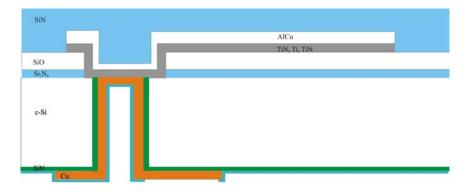

Different technologies and process flows were developed for MEMS fabrication. Thus, standard MEMS designs are not realized. Several projects tried to find a solution for this challenge, but each MEMS vendor is still using different machines or technologies to produce MEMS. These different technologies have influenced MEMS pad-cell designs. No standard pad-cell designs are available. However, a pad-cell design for a mass flow sensor from ISIT will be presented here. The entire process flow of this mass flow sensor has to be explained for this purpose. The major process steps can be summarized as follows:

- 1. The mass flow sensor is a membrane sensor and this membrane is based on a three layer stack composed of a silicon nitride, a silicon dioxide and an additional silicon nitride layer. This optimized stack shows a small tensile stress and does not show any buckling after release etch.

- 2. The sensing structures are made by a stack of TiN, Ti, TiN and Al. Al has to be deposited in order to form a pad on which a wire bond process can be applied. The TiN protects the reactive Ti during further process steps and during measurement cycles.

- 3. Silicon nitride deposited on these structures protects the Al against corrosion forced by the media investigated. The nitride is only opened at the pad-cell area.

- 4. A wafer processing from the back-side is followed, which is not important for the pad-cell design. A complete process description is given by Melani et al. [36]

(Pass.) (1000nm) Membrane (1000nm)

Figure 3.3 shows a cross section of the realized sensor.

Figure 3.3: Cross section of the realized mass flow sensor at Fraunhofer ISIT.

## 3.3 TSV hole geometry

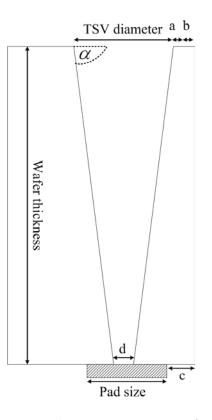

Pad-cell geometries and orientations on IC- or MEMS-wafer limit possible TSV hole geometries. Pad-cell geometries of  $90\mu m \ge 90\mu m$  are common in actual IC layouts and are placed at chip corners. Common designs uses distances of  $40\mu m$  between pads and chip edges. Pad-cells are placed often next to each other with an equidistant spacing (pitch) of  $150\mu m$ . This geometrical view results in a maximum TSV hole geometry. Holes formed can not be larger than pad-cell geometries at the hole bottom (underneath the front-side pad). Larger hole diameters can destroy surrounding functional elements. This consideration is based on vertical etched holes. Formation of tapered holes is limited by the positions of placed pad-cells at chip corners. Large angles of tapered TSV holes will intersect dicing lines and TSV formed will be destroyed by the final dicing process. The TSV hole slope in respect to the planar wafer side is expressed by  $\alpha$ .

$$\alpha_{Max} = \arctan\left(\frac{\text{Wafer thickness}}{\frac{\text{Pad size}}{2} + c - (a+b) - \frac{d}{2}}\right)$$

(3.1)

Factors used are indicated in figure 3.4. Large  $\alpha$  should be targeted, because deposition processes are easier to perform for large  $\alpha$  in deep holes. The maximum angle  $\alpha_{max}$ for different wafer thicknesses is given by equation (3.1) and is summarized in table 3.2. Equation (3.1) takes only the distance between the bond pad and the chip corner into account due to the fact that this distance is much smaller compared to pitch sizes.

| Wafer thickness / [ $\mu$ m]           | 50 | 100 | 300 | 508 | 675 | 760 |

|----------------------------------------|----|-----|-----|-----|-----|-----|

| <b>TSV angle</b> $\alpha / [^{\circ}]$ | 51 | 68  | 82  | 85  | 87  | 87  |

Table 3.2: Possible TSV profiles dependent on the wafer thickness

## 3.4 Mechanical Aspects

#### 3.4.1 Wafer robustness

A conformal deposition of electrical isolating and conducting materials is challenging in TSV geometries with high aspect ratios. A detailed explanation of the deposition processes and their capabilities to deposit a conformal layer inside  $>300\mu$ m deep TSV is discussed in chapter 4.2. Wafers of 50 $\mu$ m thickness or less are used in several TSV approaches in order to simplify this deposition challenge. Wafer handling without carriers is not possible

Figure 3.4: Possible TSV geometry at chip corners; a is a safety distance of  $25\mu$ m; b is given by possible backside chipping  $(15\mu$ m), c is the distance between the outside of a pad and the dicing line  $(40\mu$ m), d is the contact window opening (here  $10\mu$ m).

for these wafer thicknesses due to the resulting high fracture probability. Thus, carrier wafers fixed to thinned wafers are used during TSV fabrication. The processes needed to fix and release carrier wafers are expensive. In addition, a TSV implementation in MEMS wafer does not allow wafer thinning to thicknesses of  $50\mu$ m due to their sensitive stress behavior. MEMS performances are changed or even destroyed by extreme wafer thinning ( $50\mu$ m). The possibility of operating MEMS with thinned wafers to thicknesses of  $300\mu$ m to  $400\mu$ m exists. Previous investigations have shown that a wafer processing with these thicknesses is possible without a significant yield loss [38]. This investigation was performed on planar wafers without TSV. Therefore, handling limits for silicon wafers of different thicknesses that contain TSV are discussed in the following mechanical simulations. The work is performed together with Prof. Fiedel of the University of Wroclaw and is partially presented in [39].

#### Model description

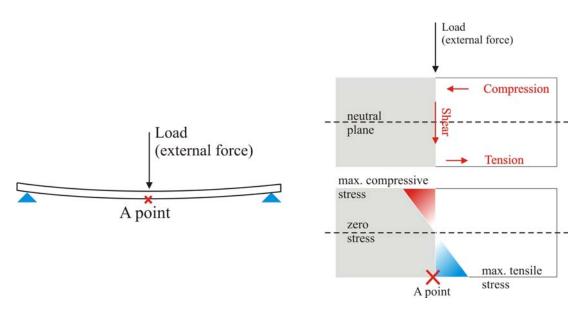

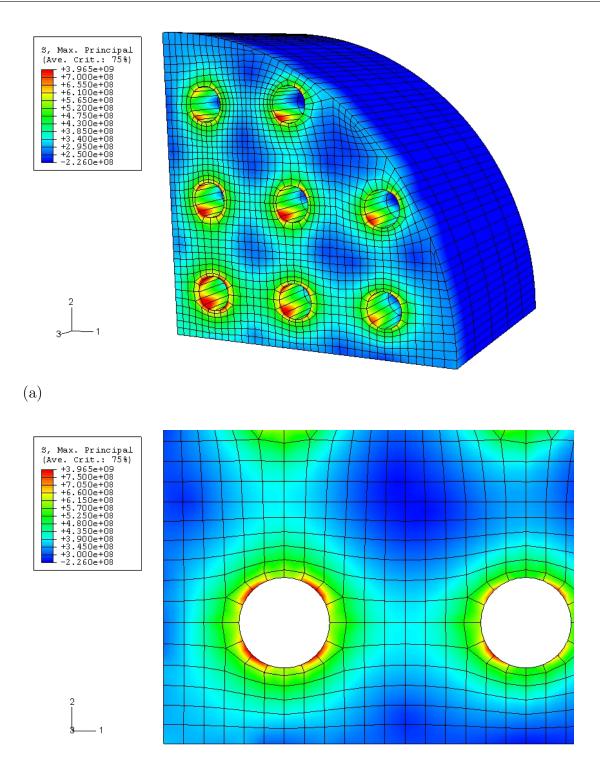

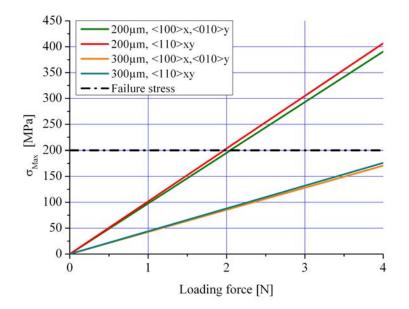

A wafer handling description in a complete process flow is difficult to perform. For instance, wafer holding systems (chucks) of processing machines are not standardized. A definition of one universal mechanical loading force is not possible. Therefore, a normal loading force applied at the wafer center is used as a mechanical loading force for all processes. In addition, the loading area is taken into account as a system parameter. Figure 3.5 shows the simulation model and the stress distribution inside the wafer while external load is applied. In brittle crystalline materials such as Si, fractures can occur by cleavage as a result of tensile stress acting normally to crystallographic planes with low bonding forces. These planes are also called cleavage planes. Values of compressive strength are much higher than the tensile strength in almost all materials. Therefore, crack initiation starts preferably at the point in which the maximal tensile stress occurs (indicated as A in figure 3.5).

Figure 3.5: Simulation model for determination of wafer stability during processing and stress distribution inside the wafer while an external load is applied

The fracture criterion is defined as follows. The flexural strength which is also known as modulus of rupture, bend strength or fracture strength should be selected as the critical material strength parameter in case of beam bending. Pecht et al show that the flexural strength is usually less than 10% of the compressive strength [40]. The compressive strength of silicon is well defined with 6GPa, but literature shows a wide range of flexural strength values for silicon. Values between 60MPa and 2.4GPa are reported [40][41]. Here, a

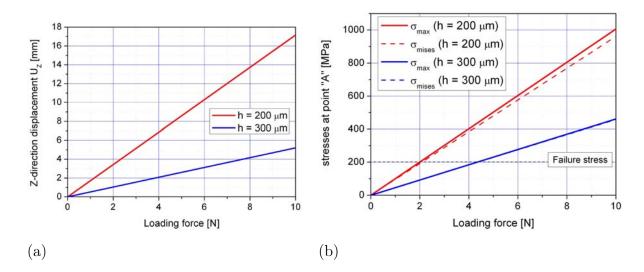

maximum flexural strength of 200MPa is taken as a fracture criterion. 8 inch (100) Si wafers with a thickness of  $200\mu$ m and  $300\mu$ m will be considered. Two different wafer types are considered for the calculation of the mechanical strength:

**Test A** Blanket Si wafer without TSV.

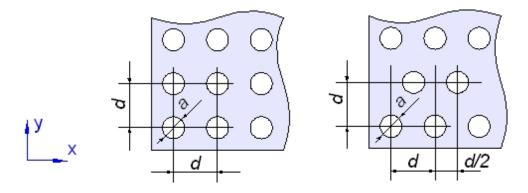

**Test B** Si wafer with TSV oriented in-one-line along the x- and y-axis and in a staggered orientation.

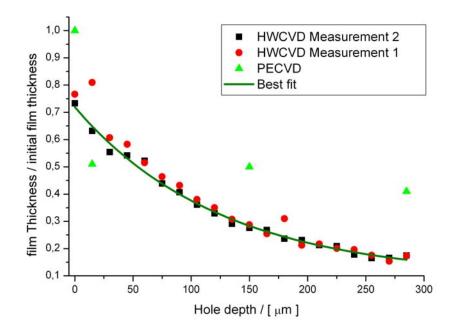

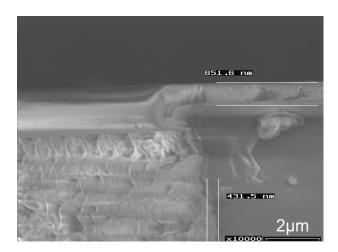

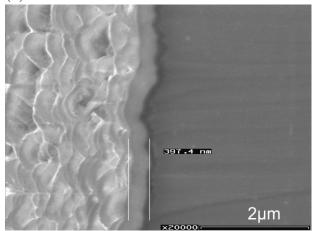

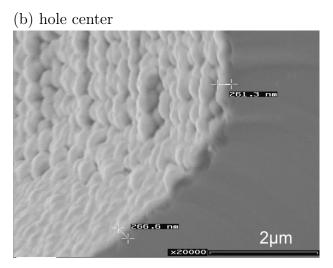

TSV hole diameters of  $30\mu$ m and a  $80\mu$ m pitch are defined in this model. These hole dimensions are four orders of magnitude smaller compared to the wafer size. In this case it is not possible to simulate the complete model (with all holes) with sufficient accuracy (coarse mesh) or in satisfactory time (to many elements). Thus, the problem is divided in two easier models. First, a coarse model uses only a few holes, but with a bigger diameter. The sum of surface areas created is the same in the coarse and the original fine models. This coarse model allows an interpretation of stability issues on wafer level. A sub-model is created in a second step at the wafer center, because the loading force is the highest at this point. Original TSV hole geometries are used in this model. In addition, wafer symmetry allows calculations on only a wafer quarter. Sub-modelling and the wafer size reduction reduces calculation times and show sufficient results.