Sajjad Nouri

## **Power and Energy Aware Heterogeneous Computing Platform**

Julkaisu 1594 • Publication 1594

| Tampereen teknillinen yliopisto. Julkaisu 1594<br>Tampere University of Technology. Publication 1594 |  |

|------------------------------------------------------------------------------------------------------|--|

|                                                                                                      |  |

Sajjad Nouri

# **Power and Energy Aware Heterogeneous Computing Platform**

Thesis for the degree of Doctor of Science in Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TC133 at Tampere University of Technology, on the 20<sup>th</sup> of November 2018, at 12 noon.

Doctoral candidate: Sajjad Nouri

Laboratory of Electronics and Communications

Engineering

Faculty of Computing and Electrical Engineering

Tampere University of Technology

Finland

Supervisor: Jari Nurmi, Professor

Laboratory of Electronics and Communications

Engineering

Faculty of Computing and Electrical Engineering

Tampere University of Technology

Finland

Pre-examiners: Dr.-Ing. Michael Hübner, Professor

Chair for Embedded Systems in Information Technique

Ruhr-University Bochum

Germany

Peeter Ellervee, Professor

Department of Computer Systems Tallinn University of Technology

Estonia

Opponent: Peeter Ellervee, Professor

Department of Computer Systems Tallinn University of Technology

Estonia

Pasi Liljeberg, Professor

Embedded Computing Architectures Department of Future Technologies

University of Turku

Finland

## **Abstract**

During the last decade, wireless technologies have experienced significant development, most notably in the form of mobile cellular radio evolution from GSM to UMTS/HSPA and thereon to Long-Term Evolution (LTE) for increasing the capacity and speed of wireless data networks. Considering the real-time constraints of the new wireless standards and their demands for parallel processing, reconfigurable architectures and in particular, multicore platforms are part of the most successful platforms due to providing high computational parallelism and throughput. In addition to that, by moving toward Internet-of-Things (IoT), the number of wireless sensors and IP-based high throughput network routers is growing at a rapid pace. Despite all the progression in IoT, due to power and energy consumption, a single chip platform for providing multiple communication standards and a large processing bandwidth is still missing. The strong demand for performing different sets of operations by the embedded systems and increasing the computational performance has led to the use of heterogeneous multicore architectures with the help of accelerators for computationally-intensive data-parallel tasks acting as coprocessors. Currently, highly heterogeneous systems are the most power-area efficient solution for performing complex signal processing systems. Additionally, the importance of IoT has increased significantly the need for heterogeneous and reconfigurable platforms.

On the other hand, subsequent to the breakdown of the Dennardian scaling and due to the enormous heat dissipation, the performance of a single chip was obstructed by the utilization wall since all cores cannot be clocked at their maximum operating frequency. Therefore, a thermal melt-down might be happened as a result of high instantaneous power dissipation. In this context, a large fraction of the chip, which is switched-off (Dark) or operated at a very low frequency (Dim) is called Dark Silicon. The Dark Silicon issue is a constraint for the performance of computers, especially when the up-coming IoT scenario will demand a very high performance level with high energy efficiency. Among the suggested solution to combat the problem of Dark-Silicon, the use of application-specific accelerators and in particular Coarse-Grained Reconfigurable Arrays (CGRAs) are the main motivation of this thesis work.

This thesis deals with design and implementation of Software Defined Radio (SDR) as well as High Efficiency Video Coding (HEVC) application-specific accelerators for computationally intensive kernels and data-parallel tasks. One of the most important data transmission schemes in SDR due to its ability of providing high data rates is Orthogonal Frequency Division Multiplexing (OFDM). This research work focuses on the evaluation of Heterogeneous Accelerator-Rich Platform (HARP) by implementing OFDM receiver blocks as designs for proof-of-concept. The HARP template allows the designer to instantiate a heterogeneous reconfigurable platform with a very large amount of custom-tailored computational resources while delivering a high performance

ii Abstract

in terms of many high-level metrics. The availability of this platform lays an excellent foundation to investigate techniques and methods to replace the Dark or Dim part of chip with high-performance silicon dissipating very low power and energy. Furthermore, this research work is also addressing the power and energy issues of the embedded computing systems by tailoring the HARP for self-aware and energy-aware computing models. In this context, the instantaneous power dissipation and therefore the heat dissipation of HARP are mitigated on FPGA/ASIC by using Dynamic Voltage and Frequency Scaling (DVFS) to minimize the dark/dim part of the chip. Upgraded HARP for self-aware and energy-aware computing can be utilized as an energy-efficient general-purpose transceiver platform that is cognitive to many radio standards and can provide high throughput while consuming as little energy as possible. The evaluation of HARP has shown promising results, which makes it a suitable platform for avoiding Dark Silicon in embedded computing platforms and also for diverse needs of IoT communications.

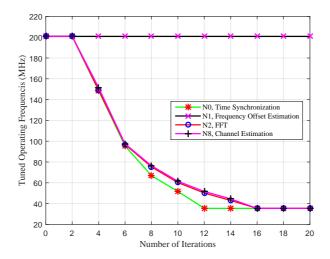

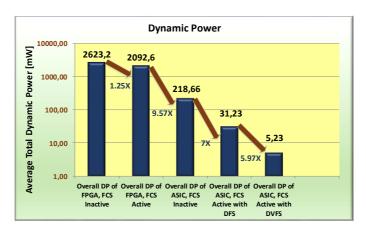

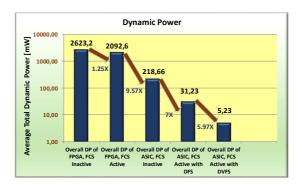

In this thesis, the author designed the blocks of OFDM receiver by crafting templatebased CGRA devices and then attached them to HARP's Network-on-Chip (NoC) nodes. The performance of application-specific accelerators generated from templatebased CGRAs, the performance of the entire platform subsequent to integrating the CGRA nodes on HARP and the NoC traffic are recorded in terms of several highlevel performance metrics. In evaluating HARP on FPGA prototype, it delivers a performance of 0.012 GOPS/mW. Because of the scalability and regularity in HARP, the author considered its value as architectural constant. In addition to showing the gain and the benefits of maximizing the number of reconfigurable processing resources on a platform in comparison to the scaled performance of several state-of-the-art platforms, HARP's architectural constant ensures application-independent figure of merit. HARP is further evaluated by implementing various sizes of Discrete Cosine transform (DCT) and Discrete Sine Transform (DST) dedicated for HEVC standard, which showed its ability to sustain Full HD 1080p format at 30 fps on FPGA. The author also integrated self-aware computing model in HARP to mitigate the power dissipation of an OFDM receiver. In the case of FPGA implementation, the total power dissipation of the platform showed 16.8% reduction due to employing the Feedback Control System (FCS) technique with Dynamic Frequency Scaling (DFS). Furthermore, by moving to ASIC technology and scaling both frequency and voltage simultaneously, significant dynamic power reduction (up to 82.98%) was achieved, which proved the DFS/DVFS techniques as one step forward to mitigate the Dark Silicon issue.

## **Preface**

This thesis is based on the research work carried out during the years 2015-2018 in the Laboratory of Electronics and Communications Engineering at Tampere University of Technology (TUT), Tampere, Finland. I would like to gratefully acknowledge the financial support I received from the TUT Graduate School (during 2017-2018), Tuula and Yrjö Neuvo fund, HPY Research Foundation, Tekniikan Edistämissäätiö (TES) Foundation, DELTA doctoral training network, HiPEAC collaboration grant and Nokia Scholarship. I also wish to acknowledge the funding received from the Academy of Finland under contract # 258506 (DEFT: Design of a Highly-parallel Heterogeneous MP-SoC Architecture for Future Wireless Technologies).

First and foremost, I wish to express my deepest gratitude to my supervisor Prof. Jari Nurmi, who welcomed me into his research group during my M.Sc. degree, always believed in my abilities, provided finance throughput my research in TUT and abroad and made possible the accomplishment of this research work. I must also thank Dr. Waqar Hussain who has been a truly inspiring instructor and always gave me precious suggestions and feedbacks and helped me to find my own way in the research world. I would like to acknowledge Prof. Dr.-Ing. Diana Göhringer and Prof. Davide Rossi for being my supervisors at Ruhr University Bochum (RUB), Bochum, Germany and University of Bologna, Bologna, Italy, respectively. I thank Jens Rettkowski for being helpful colleague collaborating for joint research work at RUB. I would like to express all my deepest acknowledgments to Prof. Markku Renfors for his support and guidance, who granted me useful feedback whenever I asked. I am also thankful to Jyrki Hyrsylä, R&D Line Manager at Nokia Networks, who welcomed me into his team recently.

I would also like to express my thanks to the reviewers of this thesis: Prof. Dr.-Ing. Michael Hübner as well as Prof. Peeter Ellervee for their invaluable comments to improve the quality of this thesis.

I have had the good fortune to meet many special individuals over the past 5 years in Tampere, many of whom have inspired me to be the person I am today. I would like to express my unutterable gratitude specially to Mohsen Shahshahan, Orod Raeesi and Mohammad Ali Pourabed who have been side by side with me through thick and thin, particularly at times when it was even hard for me to stand myself. I also must thank Ramin Ghaznavi, Mitra Akbari, Mona Aghababaee, Farid Mehrabkhani, Nader Daneshfar and Shervin Safineh for their warm friendship and nice moments we have shared together and also for their long support. I must acknowledge my dear friend, Ritayan Biswas, who has helped me in reviewing this thesis. I am also grateful to my dear friends from Iran, Mohammad Tavoli, MohammadAli Tizhoush Taban, Mehdi Joafshani, Keyvan Abdi, Ata Meshkinzar, Leila Nikouei and Makan Aghakhani. There are also so many friends whose names I have not mentioned here but whom I also must

iv Preface

#### thank.

I wish to express my deepest gratitude and respect to my mother Tayyebeh Sadeghi Moghadam and my father Majid Nouri for their patience, enormous love and invaluable support in all moments throughout my entire life to bring me up to this stage. I owe all my achievements to them and without their support, none of this would have been possible. I also thank my faithful Lucy, for making a story of love and devotion between a dog and a man and being beside me to share the joys and happy times once I started to lose them.

Finally, I wish to thank the one dearest to me, Zohre Bijani. **Zohre**, The moment it hit me, I looked and looked at you, and I knew, as clearly as day and night, that I love you more than anything I had ever seen or imagined on earth. It is like the entire universe conspired to help me find you. My love, I have been fortunate to have you on my side to provide hope and motivation throughout this journey. You are the one person that made me risk everything for a future worth having. If my love for you was an ocean, there would be no more land. With you, I finally understood what true love means.

Tampere, October 2018 Sajjad Nouri

# **Contents**

| Α  | bstract                                                                                                                                                                                                                | 1                                |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Pı | reface                                                                                                                                                                                                                 | iii                              |

| A  | cronyms  Well-Known Acronyms                                                                                                                                                                                           | <b>vii</b><br>vii<br>viii        |

| Li | st of Publications                                                                                                                                                                                                     | ix                               |

| Li | st of Figures                                                                                                                                                                                                          | х                                |

| Li | ist of Tables                                                                                                                                                                                                          | xii                              |

| 1  | Introduction  1.1 Objective and Scope of Research                                                                                                                                                                      | 1<br>3<br>5<br>7                 |

| 2  | Literature Review         2.1 Reconfigurable Devices          2.2 Multicore Platforms          2.3 Power Mitigation of Multicore platforms by DVFS Techniques          2.4 Hardware Implementation of DCT/DST for HEVC | 9<br>13<br>15                    |

| 3  | Platform Architecture 3.1 Coarse-Grained Reconfigurable Arrays                                                                                                                                                         |                                  |

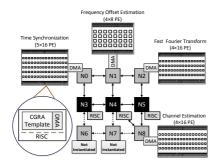

| 4  | Design and Implementation of OFDM Receiver Blocks on CGRAs4.1 Time Synchronization4.2 Frequency Offset Estimation4.3 Fast Fourier Transform4.4 Channel Estimation4.5 Symbols Demapping                                 | 25<br>26<br>28<br>31<br>31<br>35 |

| 5  | Evaluation of HARP by Design and Test of an OFDM Receiver 5.1 Measurements, Estimations, Evaluation and Comparisons                                                                                                    | <b>37</b>                        |

| 6  | Power Mitigation of a HARP on FPGA/ASIC by DFS/DVFS Techniques                                                                                                                                                         | 45                               |

vi Contents

|    | 6.1<br>6.2               | Equalization of the OFDM Receiver Performance by Frequency Scaling . Measurements and Estimations                                                                               |                       |

|----|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

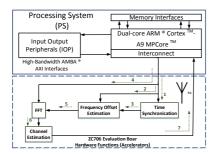

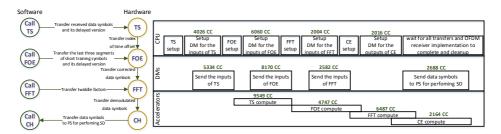

| 7  | HW<br>7.1<br>7.2         | /SW Co-design of an OFDM Receiver on Xilinx Zynq SoC using HLS Implementation of an OFDM receiver on the ZC706 Evaluation Board Experimental Results, Comparison and Discussion | <b>53</b> 53 56       |

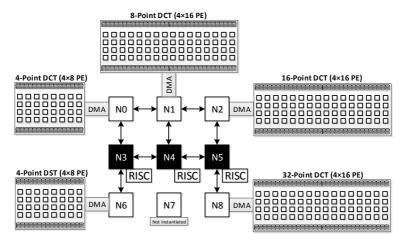

| 8  | 8.1<br>8.2<br>8.3<br>8.4 | ign and Implementation of Multi-Purpose DCT/DST-Specific Acceleration HARP  4-Point DCT                                                                                         | 61<br>62<br>63        |

| 9  |                          | Implementation of Multi-Purpose DCT/DST-Specific Accelerator on HARP Measurements, Estimations, Evaluation and Comparisons                                                      | 65<br><b>71</b><br>71 |

| Bi | bliog                    | raphy                                                                                                                                                                           | 77                    |

## Acronyms

#### Well-Known Acronyms

ASIC Application-Specific Integrated Circuit

ADC Analog to Digital Conversion

ALM Adaptive Logic Module

ALU Arithmetic and Logic Unit

ALUT Adaptive Look-Up Table

CC Clock Cycle

**CGRA** Coarse-Grained Reconfigurable Array

DA Distributed Arithmetic

DFS Dynamic Frequency Scaling

DFT Discrete Fourier Transform

DMA Direct Memory Access

DSP Digital Signal Processing

**DVFS** Dynamic Voltage Frequency Scaling

FCS Feedback Control System

FFT Fast Fourier Transform

**FPGA** Field Programmable Gate Array

**FU** Functional Unit

GOPS Giga Operations Per Second

GPP General Purpose Processor

GUI Graphical User Interface

HEVC High Efficiency Video Coding

**HLS** High-Level Synthesis

I/O Input/Output

ILP Instruction-Level Parallelism

LUT Lookup-Tables

MIMOMultiple-Input, Multiple-OutputMOPSMillions of Operations Per SecondMPEGMoving Picture Experts GroupMPSoCMulti-Processor System-on-Chip

**NoC** Network-on-Chip

OFDM Orthogonal Frequency-Division Multiplexing

RAW Reconfigurable Architecture Workstation

RISC Reduced Instruction-Set Computing

**SDR** Software Defined Radio

SIMD Single Instruction Multiple Data

VHDL Very high-speed integrated circuit Hardware Description Language

**VLIW** Very Long Instruction Word

viii Acronyms

#### **Specific Acronyms For This Thesis**

BB **Body Biasing** CE Channel Estimation **CFO** Carrier Frequency Offset

**COFFEE** COre For FrEE CP Cyclic Prefix

**CREMA** Coarse-grained REconfigurable array with Mapping Adaptiveness

DCT Discrete Cosine Transform

DRF Data Register File DST Discrete Sine Transform

Exploiting eXascale Technology with Reconfigurable Architectures **EXTRA**

FB Frame Buffer

**FBB** Forward Body Biasing **FOE** Frequency Offset Estimation **FUV Future Video Coding**

Heterogeneous Accelerator-Rich Platform HARP **HMA** Heterogeneous Multicore Architecture

**HPC High Performance Computing**

HRE Heterogeneous Reconfigurable Engine **IDCT** Inverse Discrete Cosine Transform **IDST** Inverse Discrete Sine Transform

LLC Last-Level Caches LRF Local Register File

**MFC** Multi-Function logic Cells **MVM** Matrix-Vector Multiplication Processing Array Element PAE PE

**Processing Element**

PID Proportional Integral Derivative

PUProcessing Units **RBB** Reverse Body Biasing RC Reconfigurable Cell RD Rate-Distortion

SEEC SElf-awarE Computing SMSquare Modulus TS Time Synchronization **URF** Unregistered-Feed Through

**UTBB FD-SOI** Ultra-Thin Body and Buried oxide Fully-Depleted Silicon-On-Insulator

**VCD** Value Change Dump

**VCEG** Video Coding Experts Group

## List of Publications

This thesis is mainly based on the following publications in which the author of the thesis is the main author and has the major contribution. The co-authors contributed to reviewing and providing the feedback. In the manuscript the publications are referred to as  $[P.\sharp]$ . The publications are appended at the end of the thesis.

- S. Nouri, W. Hussain, and J. Nurmi, "Implementation of IEEE-802.11a/g Receiver Blocks on a Coarse- Grained Reconfigurable Array," *International Conference on Design & Architectures for Signal & Image Processing (DASIP)*, Cracow, Poland, pp. 23-25., Sep. 2015.

- II S. Nouri, W. Hussain, and J. Nurmi, "Design and evaluation of correlation accelerator in IEEE-802.11a/g receiver using a template-based Coarse-Grained Reconfigurable Array," *Nordic Circuits and Systems Conference (NORCAS): NORCHIP & International Symposium on System-on-Chip (SoC)*, Oslo, Norway, pp. 1-6., Oct. 2015.

- III S. Nouri, J. Rettkowski, D. Göhringer, and J. Nurmi, "HW/SW Co-design of an IEEE 802.11a/g Receiver on Xilinx Zynq SoC using High-Level Synthesis," *In Proceedings of the 8th International Symposium on Highly Efficient Accelerators and Reconfigurable Technologies (HEART2017)*, Bochum, Germany, no 15, June 2017.

- IV S. Nouri, W. Hussain, and J. Nurmi, "Evaluation of a Heterogeneous Multicore Architecture by Design and Test of an OFDM Receiver," *in IEEE Transactions on Parallel and Distributed Systems*, vol. 28, no. 11, pp. 3171-3187, Nov. 2017.

- V S. Nouri, D. Rossi, and J. Nurmi, "Power Mitigation of a Heterogeneous Multicore Architecture on FPGA/ASIC by DFS/DVFS Techniques," *Elsevier Journal of Microprocessors and Microsystems (MICPRO)*, Sep. 2018.

- VI S. Nouri, R. Ghaznavi-Youvalari, and J. Nurmi, "Design and Implementation of Multi-Purpose DCT/DST-Specific Accelerator on Heterogeneous Multicore Architecture," *Nordic Circuits and Systems Conference (NORCAS): NORCHIP & International Symposium on System-on-Chip (SoC)*, Tallinn, Estonia, Oct. 2018.

# **List of Figures**

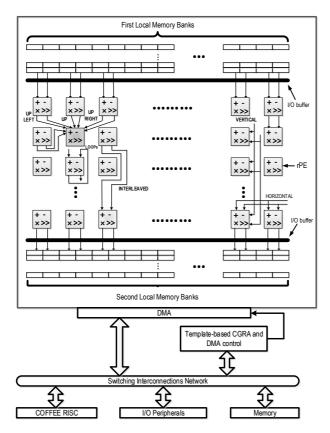

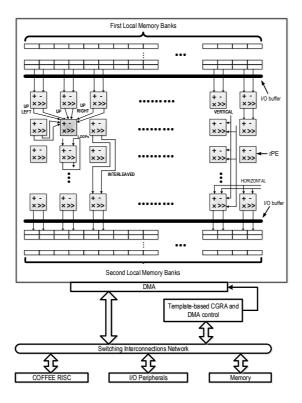

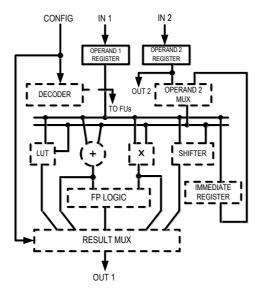

| 3.1        | The architecture of template-based CGRA used for integration as a CGRA node on HARP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

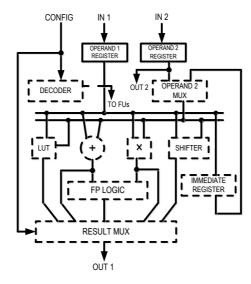

| 2.2        | PE Core Template. [P.I]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20<br>21 |

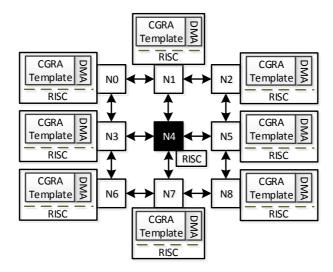

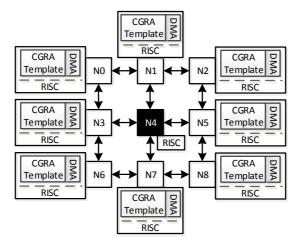

| 3.2        | General view of HARP architecture. [P.IV]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22       |

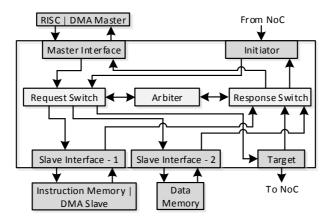

| 3.3        | A detailed view of the Master and Slave nodes of HARP. [P.IV]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 3.4        | A detailed view of the Master and Slave Hodes of HART. [F.1v]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22       |

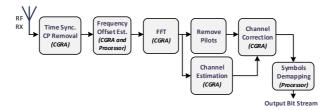

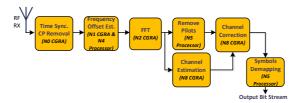

| 4.1        | A simplified view of an OFDM receiver. [P.IV]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25       |

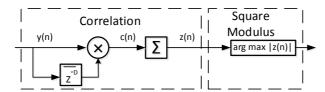

| 4.2        | Signal flow structure of CP correlation based method for TS. [P.IV]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26       |

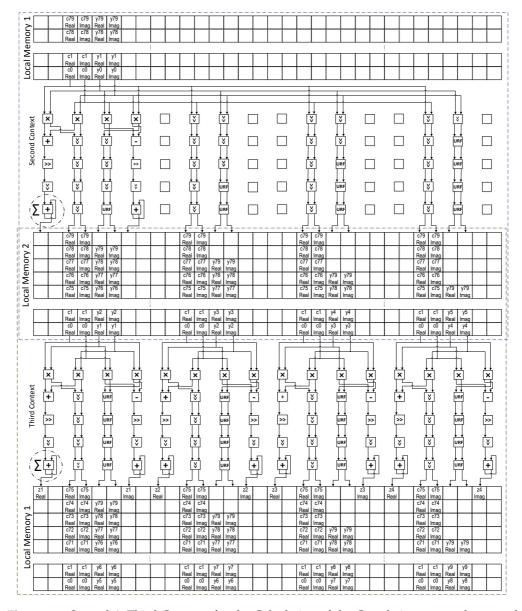

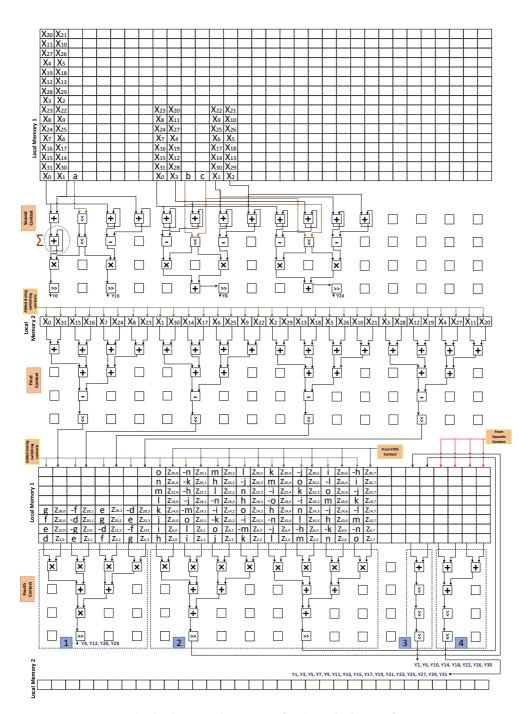

| 4.3        | Second & Third Contexts for the Calculation of the Correlations. $c_n$ and $y_n$ stand for the original received signal and the complex conjugate of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|            | delayed version of the signal, respectively. [P.II]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27       |

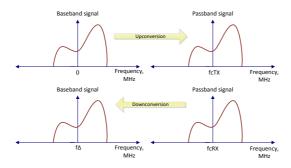

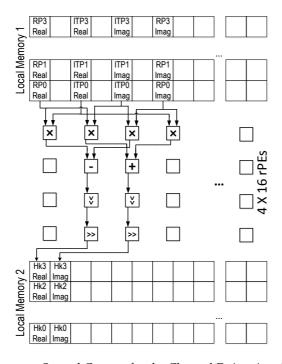

| 4·4<br>4·5 | Upconversion and downconversion of signal in transceiver. [P.IV] Context for the complex multiplication between a signal and its complex conjugation [1]. r and rD stand for the last three segments of short training                                                                                                                                                                                                                                                                                                                                                                                                                       | 28       |

|            | symbols and its delayed version. [P.I]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30       |

| 4.6        | Channel Estimation based on Pilot-Assisted Linear Interpolation. [P.IV]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31       |

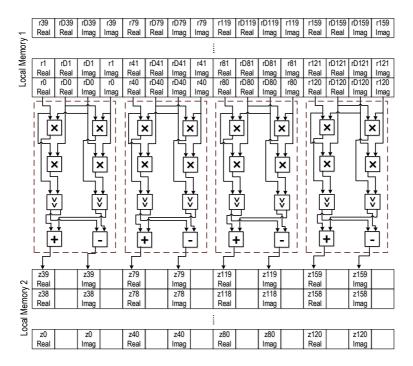

| 4.7        | Second Context for the Channel Estimation. [P.IV]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32       |

| 4.8        | Third & Fourth Contexts for the Calculation of Linear Interpolation and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

|            | Newton-Raphson Method. [P.IV]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33       |

| 4.9        | Fifth & Sixth Contexts for the Calculation of Newton-Raphson Method and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

|            | Channel Equalization. [P.IV]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35       |

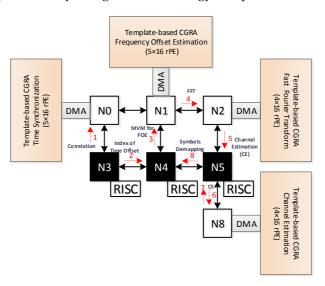

| 5.1        | Modified HARP platform for an OFDM receiver test-case. The black colored nodes are the master and white colored nodes are the slave nodes. [P.IV]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37       |

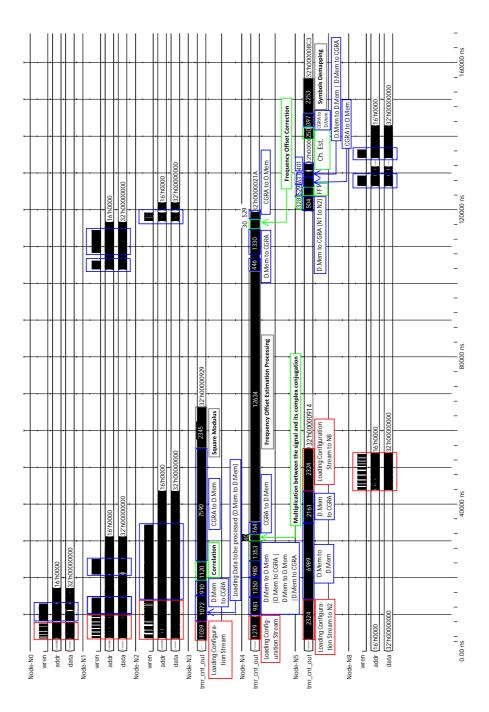

| 5.2        | The time frame related to the utilization of NoC bandwidth in which configuration words and the data transfers between the data memories of the CGRA nodes are specified with red and blue lines, respectively. The execution of OFDM receiver blocks are also specified with green lines in the case of CGRAs and gray lines in the case of RISC processor software. The signals 'wren', 'addr' and 'tmr_cnt_out' stand for write-enable, address ports of the Data Memory and the counter for enumerating the number of CC, respectively. The numbers inside the digital waveforms of N3, N4 and N5 are extracted from the Table I. [P.IV] | 44       |

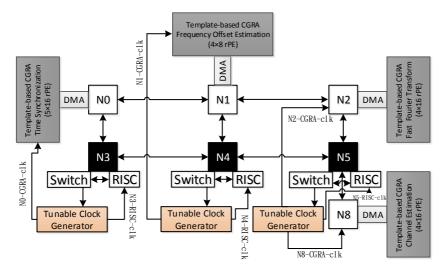

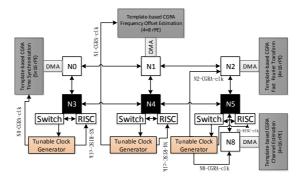

| 6.1        | A simplified overview of the HARP architecture with three RISCs and four template-based CGRAs in a processor/coprocessor model. [P.V]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46       |

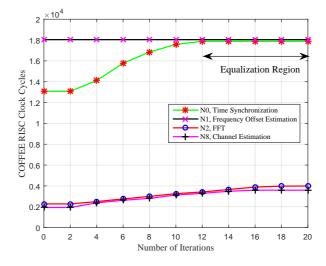

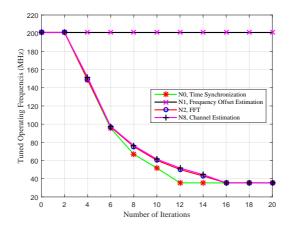

| 6.2        | Tuning the operating frequencies in the range of $\approx$ 35.0-200.0 MHz. [P.V]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47       |

List of Figures xi

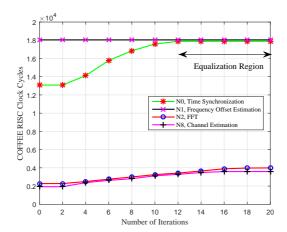

| 6.3 | Performance Equalization of the CGRAs based on the Worst-Case Execution |    |

|-----|-------------------------------------------------------------------------|----|

|     | Time. [P.V]                                                             | 47 |

| 6.4 |                                                                         |    |

|     | Active FCS, ASIC Inactive FCS, ASIC Active FCS with DFS and with DVFS.  |    |

|     | DP stands for Dynamic Power. [P.V]                                      | 52 |

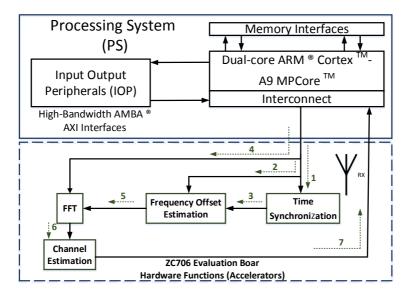

| 7.1 | An overview of an OFDM receiver implementation on ZC706 evaluation      |    |

| •   | board. [P.III]                                                          | 54 |

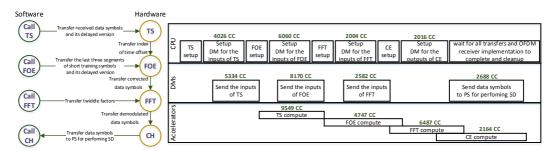

| 7.2 |                                                                         | ٠, |

| •   | function. [P.III]                                                       | 54 |

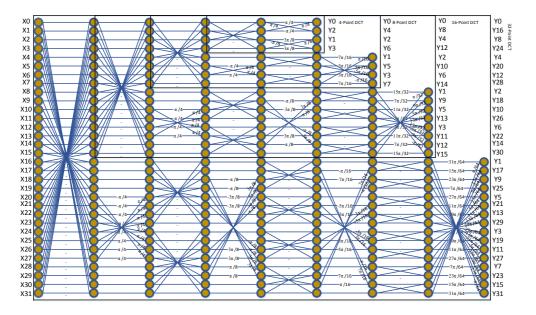

| 8.1 | DCT Flow Graph for 4/8/16/32-point                                      | 60 |

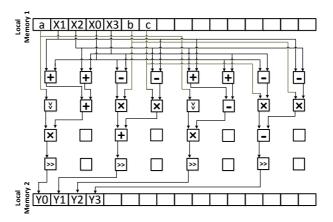

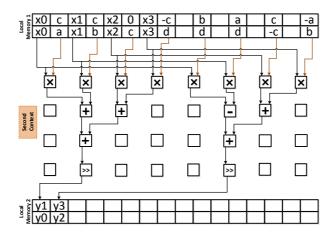

| 8.2 | Context for the Calculation of 1D DCT 4-point. [P.VI]                   |    |

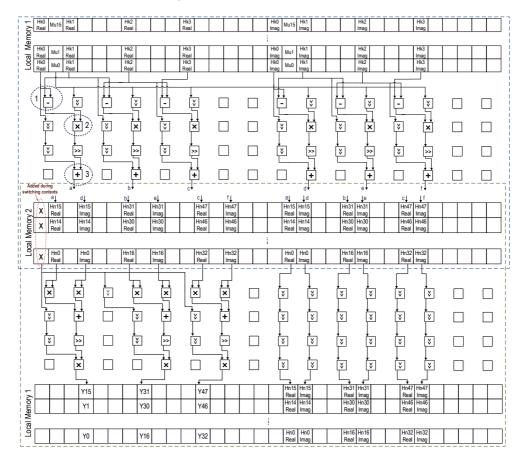

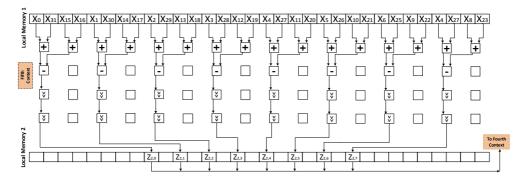

| 8.3 | Second & Third Contexts for the Calculation of 1D DCT 8-point. [P.VI]   | 63 |

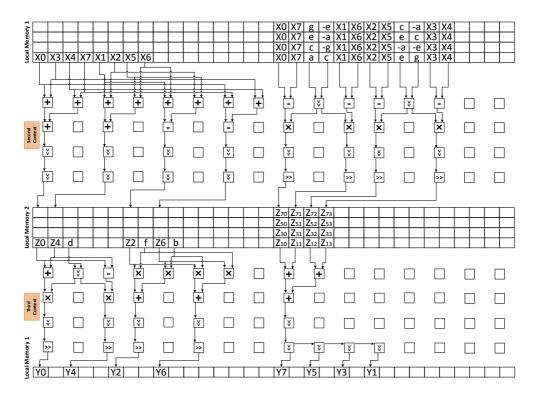

| 8.4 | Second, Third & Fourth Contexts for the Calculation of 1D DCT 16-point  | 64 |

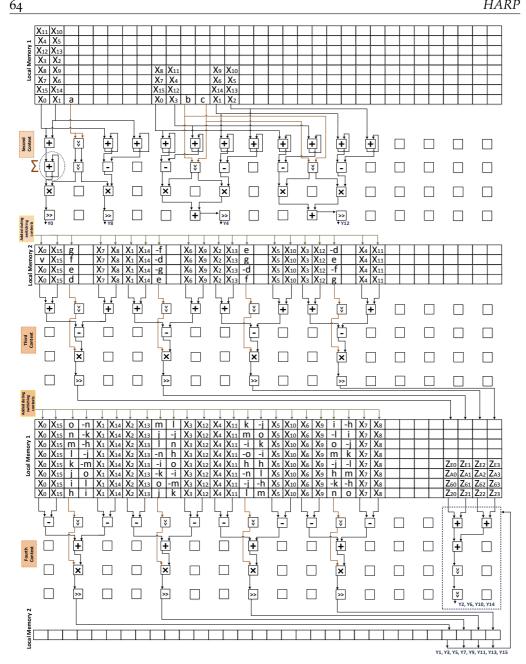

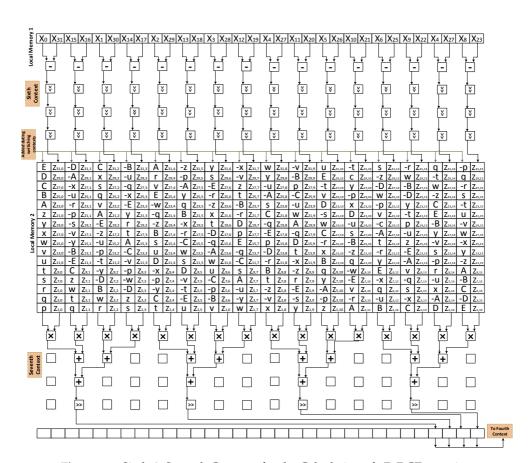

| 8.5 | Second, Third & Fourth Contexts for the Calculation of 1D DCT 32-point  | 68 |

| 8.6 | Fifth Context for the Calculation of 1D DCT 32-point                    | 69 |

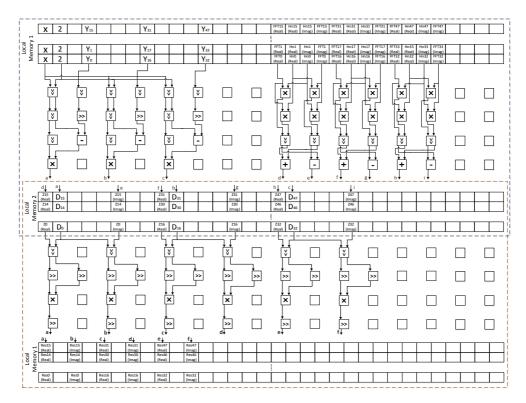

| 8.7 | Sixth & Seventh Contexts for the Calculation of 1D DCT 32-point         | 69 |

| 8.8 | Context for the Calculation of 1D 4-point DST. [P.VI]                   | 70 |

| 8.9 | Abridged general view of Multi-purpose DCT/DST-specific accelerator on  |    |

|     | HARP platform. [P.VI]                                                   | 70 |

# **List of Tables**

| 5.1        | Clock cycles required for data transfer and processing at different stages. In the table, * signs represent data transfer from CGRA to Node's data memory.                                             |          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.2        | [P.IV]                                                                                                                                                                                                 | 38       |

| 5.3        | (5SGXEA4H1F35C1) FPGA device. [P.IV]                                                                                                                                                                   | 41       |

| 5.4        | tion. [P.IV]                                                                                                                                                                                           | 41       |

|            | tively. [P.IV]                                                                                                                                                                                         | 42       |

| 6.1        | Dynamic power dissipation of each node and the NoC before/after applying FCS on FPGA prototype. [P.V]                                                                                                  | 48       |

| 6.2        | Power consumption and area utilization of the nodes synthesized on ASIC at the operating frequency of 500.0 MHz (0.9V, ss, 125°C) and typical conditions                                               |          |

| 6.3        | (tt, 25°C, 1.0V) for estimating the power numbers. [P.V]                                                                                                                                               | 50       |

| <i>(</i> . | Gains are calculated against dynamic power at 1V and 500.0 MHz. [P.V]                                                                                                                                  | 50       |

| 6.4        | Dynamic power dissipation of each node before applying FCS, after applying FCS with dynamic frequency scaling (DFS) and also with DVFS on ASIC. [P.V]                                                  | 51       |

| 6.5        | General comparison of the impact of DFS technique on FPGA and ASIC dynamic power dissipation at the same operating condition. [P.V]                                                                    | 51       |

| 7.1        | CC required for processing in two platforms at different stages. Moreover, * and ** stand for the algorithms that have been implemented by SW instead                                                  |          |

| 7.2        | of HW and data transfer from HW to SW, respectively. [P.III] Performance comparison between SDSoC HW against HARP and SDSoC SW. * stand for the algorithms that have been implemented by SW instead of | 57       |

| 7.3        | HW. [P.III]                                                                                                                                                                                            | 57       |

| 7 3        | also resource utilization summary of HARP (Stratix-V (5SGXEA4H1F35C1) FPGA device) against ZC706. Acc stands for Accelerator. [P.III]                                                                  | 58       |

| 8.1        | Clock cycles required for data transfer and processing at different stages. D. Mem, Trans and Exe. stand for Data memory, Transfer and Execution,                                                      |          |

| 8.2        | respectively. [P.VI]                                                                                                                                                                                   | 65<br>66 |

List of Tables xiii

| 8.3 | Dynamic power and energy estimation of each CGRA node and the NoC.     |

|-----|------------------------------------------------------------------------|

|     | GPP and IL stand for General Purpose Processing and Integration Logic, |

|     | respectively. [P.VI]                                                   |

## 1 Introduction

With the continuous development of wireless mobile communications and embedded systems, Internet-of-Things (IoT) as a third wave of information technology will be widely used in homes, industries and cities. Because of its huge market prospects, IoT is a hot topic today and has been paid close attention by several companies and standardization bodies all over the world. It is expected that by 2020 more than 50 billion devices will get connected with each other over a network without requiring human-to-human or human-to-computer interaction. On the other hand, with increasing demand for additional bandwidth, new wireless communication technologies namely Long-Term Evolution (LTE) and 5G (the next generation of mobile internet connectivity) should employ Dynamic Spectrum Access (DSA) [2] for efficiently utilizing the spectrum across frequency, space and time while resolving spectrum scarcity issue. In this context, the reconfigurable wireless platforms can be utilized in order to realize DSA. It can be achieved by using Software Defined Radio (SDR) technology and its intelligent version called Cognitive Radio (CR) [3]. In order to design and implement the radio systems on multi-mode multi-standard transceivers, several requirements have to be fulfilled, mainly: flexibility, scalable high computational power to meet the real-time constraints by wireless communication systems, and power efficiency to meet the allocated tight power budget in radio systems. According to the mentioned requirements, Multi-Processor Systems-on-Chip (MPSoCs) are suitable architectures for the implementation of SDR by providing a high degree of flexibility as well as high computational power. In a SDR platform, most of the kernels related to signal processing can be implemented by programmable processing technologies including General Purpose Processor (GPP), Digital Signal Processor (DSP), Field Programmable Gate Array (FPGA) and Coarse-Grained Reconfigurable Arrays (CGRAs). Different types of data transmission schemes are employed in wireless communication systems such as Orthogonal Frequency Division Multiplexing (OFDM) which is important in SDR because of its ability to provide high data rates. OFDM systems split an input high-speed data stream into several parallel streams which demand parallel processing.

The importance of meeting the real-time constraints of the new wireless standards and their requirements for parallel processing make the reconfigurable architectures as one of the most successful platforms. They can provide high computational parallelism and throughput while having low energy. Reconfigurability means modifying the functionality at run-time for several applications which offers the flexibility of software with the performance of hardware. Reconfigurable architectures can be classified into three different categories (fine-grained, middle-grained and coarse-grained) based on the level of granularity. Furthermore, considering the requirement of IoT in future, a single-chip platform for providing multiple communication standards and a large processing bandwidth is still missing. The wireless communication terminals have to

be multi-functional in order to support multiple applications. Although many Single Instruction Multiple Data (SIMD) architectures like SODA (2007) [4] and Montium (2008) [5] have been proposed for SDR applications in the past decade, an efficient cognitive radio engine based on MPSoC has not been developed yet. Currently, highly heterogeneous multicore architectures and reconfigurable platforms are one of the best candidates in terms of the power-area efficiency for performing the complex signal processing systems as well as meeting the requirements of IoT. During the recent years, a handful of research groups around the world have focused their attention on reconfigurable systems, in particular CGRAs, for wireless signal processing. An array of predefined Processing Elements (PEs) is used in CGRAs to provide high computational power as well as low energy consumption.

In 1965, Moore's Law predicted that the number of transistors per chip doubles every two years at constant cost [6]. Then Dennard in 1974 showed that the power dissipation density can be kept constant by scaling the voltage and the dimensions of the transistor which was threatening an end to Moore's Law [7]. According to the Dennard scaling, voltage and current should be proportional to the linear dimensions of a transistor. Therefore, circuits can be operated at higher frequencies at the same power as the size of the transistors shrunk and the voltage was attenuated. Even though Dennard Scaling tried to show how CMOS devices can be scaled for constant power density, it ignored the baseline of power per transistor which is established by leakage current and threshold voltage. Subsequent to putting an end to Dennard Scaling, a team at Massachusetts Institute of Technology (MIT) found a solution in multicore scaling by presenting RAW microprocessor architecture in 2002 [8]. However, in 2010, the experimental work explained in [6] showed that only 7% of a 300mm<sup>2</sup> chip can be operated at full frequency under a power budget of 8oW which means an end also to multicore scaling. This inability to keep the power constant results to a technology-imposed utilization wall which affected multicore scaling. It states that in a single chip, all cores cannot be clocked at their maximum operating frequency due to a given Thermal Design Power (TDP) constraint which forced a large fraction of chip to be to be switched-off (dark) or to be operated at very low frequency (dim). The dark or dim part of the chip is called Dark- or Dim-Silicon, respectively. In 2012, Michael B. Taylor has introduced Four Horsemen of Dark Silicon as a four top contenders in order to deal with this issue which are characterized into four different approaches: shrink, dim, specialize and technology magic [9]. Among them, the Specialized Horseman suggested that the dark area of chip can be replaced by instantiating application-specific accelerators as the compute engines highly optimized for executing massively-parallel workloads of critical-priority applications. Therefore, the execution time can be decreased while the kernels operate at very low frequencies. In this regard, template-based CGRAs, employed to build up Heterogeneous Multicore Architectures (HMAs) using a Network-on-Chip (NoC), are advocated to be instantiated in the dark area of the chip. CGRAs can be used to generate special-purpose accelerators while being operated at a very low frequency. They are run-time reconfigurable and programmable with a higher level language, i.e., C/C++ and can offer enormous performance improvements. There are a number of already existing CGRA architectures such as Pixie (2017) [10], EXTRA (2015-2016) ([11], [12]), BUTTER (2007) [13], ADRES (2003-2007) ([14], [15] [16]), Morphosys (1998-2000) ([17], [18], [19], [20]) and PACT-XPP (2002-2003) ([21], [22]). Recent outcomes suggest designing heterogeneous multicore platforms which support user-specified scalability and are composed of general-purpose and reconfigurable special-purpose cores with seamless integration capability while the communication backbone can be a NoC ([6],

[9]). On the other hand, CGRAs have potentially high transient power dissipation which requires to be mitigated by employing SElf-awarE Computing (SEEC) models and various techniques are required such as Dynamic Voltage and Frequency Scaling (DVFS) and Feedback Control System (FCS) [23]. Furthermore, in order to support IoT infrastructure, it is important that the power dissipation and energy consumption by processors reduces and the on-chip resource utilization increases. SEEC model has been introduced to dynamically control the voltage and operating frequency by using an adaptive feedback control system to mitigate the power dissipation. In this context, the instantaneous power/heat dissipation will be decreased to minimize the dark part of the chip. It should be mentioned that the frequency control system also dims that part of the chip.

#### 1.1 Objective and Scope of Research

The primary objective of this thesis is the evaluation of Heterogeneous Accelerator-Rich Platform (HARP) by subjecting it to a stringent test to determine its potential architectural fallacies and pitfalls. HARP is already designed as a template-based architecture programmable in C language in a collaboration between the University of Chicago (UoC), IL, USA, and our research group in TUT for maximizing the number of computational resources for algorithm acceleration ([24], [25]). There are a number of already existing heterogeneous platforms with nearly similar design philosophy that are generally structured as many general-purpose and application-specific cores connected over a NoC, such as MORPHEUS (2007-2017) ([26], [27], [28]) and P2012 (2012-2014) ([29], [30]). However, the efficient utilization of on-chip resources has to be justified. It is observable that most of the on-chip resources are not utilized over the entire frame of execution-time and are over or under resourced for the applications that they are designed for [6]. The HARP template allows the designer to instantiate a heterogeneous reconfigurable platform with a very large amount of custom-tailored computational resources for high performance. The HARP template is composed of nine nodes where several template-based CGRAs ([31], [32]) of specific sizes tailored for specific applications are integrated with one or a few Reduced Instruction-Set Computing (RISC) cores over a NoC as a processor/coprocessor model. The template-based CGRAs can work in parallel to execute different tasks independently or in communication with each other in the case of data dependency.

The HARP template is first evaluated by implementing the OFDM receiver blocks as a proof-of-concept. OFDM is one of the most important data transmission schemes in SDR and also one of the candidates to be employed in 5G. An OFDM receiver is composed of some of the most computationally-intensive parallel tasks such as Fast Fourier Transform (FFT), Correlation and Complex Matrix-Vector Multiplication (MVM) which should be implemented by crafting template-based CGRAs. Furthermore, it includes some serial in nature tasks which require to be performed by GPP. Recently, a power efficient, FPGA-based, parallel-pipelined architecture for an OFDM baseband modulator has been proposed in order to support a set of OFDM numerologies for future 5G communication systems ([33], [34]). Therefore, OFDM receiver with such a fine mixture of serial and parallel algorithms is selected and implemented based on IEEE 802.11a/g standard specifications [35] in order to explore and evaluate almost all the design features of HARP. The implementation of OFDM receiver blocks has led to scale template-based CGRAs to different dimensions and establish almost all possible ways of PE interconnections based on the algebraic expressions of each particular application

while time-multiplexed patterns for data placement in the CGRA memories is explored. Due to the data dependency between the blocks of an OFDM receiver, the data must be exchanged among different crafted template-based CGRAs over the NoC by using Direct Memory Access (DMA) device for complete OFDM implementation. The instantiated few RISC cores in this design and test regime distribute the configuration streams and the data to be processed to all the integrated template-based CGRAs in addition to act as the controllers. The RISC cores are also available for performing the serial in nature algorithms and establishing synchronization among all the CGRA nodes and monitor their performance. Although the implementation of an OFDM receiver provided sufficient switching activity on all the NoC nodes and resulted in meaningful and tangible conclusions, a single case-study was not be enough to empirically assess an architecture. Therefore, the author further evaluated the HARP template by selecting various sizes of Discrete Cosine Transform (DCT) and Discrete Sine Transform (DST) dedicated for High Efficiency Video Coding (HEVC) standard. In both case-studies, the performance of each template-based CGRA, the collective performance of the entire platform and the NoC traffic are recorded in terms of the number of Clock Cycles (CC) and several high-level performance metrics such as Giga Operations Per Second per milliWatts (GOPS/mW). Furthermore, cross-technology comparisons among HARP and other state-of-the-art platforms are performed.

This thesis is also addressing the power and energy issues of the computer systems by tailoring the HARP for self-aware computing model. To support IoT infrastructure, it is important that the power dissipation and energy consumption by processors reduces and the on-chip resource utilization increases. For this purpose, the HARP template is estimated in 28nm Stratix-V FPGA device ([36], [37]) and also 28 nm Ultra-Thin Body and Buried oxide (UTBB) Fully-Depleted Silicon-On-Insulator (FD-SOI) ASIC technology in order to provide the possibility of scaling the voltage in addition to the frequency and get more benefits in terms of dynamic power dissipation reduction. The self-aware computing model applied on HARP exploits Feedback Control System (FCS) which constantly monitors the execution-time of each core. Then based on the worst executiontime, FCS dynamically scales the operating frequency and the voltage of each CGRA node of the NoC. As a result, the performance of the overall system is equalized towards a desired level besides mitigating the dynamic power dissipation. The upgraded HARP can act as an energy-efficient general-purpose transceiver platform that is cognitive to many radio standards and can provide high throughput while consuming as low energy as possible. Moreover, the Dark Silicon as a resource will be harvested and transformed into efficiently utilizable processing units. In other words, the proposed approach is utilizing Dark Silicon for performing massively-parallel workloads of critical-priority applications by employing the specialized accelerators in large-scale heterogeneous multicore architecture. HARP lays an excellent foundation to investigate techniques to replace the Dark Silicon with high-performance silicon dissipating very low power and energy.

The author also presents a HW/SW codesign of an OFDM receiver by using High-Level Synthesis (HLS) tools from Xilinx. The tool provided an embedded C/C++ application programming interface in order to develop heterogeneous embedded systems. The fine mixture of serial and parallel algorithms makes an OFDM receiver as a suitable candidate to be implemented into hardware by compiling the functions written in C/C++ code for every block separately. A general comparison among the HARP template and ZC706 evaluation board with the implemented OFDM receiver is presented.

The main results achieved in this thesis can be highlighted as follows:

- Evaluation of almost all the architectural features of HARP by design and implementation of IEEE 802.11a/g receiver blocks as well as 4/8/16/32-point DCT and 4-point DST dedicated for HEVC;

- Proof-of-concept scalable template-based HARP suitable for diverse needs of IoT as a general-purpose power- and energy-aware transceiver platform;

- Methodology for improving Dark Silicon in embedded computing platforms by applying self-aware computing model on HARP and mitigating the signal transition activity over the entire platform with reference to the worst-case performing core for power conservation;

- Demonstration of modularity and regularity in the HARP as well as exploration of an architectural constant for HARP based on GOPS/mW which is not changeable by scaling the computational resources of a platform;

- Allocation of computational resources at design-time in order to utilize most of the on-chip resources over the entire frame of execution time;

- Demonstration of the benefits of scaling the integrated template-based CGRAs to very large dimensions and maximizing the number of reconfigurable processing resources on a platform by comparing the HARP template against other state-ofthe-art platforms;

- Providing important insight and guidelines for the designers in order to implement near-optimal mapping of target applications in terms of performance, resource utilization, power dissipation and execution time.

#### 1.2 Author's Contribution to the Published Work

The work presented in this thesis has mainly been extracted from the following publications in which the author was the first author and the research area was proposed and supervised by Prof. Jari Nurmi. He has contributed to all of the publications and provided extensive feedback for the manuscript drafts.

In *publication [P. I]*, the author designed and implemented the IEEE 802.11a/g receiver blocks by using the template-based CGRAs as application-specific accelerators to COFFEE RISC processor. The author designed all the accelerators by crafting the template-based CGRA, based on the algebraic expressions of the required algorithms. The accelerators designed are synthesized on the Stratix-V FPGA device and evaluated for performance in terms of the number of clock cycles, speed-up in comparison with the RISC software implementation, resource utilization, maximum operating frequency, power dissipation and energy consumption. Dr. Waqar Hussain and Prof. Jari Nurmi provided technical comments and supervised the entire work.

In *publication [P. II]*, the author put his effort in optimizing the implementation of correlation accelerator used for time synchronization block required in IEEE 802.11a/g receiver by scaling-up the template-based CGRA. The accelerator is synthesized on FPGA device and the power dissipation is estimated by simulating the postfit gate-level FPGA netlist. Furthermore, the author performed cross-technology comparisons of the

platform with the other state-of-the-art platforms in terms of GOPS and GOPS/mW. Dr. Waqar Hussain and Prof. Jari Nurmi gave the final comments on the work.

In *publication [P. III]*, the author presented an implementation of IEEE 802.11a/g receiver blocks by employing HLS tool from Xilinx called SDSoC which provides an embedded C/C++ application programming interface for developing heterogeneous embedded systems. The experimental platform in this case-study was Zynq SoC containing an ARM processor besides a FPGA. Every block of the receiver was written by the first author in C/C++ code to be realizable on the FPGA and the ARM processor and then evaluated on ZC706 board and compared against the HARP. This work was completely performed by the first author during his research visit to Ruhr University Bochum (RUB), while the second author assisted in working with HLS tool and ZC706 board. The overall work was supervised by Prof. Diana Göhringer and Prof. Jari Nurmi.

In *publication [P. IV]*, which is an extension to the author's first and second conference papers published in DASIP 2015 and NORCAS 2015, the author evaluated the HARP by implementing IEEE 802.11a/g receiver blocks as designs for the test of functionality. In this paper, the author mapped and integrated all designed receiver blocks using the template-based CGRAs on HARP and then subjected it to a stringent test for identifying potential architectural fallacies and pitfalls. The author also assigned an architectural constant based on achieved GOPS/mW to HARP due to its scalability and regularity which ensures application-independent figure of merit. Dr. Waqar Hussain and Prof. Jari Nurmi gave technical comments and invaluable feedback and supervised the entire work.

In *publication [P. V]*, which is an extension to the first author's conference paper (published in NORCAS 2017) with an invitation, the author presented an integrated self-aware computing model in the HARP to mitigate the power dissipation of an IEEE 802.11a/g receiver. In the proposed self-aware computing model, FCS is exploited for monitoring the execution-time of the NoC nodes constantly and scaling their operating frequency and the voltage dynamically based on the worst execution-time. The implementation is estimated on the FPGA-based prototyped platform and also in 28nm Ultra-Thin Body and Buried oxide (UTBB) Fully-Depleted Silicon-On-Insulator (FD-SOI) ASIC technology. This work was mainly done by the first author, while the second author assisted in synthesizing the whole platform on ASIC and scaling the voltage and frequency. Prof. Davide Rossi and Prof. Jari Nurmi gave invaluable feedback on overall work and helped the first author to come up with the final results.

In *publication [P. VI]*, the author designed and implemented various sizes of DCT/DST-specific accelerators on HARP for HEVC standard by using template-based CGRAs. The final architecture consists of 4/8/16/32-point DCT and 4-point DST. The accelerators are arranged over a NoC structure along with three RISC cores. The author reported the performance of each DCT/DST-specific accelerator, the collective performance of the whole platform and the NoC traffic in terms of the number of clock cycles and several high-level performance metrics. The whole platform is synthesized on FPGA device and then, total power dissipation and energy consumption based on post placement and routing information are reported. Moreover, the architectural constant of HARP in terms of GOPS/mW is again proven by the author. The entire work was completely performed by the first author, while the writing of introduction and the equations related to DCT/DST was done by the help of the second author. This work was fully supervised by Prof. Jari Nurmi.

1.3. Thesis Outline 7

#### 1.3 Thesis Outline

This manuscript is organized as follows: Chapter 2 presents some of the existing state-of-the-art platforms related to the work presented in the next chapters. Chapter 3 explains the architecture of HARP and the template-based CGRAs used for integration, the overall functionality of HARP and the internal structure of the NoC nodes [P.IV]. Chapter 4 presents the design and implementation of OFDM receiver blocks by using template-based CGRAs ([P.I], [P.II]). Evaluation of HARP by instantiating and implementing an OFDM receiver base-band processing as well as distributing the data among different nodes are discussed in Chapter 5 [P.IV]. Chapter 6 focuses on power mitigation and performance equalization of HARP on FPGA and ASIC devices by employing DFS and DVFS techniques, respectively [P.V]. Chapter 7 presents a novel HW/SW co-design of OFDM receiver on ZC706 board using the High-Level Synthesis (HLS) tool from Xilinx called Software Defined System-on-Chip (SDSoC) [P.III]. Chapter 8 concentrates on the design and implementation of multi-purpose DCT/DST-specific accelerator by using template-based CGRAs on HARP [P.VI]. Finally, in Chapter 9, concluding remarks, open issues and the future work is presented.

## 2 Literature Review

Application-specific accelerators in the form of processor/coprocessor model have been developed and embedded in MPSoC for accomplishing computationally intensive tasks. The most powerful class of accelerators are CGRAs, which act as coprocessor to a programmable processor to form a heterogeneous multicore platform where they can be employed simultaneously and independently of each other or even in communication with each other at run-time. Prior to creating multicore platforms in processor/coprocessor models, single core as a GPP has been in use for performing many applications. Meanwhile, some accelerators have been also assigned for some computationally intensive tasks. Later on, Very Long Instruction Word (VLIW) machines have been developed in order to support large-scale parallel applications [38]. As the time passed, VLIW architectures were combined with DSP processors for supporting also DSP applications targeting high-end mobile communication [39]. In multiocore platforms, the accelerators can be operated as coprocessors to processors either in loose or tight coupling. In loose coupling, multiple accelerators are connected to a processor with relatively low bandwidth and can work simultaneously [29]. In tight coupling, the bandwidth is higher than loose coupling for communication with the processor, which enables faster data transfer and synchronization ([40], [41]). The accelerators can be tightly-coupled to the processor by either employing coprocessor bus or integrating the accelerator in the datapath.

### 2.1 Reconfigurable Devices

In the recent past, reconfigurable devices become popular architectures due to their flexibility as well as because of time and cost reduction in system development. Reconfigurable devices are able to switch their functions at run-time occasionally based on the data flow specified at design-time by application developer for various purposes. Therefore, reconfigurable platforms are able to implement many different tasks. In general there are three different reconfigurable devices, which are classified according to their level of granularity: fine-grained (with granularity of less than 4-bit), middle-grained (with granularity of less than or equal to 8-bit) and coarse-grained (with granularity of more than 8-bit) [26]. Fine-grained devices have the most optimal resource utilization due to their fine level of granularity while the placement and routing is more demanding. Middle-grained devices are a compromise among fine-grained and coarse-grained devices with higher bit-width processing and simpler compilers for design and implementation in comparison with the fine-grained devices. Coarse-grained devices have the simplest compilers and the highest level of granularity while the processing of wide range of applications on the word level can get supported. In the following sections, several existing examples of fine-, middle-, and coarse-grained devices in the literature

are described briefly.

#### 2.1.1 Fine-Grained Devices

Fine-grained devices have much more PEs than coarse-grained devices while the granularity level of the PEs are 1 to 4 bits. Nowadays most of the applications are working with 8, 16 or 32-bit operations. In comparison with the coarse-grained devices, fine-grained devices should employ more number of PEs in order to execute the same operation at the cost of more resource utilization and inefficient mapping. One of the most promising fine-grained devices are FPGA and in particular embedded FPGA (eFPGA). Since FPGAs are not suitable for run-time reconfiguration, a small FPGA block is embedded in a fixed architecture (called eFPGA) to enable run-time reconfigurablity. An FPGA is composed of Logic Elements (LEs) including a Look-Up Table (LUT), a few logic gates, 2-to-1 multiplexers and also a few Flip-Flops (FFs). In the market, Xilinx [42] and Altera [43] are the most well-known fine-grained devices. For instance, in a case-study done by [44], three eFPGAs are integrated with the NoC-based system. One of the fine-grained devices is GARP architecture, which acts as a reconfigurable coprocessor, tightly coupled with GPP and offering a low granularity by mainly 2-bit and 4-input LUTs [45]. GARP consists of PE arrays while in each row one control block and 23 logic blocks are instantiated. The size of PE arrays can be modified at designtime. In order to keep the operating frequency fixed, the connectivity on its fabric is limited [46]. Another fine-grained device is FlexEos as an eFPGA [47]. It consists of 4K Multi-Function logic Cells (MFC) according to SRAM 1-bit Lookup-Tables (LUT). FlexEOS as a reprogrammable SRAM-based scalable FPGA fabric built on high-density multi-function logic cells can be programmed by using standard description languages, i.e., VHDL and Verilog. Another instance of fine-grained reconfigurable unit is MOLEN, which acts as a tightly-coupled coprocessor to a GPP ([48], [49]). There is possibility for MOLEN to be mapped on Xilinx FPGA chip while the FPGA fabric itself acts as an accelerator. Although MOLEN is physically separated from the GPP, added special instructions can be operated on that due to the extension of Instruction-Set Architecture (ISA) of the GPP.

#### 2.1.2 Middle-Grained Devices

Middle-grain reconfigurable devices have been introduced to support the maximum word length of eight. Therefore, the algorithm with the same processing word length can be mapped on them. It has to be mentioned that, compared to fine-grained devices, mapping the algorithms on middle-grained reconfigurable units is more difficult due to increasing the processing word length. The middle-grain paradigm could provide a good compromise among area, performance and power while different word length applications can be supported. One of the middle-grained reconfigurable devices in the literature is PiCoGA-III consisting of Reconfigurable Datapath Unit (RDU) ([50], [51]). Each RDU is composed of a 4-bit LUT, a 4-bit ALU and a 4-bit integer and Galois field multiplier. Another middle-grained reconfigurable processing engine is DART, which support 8- and 16-bit processing word length ([52], [53]).

#### 2.1.3 Coarse-Grained Devices

CGRAs are one of the most promising platforms with the possibility to support a 8-bit, 16-bit and 32-bit arithmetic or logic operation onto a single PE. In CGRAs, an array

of predefined PEs provides a high-level of granularity, high data level parallelization, high computational power, a large bandwidth, high throughput processing and low energy consumption. They are reconfigurable and programmable with a higher level language and can yield tremendous performance improvements while being operated at a very low frequency. Due to the internal structure and the level of granularity of CGRAs, they are suitable for performing massively-parallel computationally-intensive signal processing algorithms. CGRAs are successfully evaluated for a proof-of-concept for a set of data parallel applications such as FFT [32], Correlation [54], Wideband Code Division Multiple Access (WCDMA) cell search [55], image and video processing ([56], [57]), Finite Impulse Response (FIR) filtering [58]. Against all advantages of CGRAs, they have potentially high transient power dissipation and occupy a large area of a few million gates. Furthermore, most of the CGRAs have a fixed set of PEs and interconnections, which are not optimum in terms of cost and performance. Some of the CGRA architectures found in literature are briefly described as follows.

#### 2.1.3.1 BUTTER

BUTTER acts as a coprocessor for COFFEE RISC core. It has been developed by our research group in order to accomplish computationally-intensive tasks [13]. It is composed of a  $4\times8$  array of PEs. However, the size of PE array can be scaled-up/down at design-time. The PEs are connected to each other in a point-to-point fashion for exchanging data. Each PE has a functional unit for arithmetic and logic operations with the fixed granularity level at 32-bit and also with the ability to support integer and single precision floating-point. The configuration data and the data to be processed can be transferred from the main memory to the CGRA with the help of a DMA device. BUTTER is characterized by run-time reconfigurability, which means the possibility of selection of connection at run-time. The entire platform is synthesized on FPGA device.

#### 2.1.3.2 ADRES

Architecture for Dynamically Reconfigurable Embedded Systems (ADRES) as a coarsegrained reconfigurable architecture is tightly coupled with Very Long Instruction Word (VLIW) processor ([14], [15] [16]). Compared to the other CGRAs, ADRES showed many advantages such as improvement in terms of the performance, a simplified programming model, reduction of communication costs and substantial resource sharing. The VLIW processor and CGRA are integrated into a one single architecture with two virtual functional views (VLIW view and reconfigurable array view). The architecture of ADRES is composed of reconfigurable array of  $8\times8$  elements. The elements are connected in a certain topology, which comprise mainly Functional Units (FU), Register Files (RF) and routing resources. The first row of reconfigurable arrays (VLIW view) is FUs while the rest of the rows (called reconfigurable matrix) are Reconfigurable Cells (RC), which comprise FUs and RFs and belong to the second view. The FUs, which can also be heterogeneous supporting various operation sets are connected together through one multi-port global Data Register File (DRF) with the data bus width of 32 bits. The RCs communicate through a multi-port global DRF, Local Register Files (LRF) and dedicated interconnects between the FUs. In order to store the intermediate data, the RFs can be employed in such a way that the words with the length of 16 and 64 bits should be stored in local and global RF, respectively. The routing resources are composed of wires, buses and networks. The RCs are used to accelerate the dataflowlike kernels in a highly parallel way. On the other hand, for performing the non-kernel

codes, VLIW can be used by exploiting Instruction-Level Parallelism (ILP). Since ADRES is basically a processor/co-processor model, VLIW and reconfigurable array views can share some resources and therefore, their executions will never overlap with each other. In order to generate ADRES specific intances, an XML-based architecture specification language can be utilized. ADRES is synthesized on 90 nm CMOS technology and delivers a performance of 40 MOPS/mW.

#### 2.1.3.3 Morphosys

The Morphosys architecture as a single chip is designed to operate on 8 or 16-bit data ([17], [18], [19], [20]). It is composed of an 8×8 array of reconfigurable processing units called Reconfigurable Cell (RC) with configuration memory, tightly coupled 32-bit general-purpose processor (TinyRISC) and a high-bandwidth memory interface. The operation of the RC array is monitored by a RISC core. The RC array is partitioned into four quadrants. The data transfer can be initiated by RISC core between an external memory and RC array by using two sets of Frame Buffers (FBs), each has two memory banks. Each RC incorporates an ALU for fixed-point operations, a multiplier, a shift unit, input multiplexers and a register file. The RC array can be configured by using 32-bit context word, which can be distributed to all eight RCs in the same column or row. Special instructions were added to TinyRISC's ISA to transfer RC array related operations such as control operations, configuration and data transfer between the array and the main memory.

#### 2.1.3.4 PACT-XPP

PACT-XPP as a self reconfigurable processing engine is based on a hierarchical array of coarse-grained architectures ([21], [22]). It is composed of 3×3 adaptive computing elements called Processing Array Elements (PAEs) and packet-oriented communication network. The strength of PACT-XPP is powerful run-time partial reconfiguration capability, which makes the PAEs independent of each other. It means that some PAEs can be reconfigured for a new functionality while the other PAEs on different parts of the array can keep computing data simultaneously. Reconfiguration is externally-triggered event-based by special event signals originating within the array. The algorithms written in C subset program can be mapped on PACT-XPP by using vectorizing C compiler XPP-VC. PACT-XPP delivers a peak performance of 57.6 GOPS at 150.0 MHz.

#### 2.1.3.5 Pixie

Pixie as a heterogeneous Virtual CGRA (VCGRA) has been introduced for high performance image processing applications [10]. The VCGRA is composed of generic PEs and virtual channels, which are described by VHDL and optimized by using the parameterized configuration tool flow. The optimization has been resulted in resource reduction of 24% and 82% for each PE and virtual channel, respectively. The PEs are connected to each other by employing virtual connection blocks and switch blocks. The PEs of VCGRA are able to execute various arithmetic operations such as addition, subtraction, multiplication and division. In comparison with the Fine-Grained FPGAs, the compilation time has been reduced since the designers can write the code at a higher abstraction level.

#### 2.1.3.6 EXTRA