Teemu Pitkänen

Fast Fourier Transforms on

Energy-Efficient Application-Specific Processors

Julkaisu 1240 • Publication 1240

Tampereen teknillinen yliopisto. Julkaisu 1240 Tampere University of Technology. Publication 1240

Teemu Pitkänen

# Fast Fourier Transforms on Energy-Efficient Application-Specific Processors

Thesis for the degree of Doctor of Science in Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB109, at Tampere University of Technology, on the 19<sup>th</sup> of September 2014, at 10 am.

### **ABSTRACT**

Many of the current applications used in battery powered devices are from digital signal processing, telecommunication, and multimedia domains. Traditionally application-specific fixed-function circuits have been used in these designs in form of application-specific integrated circuits (ASIC) to reach the required performance and energy-efficiency. The complexity of these applications has increased over the years, thus the design complexity has increased even faster, which implies increased design time. At the same time, there are more and more standards to be supported, thus using optimised fixed-function implementations for all the functions in all the standards is impractical. The non-recurring engineering costs for integrated circuits have also increased significantly, so manufacturers can only afford fewer chip iterations. Although tailoring the circuit for a specific application provides the best performance and/or energy-efficiency, such approach lacks flexibility. E.g., if an error is found after the manufacturing, an expensive chip iteration is required. In addition, new functionalities cannot be added afterwards to support evolution of standards.

Flexibility can be obtained with software based implementation technologies. Unfortunately, general-purpose processors do not provide the energy-efficiency of the fixed-function circuit designs. A useful trade-off between flexibility and performance is implementation based on application-specific processors (ASP) where programmability provides the flexibility and computational resources customised for the given application provide the performance.

In this Thesis, application-specific processors are considered by using fast Fourier transform as the representative algorithm. The architectural template used here is transport triggered architecture (TTA) which resembles very long instruction word machines but the operand execution resembles data flow machines rather than traditional operand triggering. The developed TTA processors exploit inherent parallelism of the application. In addition, several characteristics of the application

have been identified and those are exploited by developing customised functional units for speeding up the execution. Several customisations are proposed for the data path of the processor but it is also important to match the memory bandwidth to the computation speed. This calls for a memory organisation supporting parallel memory accesses. The proposed optimisations have been used to improve the energy-efficiency of the processor and experiments show that a programmable solution can have energy-efficiency comparable to fixed-function ASIC designs.

#### **PREFACE**

The work presented in this Thesis has been carried out in the Department of Computer Systems at Tampere University of Technology, Finland and in part during my research visit at Massachusetts Institute of Technology, Cambridge, MA, USA.

I would like to express my gratitude to my supervisor Prof. *Jarmo Takala* for his support, motivation, and efforts to make this research work possible. My thesis Reviewers, Prof. *Holger Blume* and Dr. *Seppo Virtanen* deserve my deepest gratitude and thanks from their valuable and insightful comments. Because their constructive comments this Thesis has achieved its final form.

Also, I would like to thank Prof. *Arvind* from MIT to make my exchange visit possible and for his help and guidance in the US. Prof. *Mikko Tiusanen* deserve my thanks for valuable comments and support. I would like to thank also Prof. *Olli Silvén* from the University of Oulu for his encouraging support.

My friends and colleagues deserve also special thanks. Especially, the closest colleagues during the research work of this Thesis, Dr. *Perttu Salmela*, Dr. *Jari Heikkinen*, Dr. *Pekka Jääskeläinen*, Dr. *Jarno Tanskanen*, M.Sc. *Lassi Nurmi*, M.Sc. *Vladimir Guzma*, M.Sc. *Otto Esko*, M.Sc. *Heikki Kultala*, M.Sc. *Tero Partanen*, and M.Sc. *Riku Uusikartano*, thank for many fruitful discussions, observant comments, motivation, helpful assistance, constructive comments, and infectious enthusiasm. In addition, I wish to express special thanks to Prof. Arvind's research group at MIT and in particular Dr. *Nirav Dave* and M.Sc. *Myron King*, for their assistance and creative atmosphere.

Yet, there are still far too many people to name, who deserve thanks and with whom this work has been carried out. All the mentioned and many unmentioned people have had a great influence on this Thesis. Without them this work would not have been possible.

This Thesis was financially supported by the Foundation of Advancement of Technology (TES) and the National Technology Agency of Finland (TEKES). The financial support is appreciated and acknowledged gratefully.

Finally, I express the deepest gratitude to the *Pitkänen* family and *Heidi* for the support and motivation and to all the friends for their influence on this Thesis.

*Tampere, July 27, 2014*

Teemu Pitkänen

# TABLE OF CONTENTS

| Lis | st of I | Publications                                       | vii  |

|-----|---------|----------------------------------------------------|------|

| Lis | st of I | Figures                                            | ix   |

| Lis | st of T | Tables                                             | xi   |

| Lis | st of A | Abbreviations                                      | xiii |

| Lis | st of S | Symbols                                            | XV   |

| 1.  | Intro   | oduction                                           | 1    |

|     | 1.1     | Scope and Objective of Research                    | 4    |

|     | 1.2     | Main Contributions                                 | 5    |

|     | 1.3     | Author's Contribution                              | 6    |

|     | 1.4     | Thesis Outline                                     | 7    |

| 2.  | Fast    | Fourier Transform                                  | 9    |

|     | 2.1     | Discrete Fourier Transform and its Fast Algorithms | 9    |

|     | 2.2     | Radix-p Algorithms                                 | 10   |

|     | 2.3     | Radix-2 <sup>r</sup> Algorithms                    | 12   |

|     | 2.4     | Mixed-Radix FFT                                    | 14   |

|     | 2.5     | In-Place Computations                              | 15   |

|     | 2.6     | Permutations and Operand Access                    | 17   |

| 3.  | Twic    | ddle Factor Generation for FFT                     | 21   |

|     | 3.1     | Twiddle Factors                                    | 21   |

|     | 3.2     | Polynomial and Recursive Twiddle Factor Generation | 22   |

|     | 3.3    | Twiddl    | le Factor Generation Based on CORDIC            | 23  |

|-----|--------|-----------|-------------------------------------------------|-----|

|     | 3.4    | Method    | ds Based on Lookup Tables                       | 25  |

|     | 3.5    | Extens    | ion for Lookup Table Methods to Mixed-Radix FFT | 27  |

| 4.  | Arch   | nitecture | s for FFT Computation                           | 29  |

|     | 4.1    | Fixed-    | Function Architectures for FFT                  | 30  |

|     |        | 4.1.1     | Memory Architecture                             | 32  |

|     |        | 4.1.2     | Pipelined Architectures                         | 33  |

|     |        | 4.1.3     | Cache-Memory Architecture                       | 35  |

|     | 4.2    | FFT or    | n Programmable Processors                       | 36  |

|     | 4.3    | Propos    | ed Architecture Based on Transport Triggering   | 38  |

|     | 4.4    | Energy    | 7-Efficiency Comparison                         | 41  |

| 5.  | Cone   | clusions  |                                                 | 45  |

| Bi  | bliogr | aphy .    |                                                 | 49  |

| [P  | 1] Pul | olication | 1                                               | 59  |

| [P: | 2] Pul | olication | 2                                               | 71  |

| [P. | 3] Pul | olication | 3                                               | 77  |

| [P  | 4] Pul | olication | 4                                               | 89  |

| ΓD  | 51 Duk | dication  | 5                                               | 103 |

#### LIST OF PUBLICATIONS

This Thesis consists of an introductory part and five original publications. In the text, these publications are referred to as [P1] to [P5].

- [P1] T. Pitkänen, R. Mäkinen, J. Heikkinen, T. Partanen, and J. Takala, "Low-Power, High-Performance TTA Processor for 1024-Point Fast Fourier Transform," in *Embedded Computer Systems: Architectures, Modeling, and Simulation: Proc. 6th Int. Workshop SAMOS VI*, S. Vassiliadis, S. Wong, T.D. Hämäläinen, Eds. Berlin, Germany: Springer-Verlag, 2006, vol. LNCS 4017, pp. 227–236.

- [P2] T. Pitkänen, R. Mäkinen, J. Heikkinen, T. Partanen, and J. Takala, "Transport Triggered Architecture Processor for Mixed-Radix FFT," in *Proceedings of the Fortieth Asilomar Conference on Signals, Systems, and Computers*, Pacific Grove, CA, Oct. 29–Nov. 1, 2006, pp. 84–88.

- [P3] T. Pitkänen, T. Partanen, and J. Takala, "Low-Power Twiddle Factor Unit for FFT Computation," in *Embedded Computer Systems: Architectures, Modeling, and Simulation: Proc. 7th Int. Workshop SAMOS VII*, S. Vassiliadis, M. Berekovic, T.D. Hämäläinen, Eds. Berlin, Germany: Springer-Verlag, 2007, vol. LNCS 4599, pp. 233–240.

- [P4] T. Pitkänen, J. Tanskanen, R. Mäkinen, and J. Takala,"Parallel Memory Architecture for Application-Specific Instruction-Set Processors," *Journal of Signal Processing Systems*, vol. 57, no. 1, pp. 21–32, October, 2009.

- [P5] T. Pitkänen and J. Takala, "Low-Power Application-Specific Processor for FFT Computations," *Journal of Signal Processing Systems*, vol. 63, no. 1, pp.165–176, April, 2011.

### LIST OF FIGURES

| 1  | Principal block diagram of OFDM system                             | 4  |

|----|--------------------------------------------------------------------|----|

| 2  | Signal flow graphs of 8-point radix-2 DIT and DIF FFT algorithms . | 11 |

| 3  | Radix-2 FFT butterflies                                            | 12 |

| 4  | Signal flow graph of radix-4 butterfly                             | 13 |

| 5  | Signal flow graph of 32-point mixed-radix DIT FFT                  | 15 |

| 6  | Signal flow graphs of in-place FFTs                                | 16 |

| 7  | Operand address generation for in-place FFT                        | 17 |

| 8  | Twiddle factors in radix-2 FFT algorithm                           | 23 |

| 9  | Principal architectures for fixed-function FFT processors          | 31 |

| 10 | Principal organisation of scalable architecture for radix-2 FFT    | 34 |

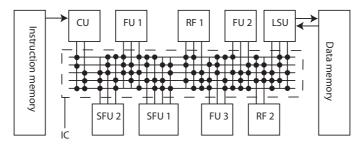

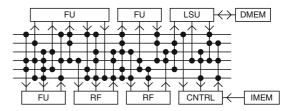

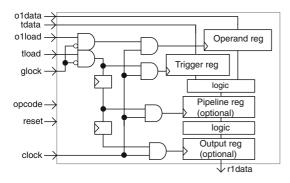

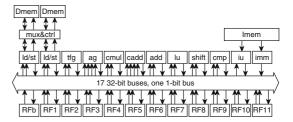

| 11 | Principal organisation of transport triggered architecture         | 39 |

### LIST OF TABLES

| 1 | Arithmetic cost and the number of butterfly stages in different FFT |    |  |

|---|---------------------------------------------------------------------|----|--|

|   | algorithms                                                          | 14 |  |

| 2 | Twiddle factors in 32-point radix-2 FFT                             | 26 |  |

| 3 | Energy-efficiency comparison of various FFT implementations         | 42 |  |

### LIST OF ABBREVIATIONS

AGU Address Generation Unit

ALU Arithmetic Logic Unit

ASIC Application-Specific Integrated Circuit

ASIP Application-Specific Instruction-set Processor

ASP Application-Specific Processor

CMP CoMPare machine instruction

CORDIC COordinate Rotation DIgital Computer

CU Control Unit

DFT Discrete Fourier Transform

DSP Digital Signal Processor

FFT Fast Fourier Transform

FPGA Field-Programmable Gate Array

FU Functional Unit

GE Gate Equivalent

IDFT Inverse Discrete Fourier Transform

IFFT Inverse FFT

IP Intellectual Property

IR Immediate Register, long

LD LoaD

LSU Load/Store Unit

LU Logic Unit

LUT Look-Up Table

OFDM Orthogonal Frequency Division Multiplexing

OPC OPeration Code

PC Program Counter

PE Processing Element

RAM Random Access Memory

RF Register File

RISC Reduced Instruction Set Computer

ROM Read Only Memory

SFU Special Functional Unit

SHU SHift Unit

ST STore

SUB SUBtract

TCE TTA-based Codesign Environment

TTA Transport Triggered Architecture

VLIW Very Long Instruction Word

WL Word Length

# LIST OF SYMBOLS

| $d_i$      | ith bit in a data sequence                           |

|------------|------------------------------------------------------|

| N          | size of FFT                                          |

| x(n)       | discrete time signal at time instant $n$             |

| X(r)       | frequency domain representation of $x(n)$            |

| $\omega_N$ | Nth principal root of unity                          |

| j          | imaginary unit                                       |

| e          | Napier's number                                      |

| F2         | radix-2 FFT butterfly                                |

| F4         | radix-4 FFT butterfly                                |

| S          | index of the processing column in FFT algorithm      |

| $a_i$      | representation of bit <i>i</i> in FFT memory address |

| $B_i$      | sector <i>i</i> in unit circle                       |

| M          | the number of memory accesses within single cycle    |

#### 1. INTRODUCTION

The recent advances in the semiconductor fabrication processes and technologies have allowed more complex integrated circuits to be developed. This has allowed more and more functionality to be integrated into a single chip. Nowadays even entire systems are integrated on a single chip, hence the name System-On-Chip (SoC). The high integration level has resulted in reduction of the size and the cost of digital systems. This has expanded the digital systems to whole new markets. The growth has been especially high in embedded systems where the system is designed for a single purpose, i.e., the system is not used for general-purpose computing. Nowadays the line between embedded and general-purpose systems is blurred and modern embedded devices have more computing power than personal computers of yesterday. As many embedded systems are handheld, or even integrated in clothing, the systems are often limited by constraints on size, weight, battery life, and cost. For such devices the area of the chip is an important cost factor but today even more important is the energy-efficiency. Many of the devices are battery powered and the battery life of the device is dependent on the energy drawn from the battery. Low power consumption is often used as a design criteria when designing energy-efficient systems but design for low-power does not necessary imply that the completed design is energy-efficient. A low-power system may have poor performance, thus the time to complete the task is long. A more efficient system may have higher power consumption but it completes the task faster, thus the energy for completing the task is lower implying better energy-efficiency. The design must also fulfil the criteria for performance, i.e., the task is required to be computed in the given time period. The energy-efficiency is defined as the energy consumed for performing the required task. Even the small mobile systems must be able to perform tasks which require high performance. Many design tradeoffs must be made to balance the often conflicting goals of energy-efficiency, low-power, high performance, and small area [6].

To address these design factors application-specific integrated circuits (ASIC) are of-

ten used as a part of the system to perform the critical tasks efficiently. As the capabilities of chip manufacturing as well as the the requirements of the applications have increased, the complexity of the designs has exploded, which increases the design time and the risks significantly. One solution for reducing the time to design an ASIC is to use modern design tools, which can be used to convert an algorithm described in a high-level language, e.g., C/C++, to a register-transfer logic (RTL) description, as presented in [9,83]. There are also modifications developed to the ASIC design flow. For example structured ASICs [93] have predetermined logic layers and the functionality is realised by a routing layer. Such an arrangement lowers the non-recurring engineering (NRE) costs. At the same time, the design time is shortened as there is no need to route all the transistor layers. Although the approach of developing a circuit for one purpose provides potentially the best performance as the design is tailored for the single application, it lacks the flexibility. E.g., if during the development an error is found or specifications change, an expensive and time consuming chip iteration is required.

To address these problems field programmable gate arrays (FPGA) have been developed where the system can be reconfigured if the design is required to be changed leading to lower NRE costs. The main drawback of the FPGA is decreased performance, increased power dissipation, and higher chip cost. Another solution is to use a programmable solution. General-purpose processors can be used but their performance may not be sufficient and, in particular, their energy-efficiency is poor. The best of both worlds can be obtained by combining the programmability with application-specific design, i.e., flexibility and efficiency are obtained by tailoring the processor according to the requirements of the application at hand. Such processors are called application-specific processors (ASP) or application-specific instruction set processors (ASIP). The motivation for the ASIP is to customise the instruction set according to the needs of the given application. In this Thesis, the name ASP is used to refer to processors with a customised instruction set. [12,25,63]

It is common that applications of wireless baseband signal processing, multimedia signal processing, on-line monitoring, or sensor signal processing exhibit very similar signal processing characteristics [55]. These application groups are called domains and when a system is designed for an application, it might be designed to support a wider range of applications in this domain. This is called domain-specific design. In a similar fashion, as fixed-function ASICs do not provide flexibility, designs custom-

ised for a single application may also show limited flexibility. When increasing the flexibility and supporting several applications from the same domain, i.e., domain-specific design, we obtain an application domain-specific processor (ADSP) [78,94]. In this Thesis, ADSPs are not considered and the thesis will concentrate on ASPs, although similar techniques are used to design ADSPs.

There are several design tools for developing ASPs, e.g., [33, 43, 77]. With the aid of modern ASP toolsets the design time can be significantly lowered and also the risks in the design are lowered, since the result is programmable and can be fixed, if needed, by modifications to the software. The main drawback of ASPs is lower energy-efficiency compared to ASICs. There are several processor architectures, which can be used as a template for customisation. E.g., very long instruction word (VLIW) machines have recently gained considerable popularity especially in digital signal processing (DSP) domain. VLIW has potential for higher performance as it may exploit instruction level parallelism (ILP) in the application by executing operations concurrently in multiple processing elements (PE).

Currently the application area where energy-efficiency and flexibility have great importance is wireless communications. In the future, cognitive radios will require functionality changed fairly often, thus programmable solutions will be preferred. In addition, in the future, almost all communications devices will be battery powered or they scavenge their energy from the environment, thus energy-efficiency is a vital property.

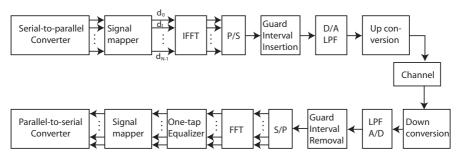

Many recent wireless communication systems are based on orthogonal frequency division multiplexing (OFDM), e.g., IEEE 802.11a/g (WiFi) [41], 802.16 (WiMAX) [42], 3GPP long term evolution (3G LTE) [1], digital video broadcasting (DVB) [61], digital audio broadcasting (DAB) [48], and ultra wideband (UWB) [67]. OFDM is also used in some wired systems, e.g., very-high-speed digital subscriber line (VDSL). The popular wired internet access asymmetric digital subscriber line (ADSL) [22,58] is based on VDSL. In OFDM systems [95], digital data is encoded on multiple carrier frequencies. The frequency modulation and demodulation are realised with the aid of one of the most popular tools in DSP, the Fast Fourier transform (FFT). In the transmitter, inverse FFT (IFFT) is used to spread the data over multiple carriers and, in receiver, FFT demodulates information from multiple carriers to time domain as illustrated in Figure 1.

**Fig. 1.** Principal block diagram of OFDM system.  $d_0...d_{N-1}$  data bits 0 to N-1; P/S: parallel-to-serial conversion; LPF: low pass filter; D/A: digital-to-analog conversion; A/D: analog-to-digital conversion; S/P: serial-to-parallel conversion.

The FFT is an efficient method for computing the Discete Fourier Transform (DFT). First, the DFT can be used to determine the frequency spectrum of a signal. This is a direct examination of information encoded in the frequency, phase, and amplitude of the component sinusoids. For example, human speech and hearing use signals with this type of encoding. Second, DFT can be used to determine the frequency response of a system based on the impulse response of the system and *vice versa*. This allows systems to be analysed in the frequency domain, just as convolution allows systems to be analysed in the time domain. Third, the DFT can be used as an intermediate step in more elaborate signal processing techniques. The classic example of this is FFT convolution, an algorithm for convolving signals that is hundreds of times faster than conventional methods [72]. The speedup in previous example is dependent of the convolution size and it will grow with the convolution.

The FFT can be used in various other applications such as sound analysis, magnetic resonance imaging (MRI) [64,71], compression methods, e.g., in Joint Photographic Experts Group (JPEG) [70,85] and Moving Picture Experts Group (MPEG) [52,90], encryption, e.g., in the public key Rivest, Shamir, and Adleman ciphering (RSA) [60, 62], and in Global Positioning System (GPS) [51,91] and Galileo [81,86] acquisition.

### 1.1 Scope and Objective of Research

The general research problem posed in this Thesis is "how to combine the flexibility and energy-efficiency in application implementation so that the design process is still general and can be supported by tools". Especially, the Thesis considers

energy-efficiency of programmable architectures in embedded systems where *a pri-ori* information about the applications is often available. The work considers also scalability, i.e., the resulting methodology must allow designer to trade-off performance against implementation cost. The resulting computing structures must exploit the inherent parallelism in the applications to support scalability. The work does not include reactive general-purpose computations and, therefore, e.g., support for interrupts is not considered.

The solutions proposed in this Thesis are based on the transport triggered architecture (TTA) template. Some earlier work has shown that TTA processors have potential for energy-efficient ASPs [10, 38, 66]. The main application area in the Thesis is computationally intensive tasks in digital signal processing and, in particular, Fast Fourier transform. The FFT uses complex-valued arithmetic, thus it represents well the current trend in DSP. The Thesis focuses primarily on mixed-radix in-place decimation-in-time (DIT) FFT algorithms and many of the novel contributions related to this algorithm can also be applied to other FFT algorithms.

The objective of the Thesis is to develop effective methods to increase the performance of an ASP in complex-valued DSP computing without major increase in power consumption and still maintaining the flexibility with the aid of programmability. The main claim in this thesis is that a programmable ASP can be designed so that it possesses energy-efficiency comparable to a fixed-function ASIC.

#### 1.2 Main Contributions

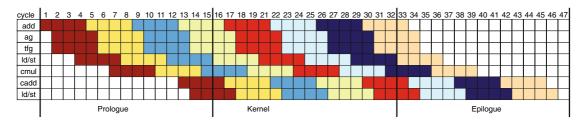

In this Thesis, mechanisms are proposed to design energy-efficient programmable solutions for embedded systems. The energy-efficiency is demonstrated with the aid of ASP based on transport triggering paradigm. The customisation is carried out for Fast Fourier transform. Several novel approaches are used for improving the performance for reducing the power consumption of the processor.

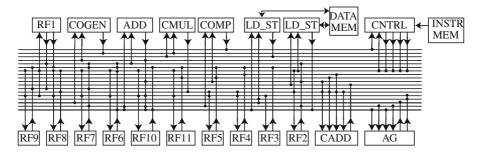

A novel energy-efficient coefficient generator is proposed in publication [P3]. Publication [P1] shows that the ASP can perform energy-efficient FFT computation with the aid of hardware supported memory address generation and the exposed data path in the used processor template. Publication [P2] introduces support for variable length FFT; the shown implementation supports all the power-of-two lengths

up to 16384. Publication [P4] shows improved energy-efficiency with conflict-free parallel memory scheme for FFT based on two– and four– ported parallel memories. The four–ported parallel memory doubles the throughput while maintaining the energy-efficiency. Publication [P5] presents how the performance can be increased by reducing the software overhead. This improves the energy-efficiency even further.

To summarise, the main contributions are the following:

- novel coefficient generation method for mixed-radix FFT, where the look-up table contains only  $\frac{N}{8} + 1$  complex-valued coefficients,

- energy-efficient memory organisation for FFT computations based on parallel memory concept,

- energy-efficient operand address generation for mixed-radix FFT, and

- novel processor structure for mixed-radix FFT computations exploiting the exposed data path of transport triggered architecture.

### 1.3 Author's Contribution

The work presented in this Thesis has been reported in publications [P1–P5]. None of the publications [P1–P5] have yet been used in another academic thesis. The author has been the first author on all of the publications [P1–P5].

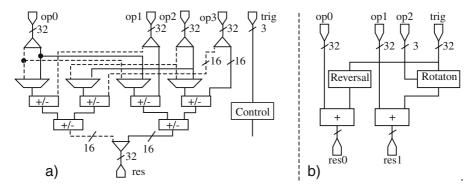

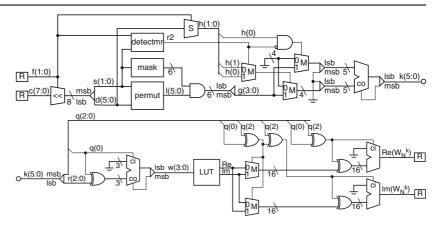

The publication [P3] describes the twiddle factor generator for mixed-radix FFT supporting radix-4 and radix-2 computations. The author proposed the principle of twiddle factor generation for radix-4 FFT and implemented the generator. M.Sc. Tero Partanen developed the initial program code for the algorithm. The author also developed and implemented twiddle factor generation for the mixed-radix FFT. This twiddle factor generation is used in publications [P1,P2,P4,P5].

An application-specific processor tailored for FFT supporting one fixed size N = 1024 is proposed in [P1]. M.Sc. Risto Mäkinen developed the initial program code for the FFT algorithm and created the first version of the corresponding assembly code. The author was responsible for developing the hardware implementation of the functional units in the processor and connectivity optimisation by programming the final version of the program with parallel assembly.

In [P2], an application-specific processor tailored for FFT supporting power-of-two lengths up to N=16384 is proposed. The author created the mechanisms to support the various transform lengths and implemented the software and hardware parts of the tailored processor.

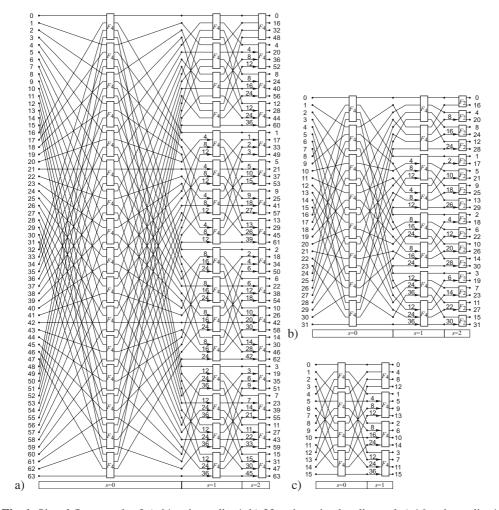

The author created the hardware implementation of the parallel memory scheme in [P4] where the access scheme for two ported access was developed by Dr. Jarno Tanskanen. The access scheme for the four ported parallel memory was created by the author and the author implemented the required hardware and software parts for the processor.

In [P5], the author developed mechanisms to reduce the software overhead and to speed up the computation. The author provided the required modifications to the hardware units. Finally, the author has carried out the verification and analysis of the developed structures described in [P1–P5].

#### 1.4 Thesis Outline

This Thesis consists of an introductory part where different FFT algorithms are described in Chapter 2. Chapter 3 describes the coefficient generation for the FFT where three different methods for coefficient generation are described. Chapter 4 describes fixed-function FFT processors, programmable FFT processors, and fundamentals of the ASP template used in this work, i.e., Transport Triggered Architecture (TTA). Finally, Chapter 5 concludes the introductory part of the Thesis. This is followed by the second part of the Thesis containing the five original publications.

#### 2. FAST FOURIER TRANSFORM

Discrete Fourier transform (DFT) is the main tool in the class of discrete trigonometric transforms. However, the definition of DFT contains redundancy and several methods have been proposed to avoid the redundant computations. Any method for computing DFT with lower arithmetic complexity than DFT is called Fast Fourier transform (FFT). In this chapter, the most popular FFT methods are discussed. Section 2.1 the describes Discrete Fourier transform and gives an introduction to Fast Fourier transform based on Cooley-Tukey decomposition. In sections 2.2, 2.3, and 2.4, different approaches for exploiting the Cooley-Tukey principle are discussed. Section 2.5 describes properties of FFT algorithms, e.g., in-place computations, which reduces the requirements for memory and, therefore, the energy consumption of the memory. Section 2.6 describes how the operand data can be fetched from the memory and how the storage is efficiently used, i.e., the possibility to use multiple single port memories.

## 2.1 Discrete Fourier Transform and its Fast Algorithms

Discrete Fourier transform is used to convert a finite sequence of equally-spaced samples to a sequence of coefficients of a finite combination of complex sinusoids. In other words, the time domain representation of an N-point discrete time signal x(n) is converted to frequency domain representation X(r) as follows [56]

$$X(r) = \sum_{n=0}^{N-1} x(n)W_N^{rn}, \ r = 0, 1, \dots, N-1$$

(1)

where the coefficients  $W_N$  are defined as

$$W_N = e^{-j2\pi/N} = \cos(2\pi/N) - j\sin(2\pi/N)$$

(2)

where j denotes the imaginary unit. As the coefficients  $W_N$  are composed of sine and cosine functions, the coefficients  $W_N^{rn}$  have symmetry and periodicity properties,

which imply that the DFT defined in (1) contains redundancy. By exploiting the underlying properties of the coefficients  $W_N^{rn}$  several fast algorithms for DFT have been developed over the years. In general, an algorithm, which has lower arithmetic complexity than DFT, is called a Fast Fourier transform (FFT). The most popular FFT is the Cooley-Tukey algorithm [23] where divide-and conquer paradigm [73] is used to decompose DFT into a set of smaller DFTs. In particular, the Cooley-Tukey principle states that a DFT of length N = PQ can be computed with the aid of P-point DFT and Q-point DFT.

### 2.2 Radix-p Algorithms

If a factor N, like P or Q above, is not a prime, the previous process can be recursively applied and the larger DFT will be computed with the aid of several smaller DFTs. Especially, when the DFT length is a power of a prime, i.e.,  $N = p^q$ , then the N-point DFT can be computed with the aid of p-point DFTs constructed in q computing stages. As the resulting fast algorithm contains only p-point DFTs, it's is called a radix-p FFT. The most popular approach is radix-p FFT algorithm where the DFT is decomposed recursively until the entire algorithm is computed with the aid of p-point DFTs as follows:

$$X(r) = \sum_{n=0}^{\frac{N}{2}-1} x(2n)W_N^{nr} + \sum_{n=0}^{\frac{N}{2}-1} x(2n+1)W_N^{nr+1}$$

$$= \sum_{n=0}^{\frac{N}{2}-1} x(2n)W_{\frac{N}{2}}^{nr} + W_N^r \sum_{n=0}^{\frac{N}{2}-1} x(2n+1)W_{\frac{N}{2}}^{nr}, r = 0, 1, \dots, N-1.$$

(3)

This equation shows that the coefficients  $W_N^{nr}$ , commonly called *twiddle factors*, serve as adjustments in the process of converting small radix DFTs into longer transforms [56].

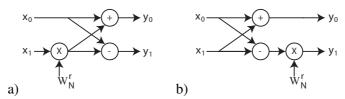

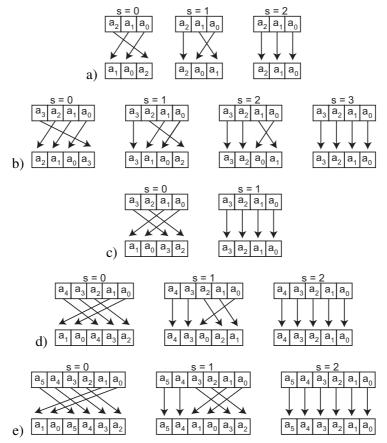

There are two principal approaches to decomposing the DFT: Decimation-In-Time (DIT) [65] and Decimation-In-Frequency (DIF) [15]. An example of both approaches is illustrated in Figure 2 where signal flow graphs of 8-point FFT derived with both approaches are shown. In the 8-point transform, the computations are carried out in three computing stages where each column contains four 2-point DFTs. The principal computation building block in the radix-2 FFT is 2-point DFT in (3), which is

Fig. 2. Signal flow graphs of 8-point radix-2 FFT: a) decimation-in-time and b) decimation-in-frequency algorithm.

also called a radix-2 butterfly. In the Figure 2, notation -1 is used to represent subtraction side of the radix-2 butterfly and notation  $W_N^r$  shows required coefficient. The Cooley-Tukey butterfly [23], shown in Figure 3(a) is used in DIT algorithms while the Gentleman-Sande butterfly [32] shown in Figure 3(b) is used in DIF algorithms.

This work concentrates on the DIT approach but both approaches result in the same arithmetic complexity and the main difference is the indexing in operand accesses for the FFT butterfly and the order of the computations inside the FFT butterfly. In fixed-point implementations, DIT and DIF approach may result in different quantisation noise performance. However, the differences seem to be small and, according to [13], DIT provides clearly better SNR in radix-2 algorithms.

In the Cooley-Tukey butterfly, one complex multiplication and two complex additions are needed, each stage contains N/2 butterflies, and the number of the stages is

Fig. 3. FFT butterflies according to a) radix-2 DIT algorithm in Figure 2(a) and b) radix-2 DIF algorithm in Figure 2(b).

$\log_2 N$ , which gives the total of  $\frac{N}{2}\log_2 N$  complex multiplications and  $N\log_2 N$  additions for an N-point transform. The complex multiplications use the complex-valued twiddle factors  $W_N^r$  as the second input.

### 2.3 Radix-2<sup>r</sup> Algorithms

Traditionally the most popular FFT have been the radix-2 FFTs where computations are based on 2-input, 2-output butterflies depicted in Figure 3. The arithmetic cost of an N-point radix-2 FFT is  $(\frac{N}{2}\log_2 N)$  complex multiplications and  $(N\log_2 N)$  complex additions. The complexity is often measured in terms of real-valued operations. The complex-valued addition requires two real-valued additions:

$$z_1 + z_2 = (a+jb) + (c+jd) = (a+b) + j(b+d).$$

The complex multiplication in turn requires more operations:

$$z_1z_2 = (a+jb)(c+jd) = (ac-bd) + j(ad+bc),$$

i.e., four real-valued multiplications and two real-valued additions.

The radix-2 FFT is a special case in the class of radix-2<sup>s</sup> FFTs [20]. The arithmetic complexity of FFT can be reduced by using greater than two radix if many of the complex coefficients turn out to be trivial that is  $(\pm 1 \text{ or } \pm j)$ . Let us consider the basic equation of the DFT in (1) and divide the original *N*-point problem to four partial sums by dividing the system to four sub problems where the length of problem

$$\begin{array}{c|c}

x_1 & & & & & & & & & & & & \\

\hline

x_1 & & & & & & & & & & & \\

x_2 & & & & & & & & & & \\

x_2 & & & & & & & & & & \\

x_3 & & & & & & & & & & \\

\end{array}$$

Fig. 4. Signal flow graph of radix-4 butterfly.

is N/4:

$$X(r) = \sum_{n=1}^{N-1} x(n)W_N^{rn}$$

$$= \sum_{n=0}^{N/4-1} x(4n)W_N^{r(4n)} + \sum_{n=0}^{N/4-1} x(4n+1)W_N^{r(4n+1)} + \sum_{n=0}^{N/4-1} x(4n+2)W_N^{r(4n+2)} + \sum_{n=0}^{N/4-1} x(4n+3)W_N^{r(4n+3)}, r = 0, 1, \dots, N-1.$$

(4)

This method results in a radix-4 algorithm where computations are based on 4-point DFT. This approach has benefits in terms of arithmetic complexity as 4-point DFT can be computed with trivial coefficients. By combining the twiddle factors, the radix-4 butterfly is defined as:

$$\begin{cases} y_0 = x_0 + W_1 x_1 + W_2 x_2 + W_3 x_3 \\ y_1 = x_0 - j W_1 x_1 - W_2 x_2 + j W_3 x_3 \\ y_2 = x_0 - W_1 x_1 + W_2 x_2 - W_3 x_3 \\ y_3 = x_0 + j W_1 x_1 - W_2 x_2 - j W_3 x_3 \end{cases}$$

(5)

This results in arithmetic cost of three complex multiplications and 12 complex additions. The radix-4 butterfly is presented in Figure 4. With the radix-4 algorithm, The computations are carried out in  $\log_4(N)$  butterfly stages; e.g., 64-point FFT is completed in three stages while the same transform requires six stages in the radix-2 algorithm. The arithmetic complexity for an *N*-point radix-4 FFT is  $\frac{3N}{4}\log_4 N$  complex multiplications and  $3N\log_4 N$  complex additions.

From the implementation point of view, the lower number of arithmetic operations provides potential for faster computation and energy savings. In addition, the latency of computations can be shorter. Besides lower arithmetic complexity, the radix-4 FFT provides also other advantages. The lower number of butterfly computation stages implies that, in memory based systems, less memory accesses are required. This

| Radix | # complex multiplications | # complex additions    | # stages            |

|-------|---------------------------|------------------------|---------------------|

| 2     | $\frac{N}{2}\log_2 N$     | $N \log_2 N$           | $\log_2 N$          |

| 4     | $\frac{3N}{8}\log_2 N$    | $\frac{3N}{2}\log_2 N$ | $\frac{1}{2}log_2N$ |

| 8     | $\frac{3N}{8}\log_2 N$    | $N \log_2 N$           | $\frac{1}{3}log_2N$ |

**Table 1.** Arithmetic cost and the number of butterfly stages in different FFT algorithms.

speeds up the computations, reduces energy consumption, and relaxes the memory bandwidth requirements.

The arithmetic complexity can further be reduced by selecting on even higher radix. However, in radix-8 and higher, the butterflies will contain non-trivial coefficients and, therefore, the relative arithmetic complexity is not decreasing as much. While radix-8 computations are applicable as they provide some advantages in specific implementation styles, higher radices are seldom used. The arithmetic cost and the number of stages of the different radix systems are presented in Table 1.

The main drawback of the higher radix p is the fact that the length of the transform has to be a power of  $2^p$ , i.e., radix-4 algorithms can only be applied when the transform length is a power of four. When the radix is higher, there are less sequence sizes where the algorithm can be applied. Due to this fact, radix-2 FFT has been popular. It also provides relatively good savings in arithmetic complexity and regularity, which eases the implementation.

#### 2.4 Mixed-Radix FFT

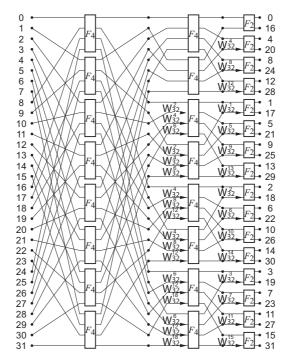

The limitation of radix-2<sup>s</sup> FFTs is the fact that it can be applied only to transform lengths that are a power of the radix. This can be overcome by using mixed-radix approach where the DFT decomposition contains several radices, e.g., 32-point FFT can be computed with two radix-4 stages and a single radix-4 stage. An example of mixed-radix FFT is shown in Figure 5 where signal flow graph of a 32-point in-place DIT FFT based on radix-4 and radix-2 is illustrated. The in-place computation saves memory, since each memory block is reused after the butterfly is computed. The memory requirements of the in-place computing is N memory locations. The operand access, i.e., the memory addressing, is discussed in more detail in Section 2.6.

The selection of the used radix is a compromise of the butterfly complexity, arithmetic cost, transform sizes to be supported, system requirements, and the design time of the

Fig. 5. Signal flow graph of 32-point mixed-radix DIT in-place FFT algorithm.

system. In this work, the mixed-radix is selected, which supports all the transform sizes of power of two. When size is not power of four the last stage of the transform is computed with radix-2 algorithm. In the developed system, one radix-4 or two radix-2 butterflies are computed simultaneously, to obtain four input and four output butterflies in either case. The mixed-radix approach is usually used when designed system should support multiple FFT sizes, since the required sizes are not usually all equal to the same power. E.g., if we need to support the IEEE 802.16.1 OFDMA PHY [42], the transform lengths 256 and 2048 need to be supported but radix-4 FFT cannot be used to compute a 2048-point FFT.

# 2.5 In-Place Computations

The mixed-radix algorithms, radix- $2^r$  FFT algorithms, and radix-p algorithms in general, are block processing algorithms where processing is carried out in processing stages consisting of butterfly computations. This can be seen from the signal flow graphs of the algorithms, e.g., Figure 2 and Figure 5: when input operands are avail-

Fig. 6. Signal flow graphs of in-place DIT FFTs: a) 8-point radix-2, b) 16-point radix-2, and c) 16-point radix-4.

able the butterfly operations in the first computing stage can be completed, results are stored, and then used as operands for the second butterfly stage. Often in software implementations, double buffering [34] is used, i.e., operands are stored in an array and results are stored to an another array and the role of buffers is exchanged for the next iteration. However, there is no need to reserve additional memory for the computation. Once the operands for a butterfly operations are read, the same memory locations can be used to store the results, i.e., computation can be performed in-place [46]. Exploitation of this property reduces the memory requirements of software implementations significantly.

Real-time FFT is often computed on consecutive blocks in the input data stream but FFT can be computed with overlapped blocks. In such a case, the computation is called sliding FFT (alternatively running FFT) [29]. There are special mechanisms for reducing complexity of sliding FFT computations but this type of computations are not considered in this thesis.

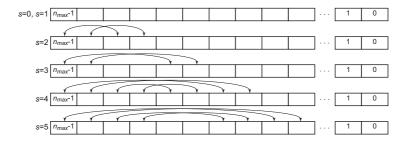

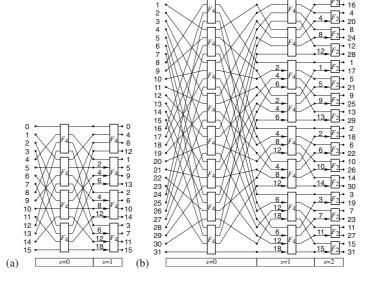

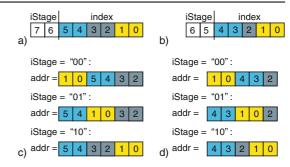

Fig. 7. Operand address generation for in-place FFT: a) 8-point radix-2 FFT at Figure 6a), b) 16-point radix-2 FTT at Figure 6b), c) 16-point radix-4 FFT in Figure 6c), d) 32-point mixed-radix FFT at Figure 5, and e) 64-point radix-4 FFT.

## 2.6 Permutations and Operand Access

Different FFT algorithms have different operand access patterns. E.g., in Figure 6a), the signal flow graph of an 8-point in-place DIT radix-2 FFT is shown where the access pattern of the operand data for butterfly computations depends on the butterfly column s of the FFT. This implies that results stored in an array from a butterfly stage need to be permuted before processing on the next stage. If the array is stored in memory and the length of array is a power of two, the permutation can be carried out with index manipulation. At bit-level, a linear address  $(a_{N-1}, a_{N-2}, \ldots, a_0)$  is rotated to the right but the bit field to be rotated depends on the stage s: the least significant bits  $(a_{\log_2 N-s-1}, \ldots, a_0)$  are rotated. The bit-level manipulation is illustrated in Figure

7. The address bit field to be rotated depends clearly on the processing stage *s*. Figure 7b) and c) show the difference between operand address generation in radix-2 and radix-4 algorithms. In radix-2, one bit rotation to the right is performed while in radix-4, two bits are rotated to the right. Mixed-radix approach is used when the number of bits in the array index is odd, as shown in Figure 7d) where two bit rotation is used for radix-4 butterflies and, in the last stage, no rotation is required for radix-2 butterflies as shown in Figure 5.

In Figure 5, the input is at natural order and the output of the FFT is at bit reversed order. In order to get the output frequencies of the FFT, the output sequences needs to be permuted according to bit reversal. The bit reversal of  $N = 2^n$  indexed data is an algorithm that reorders the data according to a reversing of the bits of the index [31]. E.g., representation of an array  $X = (x_0, x_1, ..., x_7)$  in bit reversed order is  $(x_0, x_4, x_2, ...)$  as follows

| $x_0 \to x_0 : 000 \to 000$                | $x_4 \to x_1 : 100 \to 001$                |

|--------------------------------------------|--------------------------------------------|

| $x_1 \to x_4 : 001 \to 100$                | $x_5 \rightarrow x_5: 101 \rightarrow 101$ |

| $x_2 \rightarrow x_2: 010 \rightarrow 010$ | $x_6 \rightarrow x_3: 110 \rightarrow 011$ |

| $x_3 \to x_6 : 011 \to 110$                | $x_7 \rightarrow x_7: 111 \rightarrow 111$ |

The reversal of bits of the index is clearly seen in the previous example. The previous permutation is related to radix-2 algorithms. In radix-4 algorithms, the same type of reversal in bit-level indices is visible but now the reversal is carried out in 2-bit fields as follows (array with 16 elements):

| $x_0 \to x_0 : 0000 \to 0000$    | $x_8 \to x_1 : 1000 \to 0010$                       |

|----------------------------------|-----------------------------------------------------|

| $x_1 \to x_8 : 0001 \to 0100$    | $x_9 \rightarrow x_9  : 1001 \rightarrow 0110$      |

| $x_2 \to x_4 : 0010 \to 1000$    | $x_{10} \rightarrow x_5 : 1010 \rightarrow 1010$    |

| $x_3 \to x_{12} : 0011 \to 1100$ | $x_{11} \rightarrow x_{13} : 1011 \rightarrow 1110$ |

| $x_4 \to x_2 : 0100 \to 0001$    | $x_{12} \rightarrow x_3 : 1100 \rightarrow 0011$    |

| $x_5 \to x_{10} : 0101 \to 0101$ | $x_{13} \rightarrow x_{11} : 1101 \rightarrow 0111$ |

| $x_6 \to x_6 : 0110 \to 1001$    | $x_{14} \rightarrow x_7 : 1110 \rightarrow 1011$    |

| $x_7 \to x_{14} : 0111 \to 1101$ | $x_{15} \rightarrow x_{15} : 1111 \rightarrow 1111$ |

Since bit reversal is invertible, the same permutation applies to sorting out a sequence in bit reversed order as desired for the output frequencies of the FFT.

#### 3. TWIDDLE FACTOR GENERATION FOR FFT

The twiddle factors are an integral part of FFT algorithms and often these coefficients are stored in a lookup table and fetched during computation of the algorithms. While this is a simple and quick method for short transforms, the table size increases superlinearly with the transform size. Therefore, with longer transforms it is more efficient to compute the coefficients at run-time.

In Section 3.1, we introduce the twiddle factors in FFT algorithms. Next we discuss two principal methods for computing the coefficients; polynomial and recursive methods are discussed in section 3.2, methods based on CORDIC algorithm are introduced in section 3.3, and methods exploiting lookup tables are reviewed in section 3.4. Finally in section 3.5, we discuss the proposed method to compute the coefficients based on a lookup table, which supports mixed-radix FFTs consisting of radix-4 and radix-2 computations.

#### 3.1 Twiddle Factors

The FFT algorithms contain complex-valued coefficients known as twiddle factors as shown in (3). They are defined as

$$W_N^k = e^{-j2\pi k/N} = \cos(2\pi k/N) - j\sin(2\pi k/N).$$

(6)

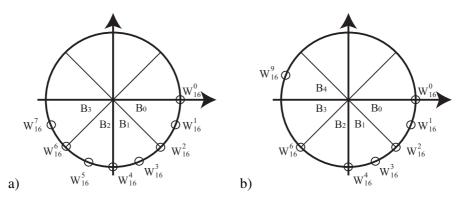

These coefficients are actually complex roots of unity evenly spaced in the unit circle on complex plane [20]. The number of different factors depends on the problem size N and the type of the fast algorithm. E.g., in radix-2 algorithms, each butterfly operation use one coefficient thus  $\frac{N}{2}\log_2 N$  factors are used in the algorithm. However, there are only  $\frac{N}{2}$  different factors in the algorithm as seen in the 16-point radix-2 Fourier transform illustrated in Figure 8 a). In the radix-4 algorithm, there are four

twiddle factors in each butterfly:

$$W_N^0, W_N^k, W_N^{2k}, W_N^{3k}, k = 0, \dots, \frac{N}{4} - 1.$$

As  $W_N^0 = 1$ , there is a total of  $\frac{3}{4}N\log_4 N$  non-trivial twiddle factors while only  $(\frac{N}{2} - 1)$  are unique, Figure 8 b) shows coefficients of 16-point radix-4 FFT.

When implementing an FFT algorithm, it is obvious that there is a large number of coefficients, which need to be used, especially when the transform size is large. The twiddle factors can be formed by using trigonometric functions, which are, however, expensive. The coefficients can be computed with fast algorithms, which exploit the trigonometric identities of twiddle factors, e.g., Singleton's method [69]. Then the coefficients can be computed on the fly, when they are needed. Another approach is to exploit lookup tables and read the coefficients from the tables. In many cases, the lookup tables are stored in ROM but, in software implementations, data memory can be used to store the coefficients. However, random access memory consumes more power than read-only memory. In addition, when coefficients are stored to data memory, additional memory accesses are required. In general, on-the-fly computation of twiddle factors requires less area, but consume more dynamic power compared to methods using lookup tables.

# 3.2 Polynomial and Recursive Twiddle Factor Generation

The twiddle factors can be generated as piecewise polynomial approximation of a function. Polynomial approximation requires multiplications and additions to compute the value of a function with given parameters. It should also be noted that the complexity of the polynomial based algorithm increases significantly with the required output precision. In [28], second order polynomial approximation is combined with Horner's rule to compute the sine and cosine values. The described computation unit contains four multipliers, four adders, and two lookup tables. The tables are used to partition the parameter ranges into regions. In order to increase precision, the number of regions have to be increased, which in turn increases the cost. Similar structure is proposed in [74].

The recursive twiddle factor generation is based on recursive feedback difference equations for sine and cosine functions. This approach is less complex compared

Fig. 8. Twiddle factors in 16-point FFT: a) radix-2 algorithm and b) radix-4 algorithm.  $B_k$  refers to sector number.

to the polynomial, one iteration uses two real-valued multiplications and two real-valued additions to produce a complex-valued result. The drawback of the algorithm is error propagation of the finite numbers due to the feedback structure of the algorithm. In [19], a method to reduce the complexity of error propagation circuit is proposed. The accuracy is improved with a LSB correction table containing  $\frac{N}{8}$  3-bit entries. The area cost is reduced by sharing the same multiplier and adder for both real and imaginary parts. This effectively doubles the latency of coefficient generation. The method uses two lookup tables for cosine and sine values and both tables require  $\log_2 N - 2$  entries. The drawback is that the method generates an ordered sequence of twiddle factors, thus it supports only a specific type of FFT algorithms and the reported unit supports only radix-2 DIF FFT.

In these algorithms, the large number of iterations will increase the length of computation kernel. This might increase the need for intermediate storage. i.e., registers. Also the large number of multiplications will increase the power consumption of twiddle factor generation [P3].

#### 3.3 Twiddle Factor Generation Based on CORDIC

The Coordinate Rotational Digital Computer (CORDIC) algorithm is a well known iterative algorithm for performing vector rotations [26, 45, 84]. All of the trigonometric functions can be evaluated by rotating an unit vector in complex plane. This operation is effectively performed iteratively with the CORDIC algorithm. The gen-

eral rotation transform at iteration t can be given as

$$\begin{cases} X_{t+1} = X_t \cos \phi - Y_t \sin \phi \\ Y_{t+1} = Y_t \cos \phi + X_t \sin \phi \end{cases}$$

(7)

where  $(X_{t+1}, Y_{t+1})$  is the resulting vector generated by rotation of an angle  $\phi$  from the original vector  $(X_t, Y_t)$ , i.e., the resulting vector rotates in the unit circle in similar fashion as the twiddle factors. Therefore, the CORDIC algorithm can be used to compute the twiddle factors, generating the sine and cosine values. In particular, CORDIC is used for replacing the twiddle factors with rotation information and, therefore, avoid multiplication with the twiddle factor by replacing it with rotation realised with additions. This operation mode is called rotation mode. The CORDIC can also operate in vectoring mode which returns the rotation angle and the scaled magnitude of the original vector.

The CORDIC multiplier consumes less power compared to a traditional multiplier. E.g., in [92], a pipelined CORDIC unit consumed roughly 20 % less power than the traditional complex-valued multiplier while the area cost was about the same. Recursive CORDIC iteration saves area compared to lookup based twiddle factors (discussed in the next section) but it introduces longer latency. In [92], the rotation angle constants for generating all the twiddle factors for an *N*-point FFT are stored in a lookup table with  $\log_2 N$  entries. In [30], the twiddle factors are generated without pre-calculated coefficients. The CORDIC algorithm is iterative, thus it can be pipelined easily and it lends itself to pipelined FFT architectures. However, the dynamic power consumption with a large number of iterations and/or long pipeline will be in higher than in a lookup table based approach. This will be the case, when longer word widths are used, i.e., increased accuracy calls for more iterations. This can be seen also with short transforms. E.g., in [7], it is shown that multiplier-based FFT consumes significantly less power compared to CORDIC FFT on FPGA. However, the clock frequency of CORDIC implementation can be much higher.

Traditionally the CORDIC has mainly beed used in fixed-function ASICs but it can be used to accelerate computations in a programmable processor as reported in [68]. The authors describe instruction extensions for CORDIC operations and there are separate instructions for vectoring and rotation mode. Four different instructions are needed for a 16-iteration CORDIC operation. The architecture supports SIMD operation and two CORDIC 16-bit operations with 16-bit operands are carried out

in parallel. Despite the overhead, the authors report 10x speedup in several matrix operations compared to a baseline architecture without the CORDIC extensions.

# 3.4 Methods Based on Lookup Tables

The twiddle factors can be stored in a lookup table, which is then indexed according to the selected algorithm. The simplest design, in radix-2, requires two coefficients in one butterfly, where the first twiddle factor is trivial +1 and the second is a nontrivial complex number. Now the memory contains all the twiddle factors in order in the memory thus the number of required coefficients in radix-2 is  $\frac{N}{2} \log_2 N$  where N is the transform size, e.g., lookup table has 448 entries when N=128 [11]. The memory can be now accessed with an index obtained from a simple counter. In this approach, the lookup table contains redundancy as many of the coefficients are the same. Such redundancy can be removed by adding an address generation logic before the lookup table. In [47,88], a method to reduce the number of coefficients in radix-2 algorithms to  $\frac{N}{2}$  is proposed. Each twiddle factor is stored only once in the table, i.e., the lookup table contains 64 entries when N=128. Such a table can be used only for a sequential implementation but, in [49], a method is proposed, which allows the N/2 entries to be distributed over  $2^P$ ,  $P=0,1,...,log_2\frac{N}{2}-1$  sub tables such that those can be accessed by  $2^P$  butterfly units simultaneously.

The previous twiddle factor table contains redundancy: as the twiddle factors are equally spaced in unit circle on the complex plane, there is symmetry as illustrated in Figure 8 a). We can note that the real and imaginary parts of the twiddle factors in the sector  $B_0$  and  $B_1$ , as seen in Figure 8 a), can be used to obtain the twiddle factors required in sectors  $B_2$  and  $B_3$ . The number of lookup table entries in the radix-2 case can be reduced down to  $\frac{N}{4} + 1$ . Such an approach has been presented in [14, 54, 80]. When N = 128 only 33 complex-valued entries are needed. In this method, the twiddle factors from sectors  $B_0$  and  $B_1$  in Figure 8 are stored to the lookup table and the rest of twiddle factors are generated simply by interchanging the real and imaginary parts of the coefficient and changing the sign of the real part of the coefficient before it is assigned to the imaginary part.

The previous representation still contains redundancy in lookup tables: the symmetry of twiddle factors between in different quadrants is exploited but the symmetry between real and imaginary parts of the twiddle factors is not used. This symmetry

allows all the twiddle factors to be generated from only one sector,  $B_0$  in Figure 8 a). In [36], this redundancy is avoided by generating twiddle factors for radix-2 FFTs with the aid of  $\frac{N}{8} + 1$  complex-valued twiddle factors stored in a lookup table, i.e., when N = 128, the lookup table contains 17 entries. A twiddle factor  $W_N^k$  is computed based on exponent k as follows

$$W_{N}^{k} = \begin{cases} R_{A} + jI_{A} & \text{, when } 0 \leq k \leq \frac{N}{8} \\ -R_{A} - jI_{A} & \text{, when } \frac{N}{8} < k < \frac{N}{4} \\ I_{A} - jR_{A} & \text{, when } \frac{N}{4} \leq k \leq \frac{3N}{8} \\ -R_{A} + jI_{A} & \text{, when } \frac{3N}{8} < k < \frac{N}{2} \end{cases}$$

(8)

where A is the index to the lookup table consisting the coefficients from the segment  $B_0$ :

$$A = \begin{cases} k[n-2:0] & \text{, when } 0 \leq k \leq \frac{N}{8} \\ \sim k[n-2:0] + 1 & \text{, when } \frac{N}{8} + 1 \leq k \leq \frac{N}{4} - 1 \\ k[n-2:0] & \text{, when } \frac{N}{4} \leq k \leq \frac{3N}{8} \\ \sim k[n-2:0] + 1 & \text{, when } \frac{3N}{8} + 1 \leq k \leq \frac{N}{2} - 1 \end{cases}$$

(9)

where k[a:b] denotes the bit field  $(k_a, k_{a-1}, k_{a-2}, \dots, k_{b+1}, k_b)$  of bit-level representation of integer k, and  $\sim$  denotes bit-wise complement operation.  $R_A$  and  $I_A$  are the real and imaginary part of the coefficient from the lookup table at the location A, respectively.

In Table 2, the twiddle factors for 32-point radix-2 FFT are listed in 2 decimals according to the sectors. The sine values, which are needed to create all the twiddle factors, are in the sector  $B_0$ . The actual twiddle factor requires only negation of sine and cosine values read from the lookup table as defined in (8). According to (9), the index to the lookup table is formed with simple operations: increment and complement. The index generation logic depends only on the length of FFT to be supported.

Table 2. Twiddle factors in 32-point radix-2 FFT.

| Table 2. I waate factors in 32 point radia 2111. |                         |                      |                       |  |  |  |  |

|--------------------------------------------------|-------------------------|----------------------|-----------------------|--|--|--|--|

| $B_0$                                            | $B_1$                   | $B_2$                | <i>B</i> <sub>3</sub> |  |  |  |  |

| $w_{32}^0(1.0,0.0)$                              | $W_{32}^{8}(0.0, -1.0)$ |                      |                       |  |  |  |  |

| $w_{32}^1(.98,20)$                               | $W_{32}^{7}(.20,98)$    | $W_{32}^9(20,98)$    | $W_{32}^{15}(98,20)$  |  |  |  |  |

| $w_{32}^2(.92,38)$                               | $W_{32}^6(.38,92)$      | $W_{32}^{10}(38,92)$ | $W_{32}^{14}(92,38)$  |  |  |  |  |

| $w_{32}^3(.83,56)$                               | $W_{32}^5(.56,83)$      | $W_{32}^{11}(56,83)$ | $W_{32}^{13}(83,56)$  |  |  |  |  |

| $w_{32}^4(.71,71)$                               |                         | $W_{32}^{12}(71,71)$ |                       |  |  |  |  |

# 3.5 Extension for Lookup Table Methods to Mixed-Radix FFT

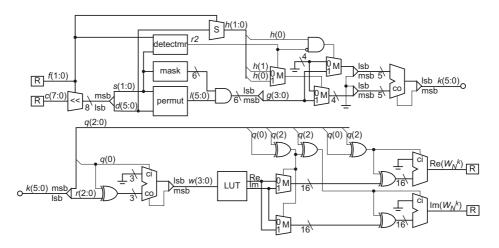

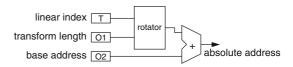

Many of the previously discussed methods are applicable only for a limited set of FFT algorithms, e.g., many methods support only radix-2 FFT. If more efficient mixedradix computations are to be used, more flexible twiddle factor generation methods need to be found. In [P3], a twiddle factor computation method is proposed, which supports radix-4 FFT and mixed-radix FFT. The method exploits lookup tables and  $\frac{N}{8}+1$  complex-valued twiddle factors need to be stored for an N-point FFT. When the lookup table has been created for an N-point FFT, the proposed method supports all the the power-of-two transform sizes up to N when computed with mixed-radix algorithms containing radix-4 and radix-2 computations. The Figure 8 b) shows that the method presented in (8) could not be used, the usage of sectors from  $b_0$  to  $B_3$  is not sufficient to generate all coefficients in radix-4 FFT. The main drawback of the lookup approach compared to polynomial methods is the fact that the size of table increases as the transform size increases. However, we target embedded systems where the FFT sizes are not huge. Therefore, the size and power consumption of the lookup tables are reasonable compared to multipliers required in polynomial methods. If huge transforms are computed, the polynomial methods will be more effective.

Apart from the lookup tables, the proposed twiddle factor unit requires only few additional components, mainly two real-valued negation units for changing the sign of sine and cosine values obtained from the lookup table. In addition, the method allows completely pipelined implementation, thus it can generate twiddle factors at each clock cycle unlike some of the other methods discussed earlier.

In the proposed method, the factor  $W_N^k$  is computed based on the given power of the principal root of unity, k. Such an approach is flexible as it allows the method to be used with several types of FFT algorithms as there is no need to compute the twiddle factors in a certain fixed order. The different ordering of twiddle factors can be organised simply by providing the powers, k, to the unit. This is also illustrated in [P3] as there is a permutation unit, in which the power parameter k is generated from a linear counter to be used as a operand for the proposed twiddle factor unit. Such permutations are performed at bit-level, thus no arithmetic units are needed and the solution requires a rather small area. Such an additional unit is not needed if radix-4 DIF algorithm is used. This is the same case as used in some polynomial methods, where the twiddle factors are generated in increasing order of powers, k.

#### 4. ARCHITECTURES FOR FFT COMPUTATION

In general, the FFT implementations can be divided to two main classes: fixed-function processors and programmable processors. The fixed-function processors are tailored for a specific application and the functionality cannot be changed at runtime. However, fixed-function FFT processors may allow parameters to be changed, e.g., the size of he the Fourier transform to be computed can be changed at run-time. Fixed-function processors can be implemented either on an FPGA or as an ASIC.

The implementation style depends on the application at hand and the design goals. Traditionally fixed-function circuit is selected when application is known, i.e., there are no changes expected to the application, and in particular, low energy and/or high performance is desired. On the other hand, software implementation is flexible as the functionality can be changed easily. This style is selected when the application is not mature and there is a high probability to change the functionality. The application-specific processor tries to collect the best features of both styles; some of the resources are tailored for the specific application, thus lower power consumption can be expected. With adequate parallelism also higher performance can be assumed. Software implementation allows the functionality to be changed by changing the program.

In this chapter, architectures for computing fast Fourier transform are reviewed. First, fixed-function FFT processors are discussed in Section 4.1. In Section 4.2, more flexible solutions, i.e., FFT on programmable processors, are discussed. The proposed energy-efficient programmable processor for FFT is discussed in Section 4.3. First, the TTA template and the design framework related to TTA are discussed. Finally in Section 4.4, the energy-efficiency of the proposed customised processor is compared to other FFT processors including both fixed-function and programmable solutions.

#### 4.1 Fixed-Function Architectures for FFT

In fixed-function FFT processors, the underlying hardware is either an FPGA or an ASIC tailored specifically for FFT computations. The circuit can be used as an accelerator for a host processor where the main goal of the circuit is to be faster and/or more energy-efficient than the host. One of the advantages of such a configuration is that while the accelerator is carrying out computations, the host is free to execute other tasks. Another possibility is to use the circuit as an individual block of a larger system or in the system-on-chip (SoC), e.g., in an OFDM transceiver.

The signal flow graphs of FFTs derived with Cooley-Tukey decomposition consist of smaller DFTs and multiplications with twiddle factors as seen in Figure 2. It can be seen that the basic building blocks of these algorithms are 2-point DFT and complex-valued multiplication, i.e., FFT butterflies. The butterfly related to radix-2 DIT algorithm in Figure 2(a) is shown in Figure 3(a). The FFT butterfly is related to the radix; radix-2 butterfly is based on 2-point DFT while radix-4 butterfly is based on 4-point DFT.

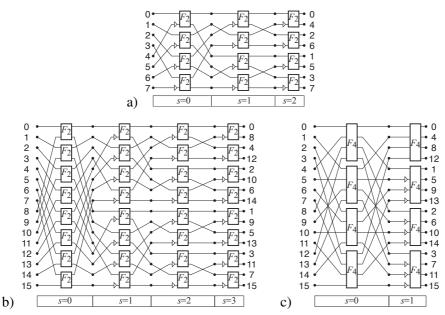

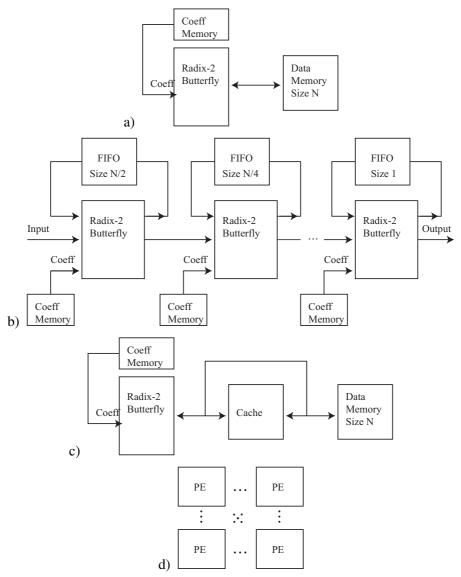

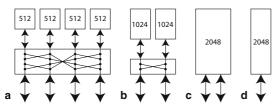

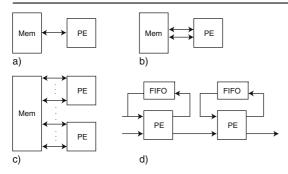

According to [3] FFT computing architectures are classified into five categories: single memory, dual-memory, pipelined, cache-memory, and array architectures. Here, single memory and dual-memory architectures are combined to memory architecture as illustrated in Figure 9(a). An example of pipeline architecture is shown in Figure 9(b), principal cache-memory architecture is shown in Figure 9(c), and array architecture depicted in Figure 9(d).

Memory architectures consist one or more processing elements within the FFT column connected to main memory. In pipeline architecture there is a processing element, or elements, dedicated for one butterfly stage in the FFT algorithm. A memory architecture where local cache is connected between main memory and processing elements is called cache-memory architecture.

The array architecture consist of several independent processing elements with local buffers connected together by an interconnection network, many implemented as Network-on-Chip (NoC) [57]. Array systems may use multiple chips [17, 76] or a single chip [50]. Throughput of the array systems can be high as several butterflies in a FFT column are computed in parallel and the data for the next column is fed from local buffers via interconnection to processing elements. However, the cost of having

Fig. 9. Principal architectures for fixed-function FFT processors: (a) memory, (b) pipelined, (c) cache-memory, and (d) array.

such amount of parallelism and parallel data transports is high.

An architecture is developed by selecting an FFT algorithm with specific features, which then can be exploited for optimising the architecture. The simplest implementation is achieved when using memory architecture with a single processing element; other implementation methods are used when the simplest implementation style can-

not satisfy the performance requirements. In the memory architecture, the computation speed of the system is restricted by the memory bandwidth since operands to butterfly computations and results use the same memory. The memory architecture with a single processing element is naturally the cheapest solution.

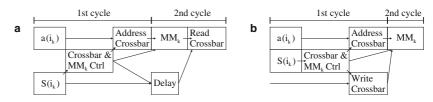

## 4.1.1 Memory Architecture

In memory architectures, one or more FFT butterflies from the same column, i.e., data processing for input set defined by FFT radix, is performed in parallel [53]. computing multiple butterflies from the same column in parallel increases the throughput of the system [89]. This increases parallelism and therefore the area cost, i.e., when using radix-2 FFT the maximum number of butterflies in one column is  $\frac{N}{2}$ . Higher radix can be used to increase parallelism, e.g., in radix-4 FFT, two radix-2 columns are combined. It should also be noted that the complexity of data flow control increases with the parallelism.

Input data for the butterfly is fetched from the data memory and the output data is stored back to it. The pressure for memory accesses increase with the parallelism. The coefficients used in the butterfly computations can be fetched from the data memory, from a separate coefficient memory, or generated on the fly. This topic was described in more details in Section 3.

Usually memory based systems are used when large Fourier transform sizes are needed but high throughput is not needed [89]. The performance is limited by the memory bandwidth, i.e., the number of available memory ports. Multi-ported memories can be used to increase the memory bandwidth but unfortunately such a solution is expensive both in area and power consumption. A cheaper solution is to use multiple single-port memories but in such parallel memory systems the bandwidth is reduced by memory conflicts. In case of conflicts, the memory accesses need to be serialised. In addition, conflict detection and management increases the area and power dissipation of the system. There are also conflict-free parallel access schemes tailored for FFT, e.g., the method reported in [35].

## 4.1.2 Pipelined Architectures

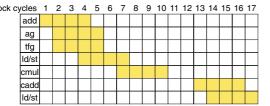

In the previous approach, parallelism was increased by computing several butterflies in parallel. However, throughput can also be increased by computing butterflies from multiple columns at the same time and this is the basis for the pipeline architecture [8, 79]. Such an architecture can achieve high throughput. At minimum, one butterfly unit is required for each column in the algorithm. This implies that the number of butterflies is dependent on the Fourier transform size unlike in the previous approach.

Another issue to note is the fact that in pipeline architecture all the twiddle factors in a butterfly column are mapped on to a single multiplier unit. This is very effective if the selected algorithm is such that many columns have constant twiddle factors and in such a case the constant multiplier can be used instead of a general complex-valued multiplier or complex rotator [59]. Different pipeline approaches are presented in [37] and the results indicate that the delay-feedback approach provides the best utilisation and minimises the memory cost. In radix-2 single delay-feedback approach, each butterfly unit requires a memory, i.e., a FIFO type structure, with size of  $\frac{N}{radix \times s_i}$ . The total size of these memories is N-1, which is the same as the memory based systems using in-place computation although the individual memories in pipeline architecture are smaller, however several different address generation schemes are required. Pipeline based systems consume more area due to the parallel resources and are used normally in FFT systems where high throughput is required.

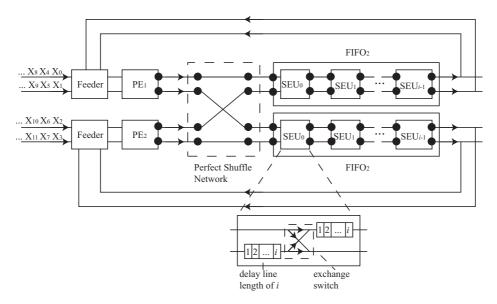

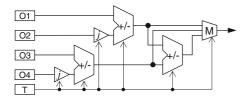

The throughput of the system can be increased by computing multiple butterflies from the same column in parallel as shown for the pipelined systems in [44] or increasing the FFT radix. This requires more memory ports and the area cost is higher due to the increased number of processing elements (PE). In [75], a scalable FFT architecture is proposed, which combines principles from the memory-based and pipelined designs. As illustrated in Figure 10, the architecture carries out iterative computations with the aid of butterfly PEs. The input multiplexer selects either the input or data from the previous iteration. The architecture is based on a constant geometry algorithm where the interconnections between the butterfly columns are perfect shuffle permutations. Such permutations are realised in the architecture with the aid of hardwired perfect shuffle network followed by temporal permutation based on cascaded switch-exchange units. Each unit contains two delay lines and multiplexers for exchanging the signals. The architecture is scalable in the sense that for *N*-point FFT

Fig. 10. Principle organisation of scalable architecture for radix-2 FFT.

the number of processing elements can be scaled from one to N/2. However, the number of processing elements must be a power-of-two. The twiddle factors for the butterfly processing elements are obtained from internal lookup tables.

In [45], an FFT architecture using a CORDIC multiplier is proposed. This pipeline architecture contains four radix-8 butterfly units and one radix-2 unit, thus it supports FFT sizes of 8192, 4096, 1024, 512, 128, and 64. The radix-8 units exploit distributed arithmetic. Each result of the radix-8 butterflies is fed to a CORDIC-multiplier and then stored to temporal memory. Due to the pipeline schedule, the memory usage is not optimal;  $\frac{3N}{2} + \frac{9N}{128}$  memory elements are required for *N*-point Fourier transform. The system has throughput of one sample per cycle and the latency depends on the Fourier transform size. The area of the system is 55k gates without memories. The small area is achieved by using 16-bit internal data representation with 8-bit input data.

An 8-parallel pipelined architecture is proposed in [79] supporting Fourier transform sizes from 64 to 1024. Different transform sizes are based on different algorithms and  $\operatorname{radix-2/2^5 radix-2/2^4/2^5}$ ,  $\operatorname{radix-2^2/2^5}$ ,  $\operatorname{radix-2^3/2^5}$ , and  $\operatorname{radix-2^4/2^5}$  FFT algorithms are used. The locality of the algorithm is exploited when mapping the computations on 8-path or 4-path modules. The first module contains four radix-2 operation sets and the second consists five radix-2 operation sets. An 1024-point Fourier transform

uses four data paths and an additional radix-2 stage in the first module. A CORDIC unit with nine pipeline stages is used in twiddle factor generation and complex multiplication. The accuracy of a 9-stage CORDIC unit is sufficient for input with 10 bits of precision. The actual input data format is block floating-point: 10-bit mantissa with shared 4-bit exponent in blocks of eight samples. The proposed scheme processes 512-point FFT in 64 cycles and 1024-point FFT in 256 cycles. The maximum clock frequency is 300MHz, which provides throughput of 2,4 Gb/s for 512-point Fourier transform. The 1024-point Fourier transforms are executed at 5 MHz speed. The processor takes 3.2 mm<sup>2</sup> of area.

# 4.1.3 Cache-Memory Architecture

In order to reduce the power consumption of a large centralised memory, a smaller memory, i.e., cache, could be used. Cache-memory architecture is based on this idea. The FFT algorithm must be such that it contains a high degree of locality [2] and the algorithm can be divided into independent groups, called epochs, of smaller FFTs [3]. The FFT size is defined by the epoch sizes,  $N = N_{eo}N_{e1}\cdots N_{en}$  and each epoch contains  $\frac{N}{N_e}$  independent  $N_e$ -point FFTs, i.e., this follows the Cooley-Tukey decomposition. For example, 1024-point FFT can be divided to two epochs, which each contain 32 FFTs of size 32. In this case, A memory with 32 entries could be used in inter-epoch computations and memory with 1024 entries is used in intra-epoch computations. The cache is usually so small that it can be implemented as a local register bank [3,4].

An energy-efficient FFT based on cache-memory architecture is proposed in [16]. The unit uses a memory model where the cache is located between main memory and the FFT butterfly. FFT sizes from 128 to 1024 are supported and the FFT scheme is radix-2 and radix-2<sup>2</sup> using pipelined dual-delay-feedback architecture. This is an example how pipelined architecture model could be combined with a memory-based model, i.e., the butterfly uses pipeline based architecture and rest of the system is memory based. The authors present a 3-epoch system. Four memory accesses are required in each cycle, which would lead to an expensive four-ported implementation. To avoid this, the cache is divided to two banks containing even and odd addresses with data exchange logic if data is required to or from different cache. The FFT scheme is manipulated in order to have only one read and write from the even cache

and the second one from the odd cache in a cycle. The main memory is divided in similar fashion to two single port memories. Two twiddle factors are required in each cycle, and those are provided from ROM memories where power consumption savings can be achieved by applying the twiddle factor generation model to the system. The system is optimised based on symbol-error-rate analysis and the word length is set to 13 bits. The multiplier is set to have two modes: full 13x13 bit multiplication and smaller, 13x(9-5) bit multiplication depending on the modulation scheme and the size of the Fourier transform.

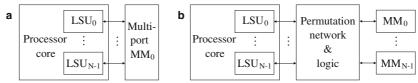

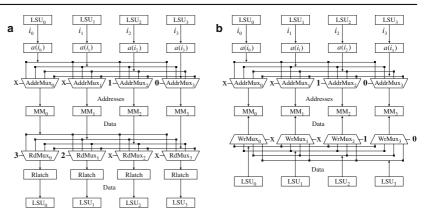

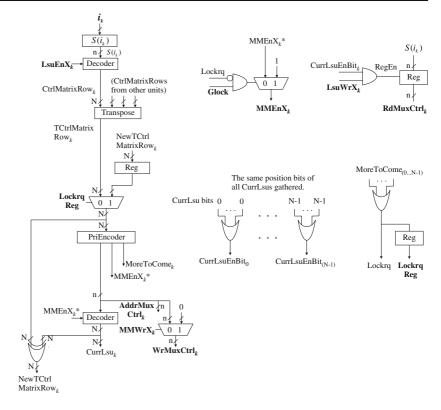

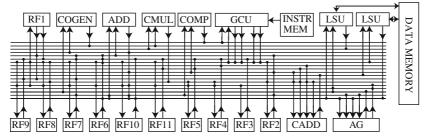

# 4.2 FFT on Programmable Processors