## TAMPERE UNIVERSITY OF TECHNOLOGY

Pekka Jääskeläinen From Parallel Programs to Customized Parallel Processors

Julkaisu 1086 • Publication 1086

Tampere 2012

Tampereen teknillinen yliopisto. Julkaisu 1086 Tampere University of Technology. Publication 1086

Pekka Jääskeläinen

# From Parallel Programs to Customized Parallel Processors

Thesis for the degree of Doctor of Science in Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB224, at Tampere University of Technology, on the 8<sup>th</sup> of November 2012, at 12 noon.

Tampereen teknillinen yliopisto - Tampere University of Technology Tampere 2012

ISBN 978-952-15-2932-0 (printed) ISBN 978-952-15-2966-5 (PDF) ISSN 1459-2045

#### ABSTRACT

The need for fast time to market of new embedded processor-based designs calls for a rapid design methodology of the included processors. The call for such a methodology is even more emphasized in the context of so called *soft cores* targeted to reconfigurable fabrics where per-design processor customization is commonplace.

The C language has been commonly used as an input to hardware/software co-design flows. However, as C is a sequential language, its potential to generate parallel operations to utilize naturally parallel hardware constructs is far from optimal, leading to a customized processor design space with limited parallel resource scalability. In contrast, when utilizing a parallel programming language as an input, a wider processor design space can be explored to produce customized processors with varying degrees of utilized parallelism.

This Thesis proposes a novel *Multicore Application-Specific Instruction Set Processor (MCASIP)* co-design methodology that exploits parallel programming languages as the application input format. In the methodology, the designer can explicitly capture the parallelism of the algorithm and exploit specialized instructions using a parallel programming language in contrast to being on the mercy of the compiler or the hardware to extract the parallelism from a sequential input. The Thesis proposes a multicore processor template based on the Transport Triggered Architecture, compiler techniques involved in static parallelization of computation kernels with barriers and a datapath integrated hardware accelerator for low overhead software synchronization implementation. These contributions enable scaling the customized processors both at the instruction and task levels to efficiently exploit the parallelism in the input program up to the implementation constraints such as the memory bandwidth or the chip area. The different contributions are validated with case studies, comparisons and design examples.

#### PREFACE

When I started to work on the *TTA-based Co-design Environment (TCE)* project about ten years ago as a research assistant, I could not have imagined what an interesting journey of learning the then part-time job would start.

I would like to thank my supervisor Professor *Jarmo Takala* for this challenging work opportunity, his guidance, and trusting me on my research ideas. Furthermore, I want to thank him and the two reviewers, Professor *Georgi Gaydadjiev* and Professor *Johan Lilius* for their invaluable comments that helped me to improve this Thesis.

The results presented in this Thesis would not have been possible without the many hard-working smart colleagues that have contributed code and ideas for TCE since the beginning of the project. I have a great deal of gratitude for all of you, but I am afraid there are too many to mention separately without still forgetting someone important.

However, I want to specifically thank the main collaborators in the work for this Thesis, which was conducted mostly in the past four years. I am grateful for the opportunity I had to work with *Carlos Sánchez de La Lama*, M.Sc., who brought a "fresh energy boost" and new ideas to TTA research after his first post to our mailing lists about four years ago. I appreciate the work on the compiler backend of *Heikki Kultala*, M.Sc., and *Vladimír Guzma*, M.Sc. Heikki's remarkable ability to remember many details of commercial off-the-self processor architectures has been a useful source of information for me numerous times. I thank *Otto Esko*, M.Sc., Dr. *Pablo Huerta*, and Dr. *Erno Salminen* for providing their FPGA and hardware expertise without which the experiments presented in this thesis would have been much less concrete.

Now that the toolset we have developed all these years is known to have been used to design processors for silicon implementation, I must thank the numerous people who have helped to stabilize TCE by using it for various ASIP design cases and reporting bugs and inefficiencies. Again, there are too many to mention, but from the "pioneers" I must bring up Prof. *Olli Silvén* and his research group in University of Oulu, especially researcher Dr. *Jani Boutellier*. I thank you for extensive testing and validating the work in various design cases and for spreading the TTA/ASIP awareness especially in the Oulu area. In this context I must also thank *Heikki Berg*, M.Sc and his research group for the chance to evaluate and test the techniques presented in this Thesis in our collaboration projects of past couple of years, and for bringing an "industrial point of view" to the research.

I am most grateful for the funding sources that enabled me to focus on the interesting research topic. In the past four years, I have received financial support from the *Academy of Finland*, *Ulla Tuominen Foundation*, *Tuula and Yrjö Neuvo fund* and *Nokia Foundation*.

I am thankful for the solid foundations provided by my siblings and parents, especially my mother who has constantly encouraged me to finish this Thesis project sooner than later. Finally, I thank my dear wife *Terhi* who has provided me a steady source of warmth and happiness during these years. Thank you for tolerating my sometimes too long work days that in part made finishing this Thesis possible.

> Tampere, September, 2012 Pekka Jääskeläinen

## **TABLE OF CONTENTS**

| Abstract |         |          |                                    |      |  |  |

|----------|---------|----------|------------------------------------|------|--|--|

| Pre      | Preface |          |                                    |      |  |  |

| Та       | ble of  | Conten   | ts                                 | v    |  |  |

| Lis      | st of F | Figures  |                                    | ix   |  |  |

| Lis      | st of T | Tables   |                                    | xi   |  |  |

| Lis      | st of A | Abbrevia | tions                              | xiii |  |  |

| 1.       | Intro   | duction  |                                    | 1    |  |  |

|          | 1.1     | Resear   | ch Objectives                      | 3    |  |  |

|          | 1.2     | Main C   | Contributions                      | 4    |  |  |

|          | 1.3     | Author   | r's Contribution and Collaboration | 4    |  |  |

|          | 1.4     | Thesis   | Outline                            | 5    |  |  |

| 2.       | Para    | llel Con | nputing                            | 7    |  |  |

|          | 2.1     | Expres   | ssing Parallelism in Software      | 7    |  |  |

|          |         | 2.1.1    | Synchronization Primitives         | 11   |  |  |

|          |         | 2.1.2    | Open Computing Language            | 12   |  |  |

|          | 2.2     | Paralle  | lism in Processor Architectures    | 14   |  |  |

|          |         | 2.2.1    | Instruction Level Parallelism      | 14   |  |  |

|          |         | 2.2.2    | Data Level Parallelism             | 16   |  |  |

|          |         | 2.2.3    | Task Level Parallelism             | 18   |  |  |

|          | 2.3     | Custon   | nized Parallel Processors          | 20   |  |  |

| 3. | Exp  | osed Da  | tapath Static Multi-Issue Architectures               | 23 |

|----|------|----------|-------------------------------------------------------|----|

|    | 3.1  | Transp   | ort Triggered Architectures                           | 23 |

|    | 3.2  | Benefi   | ts of TTA in Single Program Multiple Data Computation | 25 |

|    | 3.3  | Review   | v of Work in Exposed Datapath Architectures           | 28 |

| 4. | Cust | tomizabl | le Processor Design Methodology for Parallel Programs | 33 |

|    | 4.1  | Related  | d Work                                                | 35 |

|    | 4.2  | Paralle  | Processor Design Flow                                 | 36 |

|    |      | 4.2.1    | Software Development                                  | 36 |

|    |      | 4.2.2    | Single Core Customization                             | 38 |

|    |      | 4.2.3    | Multicore Exploration                                 | 41 |

| 5. | Cust | tomizabl | le Parallel Processor Template                        | 43 |

|    | 5.1  | Related  | d Work                                                | 43 |

|    | 5.2  | Custor   | nizable Multicore Processor Template                  | 45 |

|    | 5.3  | Memo     | ry Model                                              | 46 |

|    |      | 5.3.1    | Shared Default Data Memory configuration              | 48 |

|    |      | 5.3.2    | Local Default Data Memory configuration               | 49 |

|    | 5.4  | Softwa   | re Stack                                              | 49 |

|    | 5.5  | Thread   | l Scheduling                                          | 51 |

|    |      | 5.5.1    | Dthreads: a Distributed Threading Library             | 51 |

|    |      | 5.5.2    | Requirement: Low Instruction Memory Footprint         | 53 |

|    |      | 5.5.3    | Requirement: Autonomous Execution                     | 53 |

|    |      | 5.5.4    | Requirement: Minimal Number of Shared Memory Accesses | 54 |

|    |      | 5.5.5    | Requirement: Scalability                              | 54 |

| 6. | Ope  | n Comp   | uting Language Support                                | 57 |

|    | 6.1  | Related  | d Work                                                | 57 |

|    | 6.2  | Open O   | Computing Language in Hardware/Software Co-Design   | 59 |

|----|------|----------|-----------------------------------------------------|----|

|    | 6.3  | Compi    | ling OpenCL for Static Customized Processors        | 59 |

|    |      | 6.3.1    | Standalone and Hosted Setups                        | 60 |

|    |      | 6.3.2    | Parallelizing Work-Items                            | 60 |

|    |      | 6.3.3    | Work-item Chaining Algorithm                        | 63 |

|    |      | 6.3.4    | Instruction Level Parallelization of Work-Groups    | 65 |

|    |      | 6.3.5    | Custom Operation Support                            | 67 |

| 7. | Harc | lware A  | ccelerated Synchronization                          | 69 |

|    | 7.1  | Related  | d Work                                              | 69 |

|    | 7.2  | Datapa   | th Integrated Lock Unit                             | 71 |

| 8. | Expe | eriments |                                                     | 77 |

|    | 8.1  | Experi   | ment Environment                                    | 77 |

|    | 8.2  | TTA v    | s. SIMT in OpenGL Shader Execution                  | 79 |

|    |      | 8.2.1    | The Shader Example                                  | 79 |

|    |      | 8.2.2    | Benchmarking TTAs against a SIMT GPU                | 81 |

|    | 8.3  | Single   | Core Customization for OpenCL Kernels               | 84 |

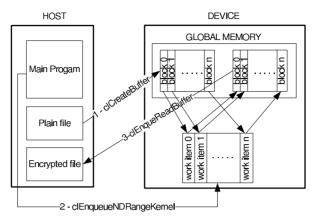

|    |      | 8.3.1    | AES OpenCL Implementation                           | 85 |

|    |      | 8.3.2    | Instruction-level Parallelism                       | 86 |

|    |      | 8.3.3    | Custom Operations                                   | 87 |

|    |      | 8.3.4    | Single Core Customization Using Standard Components | 88 |

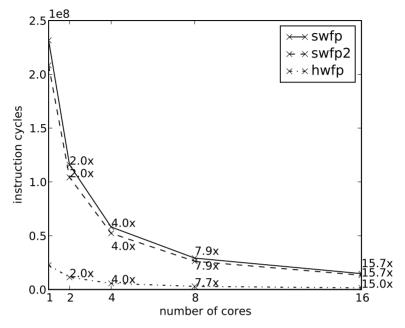

|    | 8.4  | Task L   | evel Scalability                                    | 90 |

|    | 8.5  | Barrier  | Synchronization Overheads                           | 92 |

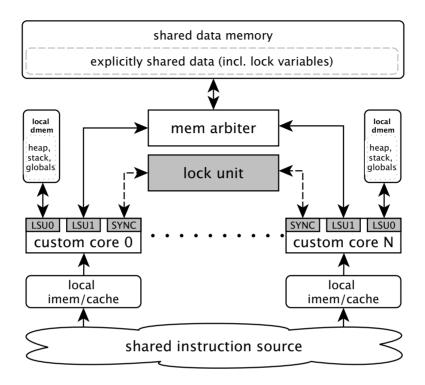

|    |      | 8.5.1    | The Benchmark Processor                             | 93 |

|    |      | 8.5.2    | Benchmark Program                                   | 94 |

| 9. | Conclusions |              |     |  |  |

|----|-------------|--------------|-----|--|--|

|    | 9.1         | Main Results | 97  |  |  |

|    | 9.2         | Future Work  | 99  |  |  |

| Bi | bliogr      | <i>aphy</i>  | 101 |  |  |

## LIST OF FIGURES

| 1  | A parallel for-loop computing a vector addition using the OpenMP                                               |    |

|----|----------------------------------------------------------------------------------------------------------------|----|

|    | pragmas in a C program.                                                                                        | 8  |

| 2  | A snippet of a program with instruction-level parallelism                                                      | 9  |

| 3  | Vector addition in ANSI C                                                                                      | 9  |

| 4  | Spin lock and unlock implementations using the atomic Compare-<br>And-Swap instruction.                        | 11 |

| 5  | Vector dot product in OpenCL C                                                                                 | 13 |

| 6  | Illustration of how the instruction bit fields control a SIMD datapath.                                        | 16 |

| 7  | Parallel instructions controlling an ILP architecture                                                          | 17 |

| 8  | Example of a TTA processor datapath.                                                                           | 24 |

| 9  | An operation scheduling example showing MIMD scheduling freedom.                                               | 27 |

| 10 | Resource overcommitting example.                                                                               | 28 |

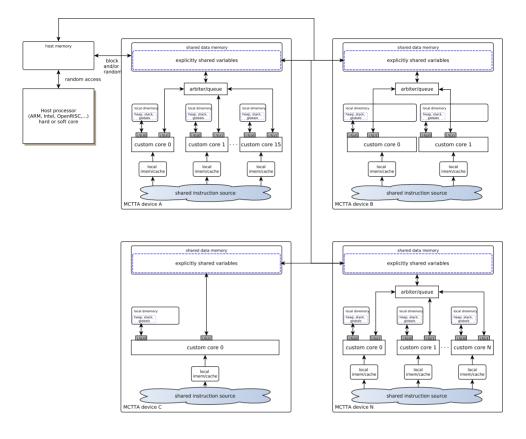

| 11 | Example of a heterogeneous MPSoC with multiple multicore TTAs.                                                 | 34 |

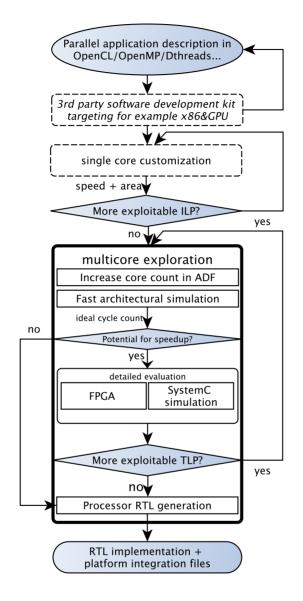

| 12 | The toolset supported design flow of parallel customized processors.                                           | 37 |

| 13 | The single core customization flow.                                                                            | 38 |

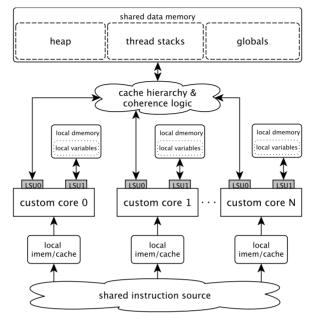

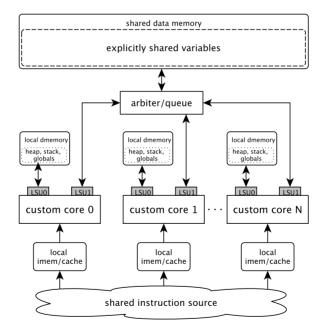

| 14 | Two different configurations of the memory model depending on the placement of the default data address space. | 47 |

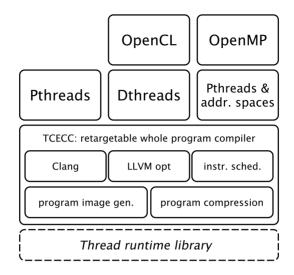

| 15 | The software stack of TCEMC                                                                                    | 50 |

| 16 | Dot product using the proposed Dthreads API                                                                    | 52 |

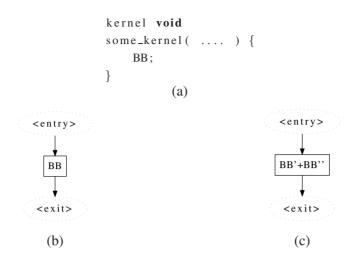

| 17 | Simple example on work-item chaining.                                                                          | 61 |

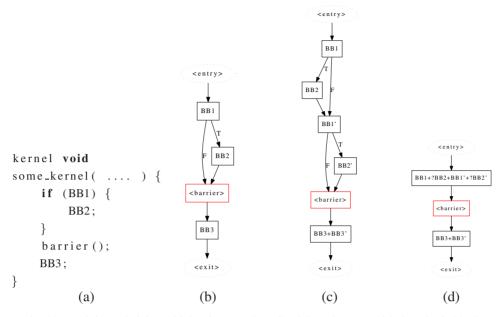

| 18 | Work-item chaining with barriers.                                                                              | 63 |

| 19 | Work-item code replication algorithm.                                                                     | 64 |

|----|-----------------------------------------------------------------------------------------------------------|----|

| 20 | Effect of avoiding register reuse in work-item register allocation                                        | 66 |

| 21 | Example of using a custom operation inside an OpenCL kernel in a portable way.                            | 68 |

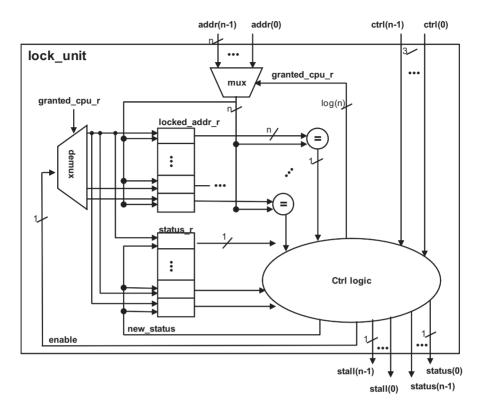

| 22 | An example hardware design of the lock unit.                                                              | 73 |

| 23 | Two spin lock implementations using the lock unit instructions                                            | 74 |

| 24 | Two barrier implementations using the lock unit instructions                                              | 75 |

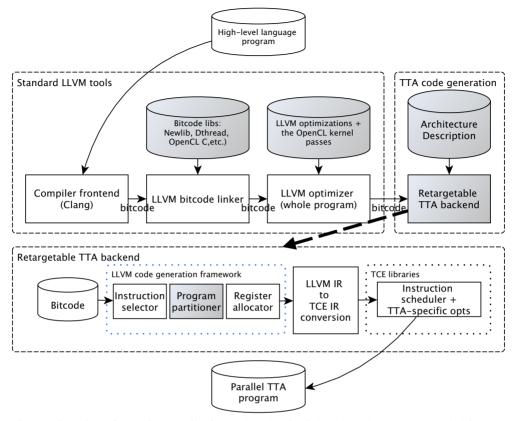

| 25 | Overview of the TCE compiler internals                                                                    | 78 |

| 26 | Wood appearance fragment shader                                                                           | 80 |

| 27 | Output image for the shader benchmark                                                                     | 82 |

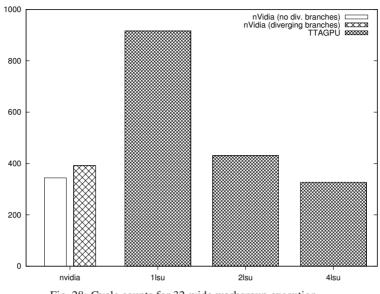

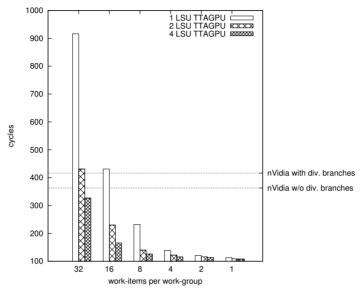

| 28 | Cycle counts for 32-wide workgroup execution.                                                             | 83 |

| 29 | Effect of the work-group size on the cycle count for running the kernel.                                  | 84 |

| 30 | The OpenCL AES encryption implementation                                                                  | 86 |

| 31 | The effect to the minimum processor cycles from increasing the core count.                                | 92 |

| 32 | The organization of the benchmarked multicore ASIP using the lock unit through a SYNC function unit.      | 93 |

| 33 | The microbenchmark that "stress tests" the shared memory overheads of the barrier alternatives.           | 94 |

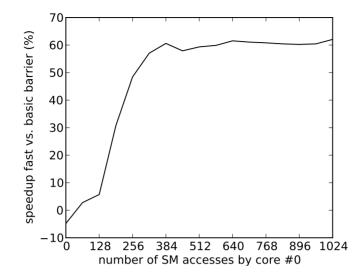

| 34 | The speedups obtained by using the <i>fast</i> barrier in comparison to the <i>basic</i> barrier version. | 95 |

Х

## LIST OF TABLES

| 1 | Required lock registers and shared memory read and write accesses<br>for the alternative lock unit based synchronization implementations. | 76 |

|---|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | Resources in the TTAs used in the shader benchmark                                                                                        | 82 |

| 3 | Effects of software bypassing on register file pressure in the shader example                                                             | 84 |

| 4 | Effect of the parallel Work-Item count to the cycle count                                                                                 | 86 |

| 5 | Resources in the AES TTA processor.                                                                                                       | 87 |

| 6 | Speedups from using custom operations                                                                                                     | 88 |

| 7 | Processor resources in the FFT experiment.                                                                                                | 89 |

| 8 | Execution time results for the FFT core.                                                                                                  | 89 |

## LIST OF ABBREVIATIONS

| AES  | Advanced Encryption Standard                          |

|------|-------------------------------------------------------|

| ALM  | Adaptive Logic Module                                 |

| ALU  | Arithmetic Logic Unit                                 |

| API  | Application Programming Interface                     |

| ASIC | Application-Specific Integrated Circuit               |

| ASIP | Application-Specific Instruction-set Processor        |

| ASP  | Application-Specific Processor                        |

| ASSP | Application-Specific Standard Product                 |

| CAS  | Compare-And-Swap (instruction)                        |

| CFG  | Control Flow Graph                                    |

| CISC | Complex Instruction Set Computer                      |

| СМР  | Chip Multiprocessor                                   |

| DILU | Datapath Integrated Lock Unit                         |

| DLP  | Data-Level Parallelism                                |

| DSP  | Digital Signal Processing or Digital Signal Processor |

| EDA  | Electronic Design Automation                          |

| FFT  | Fast Fourier Transform                                |

| FPGA | Field-Programmable Gate Array                         |

| FSM    | Finite State Machine                                                    |

|--------|-------------------------------------------------------------------------|

|        |                                                                         |

| FU     | Function Unit                                                           |

| GLSL   | OpenGL Shading Language                                                 |

| GPU    | Graphics Processing Unit                                                |

| GPGPU  | General-Purpose computing on Graphics Processing Units                  |

| HLS    | High-Level Synthesis                                                    |

| ILP    | Instruction-Level Parallelism                                           |

| ISA    | Instruction Set Architecture                                            |

| SDDM   | Shared Default Data Memory                                              |

| LDDM   | Local Default Data Memory                                               |

| LLVM   | The LLVM Compiler Infrastructure (originally Low Level Virtual Machine) |

| LSU    | Load-Store Unit                                                         |

| LTT    | Local Thread Table                                                      |

| LU     | Lock Unit                                                               |

| LUT    | Lookup Table                                                            |

| MCASIP | Multicore Application-Specific Instruction-set Processor                |

| MPSoC  | MultiProcessor System-on-Chip                                           |

| NoC    | Network-on-Chip                                                         |

| OpenCL | Open Computing Language                                                 |

| OpenGL | Open Graphics Libray                                                    |

| OTA    | Operation Triggered Architecture                                        |

| PC     | Personal Computer                                                       |

| RA    | Register Allocator                                    |

|-------|-------------------------------------------------------|

| RF    | Register File                                         |

| RISC  | Reduced Instruction Set Computer                      |

| RMW   | Read-Modify Write (instruction)                       |

| RQ    | Ready Queue                                           |

| SDDM  | Shared Default Data Memory                            |

| SDR   | Software-Defined Radio                                |

| SIMD  | Single Instruction Multiple Data                      |

| SIMT  | Single Instruction Multiple Threads                   |

| SMP   | Symmetric MultiProcessor or Symmetric MultiProcessing |

| SoC   | System-on-Chip                                        |

| SPMD  | Single Program Multiple Data                          |

| SPM   | Scratchpad Memory                                     |

| STT   | Shared Thread Table                                   |

| TCE   | TTA-based Co-design Environment                       |

| TCEMC | TTA-based Co-design Environment for MultiCores        |

| TLP   | Task-Level Parallelism or Thread-Level Parallelism    |

| TTA   | Transport Triggered Architecture                      |

| VLIW  | Very Long Instruction Word (architecture)             |

| WG    | Work-Group (OpenCL terminology)                       |

| WI    | Work-Item (OpenCL terminology)                        |

#### **1. INTRODUCTION**

Contemporary embedded systems can include *Multiprocessor System-on-Chips (MPSoC)* which integrate multiple processors and other peripherals on a single chip. Commercial examples of MPSoC platforms in 2012 include the OMAP<sup>TM</sup> [1] family from Texas Instruments, the Snapdragon<sup>TM</sup> family from Qualcomm [2], and the NVIDIA<sup>®</sup> Tegra<sup>®</sup> [3] family. Each of these platforms include multiple processors to be used for, e.g., general-purpose computing, graphics acceleration and *Digital Signal Processing (DSP)*.

In contrast to general-purpose multiprocessors with a large expected set of different applications to execute, the design of a processor targeted to an embedded system can be customized to the requirements of an application domain such as video coding or *Software Defined Radio (SDR)*. This can be seen in the special instruction sets of the processors or in the choices of the used processor architecture styles. For example, the OMAP 4 SoCs of Texas Instruments include a DSP core (C64x) designed for accelerating contemporary multimedia codecs. It has an instruction set optimized for fixed-point computation, and a statically scheduled multi-issue architecture which is expected to perform suboptimally for control-intensive and dynamic workloads, but is able to provide sufficient computation performance for algorithms used in main-stream multimedia codecs. [4]

The number of new hardware design engineering efforts has increased with the improvements in reconfigurable logic such as *Field-Programmable Gate Arrays (FPGA)*. The designs targeting FPGA implementation can include so called *soft cores* where per-design processor customization is commonplace. Thanks to the flexibility of the implementation platform, soft core architectures can be freely customized according to the software running in them, which is their main benefit in comparison to their "hard core" alternatives.

The need for fast time to market of new processor designs targeted for ASIC imple-

mentation of new embedded SoCs or softcores in FPGAs calls for a rapid *co-design methodology* of the included application (domain) specific processors.

More generally, *Electronic Design Automation (EDA)* tool vendors are developing methodologies that expand the usability of their offerings from the hands of relatively low number of hardware-skilled engineers also to the hands of software engineers or algorithm designers. The aim is to provide easy-to-use mechanisms for *High Level Synthesis (HLS)* of hardware starting from algorithm descriptions in programming languages instead of hardware design languages. [5]

The C language has been commonly used as an input to HLS and hardware/software co-design flows [5]. The C program is used to drive a design flow to produce, automatically or manually, hardware accelerators or customized processors executing the described algorithm faster than an off-the-shelf processor would. However, as C is a sequential language, its capability to express parallel operations to utilize naturally parallel hardware constructs is far from optimal, leading to hardware designs with limited parallel resource usage. In contrast, when utilizing a parallel programming language as an input, wider hardware design space can be explored to produce designs that exploit multiple levels of hardware parallelism [6,7].

This Thesis proposes a *Multicore Application-Specific Instruction Set Processor (MCASIP)* co-design methodology that exploits parallel programming languages as the application input format. In the proposed methodology, the designer can explicitly capture the parallelism of the algorithm and exploit special instructions using a parallel programming language in contrast to being on the mercy of the compiler or the hardware to extract the parallelism from a sequential input.

The multicores produced using the proposed design methodology can be used as replacements to fixed function hardware accelerators and as more general "domain-specific" co-processors. The design methodology is independent of the final implementation technique, thus is suitable both for soft core designs in FPGAs and hard core designs implemented as ASICs or ASSPs (application-specific standard prod-ucts).

The Thesis proposes several enabling components required for customized multicore design: a multicore processor template tailored for *Single Program Multiple Data (SPMD)* programming languages, compiler techniques involved in static instruction-level parallelization of SPMD computation kernels with barriers, and a simplified

instruction set for low overhead software synchronization implementation. These contributions enable the designer to scale the customized processors both at the instruction and task levels to exploit the parallelism in the input program up to the implementation constraints such as the memory bandwidth or the chip area. The proposed techniques are validated with case studies, comparisons and design examples.

#### 1.1 Research Objectives

The higher-level objective of the research conducted for this Thesis was to develop a methodology and its related techniques for customized parallel processor design. The scope of the methodology under research was limited to the case where the input is a program that expresses parallel execution in the *Single Program Multiple Data (SPMD)* style, and the output is an homogeneous parallel processor which can be potentially used in a larger heterogeneous system as an accelerating building block.

An objective within the research was to study the benefits of the *Transport Triggered Architecture (TTA)* in providing finer-grain parallelism (TTA is an exposed datapath static multi-issue architecture that has been proposed as a more scalable VLIW [8]). More generally, a research goal was to identify benefits of the *Multiple Instruction Multiple Data (MIMD)* programming model of static multiple issue architectures in comparison to the common *Single Instruction Multiple Data (SIMD)* model.

In addition to the single core customization aspects, a research goal was to propose a processor template that enables task level parallelism customization with minimal designer effort. The scope of this research was limited to shared memory architectures. Within this scope, efficient hardware accelerated synchronization between the cores was identified as a main topic to study in more detail.

In order to map the parallel software to the parallel processor hardware, a research objective was to produce static parallelization techniques for SPMD programs. In this part of the research, the scope was limited to programming languages with kernels that include barrier synchronization. The *Open Computing Language* [9] was used as an example input language in that work.

#### 1.2 Main Contributions

The main contribution of this Thesis is a methodology for producing customized parallel processors that can support the parallelism available in parallel programs at multiple granularities. Within this work at least the following novel contributions are presented:

- A customizable multicore processor template tailored for scaling parallel processor resources at multiple levels. Part of this work was a comparison of the TTA to other parallel datapath design styles in the context of instruction or data level parallel workloads.

- Techniques for efficient scheduling of parallel barrier-synchronized kernels to statically scheduled instruction-level parallel datapaths.

- A simplified memory system isolated data path integrated hardware lock unit to reduce the overheads of the common software synchronization primitives and their impact to the shared memory traffic.

#### 1.3 Author's Contribution and Collaboration

This Thesis is based on previous publications [10–13] in which the Thesis Author has acted as the main or a second author with major contributions. The Thesis contains edited and augmented text from these publications.

The author has been heavily involved in the design, implementation and team coordination effort of the *TTA-based Co-design Environment (TCE)*, a software toolset laying the foundations for the work presented in this thesis. For the TCE software implementation contributions, the author has been the main programmer of the instruction set simulator [14], the fundamental multicore features, the TCE OpenCL support, and parts of the retargetable compiler chain.

The collaboration with Mr. Carlos Sánchez de La Lama of Universidad Rey Juan Carlos (URJC), Madrid produced many of the ideas in this Thesis. This collaboration led to the research on using TTAs for highly parallel graphics-style workloads. Results from this work were published in [10]. In addition, the fundamental ideas on

how to exploit the (then recently released) OpenCL standard to extract abundance of static instruction-level (and data-level) parallel code by means of parallelizing code from multiple kernel instances were produced with Mr. Sánchez de La Lama. The initial results from this work were published in [12, 15]. For these publications, Dr. Pablo Huerta of URJC contributed the AES benchmark. The implementation work of the static OpenCL C kernel parallelization techniques was conducted in co-operation with Mr. Sánchez de La Lama.

The proposed multicore processor template was largely inspired by contemporary GPU designs which were also used as basis for the platform and memory models of the OpenCL standard. However, generalizing and adapting the template to a customizable processor design methodology was proposed by the Author. Implementation of the template in an architecture description language, and the first experiments were published in [11].

Finally, the author's research on reducing the effects of synchronization primitives to the shared memory traffic in customized manycore designs with a shared address space lead to the Author's idea of the datapath integrated lock unit, published in [13]. The first hardware design of the lock unit was produced by Dr. Erno Salminen and Mr. Otto Esko who also produced an FPGA prototype of the 48-core TTA processor used in the synthetic synchronization benchmark presented in Section 8.5.

#### 1.4 Thesis Outline

The rest of the Thesis is organized as follows. Chapter 2 revises the concepts related to parallel embedded computing that are referred to in the rest of the Thesis. Further background is given in Chapter 3 where a class of processor architectures called "the exposed datapath architectures" is defined. In addition to studying the other work in exposed datapath architectures, the *Transport Triggered Architecture* which is the single core exposed datapath processor template used in the proposed design methodology is discussed in more detail in the chapter.

Chapter 4 describes the high-level of the proposed parallel processor customization methodology in which new processors are instantiated from a processor template detailed in Chapter 5.

While the processor template is designed to support multiple parallel programming

language standards, support for the OpenCL standard was the first priority in this research due to its increasing popularity. Its adaptation to the design flow and the related compiler techniques are described in Chapter 6.

The synchronization instructions that use a simplified lock hardware to minimize synchronization overheads in the thread execution are described in Chapter 7.

Benchmarks and experimental designs are presented in Chapter 8. Finally, the Thesis is concluded in Chapter 9 along with examples of ideas for future work.

#### 2. PARALLEL COMPUTING

This Thesis refers to several concepts and techniques related to parallel computing on embedded devices. This chapter shortly revisits these concepts. The definitions can be started with the concepts of "parallelism" in comparison to the concept of "concurrency". A *concurrent* program is defined to be a set of processes of execution that might communicate and synchronize with each other. *Parallelism* can be described as executing multiple operations from a program simultaneously for improved execution time, or for other benefit such as reduced power consumption. A *concurrent* program, on the other hand, can also be executed in an interleaved manner without actual simultaneous computation taking place, thus can be seen as a way to structure programs [16]. In the rest of this thesis, the term *parallelism* is used both when writing about programming languages that can be used to express parallel execution (with the goal of improving performance) and also when writing about the processing hardware that executes operations simultaneously.

The rest of the chapter visits concepts from the point of view of the parallelism support in software and processor microarchitecture techniques that implement parallel execution at multiple levels of granularity.

#### 2.1 Expressing Parallelism in Software

Experience has shown that it is very difficult, computationally expensive, and often just plain impossible to automatically extract parallelism from sequential programs [17]. Even if the algorithm at hand was inherently parallel, a sequential programming language does not provide the expressiveness to communicate it to the compiler, thus it forces the compiler to extract the parallelism by means of complex compiler analysis. Therefore, exploiting parallel processor resources efficiently requires the use of parallelism programming languages and libraries [16].

```

#pragma omp parallel for

for(i = 0; i < width; i++) {

result[i] = A[i] + B[i];

}</pre>

```

Fig. 1: A parallel for-loop computing a vector addition using the OpenMP pragmas in a C program.

Several parallel programming languages have been proposed. Their adoption has been hindered by the additional difficulty of parallel programming in comparison to sequential programming [16]. Afterall, the design of many parallel languages and libraries has been driven by the characteristics of the platforms at hand with less consideration to the programmer-friendliness [18]. For example, the POSIX threading library *pthreads* [19] allows describing task level parallelism in C programs using shared memory communication. It provides means to spawn "threads of execution" in a single process which shares memory, thus provides a low-level API for describing *Thread Level Parallelism (TLP)*.

Describing massively parallel programs, such as ones that exploit *loop level parallelism*, using lower level threading libraries such as pthreads is burdensome. Therefore, more programmer-friendly APIs such as OpenMP [20] have been proposed to ease this task.

For example, the OpenMP *parallel for* construct (see Fig.1 for an example) allows describing *Single Program, Multiple Data (SPMD)* parallelism. In SPMD, the same program code (in this case, instructions forming a loop iteration) is executed on parallel processing elements over different sets of data (different locations in the input arrays). This style of parallelism is called *Data Level Parallelism (DLP)*. Programs with DLP can be mapped to the computational resources of different processor architectures in multiple ways as can be seen later in this chapter.

*Instruction Level Parallelism (ILP)* can be seen as a superset of DLP. It loosens the restriction of *Single Instruction stream Multiple Data streams (SIMD)* performing the same operation to parallel data to *Multiple Instructions streams Multiple Data streams (MIMD)*. That is, a processing platform that can support ILP can execute multiple different operations to multiple different data simultaneously, therefore, widening the scope of types of programs that can be parallelized. Figure 2 presents a

```

sum = a + b;

diff = a - b;

```

Fig. 2: A snippet of a program with instruction-level parallelism.

simple program that can be parallelized using ILP-capable hardware that can execute both the addition and the summation at the same time.

The examples of OpenMP and pthreads were given as ways to describe parallelism in the C language which is popular especially in the embedded domain. The C language itself is an example of an *imperative language* and is sequential in nature. That is, the compiler or the processor hardware has to extract the finer granularity parallelism from the program descriptions as there is no means to explicitly express parallel computation at the statement level.

An example of compiler analysis that is needed when automatically parallelizing C programs is the alias analysis. The example in Fig. 3 shows a basic case which already makes the compiler analysis non-trivial. In this case, the vector addition is a function which takes in three pointers to the input buffers and a result buffer. In order the compiler to be able to parallelize or reorder instructions from multiple iterations of the inner loop, it has to prove that the writes to the *result* buffer do not also write to some locations of A or B because of overlapping memory regions in the pointer buffers. Without *interprocedural alias analysis* it is impossible to know at compile time if the pointers given as the function arguments indeed point to overlapping regions in memory. [21]

```

void vec_add(float *A, float *B,

float *result, int width) {

int i;

for(i = 0; i < width; i++) {

result[i] = A[i] + B[i];

}

}</pre>

```

Fig. 3: Vector addition in ANSI C.

This particular case was addressed in ISO C99 [22] with the introduction of the *re-strict* qualifier. The qualifier can be used to mark pointers to be such that their memory region is accessed only through that pointer in the scope of the pointer declaration. This is a simple way to communicate hints to the compiler for improving parallelism. However, it is not a general solution as it applies only to the simple case. It cannot be used to improve parallelization of more complex access patterns such as independent accesses to different locations in the buffer or accesses to arrays with indices read from an another array, etc.

*Functional languages* describe the programs as stateless function calls which result in parallelizable computation trees. While functional programming is convenient for software engineers with a mathematical background, imperative programming, especially with the C-based languages, is still used by the majority of software engineers [23].

An important consideration with parallel programming is the means to communicate between the "units of computation" (later referred to as *threads*). In case of OpenMP and pthreads, for example, a random accessible shared memory is used to transfer data between the threads. Mutual accesses to the shared data are assumed to be synchronized using primitives such as *locks* and *semaphores*. Otherwise, data corruption can occur when two or more parallel threads modify the same shared memory locations at the same time (race condition).

Another prevalent communication method is "message passing". In this method, explicit "messages" that contain the data are sent between the threads which can run in the same multiprocessor or even in different computers in a networked cluster. The explicit synchronization is avoided as the threads do not modify shared data directly during the communication.

The benefits of shared memory communication include the potential to reduce copying of data which is required in the message passing implementation. Additionally, *load balancing* is easier when there is a ready queue of threads in the shared memory from which to fetch threads to an idle processor. The main drawback is that the implementation of the shared memory hierarchy in hardware becomes expensive with larger number of processor cores. Therefore, a common solution is to use both methods: message passing for higher granularity communication (e.g., between computers in a cluster or separate processors in a heterogeneous MPSoC) and a shared

```

spin_lock(lock_var* A) {

lock_var old;

do {

old = CAS(A, 0, 1);

} while (old == 1);

}

```

Fig. 4: Spin lock and unlock implementations using the atomic Compare-And-Swap instruction.

memory model inside a multicore for faster pointer based communication between tightly coupled threads [24].

#### 2.1.1 Synchronization Primitives

Locks, barriers, and semaphores are basic synchronization primitives used to orchestrate the execution of a multithreaded program. Lock variables typically reside in shared memory and atomic *Read-Modify-Write (RMW)* instructions are needed for manipulating them without corruption. Locks are used to perform mutual exclusion to ensure critical sections that manipulate shared data structures are executed only by one thread at a time.

A common synchronization primitive heavily used in system code is the *spin lock*. It performs busy wait until the *lock variable* is marked "free" (usually by writing 0 to the variable). It can be implemented with a loop that "spins" until it manages to write 1 to the target lock variable before other threads do. The atomicity of the lock acquiring operation can be implemented with RMW instructions in the instruction set.

In case a spin lock is implemented using RMW instructions, the spin lock loops until it manages to swap a 0 to a 1 at address *A*, meaning it obtained the lock without it being locked before by another thread. The basic primitives can be implemented using the atomic *Compare-And-Swap (CAS)* operation as shown in Fig. 4. Note that the unlock can be implemented with a simple store to the lock address location in case the program is known to be well-behaved and there is no need to check for lock ownership.

Another common synchronization primitive used especially in SPMD programs is the *barrier*. Barriers are used to synchronize the control flow of all threads co-operating in the execution of the multithreaded program. The semantics of the barrier is to wait

at the barrier call site until all other threads have reached the barrier. After all threads have reached the barrier, the execution of the threads continues freely. The simplest barrier implementations use counter variables that are protected with locks [25]. They count how many threads have reached the barrier and block the waiting threads until the counter reaches the total number of threads.

#### 2.1.2 Open Computing Language

In December 2008, a joint effort between major companies and other interest groups related to parallel heterogeneous programming led to the standardization effort of *Open Computing Language (OpenCL)* [26]. Albeit the background of OpenCL is clearly in the *General-Purpose computing on Graphics Processing Units (GPGPU)* community, and its version 1.2 highly resembles the proprietary CUDA language from NVIDIA [27], the aim of OpenCL is to become a universal programming standard for platforms with heterogeneous processing devices such as GPUs, CPUs and DSPs.

OpenCL programs structure the computation into *kernels* defined in OpenCL C kernel language, and specify that there shall be no data dependencies between the "kernel instances" (*work-items*, analogous to loop iterations) by default. The implementation is free to execute code from the different kernel instances sequentially, in parallel, or in an interleaved fashion, as long as the explicit synchronization primitives (e.g., *work-group barriers*) present in the kernel descriptions are respected.

The example OpenCL C kernel in Fig. 5 computes a dot product for a single location in two input buffers a and b, and places the result in the result buffer c. This kernel can be executed on different sized vectors in parallel, using as many *work-items* as there are elements in the vector. *get\_global\_id(0)* is used to query the index of the work-item in the *global index space* which in this case maps directly to the index in the buffers.

One point of difference to standard C notation in this example is the use of the *global* qualifier in the kernel arguments. This is used to mark the pointers to point to buffers in *global memory*. Other disjoint explicitly addressed memory spaces in OpenCL C include the *local memory* visible to single *work-groups* (groups of work-items within the global index space that can synchronize with each other) at a time, the *private*

Fig. 5: Vector dot product in OpenCL C.

*memory* visible only to single *work-items*, and the *constant memory* for storing readonly data.

The OpenCL runtime API (a separate API in standard C) is used to launch kernels and data transfer commands in one or more *compute devices* with *event* synchronization. Portability of OpenCL programs across a wide range of different heterogeneous platforms is achieved by describing the kernels as source code strings which are then explicitly compiled using the runtime API to the targeted devices.

While the OpenCL standard provides an extensive programming platform for portable heterogeneous parallel programming, the version 1.2 of the standard lacks in means to achieve *automatic performance portability*. It is burdensome to write an OpenCL program that performs efficiently on multiple heterogeneous computation platforms [28]. Recently it has been proposed that the performance portability of OpenCL could be improved with an introduction of a "virtual device" abstraction or a higher-level programming layer that would hide the device-specific optimization problems from the programmer [29, 30]. In addition, *auto-tuning* has been used to improve the performance portability of the OpenCL programs [29, 31].

OpenCL is an attractive candidate to act as an input for a customized parallel processor design flow such as the one proposed in this Thesis because it allows explicit definition of parallel execution at multiple granularities. Operations on OpenCL C vector data types express data level parallelism within a single work-item and the work-groups themselves implicitly describe data parallel execution across multiple work-items that is explicitly synchronized with barriers. Task level parallelism can be described at the higher level with parallel execution of multiple kernels and workgroups.

#### 2.2 Parallelism in Processor Architectures

Parallelism is a means to improve the performance of a program without increasing the clock frequency. Processor architectures expose parallel computation resources to programs in different ways at the different granularities which are discussed in the following.

#### 2.2.1 Instruction Level Parallelism

Pipelined execution in an in-order scalar processor can be seen as a way to exploit instruction-level parallelism by overlapping different *stages* of the instruction execution from multiple instructions. In such a case, data dependencies between instructions might cause pipeline stalls which can be reduced by compiler *instruction scheduling* [32], a compiler optimization that places independent instructions after each other to promote the overlapping for decreased pipeline idle time. Real parallel *execution* of multiple instructions requires, by definition, multiple parallel function units (*multi-issue*) [33].

Whether it is the responsibility of the compiler or the processor hardware to exploit the instruction-level parallelism places multi-issue processors somewhere between the classifications of *dynamic* and *static architectures*. Dynamic multi-issue architectures rely on processor hardware to extract and exploit the parallelism in a sequential input program while static multi-issue architectures rely on the compiler. This classification is not binary, that is, the real processor architectures have different levels of reliance on the compiler.

Superscalar processors can exploit hardware techniques such as hardware data dependency detection, out-of-order execution, and speculation to issue multiple instructions from the sequential program input to the multiple function units in the processor pipeline. The main benefit of such dynamic exploitation of parallelism include binary compatibility: old sequential programs run in the newer versions of the same architecture family without program recompilation. The main drawback is the added complexity in the control hardware to recognize the parallel instructions at runtime which leads to increased chip area and power consumption. [34]

*Very Long Instruction Word (VLIW)* architectures belong to the class of static multiissue architectures. VLIW designs go towards the idea of *exposed datapath archi-* *tectures* (discussed more thoroughly in the next Chapter) where the compiler (or the programmer) is given the responsibility to describe which instructions should be executed in parallel. The instruction latencies are also exposed to the programmer in VLIW architectures. Instructions have to be scheduled in such a way that they do not read their results too early or too late. The benefit of the VLIW style is clearly the simplified control logic which enables potentially very wide instruction issue widths which is achieved by placing the complexity to the compiler. In addition, the instruction windows of dynamic hardware are more limited in size while compilers see the whole function when they look for parallelism, which can lead to more parallelization opportunities. [35, 36]

How much weight should be put to the drawback of the binary incompatibility issue of static architectures depends on the usage target. In general-purpose computing where source codes of all input programs are not commonly available, it naturally is problematic [37]. On the other hand, with embedded processors, especially in case of customized architectures where the hardware and software is often co-designed using an automatically retargetable toolchain, the harm is diminished. Moreover, with the advent of programming standards targeted to platforms with heterogeneous devices, compilation from an intermediate language to the target instruction set has been made a step in the application execution [9].

Another consideration between dynamic and static architectures is how well they can deal with dynamism in the input programs. For example, dynamic architectures can react better to variable length runtime events such as those from cache accesses. An out-of-order processor can hide the cache misses more naturally than a static architecture of which instruction execution is scheduled according to static instruction latencies. [38]

Branches in the program are another source of dynamism. Dynamic architectures can use techniques such as dynamic branch prediction [39] and speculation [34] to schedule instructions from a predicted path of the program ahead of time. Similar results can be achieved using the compiler by means of predicated execution (e.g., using if-conversion [40]) or speculative code motion (e.g., with trace scheduling [41]).

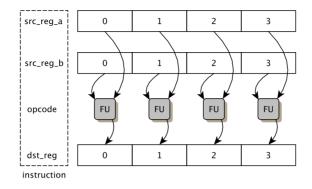

Fig. 6: Illustration of how the instruction bit fields control a SIMD datapath. SIMD instructions can refer to wide vector registers with subwords instead of defining the independent elements, thus compacting the instruction word. The opcode field controls all the four parallel function units (FU). In this case the SIMD instruction expresses four parallel operations on independent elements 0..3 of the vector registers.

#### 2.2.2 Data Level Parallelism

Data level parallelism is a more restricted form of parallelism than ILP. In contrast to ILP where multiple different parallel operations can be applied to multiple different data, DLP is limited to same operation applied to multiple data.

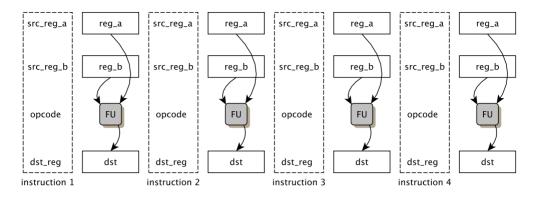

A major benefit of limiting the parallelism to DLP in the processor architecture is requiring less instruction bits per executed parallel operation. In case of DLP, multiple parallel operations can be described by using a single opcode field and vector register identifiers (see Fig. 6). In comparison, the ILP architectures each operation requires a separate opcode field and one or more scalar register identifiers (see Fig. 7).

Single core architectural support for data-level parallel programs is provided by means of vector instruction set extensions (e.g., Intel<sup>®</sup> Advanced Vector Extensions [42] and the ARM<sup>®</sup> NEON<sup>TM</sup> general-purpose SIMD engine [43]) or with more SIMD-oriented instruction sets (e.g., the Synergistic Processor Unit in the Cell Broadband Engine [44]).

In order to efficiently utilize a SIMD datapath in SPMD-style execution, parallel operations are extracted from multiple SPMD program "threads" or loop iterations with loop vectorization. The matching operations from the different iterations are scheduled to execute in lockstep in the *vector lanes* (parallel scalar function units controlled by the SIMD instruction). This results in parallel execution of N iterations using a single SIMD instruction stream, where N is the *issue width* of the SIMD

Fig. 7: Four parallel instructions controlling an ILP architecture with four parallel function units (FU). The instructions specify scalar operations. Each instruction can define a separate opcode for the computed data. The drawback is the program memory overhead of the four separate instructions.

hardware.

The "lockstep SIMD" style of execution is efficient as long as the iterations do not have diverging control paths such as an if-else-structure of which execution path depends on the iteration (thread id). In case of diverging branches, some of the vector lanes should be disabled in case all of the parallel iterations are not executing the branch at hand. This problem is discussed in more detail in the next chapter.

In some SIMD instruction sets, vector masks provide architectural support for diverging branches. In such cases, some of the vector instructions in the instruction set include a mask register operand which communicates the set of lanes that are enabled, thus providing the ability to "squash" the execution of the diverging iterations. Intel's Advanced Vector Extensions, for example, support load/store masking which can be used to squash the loads and stores of the disabled lanes. In addition, its *blend instructions* can be used to pick selected elements from input vectors to implement conditional branches as conditional data selection. [42]

Contemporary manycore processors originally designed for graphics processing, which are nowadays used also for general-purpose high performance computing, have their architectures optimized for SPMD programs. [27, 45]

An example of a processor architecture feature tailored for SPMD programs is *Single Instruction Multiple Thread (SIMT)*. SIMT is a term used mainly by NVIDIA. It differs from the lock-step SIMD execution in its ability to handle diverging branches in the program code transparently. SIMT hardware includes a separate program counter per each function unit that is used to disable the execution in case the processor is currently executing an instruction from a branch that should not be taken by the SPMD thread mapped to the unit. In the SIMT case, instead of decoding statically parallel wide SIMD instructions, the processor hardware inputs a single thread/iteration of the SPMD program which is distributed to the parallel scalar cores at processor runtime. [27, 46, 47]

#### 2.2.3 Task Level Parallelism

Instruction scheduling, implemented by either the compiler, the processor microarchitecture, or both, can be used to hide latencies in the instruction pipeline. However, parallelism at the instruction-level has its limits. Most programs do not have enough independent instructions to hide very long latencies (hundreds or even thousands of clock cycles) that occur with cache misses. Furthermore, such latencies are usually dynamic, thus they cannot be efficiently alleviated with static compiler instruction scheduling. [36]

Multithreading is a technique that can be used to hide long latencies with useful computation by switching the execution to other independent threads of execution whenever long latencies occur (*coarse grained or "block" multithreading* [48]) or even at every cycle (*fine grained multithreading* [49]) for hiding also shorter latencies.

In order to benefit from *Task Level Parallelism (TLP)* (also called Thread Level Parallelism), the program must be structured in independent threads of execution. The idea in TLP is to utilize the execution resources in the processor to advance other parts of the program (or even a completely different program running in another process) while another thread waits for a long latency operation to be served. Fast context switches require duplication of some resources, usually the register file, in the hardware to avoid slow copying and restoring of context data residing in a slower storage [48]. One interesting implementation of multithreading is *Symmetric Multithreading (SMT)*. SMT extends the dynamic processor hardware used for extracting ILP from a single thread to schedule instructions from multiple threads simultaneously to the function units in the machine, therefore interleaving execution from multiple threads on every cycle. [50]

Multithreading implements TLP by duplicating the processor resources only par-

tially. Fully parallel TLP requires duplicating the resources of the whole core to implement independent execution of multiple threads.

Multiprocessors include two or more full instances of processor cores to support executing multiple threads simultaneously. In case the processors are implemented in separate chips, the thread communication bottleneck is high. The increasing number of available transistors per chip has made it possible to include multiple cores in a single chip (*Chip Multiprocessors, CMP*). CMP allows cores to communicate with fast lower level caches for enhanced inter-thread data transfer speed. [51]

The connectivity, the level of memory sharing, and the datapath uniformity among the multiple cores leads to different categorizations of the multiprocessors. A *Symmetric Multiprocessor (SMP)* is a *homogeneous* multicore setup where the cores with identical instruction set architectures (ISA) access a shared memory. The shared memory is usually cached using cache coherence logic in hardware to maintain a consistent view to data from all the cores. This style of setup is easy to program as any thread can be assigned to any core uniformly which also eases load-balancing.

A major drawback in the SMP setup is the single shared memory bus and the associated cache coherence logic which becomes a bottleneck with increasing number of cores attached to it. *Non-Uniform Memory Access (NUMA)* improves the situation by dividing the memory hierarchy to *local memories* that are fast to a subset of cores, and *remote memories* that are slower to access (but are local to another subset of cores). [52]

In contrast to homogeneous multiprocessing where the cores are identical, *heterogeneous computation platforms* include multiple processors with different microarchitectures and varying memory hierarchies. The benefits from such setups are clear whenever the platform is supposed to run a varying set of algorithms from different application domains, or just a large application using a range of varying algorithms. The assumption is that a processor tailored to a specific application domain can execute the application more efficiently (e.g., with less power or area, or faster) compared to a more general-purpose core. This potentially leads to better utilization of the processing resources as the best matching cores can be picked for each algorithm. For example, running a serial control-oriented program in a 12-issue VLIW architecture is waste of the computational resources, while, on the other hand, a statically parallel algorithm can be executed very quickly on such an architecture after which the core

can be switched off for power saving. [53]

Heterogeneous platforms are common in the embedded domain. In embedded *System-on-a-Chip (SoC)* platforms, processors with different ISAs, hardware accelerators and peripherals are integrated to a single chip. A subcategory of SoCs is the *Mul-tiProcessor SoC (MPSoC)* which means a SoC with more than one programmable processors on the same chip [54]. Another heterogeneous processing style that has received interest in the recent years is the GPGPU setup where a general-purpose processor runs an operating system and more serial parts of the program which is accelerated using a different processor originally designed for high performance graphics processing.

# 2.3 Customized Parallel Processors

In general, hardware-software co-design is a means to design an electronic system as a combination of application software running in instruction set processors and parts implemented with fixed function hardware. In hardware-software co-design methodologies, consideration of the hardware resources available in the designed system, the software organization, and the mapping of algorithms to the different resources in the system is performed concurrently. [55] In this Thesis, the focus is on a smaller subset of the co-design problem, that is, the co-design of instructionset processors. Such processor co-design is performed at a phase of the electronic system design when a piece of application is mapped to a software-reprogrammable processor of which datapath resources should be customized to meet the requirements of the application at hand.

The line between the definitions of *Application Domain-Specific Processors (ADSP)*, *Application-Specific Instruction-set Processors (ASIP)* and *Application-Specific Processors (ASP)* is thin. The difference is defined to be in their level of specialization and compromises made to the generality in programmability. ADSPs are designed to be used for a wider range of algorithms within a single domain, such as processors tailored for popular multimedia codecs [56]. The concept of ASIP and its difference to ASP, however, is not so strictly defined in the literature. ASIP is commonly understood as a programmable hardware accelerator, a specialized replacement for a fixed function accelerator implemented as an ASIC or on an FPGA. Corporaal [8] proposes an additional level of specialization. He describes the difference between

an ASIP and ASP being in the software reprogrammability. In his definition, ASIP, while tailored for a single application, can still support (albeit perhaps not as efficiently) all programs defined in a higher-level language, while ASP can run only the targeted program, thus can be seen as merely a means to implement a fixed function accelerator.

The design methodology described in this Thesis supports all the above levels of processor specialization. Therefore, a common definition of *customized processor* will be used in the rest of this Thesis to describe the general case of a processor tailored for a *known set of targeted applications* (where the size of the set can vary from one to many).

A suggested difference between customized processors and "off-the-shelf" processors is that with customized processors the fabrication volumes can be lower and their "turn-around-time" shorter [57]. In other words, the design effort per manufactured chip is expected to be higher. In order to lower the design time, the customized processor design methodologies should be supported by design toolset with automatic toolchain retargeting. Especially important tool in such toolsets is an automatically retargetable higher-level language compiler, in order to avoid manual porting of assembly language programs to the designed processor variations, or manual retargeting of the compiler backend. Otherwise, the process of finding the desired processor alternatives (design space exploration) for the programs at hand is not feasible.

In order to make implementing a processor design toolset feasible, the *design space* of the customized processor alternatives is usually limited using a *processor template* which defines the set of parameters within which the new designed processors can differ [58]. Some processor templates limit the customization capabilities to one or more extra *special instructions* (also known as *custom operations* or *special function units*) attached to a predefined processor datapath. In some cases, the special instructions can also be runtime reconfigurable. Some templates allow customizing also the issue-width and the number of general purpose registers to match the provided ILP or DLP in the processor with the parallelism available in the programs at hand. In addition, the provided TLP can be varied in some templates (such as the one proposed in this Thesis) by defining the number of processor cores or the processor contexts available for multithreading. In these cases, the processor template supports the customization of the level of parallel execution resources provided by the processor, thus leading to the subcategory of *customized parallel processors*. [59]

# 3. EXPOSED DATAPATH STATIC MULTI-ISSUE ARCHITECTURES

The term "exposed datapath" is seen in the literature being attached to processor architectures where the processor datapath resources and even in some cases the data transports between the register files and function units are exposed for the direct control of the programmer. [60–62]

The *Transport Triggered Architecture (TTA)* which is used as the single-core processor template in the proposed processor customization flow can be classified as an exposed datapath architecture as it presents very low level details of computation to the programmer. The motivation for using an exposed datapath comes from the assumption of a parallel input program. As the input is parallel, as little additional hardware as possible should be dedicated to the runtime extraction of parallelism.

This chapter introduces the TTA, compares it to the other common parallel datapath paradigms, and reviews the work in the exposed datapath architectures.

# 3.1 Transport Triggered Architectures

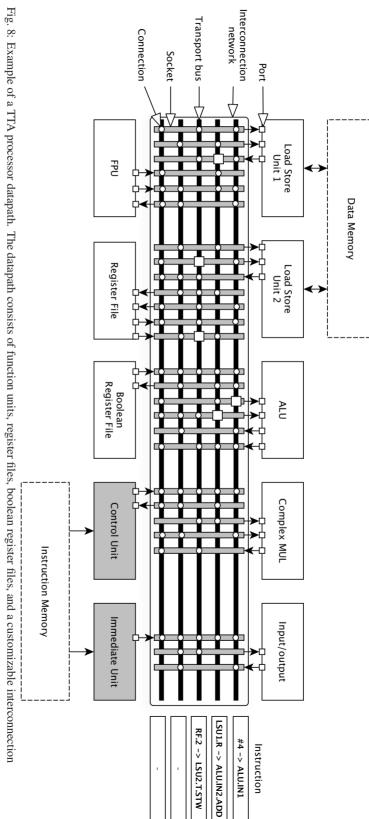

VLIWs are considered interesting processor alternatives for applications with high requirements for data processing performance [63] and with limited control flow. *Transport Triggered Architecture (TTA)* is a modular processor architecture template which can be used as a design paradigm for wide static multi-issue architectures. The main difference between wide TTAs and VLIWs can be seen in how they are programmed: instead of defining which operations are started in which function units (FU) at which instruction cycles, TTA programs are defined as data transports between register files (RF) and FUs of the datapath. The operations are started as side-effects of writing operand data to the "triggering port" of the FU. Fig. 8 presents a simple example TTA processor [8].

register to memory. The rest of the buses are idle. The connections enabled by the moves are highlighted with squares defines moves for three buses out of five, performing an integer summation of a value loaded from memory and a constant. In parallel, the third move stores a network. Data transports are explicitly programmed; a write to a special trigger port of a function unit starts the operation execution. The example instruction The programming model of VLIW imposes limitations for scaling the number of FUs in the datapath. Increasing the number of FUs has been problematic in VLIWs due to the need to include as many write and read ports in the RFs as there are FU operations potentially accessing it the same time. Additional ports increase the RF complexity, resulting in larger area, critical path delay and power consumption. Register file complexity of wide VLIW architectures has been identified as an obstacle in adoption of large VLIW architectures as soft-cores in FPGAs [64].

In case the VLIW supports register file bypassing, adding an FU to the datapath requires new bypassing paths to be added from the FU's output ports to the input ports of the other FUs, increasing the interconnection network complexity. Thanks to its programmer-visible interconnection network, TTA datapath can support more FUs with simpler RFs [65]. Because the timing of data transports between datapath units are programmer-defined, there is no obligation to scale the number of RF ports according to the worst case number of FUs accessing the RF at the same time [66]. As the register file bypassing is done in software instead of hardware, it is often possible to avoid the use of general-purpose registers as temporary storage, thus reducing both register pressure and register file port requirements even further. In addition, as the datapath connectivity is part of the architecture (visible to the programmer), it can be tailored according to the set of applications at hand, including only the most beneficial connections.

### 3.2 Benefits of TTA in Single Program Multiple Data Computation

The SIMD/vector or SIMT processors provide a good balance between hardware complexity and programming flexibility, but, in order to be efficient, the executed program must be data parallel, i.e. contain parts that can be efficiently vectorized with minimal branch divergence. Otherwise, diverging branches where the number of parallel instances of the SPMD program going into each branch is not a multiple of the issue width size will cause resource underutilization.

For example, let us assume a lockstep SIMD-programmed machine with 16 parallel function units, thus capable of running 16 instances ("threads") of a given program in parallel. Each thread is given a unique identifier (*thread\_id* or an iteration number). In order to see the level of function unit idle time the SIMD execution model can cause, let us consider a couple of example branching conditions:

- (thread\_id % 2 == 0) Every two consecutive threads take different branches. This causes half of the FUs to be idle.

- (thread\_id == 0) Only the first thread enters the branch, rest of the 16 FUs are idle.

The underutilization results from the fact that SIMD/SIMT is limited to a single operation code per SIMD instruction. Therefore, in the case of branch divergence the diverged lanes must be "squashed" at run time using "vector masks" in case of static SIMD instructions or with per-FU program counters in case of SIMT scalar units. In other words, the squashed function units are waiting for the correct branch to be executed for their thread without doing any useful work.

On the other hand, when the program is scheduled for a TTA or VLIW with predicated execution support it is possible to reach higher utilization of FUs for programs with compile-time known control flow given that there are independent parallel operations to schedule at the idle function units. Two clear cases where TTA/VLIW machines can outperform the SIMD/SIMT machines with similar FUs can be isolated:

1. Number of function units in the architecture does not equally divide the number of "threads" in the program.

If a program cannot be split perfectly to the SIMD lanes in the core, TTA/VLIW processors allow using the extra FUs to execute independent parts of the code within the threads itself. Consider a simple program structure like the following:

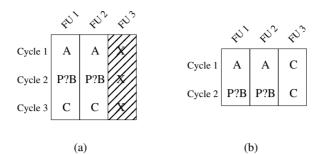

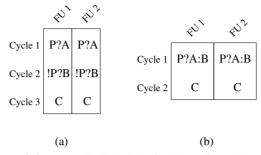

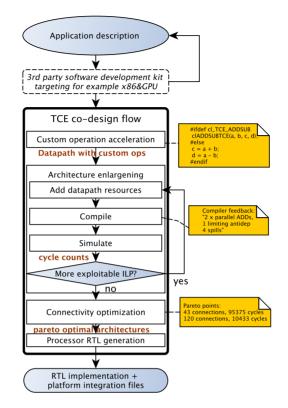

where A, B and C are data-independent. This program is to be run for two pieces of input data. Figure 9(a) shows how this example could be scheduled on a 3-way SIMD group. It can be clearly seen that one of the execution lanes is never used. Figure 9(b) shows how a predicated TTA/VLIW machine with

Fig. 9: An operation scheduling example showing MIMD scheduling freedom. Schedule for (a) predicated 3-way SIMD, and (b) predicated TTA/VLIW. Question mark denotes the predication of the succeeding operation with the preceding predicate register. Each function unit (FU) can execute all the operations (A, B, C).

the same number of function units can save a cycle out of three thanks to the scheduling freedom.

2. Runtime conditions allow "overcommitting" of datapath resources by means of predicated execution.

A TTA/VLIW architecture that supports overcommitting of resources allows scheduling of two predicated operations to be executed in the same function unit at the same time cycle, in case it is known at compile time that the predicates of the two operations are never simultaneously true [67]. Code suitable for overcommitting is usually generated from *if...else* constructs. For example, consider the following program structure:

Let us assume that all operations (A, B and C) in the program are data independent, and that there are two threads scheduled on two FUs. Fig. 10(a) shows the resulting schedule for a SIMD machine: one third of the execution time is wasted for each lane. An overcommitting schedule for VLIW/TTA, as shown in Fig. 10(b) saves that third cycle and results every computing element being used on each cycle.

Fig. 10: Resource overcommitting example. Schedules for (a) predicated SIMD machine without overcommitting support, and (b) predicated TTA/VLIW with function unit overcommitting support. Question mark denotes the predication of the succeeding statement with the preceding predicate, the possible negated statement is given after a colon.

Clearly the programming freedom of overcommitting TTA/VLIW has its benefits in function unit utilization point of view. However, the obvious drawback is that in order to express the additional programming freedom, more program bits are required. The actual impact of this is program dependent and cannot be generalized. While the SIMD style provides excellent instruction density in comparison to the VLIW/TTA approach, the reduced scheduling freedom (single operation code per instruction) might mean that more SIMD instructions are needed due to the diverging branches to encode the whole program. The overcommitting predication support requires the capability to describe, in addition to the predicate, the execution of two operations per each FU, growing the instruction word even wider for the VLIW datapaths. In case of the bus programmed TTA, the number of buses per FU, thus the number of move slots, has to be doubled.

### 3.3 Review of Work in Exposed Datapath Architectures