Jarno Vanne

Design and Implementation of Configurable Motion Estimation Architecture for Video Encoding

Julkaisu 982 • Publication 982

| Tampereen teknillinen yliopisto. Julkaisu 982 Tampere University of Technology. Publication 982                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jarno Vanne                                                                                                                                                                                                                                                |

| Design and Implementation of Configurable Motion Estimation Architecture for Video Encoding                                                                                                                                                                |

| Thesis for the degree of Doctor of Science in Technology to be presented with due permission for public examination and criticism in Tietotalo Building, Auditorium TB109, at Tampere University of Technology, on the 23rd of September 2011, at 12 noon. |

|                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                            |

### **Abstract**

A key factor behind the success of video products and services is video compression that makes digital video practical in the current communication networks and storage devices. However, video compression involves complex encoding algorithms whose real-time execution is particularly challenging in portable devices due to strict constraints on cost, size, and power consumption. In addition, modern devices are expected to be flexible enough to support plethora of video coding standards.

This Thesis focuses on motion estimation (ME) that is the main coding tool for removing temporal redundancy of video scenes and it typically accounts for 50 - 90% of the video encoding complexity. Due to these two reasons, hundreds of algorithms and architectures have been proposed for non-standardized ME. However, most of the current ME architectures are limited to a single video coding standard or ME algorithm, whereas existing flexible architectures are realized with large silicon area, limited processing speed, unsustainable power budget, or over restricted ME parameters.

The main contribution of this Thesis is a novel ME architecture that overcomes all the crucial limitations faced by the contemporary approaches. The designed and implemented hardware architecture is compatible with all inter coding modes of H.261/3, MPEG-1/2, MPEG-4 Visual, H.264/AVC, and VC-1 standards. In addition, it can perform rate-constrained integer ME (IME) with various fast ME algorithms such as BBGDS, CDS, DS, HEXBS, and TSS. It also reduces the complexity of the subsequent fractional ME (FME) by conducting mode decision jointly with IME. The flexibility of the architecture is based on a parametrizable search strategy control and associated separable search path generation through which different ME algorithms and inter coding modes are easily implemented and efficiently executed. The architecture is composed of the three accurately optimized and seamlessly coupled components: a control unit, a memory system, and distortion computation unit.

The results illustrate that the architecture can process real-time (30 fps) single reference frame ME up to 1080p format (1920×1080pixels) with H.261/3, MPEG-1/2, MPEG-4 Visual, and VC-1 standards. When processing CIF, D1, and 1080p formats at 30 fps, the architecture consumes only 22.3 - 25.1 kgates, 20.5 KB of memory with 123×123 pixel search range, and 3 - 184 mW of power with a 0.13-micrometer CMOS standard cell technology. Supporting ME for H.264/AVC 1080p video at 30 fps requires a duplicated architecture whose respective metrics are 49.7 kgates, 41.0 KB of memory, and 364 mW of power. The performance comparison shows that the designed architecture consumes 39 - 89% less logic gates than the existing approaches.

### **Preface**

The research work for this Thesis has been carried out in the Department of Computer Systems at Tampere University of Technology during the years 2003 - 2011.

I would like to express my gratitude to my supervisor Prof. *Timo D. Hämäläinen* for his guidance, motivation, and successful efforts that have made this research work possible. Sincere acknowledgements go also to Prof. *Holger Blume* and Prof. *Janne Heikkilä* for reviewing and providing constructive comments on the manuscript of this Thesis.

I would like to thank all my colleagues for assistance, fruitful discussions, and inspiring atmosphere. I express my special thanks to *Kimmo Kuusilinna*, Dr. Tech., for co-authoring publications and providing thorough guidance especially in the first years of my academic career. In addition, I am deeply grateful to my closest colleague *Eero Aho*, Dr. Tech., who has co-authored publications and given valuable support during these years. Special thanks also to Mr. *Marko Viitanen*, *Olli Lehtoranta*, Dr. Tech., *Antti Rasmus*, M.Sc., *Ari Kulmala*, Dr. Tech, *Juha Pirttimäki*, M.Sc., and *Tero Arpinen*, M.Sc., for their technical and less technical contribution to my research work. In addition, I would like to thank the deceased Mr. *Jussi Uusitalo* whose promising research career was over far too early.

This Thesis was financially supported by Tampere Graduate School in Information Science and Engineering (TISE), Academy of Finland, Nokia Foundation, Emil Aaltonen Foundation, Heikki and Hilma Honkanen Foundation, and HPY foundation. They are all gratefully acknowledged.

Finally, I would like to thank my parents *Riitta* and *Arto* for all their support during my whole life and my parents-in-law *Liisa* and *Erkki* for assistance during busy times. The warmest thanks are dedicated to my wife *Tarja* for her endless love, understanding, and support and my daughter *Nelli* for giving me so much fun and happiness every day. You two are the sunshines of my life.

Kangasala, August 2011

Jarno Vanne

## **Table of Contents**

| A]         | BSTRACT  | · · · · · · · · · · · · · · · · · · ·       | I    |

|------------|----------|---------------------------------------------|------|

| ΡI         | REFACE   |                                             |      |

| T          | ABLE OF  | CONTENTS                                    | V    |

| LI         | ST OF PU | JBLICATIONS                                 | IX   |

| LI         | ST OF FI | GURES                                       | XI   |

| LI         | ST OF TA | ABLES                                       | XIII |

| <b>A</b> ] | BBREVIA  | TIONS                                       | XV   |

| SY         | YMBOLS   |                                             | XXI  |

| 1.         | INTR     | ODUCTION                                    | 1    |

|            | 1.1 O    | DBJECTIVE AND SCOPE OF RESEARCH             | 4    |

|            | 1.2 N    | AAIN CONTRIBUTIONS                          | 4    |

|            | 1.3 S    | SUMMARY OF PUBLICATIONS                     | 6    |

|            | 1.4 O    | OUTLINE OF THESIS                           | 6    |

| 2.         | VIDE     | O ENCODING                                  | 7    |

|            | 2.1 D    | DIGITAL VIDEO                               | 7    |

|            | 2.1.1    | Digitization of natural video               |      |

|            | 2.1.2    | Color spaces                                | 8    |

|            | 2.1.3    | Motivation for video compression            | 9    |

|            | 2.1.4    | Lossless and lossy compression              | 9    |

|            | 2.1.5    | PSNR                                        |      |

|            | 2.2 In   | NTERNATIONAL VIDEO CODING STANDARDS         |      |

|            | 2.2.1    | MPEG-1, MPEG-2, and MPEG-4 Visual           |      |

|            | 2.2.2    | H.261, H.262, and H.263                     |      |

|            | 2.2.3    | H.264/AVC                                   |      |

|            | 2.2.4    | VC-1                                        |      |

|            | 2.2.5    | Future international video coding standards |      |

|            | 2.3 V    | IDEO ENCODER                                |      |

|            | 231      | MCP stage                                   | 14   |

### Table of Contents

|    | 2.3.2 | TC stage                                                    | 15 |

|----|-------|-------------------------------------------------------------|----|

|    | 2.3.3 | EC stage                                                    | 15 |

|    | 2.3.4 | Decoding path                                               | 16 |

|    | 2.3.5 | MB coding modes                                             | 16 |

|    | 2.3.6 | Encoder control                                             | 17 |

|    | 2.4 S | TATE-OF-THE-ART ENCODERS                                    | 17 |

|    | 2.4.1 | H.264/AVC encoders                                          | 17 |

|    | 2.4.2 | Practical implementation constraints                        | 18 |

|    | 2.4.3 | Software implementations                                    | 19 |

|    | 2.4.4 | Hardware/software implementations                           | 20 |

|    | 2.4.5 | Academic hardware implementations                           | 21 |

|    | 2.4.6 | Commercial hardware implementations                         | 23 |

|    | 2.4.7 | Discussion                                                  | 23 |

| 3. | MOT   | ION ESTIMATION                                              | 25 |

|    | 3.1 C | ONCEPT OF MOTION                                            | 25 |

|    | 3.1.1 | True and apparent motion                                    | 25 |

|    | 3.1.2 | Practical usage of apparent motion                          | 26 |

|    | 3.2 N | OTION MODEL FOR MOTION-COMPENSATED PREDICTION               | 26 |

|    | 3.2.1 | Spatially translational and temporally linear motion model  | 27 |

|    | 3.2.2 | Motion modeling, estimation, and compensation               |    |

|    | 3.2.3 | Motion compensated prediction in video encoders             | 29 |

|    | 3.2.4 | Region of support                                           | 30 |

|    | 3.3 B | LOCK-BASED MOTION ESTIMATION AND COMPENSATION               | 31 |

|    | 3.3.1 | Fixed and variable block-size motion estimation             | 32 |

|    | 3.3.2 | Integer and fractional motion estimation                    | 34 |

|    | 3.3.3 | Motion vector coding and prediction                         | 36 |

|    | 3.3.4 | Reference frames in motion estimation                       | 38 |

|    | 3.3.5 | Summary of standard-specific techniques and emerging trends | 40 |

|    | 3.4 B | LOCK MATCHING                                               | 41 |

|    | 3.4.1 | Basic operating principle                                   | 42 |

|    | 3.4.2 | Motion vector prediction for block matching                 | 43 |

|    | 3.4.3 | Matching criteria in block matching                         | 44 |

|    | 3.4.4 | Rate-constrained block matching                             | 46 |

|    | 3.4.5 | Rate-constrained inter mode decision                        | 47 |

| 4. | CONT  | TEMPORARY MOTION ESTIMATION ALGORITHMS AND ARCHITECTURES    | 49 |

|    | 4.1 C | ONTEMPORARY BLOCK MATCHING ALGORITHMS                       | 49 |

|    | 111   | Lossless speed-up techniques                                | 50 |

### Table of Contents

|    | 4.1.2     | Lossy speed-up techniques                                   | 51  |

|----|-----------|-------------------------------------------------------------|-----|

|    | 4.1.3     | Reduction of checking points                                | 52  |

|    | 4.2 E     | XISTING VARIABLE BLOCK-SIZE MOTION ESTIMATION ARCHITECTURES | 55  |

|    | 4.2.1     | FFS -based architectures                                    | 55  |

|    | 4.2.2     | Fast BMA -based architectures                               | 56  |

|    | 4.2.3     | Flexible architectures                                      | 57  |

|    | 4.2.4     | Summary of architectures                                    | 58  |

| 5. | DESIG     | GNED CONFIGURABLE MOTION ESTIMATION ARCHITECTURE            | 59  |

|    | 5.1 P     | ROPOSED MOTION ESTIMATION FRAMEWORK                         | 59  |

|    | 5.1.1     | Rate-constrained motion estimation                          | 59  |

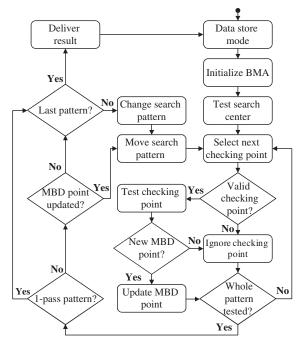

|    | 5.1.2     | Inter mode decision                                         | 63  |

|    | 5.1.3     | Inter mode delivery                                         | 63  |

|    | 5.2 P     | ROPOSED MOTION ESTIMATION IMPLEMENTATION                    | 65  |

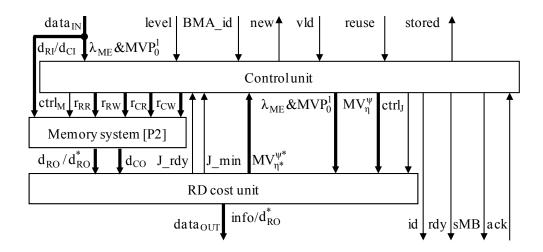

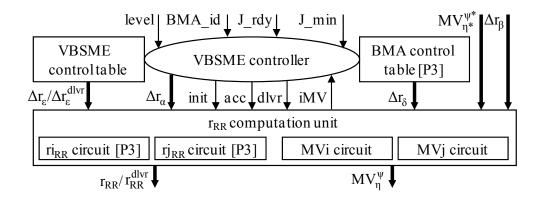

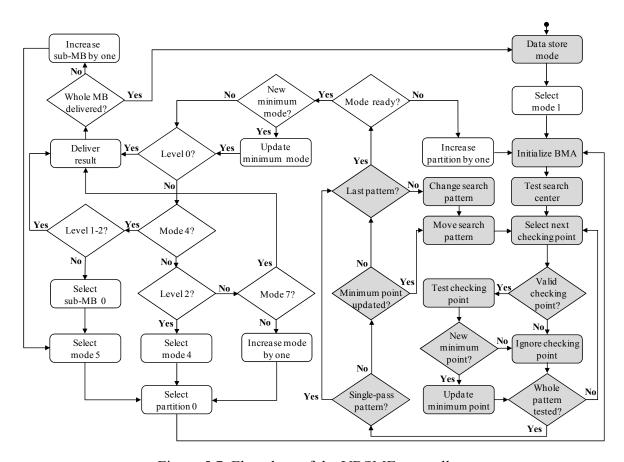

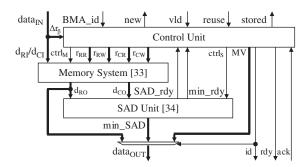

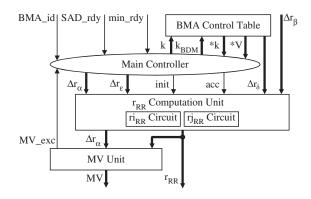

|    | 5.2.1     | Control unit                                                | 67  |

|    | 5.2.2     | Memory system                                               | 70  |

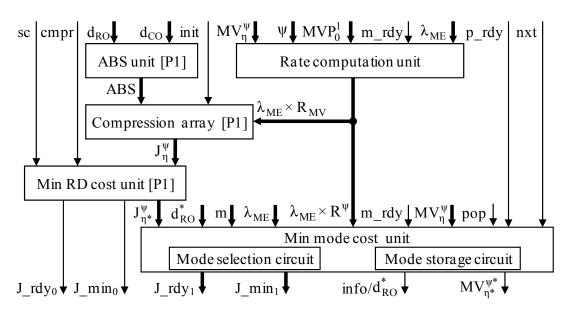

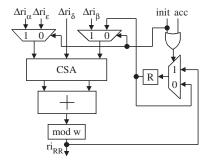

|    | 5.2.3     | RD cost unit                                                | 71  |

|    | 5.3 A     | RCHITECTURE SUMMARY                                         | 74  |

| 6. | PERF      | ORMANCE ANALYSIS                                            | 75  |

|    | 6.1 F     | RAMEWORK EVALUATION                                         | 75  |

|    | 6.1.1     | Rate-Distortion performance analysis                        | 76  |

|    | 6.1.2     | Search speed analysis                                       | 77  |

|    | 6.2 In    | MPLEMENTATION RESULTS                                       | 79  |

|    | 6.3 P     | ERFORMANCE COMPARISON                                       | 81  |

| 7. | CONC      | CLUSIONS                                                    | 83  |

|    | 7.1 M     | IAIN RESULTS                                                | 83  |

|    | 7.2 F     | UTURE WORK                                                  | 84  |

| RI | EFERENC   | ES                                                          | 85  |

| DТ | IDI ICATI | IONIC                                                       | 0.5 |

### **List of Publications**

This Thesis consists of an introductory part and a part containing the following publications. In the text, these publications are referred to as [P1], [P2], and [P3].

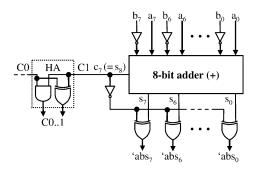

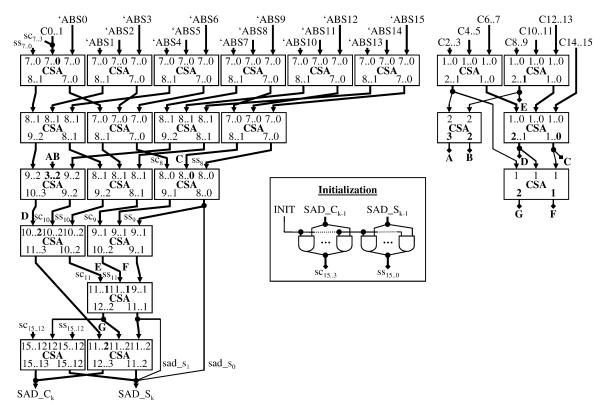

- [P1] J. Vanne, E. Aho, T. D. Hämäläinen, and K. Kuusilinna, "A high-performance sum of absolute difference implementation for motion estimation," *IEEE Trans. Circuits Syst. Video Technol.*, vol. 16, no. 7, Jul. 2006, pp. 876-883.

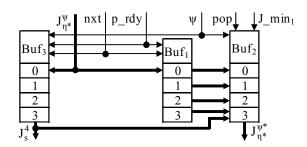

- [P2] J. Vanne, E. Aho, T. D. Hämäläinen, and K. Kuusilinna, "A parallel memory system for variable block-size motion estimation algorithms," *IEEE Trans. Circuits Syst. Video Technol.*, vol. 18, no. 4, Apr. 2008, pp. 538-543.

- [P3] J. Vanne, E. Aho, K. Kuusilinna, and T. D. Hämäläinen, "A configurable motion estimation architecture for block-matching algorithms," *IEEE Trans. Circuits Syst. Video Technol.*, vol. 19, no. 4, Apr. 2009, pp. 466-476.

# **List of Figures**

| Figure 1.1. Consumer IP traffic forecast [22]                                        | 2  |

|--------------------------------------------------------------------------------------|----|

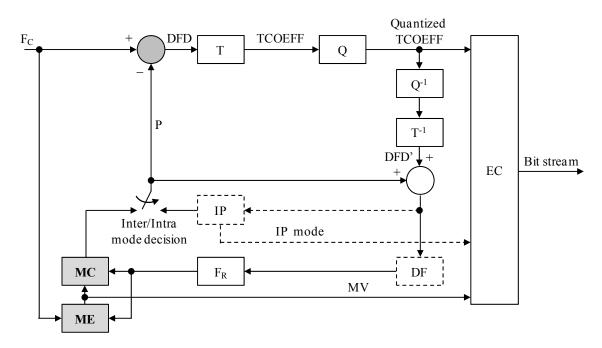

| FIGURE 2.1. GENERALIZED BLOCK DIAGRAM OF THE HYBRID VIDEO ENCODER.                   | 13 |

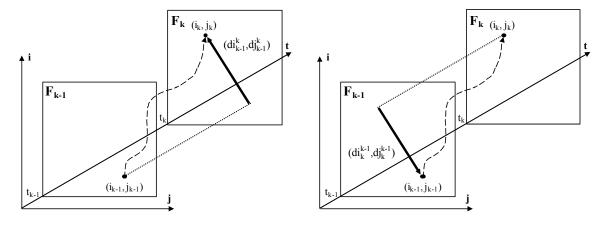

| FIGURE 3.1. A TRAJECTORY OF AN IMAGE POINT AND ASSOCIATED LINEAR DISPLACEMENT VECTOR | 28 |

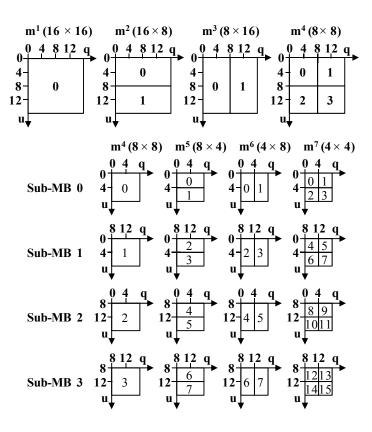

| FIGURE 3.2. SEVEN INTER CODING MODES AND ASSOCIATED MB PARTITIONS.                   | 33 |

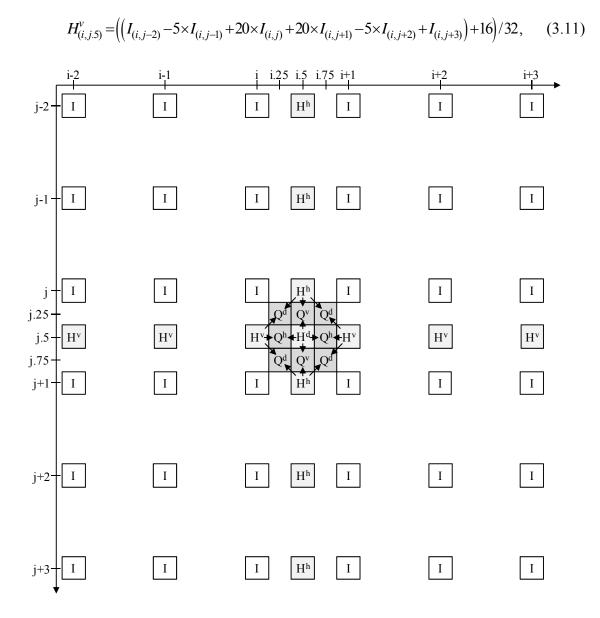

| FIGURE 3.3. INTERPOLATION OF LUMINANCE SAMPLES IN H.264/AVC.                         | 35 |

| FIGURE 3.4. BASIC PRINCIPLE OF THE MOTION VECTOR PREDICTION.                         | 38 |

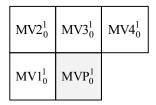

| FIGURE 3.5. MULTIPLE REFERENCE FRAME MOTION ESTIMATION IN H.264/AVC                  | 39 |

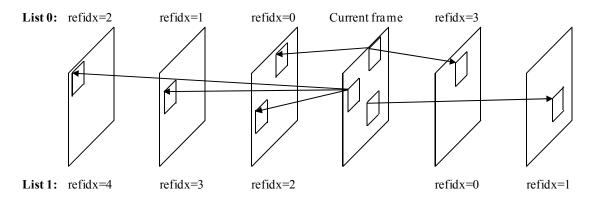

| FIGURE 3.6. BLOCK MATCHING PROCESS.                                                  | 43 |

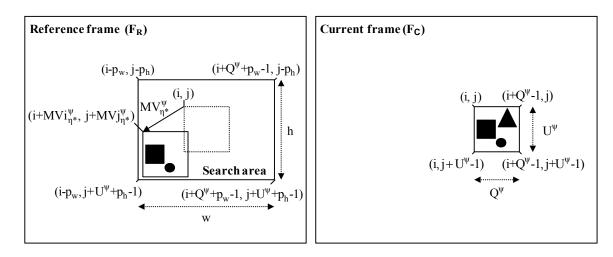

| FIGURE 3.7. EXAMPLE OF THE HARDWARE-ORIENTED MOTION VECTOR PREDICTION.               | 44 |

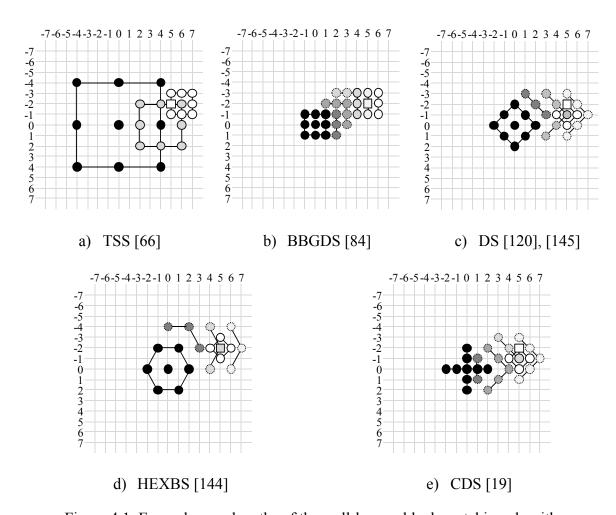

| FIGURE 4.1. EXAMPLE SEARCH PATHS OF THE WELL-KNOWN BLOCK-MATCHING ALGORITHMS         | 54 |

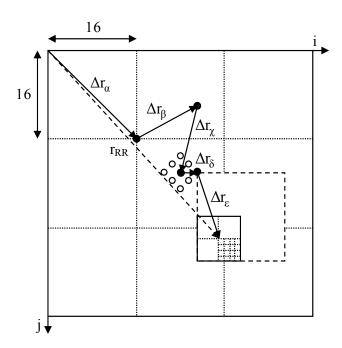

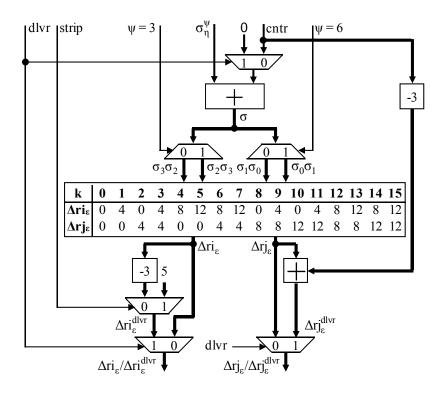

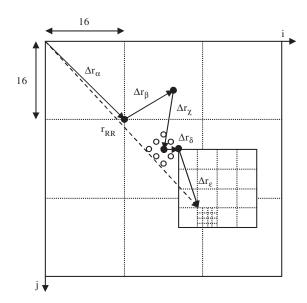

| FIGURE 5.1. PROPOSED SEPARABLE COMPOSITION OF A BLOCK ADDRESS IN THE SEARCH AREA     | 60 |

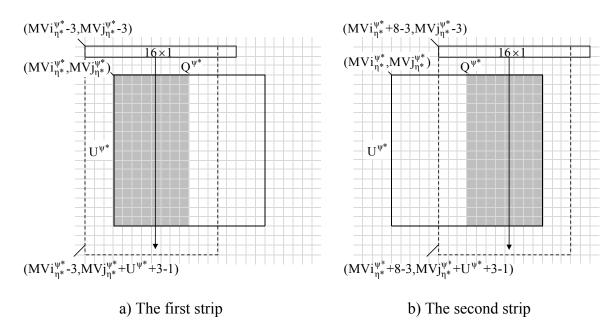

| FIGURE 5.2. SCAN SEQUENCES FOR THE CANDIDATE AND CURRENT MBS.                        | 61 |

| Figure 5.3. Retrieving pixels of a $16 \times 16$ block to FME.                      | 65 |

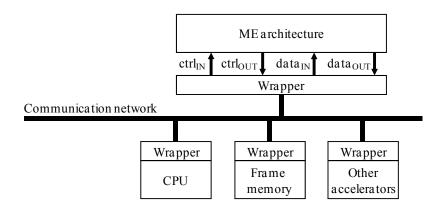

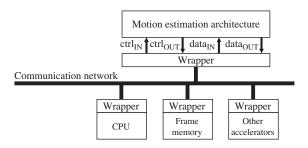

| FIGURE 5.4. AN EXEMPLARY SYSTEM ARCHITECTURE FOR A VIDEO ENCODER.                    | 66 |

| FIGURE 5.5. THE IMPLEMENTED MOTION ESTIMATION ARCHITECTURE.                          |    |

| Figure 5.6. Control unit                                                             | 67 |

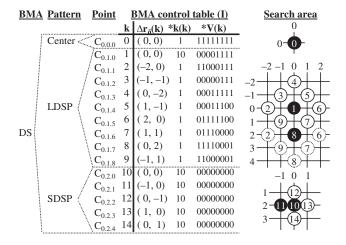

| FIGURE 5.7. FLOWCHART OF THE VBSME CONTROLLER.                                       | 68 |

| FIGURE 5.8. VBSME CONTROL TABLE.                                                     | 69 |

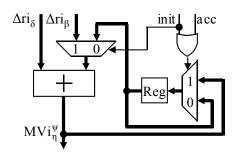

| Figure 5.9. MV <i>i</i> circuit                                                      | 70 |

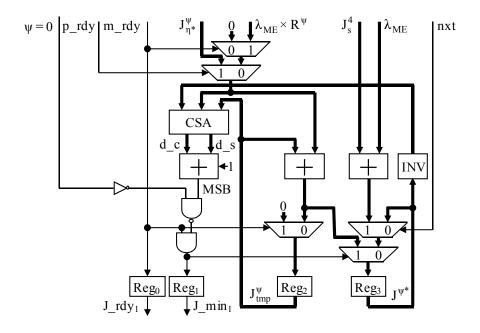

| Figure 5.10. RD cost unit.                                                           | 71 |

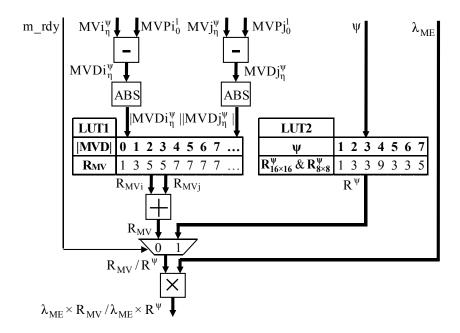

| FIGURE 5.11. RATE COMPUTATION UNIT                                                   | 72 |

| Figure 5.12. Mode selection circuit.                                                 | 73 |

| FIGURE 5.13. STORAGE LOGIC FOR PARTITION COSTS.                                      | 74 |

## **List of Tables**

| TABLE 2.1. ENCODING PERFORMANCE OF THE WELL-KNOWN PROCESSORS                           | 20 |

|----------------------------------------------------------------------------------------|----|

| TABLE 2.2. ENCODING PERFORMANCE OF THE STATE-OF-THE-ART VIDEO-ORIENTED MPSOCS.         | 21 |

| TABLE 2.3. ENCODING PERFORMANCE OF THE STATE-OF-THE-ART ACADEMIC HW ENCODERS           | 23 |

| TABLE 2.4. ENCODING PERFORMANCE OF THE STATE-OF-THE-ART INDUSTRIAL HW ENCODERS         | 24 |

| TABLE 3.1. STANDARD-SPECIFIC KEY CHARACTERISTICS OF MOTION ESTIMATION AND COMPENSATION | 41 |

| TABLE 4.1. CHARACTERISTICS OF CONTEMPORARY MOTION ESTIMATION ARCHITECTURES.            | 58 |

| TABLE 6.1. RD PERFORMANCE COMPARISON OF FAST BMAS AND FS IN JM 17.0                    | 77 |

| TABLE 6.2. SEARCH SPEEDS OF BMAS AND MINIMUM OPERATING FREQUENCIES FOR REAL-TIME IME   | 78 |

| TABLE 6.3. IMPLEMENTATION RESULTS OF THE ARCHITECTURE CONFIGURATIONS.                  | 80 |

| TABLE 6.4. COMPARISON OF THE PROPOSED AND EXISTING STATE-OF-THE-ART ME ARCHITECTURES   | 82 |

### **Abbreviations**

1080p Video format (1920×1080 pixels, progressive scan)

720p Video format (1280×720 pixels, progressive scan)

1D, 2D, 3D One-, Two-, Three-Dimensional 3DTV Three-Dimensional Television

4SS Four-Step Search

ABS Absolute

ADSL Asymmetric Digital Subscriber Line

ALUT Adaptive Look-Up Table of Altera

ARM Advanced RISC Machine

ASIC Application-Specific Integrated Circuit

ASP Advanced Simple Profile of MPEG-4 Visual

AVC Advanced Video Coding

AVS Audio Video coding Standard of China

B Bidirectional prediction

BBGDS Block-Based Gradient Descent Search

BD-PSNR Bjøntegaard Delta Peak Signal-to-Noise Ratio

BD-rate Bjøntegaard Delta bit rate

BMA Block-Matching Algorithm

BP Baseline Profile of H.264/AVC

CABAC Context-Adaptive Binary Arithmetic Coding

CAVLC Context-Adaptive Variable Length Coding

CBEA Cell Broadband Engine Architecture

CD Compact Disc

CDS Cross-Diamond Search

CIF Common Intermediate Format (352 × 288 pixels)

CMOS Complementary Metal Oxide Semiconductor

#### **Abbreviations**

CPU Central Processing Unit

CRT Cathode Ray Tube

CS Cross Search

CSA Carry-Save Adder

CSP Cross-shaped Search Pattern

D1 Video format (720×576 pixels for PAL)

DCT Discrete Cosine Transform

DE Disparity Estimation

DF Deblocking Filter

DFD Displaced Frame Difference

DFD' Reconstructed Displaced Frame Difference

DPB Decoded Picture Buffer

DS Diamond Search

DSP Digital Signal Processor

DVB-C, -S, -T Digital Video Broadcasting, -Cable, -Satellite, -Terrestrial

DVD Digital Versatile Disc

EC Entropy Coding

EPZS Enhanced Predictive Zonal Search

FBSME Fixed Block-Size Motion Estimation

FFS Fast Full-Search

FIR Finite Impulse Response

FME Fractional Motion Estimation

FPGA Field Programmable Gate Array

fps Frames per second

FS Full-Search

FTV Free viewpoint Television

GIPS Giga Instructions Per Second

GFLOPS Giga Floating Point Operations Per Second

GPP General-Purpose Processor

GPU Graphics Processing Unit

H.261, H.262, H.263 Video coding standards issued by ITU-T

H.264/AVC Video coding standard issued by ITU-T and ISO/IEC

HD High Definition

HDTV High-Definition Television

HEVC High Efficiency Video Coding

HEXBS Hexagon-Based Search

HIBI Heterogeneous IP Block Interconnection

HiP High Profile of H.264/AVC

HVS Human Visual System

HW Hardware

I Intra

ICT Integer Cosine Transform

IEC International Electrotechnical Commission

IEEE The Institute of Electrical and Electronics Engineers

IME Integer Motion Estimation

INV Inversion

IP Intra Prediction, also Internet Protocol

IPP Integrated Performance Primitives

IPTV Internet Protocol Television

ISDN Integrated Services Digital Network

ISO International Organization for Standardization

ITRS International Technology Roadmap for Semiconductors

ITU International Telecommunication Union

ITU-T Telecommunication Standardization Sector of ITU

JCT-VC Joint Collaborative Team on Video Coding

JM Joint Model of H.264/AVC

JVT Joint Video Team

LCD Liquid Crystal Display

LDSP Large Diamond Search Pattern

LSB Least Significant Bit

LUT Look-Up Table

MAD Mean Absolute Difference

MAE Mean Absolute Error

MB Macroblock

**MBD** Minimum Block Distortion

MC **Motion Compensation**

**MCP Motion-Compensated Prediction**

ME **Motion Estimation**

**MPEG** Moving Picture Experts Group

Video coding standards issued by ISO/IEC MPEG-1, -2, -4

**MRFME** Multiple Reference Frame Motion Estimation

MP Main Profile of MPEG-2

**MPSoC** Multiprocessor System-on-Chip

**MSB** Most Significant Bit

**MSD** Mean Squared Difference

**MSE** Mean Squared Error

MV Motion Vector

**MVC** Multiview Video Coding, Annex H of H.264/AVC

MVD Motion Vector Difference

MVP Motion Vector Predictor

NoC Network-on-Chip

**NRE** Non-Recurring Engineering

**NTSC** National Television System Committee

P Prediction

P4EE Pentium 4 Extreme Edition

**PAL** Phase Alternate Line PC Personal Computer PE

**PMVFAST** Predictive MV Field Adaptive Search Technique

**Processing Element**

Power Processor Element of CBEA **PPE**

**PSNR** Peak Signal-to-Noise Ratio

Q Quantization

$Q^{-1}$ **Inverse Quantization**

**QCIF** Quarter Common Intermediate Format (176×144 pixels) Quad Full High Definition format (3840×2160 pixels) **QFHD**

QP Quantization Parameter

#### **Abbreviations**

QVGA Quarter Video Graphics Array format (320×240 pixels)

WQHD Wide Quad High Definition format (2560×1440 pixels)

RC Rate Control

RD Rate-Distortion

RDO Rate-Distortion Optimization

RGB Red Green Blue color space

RISC Reduced Instruction Set Computer

RM Reference Model of H.261

ROS Region Of Support

SAD Sum of Absolute Differences

SATD Sum of Absolute Transformed Differences

SAE Sum of Absolute Errors

SD Standard Definition

SDTV Standard-Definition Television

SEA Successive Elimination Algorithm

SECAM Sequential Color with Memory

SIF Source Input Format (352×240 pixels for NTSC)

SIMD Single Instruction Multiple Data

SDSP Small Diamond Search Pattern

SMPTE Society of Motion Picture and Television Engineers

SoC System-on-Chip

SP Simple Profile of MPEG-2 or MPEG-4 Visual

SPE Synergistic Processor Element of CBEA

SRAM Static Random Access Memory

SSD Sum of Squared Differences

SSE Sum of Squared Errors

Sub-QCIF Sub-Quarter Common Intermediate Format (128×96 pixels)

SVC Scalable Video Coding, Annex G of H.264/AVC

SW Software

T Transform

T<sup>-1</sup> Inverse Transform

TC Transform Coding

#### **Abbreviations**

TCOEFF Transform Coefficient

TI Texas Instruments

TM Test Model of MPEG-1/2

TMN Test Model Near-term of H.263

TSS Three-Step Search

TV Television

UHDTV Ultra High Definition Television (7680 × 4320 pixels)

UMHexagonS Unsymmetrical-cross Multi-Hexagon-grid Search

UVLC Universal Variable Length Coding

VBS Variable Block-Size

VBSME Variable Block-Size Motion Estimation

VC-1 Video Codec-1, informal name of the SMPTE 421M video

coding standard

VCD Video Compact Disc

VCEG Video Coding Experts Group

VGA Video Graphics Array format (640×480 pixels)

VHDL VHSIC Hardware Description Language

VHS Video Home System

VHSIC Very High Speed Integrated Circuit

VLC Variable Length Coding

VLSI Very Large Scale Integration

VM Verification Model of MPEG-4 Visual

VoD Video on Demand

WMV-9 Windows Media Video 9 codec

XP Extended Profile of H.264/AVC

YCbCr Luminance, Blue chrominance, Red chrominance color space

YUV Color space

## **Symbols**

| $\Delta r_{\alpha}(\Delta ri_{\alpha}, \Delta rj_{\alpha})$                                          | Initial offset of $r_{RR}$ in the 2D search area memory                                                                                          |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| $\Delta r_{\beta}(\Delta ri_{\beta}, \Delta rj_{\beta})$                                             | Prediction-based offset of $r_{RR}$ in the 2D search area memory                                                                                 |

| $\Delta r_{\delta}(\Delta ri_{\delta}, \Delta rj_{\delta})$                                          | Checking point offset of $r_{RR}$ in the 2D search area memory                                                                                   |

| $\Delta r_{\varepsilon}(\Delta ri_{\varepsilon}, \Delta rj_{\varepsilon})$                           | Base block offset of $r_{RR}$ in the 2D search area memory                                                                                       |

| $\Delta r_{arepsilon}^{ m dlvr}(\Delta r i_{arepsilon}^{ m dlvr}, \Delta r j_{arepsilon}^{ m dlvr})$ | Base block offset of $r_{RR}^{\text{dlvr}}$ in the 2D search area memory                                                                         |

| $\Delta r_{\chi}(\Delta ri_{\chi}, \Delta rj_{\chi})$                                                | BMA movement offset of $r_{RR}$ in the 2D search area memory                                                                                     |

| $\eta$                                                                                               | Index of the partition                                                                                                                           |

| $\eta$ *                                                                                             | Index of the best matching block                                                                                                                 |

| Λ                                                                                                    | Sampling grid (orthogonal lattice)                                                                                                               |

| λ                                                                                                    | Lagrange multiplier                                                                                                                              |

| $\lambda_{	ext{MD}}$                                                                                 | Lagrange multiplier in mode decision                                                                                                             |

| $\lambda_{ m ME}$                                                                                    | Lagrange multiplier in ME                                                                                                                        |

| ho                                                                                                   | Number of the reference frames                                                                                                                   |

| $\sigma$                                                                                             | $4 \times 4$ pixel block index of the MB                                                                                                         |

| $\sigma_{\eta}^{\psi}$                                                                               | The first $4 \times 4$ pixel block index of $p_{\eta}^{\psi}$                                                                                    |

| $\sigma^{\psi^*}_{\eta^*}$                                                                           | The first $4 \times 4$ pixel block index of $p_{\eta^*}^{\psi^*}$                                                                                |

| $\sigma_{_{\chi}}$                                                                                   | Bit $x$ of $\sigma$                                                                                                                              |

| Ψ                                                                                                    | Index of the inter coding mode                                                                                                                   |

| ψ*                                                                                                   | Index of the best $\psi$                                                                                                                         |

| $\psi x$                                                                                             | Index of the inter coding mode in left $(x = 1)$ , top-left $(x = 2)$ , top $(x = 3)$ , and top-right $(x = 4)$ candidate of $MVP_{\eta}^{\psi}$ |

| D                                                                                                    | Distortion between a current $p_{\eta}^{\psi}$ and its reconstruction                                                                            |

| $d_{k-1}^k(di_{k-1}^k,dj_{k-1}^k)$                                                                   | Linear displacement vector in the 2D field (from $F_{k-1}$ to $F_k$ )                                                                            |

|                                                                                                      |                                                                                                                                                  |

| $d_k^{k-1}(di_k^{k-1},dj_k^{k-1})$ | Linear displacement vector in the 2D field (from $F_k$ to $F_{k-1}$ ) |

|------------------------------------|-----------------------------------------------------------------------|

| $d_{CI}$                           | Current frame data (current block memory input data)                  |

| $d_{CO}$                           | Current block data (current block memory output data)                 |

| $d_{RI}$                           | Reference frame data (search area memory input data)                  |

| $d_{RO}$                           | Search area data (search area memory output data)                     |

| $d_{RO}^*$                         | The best matching block (search area memory output data)              |

| $E_k$                              | Error of the pixel(s) predicted for $F_k$                             |

| $F_C$                              | Current frame                                                         |

| $F_k$                              | The <i>k</i> th frame of a video sequence                             |

| $F_R$                              | Reconstructed reference frame(s)                                      |

| h                                  | Height of the search area (in pixels)                                 |

| $H^d$                              | Diagonally interpolated ½-pixel value                                 |

| $H^h$                              | Horizontally interpolated ½-pixel value                               |

| $H^{v}$                            | Vertically interpolated ½-pixel value                                 |

| I                                  | Integer-pixel value                                                   |

| i                                  | Horizontal pixel coordinate of the frame                              |

| $i_k$                              | Horizontal pixel coordinate in $F_k$                                  |

| J                                  | RD optimized cost function                                            |

| $J^{\psi}$                         | RD cost of $m^{\psi}$                                                 |

| $J^{\psi^*}$                       | RD cost of $m^{\nu^*}$                                                |

| $J_{\eta}^{\psi}$                  | RD cost of $p_{\eta}^{\psi}$                                          |

| $J_{\eta^*}^{\psi}$                | RD cost of $p_{\eta^*}^{\psi}$                                        |

| $J_{\eta^*}^{\psi^*}$              | RD cost of $p_{\eta^*}^{\psi^*}$                                      |

| $J^{\psi}_{16	imes16}$             | RD cost of a MB                                                       |

| $J^{\psi}_{8	imes8}$               | RD cost of a sub-MB                                                   |

| $J_{ m tmp}^{\psi}$                | Unfinished $J_{16\times 16}^{\psi}$ or $J_{8\times 8}^{\psi}$ value   |

| j                                  | Vertical pixel coordinate of the frame                                |

| $\dot{J}_k$                        | Vertical pixel coordinate in $F_k$                                    |

| K                                  | Number of the frames in a video sequence                              |

|                                    |                                                                       |

| k                                                                    | Index of a frame in a video sequence                                                                           |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| $L_x$                                                                | Quality level <i>x</i> of the ME architecture                                                                  |

| $L_x^y$                                                              | ME architecture configuration for format $y$ and quality level $x$                                             |

| $L0_x^{y/2}$                                                         | The first instance of the dual-instance $L_x^y$                                                                |

| $L1_x^{y/2}$                                                         | The second instance of the dual-instance $L_x^y$                                                               |

| MV(MVi, MVj)                                                         | MV in 2D $F_k$                                                                                                 |

| $MV^\psi_\eta(MVi^\psi_\eta, MVj^\psi_\eta)$                         | MV of $p_{\eta}^{\psi}$ in the 2D search area (a top-left corner of $p_{\eta}^{\psi}$ )                        |

| $MV^\psi_{\eta^*}(MVi^\psi_{\eta^*},\!MVj^\psi_{\eta^*})$            | MV of $p_{\eta^*}^{\psi}$ in the 2D search area (a top-left corner of $p_{\eta^*}^{\psi}$ )                    |

| $MV^{\psi^*}_{\eta^*}(MVi^{\psi^*}_{\eta^*}, MVj^{\psi^*}_{\eta^*})$ | MV of $p_{\eta^*}^{\psi^*}$ in the 2D search area (a top-left corner of $p_{\eta^*}^{\psi^*}$ )                |

| $\text{MV1}_{\eta x}^{\psi x}$                                       | Left $(x = 1)$ , top-left $(x = 2)$ , top $(x = 3)$ , and top-right $(x = 4)$ candidate of $MVP_{\eta}^{\psi}$ |

| $MVD^\psi_\eta(MVDi^\psi_\eta, MVDj^\psi_\eta)$                      | MVD for $p_{\eta}^{\psi}$ in the 2D search area                                                                |

| $MVP^{\psi}_{\eta}(MVPi^{\psi}_{\eta},MVPj^{\psi}_{\eta})$           | MVP for $p_{\eta}^{\psi}$ in the 2D search area                                                                |

| $m^{\psi}$                                                           | Inter coding mode $\psi$                                                                                       |

| $m^{\psi^*}$                                                         | The best $m^{\psi}$                                                                                            |

| $m^{\psi x}$                                                         | Inter coding mode $\psi x$ in left $(x = 1)$ , top-left $(x = 2)$ , top $(x =$                                 |

|                                                                      | 3), and top-right ( $x = 4$ ) candidate of $MVP_{\eta}^{\psi}$                                                 |

| $n^{\psi}$                                                           | The number of partitions in $m^{\psi}$                                                                         |

| $P_k$                                                                | Predicted pixel(s) for $F_k$                                                                                   |

| $p_{\eta}^{\psi}$                                                    | Partition $\eta$ of $m^{\psi}$                                                                                 |

| $p_{\eta^*}^{\psi}$                                                  | The best matching block for the current $p_{\eta}^{\psi}$                                                      |

| $P_{\eta^*}^{\psi^*}$                                                | Partition $\eta$ of $m^{\psi^*}$                                                                               |

| $p_h$                                                                | Horizontal search range in the positive/negative direction                                                     |

| $p_w$                                                                | Vertical search range in the positive/negative direction                                                       |

| Q                                                                    | Height of the frame (in pixels)                                                                                |

| q                                                                    | Horizontal pixel coordinate of $p_{\eta}^{\psi}$                                                               |

| $Q^{\psi}$ $Q^{\psi^*}$                                              | Height of $p_{\eta}^{\psi}$ (in pixels)                                                                        |

| $Q^{\psi^*}$                                                         | Height of $p_{\eta^*}^{\psi^*}$ (in pixels)                                                                    |

$Q^d$  Diagonally interpolated ¼-pixel value  $Q^h$  Horizontally interpolated ¼-pixel value

$Q^{\nu}$  Vertically interpolated  $\frac{1}{4}$ -pixel value

R Bit count of the encoded prediction error

$R^{\psi}$   $R^{\psi}_{16\times 16}$  or  $R^{\psi}_{8\times 8}$

$R_{16\times16}^{\psi}$  Bit count of the MB header

$R_{8\times8}^{\psi}$  Bit count of the sub-MB header

$r_{CR}(ri_{CR}, rj_{CR})$  Scanning point to read  $d_{CO}$  from the 2D current block

memory

$r_{CW}(ri_{CW}, rj_{CW})$  Scanning point to write  $d_{CI}$  into the 2D current block memory

$R_{\text{MV}}(R_{\text{MV}i}, R_{\text{MV}j})$  Bit count of the MVD<sub>n</sub><sup>\(\nu\)</sup>

$r_{RR}(ri_{RR}, rj_{RR})$  Scanning point to read  $d_{RO}$  from the 2D search area memory

$r_{RR}^{\text{dlvr}}(ri_{RR}^{\text{dlvr}},rj_{RR}^{\text{dlvr}})$  Scanning point to read  $d_{RO}^*$  from the 2D search area memory

$r_{RW}(ri_{RW}, rj_{RW})$  Scanning point to write  $d_{RI}$  into the 2D search area memory

s Index of the sub-MB

$t_k$  Discrete time instant k

U Width of the frame (in pixels)

$U^{\psi}$  Width of  $p_{\eta}^{\psi}$  (in pixels)

$U^{\psi^*}$  Width of  $p_{\eta^*}^{\psi^*}$  (in pixels)

*u* Vertical pixel coordinate of  $p_n^{\psi}$

w Width of the search area (in pixels)

### 1. Introduction

The evolution of digital technology has made possible to process, transmit, and store video in a digital form. In the past two decades, *digital video* has penetrated a wide range of industries, especially in the area of entertainment, communications, and broadcasting. The widespread applications of digital video include products in consumer electronics, digital cinema, video on demand (VoD), video conferencing, digital television, and surveillance. These products and services have huge revenue potential since the amount of end users increases continuously. Currently, online video communities have reached over one billion users [22] who, among others, watch two billion Youtube videos daily [139]. In addition, the shortened product life cycle drives consumers and companies to replace their obsolete digital products with newer ones. For example, feature phones are often replaced with smartphones that are forecast to be sold 2.5 billion units during the years 2010 - 2015 with the annual growth rate of 24% [24]. To ensure continuous growth in the long term, digital video industry invests a lot in the research and development of video technology.

In the video applications, the vast amount of video data is the major challenge for efficient video storage and communication. Therefore, *digital video compression* (*video coding*) has been actively developed by researches, companies, and standard bodies since the 1980s [54]. The purpose of video compression is to represent a digital video with reduced amount of data but still with acceptable visual quality.

Video compression involves two processes: a *video encoder* encodes (compresses) the original video material for storage and transmission after which the encoded video is decoded (decompressed) by a *video decoder* back to the displayable video before playback and editing. In *two-way applications* such as video communication, both ends of the system encode and decode videos. Instead, in *one-way applications* such as broadcast and streaming, only one end encodes and the other end decodes videos. International standardization work ensures that these applications can interoperate between different platforms, storage devices, and communication networks. The well-known *video coding standards* include former H.261 [55], MPEG-1 [49], MPEG-2 [50], H.263 [56], and MPEG-4 Visual [51] as well as state-of-the-art H.264/AVC [57] and VC-1 [109].

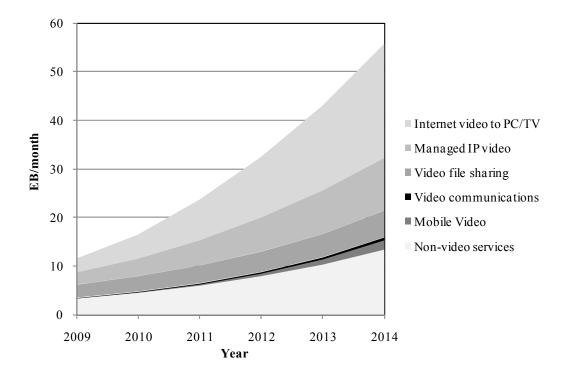

Video compression makes digital video practical in the current communication networks and storage devices that have to cope with steadily increasing volume of digital material. According to Cisco [22], *global IP (Internet Protocol) traffic* was 14.7 exabytes (14.7×10<sup>18</sup> bytes) per month (EB/month) in 2009 and it is estimated to reach 63.9 EB/month in 2014 with the annual growth rate of 34%. The majority of the global IP traffic is and will be consumer video data that is produced by households, university populations, and Internet cafes. Figure 1.1 depicts a global consumer traffic forecast and portions of the popular video services. The forecast assumes that 7% annual gain will be attained in video compression.

Figure 1.1. Consumer IP traffic forecast [22].

In 2014, the overall *consumer video traffic* will be over five times higher that it was in 2009. Actually, it will be over 3.5 times the whole *consumer IP traffic* in 2009. The largest traffic type, *Internet video to PC/TV*, includes all free TV, pay TV, and VoD data delivered via Internet to PC or TV. It will increase eightfold from 2009 to 2014. *Managed IP video* represents traffic generated under control of TV service providers (IPTV and cable TV). The amount of managed IP video data will quadruple from 2009 to 2014. Traffic caused by the exchange of video files is covered by *video file sharing*, whose amount will almost triple during the examined period. It is estimated that video file sharing accounts for 70 - 80% of the whole file sharing traffic. The smallest fraction is *video communications* which includes services like Internet video calling, video monitoring, and webcams. It will increase sevenfold from 2009 to 2014. Due to popularization of smartphones and other portables, *mobile video* traffic will be 70 times higher and it will account for almost 66% of the overall mobile data traffic by 2014 [23]. In 2014, the portion of *non-video traffic* (web browsing, email, instant messaging, file transfer, Internet gaming, etc.) will be below 20%.

There are several drivers for the growth of digital video material. Firstly, digital video capture and playback are nowadays standard features in numerous personal and professional electronic products. The price erosion has and will accelerate sales of these products. Secondly, the expansion of digital screens together with user demand for better quality drive video resolutions to grow from *standard definition* (*SD*) to *high definition* (*HD*) and beyond. Finally, the proliferation of *3D applications* such as 3DTV will further augment the amount of video data since several video signals are needed per a single 3D video sequence. Compared to 2009, HD and 3D traffic are assumed to be 23-fold in 2014 [22].

Advances of the underlying transmission, storage, and processing technologies ease proliferation of high-resolution video content. For example, the global average broadband speed is assumed to quadruple from 2009 to 2014 [22] and the similar growth rate is expected in the amount of logic and main memory of the portable devices [48]. Since advances in technology cannot completely compensate the explosion of video traffic, efficient *video coding algorithms* have been and will be needed [34], [92]. For example, H.264/AVC and VC-1 have made high quality video services possible. However, the new algorithms typically improve coding efficiency at a cost of higher computational complexity.

Real-time video coding is extremely sensitive to complexity increase, since the processing result has to appear without user-perceivable delay once the input becomes available [6], [64]. The importance of real-time video coding will emphasize in the future [22] and the modern devices are expected to be compatible with plethora of video coding standards. These two requirements are particularly challenging for portable devices which also have to satisfy strict constraints on cost, size, and power consumption.

A standard-compliant video encoder is usually about 5 - 10 times more complex than a respective video decoder and the complexity ratio can grow up to two orders of magnitude if all encoder options are applied [68], [96]. The encoder/decoder complexity ratio has significantly augmented with state-of-the-art standards. For example, H.264/AVC encoder is at least ten times more complex than MPEG-4 Visual encoder, but respective decoder complexity has increased only by a factor of two [96]. The encoder/decoder complexity gap is mainly caused by a single encoder tool: block-based *motion estimation (ME)*. ME is only included in the encoder and its complexity accounts for 50 - 90% of the total encoder complexity [11], [44], [68]. Hence, ME is the main challenge for implementing real-time encoding with low cost and low power consumption.

The video encoder utilizes ME in *motion compensated prediction (MCP)* to reduce temporal redundancy of video sequences. MCP has been included in all international video coding standards. However, ME is excluded from these standards, so it is open for competition. Due to its extensive complexity and importance in video encoding, hundreds of *architectures* and *algorithms* have been proposed for ME since its introduction in 1981 [58].

Majority of the *real-time ME architecture* proposals have been implemented in *hardware* (*HW*) instead of more flexible *software* (*SW*) in order to meet real-time requirements in allowed power budget [6], [11], [68]. Introduced ME algorithms have mainly concentrated on speeding-up the original *exhaustive ME algorithm*, whose estimation strategy produces excellent compression performance but at a cost of intensive computation [42], [68]. With a specific motion content (low, medium, or high) and resolution, single *fast ME algorithms* have proved to be competitive with the original exhaustive ME. However, their compression efficiency decreases more clearly below the exhaustive ME when diverse motion contents and resolutions are processed [41]. In addition, most of the fast ME algorithms have been considered to complicate HW implementation.

### 1.1 Objective and scope of research

The scope of this Thesis is on MCP in video encoding. The coding tools and options of MCP are examined in the context of the following underlying video coding standards: H.261/3, MPEG-1/2, MPEG-4 Visual, H.264/AVC, and VC-1. The emphasis is on state-of-the-art standards, especially in H.264/AVC. Among the coding tools of MCP, this Thesis primarily focuses on *integer ME (IME)* and its practical HW implementation in portable devices. The proposed techniques are particularly designed for progressively scanned natural videos.

The problem addressed in this Thesis is how to overcome the computational complexity of ME. Most of the contemporary ME architectures are tailored to the exhaustive ME algorithm whose inherent complexity requires lots of HW resources. On the other hand, fast ME algorithms are typically implemented with dedicated *algorithm-specific architectures*, whose compression performance is vulnerable to variation of video resolutions and contents.

The objective of this Thesis is to illustrate that the best trade-off between HW complexity and ME compression performance is reached with a *configurable ME architecture* that can adaptively select the most appropriate fast ME algorithm at run time. Another goal is to ensure that the same architecture can be applied to all well-known video coding standards without noticeable overheads. In the literature, a couple of configurable HW approaches have been presented before, but they contain standard-specific limitations. In addition, their flexibility is realized at a cost of large silicon area, limited processing speed, unsustainable power budget, or over restricted ME parameters.

The main claim of this Thesis is that a single configurable HW architecture is able to support multiple video coding standards and various fast ME algorithms at adequate processing speed, low cost, and acceptable power consumption. The claim is proved by the presented configurable ME architecture that overcomes all the critical limitations of the existing flexible ME architectures.

#### 1.2 Main contributions

The main contribution of this Thesis is the design and implementation of configurable ME architecture for video encoding. The architecture can be divided into three main components: a *control unit*, a *memory system*, and a *distortion computation unit*. In summary, the most significant contributions are:

1. The overall ME architecture that performs *rate-constrained IME* with fast ME algorithms such as BBGDS, CDS, DS, HEXBS, and TSS. The architecture is configurable to different ME algorithms and *inter coding modes* at run time. It achieves low area cost by reusing the HW as much as possible. It also reduces the complexity of the subsequent *fractional ME (FME)* by conducting *inter mode decision* jointly with IME. To the best of Author's knowledge, the designed HW architecture is the first one that supports fast rate-constrained IME algorithms and

- is compatible with all inter coding modes of H.261/3, MPEG-1/2, MPEG-4 Visual, H.264/AVC, and VC-1 standards.

- 2. The *ME framework* behind the joint rate-constrained IME and inter mode decision. The framework replaces fixed search strategies of the individual ME algorithms with a single *generic search strategy* that is parametrizable to algorithm-specific coding modes, search centers, and search patterns. The parametrizable search strategy is realized by composing the search paths of the algorithms from five mutually independent offsets so that each offset is a function of the associated parameter(s). The *separable search path generation* provides easy access to individual algorithm-specific parameters which can be modified without changing other features of the algorithm. In addition, the control and computation of each offset can be modularly designed and optimized. All the coding modes of the algorithm undergo similarly parameterized search. The mode decision monitors the serially executed coding modes and selects the best one.

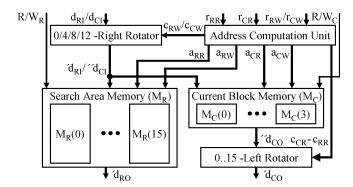

- 3. The control unit of the ME architecture. The unit implements control for the ME framework. A chosen framework configuration determines ME algorithms available at run-time and reparametrization of the framework can be done at design-time. The execution time of each ME algorithm is almost directly proportional to the number of tested search points, so the implementation is very tolerant of different algorithm-specific search strategies.

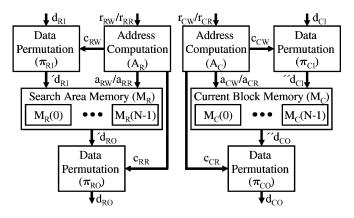

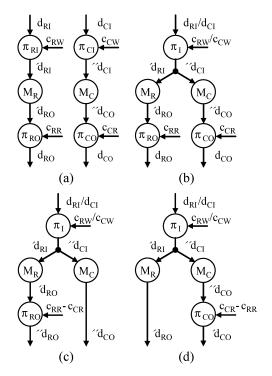

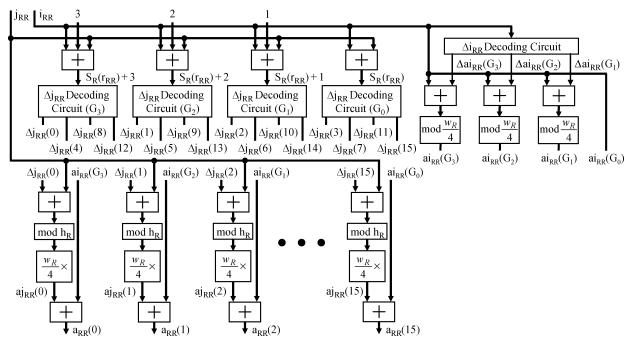

- 4. The memory system of the ME architecture. It includes a novel combination of two *parallel memory architectures*, in which the distribution of data among the memory modules is improved over contemporary approaches. In addition, memory address generation and data permutation scheme are optimized for ME. The memory system provides efficient data storage and supports arbitrary memory accesses needed by fast ME algorithms.

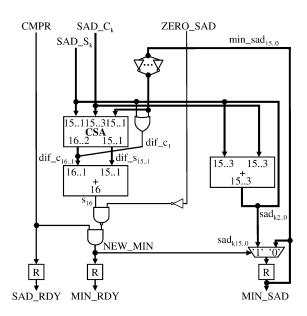

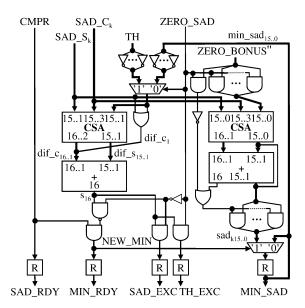

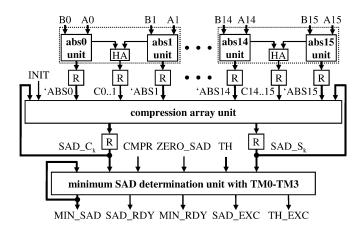

- 5. The distortion computation unit of the ME architecture. The unit implements a HW-oriented *rate-distortion* (*RD*) *cost function*. It contains several new algorithm-level and circuit-level optimizations for RD cost computation and minimum RD cost selection. The optimizations of RD cost function are primarily focused on *sum of absolute difference* (*SAD*) computation.

Besides the designed ME architecture, the contributions of this Thesis include:

- 6. A survey of existing real-time H.264/AVC video encoders.

- 7. An overview and feasibility evaluation of the essential coding tools in MCP.

- 8. A survey of ME algorithms and state-of-the-art ME architectures.

- 9. Performance comparison between several ME algorithms and architectures.

### 1.3 Summary of publications

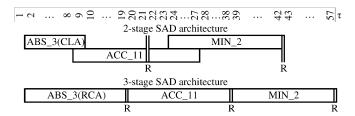

The distortion computation unit, the memory system, and the control unit of the ME architecture have originally been introduced in the included publications [P1], [P2], and [P3], respectively.

The Author acted as the first author and the main contributor in [P1]-[P3]. Eero Aho, Dr. Tech., provided valuable criticism and comments according to which [P1]-[P3] were improved. Prof. Timo D. Hämäläinen and Kimmo Kuusilinna, Dr. Tech, assisted in writing and supervised the research work.

#### 1.4 Outline of Thesis

The introductory part of this Thesis is organized as follows.

Chapter 2 introduces the basic concepts of digital video encoding and analyzes state-of-the-art video encoders. Besides providing the relevant background information for this Thesis, the need for HW-accelerated video encoding and ME is justified.

Chapter 3 considers fundamentals of MCP in which the main focus is on ME. Relying on the experiments in the literature, it is shown that many ME parameters can be simplified or completely excluded without compromising compression performance.

Chapter 4 surveys contemporary ME algorithms and architectures. Related works on distinct components of the ME architecture are presented in [P1]-[P3].

Chapter 5 provides an overview of the designed ME architecture whose components are more thoroughly considered in [P1]-[P3]. In addition, new architecture features introduced after publishing [P1]-[P3] are considered in detail.

Chapter 6 presents performance comparisons between the proposed and contemporary ME architectures. The component-specific performance comparisons are available in [P1]-[P3].

Chapter 7 concludes the introductory part of Thesis.

### 2. Video Encoding

This chapter presents the basic principles of digital video representation and video encoding. In addition, a brief overview is given about international video coding standards and associated video encoders. Finally, state-of-the-art encoders and their implementations in the current platforms are analyzed.

### 2.1 Digital video

Digital video represents a visual scene in a binary format in which intensities and colors of the scene are specified with strings of bits (logical 0s and 1s). The visual scene describes a real world, an imaginary world, or a hybrid of them. The real world visual information is obtained from natural video material whereas the imaginary world represents computergenerated visual scenes or objects (synthetic video). This Thesis focuses on natural video.

### 2.1.1 Digitization of natural video

Current digital video cameras capture natural video scenes via image sensors that convert the arriving light into *spatially* and *temporally* continuous analog video signals. *Digitization* of these signals is accomplished by sampling them in spatial and temporal domains and quantizing the obtained continuous-valued samples to a discrete range of intensities and colors.

The produced spatio-temporal samples are referred to as *picture elements*, *pels*, or *pixels*. The simultaneously sampled pixels reconstruct a two-dimensional (2D) digital *still image*, whose maximum resolution is determined by the sampling grid. Limited *spatial resolution* may cause *spatial aliasing*, i.e., details of the original scene are missing or they are incorrectly represented in the reconstructed image. To avoid spatial aliasing, the well-known Nyquist sampling theorem states that the sampling grid in horizontal and vertical directions has to be two times denser than the upper frequency bound in the respective directions. The current consumer applications typically utilize resolutions from Sub-QCIF (128×96 pixels) up to high-definition television (HDTV) formats such as 1080p (1920×1080 pixels). In the future, the resolutions will evolve towards WQHD (2560×1440 pixels) and QFHD (3840×2160 pixels) formats and even up to UHDTV (7680×4320 pixels) format. This Thesis mainly considers QCIF (176×144 pixels), CIF (352×288 pixels), D1 (720×576 pixels), 720p (1280×720 pixels), and 1080p formats that are the current mainstream.

Digital video can be seen as a sequence of still images (frames) which are displayed at a certain frame rate. A temporal sampling rate (temporal resolution) determines the

maximum frame rate. The sampling rate below the Nyquist criterion causes *temporal aliasing*. I.e., motion may seem jerky and unnatural if the frame rate is too low with respect to object motion. Applications of low data rate typically use 10 - 20 *frames per second* (fps), standard-definition TV (SDTV) supports 25 - 30 fps, and high-end applications require up to 50 - 60 fps. Humans perceive continuous motion if screen updates occur at 30 fps [64], so 30 fps is often considered as a minimum frame rate for real-time video. The *refresh rate* at which a display device redraws images in a second is typically higher (e.g., 50 Hz, 60 Hz, 100 Hz, or 200 Hz) than a frame rate since the human eye detects flicker if the refresh rate is below 50 Hz [6]. The frame rate is accommodated to refresh rate by repeating the same frame multiple times.

The displays utilize *progressive scan* or *interlaced scan*. The progressive scan traces all the lines of the frame simultaneously. The interlaced scan halves the data rate by displaying odd- and even-numbered lines of frames (*fields*) alternately. Hence, the field rate can be doubled over frame rate without bandwidth increase, so that flicker effect is removed. However, interlacing introduces artifacts such as interline twitter, i.e., an aliasing effect perceived as a scintillation or rapid up-and-down motion. Traditional cathode ray tube (CRT) TV displays and all three SDTV standards (NTSC, PAL, and SECAM) are interlaced. However, HDTV formats such as 720p and 1080p as well as modern displays, e.g., plasma and LCD displays, are progressive. Currently, the progressive scan is dominating technique since it doubles the resolution with the same frame rate and avoids interlace artifacts. This Thesis concentrates on progressively scanned video sequences whose frame rates are 25 - 30 fps.

#### 2.1.2 Color spaces

The *color space* of digital video determines how the brightness (*luminance*) and color are described. The *RGB color space* is suitable for video capture and display, whereas *YCbCr* (*YUV*) [52] *color space* is better suited for storage and transmission. In the RGB space, colors are created by combining red (*R*), Green (*G*), and Blue (*B*) in varying proportions. The YCbCr space separates the luminance (*Y*) from the color information, where *Cb* and *Cr* represent color difference (*chrominance*) components. If the YCbCr color space has the same resolution for *Y*, *Cb*, and *Cr* components, the associated sampling pattern is referred to as 4:4:4. However, *Cb* and *Cr* components are typically represented with lower resolution than *Y*, since the *human visual system* (*HVS*) is more sensitive to luminance than color. A 4:2:2 sampling pattern halves the horizontal resolution of *Cb* and *Cr*, whereas a 4:2:0 pattern reduces the resolution of *Cb* and *Cr* to one fourth (halves horizontal and vertical resolution) without essentially sacrificing visual quality.

This Thesis considers designs that operate only on brightness information, so they are independent on the selected color sampling pattern. I.e., pixels are assumed to contain only the *Y* component of the *YCbCr* color space. In typical consumer applications, the used bit depth for pixels (*Y* component only) is 8 bits which equals 256 (0 - 255) different intensity levels from black (weakest) to white (strongest).

#### 2.1.3 Motivation for video compression

A raw (uncompressed) video requires impractical high transfer capacity. For example, a raw bit rate for QCIF format (frame rate: 30 fps, bit depth: 8, sampling pattern: 4:4:4) is  $30 \times (176 \times 144) \times 8 \times 3 = 17.4$  megabits per second (Mbit/s). The respective bit rates for CIF, D1, and 1080p formats are 69.6 Mbit/s, 285 Mbit/s, and 1.39 Gbit/s. At the current technology [108], it would be impossible to deliver raw 1080p real time video over any of the normal Internet Protocol TV (IPTV), cable (DVB-C), satellite (DVB-S), or terrestrial (DVB-T) TV networks. For example, ADSL2+ [53] has a maximum downstream bandwidth of 24 Mbit/s, so it could theoretically be able to transmit a single QCIF stream in real time, whereas 1080p would require 60 times more bandwidth. The bandwidth problem is emphasized with wireless networks [61].

Another obstacle is insufficient capacities of storage devices. For example, the storage requirement of one hour raw QCIF format is  $3600 \, s \times 17.4 \, \text{Mbit/s} = 7.6 \, \text{GB}$  and the respective values for CIF, D1, and 1080p are 31 GB, 125 GB, and 626 GB. A typical single-layer Digital Versatile Disc (DVD) having a capacity of 4.7 GB would be sufficient for less than 3 minutes of D1 format instead of a whole movie. On the other hand, a two hour movie in 1080p format would need 25 dual-layered Blu-ray discs.

Although the price per transmitted or stored bit is continually falling, the capacities of communication networks and storage devices are growing much more slowly than the amount of produced video material. Therefore, video compression will also play a significant role in the future [34], [92], [132].

#### 2.1.4 Lossless and lossy compression

Video compression is performed by a *video codec* that contains a complementary pair of systems: a *video encoder* and a *video decoder*. This Thesis focuses on the encoder.

The objective of the encoder is to achieve high *compression ratio* with minimum visual quality degradation. It uses different video coding algorithms to detect and remove *statistical*, *spatial*, and *temporal* redundancies inherent in video [104]. The statistical redundancy can be efficiently compressed with *lossless* (reversible) compression methods but the compression ratios are only about 3:1 or 4:1 in the best case [104]. *Lossy* (irreversible) compression methods remove perceptually irrelevant parts from the video. In a normal video sequence, removable temporal and spatial redundancies occur between adjacent frames and adjacent pixels, respectively. The stronger the compression, the more original information is lost. Typical lossy compression ratios are from 50:1 to 200:1 and even above [67]. The inverse of compression ratio is called *coding efficiency*, i.e., the degree to which the encoder reduces the bit rate. The encoder is typically evaluated with *rate-distortion* (*RD*) performance that describes a trade-off between the coding efficiency (bit rate) and loss of information (distortion).

#### 2.1.5 PSNR

The distortion is typically measured by computing *Peak Signal to Noise Ratio (PSNR)* between original video sequence and its reconstruction after compression. PSNR between original 8-bit luminance frame  $(F_C)$  and its reconstruction  $(F_R)$  is computed as

$$PSNR(F_C, F_R) = 10 \times \log_{10} \left( \frac{255^2}{MSE(F_C, F_R)} \right).$$

(2.1)

In (2.1), the square of the maximum available 8-bit brightness value is divided by the mean square error (MSE) between  $F_C$  and  $F_R$ . For  $F_C$  and  $F_R$  of size  $Q \times U$  pixels, MSE is defined as

$$MSE(F_C, F_R) = \frac{1}{(Q-1)\times(U-1)} \sum_{i=0}^{Q-1} \sum_{j=0}^{U-1} (F_C(i,j) - F_R(i,j))^2, \qquad (2.2)$$

where  $F_C(i, j)$  and  $F_R(i, j)$  indicate individual pixels of  $F_C$  and  $F_R$ , respectively. In practice, PSNR between original and reconstructed sequences is measured by computing PSNR separately for each frame and taking the arithmetic mean of the frame-specific PSNRs.

PSNR is an *objective* mathematical measure, which produces results independent of viewers' opinions, viewing conditions (viewing distance, illumination, etc.), and display technologies. However, MSE used in PSNR is sensitive to the energy of errors instead of structural image distortions, so PSNR does not necessarily correlate with *subjective* video quality perceived by HVS. It is roughly approximated in [74], that 40 dB, 33 dB, and 30 dB are minimum PSNR values for high, good, and adequate video qualities, respectively.

The most reliable measure for visual quality would require subjective assessments with large number of human observers, but subjective tests are cumbersome, expensive, and time-consuming to organize. Therefore, developers typically rely on automatic and repeatable objective quality measures of which PSNR is by far the most widely used technique. PSNR is also used in this Thesis. As suggested in [2], RD performance of the encoders is compared either as Bjøntegaard delta PSNR (BD-PSNR) for the same output bit rate or, alternatively, Bjøntegaard delta bit rate (BD-rate) for the same PSNR.

Besides high RD performance, the encoder has to produce a decoder-compatible bit stream that is often determined by some video coding standard. This Thesis considers only widespread *international video coding standards* and omits proprietary compression schemes (e.g., Sorenson Video 3), nonstandard open codecs (e.g., VP8), as well as national standards (e.g., AVS China [10]).

# 2.2 International video coding standards

The international standardization work on video coding is mainly coordinated by ISO/IEC Moving Picture Experts Group (MPEG), ITU-T Video Coding Experts Group (VCEG), and Society of Motion Picture and Television Engineers (SMPTE).

### 2.2.1 MPEG-1, MPEG-2, and MPEG-4 Visual

The widely used MPEG standards for audio/video coding are *MPEG-1* [49], *MPEG-2* [50], and *MPEG-4 Visual* (*Part 2*) [51]. MPEG-1 is optimized to VHS-quality video at bit rate of 1.5 Mbit/s. Its applications include Video Compact Disc (VCD).

As an extension to MPEG-1, MPEG-2 is targeted to compress higher quality video at bit rates of 2 - 100 Mbit/s. The main feature distinguishing MPEG-2 from MPEG-1 is the efficient coding of interlaced videos. MPEG-2 is a commonly used compression scheme in DVD as well as in DVB-C, DVB-S, and DVB-T broadcasting standards. It is capable of coding SDTV and HDTV at bit rates of 3.5 Mbit/s and 15 Mbit/s, respectively [39]. MPEG-2 classifies the group of application specific features into *profiles* (subsets) which specify a set of coding tools that can be used to generate a bit stream. The most widely used profiles are *simple profile* (SP) and main profile (MP) which are targeted for low delay and high quality applications, respectively.

MPEG-4 Visual achieves 20 - 30% BD-rate savings over MPEG-2 [133]. The target bit rates of MPEG-4 Visual are 5 - 64 kbit/s in mobile applications, but it is able to support bit rates of about 1 Gbit/s in studio editing resolutions (4K × 4K pixels). Its most popular profiles are SP and ASP (Advanced Simple Profile). Nowadays, MPEG-4 SP is widely supported feature in Internet-based videos and mobile applications [6], whereas MPEG-4 ASP is used in surveillance cameras and other higher quality video systems. Besides coding rectangular frames, MPEG-4 Visual also supports object-based coding that enables access and manipulation of individual objects in a video scene. At least so far, the object-based coding has been impractical solution due its huge complexity.

### 2.2.2 H.261, H.262, and H.263

The ITU-T standards *H.261*, *H.262*, and *H.263* are primarily developed for video communication over telecommunication and computer networks. They share many identical features with MPEG standards.

H.261 is targeted for videophone and video conferencing over Integrated Services Digital Network (ISDN). It was designed to support target bit rates of multiples of 64 kbit/s (64 - 1920 kbit/s). H.262 is omitted here, because its functionality is equivalent to MPEG-2. H.263 was primarily developed to support low bandwidth applications on telephony and data networks. Although its target bit rate is below 30 kbit/s, it also offers good performance at higher bit rates (up to 16 Mbit/s).

### 2.2.3 H.264/AVC

The latest video coding standard of ISO and ITU-T is entitled as *H.264/AVC* (*Advanced Video Coding*) [57] and it is published jointly by MPEG (*MPEG-4 Part 10*) and VCEG (H.264). Contrary to MPEG-4 Visual, H.264/AVC omits the complex object-based coding and focuses only on traditional coding of rectangular frames. It supports bit rates from 5 kbit/s to 960 Mbit/s. The most popular profiles of H.264/AVC are *Baseline Profile* (*BP*), *High Profile* (*HiP*), and *Extended Profile* (*XP*). BP is widely used in videoconferencing

and mobile applications, HiP is targeted for broadcast and disc storage applications, and XP is intended for streaming and error prone environments such as wireless networks.

H.264/AVC achieves about 50 - 60% BD-rate reduction over MPEG-2, whereas the BD-rate decrease over MPEG-4 Visual and H.263 is at least 30% [133]. Due to its high compression and error resilience capabilities, H.264/AVC has become a widely deployed coding technique in various products and services such as Blu-ray Disc, YouTube videos, Adobe Flash, and DVB standards. For example, H.264/AVC is able to code SDTV and HDTV at bit rates of 2 - 3.2 Mbit/s and 7.5 - 13 Mbit/s, respectively [39].

H.264/AVC has been recently extended by two amendments that consider *scalable video coding (SVC)* and *multiview video coding (MVC)* [57]. SVC provides a compressed video with two or more quality options (spatial resolution, temporal resolution, and fidelity) from which the most suitable one is selected according to available transmission, display, or storage capability. MVC, in turn, operates on multiview video that is captured by synchronized cameras from different viewpoints. Multiview video provides three-dimensional (3D) depth impression of the observed scenery. It is utilized by emerging 3D applications such as *3DTV* and *free viewpoint TV (FTV)* [116] in which the user can control the viewpoint and generate new views from any 3D position.

### 2.2.4 VC-1

SMPTE 421M [109] is another state-of-the-art video coding standard. SMPTE 421M is informally referred to as VC-1 and it was initially developed as a proprietary video format by Microsoft. Depending on the applied compression options and source content, the BD-rate of VC-1 over H.264/AVC is approximately  $\pm$  10% [73]. Therefore, VC-1 is widely characterized as an alternative to H.264/AVC.

VC-1 has target bit rates of 96 kbit/s - 135 Mbit/s and its applications include Blu-ray Discs, Windows Media Video 9 (WMV-9), and Microsoft Silverlight framework. VC-1 contains three profiles: *Simple profile* for low-complexity applications, *Main profile* for high data rate Internet applications, and *Advanced profile* for broadcast applications.

### 2.2.5 Future international video coding standards

Although H.264/AVC and VC-1 significantly outperform the older video coding standards, their compression efficiencies tend to be inadequate for the wireless and wired transmission of the next generation resolutions (QFHD and beyond) [92]. Therefore, MPEG and VCEG have established a *Joint Collaborative Team on Video Coding (JCT-VC)* to develop a successor to H.264/AVC.

This forthcoming international video coding standard is tentatively referred to as *High Efficiency Video Coding* (*HEVC*) [34], [132]. HEVC focuses on coding of progressively scanned rectangular frames whose resolution can vary at least between QVGA (320×240 pixels) and UHDTV formats. JCT-VC is currently integrating and refining the features of the best-performing HEVC proposals [5], [35], [63], [89], [124]. The combination of these most promising proposals roughly halves the bit rate over H.264/AVC with the same

subjective perceptual quality, whereas their respective BD-rate savings are measured to be around 30 - 40% [132]. The coding gain tends to increase as a function of resolution. To obtain better trade-off between complexity and compression efficiency, the coding tools of HEVC are separately specified for high efficiency and low complexity applications [92].

The plan of JCT-VC is to publish draft versions of HEVC in 2012 and the first version of the final standard in early 2013. Since HEVC is still a moving target with many uncertain elements and open questions, this Thesis mainly focuses on the existing ratified standards.

# 2.3 Video encoder