Farid Shamani

Design of Intellectual Property-Based Hardware Blocks Integrable With Embedded RISC Processors

Julkaisu 1498 • Publication 1498

| Farid Shamani                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Farid Shamani                                                                                                                                                                        |

| Design of Intellectual Property-Based Hardware Blocks Integrable with Embedded RISC Processors                                                                                       |

| Thesis for the degree of Doctor of Science in Technology to be presented with due                                                                                                    |

| permission for public examination and criticism in Tietotalo Building, Auditorium TB109, at Tampere University of Technology, on the 22 <sup>nd</sup> of September 2017, at 12 noon. |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

| Tampereen teknillinen yliopisto - Tampere University of Technology                                                                                                                   |

Tampereen teknillinen yliopisto. Julkaisu 1498 Tampere University of Technology. Publication 1498

Tampere 2017

Doctoral candidate: Farid Shamani

Laboratory of Electronics and Communications

Engineering

Tampere University of Technology

Finland

Supervisor: Professor Jari Nurmi

Laboratory of Electronics and Communications

Engineering

Tampere University of Technology

Finland

Pre-examiners: Professor Michael Hübner

Lehrstuhl für Eingebettete Systeme der

Informationstechnik (ESIT) Ruhr-Universität Bochum

Germany

Adjunct Professor Pasi Liljeberg Department of Future Technology

University of Turku

Finland

Opponents: Professor Peeter Ellervee

Department of Computer Systems Tallinn University of Technology

Estonia

Adjunct Professor Pasi Liljeberg Department of Future Technology

University of Turku

Finland

# **Abstract**

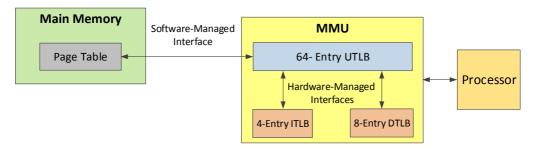

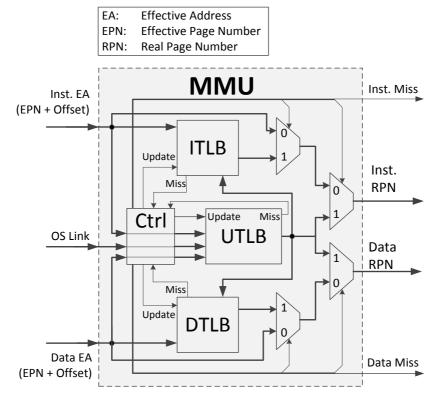

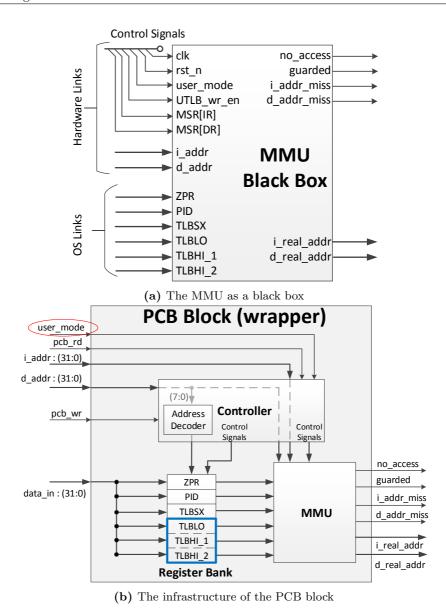

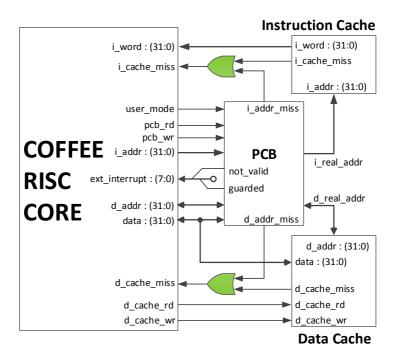

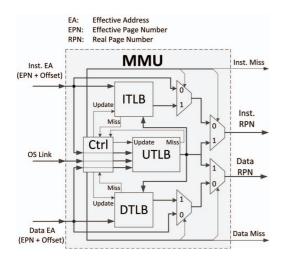

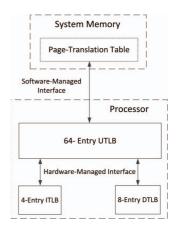

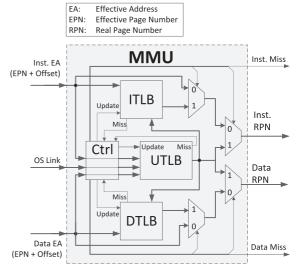

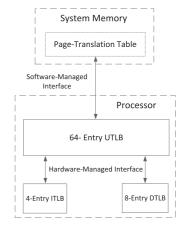

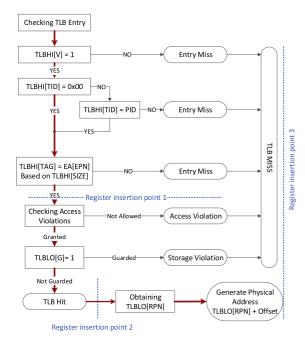

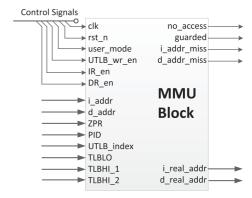

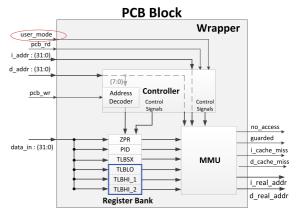

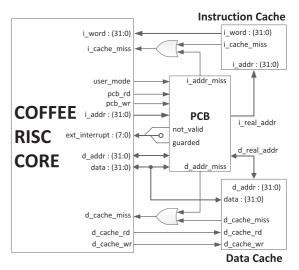

The main focus of this thesis is to research methods, architecture, and implementation of hardware acceleration for a Reduced Instruction Set Computer (RISC) platform. The target platform is a single-core general-purpose embedded processor (the COFFEE core) which was developed by our group at Tampere University of Technology. The COFFEE core alone cannot meet the requirements of the modern applications due to the lack of several components of which the Memory Management Unit (MMU) is one of the prominent ones. Since the MMU is one of the main requirements of today's processors, COFFEE with no MMU was not able to run an operating system. In the design of the MMU, we employed two additional micro-Translation-Lookaside Buffers (TLBs) to speed up the translation process, as well as minimizing congestions of the data/instruction address translations with a unified TLB. The MMU is tightly-coupled with the COFFEE RISC core through the Peripheral Control Block (PCB) interface of the core. The hardware implementation, alongside some optimization techniques and post synthesis results are presented, as well.

Another intention of this work is to prepare a reconfigurable platform to send and receive data packets of the next generation wireless communications. Hence, we will further discuss a recently emerged wireless modulation technique known as Non-Contiguous Orthogonal Frequency Division Multiplexing (NC-OFDM), a promising technique to alleviate spectrum scarcity problem. However, one of the primary concerns in such systems is the synchronization. To that end, we developed a reconfigurable hardware component to perform as a synchronizer. The developed module exploits Partial Reconfiguration (PR) feature in order to reconfigure itself. Eventually, we will come up with several architectural choices for systems with different limiting factors such as power consumption, operating frequency, and silicon area. The synchronizer can be loosely-coupled via one of the available co-processor slots of the target processor, the COFFEE RISC core.

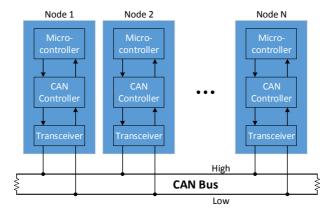

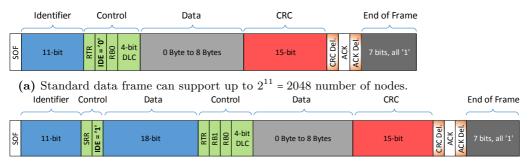

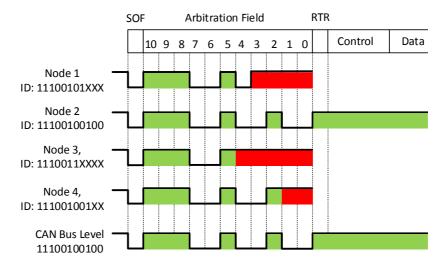

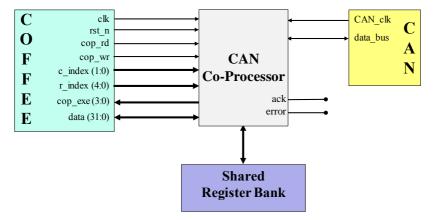

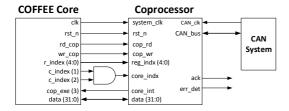

In addition, we are willing to improve the versatility of the COFFEE core even in industrial use cases. Hence, we developed a reconfigurable hardware component capable of operating in the Controller Area Network (CAN) protocol. In the first step of this implementation, we mainly concentrate on receiving, decoding, and extracting the data segment of a CAN-based packet. Moreover, this hardware block can reconfigure itself on-the-fly to operate on different data frames. More details regarding hardware implementation issues, as well as post synthesis results are also presented. The CAN module is loosely-coupled with the COFFEE RISC processor through one of the available co-processor blocks.

# Preface

The work presented here was carried out during 2014-2017 with the Department of Electronics and Communications Engineering at Tampere University of Technology (TUT).

Given the opportunity, I would like to express my deepest gratitude to Prof. Jari Nurmi, who made this possible to complete my M.Sc. degree first, and the Ph.D. degree in the second stage. It was my absolute pleasure to be a member of *Team Nurmi* for more than five years. I would also like to extend my many thanks to Dr. Tech. Tapani Ahonen, who always gave me precious suggestions, comments and feedbacks. It would have never been possible without his friendly support. I also acknowledge Dr. Tech. Jarno M. A. Tanskanen for giving the opportunity to expand my knowledge in other fields of science and technology, as well as the financial support of a portion of this work.

I would laso like to acknowledge the reviewers of this thesis: Prof. Michael Hübner from Ruhr-University Bochum, as well as the Adjunct Prof. Pasi Liljeberg from University of Turku for their invaluable comments to improve the quality of this thesis.

This work was financially supported by the ARTEMIS JU under grant agreement number 295371, as well as the Academy of Finland under contract number 258506 (DEFT: Design of a Highly-parallel Heterogeneous MP-SoC Architecture for Future Wireless Technologies). I would like to gratefully acknowledge the grants supported by the Finnish Cultural Foundation, along with the Jane and Aatos Erkko Foundation under the project Biological Neuronal Communications and Computing with ICT.

Over the last 6 years in Tampere, there was a great number of people who came to my life and left after a while. I learned from many of them, some made me suffer, and some left unforgettable memories of themselves. I would like to extend my appreciation to all my friends who came, who stayed, and who left; especially the ones who became happy with my every little achievement, and stayed right beside me when I was about to fail. Although there are too many of you to name here, I would like to specifically name Payman Aflaki, Milad Mosallaei, Zahra Abbaszadeh, Maede Arvani, Vida Fakour Sevom, Hadis Behzadifar, and Paula Rakowska for the nice moments we shared together.

I would like to express my unutterable gratitude to my family: Masoud, Ada, Saeed, Sepideh, Saghar, and especially my Mother, Soror Zamani, for their unconditional love, support, and kindness. Thank you for standing right beside me through all these tough years. Although we have been living all around the world for the last 15 years, your presences linger in my daily life. Words cannot describe how much I am proud to have such a supportive family.

Many many thanks to my closest relatives who have enlarged my family: my sisters-in-law Nasrin Aminian and Shideh Bakhshi, and brothers-in-law Amir Taheri and Mohsen

iv Preface

Shamani, for giving positive energy, alongside the non-stop love they shared. The same words are extended to my lovely nephews and nieces: Arman, Armin, Ava, Tara, Adrian, Toulu, Roz, Bardia, and Benita.

I lost my father when I just filled four. There are two persons in my life who never let me feel the lack of my father. The first and foremost, my beloved mother, Soror, who sacrificed her own life to raise her children. I do believe that the heaven would not be sufficient to accommodate her in the other life. I wish there would have been a sentence to express how thankful I am. In the second place, I would like to sincerely acknowledge my elder brother Masoud for fulfilling my father's place. All the support he has provided me over the years was the greatest gift anyone has ever given me. Thank you for sacrificing your own life for teaching me how to realize my own potentials.

My extreme appreciation is extended to Ada, as well. Thank you, Ada, for the pure love and your full support during these years. Nothing would have been possible without your unconditional love and support. Words are quite limited to express me deep inside, hence, the least I can do is to dedicate this work to you dear.

I would like to explicitly appreciate Saeed Shamani for being more than just a brother. Although you are sixteen years older than me, you are the best friend in the world that I have ever had, without even a second thought. Back when I was a kid, I swear I could never have imagined that one day we could build such a strong friendly relationship. Do you remember years ago when I was a teenage? I am talking about the time you were my private teacher in Mathematics and Physics. Whoever I am today and whatever I have achieved so far, is the fruit of the tree you planted many years ago.

I would like to thank Sepideh for pushing me towards studying at TUT. This would have not been possible without your unlimited encouragements and motivations. I have to admit that I owe you one of the most important achievement of my life.

Thank you, Saghar, for all the love and support you shared, especially when I was in Iran. I will never forget that you would always be there whenever I needed a shoulder to cry on. I spent the best days of my 20s with you.

To the future love of my life, thank you for being disappeared within these rough years and let me progress towards my ultimate goals. Whoever and wherever you are, it is now the time to show yourself up.  $\odot$

31 August 2017, Espoo, Finland Farid Shamani

# Contents

| A  | ostra             | lCt                                                  | 1   |

|----|-------------------|------------------------------------------------------|-----|

| P  | refac             | e                                                    | iii |

| A  | crony             | yms                                                  | vii |

| Li | st of             | Publications                                         | xi  |

| 1  | 1.1               | Coduction Objective and Scope of the Research        |     |

|    | 1.2<br>1.3        | Author's Contribution to the Published Work          |     |

| 2  |                   | configurable IP-Based NC-OFDM Synchronizer Module    | 5   |

|    | 2.1<br>2.2<br>2.3 | Spectrum Scarcity Problem                            | 5   |

|    | $\frac{2.3}{2.4}$ | The State-of-the-art in NC-OFDM Synchronization      |     |

|    | 2.5               | The Infrastructure of the Multicorrelator            | 10  |

|    | 2.6               | Partial Reconfiguration                              |     |

|    | $\frac{2.7}{2.8}$ | FPGA Constraints                                     |     |

|    | 2.9               | Concluding Remarks                                   |     |

| 3  | Rec               | configurable IP-Based Memory Management Unit         | 29  |

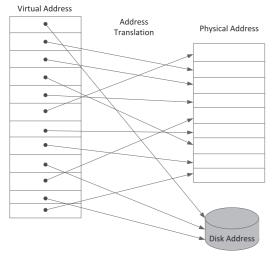

|    | 3.1               | The Virtual Memory                                   | 29  |

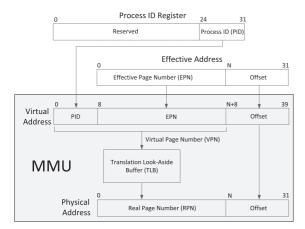

|    | 3.2               | The Virtual Address                                  |     |

|    | 3.3               | How the OS Manages Virtual Addresses                 |     |

|    | 3.4               | Memory Management Unit                               |     |

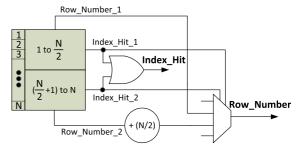

|    | 3.5               | The Infrastructure of the MMU                        |     |

|    | $\frac{3.6}{3.7}$ | FPGA Implementations                                 |     |

|    | $\frac{3.7}{3.8}$ | Synthesis Results                                    |     |

|    | 3.9               | Concluding Remarks                                   |     |

| 4  | Rec               | configurable IP-Based Controller Area Network Module | 51  |

|    | 4.1               | Background                                           |     |

|    | 4.2               | Motivation                                           |     |

|    | 4.3               | CAN Protocol Specification                           | 52  |

vi

|              | 4.4    | The Structure of a CAN Frame               | 53 |

|--------------|--------|--------------------------------------------|----|

|              | 4.5    | Design Considerations                      | 54 |

|              | 4.6    | The FPGA Implementation and Integration    | 57 |

|              | 4.7    | Synthesis Results                          |    |

|              | 4.8    | Concluding Remarks                         | 57 |

| 5            | Con    | nclusion                                   | 59 |

|              | 5.1    | Main Results                               | 59 |

|              | 5.2    | Future Developments                        | 60 |

| B            | ibliog | graphy                                     | 61 |

| $\mathbf{A}$ | ppen   | dix A                                      | 67 |

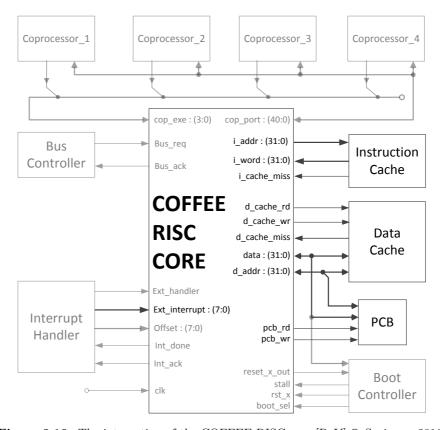

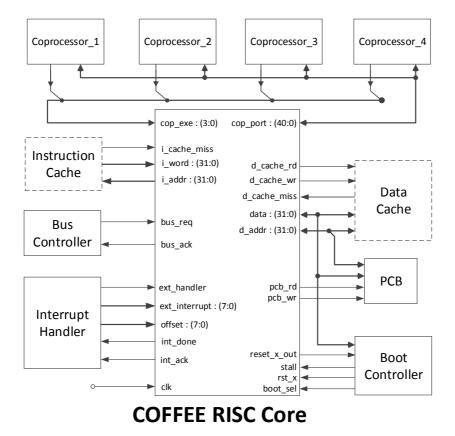

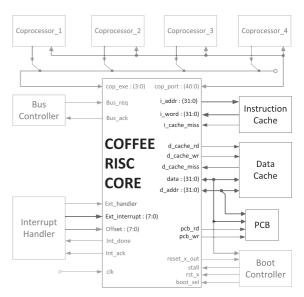

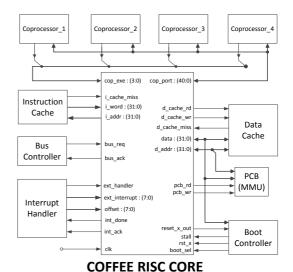

| $\mathbf{T}$ | he A   | rchitecture of the Platform                | 69 |

|              | Emb    | pedded Processors                          | 69 |

|              | COI    | FFEE, a General-Purpose Embedded Processor | 69 |

|              | Gen    | eral Characteristics                       | 70 |

|              | An l   | Insight to the Architecture of the Core    | 71 |

|              | Hard   | dware Implementation Costs and Details     | 72 |

| Ρı           | ublic  | ations                                     | 75 |

# Acronyms

ACK Acknowledge

**ALMs** Adaptive Logic Modules

**ALUTs** Adaptive Look-Up Tables

**APP** A Posterior Probability

ASIC Application Specific Integrated Circuit

**ATT** Address Translation Table

CAN Controller Area Network

**CP** Cyclic Prefix

**CCB** Core Configuration Block

CISC Complex Instruction Set Computer

CR Cognitive Radio

**CRs** Condition Registers

CRC Cyclic Redundancy Check

CSMA/CR Carrier Sense Multiple Access/Collision Resolution

**CGRAs** Coarse-Grain Reconfigurable Arrays

**DF** Direct Form

**DLC** Data Length Code

**DMA** Direct Memory Access

**DSA** Dynamic Spectrum Access

**DSP** Digital Signal Processor

**DTLB** Data Translation Look-aside Buffer

**EA** Effective Address

**EOF** End-of-Frame

**EPN** Effective Page Number

viii Acronyms

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

**GPP** General Purpose Processor

**GPRs** General Purpose Registers

**HDD** Hard Decision-based Detection

**IFFT** Inverse Fast Fourier Transform

IC Integrated Circuit

**IDE** Identifier Extension

I/O Input/Output

IP Intellectual Property

**ISA** Instruction Set Architecture

ITLB Instruction Translation Look-aside Buffer

LAN Local Area Network

LDPC Low-Density Parity-Check

LRU Least Recently Used

LTF Long Training Field

LTS Long Training Symbol

MAC Multiply-Accumulate

ML MultiplierLess

MMU Memory Management Unit

MSR Machine State Register

NIC Network Interface Controller

NC-OFDM Non-Contiguous Orthogonal Frequency Division Multiplexing

**OFDM** Orthogonal Frequency Division Multiplexing

OOB Out-of-Band

**OPDF** Optimized Parallel Direct Form

**OPPDF** Optimized Pipelined-Parallel Direct Form

**OS** Operating System

**OTDF** Optimized Transposed Direct Form

PAPR Peak-to-Average Power Ratio

PCB Peripheral Control Block

**PDF** Parallel Direct Form

PID Process ID

**PPDF** Pipelined-Parallel Direct Form

PR Partial Reconfiguration

**PSR** Processor Status Register

RI Register Insertion

RISC Reduced Instruction Set Computer

**RPN** Real Page Number

RTR Remote Transmission Request

SDD Soft Decision-based Detection

**SDR** Software Define Radio

**SNR** Signal-to-Noise Ratio

**SOF** Start-of-Frame

SRR Substitute Remote Request

STF Short Training Field

STS Short Training Symbol

**TDF** Transposed Direct Form

TLB Translation-Lookaside Buffer

UTLB Unified Translation Look-aside Buffer

VCD Value Change Dump

VHDL Very high speed integrated circuits Hardware Description Language

VM Virtual Memory

VPN Virtual Page Number

**ZPR** Zone Protection Register

# List of Publications

Most of the contents of this thesis is based on the following publications in which the author of the thesis is the main author. The publications are referred to as [P. #] in the manuscript. All the following publications are appended at the end of the thesis.

- I F. Shamani, R. Airoldi, T. Ahonen, and J. Nurmi, "FPGA Implementation of a Flexible Synchronizer for Cognitive Radio Applications", in *Proceedings of the 2014 Conference on Design and Architectures for Signal and Image Processing (DASIP)*, Madrid, Spain, pp. 1–8, Oct. 2014.

- II F. Shamani, V. F. Sevom, T. Ahonen, and J. Nurmi, "FPGA Implementation Issues of a Flexible Synchronizer Suitable for NC-OFDM-Based Cognitive Radios", in *Elsevier Journal of Systems Architecture (SYSARC)*, Nov. 2016.

- III F. Shamani, T. Ahonen, and J. Nurmi, "Synchronization in NC-OFDM-Based Cognitive Radio Platforms", in W. Hussain et al. "Computing Platforms for Software-Defined Radio", Springer International Publishing, pp. 189–207, 2017.

- IV F. Shamani, V. F. Sevom, J. Nurmi, and T. Ahonen, "Design, Implementation and Analysis of a run-Time Configurable Memory Management Unit on FPGA", in *IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP & International Symposium on System-on-Chip (SoC)*, Oslo, Norway, pp. 1–8, Oct. 2015.

- V F. Shamani, V. F. Sevom, T. Ahonen, and J. Nurmi, "Integration Issues of a run-Time Configurable Memory Management Unit to a RISC Processor on FPGA", in Elsevier Journal of Microprocessors and Microsystems (MICPRO), Dec. 2016.

- VI F. Shamani, V. F. Sevom, T. Ahonen, and J. Nurmi, "FPGA Implementation and Integration of a Reconfigurable CAN-Based co-Processor to the COFFEE RISC Processor", in *IEEE Nordic Circuits and Systems Conference (NORCAS):* NORCHIP & International Symposium on System-on-Chip (SoC), Copenhagen, Denmark, pp. 1–6, Nov. 2016.

# 1 Introduction

During the last decade, technology advancements have significantly affected people's lives. Unprecedented growth in science and technology has accomplished modernity. In that respect, a number of digital systems can be found in most of the electronics devices. The main engine of such systems is typically a programmable processor which controls other peripheral electronics components. In the world of *Embedded Systems* and *Systems-on-Chip (SoCs)*, these programmable processors are designed in a way to offer the maximum flexibility, minimum silicon area, fast operating frequency, and low power consumption. On the other hand, they do not necessarily perform well enough to meet some real-time requirements of embedded applications. Hence, the demand of real-time support in embedded applications is become more into picture day by day.

One possible solution is to employ hardware accelerators, which also called Functional Units (FUs), co-processing in parallel with the main processor [1]. In principle, co-processing accelerates the overall performance of the system by offloading computationally intensive task from the main processor. Therefore, components capable of co-processing are usually dedicated Intellectual Property (IP) blocks which can execute a certain function considerably faster than the main processor. Nevertheless, characteristics such as scalability, flexibility, and reconfigurability are some of the prominent features of a good design.

Decades ago, computer architectural designers were encountered to choose between flexibility and performance. If we consider Application Specific Integrated Circuit (ASIC) technology on one end and the General Purpose Processor (GPP) on the opposite end, there was a huge gap between these two design choices. Typically, GPPs are closer to the software side. They can execute any function consisted of several instructions due to the versatility of their instruction set. Thus, they are very flexible to perform any computable task, while their performance is very poor for performing some specific tasks. In principle, an ASIC is designed to perform some specific tasks very fast and efficient. Hence, ASICs has the potential to achieve higher speed, less silicon area, and less power consumption compared to the GPPs on performing a specific task. On the other hand, ASICs are not flexible in terms of architectural changes. Once an ASIC is fabricated, it cannot be altered to perform another application [2]. Therefore, ASICs are typically used for high-volume embedded systems, such as mobile phones. In addition, only few companies can afford to implement their products on ASICs due to the high production costs

Reconfigurable Computing is intended to fill the gap between ASIC (hardware) and GPP (software) by achieving higher performance than software, while offering more flexibility compared to the hardware [3]. The main idea of employing reconfigurable architectures is back to 1950s where the Gerald Estrin proposed the concept of Reconfigurable Architecture

Blocks [4]. The idea was to use the main processor to control and monitor the behavior of an array of reconfigurable hardware blocks. We can consider that the 1980s-1990s was a renaissance in this field of research and several reconfigurable platforms were introduced, including Ramming Machine, Hartenstein's XPuter, and PAM Machine [5]. By the invent of the Field Programmable Gate Array (FPGA) in the mid 1980s and early 1990s, real-time signal processing (such as video and audio signal processing) which was too computationally intensive for microprocessors, came more into picture [6]. Indeed, the FPGAs, as one of the major reconfigurable platforms, could successfully fill the gap between software-oriented and hardware-oriented architectures. Although the FPGAs offer satisfactory performance for most of the embedded applications, the energy consumption of an FPGA-based embedded system should be carefully considered.

## 1.1 Objective and Scope of the Research

The primary objective of this work is to research the influence of hardware acceleration in the world of embedded systems. In that sense, some reconfigurable architectural solutions and research methods, with their respective hardware implementations suitable for a Reduced Instruction Set Computer (RISC)-based platform are developed. The main motivation, in that respect, is to provide a flexible approach to increase the overall performance of a computing platform, while the efficiency is maximized and power consumption is maintained at an acceptable level. In addition, a reconfigurable platform has the potential to be adapted in different operational environments.

As the case study, we take into consideration an embedded processor named *COFFEE* core for the proof-of-concept. The core is an open-source embedded processor in which reusability and configurability are two prominent characteristics of the core. So far, the core is integrated with several IP blocks as different co-processors to create an embedded platform. For example, the integration of a floating point unit as a co-processor was done in [7]. The floating point co-processor is called MILK. The COFFEE core which is tightly-coupled with the MILK co-processor is named CAPPUCCINO. In another attempt, the COFFEE is integrated with three co-processors to form a programmable baseband receiver platform [8]. In [9], the multi-core version of the COFFEE is used to build a platform suitable for Software Define Radio (SDR). The COFFEE is also used to create a template named CREMA which is based on the principle of Coarse-Grain Reconfigurable Arrays (CGRAs) [10]. More information regarding the COFFEE core is appended at the end of this thesis in Section Appendix A.

Although the COFFEE has exploited different configurations to create various platforms, it still requires more efforts to increase the versatility and application performance of the core. For example, the core is heavily suffering from the lack of a Memory Management Unit (MMU) [11]. As discussed earlier, the ultimate motivation behind this research work is to design several reconfigurable IP blocks loosely/tightly-coupled with the COFFEE processor. However, the integration of the developed IP blocks are not only limited to the target processor; they are integrable with any standard RISC architecture. The developed IP blocks fulfill the general characteristics of a good digital design previously mentioned. In addition, other design parameters, such as energy efficiency, are vastly taken into consideration in the hardware description of each IP block. Indeed, the energy efficiency is very crucial in battery-powered embedded applications. In our research group, we have a way of thinking that a good IP block is worth more than a good design.

The overall content of this thesis is composed of three main sections. In each section, we

try to develop a reconfigure architecture specifically designed for a particular application. In the first section, a reconfigurable module which is capable of receiving and decoding one of the potential modulation techniques of the next generation wireless communication is developed. The target modulation is the Non-Contiguous Orthogonal Frequency Division Multiplexing (NC-OFDM) technique, in which the wireless spectrum can be utilized efficiently. Although the NC-OFDM has the potential to alleviate spectrum scarcity to some extent, synchronization in those systems is one of the major problems. In that respect, we propose a reconfigurable architecture which is able to tackle synchronization problem of an NC-OFDM-based system. One of the main characteristics of the synchronizer is the capability of reconfiguring itself during the run-time using Partial Reconfiguration (PR) feature.

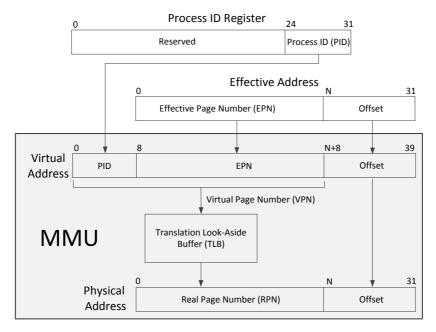

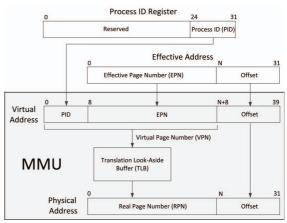

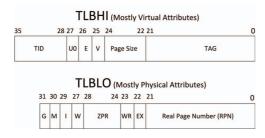

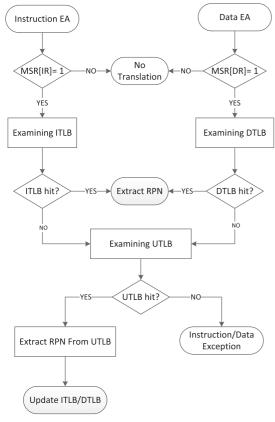

In the second section, another reconfigurable architecture is designed to operate as an MMU. One of the main applications of the MMU is to enable virtual-to-physical address translations. In fact, the MMU is developed to improve the overall performance of the processor. The infrastructure of the MMU is based on employing several Translation-Lookaside Buffers (TLBs) simultaneously in different hierarchies. Each TLB has a different size in terms of the number of entries. The MMU reconfigures itself during the run-time to operate on different page sizes, from 1KB to 16MB in the virtual space.

The third section concentrates on another reconfigurable module which is able to operate in the context of Controller Area Network (CAN) protocol. The CAN module is capable of reconfiguring itself while operating to operate on different data frames, i.e. *standard data frame* and *extended data frame*. Furthermore, the CAN module guarantees the integrity of the data in several situations.

#### 1.2 Author's Contribution to the Published Work

The context of this thesis has mainly been extracted from the Publications [P. I] – [P. VI] in which the author was the primary author. Prof. Nurmi supervised the overall work and gave invaluable comments and feedbacks on each of the publications.

Publication [P. I]: The purpose of this paper was to design and develop an IP-based synchronizer to alleviate one of the major problems in next generation wireless communications. We developed a novel method how to perform synchronization in such systems. The hardware implementation and considerations are done by the author. The idea of using Partial Reconfiguration (PR) technique arose by the second author, Dr. Tech. R. Airoldi. The third author, Dr. Tech. T. Ahonen, as well as the fourth author, Prof. J. Nurmi, gave technical comments, along with invaluable feedbacks.

Publication [P. II]: This paper was an extension to our previous work [P. I] with an invitation. In this paper, the first author put his best effort on optimizing the hardware implementation of the mentioned design. As a result, magnificent improvements in terms of maximum operating frequency were achieved, while the hardware resource allocation, alongside the power consumption drastically reduced. This IP block has the potential to be loosely-coupled with the COFFEE RISC processor. This work is mainly done by the first author, while the third author V.F. Sevom assisted in some simulations and verifications. The remaining authors gave very nice comments on overall work.

Publication [P. III]: In this publication, the first author discussed the synchronization problem in next generation wireless communications. The entire work is done by the first author, while Dr. Ahonen and Prof. Nurmi gave the final comments on the work.

Publication [P. IV]: The main contribution of this paper was to develop a run-time configurable memory management unit. The entire hardware implementation was done by the first author. The second author assisted in MatLab computations. Dr. Ahonen and Prof. Nurmi gave technical comments and supervised the entire work.

Publication [P. V]: This publication was an extension to our previous work in [P. IV]. In this paper, the integration issues of the proposed memory management unit with the COFFEE core (tightly-coupled) was investigated in detail. The overall work, including integration and optimizations, were performed by the first author. The second author assisted in some simulations and verifications with a new set of test vectors. The entire work was supervised by Dr. Ahonen, along with Prof. Nurmi.

Publication [P. VI]: In this publication, a reconfigurable Controller Area Network (CAN) protocol was developed which was loosely-coupled with the COFFEE RISC processor. The first author designed and implemented the entire CAN protocol as an IP block on FPGA. The integration with COFFEE processor was done by the first author, as well. The verification of the design was done by the help of the second author. This work was fully supervised by Dr. Ahonen and Prof. Nurmi.

#### 1.3 Thesis Outline

The rest of this thesis is organized as follows. In Chapter 2, the author discusses the synchronization problem in next generation wireless communications. The-state-of-the-art, as well as the hardware implementation issues are widely discussed. Chapter 3 describes the developed memory management unit and its respective technical issues, e.g. how to integrate the MMU with the COFFEE processor. Chapter 4 explains the development of the proposed CAN module on FPGA with its respective integration with COFFEE RISC processor. Eventually, Chapter 5 summarizes the overall research work. Appendix A gives an insight to the COFFEE platform in terms of architecture, design considerations, hardware cost, etc.

# 2 Reconfigurable IP-Based NC-OFDM Synchronizer Module

The main context of this chapter is extracted from [PI], [PII] and [PIII]. This chapter provides a wide discussion about an alternative solution to cope with spectrum scarcity problem. In this regard, we proposed a flexible Non-Contiguous Orthogonal Frequency Division Multiplexing (NC-OFDM)-based synchronizer which is capable of reconfiguring itself on-the-fly using Partial Reconfiguration (PR) feature. In addition to the state-of-the-art, this chapter provides a deep insight to the hardware implementation which leads to revealing various constraints. Furthermore, the author provides different architectural choices with their respective trade-offs, e.g. using more silicon area to achieve higher operating frequency. The proposed synchronizer has the potential to be loosely-coupled with the COFFEE core as a co-processor.

# 2.1 Spectrum Scarcity Problem

The trend towards replacing wired systems with wireless devices is getting stronger. Generally speaking, wireless technology is being advanced day after day. The number of wireless users who demand higher data rate is increasing per day [12]. Since the spectrum is a finite resource, increasing number of wireless users is leading to spectrum scarcity problem. It is mainly due to the fact that the frequency bands between 10MHz to 6GHz are most suitable for wireless communications due to the characteristics of the electromagnetic waves. However, this wide frequency band is not sufficient to accommodate all today's wireless users at once [13].

# 2.2 Cognitive Radio as a Solution

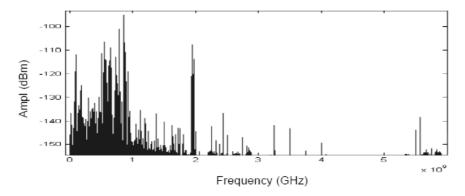

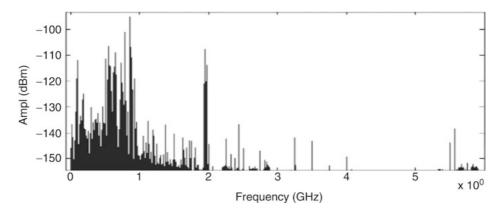

One possible solution to resolve spectrum scarcity problem is to employ Dynamic Spectrum Access (DSA). Conceptually, the DSA is a promising technique which employs unused frequency bands allocated to a licensed user, e.g. TV broadcast, for secondary user activities [14]. These unoccupied frequency bands are also known as white spaces. In principle, secondary users willing to transmit within a licensed band are permitted to transmit their data via the available white spaces as long as they do not interfere with the incumbent licensed user. Cognitive Radio (CR) is a device capable of employing DSA technique. In context, the CR is a flexible platform in which most of the baseband processing is performed in programmable processing technologies such as GPP, Digital Signal Processor (DSP), and FPGA [9]. In CR, the transmitter is able to detect which communication channels are occupied and which are not. Indeed, the CR is always aware of its surrounding. For example, Figure 2.1 depicts a real measurement of the spectrum

**Figure 2.1:** A portion of the spectrum allocated to a licensed user. Obviously, the licensed user does not efficiently utilize the spectrum [15, p. 163]

at downtown Berkeley. As it is obviously clear, the licensed user mostly utilizes the first 2GHz of the dedicated 6GHz spectrum, while the rest of the spectrum is not fully utilized. The CR has the ability to instantly employ unoccupied channels within the licensed spectrum for secondary transmissions while avoiding the ones occupied by the primary user. Moreover, the CR should guarantee that there will be no interference with the licensed user's subbands.

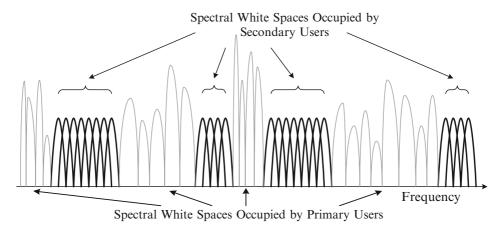

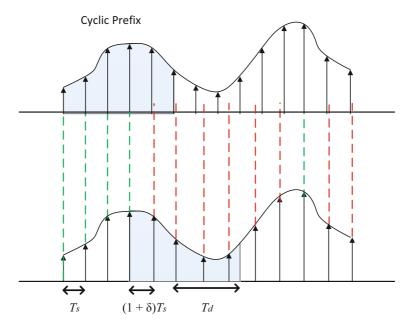

### 2.2.1 NC-OFDM, a Recently Emerged Technology

CRs have still their own challenges including how to sense the spectrum, which data transmission technique is the most efficient one, etc. So far, there have been several modulation techniques to be employed in CR of which the Orthogonal Frequency Division Multiplexing (OFDM) is the most favorable one [16]. The orthogonality between overlapped carriers is one of the major features that discriminates the OFDM from the other modulation techniques [17]. However, the OFDM technique has its own disadvantages such as Peak-to-Average Power Ratio (PAPR), sensitivity to carrier frequency offset, and extra overhead due to using a Cyclic Prefix (CP). In addition, since the OFDM operates in a contiguous spectrum mode, a 5MHz transceiver can only transmit when an idle 5MHz spectrum band is detected. If we take into the assumption that a 5MHz band is occupied by a narrowband transceiver, e.g. 200kHz, the entire 5MHz band is treated as busy. In this case, more than 90% of the bandwidth is being wasted by the narrowband transceiver to transmit at only 200kHz speed [18].

One alternative solution capable of tackling the above-mentioned problem is an upgraded form of the conventional OFDM technique named NC-OFDM. Indeed, the NC-OFDM technique has recently attracted many researchers due to its capability of turning off a subset of subcarriers which are not required for the transmission or those which might cause interferences with the adjacent users. Furthermore, the NC-OFDM has been nominated as a promising candidate for high data rate transmissions in the context of the CR [14]. Potentially, the NC-OFDM can be one of the best candidates towards the next generation wireless communications, 5G [19].

2.3. Related Works 7

#### 2.2.2 Synchronization, one of the Major Problems

As previously mentioned, NC-OFDM is a reliable candidate to exploit the spectrum more efficiently. Although this technique is able to cope with the spectrum scarcity problem, similar to other techniques, it has its own challenges. One of the primary challenges in NC-OFDM is how to synchronize the receiver with the transmitter. The main reason is that since the NC-OFDM transmitter is able to use any white space within the licensed spectrum (of course, by considering the constraints mentioned such as not interfering with the licensed user's subbands), the secondary user has the potential to be presented in any location within the spectrum. Nevertheless, one challenge is to detect the location of the secondary transmitter within the prime spectrum from the receiver's point of view. In addition, the NC-OFDM transmitter is able to switch off unnecessary subcarriers which result in an alteration to the time-domain representation of the signal. A tiny change in the waveform of a time-domain signal will generate a stochastic location for the preamble, pilot and data carriers. In this regard, the second challenge is to find the exact locations of the mentioned subcarriers in the receiver side.

### 2.3 Related Works

In principle, there are two well-known methods which have widely been used to synchronize both receiver and transmitter. A very straightforward solution is to dedicate a particular channel (a secondary channel) to reveal the essential synchronization characteristics of the transmitter to the receiver. In the literature, this solution is known as the *Out-of-Band (OOB)* communication. Authors in [20, 21, 22, 23, 24] have studied synchronization in OOB systems and proposed some techniques with respect to the out-of-band synchronization. In this method, since the receiver is always aware of the location of the secondary user in the entire spectrum, the synchronization is potentially similar to that of OFDM. However, the additional hardware cost, along with dedicating a portion of bandwidth to the secondary channel are two limiting factors which limit the functionality of the out-of-band data transmission in some practical situations [25].

In contrast to the out-of-band communications, *In-Band* data transmissions more attract researchers in the field of NC-OFDM systems. In this method, the prerequisite synchronization information is embedded in the same packet sent by the transmitter. It is now the receiver's concern how to extract that information in order to synchronize itself with the transmitter. In this thesis, we have also taken into account how to perform synchronization in an in-band environment. Similar to out-of-band systems, there are some studies regarding the in-band communication which few of them are briefly explained as follows.

In [26], a fractional bandwidth model is proposed in which a new format for the preamble is introduced. In frequency-domain, a specific pseudo-noise is generated in a way that the time-domain representation of the preamble comes with two identical halves with different sign bits. Apart from the OFDM based scheme, the interferences caused by the licensed users have not been fully considered. The authors took into the assumption that the power level of the primary user is lower than the secondary transmitter, while in reality, it is the secondary transmitter which should minimize its transmitting power to prevent interference with the adjacent primary user due to the sidelobe leakages [27].

In [25], the receiver takes A Posterior Probability (APP) algorithm into consideration to discover the active subchannels, while the interference caused by the licensed user

is accounted. In the case of detecting an active subchannel, the receiver performs a Hard Decision-based Detection (HDD) algorithm to extract NC-OFDM symbols. A poor performance in a noisy channel, as well as the subchannels closed to the primary user, is one drawback of employing HDD algorithm. Therefore, the receiver takes into account a Soft Decision-based Detection (SDD) to increase the performance in such noisy environments.

Li et al. in [28], tried to improve the methodology introduced in [25]. According to their claim, the system code rate of the proposed algorithm is only 1/4, while only half of the subcarriers are active. They propose a Low-Density Parity-Check (LDPC) to improve system code rate right after the APP is finished. The authors mainly emphasized on how to generate the LDPC code, while the synchronization procedure is not exactly addressed. They have taken into the assumption that the receiver has a perfect solution to synchronize itself with the transmitter.

Saha et al. proposed a blind synchronization method in which the receiver is capable of locally regenerating the time-domain representation of the frequency-domain incoming signal [29, 30]. They also exploit a multiplier-less approach to detect active subcarriers in the frequency-domain. The multiplier-less approach provides an acceptable performance in packet detection stage while omitting a massive number of unnecessary complex computations. Furthermore, by having known the fundamental information regarding the primary user's activities in the spectrum, a binary mask is employed to filter out the primary user's active subcarriers in the frequency-domain. The rest of synchronization is inferred to be similar to the OFDM.

## 2.4 The State-of-the-art in NC-OFDM Synchronization

As previously stated, since the time-domain representation of the signal in an NC-OFDM-based system is altered, the synchronizer block should find another way to detect the secondary transmission. Although synchronization in an OFDM system can be performed in time-domain, frequency-domain or both, an OFDM receiver is more likely to perform synchronization in time-domain. The main reason is that synchronization in frequency-domain is very computationally expensive in the receiver. However, it seems that an NC-OFDM receiver has no possible solution than to perform synchronization in the frequency-domain, since the shape of the time-domain preamble is altered. In this work, we employ several techniques, e.g. multiplier-less approach, alongside the state-of-the-art features, e.g. partial reconfiguration, in order to keep the receiver synchronized with the secondary transmitter. Moreover, the synchronizer block is carefully designed for different scenarios, for example, when the silicon area is the limiting factor, when power consumption is the main factor, or reaching to the maximum operating frequency is the ultimate target.

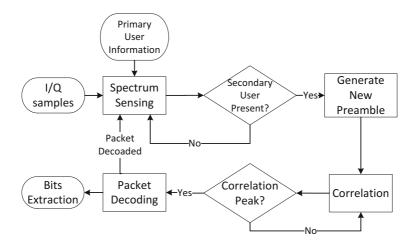

#### 2.4.1 The Conventional Method

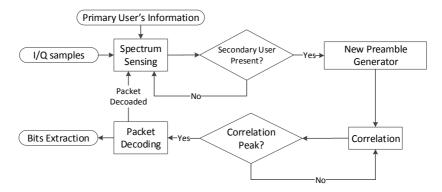

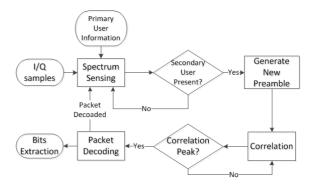

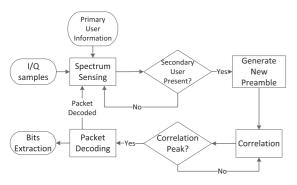

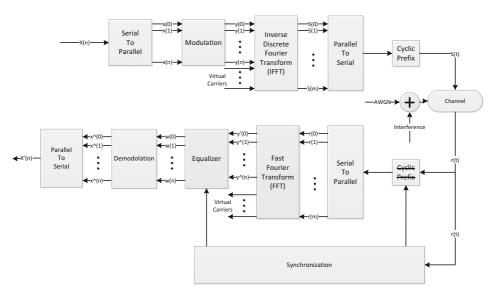

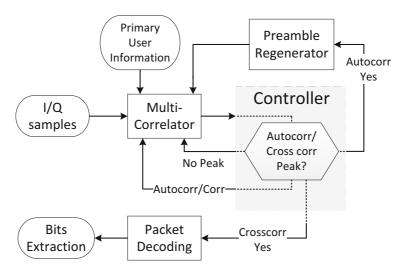

Figure 2.2 shows the most common synchronization mechanism in an NC-OFDM system. Conceptually, the synchronization is performed in two major sections. First, the subcarrier detection and, second, preamble regeneration and packet detection. As previously studied, the receiver has no prior information about the subbands in which the secondary user is active. Nevertheless, the first step is to collect as much information about the spectrum as possible. Hence, the receiver gathers all the available subbands in the spectrum and starts sensing each of them to detect the active ones, using one of the sensing methods.

**Figure 2.2:** The most common synchronization scheme. Reconstructed from [P. I] ◎ IEEE, 2014.

According to the Federal Communications Commission, secondary users willing to transmit in a licensed spectrum may have the preliminary information about the licensed user such as power, location, and signal structure [31]. Having fundamental information about the licensed user, those subcarriers which belong to the licensed user are masked. Once the licensed user is masked, the remaining active subcarriers are considered for the secondary transmitter. The first phase of the synchronization (secondary user detection) is successfully finished at this stage.

Now, it is possible to form the time-domain representation of the secondary signal by using a low-cost Inverse Fast Fourier Transform (IFFT) unit. Once the new preambles are generated, the correlator is fed by recently generated parameters and, subsequently, the maximum similarity between a buffered version of the incoming signal and the generated preamble is investigated. As soon as the correlator finds a peak, the entire packet is delivered to the packet decoding block to extract the data bits. In case that the correlator fails to detect a peak, there is a possibility that the secondary transmitter has terminated the connection on the set of subcarriers detected as active in the previous stage. Therefore, the sensing unit will start sensing the spectrum from the scratch to find active subbands occupied by the secondary transmitter.

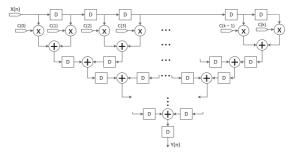

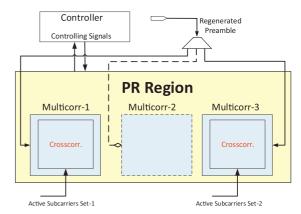

### 2.4.2 The Proposed Synchronizer

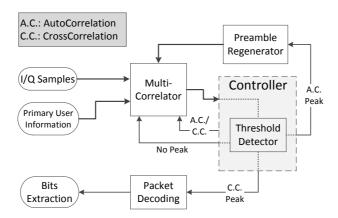

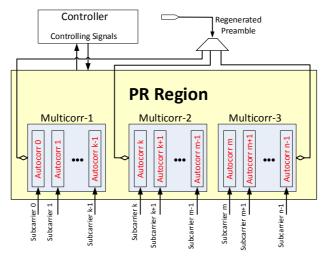

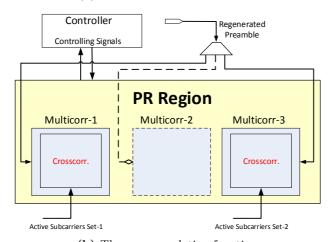

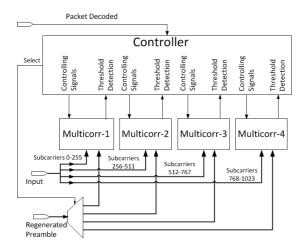

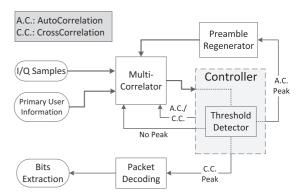

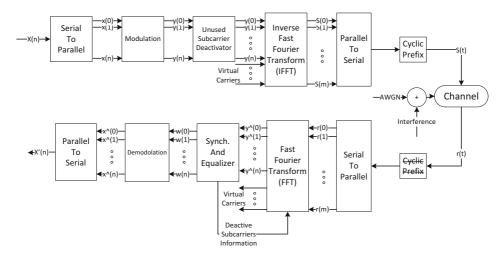

The synchronizer proposed in this work follows the same dataflow as Figure 2.2 presents. The contribution beyond the state-of-the-art of this work is to employ a reconfigurable multicorrelator to perform both spectrum sensing and correlation on demand. From the architectural point of view, the multicorrelator is able to reconfigure its parameters to perform either autocorrelation function for spectrum sensing or crosscorrelation function for packet detection phase using Partial Reconfiguration feature.

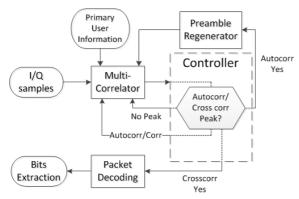

Figure 2.3 illustrates how the multicorrelator operates in an NC-OFDM receiver. In the first phase (secondary transmission detection), the controller block (re)configures the multicorrelator to perform autocorrelation during the run-time to monitor the entire spectrum. Here, the autocorrelation function computes the maximum similarity between the incoming signal and a delayed version of itself. The achieved results are compared with a threshold. The magnitude of the threshold is determined by the receiver during the inter packet time slot. When the channel is idle, the magnitude of the noise is determined. Then, the noise level is subtracted from the overall energy of the signal, leading to an

approximate threshold value. However, this method might not be practical in very low Signal-to-Noise Ratio (SNR) regions.

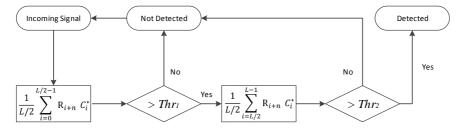

When the presence of the secondary user is detected by the receiver, all active subcarriers (excluding those related to the licensed user) are handed to the preamble regenerator unit to generate a time-domain form of the frequency-domain signals. Meanwhile, the controller reconfigures the multicorrelator using PR feature to perform crosscorrelation function (packet detection phase). Once the multicorrelator is set up with regenerated coefficients, the crosscorrelation is performed to find the boundaries of the packet. Since the crosscorrelation function is a computationally intensive task, Roberto Airoldi proposed a two-step threshold verification mechanism in [32]. This method is further investigated in next sections. Once the second threshold level is met by the Threshold Detector block, the packet is delivered to the Packet Decoding block to extract the data.

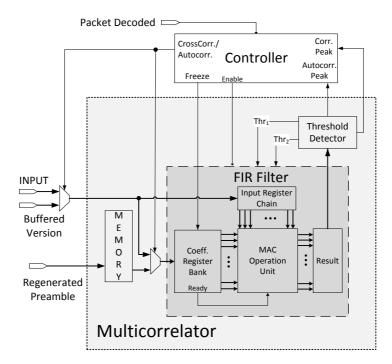

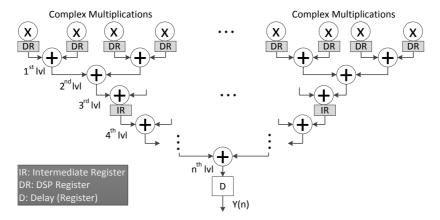

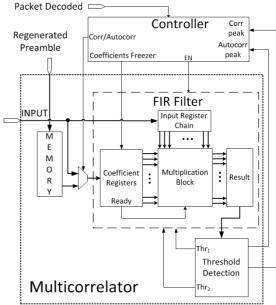

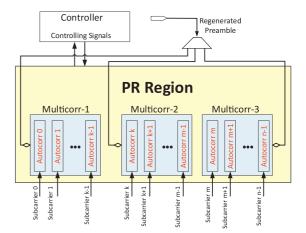

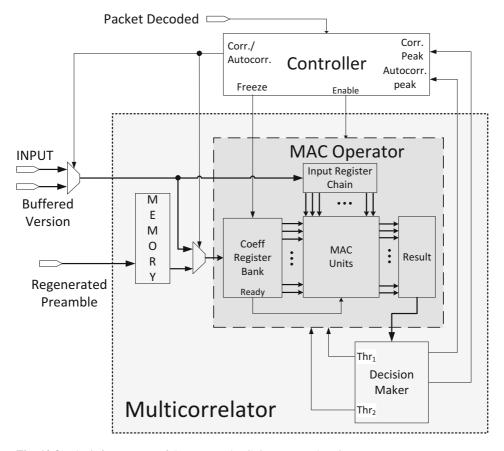

#### 2.5 The Infrastructure of the Multicorrelator

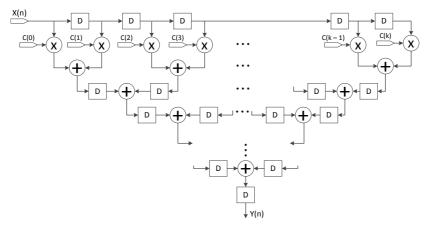

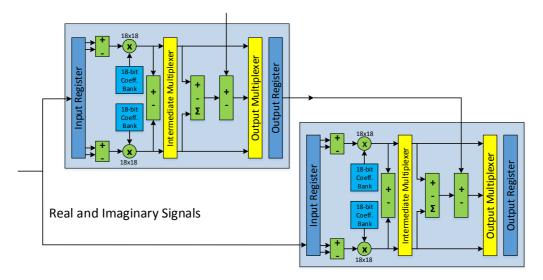

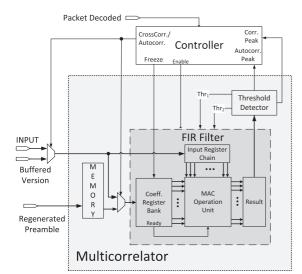

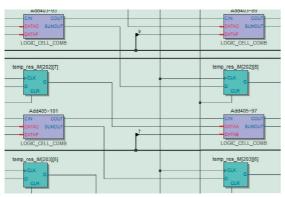

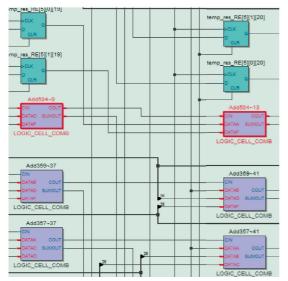

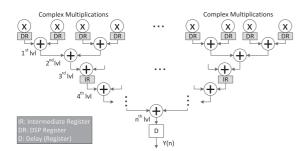

The multicorrelator is composed of several fundamental subblocks of which the Finite Impulse Response (FIR) block is the most prominent one. As Figure 2.4 presents, the multicorrelator consist of a Memory block, FIR filter block, Threshold Detector block, and Controller block. Each block is briefly explained in the following subsections.

### 2.5.1 Memory Block

This block is a simple SRAM which is used to store regenerated coefficients. Each memory word is 32 bits long of which we assigned the first 16 bits for the *Real* part and the remaining 16 subsequent bits represent the *Imaginary* part of the incoming signal. For example, the value 0x1234ABCD in a memory block infers that 0x1234 is the real part and 0xABCD is the imaginary part of the signal, respectively. The main reason why we take 16-bit input signals into consideration is that 16-bit coefficients provide enough accuracy for the FIR filter to perform crosscorrelation [33]. From the hardware implementation point of view, we employed an unsynthesizable SRAM described by the Very high speed integrated circuits Hardware Description Language (VHDL) code for the simulation and a synthesizable IP block provided by Quartus II environment for synthesis purpose, respectively.

Figure 2.3: The proposed architecture for the synchronizer [P. II] © Elsevier, 2016.

Figure 2.4: The infrastructure of the multicorrelator [P. II] © Elsevier, 2016.

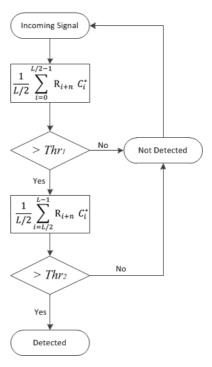

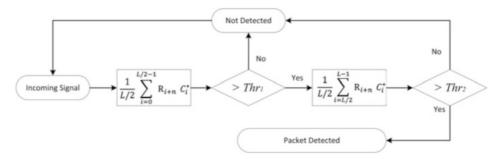

#### 2.5.2 Threshold Detector block

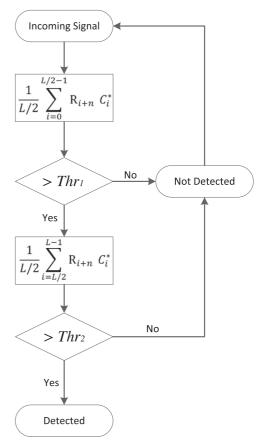

The main objective of this block is to compare the computed results of the FIR filter with a predefined threshold value. In the first phase (secondary transmitter detection) the filter computes the autocorrelation function. The autocorrelation measures when the similarity between the incoming signal and a delayed version of itself is in the maximum level. In that respect, the energy of the noise is calculated when the channel is idle. Once the channel becomes busy, the energy of the noise is subtracted from the total energy. As soon as the final result exceeds a threshold, the corresponding subcarrier is considered to be active. In contrast to autocorrelation, the threshold detector employs two threshold points when the filter is computing crosscorrelation function. It is mainly due to the fact that calculating crosscorrelation function is a very energy-hungry task. Therefore, we apply a 2-step verification algorithm proposed in [32]. As Figure 2.5 illustrates, in the first step the crosscorrelation of the first half of the signal is computed. The obtained results are compared with a preliminary threshold  $Thr_1$ . If the magnitude of the  $Thr_1$ for the first-half calculation is met, the multicorrelator computes the second half and, subsequently, computes the overall results with a second threshold  $Thr_2$ . At this stage, a peak shows that there was a good correlation between the buffered signal and the regenerated preambles. Otherwise, the buffered version of the signal is discarded, even though the first threshold was met. A proper value of the preliminary threshold  $(Thr_1)$ , as well as the original threshold  $(Thr_2)$ , has a massive impact on the signal detection. For example, setting a low value for the  $Thr_1$  might lead to false detection of the signal in low SNR regions. On the other hand, although a high value will guarantee the robustness of the calculation, it might result in packet loss since a low-power signal might be considered as noise. Therefore, a good approximation for the  $Thr_1$  is 45% of the  $Thr_2$  [32].

Figure 2.5: The 2-step verification algorithm [P. III] © Springer, 2017.

#### 2.5.3 Controller Block

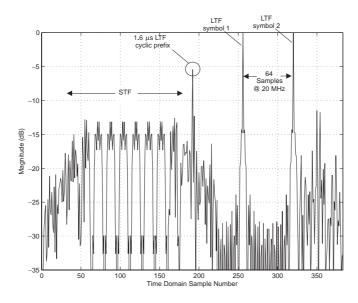

The controller block continuously monitors all the subblocks. Based on the information received by the threshold detector, the controller decides how to configure the multicorrelator. When the multicorrelator is detecting a secondary transmission, the controller configures the coefficients of the filter with the delayed version of the incoming signal. The length of the filter for calculating autocorrelation is 16-tap due to the structure of the preamble in IEEE 802.11a. In this standard, each packet starts with a predefined sequence of bits known as preamble. The preamble consists of two parts, a Short Training Symbol (STS) alongside a Long Training Symbol (LTS). The STS is composed of ten repetitive sequences of bits, each sequence is 16-bit long. Thus, the STS, which also known as Short Training Field (STF), provides a very good autocorrelation properties. The LTS is constructed from two identical 64-bit sequences. The LTS, or Long Training Field (LTF), provides more robust properties for exact timing acquisition [34]. Figure 2.6 illustrates the correlation characteristics of the preamble. The controller can simply configure the filter to compute the autocorrelation function by redirecting the incoming signal to the coefficients of the filter. In a similar way, the controller sets up the filter with regenerated preamble stored in the SRAM.

Figure 2.6: The correlation of the preamble with STS and LTS [35]

#### 2.5.4 FIR Filter Block

As earlier mentioned, the FIR filter is the most resource-hungry and power-consuming block of the synchronizer. Therefore, we put our best effort to carefully design the filter to minimize the hardware costs. As previously studied, NC-OFDM-based CR should gather as much information about the spectrum as possible. Hence, the CR receiver has to employ a very large order of the FIR filter in the synchronizer (e.g. 4096-tap filter). Although having such a high-order FIR filter is feasible, it raises serious issues from the hardware limitations point of view. The first concern is the limited silicon area. Another problem is the massive energy consumption of the high-order filters due to performing a large number of complex Multiply-Accumulate (MAC) operations. In addition, a high-order filter has the potential to degrade the overall performance of the whole system when some crucial considerations are ignored during the design time. In the following, we will explain some techniques in order to overcome the above-mentioned issues to some extent.

An FIR filter periodically calculates the MAC operation as Equation 2.1

$$y(n) = c(n) * x(n) = \sum_{k=0}^{N-1} c(k)x(n-k)$$

(2.1)

where the y(n) is the filter response, comprising the sum of products of a set of conjugated coefficients c(k) with the filter input x(n-k) delayed by k samples, on a window whose length is N. Therefore, we will have the complex operation as Equation 2.2

$$(Re_1 + Im_1i) \times (Re_2 - Im_2i) = Re_1(Re_2 - Im_2i) + Im_1i(Re_2 - Im_2i)$$

$$= Re_1Re_2 - (Re_1Im_2)i + (Re_2Im_1)i - (Im_1Im_2)i^2$$

$$= Re_1Re_2 + Im_1Im_2 + (Re_2Im_1 - Re_1Im_2)i$$

(2.2)

where  $Re_1Re_2 + Im_1Im_2$  and  $Re_2Im_1 - Re_1Im_2$  are the Real and Imaginary calculations of the I/Q signals, respectively. By taking Equation 2.2 into consideration, we can figure out that an N-tap complex FIR filter requires  $2 \times N$  multipliers, as well as  $(2 \times N) - 1$  adders to compute the final results. On the other hand, implementing a multiplier requires more hardware resources than an adder. Additionally, the hardware implementation of the multiplier is very much slower than the adder, as well. Therefore, there have been some studies on the possibility to replace a multiplier with the cost of inserting additional adders. Karatsuba multiplication [36] as well as the Golub's method [37] were two famous multiplication methods in which a multiplier can be replaced by three adders. In Karatsuba multiplication, if we assume  $P = (Re_1 + Im_1) \times (Re_2 - Im_2)$ ,  $R = Re_1Re_2$  and  $I = Im_1Im_2$ , we will generate the Equation 2.3 as follows:

$$P = (Re_1 + Im_1) \times (Re_2 - Im_2)$$

$$= Re_1 Re_2 + Re_2 Im_1 - Re_1 Im_2 - Im_1 Im_2$$

$$= R + Re_2 Im_1 - Re_1 Im_2 - I$$

$$Re_2 Im_1 - Re_1 Im_2 = P - R + I$$

(2.3)

Then, the Equation 2.4 is derived as:

$$(Re_1 + Im_1i) \times (Re_2 - Im_2i) = (R - I) + (P - R + I)i$$

$$= Re_1Re_2 + Im_1Im_2$$

$$+ [(Re_1 + Im_1)(Re_2 - Im_2) - Re_1Re_2 + Im_1Im_2]i$$

(2.4)

Golub's method can be derived in a similar way to the Karatsuba's as Equation 2.5

$$(Re_1 + Im_1i) \times (Re_2 - Im_2i) = [(Re_1 + Im_1)(Re_2 + Im_2) - Re_1Im_2 - Re_2Im_1] + (Re_2Im_1 - Re_1Im_2)i$$

(2.5)

At first glance, both methods require 5 multipliers, the multiplication results for both  $Re_1Re_2$  and  $Im_1Im_2$  are computed once, though. Hence, we can reuse those results in the other section of the equation.

All these efforts try to replace only one multiplier with the cost of some adders. It is mainly because of that implementing a complex FIR filter is potentially 4 times more hardware resource expensive than a real-valued FIR filter. In the next section, we will investigate which one of these methods is the most suitable one for the target FPGA device.

Technically, the proposed multicorrelator operates in two different modes. First one is the high-precision mode in which the multicorrelator employs a MAC-based FIR filter and the second mode is the low-precision mode in which the multicorrelator degrades the precision of the filter using a MultiplierLess (ML) method. The multicorrelator reconfigures the FIR filter block on-the-fly using high-precision alongside the low-precision mode to compute crosscorrelation and autocorrelation functions, respectively. These two modes are further inspected in the following subsections.

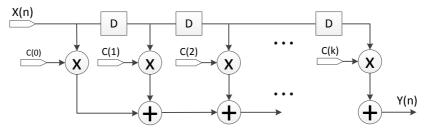

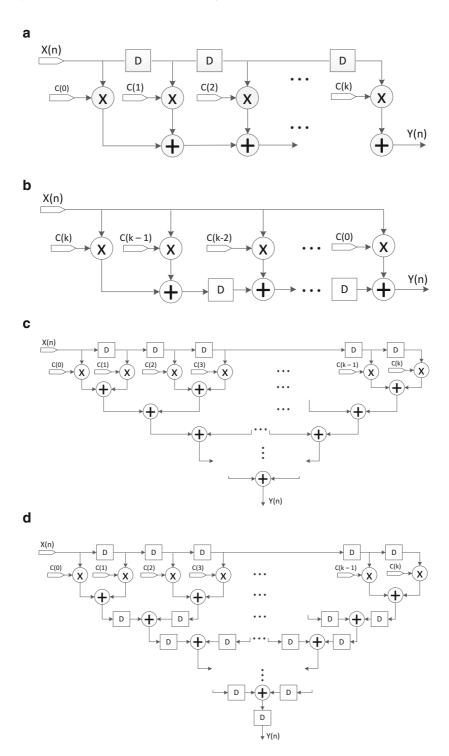

#### 2.5.4.1 MAC-Based FIR Filter Architecture

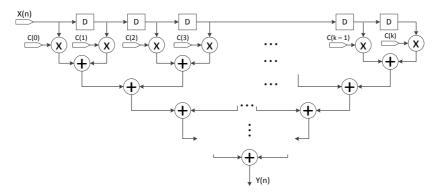

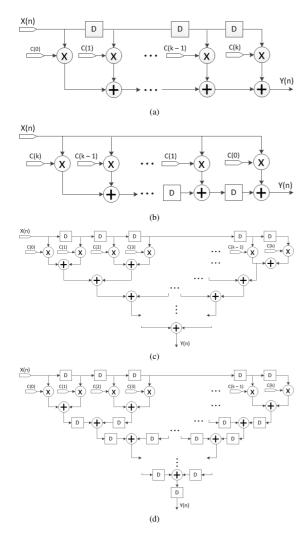

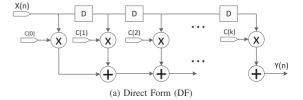

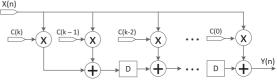

In principle, FIR filters are constructed from three fundamental blocks known as multipliers, adders and delay elements. These three blocks can be integrated together in different shapes, each of them calculates the Equation 2.1. The most straightforward structure for the FIR filters is the Direct Form (DF) architecture. In DF, the input is propagated through the delay elements as Figure 2.7a depicts. The DF architecture heavily suffers from the long critical path in a design with a high-order FIR filter. For example, the critical path for a 256-tap FIR filter is equal to  $T_{crit.} = T_m + (255 \times T_a)$ , where the  $T_m$  and  $T_a$  are units of time required by the multiplier and adder to compute the corresponding results, respectively. Hence, we do not study this structure any further and just present some preliminary results after the synthesis in section 2.8.1.

Figure 2.7b is a well-known enhanced form of the DF architecture which is widely known as Transposed Direct Form (TDF). Technically, the main difference between TDF and DF is only the change in the location of the delay elements, as well as inverting the coefficient elements. Irrespective of the order of the FIR filter, the critical path of the TDF is always  $T_{crit.} = T_m + T_a$  since the delay elements cut the long critical path introduced in high-order filters. However, the TDF architecture may suffer from the long interconnection problem

(a) The DF architecture suffers from the long critical path

(b) The TDF architecture mitigates the critical path, but potentially suffers from long input interconnection

Figure 2.7: The most common forms of the FIR filter [P. II] © Elsevier, 2016.

in the input path of a filter with a large number of taps. Moreover, TDF architecture is not capable of employing ternary adders due to the nature of its structure. We will explain when and where employing ternary adders are useful in section 2.7 in detail.

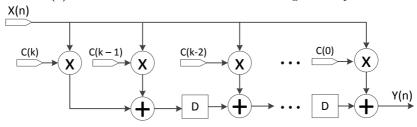

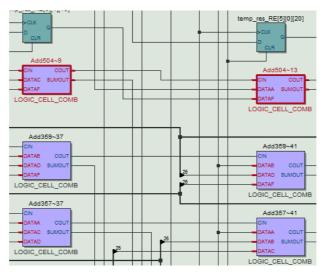

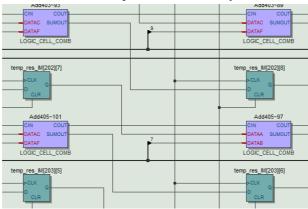

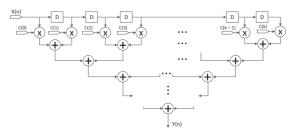

Since both DF and TDF architectures have some critical issues in high-order filter designs, we further investigate two other candidates to mitigate the long critical path, introduced in DF, along with the long interconnection problem, which is potentially introduced in TDF. These two methods are known as Parallel Direct Form (PDF) and Pipelined-Parallel Direct Form (PPDF). Figure 2.8 presents the PDF architecture which is another alteration to the DF format. Instead of employing a serial chain of adders, the PDF uses a specific structure similar to binary adders tree in which all the branches are processed in parallel. Hence, the critical path is limited to  $T_{crit} = T_m + (\lceil \log_2^N \rceil \times T_a) = T_m + (8 \times T_a)$  for the example 256-tap FIR filter. This architecture does not introduce a long critical path, while it distributes the long interconnection through the binary tree. Similar to previous architectures, the PDF form has its own disadvantages of which hardware implementation complexity is one of the major ones.

The PPDF shown in Figure 2.9 is an enhanced form of the PDF structure in which all the branches are pipelined. Although both critical path and long interconnection problems are mitigated in this structure, the resource usage is heavily increased. The PPDF employs an additional delay element after each addition. Therefore, the critical path will remain at the minimum level of  $T_{crit.} = T_m + T_a$ . This architecture also has the same design complexity as of the PDF, alongside using a huge amount of hardware resources. Furthermore, this architecture cannot exploit ternary adders due to the nature of its structure. Further explanation about the ternary adders are given in section 2.8.2 in detail.

Figure 2.8: The PDF architecture uses a binary adder tree shape [P. II] © Elsevier, 2016.

Figure 2.9: The PPDF architecture employs a bunch of delay elements to minimize both the critical path and the interconnections [P. II] © Elsevier, 2016.

#### 2.5.4.2 ML-Based FIR Filter

The ML-based FIR filters have recently attracted more researchers since it requires a very low amount of hardware resources. The ML is an approximate computing technique where the most of the computations are mitigated [38]. In the context of the FIR filters, the coefficient multipliers are replaced by adders and shift elements, while the coefficients are represented in a form of summed powers of 2. According to Saha et al., experiences with MATLAB reveal that a sign bit correlation (instead of a full MAC operation) between the filter input and coefficients, provide sufficient accuracy to detect the secondary transmitter (autocorrelation) even in low SNR regions [29, 30]. In either case, the total number of registers, multiplier, and adders are dramatically decreased. Furthermore, the energy consumption of an ML-based correlator is massively lower than the MAC-based ones since a significant number of intensive MAC operations are mitigated. We will further investigate the overall results later on in section 2.8. We also observed that the hardware implementation of the sign bit correlation was successful to detect the secondary transmitter. Implementing an ML-based FIR filter is very straightforward without introducing additional complexity to the design. Hardware implementation of the sign-bit correlator is a simple XOR or XNOR gate depending on the designer's choice. Although the ML-based FIR filter presents satisfactory results to perform autocorrelation

function, it still requires more practical studies in the field of communications since it is an approximate computing method.

## 2.6 Partial Reconfiguration

Partial Reconfiguration is a powerful ability available on some of the FPGA devices in which a particular part of the FPGA can be reconfigured, while the remaining parts are operating normally. Partial Reconfiguration was first available on Xilinx XC6200 devices in 1995 [39]. Later on in mid-2010, Altera Corporation announced that their newly released 28nm Stratix V FPGA was equipped with a friendly method to do PR [40]. The PR is a specific feature which enables particular portions of the FPGA to be reconfigured on-the-fly without disrupting rest of the circuit during the run-time. This feature reserves a portion of the FPGA to perform PR on that region. The PR region may have different configurations, as well as the functionality, while everything else outside of this region has a normal operation. It implies that the PR region is dynamically changed, while the remaining portions of the FPGA are static.

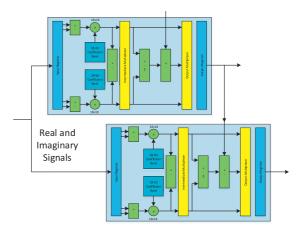

In this work, the synchronizer employs the PR feature to reconfigure itself to either perform autocorrelation or crosscorrelation functions on demand. Figure 2.10a illustrates an example of the multicorrelator infrastructure when it is (re)configured to perform autocorrelation function. In the same figure, the PR region consists of three identical multicorrelators. Three is the maximum number of multicorrelators that our target FPGA device allows implementing on hardware due to the resource constraints. Nevertheless, fewer multicorrelators can be assigned in PR region depending on the application, as well as the FFT window. Furthermore, the multicorrelator is (re)configured to detect any secondary transmission. Therefore, each multicorrelator is (re)configured with ML-based FIR filters. On the other hand, there are plenty of resources dedicated to each multicorrelator in the PR region, because each multicorrelator should also be able to perform crosscorrelation function in the following steps. In addition, since the ML-based technique is a very low-cost approach, each multicorrelator has sufficient resources available to perform autocorrelation on a wide-band spectrum. How wide a multicorrelator can be is totally dependent to other parameters such as the spectrum, FFT window, etc.

Figure 2.10b illustrates a scenario in which two multicorrelators have detected a secondary transmission, while the remaining one has failed to detect. In this example, the first multicorrelator alongside the third one is configured to perform crosscorrelation between the buffered version of the incoming signal and the regenerated time-domain preambles. Meanwhile, the CR can decide what the second idle multicorrelator should do. For instance, the CR might allow the idle multicorrelator to keep sensing the spectrum or release the hardware resources dedicated to the second multicorrelator for other purposes, e.g. hardware accelerators. Once the connection is disrupted, the PR region is reconfigured for all the multicorrelators to perform autocorrelation function and this circulation will be continued.

Another advantage of using PR feature is to set up a multi-standard receiver. Reconfiguration on-the-fly provides the ability to load various IEEE standards on the system, at will. For example, a single receiver can set up its parameters to operate in a variety of IEEE standards (such as 802.11, 802.15, 802.22, etc) without a single change in the hardware. Using PR feature enables such a CR to be more versatile and powerful than ever.

(a) The autocorrelation function

(b) The crosscorrelation function

Figure 2.10: The infrastructure of the multicorrelator when employs Partial Reconfiguration feature to perform either autocorrelation or crosscorrelation functions on demand [P. II] © Elsevier, 2016.

#### 2.7 FPGA Constraints

In this section, we further inspect the hardware implementation, as well as the obstacles one might encounter during the implementation. Although NC-OFDM-based CR brings a variety of advantages, it has its own challenges and constraints. Some of the most important hardware constraints are inspected as follows.

#### 2.7.1 Insufficient DSP Blocks

Technically, today's FPGAs are equipped with several DSP blocks depending on the family board. DSP blocks can implement chain adders, multipliers and a combination of both (MAC operations) on the hardware. Practically, DSPs are used to calculate

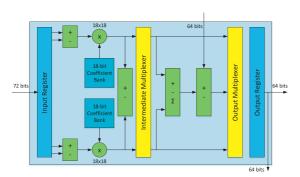

**Figure 2.11:** How the Stratix V cascades two DSP blocks to compute a complex multiplication [P. II] © Elsevier, 2016.

computationally intensive tasks such as digital filtering algorithms. However, such as other hardware elements, DSP blocks are finite hardware resources. Hence, utilizing a DSP block as much as possible is a very important issue from the hardware point of view. Depending on the FPGA technology, each DSP block tries to perform the MAC operation in the best efficient way. For example, DSP blocks on the Stratix II and Stratix III FPGA devices of the Altera Corporation are designed to compute Karatsuba algorithm more efficient than the conventional method [41]. In contrast to the above-mentioned FPGA families, Stratix V provides a different mode to calculate MAC operations. Additionally, Stratix V have a specific mode in the DSP structure to compute complex multiplication as the traditional method [42]. As we practically observed, DSP blocks of a Stratix V board are utilized more efficiently in the traditional method than neither Gulob's method nor Karatsuba's algorithm. Numerically, each complex multiplication requires two cascaded DSP blocks whereas three DSP blocks are required in both Gulob's and Karatsuba's methods. Figure 2.11 presents the infrastructure of a DSP block available on Stratix V series, as well as how the board cascades two DSPs to compute a complex multiplication.

The FPGA board we employed for prototyping is the Altera FPGA Stratix V family, series "5SGSMD5K2F40C2N". The maximum number of available DSP blocks for this series is 1590 units. Moreover, each multicorrelator is able to perform crosscorrelation on an FFT window size of 256. As mentioned above, each complex multiplication requires 2 DSP blocks to compute the result. Hence, each multicorrelator demands  $256 \times 2 = 512$  DSP blocks to operate normally. Therefore, the target FPGA device does not allow the designer to implement more than three multicorrelators. This is the first limitation for such a platform from the hardware point of view. However, there are two approaches to tackle the insufficient DSP problem. A very straightforward solution is to enforce the synthesis tool to implement the MAC operation on look-up tables instead of implementing in the DSP. This method has the potential to increase hardware resources up to 10 times more, while the MAC operation is executed much slower than when the DSP block computes the results. Another alternative is to degrade the filter precision. For example, one can

employ several 64-tap FIR filters instead of employing a 256-tap one. This method is also heavily dependent on the application, as well as the environment.

#### 2.7.1.1 Silicon Area

The silicon area is another concern in such large designs. On FPGA, silicon area is translated to advanced look-up table based units that form the combinatorial logic of the design. As previously mentioned, the FIR filter is the most resource-hungry block in the synchronizer. In the previous subsection, we studied that the DSP blocks are very limited. In addition, a high-order FIR filter will also exhaust other fundamental components, such as registers. As the order of the filter becomes larger, the more hardware resources are required. Potentially, an FIR filter with a large number of taps can occupy most of the available hardware resources on the target FPGA. It does not allow to implement other fundamental components of a CR receiver, e.g. FFT, on the same FPGA die.

#### 2.7.1.2 Power Consumption

The total power consumption is mainly depending on three major parameters known as static power  $(P_s)$ , dynamic power  $(P_d)$  and Input/Output (I/O) power  $(P_{io})$ . Static power is the power required to operate the FPGA when there is no activity on the circuit. Therefore, the  $P_s$  is almost constant in each design.  $P_d$  is the power consumed when there is an activity on the circuit and transistors are toggling and parasitic capacitors are charged and discharged.  $P_{io}$  is a magnitude of the power required for a signal to start from the input, traverses the design and finally reaches to the output. Design issues such as long critical path, long interconnections, and bad hardware description have a proportional effect on  $P_d$  along with the  $P_{io}$ . As previously explained, a high-order FIR filter has the potential to carry all the mentioned design issues which proportionally increase the overall power consumption of the design.

## 2.8 Experimental Results with Further Discussion

The explained synchronizer block was described using VHDL description language; it was simulated using ModelSim software and synthesized using Quartus II 12.1 and 15.1 environments. Eventually, the synthesized design was implemented on Stratix V FPGA device speed grade 2 series. We achieved a preliminary result for each configuration and, then, we tried to improve the candidates by imposing some optimization techniques explained in next subsection. The preliminary results are reported by Quartus II 12.1, whereas the final results are achieved by Quartus 15.1.

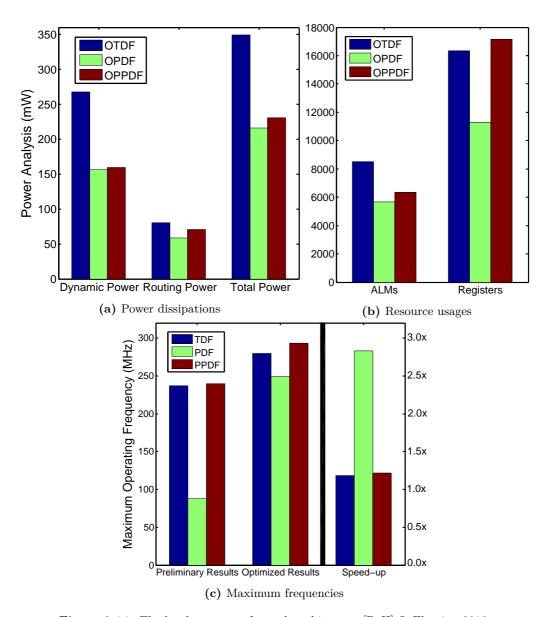

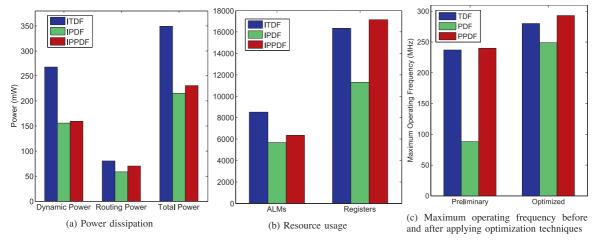

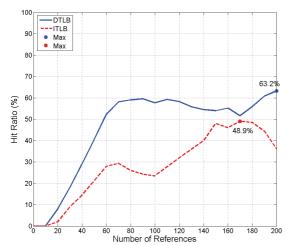

#### 2.8.1 Preliminary Results

Table 2.1 shows the preliminary results after synthesizing the multicorrelator configured with specifically mentioned FIR filter structures in terms of employing Adaptive Logic Modules (ALMs), DSP blocks, and registers, as well as the maximum achieved operating frequencies. The TDF configuration shows satisfactory results for the multicorrelator configured with a 256-tap FIR filter. The DF architecture requires almost the same amount of hardware resources as TDF, but the maximum operating frequency is not acceptable. Although the PDF architecture requires only about half of the resource elements and registers compared to the mentioned architectures, it seems that the long interconnection in binary adder tree does not allow this architecture to achieve better results than DF.

|                          | TDF    | DF     | PDF  | PPDF   | ML   |

|--------------------------|--------|--------|------|--------|------|

| Logic Utilization (ALMs) | 12,483 | 12,490 | 7504 | 14,611 | 1876 |

| Total DSP Blocks         | 512    | 512    | 512  | 512    | 0    |

| Total Registers          | 16,378 | 16,883 | 8873 | 28,037 | 2886 |

| Max. Freq. [MHz]         | 237    | 68     | 88   | 240    | 257  |

**Table 2.1:** Preliminary results for the multicorrelator with different configurations [P. II] © Elsevier, 2016.

**Table 2.2:** Power Consumption Analysis (mW) [P. II] © Elsevier, 2016.

|               | TDF     | DF      | PDF     | PPDF    | $\mathbf{ML}$ |

|---------------|---------|---------|---------|---------|---------------|

| I/O Power     | 22.58   | 2108.14 | 33.92   | 22.86   | 26.20         |

| Dynamic Power | 344.17  | 200.59  | 265.89  | 160.10  | 9.42          |

| Static Power  | 1070.06 | 1062.71 | 987.12  | 955.80  | 951.50        |

| Total Power   | 1436.82 | 3371.43 | 1286.92 | 1138.75 | 937.13        |

The PPDF configuration requires slightly more logic than the TDF and DF, while the total number of registers is massively increased. Eventually, a multicorrelator with the ML-based FIR filters shows that it can be the best candidate to perform autocorrelation function.

Power dissipation analysis is reported based on the results generated by "PowerPlay Power Analyzer" tool in Quartus II environment. The analyzer reads the Value Change Dump (VCD) file, which contains signal transaction activities, generated by the ModelSim software.

Table 2.2 reports the total power consumption for each configuration. The TDF architecture has a higher dynamic power consumption than the other configurations. The DF has a massive power consumption on its I/O path due to the long critical path. The PDF architecture was successful to resolve the massive I/O power consumption observed in the DF structure. The PPDF is the greenest architecture among the MAC-based designs from the power consumptions point of view. Eventually, the ML architecture once again shows that it is also a good candidate to perform autocorrelation function in terms of overall power consumption.

#### 2.8.2 Optimization Techniques and Final Results

In this subsection, we will not study the DF architecture due to showing unacceptable preliminary results, as well as the ML approach since it is not a robust algorithm for computing crosscorrelation function. It is worth to recall that since computing crosscorrelation is computationally much more intensive than the autocorrelation, we try to minimize the logic utilization, register usage, and power consumption while increasing the maximum operating frequency in other MAC-based candidates. We employed some optimization techniques to improve the final results as follows. Henceforth, we will consider Optimized Transposed Direct Form (OTDF), Optimized Parallel Direct Form (OPDF) and Optimized Pipelined-Parallel Direct Form (OPPDF) as the optimized version of their

previously studied architectures, respectively.

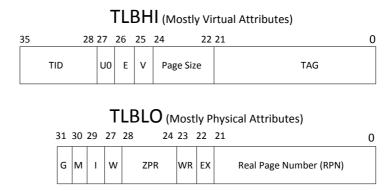

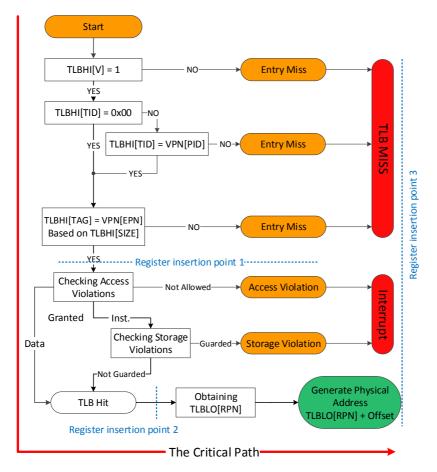

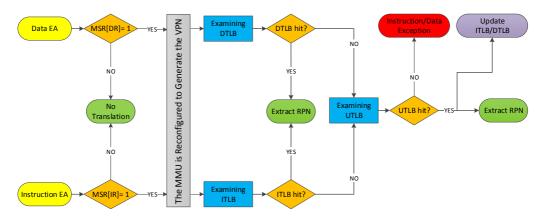

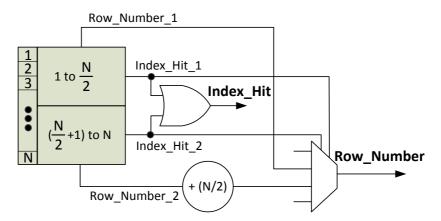

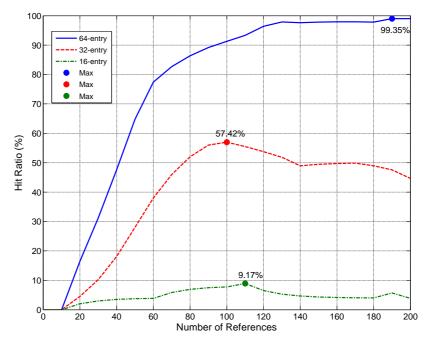

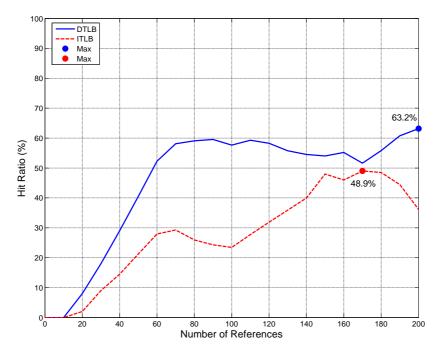

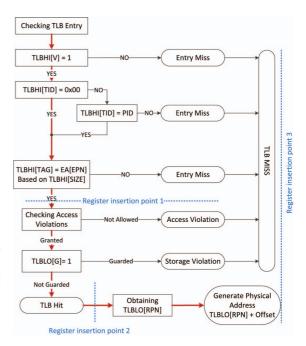

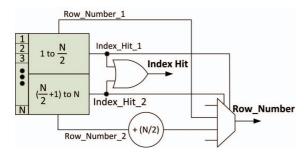

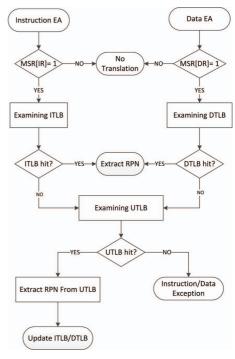

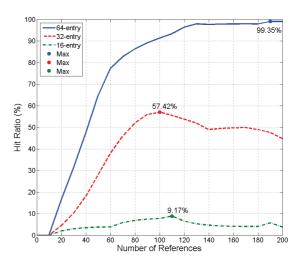

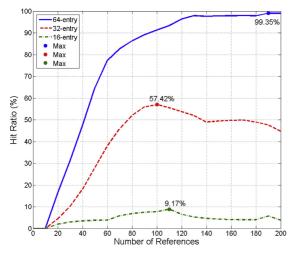

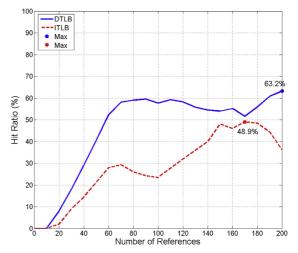

**HDL Modification:** The HDL modification is the foremost step of optimizing a design. We start modifying the codes to mitigate unnecessary registers, shortening the critical path, employing parallelism where applicable, etc.