TAMPEREEN TEKNILLINEN YLIOPISTO TAMPERE UNIVERSITY OF TECHNOLOGY

## **QIUTING WANG** DESIGN AND CONSTRUCTION OF A PLL SYSTEM FOR A 96-MHZ FM TRANSMITTER

Master of Science Thesis

Examiner: University Lecturer Olli-Pekka Lundén and Lecturer Jari Kangas Examiner and topic approved by the Faculty Council of the Faculty of Computing and Electrical Engineering on 31st May 2017

## ABSTRACT

QIUTING WANG: Design and Construction of A PLL System for A 96-MHz FM Transmitter Tampere University of Technology Master of Science Thesis, 54 pages, 3 Appendix pages December 2017 Master's Degree Programme in Electrical Engineering Major: Electronics Examiner: University Lecturer Olli-Pekka Lundén and Lecturer Jari Kangas Keywords: phase-locked loop, crystal oscillator, voltage-controlled oscillator, frequency divider, phase detector, loop filter

The phase-locked loop (PLL) is used as frequency synthesizer in numerous electronic devices. This thesis presents design and construction of a basic PLL system on solderless breadboard, using discrete components and integrated circuits (ICs). The circuitry is designed to synthesize a 96-MHz sinusoidal signal, which can be used as the carrier wave for an FM transmitter. The circuitry includes a 24-MHz crystal oscillator (XO), a 96-MHz voltage-controlled oscillator (VCO), two frequency dividers, a phase detector (PD), and a loop filter (LF). In addition, a buffer amplifier is placed before each frequency divider for diminishing spurious frequencies. The XO provides 24-MHz reference frequency while the VCO is tunable between 86 MHz and 100 MHz. The constructed PLL system is able to lock the VCO frequency to 96 MHz.

In this thesis, fundamental knowledge related to PLL is reviewed, and all building blocks of the PLL system are studied and analyzed. The challenges on utilizing IC chips are also discussed. Therefore this work provides a guide and reference for similar works and future study. For further research, the method of eliminating spurious frequencies and improving loop stability could be explored deeper to optimize the PLL performance.

## PREFACE

Although this work took longer time than expected, I feel very glad that it was completed finally. I would like to thank my supervisors and examiners, Olli-Pekka Lundén and Jari Kangas, for offering me so many helpful suggestions and a variety of assistance, either on lab work or on thesis writing. I would also like to thank my parents and friends for always supporting and encouraging me.

Tampere, 20th December 2017

Qiuting Wang

# CONTENTS

| 1. Introduction                                                    | . 1  |

|--------------------------------------------------------------------|------|

| 2. Background                                                      | . 3  |

| 2.1 Commonly used units                                            | . 3  |

| 2.2 The development of PLL                                         | . 4  |

| 2.2.1 The History of PLL                                           | . 4  |

| 2.2.2 The classification of PLL                                    | . 4  |

| 2.3 The building blocks of PLL                                     | . 4  |

| 2.3.1 Crystal oscillators                                          | . 5  |

| 2.3.2 Voltage-controlled oscillators                               | . 9  |

| 2.3.3 Frequency dividers                                           | . 12 |

| 2.3.4 Phase detectors                                              | . 14 |

| 2.3.5 Loop filters                                                 | . 21 |

| 2.4 The control theory of PLL and key parameters                   | . 22 |

| 3. Block design, construction and testing                          | . 26 |

| 3.1 Crystal oscillator design, construction and testing            | . 26 |

| 3.2 Voltage-controlled oscillator design, construction and testing | . 29 |

| 3.3 Frequency divider design, construction and testing             | . 34 |

| 3.4 Phase detector design, construction and testing                | . 36 |

| 3.5 Loop filter design, construction and testing                   | . 41 |

| 4. Results and analysis                                            | . 43 |

| 4.1 Analysis of the phase detector                                 | . 43 |

| 4.2 Analysis of the frequency divider                              |      |

| 4.3 Measurement results                                            |      |

| 5. Conclusions                                                     |      |

|                                                                    |      |

| References                                                         |      |

| APPENDIX A. Measurement setups                                     | . 55 |

| APPENDIX B. | VCO tuning range | • | • | • | • | • | • | • | • | • | • | • |  | • | • | • | • | • | • | 57 |

|-------------|------------------|---|---|---|---|---|---|---|---|---|---|---|--|---|---|---|---|---|---|----|

# LIST OF FIGURES

| 2.1 A block diagram of PLL                                                 | 5  |

|----------------------------------------------------------------------------|----|

| 2.2 The concept of most electronic oscillators.                            | 5  |

| 2.3 (a) A quartz crystal and (b) the electronic symbol of quartz crystal.  | 6  |

| 2.4 An equivalent circuit of quartz crystal.                               | 6  |

| 2.5 The magnitude of $Z_{eq}$ as a function of frequency f (generated by   |    |

| Matlab)                                                                    | 7  |

| 2.6 A typical Pierce crystal oscillator circuit.                           | 8  |

| 2.7 A simple crystal oscillator with transistor.                           | 8  |

| 2.8 The topology of three-point oscillator (using MOSFET), (a) with gate   |    |

| grounded, (b) with drain grounded, (c) with source grounded                | 9  |

| 2.9 (a) A Clapp oscillator and (b) a Clapp VCO circuit.                    | 10 |

| 2.10 The characteristic of VCO output frequency.                           | 11 |

| 2.11 D flip-flop symbol.                                                   | 12 |

| 2.12 A D flip-flop composed by logic gates                                 | 12 |

| 2.13 An example sequence diagram of a positive edge-triggered D flip-flop. | 13 |

| 2.14 (a) The diagram of a by-2 divider and (b) the sequence diagram of     |    |

| by-2 divider                                                               | 13 |

| 2.15(a) The diagram of a by-4 divider and (b) the sequence diagram of      |    |

| by-4 divider                                                               | 14 |

| 2.16 A double-balanced diode mixer.                                        | 15 |

| 2.17 The input and output waveforms of double-balanced diode mixer         |    |

| when $\theta_e = 0$                                                        | 15 |

| 2.18 The input and output waveforms of double-balanced diode mixer                   |    |

|--------------------------------------------------------------------------------------|----|

| when $0 < \theta_e < \frac{\pi}{2}$ .                                                | 16 |

| 2.19 The input and output waveforms of double-balanced diode mixer                   |    |

| when $\theta_e = \pi$ .                                                              | 16 |

| 2.20 The input and output waveforms of double-balanced diode mixer                   |    |

| when $\frac{\pi}{2} < \theta_e < \pi$ .                                              | 17 |

| 2.21 The input and output waveforms of double-balanced diode mixer                   |    |

| when $\theta_e = \pi$ .                                                              | 17 |

| 2.22 The $\bar{u}_{pd}$ as a function of $\theta_e$ for double-balanced mixer        | 18 |

| 2.23 Schematic symbol an XOR gate.                                                   | 18 |

| 2.24 The input and output waveform of XOR gate when $\theta_e = 0$                   | 19 |

| 2.25 The input and output waveform of XOR gate when $0 < \theta_e < \frac{\pi}{2}$   | 19 |

| 2.26 The input and output waveform of XOR gate when $\theta_e = \pi/2$               | 20 |

| 2.27 The input and output waveform of XOR gate when $\frac{\pi}{2} < \theta_e < \pi$ | 20 |

| 2.28 The input and output waveform of XOR gate when $\theta_e = \pi$                 | 20 |

| 2.29 The $\bar{u}_{pd}$ as a function of $\theta_e$ for XOR gate.                    | 21 |

| 2.30 An RC low-pass filter.                                                          | 22 |

| $2.31{\rm The\ modeled\ PLL\ loop\ showing\ voltages\ and\ angular\ frequencies.}$   | 22 |

| 2.32 The modeled PLL loop focused on phases.                                         | 23 |

| 3.1 The block diagram of PLL system for this project                                 | 26 |

| 3.2 The designed 24-MHz crystal oscillator circuit.                                  | 27 |

| 3.3 The redrawn crystal oscillator circuit.                                          | 28 |

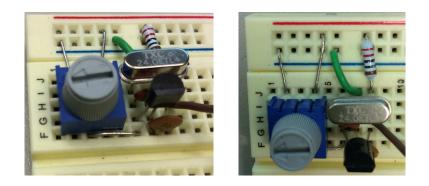

| 3.4 The constructed 24-MHz crystal oscillator circuit.                               | 28 |

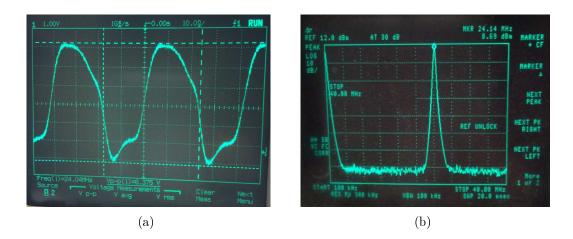

| 3.5 (a) The output signal of XO observed through oscilloscope and (b)                |    |

| observed through spectrum analyzer.                                                  | 28 |

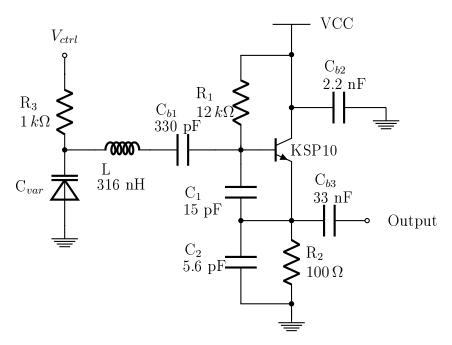

| 3.6 The designed 96-MHz VCO circuit.                                               | 29 |

|------------------------------------------------------------------------------------|----|

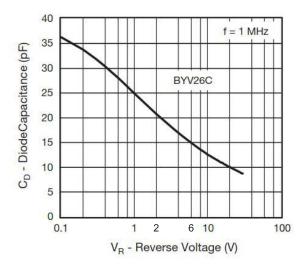

| 3.7 The diode capacitance of BYV26C as a function of its reverse voltage.          | 30 |

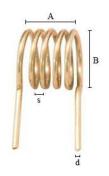

| 3.8 An air-wound coil.                                                             | 30 |

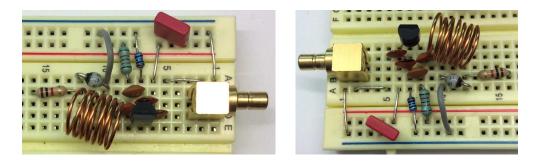

| 3.9 The constructed 96-MHz VCO circuit.                                            | 32 |

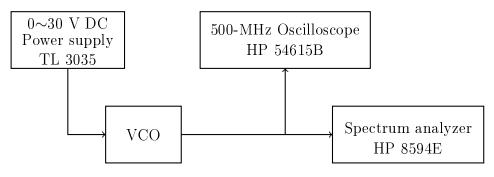

| 3.10 Measurement setup for VCO test.                                               | 32 |

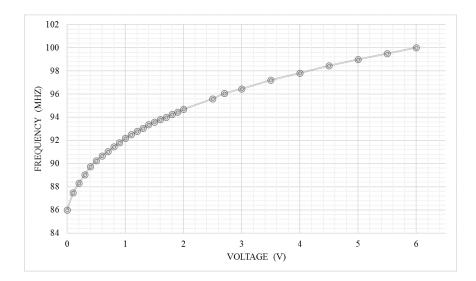

| 3.11 The output frequency of the VCO $(f_o)$ as a function of input control        |    |

| voltage $(V_{ctrl})$ .                                                             | 32 |

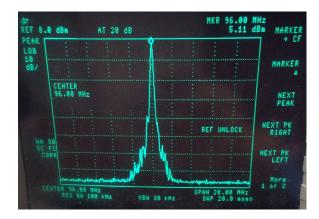

| 3.12 The VCO output measured by spectrum analyzer with 2.7-V $V_{ctrl}.$ .         | 33 |

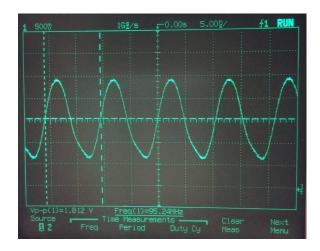

| 3.13 The output waveform of 96-MHz VCO circuit observed through os-                |    |

| cilloscope                                                                         | 33 |

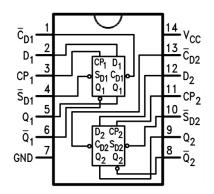

| 3.14 The pin diagram of 74AC74.                                                    | 34 |

| 3.15 The connection diagram of by-4 divider.                                       | 35 |

| 3.16 The connection diagram of by-16 divider.                                      | 36 |

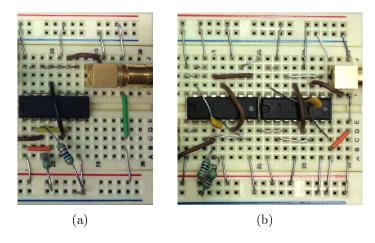

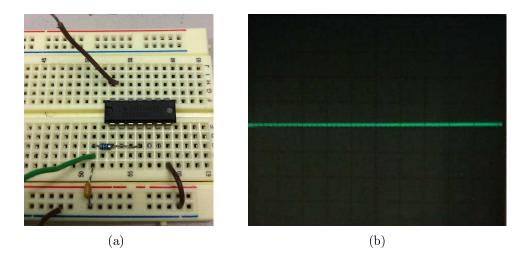

| 3.17 (a) The constructed by-4 divider for XO and (b) the constructed by-           |    |

| 16 divider for VCO.                                                                | 36 |

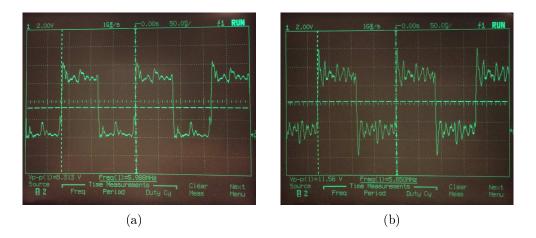

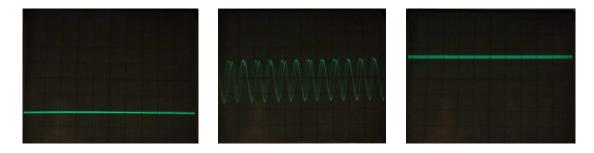

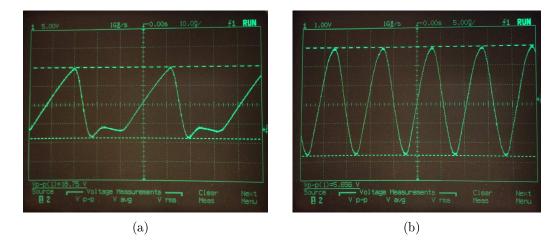

| 3.18 (a) Divided XO signal and (b) divided VCO signal.                             | 37 |

| 3.19 The schematic for phase detector testing.                                     | 37 |

| 3.20 The input and output waveform of phase detector.                              | 38 |

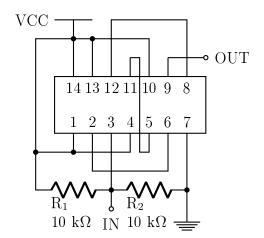

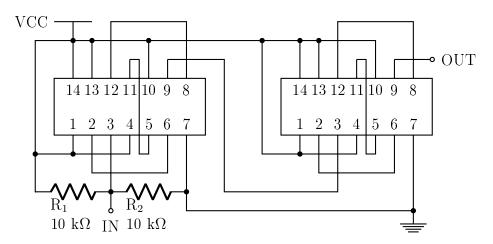

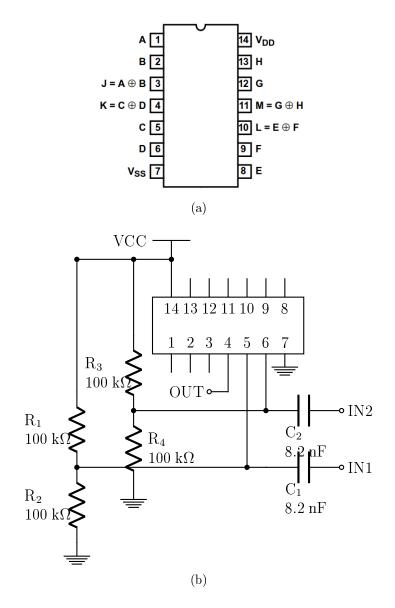

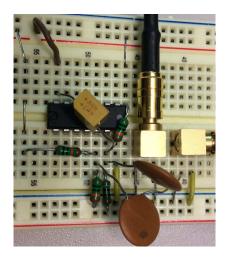

| 3.21 (a) The pinouts of CD4070BE and (b) the connection way of CD4070BE            |    |

| in this project.                                                                   | 39 |

| 3.22 The constructed phase detector.                                               | 39 |

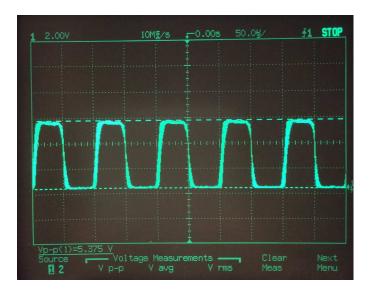

| 3.23 The output waveform of detecting two signals of 6 MHz (seconds/di-            |    |

| vision 50 ns, volts/division 2 V).                                                 | 40 |

| $3.24\mathrm{The}$ output waveform of detecting two signals of 10 kHz (seconds/di- |    |

| vision 50 $\mu$ s, volts/division 2 V).                                            | 40 |

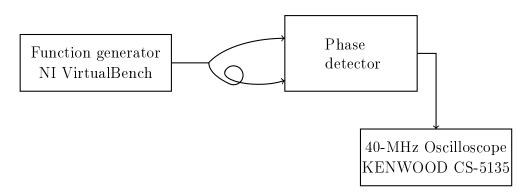

| $3.25$ Measurement setup for measuring $K_d$ .                                     | 40 |

| 3.26 The RC low-pass filter.                                                                 | 41 |

|----------------------------------------------------------------------------------------------|----|

| 3.27 (a) The constructed LPF circuit and (b) the output waveform of LPF                      |    |

|                                                                                              | 42 |

|                                                                                              |    |

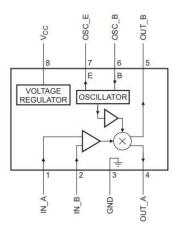

| 4.1 The diagram of SA602A.                                                                   | 44 |

| 4.2 (a) The connection way of SA602A for testing, and (b) the con-                           |    |

| structed circuit of SA602A for testing.                                                      | 45 |

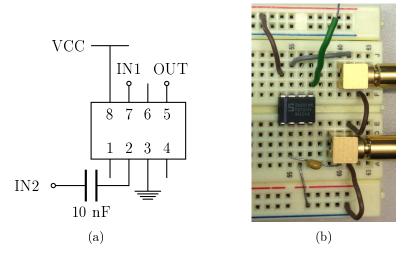

| 4.3 The output waveforms of SA602A when detecting two 1-MHz signals                          |    |

| (volts/division 0.5 V, seconds/division 0.5 $\mu$ s, lowest line as ground                   |    |

| level).                                                                                      | 45 |

| 4.4 The output waveforms of CD4070BE when detecting two 1-MHz sig-                           |    |

| nals (volts/division 2 V, seconds/division 1 $\mu$ s, lowest line as ground                  |    |

| level)                                                                                       | 46 |

| 4.5 The average voltage $\bar{u}_{pd}$ as a function of phase error $\theta_e$ for CD4070BE. | 46 |

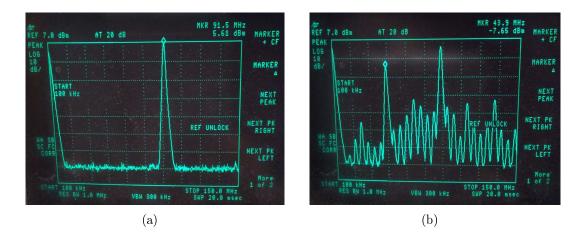

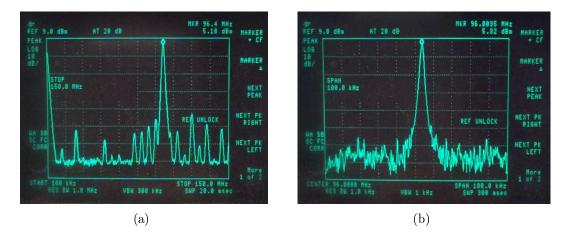

| 4.6 (a) The spectrum of VCO output when VCO works independently                              |    |

| and (b) the spectrum of VCO output when VCO works with divide-                               |    |

| by-16 circuit.                                                                               | 47 |

| 4.7 (a) The spectrum of XO output when XO works independently and                            |    |

| (b) the spectrum of XO output when XO works with divide-by-4 circuit.                        | 47 |

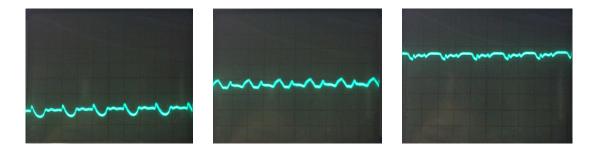

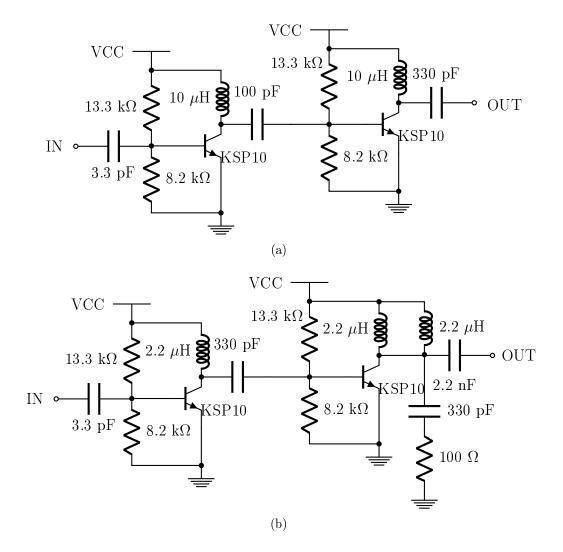

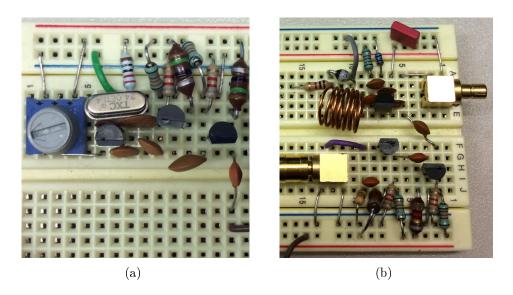

| 4.8 (a) The buffer circuit for XO and (b) the buffer circuit for VCO 4                       | 48 |

| 4.9 (a) The XO with its buffer and (b) the VCO with its buffer. $\ldots$                     | 48 |

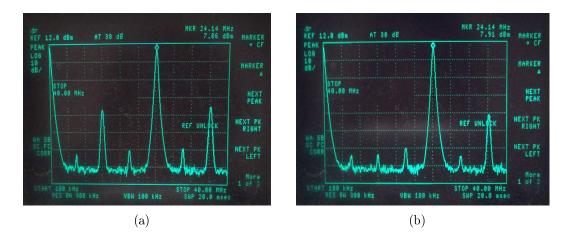

| 4.10 (a) The spectrum of XO working without buffer and (b) the spectrum                      |    |

| of XO working with buffer                                                                    | 49 |

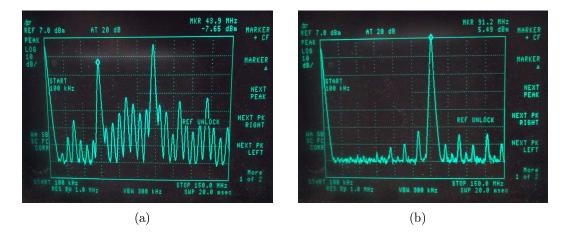

| 4.11(a) The spectrum of VCO when working without buffer and (b) the                          |    |

| spectrum of VCO when working with buffer.                                                    | 49 |

| 4.12 (a) The amplified XO output and (b) the amplified VCO output.                           | 49 |

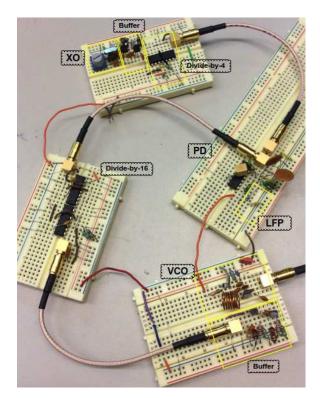

| 4.13 The block diagram of whole PLL system.                                                  | 50 |

| 4.14 The completed PLL circuitry.                                                            | 50 |

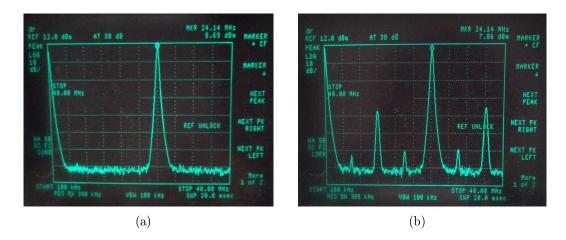

| [ | 4.15 The spectrum of VCO output at locked state: (a) with 150-MHz span |    |

|---|------------------------------------------------------------------------|----|

|   | and (b) with 100-kHz span. $\ldots$                                    | 51 |

# LIST OF TABLES

| 2.1 | The truth table of a positive triggered D flip-flop.     | 13 |

|-----|----------------------------------------------------------|----|

|     |                                                          |    |

| 2.2 | The truth table of an XOR gate.                          | 18 |

|     |                                                          |    |

| 3.1 | Measured parameters of 24-MHz crystal oscillator circuit | 29 |

|     |                                                          |    |

| 3.2 | Measured parameters of 96-MHz VCO circuit.               | 34 |

| 3.3 | The truth table of 74AC74.                               | 35 |

| 3.4 | The result of detecting two 4.8-MHz square waves         | 41 |

|     |                                                          |    |

| 4.1 | Transition time and propagation delay time of CD4070BE   | 43 |

# LIST OF ABBREVIATIONS AND SYMBOLS

| PLL                                                                                                                                                                                                                                 | phase-locked loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCO                                                                                                                                                                                                                                 | voltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $\mathrm{FM}$                                                                                                                                                                                                                       | frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XO                                                                                                                                                                                                                                  | crystal oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PD                                                                                                                                                                                                                                  | phase detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| m LF                                                                                                                                                                                                                                | loop filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IC                                                                                                                                                                                                                                  | integrated circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $\operatorname{RF}$                                                                                                                                                                                                                 | radio frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RMS                                                                                                                                                                                                                                 | root mean square                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LPLL                                                                                                                                                                                                                                | linear phase-locked loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DPLL                                                                                                                                                                                                                                | digital phase-locked loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ADPLL                                                                                                                                                                                                                               | all-digital phase-locked loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPLL                                                                                                                                                                                                                                | software phase-locked loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| APLL                                                                                                                                                                                                                                | analog phase-locked loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LO                                                                                                                                                                                                                                  | local oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IF                                                                                                                                                                                                                                  | intermediate frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LPF                                                                                                                                                                                                                                 | low-pass filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $A_P _{\mathrm{dB}}$                                                                                                                                                                                                                | power gain in dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $A_P _{ m dB} P_{in}$                                                                                                                                                                                                               | power gain in dB<br>input power                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $P_{in}$                                                                                                                                                                                                                            | input power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $P_{in}$<br>$P_L$                                                                                                                                                                                                                   | input power<br>load power                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $P_{in}$<br>$P_L$<br>$A_V _{\mathrm{dB}}$                                                                                                                                                                                           | input power<br>load power<br>voltage gain in dB                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $P_{in}$<br>$P_L$<br>$A_V _{\mathrm{dB}}$<br>$V_{in}$<br>$V_{out}$<br>$P _{\mathrm{dBm}}$                                                                                                                                           | input power<br>load power<br>voltage gain in dB<br>input voltage RMS value                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $P_{in}$<br>$P_L$<br>$A_V _{\mathrm{dB}}$<br>$V_{in}$<br>$V_{out}$                                                                                                                                                                  | input power<br>load power<br>voltage gain in dB<br>input voltage RMS value<br>output voltage RMS value                                                                                                                                                                                                                                                                                                                                                                                        |

| $P_{in}$<br>$P_L$<br>$A_V _{\mathrm{dB}}$<br>$V_{in}$<br>$V_{out}$<br>$P _{\mathrm{dBm}}$                                                                                                                                           | input power<br>load power<br>voltage gain in dB<br>input voltage RMS value<br>output voltage RMS value<br>power in dBm                                                                                                                                                                                                                                                                                                                                                                        |

| $P_{in}$<br>$P_L$<br>$A_V _{dB}$<br>$V_{in}$<br>$V_{out}$<br>$P _{dBm}$<br>$P _{mW}$                                                                                                                                                | input power<br>load power<br>voltage gain in dB<br>input voltage RMS value<br>output voltage RMS value<br>power in dBm<br>power in mW                                                                                                                                                                                                                                                                                                                                                         |

| $P_{in}$<br>$P_L$<br>$A_V _{dB}$<br>$V_{in}$<br>$V_{out}$<br>$P _{dBm}$<br>$P _{mW}$<br>$V_{eff}$                                                                                                                                   | input power<br>load power<br>voltage gain in dB<br>input voltage RMS value<br>output voltage RMS value<br>power in dBm<br>power in mW<br>RMS value (effective value) of voltage                                                                                                                                                                                                                                                                                                               |

| $P_{in}$<br>$P_L$<br>$A_V _{dB}$<br>$V_{in}$<br>$V_{out}$<br>$P _{dBm}$<br>$P _{mW}$<br>$V_{eff}$<br>$V_{pp}$                                                                                                                       | input power<br>load power<br>voltage gain in dB<br>input voltage RMS value<br>output voltage RMS value<br>power in dBm<br>power in mW<br>RMS value (effective value) of voltage<br>peak-to-peak value of voltage                                                                                                                                                                                                                                                                              |

| $P_{in}$<br>$P_L$<br>$A_V _{dB}$<br>$V_{in}$<br>$V_{out}$<br>$P _{dBm}$<br>$P _{mW}$<br>$V_{eff}$<br>$V_{pp}$<br>$\omega_i$                                                                                                         | input power<br>load power<br>voltage gain in dB<br>input voltage RMS value<br>output voltage RMS value<br>power in dBm<br>power in mW<br>RMS value (effective value) of voltage<br>peak-to-peak value of voltage<br>reference (angular) frequency                                                                                                                                                                                                                                             |

| $P_{in}$<br>$P_L$<br>$A_V _{dB}$<br>$V_{in}$<br>$V_{out}$<br>$P _{dBm}$<br>$P _{mW}$<br>$V_{eff}$<br>$V_{pp}$<br>$\omega_i$<br>$\omega_o$                                                                                           | input power<br>load power<br>voltage gain in dB<br>input voltage RMS value<br>output voltage RMS value<br>power in dBm<br>power in mW<br>RMS value (effective value) of voltage<br>peak-to-peak value of voltage<br>reference (angular) frequency<br>VCO output (angular) frequency                                                                                                                                                                                                           |

| $\begin{array}{l} P_{in} \\ P_{L} \\ A_{V} _{\mathrm{dB}} \\ V_{in} \\ V_{out} \\ P _{\mathrm{dBm}} \\ P _{\mathrm{mW}} \\ V_{eff} \\ V_{pp} \\ \omega_{i} \\ \omega_{o} \\ \frac{\omega_{o}}{N} \end{array}$                       | <ul> <li>input power</li> <li>load power</li> <li>voltage gain in dB</li> <li>input voltage RMS value</li> <li>output voltage RMS value</li> <li>power in dBm</li> <li>power in mW</li> <li>RMS value (effective value) of voltage</li> <li>peak-to-peak value of voltage</li> <li>reference (angular) frequency</li> <li>VCO output (angular) frequency</li> <li>divided VCO output (angular) frequency</li> </ul>                                                                           |

| $\begin{array}{l} P_{in} \\ P_{L} \\ A_{V} _{\mathrm{dB}} \\ V_{in} \\ V_{out} \\ P _{\mathrm{dBm}} \\ P _{\mathrm{mW}} \\ V_{eff} \\ V_{pp} \\ \omega_{i} \\ \omega_{o} \\ \frac{\omega_{o}}{N} \\ u_{pd} \end{array}$             | <ul> <li>input power</li> <li>load power</li> <li>voltage gain in dB</li> <li>input voltage RMS value</li> <li>output voltage RMS value</li> <li>power in dBm</li> <li>power in mW</li> <li>RMS value (effective value) of voltage</li> <li>peak-to-peak value of voltage</li> <li>reference (angular) frequency</li> <li>VCO output (angular) frequency</li> <li>divided VCO output (angular) frequency</li> <li>phase detector output voltage</li> </ul>                                    |

| $\begin{array}{l} P_{in} \\ P_{L} \\ A_{V} _{\mathrm{dB}} \\ V_{in} \\ V_{out} \\ P _{\mathrm{dBm}} \\ P _{\mathrm{mW}} \\ V_{eff} \\ V_{pp} \\ \omega_{i} \\ \omega_{o} \\ \frac{\omega_{o}}{N} \\ u_{pd} \\ V_{ctrl} \end{array}$ | <ul> <li>input power</li> <li>load power</li> <li>voltage gain in dB</li> <li>input voltage RMS value</li> <li>output voltage RMS value</li> <li>power in dBm</li> <li>power in mW</li> <li>RMS value (effective value) of voltage</li> <li>peak-to-peak value of voltage</li> <li>reference (angular) frequency</li> <li>VCO output (angular) frequency</li> <li>divided VCO output (angular) frequency</li> <li>phase detector output voltage</li> <li>VCO input control voltage</li> </ul> |

| $C_{var}$             | capacitance of varactor diode        |

|-----------------------|--------------------------------------|

| $\omega_{max}$        | maximum VCO output frequency         |

| $\omega_{min}$        | minimum VCO output frequency         |

| $K_v$                 | VCO gain                             |

| $\Delta \omega_{VCO}$ | VCO tuning range                     |

| $K_n$                 | frequency divider gain               |

| $	heta_n$             | frequency divider output phase       |

| $	heta_e$             | phase difference between two signals |

| $\bar{u}_{pd}$        | average voltage of $u_{pd}$          |

| $K_d$                 | phase detector gain                  |

| $\omega_c$            | cutoff frequency of low-pass filter  |

| au                    | time constant                        |

| $K_{f}$               | loop filter gain                     |

| $	heta_i$             | XO output phase                      |

| $\theta_o$            | VCO output phase                     |

| $\omega_n$            | natural frequency                    |

| ζ                     | damping factor                       |

| $\omega_{cr}$         | lock range (capture range)           |

| $t_L$                 | locking time (settling time)         |

|                       |                                      |

### 1. INTRODUCTION

The phase-locked loop (PLL) is a feedback circuitry that can control an oscillator signal to track a reference signal by locking the phase difference between these two signals into a constant. The oscillator is commonly a voltage-controlled oscillator (VCO), and the phase difference is detected by a phase detector. [I, p.3]

The PLL was invented in 1930s [2], p.6] and it has been extensively utilized in many electronic fields, such as in wireless communication, microprocessor, and navigation. A PLL system can be found for example, in FM (frequency modulation) radios, televisions, computers, and cell phones [3], p.269].

The main applications of PLL system are reproduction of signals (as with noise reduction), modulation and demodulation, plus frequency synthesis. [1, p.3-4] [3, p.270-271]

A signal usually needs to be modulated before being sent out through a transmitter. The object of this work is to design and build a PLL circuitry, which can synthesize a 96-MHz carrier frequency for the purpose of frequency modulation. This PLL system is composed by five building blocks: a 24-MHz crystal oscillator (XO) which offers a reference signal, a 96-MHz VCO, two frequency dividers, a phase detector (PD), and a loop filter (LF). The whole circuitry is constructed on solderless breadboards with discrete components, except an IC (integrated circuit) chip CD4070BE used as PD and three IC chips 74AC74 used as dividers. The 96-MHz output signal can be used for an FM transmitter.

The PLL plays a preliminary but important role in radio frequency (RF) study. This thesis reviews the concept and mechanism of the PLL, presents the construction of each block and records their testing results, therefore providing a guide and reference for similar works and future study. The thesis also compares and discusses the applicability of some IC chips for the studied PLL.

This thesis is organized as follows. Chapter 2 introduces the reader to the fundamentals of PLL, including the development of PLL, the building blocks of PLL, and related control theory. Chapter 3 demonstrates the design of every block, also presents their constructed circuits and measurement results. Chapter 4 analyzes some challenges on the phase detector and the frequency divider, presents the results of whole system, followed by conclusions in Chapter 5.

## 2. BACKGROUND

In this chapter, firstly some commonly used units are mentioned in Section 2.1. The development of phase-locked loop (PLL) is introduced in Section 2.2. Then each building block is explained separately in Section 2.3. Lastly the control theory of PLL is demonstrated in Section 2.4.

#### 2.1 Commonly used units

Decibels (dB) are generally used when describing power and gain [4, p.7]. The power gain is expressed as:

$$A_P|_{\rm dB} = 10\log\frac{P_L}{P_{in}},\tag{2.1}$$

where  $P_{in}$  is the input power and  $P_L$  is the load power.

The voltage gain (assuming the input impedance equals the load impedance) is expressed as:

$$A_V|_{\rm dB} = 20\log\frac{V_{out}}{V_{in}},\tag{2.2}$$

where  $V_{in}$  is RMS (root mean square) value of input voltage and  $V_{out}$  is RMS value of output voltage.

A power level is converted into dBm as:

$$P|_{\rm dBm} = 10 \log \frac{P|_{\rm mW}}{1 \,{\rm mW}},$$

(2.3)

where  $P|_{\rm mW}$  is a power value in mW.

The RMS value (or effective value) of voltage  $V_{eff}$  across 50- $\Omega$  load can be converted into power value as:

$$P|_{\rm dBm} = 10 \log \frac{(V_{eff}|_{\rm V})^2}{50 \,\Omega \times 10^{-3} \,\rm W},\tag{2.4}$$

while for a sinusoidal signal, the relationship between  $V_{eff}$  and peak-to-peak value of voltage  $V_{pp}$  is described as:

$$V_{pp} = 2\sqrt{2} V_{eff}.$$

(2.5)

### 2.2 The development of PLL

This section presents the history and classification of PLL.

#### 2.2.1 The History of PLL

In 1932, a French engineer named *Henri de Bellescize* published a paper in the French periodical *L'Onde Electrique*, presenting the first PLL circuit in the world. This PLL was built based on two vacuum tubes, for the purpose of receiving signals synchronously. However, his work failed to attract public attention at that time. [2], p.6-7]

After about twenty years, the PLL began to be applied as a synthesizer due to the development of color televisions. The popularity of computers also promoted the innovation of PLL. Nowadays, PLL has been utilized in a variety of electronic devices. [2, p.7][5, p.8-9]

### 2.2.2 The classification of PLL

There are primarily four types of PLL at present: linear PLLs (LPLLs), digital PLLs (DPLLs), all-digital PLLs (ADPLLs), and software PLLs (SPLLs). [2, p.8]

LPLLs are also referred as analog PLLs (APLLs), constructed purely by analog components. DPLLs have gradually replaced LPLLs, since 1970's, due to their advantages in system stability. In DPLLs, some parts of the circuitry utilize digital elements. The third type, ADPLLs do not include any analog components. Finally, SPLLs are implemented by software and the PLL function is realized based on programs. [2, p.8]

This work is focusing on DPLLs, hence the following PLLs in this thesis mainly refer to digital PLLs.

### 2.3 The building blocks of PLL

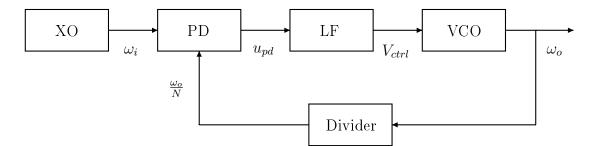

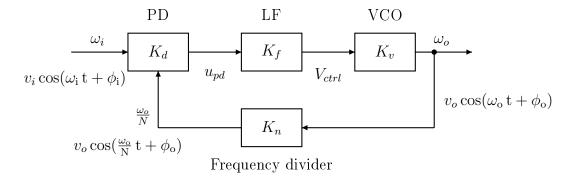

A primary block diagram of PLL is depicted in Figure 2.1 It consists of a crystal oscillator (XO), a voltage-controlled oscillator (VCO), a frequency divider, a phase detector (PD), and a loop filter (LF).

Figure 2.1 A block diagram of PLL.

The XO provides a stable reference (angular) frequency  $\omega_i$ . During the test, it can be replaced by other signal generators. The VCO creates a signal at frequency  $\omega_o$ , which could be several times greater than  $\omega_i$ . This  $\omega_o$  will be divided by N (the division number) through the divider, such that  $\omega_i$  and divided frequency  $\frac{\omega_o}{N}$  are close to each other. The PD compares the phase difference between  $\omega_i$  and  $\frac{\omega_o}{N}$ , outputting a beat signal of voltage  $u_{pd}$ . After the LF, the filtered  $u_{pd}$  becomes  $V_{ctrl}$ that controls the operation of VCO. Eventually,  $\omega_o$  will be adjusted to be identical to  $N\omega_i$  due to this negative feedback loop.

Each block is shortly clarified in the following sections.

#### 2.3.1 Crystal oscillators

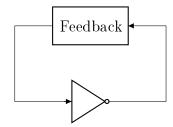

Oscillator circuits are currently applied in almost every electronic device to offer a specific and steady frequency [6]. Figure 2.2 shows the concept of most electronic oscillators.

Figure 2.2 The concept of most electronic oscillators.

Basically, a oscillator can be regarded as a closed-loop circuit that consists of an amplifier and a feedback network [7], p.12-13]. The feedback part provides positive feedback and works as a frequency-selective network. It determines the oscillation frequency. The signal at selected frequency is amplified by the amplifier, meanwhile the signals at other undesired frequencies attenuate. Due to the positive feedback, the wanted signal will be amplified repeatedly, until its amplitude reaches the limitation and does not increase any more.

There are two necessary requirements for generating stable sinusoid. Firstly, the total phase shift of loop equals  $360^{\circ}$ . Usually the amplifier provides  $180^{\circ}$  phase shift and the feedback network provides another  $180^{\circ}$  phase shift. Secondly, the closed-loop gain must be 1, which means the amplifier gain compensates fully for the signal attenuation in the feedback path. [4, p.502-506] [7], p.10-13]

According to the components of feedback network, oscillators can be basically divided into RC oscillators, LC oscillators, crystal oscillators, and other oscillators. The one used in this project is a crystal oscillator.

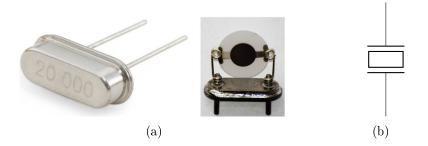

The crystal oscillator appeared in 1920's  $[\overline{7}, p.1]$ . It is usually used for creating a reference signal at a precise frequency because it usually has better frequency stability than an RC or LC oscillator. Figure 2.3 presents a picture of quartz (SiO<sub>2</sub>) crystal and its electronic symbol. Both two opposite sides of the thin piece of quartz are metalized for electrical contact. Because of the piezoelectric effect, the quartz vibrates in its thickness direction and finally generates an alternating current at its resonant frequency. Thinner quartz has higher resonant frequency, thereby the physical thickness of a quartz restricts its frequency upper limitation. Commonly, the resonant frequency of a quartz crystal is made from several tens of kHz to several tens of MHz.  $[\overline{7}, p.3]$

Figure 2.3 (a) A quartz crystal and (b) the electronic symbol of quartz crystal.

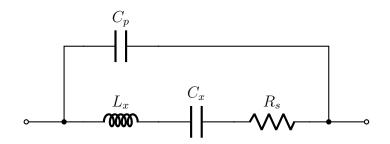

Figure 2.4 An equivalent circuit of quartz crystal.

As shown in Figure 2.4, an equivalent circuit of quartz crystal includes an inductor  $L_x$  and a capacitor  $C_x$ , that make the crystal strongly frequency-selective. There is also a parallel capacitor  $C_p$  representing the parasitic capacitance of the metal

platings, the package, and the leads. A series resistor  $R_s$  representing the mechanical and electrical losses. Crystal exhibits two different resonant frequencies: one is the series resonant frequency  $(f_s)$  caused by  $L_x$  and  $C_x$ , the other is the parallel resonant frequency  $(f_p)$  caused by  $L_x$ ,  $C_x$  and  $C_p$ . These two frequencies can be calculated from:

$$f_s = \frac{1}{2\pi\sqrt{L_x C_x}},\tag{2.6}$$

$$f_p = \frac{1}{2\pi \sqrt{L_x \frac{C_x C_p}{C_x + C_p}}}.$$

(2.7)

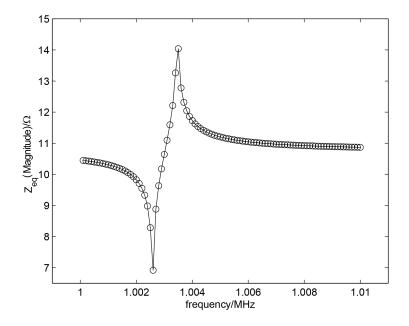

Supposing  $L_x = 4.2$  H,  $C_x = 0.006$  pF,  $R_s = 260 \Omega$ ,  $C_p = 3.4$  pF (values from [7], p.5]),  $f_s$  and  $f_p$  can be obtained as approximately 1.00258 and 1.00346 MHz respectively, from Equation 2.6 and 2.7. The impedance of this equivalent circuit  $Z_{eq}$  can be calculated from:

$$Z_{eq} = (-j2\pi fC_p) // (j2\pi fL_x - j2\pi fC_x + R_s)$$

(2.8)

Figure 2.5 The magnitude of  $Z_{eq}$  as a function of frequency f (generated by Matlab).

Figure 2.5 plots the magnitude of  $Z_{eq}$  as a function of frequency f. The circuit presents low impedance at its series resonant frequency (1.00258 MHz) and high impedance at parallel resonant frequency (1.00346 MHz). Crystal oscillators work at the series resonant frequency. However, according to the connecting ways of crystal, the oscillator circuits can be divided into series-resonant circuits and parallel-

resonant circuits. In a series-resonant oscillator, the crystal impedance is low at the oscillation frequency while in a parallel-resonant oscillator, the crystal impedance is high at the oscillation frequency. [7], p.9]

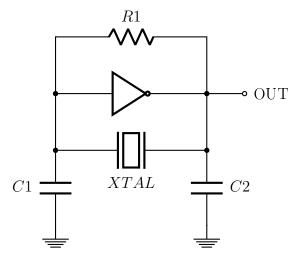

Pierce crystal oscillator (see Figure 2.6) has simple structure and good frequency stability. Consequently, it was selected for this project. Pierce oscillator circuit was derived from Colpitts oscillator, a parallel-resonant circuit (see Figure 2.7), by George W. Pierce. [7], p.25-27,45-51]

Figure 2.6 A typical Pierce crystal oscillator circuit.

Figure 2.7 A simple crystal oscillator with transistor.

In a Pierce crystal oscillator, it is the quartz crystal and two capacitors that form the feedback network, determine the resonant frequency and provide  $180^{\circ}$  phase shift.

#### 2.3.2 Voltage-controlled oscillators

The frequency of a voltage-controlled oscillator (VCO) can be tuned by a input voltage within a range. It is a necessary part in PLL loop.

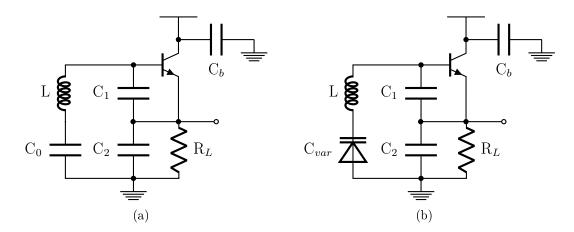

A high-frequency VCO circuit for PLL is usually built by adding a varactor diode into an LC resonant oscillator. Its tunability is realized through the variable capacitance of varactor diode. It can provide more linear gain over other VCOs. [2, p.38-42]

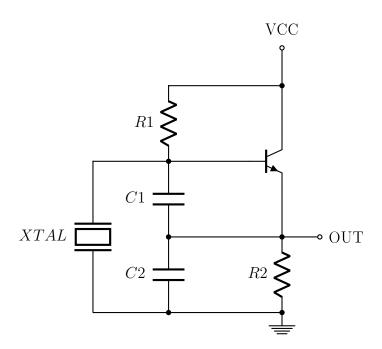

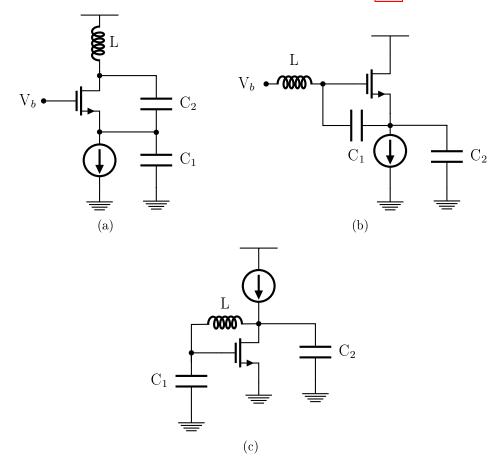

Most LC oscillators use the topology called "three-point" type. The three-point oscillator contains a transistor and a LC tank. The three terminals of transistor are connected to three nodes of the LC tank respectively. [8], p.749-750]

According to Razavi [4], p.517], three-point oscillators can be divided into three different groups: with gate (or base) grounded, with drain (or collector) grounded, and with source (or emitter) grounded, as shown in Figure 2.8.

**Figure 2.8** The topology of three-point oscillator (using MOSFET), (a) with gate grounded, (b) with drain grounded, (c) with source grounded.

The Clapp oscillator [9], p.605], which is a common choice for VCO design, has its

drain (or collector) grounded, as shown in Figure 2.9(a). The tunable oscillator is obtained by replacing the capacitor  $C_0$  with a varactor diode (see Figure 2.9(b)). [9, p.606-607]

Figure 2.9 (a) A Clapp oscillator and (b) a Clapp VCO circuit.

The capacitance of a varactor diode  $C_{var}$  decreases as its reverse-biasing voltage increases, which can be described as followed:

$$C_{var} = C_{V0} \left( 1 - \frac{V_{ctrl}}{V_{diff}} \right)^{(-1/2)}, \qquad (2.9)$$

where  $C_{V0}$  is the original capacitance of diode without any applied voltage,  $V_{ctrl}$  is the applied reverse-biasing voltage, and  $V_{diff}$  is the barrier voltage of the pn-junction. [9], p.307-308]

The resonant frequency  $\omega_o$  of clapp VCO in Figure 2.9(b) is calculated from:

$$\omega_o = \sqrt{\frac{1}{L} \left( \frac{1}{C_{var}} + \frac{1}{C_1} + \frac{1}{C_2} \right)}.$$

(2.10)

Thereby, the maximum output frequency  $\omega_{max}$  is calculated from:

$$\omega_{max} = \sqrt{\frac{1}{L} \left( \frac{1}{C_{var}\_min} + \frac{1}{C_1} + \frac{1}{C_2} \right)},$$

(2.11)

and the minimum output frequency  $\omega_{min}$  is calculated from:

$$\omega_{min} = \sqrt{\frac{1}{L} \left( \frac{1}{C_{var} max} + \frac{1}{C_1} + \frac{1}{C_2} \right)}.$$

(2.12)

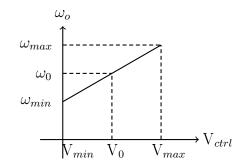

The  $\omega_o$  can be described as a function of input control voltage  $V_{ctrl}$  after a locally

Figure 2.10 The characteristic of VCO output frequency.

linearized approximation, as plotted in Figure 2.10:

$$\omega_o = K_V V_{ctrl} + \omega_{min}, \qquad (2.13)$$

where  $K_V$  is the slope of function, called the VCO gain and expressed in rad/s/V:

$$K_V = \frac{\Delta \omega_o}{\Delta V_{ctrl}} \approx \frac{\omega_{max} - \omega_{min}}{V_{max} - V_{min}} \text{ rad/s/V.}$$

(2.14)

For typical varactors  $V_{min}$  can be zero and  $V_{max}$  several volts or even tens of volts.

The difference between  $\omega_{max}$  and  $\omega_{min}$  is called the tuning range  $\Delta \omega_{VCO}$ :

$$\Delta \,\omega_{VCO} = \omega_{max} - \omega_{min},\tag{2.15}$$

while the angular center frequency  $\omega_0$  is the center point between  $\omega_{max}$  and  $\omega_{min}$ .

In time domain, phase  $\theta_o$  is obtained by integrating instantaneous angular frequency  $\omega_o$  over time:

$$\theta_o(t) = \int_0^t \omega_o(\tau) d\tau + C.$$

(2.16)

On the other hand, the Laplace transform of integration is division by s [4], p.607]. Therefore, the Laplace domain phase of a VCO is given by:

$$\theta_o = \frac{\omega_o}{s}.\tag{2.17}$$

$\Delta \theta_o$  can be written as:

$$\Delta \theta_o = \frac{\Delta \omega_o}{s} = \frac{K_V \cdot \Delta V_{ctrl}}{s} = \underbrace{\frac{K_V}{s}}_{\text{VCO gain}} \cdot \Delta V_{ctrl}.$$

(2.18)

#### 2.3.3 Frequency dividers

A frequency divider divides an input frequency usually by an integer. There are analog dividers and digital dividers: analog dividers are targeted at very high frequencies, while digital dividers are commonly used in IC chips. [4, p.655-661]

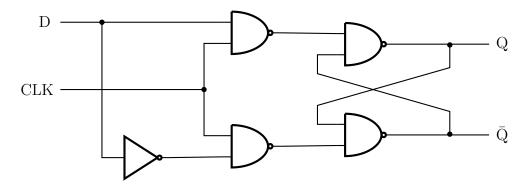

The flip-flop divider is a digital divider. Flip-flops [10, p.142] are bistable circuits meaning that it can flip between state "0" (logic low level) and "1" (logic high level) under the effect of its input signal. Flip-flop dividers have the advantages of simple structure, low power consumption, and low cost. [10, p.143-145]

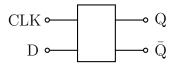

The D flip-flop (data flip-flop, or delay flip-flop) is popular for frequency division. It is an edge triggered flip-flop, which means the stored state will flip at the positive edge or the negative edge of input clock signal.

Figure 2.11 D flip-flop symbol.

As shown in Figure 2.11, a D flip-flop has two input nodes and two output nodes: data input D, clock input CLK, output Q and its complement  $\overline{Q}$ . Q and  $\overline{Q}$  are opposite to each other. A D flip-flop can be made by connecting logic gates in the way shown in Figure 2.12, using four NAND gates with one NOT gate.

Figure 2.12 A D flip-flop composed by logic gates.

Table 2.1 shows the truth table of a positive edge-triggered D flip-flop.  $Q_n$  is the previous state of  $Q_{n+1}$ . In brief, the output Q takes the state of data input only when CLK jumps from low to high. In any other cases, Q and  $\bar{Q}$  remain their previous value no matter which state D is, because the stored memory is latched. If the flip-flop is negative triggered, the output values will flip at negative edges. This edge triggered flip-flops help to reject the interference and reduce the possibility of

error, because the output will hold its state except the moment of triggering even if there are interferences at input D.

|              |   | F         |                 |

|--------------|---|-----------|-----------------|

| CLK          | D | $Q_{n+1}$ | $\bar{Q}_{n+1}$ |

| $\uparrow$   | 0 | 0         | 1               |

| $\uparrow$   | 1 | 1         | 0               |

| $\downarrow$ | × | $Q_n$     | $\bar{Q}_n$     |

| 0            | × | $Q_n$     | $\bar{Q}_n$     |

| 1            | × | $Q_n$     | $\bar{Q}_n$     |

Table 2.1 The truth table of a positive triggered D flip-flop.

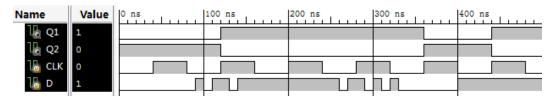

Figure 2.13 shows an example sequence diagram of a positive edge-triggered D flip-flop, designed with Xilinx ISE (a VHDL design tool).

Figure 2.13 An example sequence diagram of a positive edge-triggered D flip-flop.

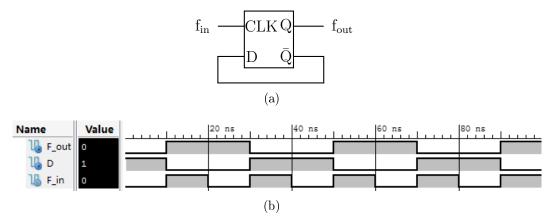

A by-2 divider can be obtained by connecting the  $\overline{Q}$  of D flip-flop to its D. Figure 2.14 presents a by-2 divider and its corresponding sequence diagram created with Xilinx ISE.

**Figure 2.14** (a) The diagram of a by-2 divider and (b) the sequence diagram of by-2 divider.

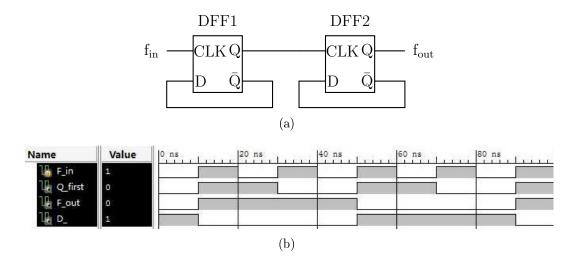

Similarly, a by-4 divider can be implemented by cascading two D flip-flop, as depicted in Figure 2.15(a). The input signal goes into the CLK pin of first flip-flop, then its Q is connected to the CLK of second flip-flop.

**Figure** 2.15 (a) The diagram of a by-4 divider and (b) the sequence diagram of by-4 divider.

From Figure 2.15(b), it can be seen that  $Q_1$  changes from its previous state to the opposite at each positive edge of  $f_{in}$ , having a frequency of  $f_{in}/2$ . At the same time,  $Q_2$ , which is the desirable output signal  $f_{out}$ , flips its state at every positive edge of  $Q_1$  (*CLK*<sub>2</sub>), having a frequency of  $Q_1/2$ . Therefore,  $f_{out}$  equals a quarter of  $f_{in}$ .

Likewise, a divide-by-N circuit can be made up of M D flip-flops while  $N = 2^{M}$ . The gain of the by-N divider is:

$$K_n = \frac{\theta_n}{\theta_o} = \frac{\frac{\omega_o/s}{N}}{\omega_o/s} = \frac{1}{N},$$

(2.19)

where  $\theta_n$  is the phase of divided signal.

#### 2.3.4 Phase detectors

A phase detector generates an output signal that is proportional to the phase difference between two input signals. There are several means for realizing the function of phase detection [2, p.15]. In this section, two types of phase detectors are introduced: the double-balanced diode mixer and the Exclusive-OR (XOR) gate.

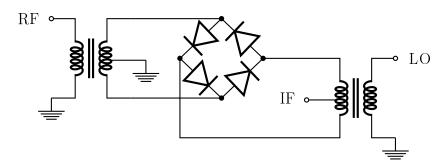

#### Double-balanced diode mixer

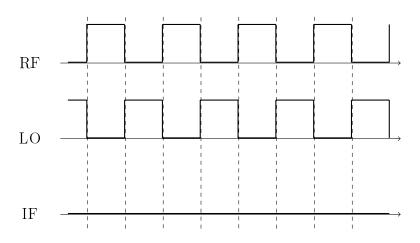

A double-balanced diode mixer contains four end-to-end diodes and two transformers (see Figure 2.16). In down conversion operation LO (local oscillator) and RF (radio frequency) are input ports while IF (intermediate frequency) is output port.

Figure 2.16 A double-balanced diode mixer.

Two input ports are fed with strong enough square waves at same frequency. When LO signal is positive, the upper two diodes conduct current and lower two diodes are off. Therefore, RF signal flows from the upper terminal of its secondary side into IF, which means the IF reproduce the signal of RF. When LO signal is negative, there is the opposite situation. The lower two diodes conduct current instead, and RF signal flows from the lower terminal into IF. In this case, the IF signal is the negative of RF. Figures 2.17 - 2.21 illustrate how the double-balanced mixer detects two square waves.

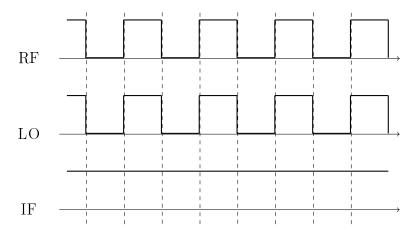

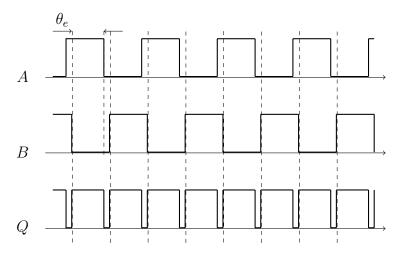

When LO and RF are in phase, the phase difference between them is 0 ( $\theta_e = 0$ ), the result of mixer is a square wave with 100% duty cycle, see Figure 2.17.

Figure 2.17 The input and output waveforms of double-balanced diode mixer when  $\theta_e = 0$ .

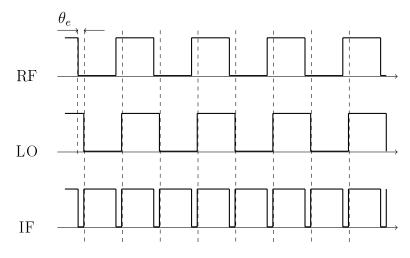

When the phase difference between LO and RF is higher than 0 but lower than  $\pi/2$   $(0 < \theta_e < \frac{\pi}{2})$ , the duty cycle of the output wave is between 100% and 50%, as shown in Figure 2.18.

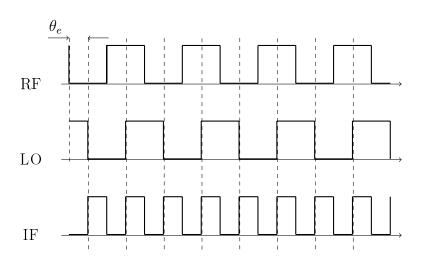

When the phase difference between LO and RF is exactly  $\pi/2$  ( $\theta_e = \pi$ ), the result of mixer is a square wave with 50% duty cycle, as shown in Figure 2.19.

When the phase difference between LO and RF is higher than  $\pi/2$  but lower than  $\pi$

Figure 2.18 The input and output waveforms of double-balanced diode mixer when  $0 < \theta_e < \frac{\pi}{2}$ .

Figure 2.19 The input and output waveforms of double-balanced diode mixer when  $\theta_e = \pi$ .

$(\frac{\pi}{2} < \theta_e < \pi)$ , the duty cycle of the output wave is between 50% and 0%, as shown in Figure 2.20.

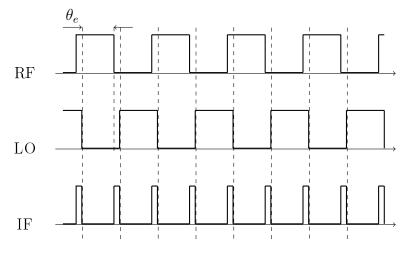

When LO and RF are completely out of phase,  $\theta_e = \pi$ , the result of mixer is a square wave with 0% duty cycle, as shown in Figure 2.21.

Overall, the output signal  $u_{pd}$  at IF port is a square wave that has identical frequency with input signals. The duty cycle of  $u_{pd}$  is inversely proportional to  $\theta_e$ :

Duty cycle =

$$(1 - \frac{\theta_e}{\pi}) \times 100\%$$

. (2.20)

And the average voltage of  $u_{pd}$  is proportional to the duty cycle:

$$\bar{u}_{pd} = V_{pd} \times \text{Duty cycle}, \qquad (2.21)$$

**Figure** 2.20 The input and output waveforms of double-balanced diode mixer when  $\frac{\pi}{2} < \theta_e < \pi$ .

Figure 2.21 The input and output waveforms of double-balanced diode mixer when  $\theta_e = \pi$ .

where  $V_{pd}$  is the amplitude of  $u_{pd}$ .

Therefore,  $\bar{u}_{pd}$  can be written as a function of  $\theta_e$ :

$$\bar{u}_{pd} = V_{pd} \times (1 - \frac{\theta_e}{\pi}). \tag{2.22}$$

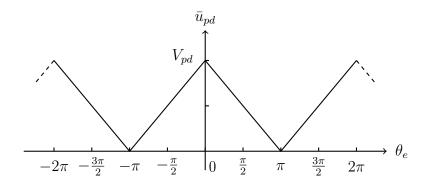

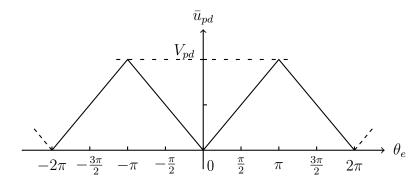

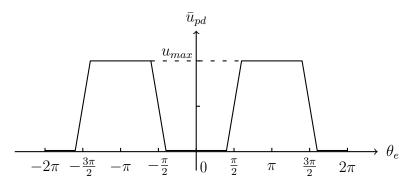

The relationship between  $\theta_e$  and  $\bar{u}_{pd}$  is plotted in Figure 2.22. It is a periodical triangle wave with period of  $2\pi$ . The slope at  $-\frac{\pi}{2}$  is also called the gain of this phase detector, which is calculated from:

$$K_d = \frac{\Delta \ \bar{u}_{pd}}{\Delta \ \theta_e} = \frac{V_{pd}}{\pi}.$$

(2.23)

Figure 2.22 The  $\bar{u}_{pd}$  as a function of  $\theta_e$  for double-balanced mixer.

#### Exclusive-OR gate

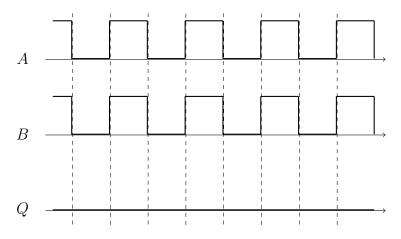

The Exclusive-OR (XOR) gate is a simple logic gate, usually represented as shown in Figure 2.23. According to its truth table shown in Table 2.2, if input A and B are different, the XOR gate generates a logic "1", otherwise the output Q will be logic "0".

Figure 2.23 Schematic symbol an XOR gate.

| A | В | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Table 2.2 The truth table of an XOR gate.

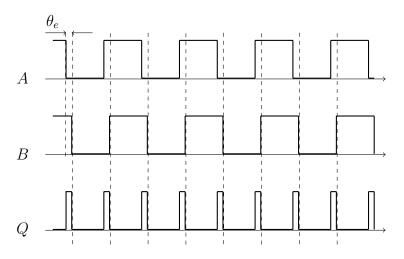

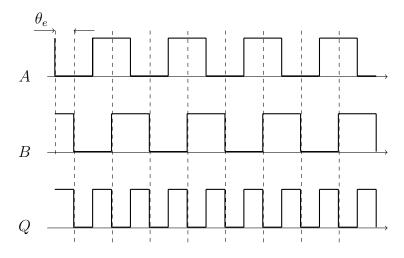

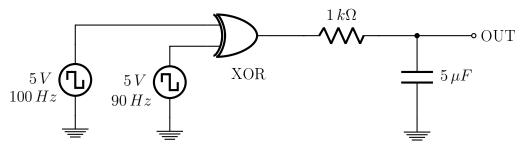

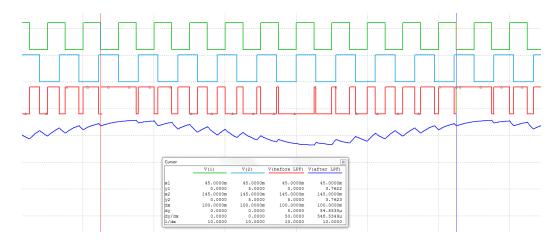

Figures 2.24 - 2.28 depict the output waveforms of XOR gate when comparing two square waves of identical frequency. Basically, they are opposite to the results of double-balanced mixer. [2, p.52-55]

When  $\theta_e = 0$ , the result of XOR gate is shown in Figure 2.24. The duty cycle of square wave equals 0%.

When  $0 < \theta_e < \frac{\pi}{2}$ , see Figure 2.25, the duty cycle of the output is lower than 50%.

Figure 2.24 The input and output waveform of XOR gate when  $\theta_e = 0$ .

**Figure** 2.25 The input and output waveform of XOR gate when  $0 < \theta_e < \frac{\pi}{2}$ .

When  $\theta_e = \pi/2$ , the result of XOR gate is shown in Figure 2.26. The duty cycle of square wave is exactly 50%.

When  $\frac{\pi}{2} < \theta_e < \pi$ , see Figure 2.27, the duty cycle of the output is higher than 50%.

When  $\theta_e = \pi$ , two input signals are completely out of phase, the waveform is shown in Figure 2.28. The duty cycle of square wave reaches 100%.

The relationship between  $\bar{u}_{pd}$  and  $\theta_e$  can be described as:

$$\bar{u}_{pd} = V_{pd} \times \frac{\theta_e}{\pi}.$$

(2.24)

Figure 2.29 presents the  $\bar{u}_{pd}$  as a function of  $\theta_e$  for XOR gate. Maximum  $\bar{u}_{pd}$  is achieved when input waves are out of phase by  $\pi$ , and minimum  $\bar{u}_{pd}$  is obtained

Figure 2.26 The input and output waveform of XOR gate when  $\theta_e = \pi/2$ .

Figure 2.27 The input and output waveform of XOR gate when  $\frac{\pi}{2} < \theta_e < \pi$ .

Figure 2.28 The input and output waveform of XOR gate when  $\theta_e = \pi$ .

**Figure** 2.29 The  $\bar{u}_{pd}$  as a function of  $\theta_e$  for XOR gate.

when input waves are in phase. The slope at  $\frac{\pi}{2}$  equals phase detector gain  $K_d$ :

$$K_d = \frac{\Delta \ \bar{u}_{pd}}{\Delta \ \theta_e} = \frac{V_{pd}}{\pi}.$$

(2.25)

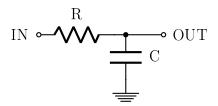

### 2.3.5 Loop filters

The loop filter (LF) is invariably a low-pass filter (LPF). It is driven by the phase detector output  $u_{pd}$ , allowing frequencies that are lower than the cutoff frequency pass and filtering out undesired high frequency components. After passing the LPF,  $u_{pd}$  becomes the input control voltage of VCO. [2, p.33-34]

The order of a LPF equals the number of poles to its transfer function. Higher-order LPFs provide better performance in filtering, however on the other hand, lower-order system could be more stable. For real applications nowadays, second-order LPFs are mostly used. [2, p.60]

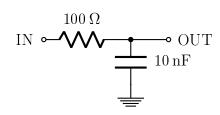

This work utilizes an RC low-pass filter, which is one of the simplest first-order LPFs [9, p.210]. It consists of a series resistor and a shunt capacitor, as shown in Figure 2.30. The corresponding transfer function can be obtained from:

$$H(j\omega) = \frac{V_{out}}{V_{in}} = \frac{\frac{1}{j\omega C}}{R + \frac{1}{j\omega C}}$$

$$= \frac{1}{1 + j\omega RC}$$

$$= \frac{1}{1 + j\omega \tau},$$

(2.26)

where  $\tau = RC$  is the time constant. The cutoff frequency  $\omega_c = 1/\tau$  is defined as the point where the gain through the filter drops 3 dB. [11, p.386]

Figure 2.30 An RC low-pass filter.

Therefore the gain of LPF  $K_f(s)$  in frequency domain is presented as:

$$K_f(s) = \frac{1}{1+s\tau},$$

(2.27)

where  $s = j\omega$ .

#### 2.4 The control theory of PLL and key parameters

The gain of each block has been introduced in previous sections. Therefore, this closed-loop PLL system can be modeled as shown in Figure 2.31.

Figure 2.31 The modeled PLL loop showing voltages and angular frequencies.

Supposing that the reference signal is a wave with amplitude at  $v_i$ , angular frequency at  $\omega_i$  and initial phase at  $\phi_i$ , and the divided VCO output is another signal with amplitude at  $v_o$ , angular frequency at  $\frac{\omega_o}{N}$  and initial phase at  $\phi_o$ . As explained in Section 2.3.4, the phase detector compares the instantaneous phase of these two input signals, generating an AC signal  $u_{pd}$  of which average voltage is proportional to the phase difference  $\theta_e$ . They can be expressed as:

$$\theta_i = \omega_i t + \phi_i, \tag{2.28}$$

$$\frac{\theta_o}{N} = \frac{\omega_o}{N} t + \phi_o, \tag{2.29}$$

$$\theta_e = \theta_i - \frac{\theta_o}{N} = (\omega_i - \frac{\omega_o}{N})t + (\phi_i - \phi_o), \qquad (2.30)$$

$$u_{pd} = K_d \,\theta_e. \tag{2.31}$$

After passing LF,  $u_{pd}$  is filtered and integrated, becoming a DC signal  $V_{ctrl}$ , provided that  $\omega_i$  equals  $\omega_o/N$ . It tunes the VCO and determines the output frequency  $\omega_o$ .

$$V_{ctrl} = K_f \, K_d \, \theta_e, \tag{2.32}$$

$$\omega_o = K_v \, K_f \, K_d \, \theta_e + \omega_{min}. \tag{2.33}$$

If there is a difference in  $\omega_i$  and  $\frac{\omega_o}{N}$  at the beginning,  $\theta_e$  would change from 0 to  $2\pi$  periodically, therefore making  $V_{ctrl}$  also beat between  $V_{max}$  and  $V_{min}$ . It causes the  $\omega_o$  swing between  $\omega_{max}$  and  $\omega_{min}$ . Meanwhile this variation of  $\omega_o$  is fed back to phase detector, changing  $\theta_e$  and tuning the VCO again continuously. Eventually the VCO generates an exactly same frequency as  $N\omega_i$ ,  $\theta_e$  becomes a constant, and the loop achieves locked state at this time.

There are two necessary requirements for locking the loop:  $\frac{\omega_o}{N}$  equals  $\omega_i$  and  $\theta_e$  reaches a proper constant. During the settlement process, if frequency  $\frac{\omega_o}{N}$  is equal to  $\omega_i$  but  $\theta_e$  is improper,  $\omega_o$  may keep changing. The loop would not be locked until both two requirements are met. [4, p.604-605]

In this project,  $\theta_e$  is supposed to equal  $\pi/2$  when PLL is locked, because only at this time the control voltage  $V_{ctrl}$  reaches the center point, making the VCO create its center frequency, which is about 96 MHz.

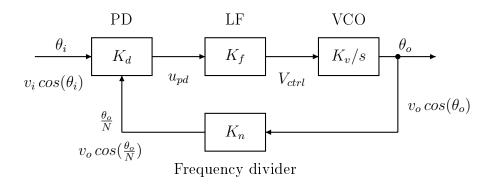

As final constant  $\theta_e$  is independent of the initial phases  $\phi_i$  and  $\phi_o$ , it can be assumed that both  $\phi_i$  and  $\phi_o$  are equal to 0, so that the reference signal becomes  $v_i \cos(\theta_i)$ while the VCO output becomes  $v_o \cos(\theta_o)$ . The loop block diagram is then modified as shown in Figure 2.32.

Figure 2.32 The modeled PLL loop focused on phases.

Hence, the output phase of VCO is obtained as:

$$\theta_o = \frac{K_v}{s} K_f K_d \left(\theta_i - K_n \theta_o\right), \qquad (2.34)$$

and the closed-loop transfer function is given by:

$$H(s) = \frac{\theta_o}{\theta_i} = \frac{K_d K_f K_v}{s + K_n K_d K_f K_v},$$

(2.35)

where the gains of the phase detector, the filter, the VCO and the divider are:

$$K_d = \frac{\Delta V}{\pi} \, \mathrm{V/rad}, \qquad (2.36)$$

$$K_f = \frac{1}{1+s\tau},\tag{2.37}$$

$$K_v = \frac{\Delta \,\omega}{\Delta V} \,\,\mathrm{rad/s/V},\tag{2.38}$$

$$K_n = \frac{1}{N}.\tag{2.39}$$

When the loop is locked, the divided frequency tracks the reference frequency, that is to say:  $d\theta = dK \ \theta$

$$\frac{d\,\theta_i}{d\,t} = \frac{d\,K_n\,\theta_o}{d\,t}.\tag{2.40}$$

In order to analyze the stability of this system, the poles of closed-loop can be found from:

$$s + K_n K_d K_f K_v = 0$$

$$\Rightarrow s = -\frac{\frac{1}{1+s\tau} K_d K_v}{N}$$

$$= -\frac{1}{2\tau} \pm \sqrt{\left(\frac{1}{2\tau}\right)^2 - \frac{K_d K_v}{\tau N}} \text{ rad/s.}$$

(2.41)

According to the Nyquist stability criterion, the loop is unstable if the number of poles located in the right-half complex plane is not equal to zero.

The order number of a PLL equals the order number of the loop filter plus 1. This work applies simple first-order loop filter, hence it is a second-order PLL system, which is to say, the loop has two poles: one from LPF and the other one from VCO. Both two poles are supposed to be in the left-half plane.

The corresponding natural frequency  $\omega_n$  and damping factor  $\zeta$  are obtained from:

$$\omega_n = \sqrt{\frac{K_d \, K_v \, \omega_c}{N}} \, \text{rad/s}, \qquad (2.42)$$

$$\zeta = \frac{\omega_c}{2\,\omega_n}.\tag{2.43}$$

Normally,  $\zeta$  is selected to be between  $1/\sqrt{2}$  and 1, to avoid damped or over-damped problems. [4, p.608]

Lock range  $\omega_{cr}$  (also known as capture range) and locking time  $t_L$  (also known as settling time) are important parameters for analyzing this kind of traditional PLL system. The lock range means the loop is able to get locked rapidly within this frequency range. The lock time refers to the time that system needs to achieve locked state. [2, p.70-72]

Values of  $\omega_{cr}$  and  $t_L$  are calculated from [2, p.101]:

$$\omega_{cr} = \sqrt{N K_d K_v \omega_c} \quad \text{rad/s}, \tag{2.44}$$

$$t_L \approx \frac{2\pi}{\omega_n} \,\mathrm{s.}$$

(2.45)

# 3. BLOCK DESIGN, CONSTRUCTION AND TESTING

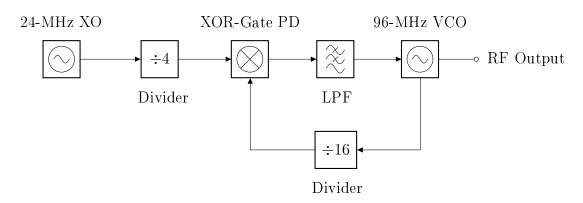

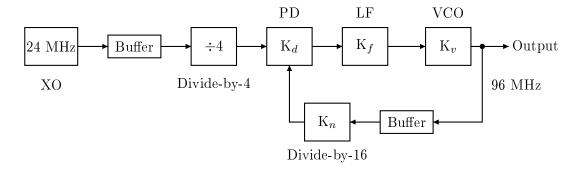

Figure 3.1 shows the block diagram of this project. A 24-MHz sine-wave from crystal oscillator (XO) is divided by 4, while the output signal of 96-MHz voltage-controlled oscillator (VCO) is divided by 16. Two divided frequencies are compared by phase detector (PD), generating a signal that is proportional to the phase difference. This signal is then filtered by low-pass filter (LPF) and becomes the input control voltage of VCO.

Figure 3.1 The block diagram of PLL system for this project.

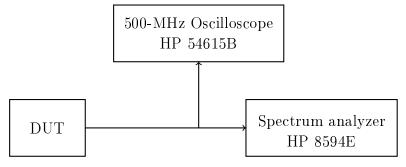

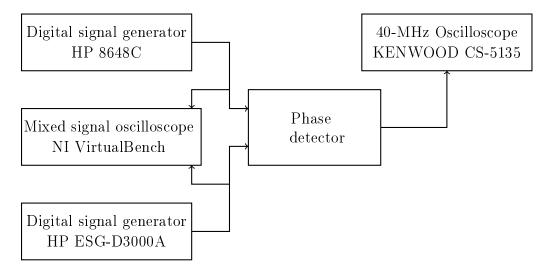

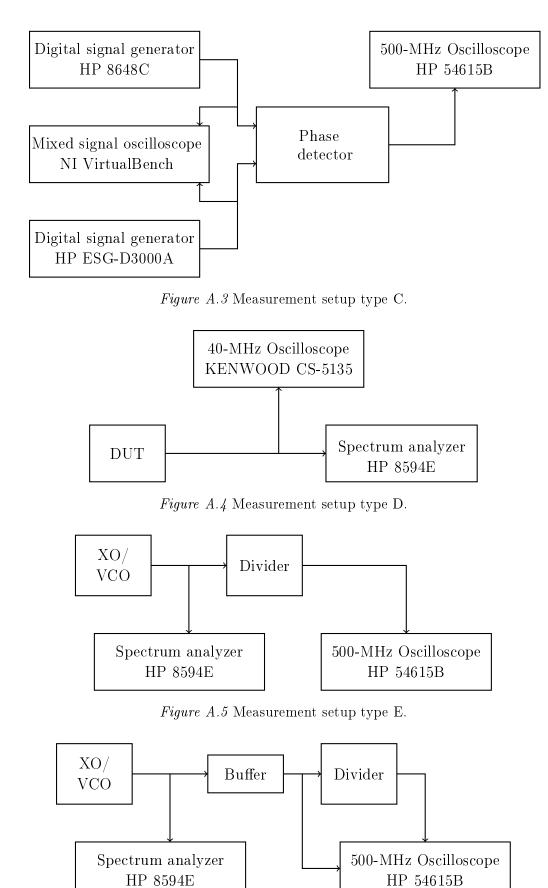

The detailed design, construction and testing for each block are discussed in this chapter. The information on measurement setups can be found in Appendix.

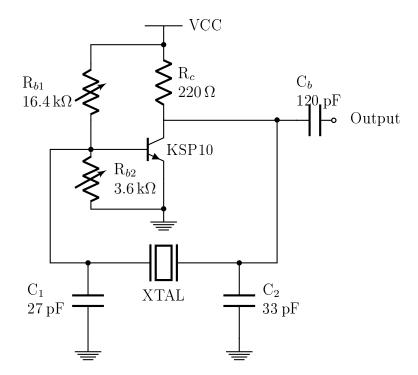

#### 3.1 Crystal oscillator design, construction and testing

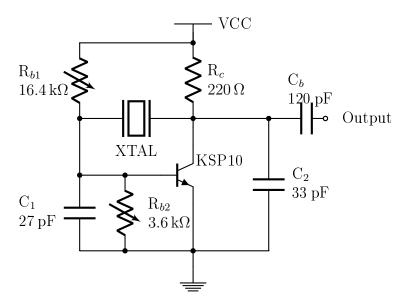

A 24-MHz quartz crystal oscillator circuit is chosen for providing a stable reference signal at around 24 MHz. The circuit (see Figure 3.2) is designed based on Pierce oscillator (see Figure 2.6 in Section 2.3.1). An NPN-type bipolar junction transistor KSP10 works as the inverting amplifier, providing 180° phase shift. A 24-MHz quartz and capacitors  $C_1$  and  $C_2$  work as the feedback network, providing another 180° phase shift. Potentiometer  $R_b$  and resistor  $R_c$  are used for transistor biasing. Capacitor  $C_b$  is used for DC block.

Figure 3.2 The designed 24-MHz crystal oscillator circuit.

The Pierce oscillator can work either at or slightly beyond the series resonant frequency of quartz crystal. Decreasing the value of  $C_1$  and  $C_2$  makes the operating frequency approach resonant frequency [12, p.249], and helps to improve the output power of oscillator. However, there is a lower bound for capacitors' value. The circuit does not oscillate any more if the value of capacitors are lower than this bound. [13, p.90]