# MATIAS LEHTINEN VERIFICATION OF A MODULAR GRAPH BASED IMAGE PROCESSING SYSTEM

Master of Science thesis

Examiner: Prof. Karri Palovuori Examiner and topic approved by the Faculty Council of the Faculty of Computing and Electrical Engineering on 9th December 2015

### **ABSTRACT**

MATIAS LEHTINEN: Verification of a modular graph based image processing

Tampere University of Technology

Master of Science thesis, 61 pages, 0 Appendix pages

May 2016

Master's Degree Programme in Electrical Engineering

Major: Electronics product design Examiner: Prof. Karri Palovuori

Keywords: Verification, graph, image processing system, heterogeneous

Electronic devices today have become complex. Any non-trivial device consists of both hardware and software. Tightening time to market and cost requirements put pressure on the development process of the devices. Software and hardware needs to be developed concurrently and must be verified in an early phase of product development.

This thesis introduces a graph based image processing system. Image processing system is a complex system that usually consists of software, firmware and hardware. The possibilities and methods of graph verification are investigated in this thesis. Graphs can be used to handle the complexity of the system by encapsulating the functionality of the underlying implementations. Graphs provide modularity and configurability that can be utilized in the development and verification of the system. Reuse of software is increased due to the consistent and defined nature of graphs and their vertices. Software development shift left can be enabled by performing graph vertex verification in isolation by using pre-silicon development platforms.

In this thesis, image processing system graphs were also used in a real life product development project. Graph verification was initiated early in the product development. Shift left was exercised by utilizing the graph verification in several pre-silicon platforms. Functional, performance and stability testing was implemented. Both complete graphs and their vertices were verified in isolation. Graph verification provided many benefits to the product development. Implementations could be tested in several different environments in isolation using only a light test framework. Issues could be found and fixed early. Performance bottlenecks could be pinpointed and acted upon.

With the foundations laid in this project, it would be possible in the future to take more advantage of graphs. More advanced automated image quality testing would allow efficient verification. Finer granularity graphs would allow more configurability and more focused testing. Shift left could be further increased by adapting the development of the algorithms to use graphs. This would lower the gap between algorithms and actual vertex implementations and also introduce the available test infrastructure to algorithm development.

# TIIVISTELMÄ

MATIAS LEHTINEN: Modulaarisen graafipohjaisen kuvankäsittelyjärjestelmän

verifiointi

Tampereen teknillinen yliopisto Diplomityö, 61 sivua, 0 liitesivua Toukokuu 2016

Sähkötekniikan koulutusohjelma

Pääaine: Elektroniikan tuotesuunnittelu Tarkastajat: Prof. Karri Palovuori

Avainsanat: Verifiointi, graafi, kuvankäsittelyjärjestelmä, heterogeeninen

Nykyaikaiset elektroniset laitteet ovat monimutkaistuneet. Mikä tahansa arkipäiväinenkin laite koostuu sekä laitteistosta että ohjelmistosta. Samalla vaatimukset kustannuksista ja ajasta alkukehityksestä markkinoille siirtymiseen ovat kiristäneet kehitysprosessia. Ohjelmisto ja laitteisto on kehitettävä rinnakkain, ja nämä on kyettävä verifioimaan laitekehityksen varhaisessa vaiheessa.

Tämä diplomityö esittelee graafipohjaisen kuvankäsittelyjärjestelmän, joka koostuu tyypillisesti ohjelmistosta, sulautetusta ohjelmistosta ja laitteistosta. Työssä tutkitaan graafien verifioinnin mahdollisuuksia ja menetelmiä. Graafien avulla järjestelmän monimutkaisuutta hallitaan eristämällä ja piilottamalla itse toteutus. Graafien modulaarinen lähestymistapa tuo etuja järjestelmän kehittämiseen ja verifioimiseen. Ohjelmiston uudelleenkäyttömahdollisuudet kasvavat graafien määritellystä ja johdonmukaisesta luonteesta johtuen. Ohjelmistokehityksen aikaistaminen on mahdollista verifioimalla graafien solmuja eristyksissä käyttäen kehitysympäristöjä ilman valmista laitteistoa.

Tässä työssä kuvankäsittelyjärjestelmägraafeja käytettiin myös todellisessa tuotekehityshankkeessa. Graafien verifiointi aloitettiin tuotekehityksen varhaisessa vaiheessa. Ohjelmistokehityksen aikaistaminen oli mahdollista hyödyntämällä graafien verifioimista useissa kehitysympäristöissä. Toiminnallisuus-, suorituskykyja vakaustestaus toteutettiin. Sekä kokonaisia graafeja että yksittäisiä solmuja verifioitiin eristyksissä. Graafien verifiointi mahdollisti useita etuja tuotekehityksessä. Toteutukset oli mahdollista testata useissa eri ympäristöissä käyttäen hyödyksi kevyttä testiohjelmistoa. Ongelmat löydettin ja korjattiin varhaisessa vaiheessa. Suorituskykypullonkaulat oli mahdollista havaita ja purkaa.

Tämän työn pohjalta on tulevaisuudessa mahdollista hyödyntää graafeja yhä paremmin. Kehittyneemmät automatisoidut kuvanlaatutestit mahdollistaisivat tehokkaan verifionnin. Hienojakoisemmat graafit mahdollistaisivat joustavamman konfiguroinnin ja kohdistetumman testauksen. Ohjelmistokehityksen aikaistamista olisi mahdollista lisätä entisestään ottamalla graafit käyttöön myös algoritmikehityksessä. Tämä pienentäisi kuilua algoritmien ja solmutoteutusten välillä tuoden samalla graafitestauksen hyödyt algoritmikehitykseen.

## **PREFACE**

This thesis has given me an opportunity to research the area that I have been working on, and writing the thesis has been a great experience. I have been able to broaden my knowledge on the subject, and I have learned much new that can be applied in the future.

I would like to thank my colleagues for all the support that I have received during the writing of my thesis. I would especially like to thank Teemu Tuominen and Janne Kotka for instructing me and supporting me to keep the thesis writing ongoing.

I would also like to thank my family and my friends for their support. Finally, I would like to thank my beloved fiancée Enni for supporting, loving and understanding.

Tampere, 17.4.2016

Matias Lehtinen

# TABLE OF CONTENTS

| 1. | Intro                  | oduc   | tion                              | 1  |  |  |  |  |

|----|------------------------|--------|-----------------------------------|----|--|--|--|--|

| 2. | Image capture pipeline |        |                                   |    |  |  |  |  |

|    | 2.1                    | Ima    | age quality                       | 5  |  |  |  |  |

|    | 2.2                    | Ima    | age sensors                       | 7  |  |  |  |  |

|    | 2.3                    | 3A     |                                   | 9  |  |  |  |  |

|    | 2.                     | 3.1    | Auto exposure                     | 9  |  |  |  |  |

|    | 2.                     | 3.2    | Auto focus                        | 10 |  |  |  |  |

|    | 2.                     | 3.3    | Auto white-balance                | 11 |  |  |  |  |

|    | 2.4                    | Pre    | processing                        | 11 |  |  |  |  |

|    | 2.5                    | Den    | nosaicking                        | 12 |  |  |  |  |

|    | 2.6                    | Pos    | tprocessing                       | 14 |  |  |  |  |

|    | 2.7                    | For    | mat conversion                    | 15 |  |  |  |  |

|    | 2.                     | 7.1    | YUV                               | 15 |  |  |  |  |

|    | 2.                     | 7.2    | Compression                       | 16 |  |  |  |  |

| 3. | Graj                   | phs .  |                                   | 18 |  |  |  |  |

|    | 3.1                    | Bas    | ic graph theory                   | 18 |  |  |  |  |

|    | 3.2                    | Dire   | ected graphs                      | 20 |  |  |  |  |

|    | 3.3                    | Dat    | a flow                            | 21 |  |  |  |  |

|    | 3.4                    | Soft   | tware frameworks                  | 23 |  |  |  |  |

|    | 3.5                    | Gra    | ph implementation                 | 25 |  |  |  |  |

|    | 3.6                    | Gra    | phs in an image processing system | 29 |  |  |  |  |

| 4. | Veri                   | ficati | on of image processing graphs     | 33 |  |  |  |  |

|    | 4.1                    | Util   | lizing the modularity of graphs   | 34 |  |  |  |  |

|    | 4.2                    | Gra    | ph verification                   | 36 |  |  |  |  |

|    | 4.                     | 2.1    | Functionality                     | 37 |  |  |  |  |

|    | 4.                     | 2.2    | Performance                       |    |  |  |  |  |

|    | 4.                     | 2.3    | Stability                         | 40 |  |  |  |  |

|    | 4.3 Au    | tomating the test execution   | 41         |

|----|-----------|-------------------------------|------------|

| 5. | Usage in  | a product development project | 42         |

|    | 5.1 Tes   | st framework                  | 43         |

|    | 5.2 Tes   | st implementation             | 43         |

|    | 5.2.1     | Functionality                 | 43         |

|    | 5.2.2     | Performance                   | 45         |

|    | 5.2.3     | Stability                     | 45         |

|    | 5.3 Tes   | st environments               | 46         |

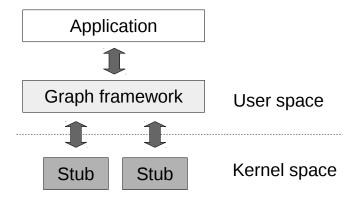

|    | 5.3.1     | Software stub                 | 46         |

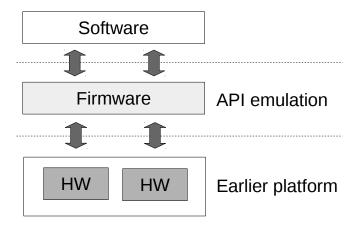

|    | 5.3.2     | Software API emulation        | 47         |

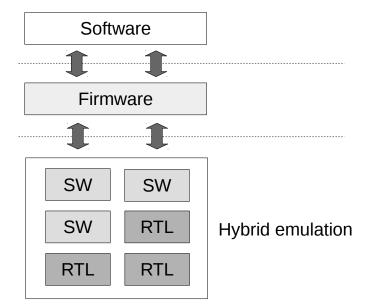

|    | 5.3.3     | Hybrid system emulation       | 48         |

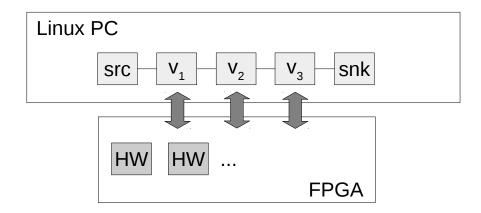

|    | 5.3.4     | Host PC and FPGA              | 49         |

|    | 5.3.5     | Actual device                 | 50         |

| 6. | Future p  | possibilities                 | 52         |

| 7. | Conclus   | ions                          | 54         |

| Bi | bliograph | y                             | <b>5</b> 6 |

# LIST OF FIGURES

| 2.1  | An example camera pipeline                                                                                                                     | 4  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | CCD and CMOS image sensors [12, p. 6]                                                                                                          | 7  |

| 2.3  | Bayer RGGB color filter array                                                                                                                  | 8  |

| 2.4  | Common demosaicking artifacts [42, p. 14]                                                                                                      | 13 |

| 2.5  | Different YUV subsampling ratios. The above pixel array describes the luma samples and the below pixel array describes the chroma sample pairs | 16 |

| 3.1  | Example applications of graphs                                                                                                                 | 18 |

| 3.2  | Example graph diagram                                                                                                                          | 19 |

| 3.3  | Example subgraph diagrams of graph in figure 3.2                                                                                               | 20 |

| 3.4  | Example directed graph diagram                                                                                                                 | 21 |

| 3.5  | Example directed acyclic graph diagram                                                                                                         | 22 |

| 3.6  | Flexibility in relation to efficiency in different technologies                                                                                | 25 |

| 3.7  | Traditional hardware and software development schedule                                                                                         | 26 |

| 3.8  | Shift left software development schedule                                                                                                       | 27 |

| 3.9  | Example software stacks without and with graphs                                                                                                | 28 |

| 3.10 | Image processing data flow graph                                                                                                               | 29 |

| 4.1  | Traditional testing of a processing system                                                                                                     | 35 |

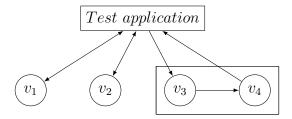

| 4.2  | Example testing of subgraphs in isolation                                                                                                      | 35 |

| 4.3  | Usage of different development platforms in testing                                                                                            | 36 |

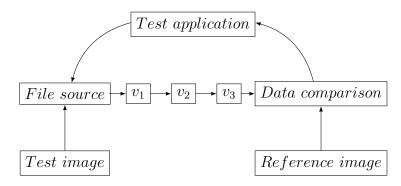

| 4.4  | Testing the graph bit exactness against reference data                                                                                         | 37 |

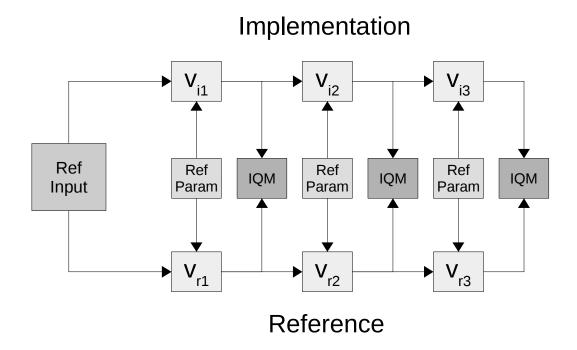

| 5.1 | using IQM (Image Quality Metric) against a reference                                                                                                                             | 44 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

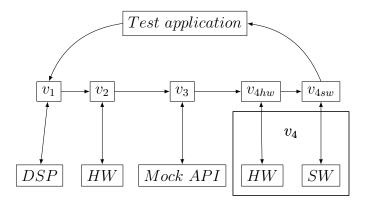

| 5.2 | Software stubs in early development                                                                                                                                              | 46 |

| 5.3 | Software API emulation using an earlier product. Firmware performs the emulation by mapping old hardware to mimic future hardware behavior                                       | 47 |

| 5.4 | Hybrid system emulation using both software and RTL to emulate the behavior of the hardware                                                                                      | 49 |

| 5.5 | Hybrid FPGA emulation. Graph framework and test related vertices are running on a generic Linux PC. FPGA is used to emulate hardware that the graph vertices are implemented for | 50 |

### LIST OF ABBREVIATIONS

3A 3 Algorithms

ADC Analog-To-Digital Converter

API Application Programming Interface

ASIC Application-Specific Integrated Circuit

BSD Berkeley Software Distribution

CCD Charge Coupled Device

CFA Color Filter Array

CMOS Complementary Metal-Oxide Semiconductor

CPU Central Processing Unit

DAG Directed Acyclic Graph

DMOS Difference Mean Opinion Score

DSP Digital Signal Processor

FPGA Field-Programmable Gate Array

FPS Frames Per Second

GPU Graphics Processing Unit

HDR High Dynamic Range

IQM Image Quality Metric

MOS Mean Opinion Score

MSE Mean Squared Error

MTBF Mean Time Between Failures

OS Operating System

PSNR Peak Signal-to-Noise Ratio RTL Register-Transfer Level

SoC System on a Chip

SSIM Structural Similarity Index

V4L2 Video4Linux2

VIF Visual Information Fidelity

VLIW Very Long Instruction Word

VSNR Visual Signal-to-Noise Ratio

### 1. INTRODUCTION

Electronic devices today are becoming more and more complex, including more functionality and more performance demanding features than ever. However, the cost to create such devices is not allowed to rise. Rather, the costs need to go down, while the time to market for products is squeezed into a minimum. Competition, especially in the lower segment of devices, makes sure of this with more and more companies emerging and competing in the same technological area.

Software is becoming pervasive in the products we use today. Any non-trivial device today consists of both hardware and software. There are several reasons for the popularity of software. Software is flexible, it is in general easy to develop, relatively easy to reuse and most importantly cheap when compared to pure hardware [28]. In other words, the easiest way to add features is to use software. However, software has its disadvantages when compared to hardware. The two most important factors are performance and energy efficiency [28]. A hardware implementation surpasses software in these and will be present in devices requiring either of the advantages.

To make things more complicated, software can be run on several platforms. There may be multiple CPUs (Central Processing Unit), GPUs (Graphics Processing Unit) or DSPs (Digital Signal Processor) that all are programmed differently. Or the software may only be some control logic for a fixed function hardware block in a SoC (System on a Chip), an ASIC (Application Specific Integrated Circuit) or an FPGA (Field-Programmable Gate Array). [10]

All the different processors and hardware blocks have their advantages and disadvantages. Depending on the requirements of a certain computation task, the most suitable compute device is chosen. As the nature of the tasks that need to be performed vary from one to another, the best results can usually be received by utilizing multiple compute devices. The combination of different compute devices is called heterogeneous computing, and several standards are emerging with the aim of simplifying the usage and unifying the APIs (Application Programming Interface) [24, 30].

1. Introduction 2

In order to succeed in the increasing demands to the cost of the device and the time to market requirements, while still being capable of handling the complexity of the devices, several aspects in the development process need to be thought of. Existing implementations need to be reused as much as possible with the minimum required changes. Different use cases need to be easily configured from whatever building blocks are available. Most importantly, components need to be functionally verified as early as possible.

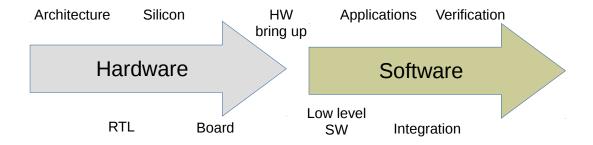

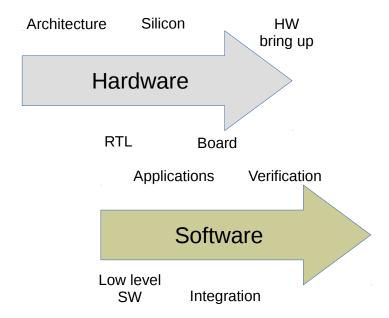

Traditionally hardware and software has been developed sequentially [53]. Software development has only been able to commence after the real hardware is available. In the past, when the software stacks were relatively simple, this may not have been a problem. However, with today's complex hardware and software stacks in addition to the ever more demanding time to market requirements, this process has become infeasible.

In order to squeeze the total time required to develop a product into the time frame required, it is necessary to start developing software earlier than traditionally is done. In this context, shift left means moving development that has traditionally begun after the actual hardware is available in parallel with the development of the hardware. This however raises important questions. How to develop program code for a platform that does not exist yet? How to verify that the hardware is going to be implemented in a way that the users expect? How are the different blocks consisting of software, firmware and hardware going to work together in the final product?

The purpose of this thesis is to investigate the aforementioned problems in the context of an image processing system for mobile devices. Image processing pipeline is an example of a highly complex and computationally demanding system and usually includes software, firmare and hardware. Especially in mobile devices, both the small physical size of the device and the rather restricted hardware budget create pressure on the actual image processing. Not only does the image format need to be converted and compressed, but also multiple correction algorithms need to be applied in order to provide an image with satisfactory quality [48].

Graphs are introduced as an option to handle the requirements of different use cases and products. Graphs help to cope with the increasing complexity of both hardware and software. They provide a generic way to integrate complex processing entities into the software stack. At the same time graphs allow the required modularity and flexibility without the burden of increasingly complex software exposed to the software stack above. The increased modularity allows convenient reuse of software

1. Introduction 3

and hardware building blocks. Moreover, graphs allow development and testing to begin very early in the development phase continuing all the way until the final product.

In this thesis, a standard image processing pipeline is first explained. Graphs are then introduced and their usage in image processing pipelines is explained. The possibilities and methods of verifying image processing graphs are investigated. Verification is then used in a real product development project utilizing the modularity obtained from the graphs, starting from the early phases of development and continuing all the way until the final product. Finally, several future improvements and possibilities are considered.

The thesis is organized as follows. Chapter 2 introduces and explains the image capture pipeline. Chapter 3 provides information about graphs and their usage in the image capture pipelines. Verification of image processing graphs is then investigated in chapter 4. Chapter 5 follows a product development project using image processing graphs. In chapter 6, future improvements are discussed. Finally, chapter 7 concludes the thesis.

### 2. IMAGE CAPTURE PIPELINE

In digital photography, image processing plays a key role in the process of obtaining actual human readable images to the screen of a camera. What might seem a simple process from the point of view of the user, is in fact often a very complex one, requiring seamless functionality between different hardware and software blocks. [3]

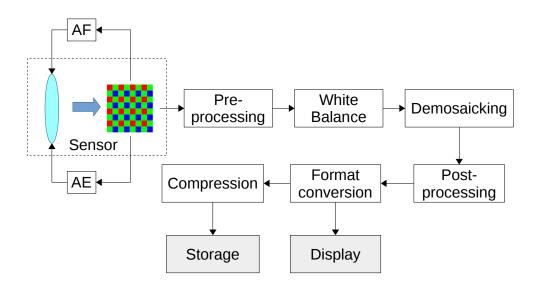

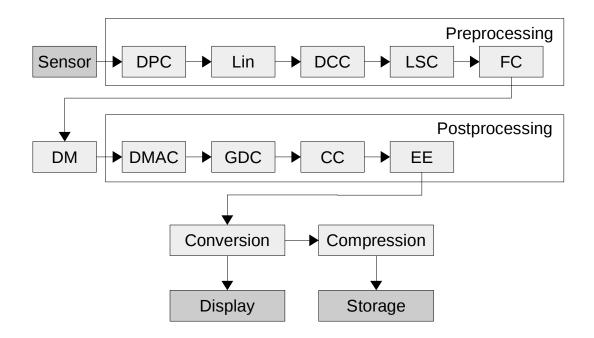

The image capture process begins with capturing light through the lens system onto a sensor. The light received by the sensor will then be converted into electric signals and is furthermore passed forward to be processed. A series of analyzing and processing is performed, until finally a complete image with the required corrections, resolution and format is displayed on the screen or saved to the memory of the device. [48] An example image pipeline is shown in figure 2.1.

Figure 2.1 An example camera pipeline

This example pipeline is only a basic representation of what an image capture pipeline may look like. The amount of different computations, and the order of those computations, change from one product to another. There is no standard

image capture pipeline, but each pipeline is designed to fit the needs and constraints of a certain product. However, using some common elements found in many real image capture pipelines, a basic example pipeline can be created. The following sections describe the different blocks found in the figure 2.1 in more detail.

### 2.1 Image quality

In an ideal case, the captured image that is viewed by the user is an exact representation of the scene that was photographed. However, in a real world the image is subject to many different distortions that happen during the various stages of the image capture pipeline. Image acquisition, processing, transmission and compressing all add some kind of an error to the data. Many of the steps in the processing pipeline try to correct these errors aiming to an enhanced image quality. Because of the limitations in each product, the final outputted image will always contain some errors. [58]

In order to investigate the quality of a captured image, evaluation is required. Image quality assessment can be split into two methods: subjective and objective assessment. In a subjective evaluation [26] the image quality is assessed by humans, while in an objective evaluation [55] the quality is assessed via metrics predicting the image quality automatically. Both methods have their strengths and weaknesses. Depending on the need, either or both methods can be used.

Since most of the images are processed to be eventually viewed by human beings, subjective assessment produces the most reliable outcome [58]. Traditionally, in a subjective assessment the overall quality for the images is evaluated by multiple viewers. Test sequences are presented to the subjects using a specified method and are then rated for quality [26]. Of these ratings a metric called MOS (Mean Opinion Score) or DMOS (Difference Mean Opinion Score) can be calculated to determine the quality of the image [45]. While subjective assessment is reliable, it is slow and expensive and can be very inconvenient, therefore being not suitable for many applications.

Objective assessment on the other hand aims to accurately and automatically measure the different aspects of what human viewers perceive as being good quality. Different metrics are available to be used to measure the quality. The metrics can be classified based on the availability of the perfect quality reference image. Full reference quality assessment assumes that a perfect quality reference image is available, reduced reference quality assessment only has partial data

available from the reference image, and no reference quality assessment has no reference image at all. Objective image quality assessment without any reference data is very difficult and hence full reference assessment is mostly used. [58]

Many objective image quality assessment algorithms have been proposed. Traditionally, the most common full reference image quality assessment metrics have been MSE (Mean Squared Error) and PSNR (Peak Signal-to-Noise Ratio). MSE can be presented the following way [58]:

$$\frac{1}{N} \sum_{i=1}^{N} (x_i - y_i)^2 \tag{2.1}$$

where N is the number of pixels in the image and  $x_i$  and  $y_i$  are the i-th pixels in the reference and distorted images, respectively.

PSNR can be presented based on MSE the following way [58]:

$$10log_{10} \frac{L^2}{\text{MSE}} \tag{2.2}$$

where L is the dynamic range of the pixel values.

The issue with MSE and PSNR is that while they do measure the signal fidelity, they do not accurately predict the human perception of the image quality [56]. This difference is a result of the human visual system characteristics which perceive certain errors in the image differently than what could be interpreted directly from the data.

More advanced metrics that correlate better with the actual perceived image quality have been proposed [15, 40, 45, 56]. SSIM [57] (Structural Similarity Index) takes advantage of the fact that the human visual system is highly adapted for extracting structural information. VIF [49] (Visual Information Fidelity) measures the loss of information extracted by the brain by modeling a natural image source, distortion channel and the human visual system. VSNR [9] (Visual Signal-to-Noise Ratio) is a wavelet-based measurement that takes into account the human visual system capabilities of seeing distortions.

Research shows that with the more advanced objective image quality metrics a better correlation can be achieved between objective and subjective evaluation results than what is achievable with the traditional metrics [40]. However, objective assessment

still does not match the results of subjective evaluation. Nevertheless, especially with the recent developments in the field, objective assessment can be utilized in the image quality evaluation.

### 2.2 Image sensors

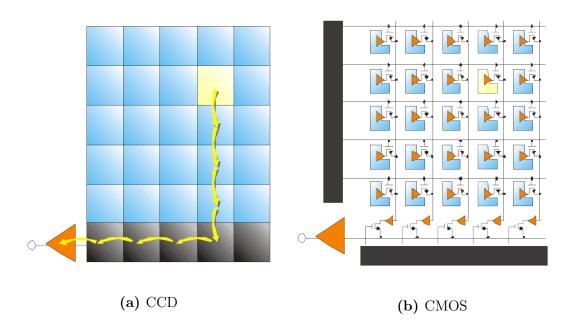

Digital cameras use most commonly two types of sensors: CCD (Charge Coupled Device) and CMOS (Complementary Metal-Oxide Semiconductor). The two types of sensors both sense light through similar mechanics utilizing the photoelectric effect. For each pixel in the sensor, received photons are transformed to an electric charge. The difference between these sensors is how the information stored as a charge is converted to voltage and transferred out of the pixel array. [47, pp. 55-61].

For a CCD sensor, charge is shifted from each capacitor (pixel) to another and the conversion from the charge to voltage is done in the last capacitor. Once this process has been repeated enough, the entire contents of the sensor have been read. For a CMOS sensor, each pixel itself contains a circuit that converts the charge to a voltage. These values can then be read one pixel at a time, allowing also to only read part of the image data if required. [12, p. 5] Both types of sensors can be seen in figure 2.2.

Figure 2.2 CCD and CMOS image sensors [12, p. 6]

Both sensors have their strengths and weaknesses. CCD has been around in digital cameras for a longer period and has been traditionally providing a better image

quality. However, CMOS technology has been rapidly developing and has narrowed down much of the quality gap between the two types of sensors. Because of the limitations in the CCD technology, such as price and power usage, CMOS has been widely used in the lower-end segment of digital cameras, while CCD has been the choice for higher end products. [12]

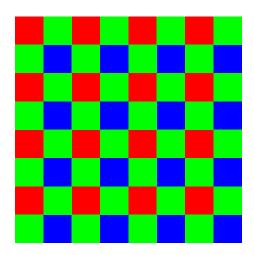

Both of the sensor types described above are monochromatic and hence cannot make a distinction between different wavelengths of light. There exists several ways to overcome this issue. One way is to use multiple separate sensors, each dedicated to a single color, so that when all the images are combined a full colored image can be reproduced. Another method is to use the silicon itself as a filter since the light penetration of the silicon is dependent on the wavelength of the light. This method was used in the Foveon X3 sensor [17], where three photodiodes were stacked on top of each other, each capturing red, green or blue color. However, the most common solution is to pass the light through a CFA (Color Filter Array), so that each pixel only receives light of a certain color, and then later interpolate the full colored image. [12, pp. 8-9]

The most common color filter array filter is the Bayer filter [4], which has 50% green, 25% red and 25% blue pixels [42, pp. 3-7]. This filter is also called GBRG, GRBG, BGGR or RGGB depending on the order of the pixels in one 2x2 bayer quad. The reason for twice the amount of pixels used for green as is for red or blue, is because the human eye behaves in a similar way, being more sensitive to green than to other colors [22, pp. 44-45]. An example color filter array can be seen in figure 2.3. This color filter array is RGGB, as can be seen from the pixel order starting from the upper left corner.

Figure 2.3 Bayer RGGB color filter array

2.3. 3A

Once all the voltage data is read, the pixel values are passed through an ADC (Analog-To-Digital Converter), which transfers the generated digital information further to be processed. [12, p. 5]

Two types of sensor solutions exist in the digital camera domain. SoC sensors contain an integrated SoC, which performs all or part of the required processing internally in the sensor module, and only needs to be controlled by the host as required, providing images ready to be displayed on the screen or saved to the device. Raw image sensors on the other hand only output the captured raw data for which additional processing is still needed. [12, p. 5] In this thesis, the word sensor refers to a raw sensor without any additional processing capabilities.

#### 2.3 3A

3A (3 Algorithms) is the automatic selection of the control values for focus, exposure and white-balance [1]. These three key values greatly affect the quality of the output images [38, p. 694]. Especially in mobile cameras, a majority of the images is taken by simply pointing the device and clicking the shutter release button instead of carefully selecting the suitable values for each by hand. This makes the functionality of 3A, its convergence speeds and human noticeable behaviors in different scenarios crucial to a camera device.

### 2.3.1 Auto exposure

Auto exposure means adjusting the amount of light on the sensor in order to be able to utilize the full dynamic range of the sensor. The adjustment can be done via aperture setting (unless the device has a fixed aperture), shutter speed and ISO speed. Over-exposed and under-exposed images result in lost details that are impossible to be corrected later, so being able to set the exposure values correctly is crucial. [47, p. 238] [48, p. 36]

The image received from the sensor is divided into multiple sub-blocks that are also called AE windows. For each window the average and peak luminance values are calculated. The best fitting combination of the configuration values are then generated automatically by a special algorithm. The values are used in the image sensor for the next image to be captured. This loop is repeated continuously, as the environment can change from one frame to another. [47, pp. 238-239] [48, p. 36]

In a scene that has large brightness variations, the limitations of the sensor results in a situation in which details are inevitably lost, as the dynamic range of the sensor 2.3. 3A

is insufficient. A solution to this problem is called HDR (High Dynamic Range). In HDR images, multiple frames are captured vith varying exposure settings, each frame having the correct values to capture a certain section of the scene. The information from the images is then combined together using a special algorithm, resulting in an image with a substantially higher dynamic range than what would have been achievable with capturing only a single frame. [29]

### 2.3.2 Auto focus

Auto focus, as the name suggests, is focusing the image automatically to a certain point by moving the lens, so that the desired object in the image is not blurred. Two types of auto focus exists: passive auto focus and active auto focus. The difference between these two types is that active auto focus sends some kind of a signal to estimate the distance to the subject, while passive auto focus relies on the information obtained from the image to achieve the desired focus. [48, pp. 36-37]

Active auto focus can send ultrasound [6] or light [59], either in the infrared or visible range, to the object where the focus is desired. The signal is then reflected back from the object to the camera. From the intensity or angle of the returning signal, or the time it takes the signal to return back to the camera, distance between the camera and the object can be calculated, and the lens moved accordingly. [48, p. 36]

In passive auto focus, the captured image is first analyzed for the focus, after which the lens is moved a bit and the image is analyzed again. Depending on whether the move resulted in a better or worse focus, the lens is moved accordingly trying to achieve the correct focus. This loop is iterated as long as it is required to achieve a satisfactory focus. [47, pp. 240-241] [48, pp. 36-37]

Two types of analysis techniques are currently used in passive auto focus. One way is to use the contrast found in the image to find out the current focus [20]. The intensity between adjacent pixels increases when the area is focused, so the correct focus can be found by looking for the maximum intensity difference. The other method is to use phase detection auto focus [51], which compares the light coming through the opposite sides of the lens by using two or more small image sensors. If the object is not in focus, the images are out of phase. The correct lens position can be calculated from the resulted values. [48, pp. 36-37]

#### 2.3.3 Auto white-balance

In the human vision, white is perceived as white even under different lighting. Fluorescent, incandescent and daylight are all of different color, but for example white walls are still seen as white. This is called color constancy. For digital cameras the same is not true. Color intensities will be captured exactly the way the objects emit the different wavelengths of light. A white wall in a red light will be a red wall in the picture. In order to correct this, white balance correction is required. [42, pp. 267-268]

White balance correction is all about neutralizing the color of the light source in the image. First the image needs to be analyzed and the color of the surrounding light needs to be detected. As the automatic detection has its flaws, this can usually be also selected by the user from a set of possible pre-defined light sources. After the color of the surrounding light is known, the image can be corrected to look like it had been taken in white light. [42, p. 268]

The actual correction usually happens by setting the gains of each independent three color signals. Various algorithms exist to produce the correct gain values. One example is the gray world assumption, in which it is assumed that the mean values for all the three color channels should be equal. The gains for two of the three channels can hence be adjusted so that all the three channels have an equal mean value. [42, p. 280]

# 2.4 Preprocessing

The image received from the sensor is in a raw bayer format, each pixel only containing the amount of light received through the specific color filter on top of the given pixel as was described in section 2.2. This data is by no means perfect and requires a substantial amount of processing to produce a satisfactory image [48, p. 38].

Preprocessing deals with the defects in the captured bayer image before a full color image is produced by demosaicking. As all the original pixel values are still available, defects related to individual pixels need to be handled while the image is still in this format and the errors are not mixed with other pixels during interpolation. Another reason for performing corrections as early in the processing chain as possible is to avoid amplifying the defects by algorithms later on. On the other hand, some corrections cannot be performed in the bayer format since the algorithms require the

12

full color image and need to be performed after the demosaicking. [42, pp. 7-9] [48, p. 38]

Some common corrections usually performed in the preprocessing phase are listed below.

- **Defective pixel correction** Some of the pixels in the sensor may be defective. Without correction these pixel values would show up as errors in the image after the demosaicking, as the values of the color image pixels are interpolated from the neighboring pixels. Defective pixel values can be replaced using average values from the surrounding pixels. [44]

- **Linearization** Not all the data received from the sensor is linear because of the electronics involved in the sensor. Therefore, linearization is required, which means transforming the raw measured nonlinear data into a linear space. [48, p. 38]

- Dark current compensation Receiving no light at all into the sensor does not actually produce zero values as could be expected. This phenomenon happens because a current is flowing through the photodiodes even when no photons are received. To account for this, an average dark current value can be calculated, which then needs to be subtracted from the values received from the sensor in order to capture the black level correctly. [42, p. 70] [48, p. 38]

- Lens shading correction The optics of the camera also produce some artifacts. Lens shading, also called vignetting, appears in the corners of the image due to the physical properties of the lens. This needs to be linearized, requiring the usage of lens shading correction. [60]

- Flare compensation In images that have a high source of light, light scatters in the optics of the camera, which causes a shift in the received energy. This distortion is called the lens flare, for which a flare compensation is needed. Plainly, flare compensation reduces the pixel values in the image near the affected pixels. [48, p. 38]

# 2.5 Demosaicking

After the required analyzations and corrections are finished in the RAW bayer format, the image needs to be converted from a grayscale bayer to a full color image. This step is called demosaicking, and is usually the most compute intensive step in the processing pipeline [22, p. 44].

In order to be able to represent a full color image, each pixel needs three color values. Traditionally in computer images the values have been red, green and blue. In single sensor systems, a color filter array is used as is explained in section 2.2. This means that for each pixel in the image, two out of three color image values are missing. The missing values need to be estimated based on the rest of the image. [22, p. 44]

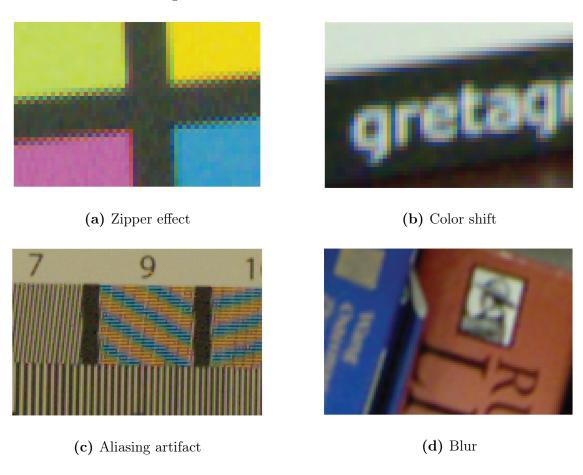

Demosaicking is also called color filter array interpolation since each missing value needs to be interpolated from the surrounding pixels. Naturally, whenever data is interpolated, accuracy is lost as the result is only an estimation of the original. Several different algorithms exist to perform the demosaicking. Different algorithms may trade image quality in favor of performance while some may produce more artifacts than others to the image that need to be corrected in post-processing. [22]

Demosaicking has a high impact to the rest of the pipeline and to the overall quality of the outputted image. The output quality has to meet the requirements, and any artifacts generated by the algorithm need to be corrected later. Some common artifacts are shown in figure 2.4.

Figure 2.4 Common demosaicking artifacts [42, p. 14]

### 2.6 Postprocessing

After all the required preprocessing steps and the successive demosaicking is complete a viewable image exists. This image is in a color space that has all the required color components for each pixel in order to reproduce a complete color image. However, some corrections are still to be done in this step now that the proper image with separate color channels is available. Also, the previous steps in the pipeline introduce some artifacts and distortions that need to be corrected in order to produce an image with an acceptable quality. This part of the pipeline is called postprocessing.

Some common corrections usually performed in the postprocessing phase are listed below.

Demosaicking artifact correction Some of the artifacts present in the image depend on the processing algorithms used. For example, the demosaicking algorithm may produce, depending on the input image and the algorithm used, zipper effect, color shift, aliasing artifacts or blur (figure 2.4). These artifacts need to be corrected while still retaining the sharpness of the image. [48, pp. 40-41]

Geometric distortion correction The lens optics introduce distortion that affects the image. Geometric distortion, for example barrel distortion, misplaces information geometrically. In other words, pixels in the image present information that should be elsewhere. [61] In addition, various wavelengths behave differently in the lens because of different refraction indexes, creating chromatic aberration where different colors are not focusing correctly in the same place. [36] Geometric distortion correction is performed to correct these artifacts.

Color correction Colors captured by the sensors do not match that what is considered a pleasant image by humans since the color sensitivity of the sensor is different than that of the human eye. The captured image needs to be transformed into a calibrated color space which is the purpose of color correction. [42, pp. 77-78] [48, p. 40]

Edge enhancement The human eye is very sensitive to sharp edges [48, p. 41]. Therefore, a step that performs edge enhancement, or in other words sharpening, is usually performed. The purpose of this processing is to make the image look sharper by amplifying the high-frequency components of the image. [42, p. 80]

As part of the correction algorithms required depend on the previous steps in the pipeline, postprocessing needs to be adapted to the sensor, preprocessing and demosaicking algorithms used. Therefore, there may be great variance in the post processing between devices, and each device needs to be configured separately.

#### 2.7 Format conversion

Depending on the device and the use case of the processing pipeline, additional color space conversions may be required. While the RGB format may be useful in some of the aforementioned image processing algorithms, it is not a practical format to store the data.

For RGB formats, each color channel has the equal amount of information. For example RGB888 uses a total of 24 bits to store the information for each pixel [52]. The larger the images are, the higher the burden is to store, transmit and display the data. Therefore, other formats with a lower bit rate are needed.

#### 2.7.1 YUV

A frequently used way to reduce the amount of data used for an image is to take advantage of the biological capabilities of the human vision system. The human eye is less sensitive to color differences than it is to luminance differences [25]. The method taking advantage of this fact reduces the amount of data of color in the image, while still keeping the same amount of data for the brightness. This is called chroma subsampling [14].

Obviously this kind of data reduction is impossible to do in the RGB color space as the brightness of each pixel is a combination of each color value, all three represented separately. The solution for this is to use an image format where luminance and chrominance values are separated. These formats are referred as  $Y'C'_BC'_R$ , where Y' is the luminance,  $C'_B$  is the difference between blue and the luminance, and  $C'_R$  is the difference between red and the luminance. [27, pp. 16-18]

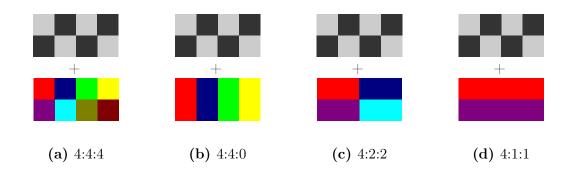

After the chrominance has been separated from the luminance, the data of the chrominance can be reduced while still sustaining the original luminance information. Usually this chroma subsampling is notated as a three part ratio A:B:C [52]. The ratio tells us that in a sample region that is A pixels wide and 2 pixels high, there are B horizontal chroma samples, and C changes in the chrominance values between the first and the second row. Some commonly used examples are given below and can be seen in figure 2.5.

- **4:4:4** Each pixel has both luminance and chrominance samples. This format has no chroma subsampling at all. Full horizontal and vertical resolution.

- **4:4:0** Each pixel in the first row has chrominance samples, but these are shared between two rows. Full horizontal resolution, ½ vertical resolution.

- **4:2:2** For 4 pixels in the first row, two chrominance samples exist. Each row has its own samples. ½ horizontal resolution, full vertical resolution.

- **4:1:1** For 4 pixels in the first row, only a single chrominance sample exists. Each row has its own samples. ¼ horizontal resolution, full vertical resolution.

Figure 2.5 Different YUV subsampling ratios. The above pixel array describes the luma samples and the below pixel array describes the chroma sample pairs.

Depending on the required quality of the output and the restraints of the storage size of the image, an appropriate subsampling ratio is chosen. Of course it goes without saying that the less there are chroma samples, the lower the quality of the image will be.

Different YUV formats exist even with the same subsampling ratio. Luma and chroma values can be combined into macro pixels (packed formats), or they can be in separate planes (planar formats). The chroma planes may also be interleaved in different ways or the image may have some padding. The range of different YUV formats is vast. [16]

# 2.7.2 Compression

While the chroma subsampling in the YUV formats lowers the bandwidth needed for the images and may be enough to satisfy the needs of storing, transferring and displaying a single image, this still leaves the images with a storage size too large for many uses. For example, in mobile devices the available disk space for storage may be a bottleneck especially in the lower end segment. Compression is needed to overcome this problem.

A commonly used compression method for digital images is JPEG (Joint Photographic Experts Group) [54]. This method is lossy, meaning that information is lost in the process. However, JPEG takes advantage of the human visual system in a way that makes high compression possible without reducing the quality of the image below a satisfactory level.

JPEG compression is done to images in the YUV color space. The chroma subsampling already explained in the section 2.7.1 is also usually used in the JPEG compression. The YUV image is then split into 8x8 blocks called macroblocks. After this, macroblocks are converted into frequency domain by DCT (Discrete Cosine Transform). The values are then quantized by dividing each component by a constant and rounding them to the nearest integer, reducing information in the high frequency domain. The resulted values are finally encoded using run-length encoding and huffman coding. [54]

JPEG standard supports different compression ratios enabling the user to select the best tradeoff between image quality and the resulting image size. In practice, the compression ratio is chosen by setting the quantization table [54], which is the only lossless part of the JPEG encoding apart from the chroma subsampling. Images compressed with a low ratio are usually indistinguishable from uncompressed ones by the naked eye, while higher ratios might still be adequate for certain use cases but have noticeable artifacts.

Video capture, where multiple frames are captured and combined together, requires much more information to be stored than what is the case with still images. Therefore, compression is especially important with videos. JPEG can also be used for video compression [39]. However, it is quite inefficient since no temporal redundancy is used. This means that pixels having the same data from one frame to another is not exploited in the compression.

Several compression standards specifically aimed to be used for video compression exist. Common video coding formats include Motion JPEG [39], MPEG-4 [46] and H.264 [2] among others. Motion JPEG is the video compression based on the JPEG image compression. MPEG-4 and H.264 on the other hand use several frames to compress the stream, taking advantage also of the temporal redundancy in addition to the spatial redundancy.

### 3. GRAPHS

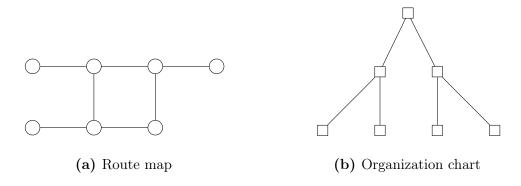

Graph is a set of points and lines connecting the points. Graphs can be used to describe many different situations in real word and have applications in a variety of different areas [8]. An example application of the graphs in the physical world is to represent all the possible routes from one place to another like a subway map. Another everyday example is a company organization chart. Example illustrations of these graphs can be seen in figure 3.1

Figure 3.1 Example applications of graphs

These graphs can be used to solve problems like what is the fastest or shortest route from one place to another, or who is the manager of a given person in the organization. Of everyday graphs similar to these, a mathematics branch called graph theory has emerged, dating back to 1735 and the Königsberg bridge problem [8]. The following sections give an overview of the graph theory and their applications in the computing domain.

# 3.1 Basic graph theory

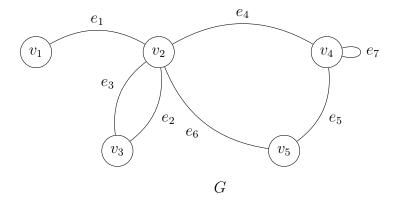

A graph consists of a finite set of objects called vertices and a finite set of unordered pairs of the vertices. A graph can be represented as a diagram where vertices are points, and the elements of the ordered set, called edges, are lines connecting the points. [7, p. 1] [13, p. 2] An example graph can be seen in figure 3.2.

Figure 3.2 Example graph diagram

In this graph, V is the set of vertices, and E is the set of edges. The graph itself is labeled with a letter, in this case G = (V, E). The two vertices of an edge are called the end vertices. An edge, which has the same vertex as both of its end vertices, is a loop. Edges with the same end vertices are parallel. Edges that share one end vertex are adjacent. The amount of adjacent edges to a vertex is the degree of the vertex. A graph that has neither loops nor parallel edges is simple. [7, pp. 1-3] [13, pp. 2-5] Similar labeling and terminology will be used throughout this thesis.

In the graph in figure 3.2, we have both parallel edges and a loop, therefore the graph is not simple. Edges  $e_2$  and  $e_3$  both have the same end vertices and are hence parallel. Edge  $e_7$  has the same vertex as its both end vertices, which means the edge is a loop.

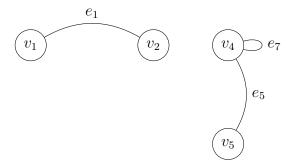

Subgraph is a graph that is part of another graph. In other words, all its vertices and edges are in the other graph. More formally,  $g \subseteq G$  if  $E(g) \subseteq E(G)$  and  $V(g) \subseteq V(G)$  [13, p. 4]. Two example subgraph diagrams of the graph in figure 3.2 are presented in figure 3.3. It should be noted that the graph representation in the graph diagram, meaning the placement of the vertices and edges in the drawing, has no meaning. Two graphs are equal if they both contain the same edges and vertices [7, p. 2].

A walk is a finite sequence of alternating vertices and edges. Each walk begins and ends with a vertex, and each edge is incident with both the preceding and the following edge. Starting from the initial vertex and concluding to the terminal vertex, the length of the walk equals the number of edges in the walk. Vertices  $v_{it-1}$  and  $v_{ik}$  are the end vertices of  $e_{jt}(t=1,...,k)$ . A walk with the length of 0 only

Figure 3.3 Example subgraph diagrams of graph in figure 3.2

consists of a single vertex. A walk is open if  $v_{i0} \neq v_{ik}$  and closed if  $v_{i0} = v_{ik}$ . [7, p. 12] For example a walk in the graph in figure 3.2:

has the length of 4 and is open since the end vertices are not the same  $(v_1 \neq v_4)$ .

Another walk:

has the length of 3 and is closed since both the end vertices are the same  $(v_2 = v_2)$ .

A trail is a walk, which contains each edge at most once. Both examples above are trails, since no edge appears more than once in either walks. A trail is a path if it does not contain any vertex more than once, not including the end vertices that can be the same. [7, p. 12] The second example is a path since no vertex except the end vertices appears more than once. The first example on the other hand contains  $v_2$  twice and is not a path. Path is a cycle if both the start and the end vertices are the same [7, p. 7]. The path in the second example is a cycle. Trails and paths in a graph G are also subgraphs of the graph G.

A graph is connected if any of the vertices can be reached from any of the other vertices by traversing the edges [7, p. 13]. In other words, a path exists from every vertex to every other vertex. The graph in figure 3.2 is connected.

# 3.2 Directed graphs

The graphs presented earlier, in which all the edges are bidirectional, are undirected graphs. Directed graphs, also called digraphs, are graphs in which the edges are directed from one vertex to another. One vertex is a start, and the other is a finish. These edges are also called arcs. [7, p. 171] Directed graphs can be drawn as

3.3. Data flow

undirected graphs but with arrows instead of lines representing edges. An example directed graph is seen in 3.4.

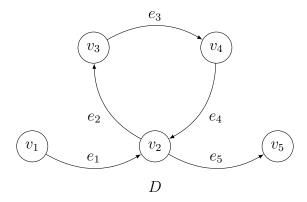

Figure 3.4 Example directed graph diagram

Directed graphs also allow some additional definitions. A vertex that only has arcs leading away from the vertex (indegree is zero) is called a source. Likewise, a vertex that only has arcs leading into the vertex (outdegree is zero) is called a sink. Walks, trails and paths work similarly with directed graphs as they do with undirected graphs, expect that they take into account the direction of the graph. [13, p. 125]

One useful special case of graphs is a DAG (Directed Acyclic Graph). This graph is directed and does not allow any cycles to occur. DAGs are useful in situations where certain tasks have a strict priority relationship - a task cannot be done before another is finished. All the precedence requirements are automatically described in the graph by following the directions. The reason why some applications benefit from DAGs that do not allow cycles is because a cycle would indicate a task that is a prerequisite for itself and the prerequisites would be infinite. An example DAG can be seen in 3.5.

#### 3.3 Data flow

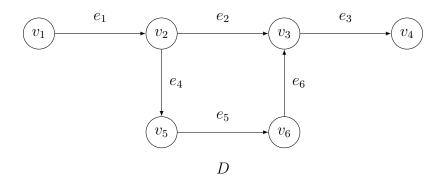

For applications that perform processing to data, the flow of the data can be represented using directed graphs [5]. At simplest, the graph consists of a source, vertex, sink and arcs combining the elements together. Source represents the interface to which the data is fed into, vertex represents the computation performed to the data, and the sink represents the interface where the processed data is finally outputted. Data flow graphs can naturally be much more complex, consisting of multiple sources, vertices and sinks. The example directed graph D in figure 3.5 could also represent a data flow,  $v_1$  being the source and  $v_4$  the sink.

3.3. Data flow

Figure 3.5 Example directed acyclic graph diagram

In order to ease the usage of the data flow graphs in any real world applications, several restrictions can be defined. Naturally, the vertices can only be dependent on the data of the inbound arcs. However, it is typically allowed that data staying constant over all the graph cycles can be provided by other means. This allows for example configuring complex hardware to operate in a certain way. In addition to the data resource restrictions, also the when and how the vertices are fired is typically a part of the data flow graph models.

A widely known data flow graph model is SDF (Synchronous Data Flow) [37]. Each vertex in the SDF graph needs to be a specific function that can be invoked after the input data for that vertex is available. There cannot be any side effects for any vertices. The only interactions between separate vertices can happen through the arcs connecting them. The amount of items consumed and produced by each vertex is known statically. Many applications and APIs especially in the imaging context are defined after these basic foundations.

The independence of the vertices allows the graphs to be modular. Vertices can be reused in different configurations and their ordering in the graph does not affect the internal computation of a single vertex. In other words, the computations are deterministic. Also, the granularity of the graph can vary significantly. A vertex can be implemented by a subgraph that performs the computation in an arbitrary number of vertices or all the subgraph vertices can be included in the SDF graph.

Since the vertices are black boxes to the outside observer, any form of operation may occur behind the interfaces of the vertex. The implementation of a certain vertex can be done on many different platforms like CPU, DSP or fixed hardware blocks. Two graphs can be functionally equivalent even if different implementations

are used. What matters is that for a given input to a graph, a known output can be received.

SDF allows efficient scheduling of the different vertices since it is known exactly when the vertices are ready to be executed. SDF graphs also provide the ability to execute separate vertices concurrently. Since each vertex is independent, given that the inputs for all the vertices going to be fired are ready and hardware resources are available, they can be executed in parallel. [37]

#### 3.4 Software frameworks

In order to take the aforementioned data flow graphs to a practical level in imaging, a software based framework capable of presenting operations as a graph to programmers is valuable. The frameworks can also allow running consecutive elements in parallel which is called pipelining [23]. Depending on the resource availability, pipelining can be used achieve notable performance increases.

There exists many different frameworks publicly available. All frameworks have their own capabilities and limitations, and a framework best suiting the needs of the product should be chosen. A short overview of widely used pipeline frameworks available is given below.

#### **OpenMAX**

OpenMAX is a set of open cross-platform APIs defined by the Khronos Group [31]. The main purpose of these APIs is to provide a set of standardized layers enabling the development and integration of multimedia components across different operating systems and platforms. The standard is split into three parts, OpenMAX AL, OpenMAX IL and OpenMAX DL. Moving from the bottom of the stack upwards, the OpenMAX DL is the development layer which defines a set of low-level multimedia kernels that can be used to accelerate traditional computational hotspots in media codecs [32]. OpenMAX IL is the integration layer which defines the standardized API for different audio, video and imaging components providing encapsulation and portability [33]. OpenMAX AL is the application layer that defines a set of multimedia use cases to be used by applications, like video playback or image capture, that can be constructed by connecting multiple IL components together [34].

#### OpenVX

OpenVX is an open standard for computer vision application acceleration defined by the Khronos Group. The idea is to allow cross-OS (Operating System) and cross-platform portability with minimum effects on the applications. OpenVX is graph based, and the APIs are defined in C. The standard does not define the implementation of the framework, but the APIs for building, verifying and coordinating graph execution, and for accessing memory objects. [35]

#### Gstreamer

Gstreamer is a cross-OS multimedia framework written in C. The framework is distributed under GNU Lesser General Public License, and is therefore open source and copylefted. The supported platforms include Linux, Windows and OSX among others. Gstreamer includes many plugins of its own, providing an extensive library of elements, and supports extending its capabilities through plugins. Gstreamer also has API bindings to many other programming languages than C which it natively supports. [21]

#### **DirectShow**

DirectShow is a multimedia framework for Windows developed by Microsoft. DirectShow consists of filters, which are the software components performing some operations for the multimedia stream. Applications then perform tasks by creating filter graphs which are constructed by connecting different filters together. DirectShow can be used for video and audio playback and capture. [43]

#### V4L2

V4L2 (Video4Linux2) is a Linux kernel video capture and output driver framework. It is written in C and is licensed as GNU General Public License. Different hardware blocks are exposed as V4L2 devices, which can be configured and connected as requested. Using media controller that is a part of V4L2, these devices can then be used and connected together to form a graph. V4L2 can be used in a variety of applications like image capture, radio controlling or digital video broadcast receiving. [41]

#### 3.5 Graph implementation

Each graph is defined to a certain task. Data flows from the source through each vertex and finally reaches the sink. With a sane input a valid output is received. The vertices in the graph define what is to be done to the data. However, the graph does not dictate how each vertex is to be implemented. The graph only governs the order and the dependencies of the vertices.

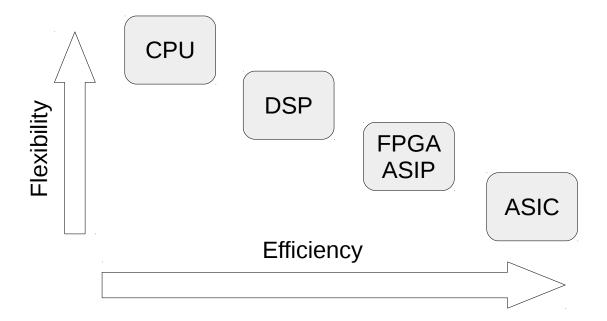

The implementations for each vertex can be done on any supported compute resource. With today's SoCs, devices have become heterogeneous and implementations can be for example pure hardware, firmware running on specialized processors, or just software executed on a CPU [53]. Based on the product requirements, appropriate implementations are designed. A figure showing the tradeoff between efficiency and flexibility of some of the different technologies can be seen in 3.6.

Figure 3.6 Flexibility in relation to efficiency in different technologies

Implementations can also combine multiple vertices into a single vertex if required. This can be useful for example to allow performance enhancements via reducing the memory bandwidth between vertices by performing all steps of an algorithm on the same target without the need for host control. While the implementation can be highly optimized for a given platform, this makes the granularity of the graph coarser.

Encapsulating the vertices behind a standardized API allows the development of separate vertices in isolation. Vertex implementations could potentially be done by separate teams or even companies. Ready implementations can then be connected together using a common framework as the interoperability of the vertices is guaranteed by the specification. Encapsulation also provides benefits related to reuse. As the requirements for each product differ from one another, being able to flexibly create new graphs reusing the already existing implementations is a major advantage.

With software development starting very early in the process of developing the device when the actual hardware implementation is not ready, the modularity provided by the graphs is an efficient way to enable development of the software earlier than traditionally. Traditionally software development has only begun after a prototype hardware is available [53]. An example traditional schedule can be seen in figure 3.7. However, with the complexity of today's systems, this no longer fits the needs of the time to market requirement of the products. A shift left approach is needed, in which software development is performed concurrently with the hardware development. The shift left software schedule can be seen infigure 3.8.

Figure 3.7 Traditional hardware and software development schedule

Graphs provide a systematic way to utilize shift left. As the implementation of the vertices in a graph is meaningless from the point of view of the user, work with several of the technologies used in the development phase of the device can be enabled. At the beginning of the product development, only rudimentary implementations of different processing blocks may be available. Some of the implementations may be missing and may need to be replaced for example with generic CPU software that is lacking the image quality and processing speed present in the real implementations.

Gradually new implementations will be available. New development platforms will be enabled. Development moves from software stubs to emulation and finally to real prototypes. The hardware will start resembling more and more what it will be in the final product.

Figure 3.8 Shift left software development schedule

A list of commonly used development platforms is given below.

- **Software stub** can be used to begin development of software without any real software or hardware implementations below. Stubs can implement the required low level APIs by just providing some initial responses regardless of the input.

- **Simulation** is simulating the behavior of a system. Simulation does not perfectly replicate the actual target being simulated but provides behavior similar to that.

- **Software emulation** is emulating the behavior of a system using software. This can for example emulate the behaviour of lower level APIs to allow the development and verification of higher level software layers.

- **Hardware emulation** is emulating the behavior of a system using hardware. For example, an FPGA can be used to emulate the system accurately with impacts only to the performance.

- Hardware prototype is a prototype of the actual device. Prototypes are the development platforms closest to the actual finished products. They contain the real hardware that is going to be in the final product although some changes can still be done to later revisions.

These development platforms can be used to enable software shift left and verification beginning from the early stages of the product development until the final product by using implementations for platforms available at each time. Traditionally handling the complexity of different implementations and compute resources has been hard. Individual blocks may have been tested independently, but it has not been consistent across all algorithms. This means less reuse and higher risk in further development phases.

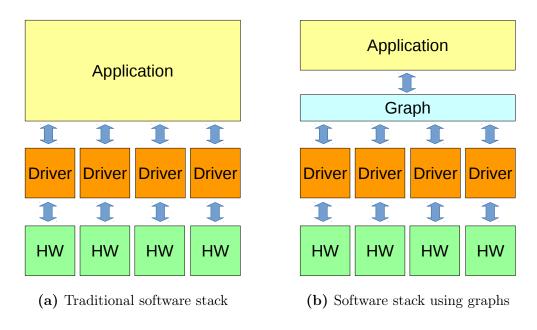

Utilizing different resources require changes in the whole software stack which potentially has an effect all the way up to the application layer. This makes development and maintaining the software stack cumbersome. With graphs, however, the complexity of the underlying computing can be abstracted and managed in a simple way. Example software stacks without and with graphs can be seen in figure 3.9.

Figure 3.9 Example software stacks without and with graphs

Graphs can expose any external requirements needed, for example to allocate the required memory buffers, to the layers above in a generic way independent of the vertex implementations. This allows us to encapsulate the whole functional complexity behind generic interfaces. In other words, the software stack above the graph does not need to know about the implementation details of the graph, and any changes to the implementations can be hidden from the applications.

## 3.6 Graphs in an image processing system

The camera capabilities of a product can range from simple fixed surveillance cameras to highly complex devices providing vast amounts of features and different operating modes. As the devices have become more capable and rich in features, handling the complexity of subsystems (e.g. camera) has become increasingly difficult. For example in mobile devices, camera requires seamless cooperation between traditionally separate domains like display, graphics, storage and a variety of other sensors. As described in the previous section, graphs can be used to handle and hide the complexity from the above software layers.

Camera pipelines introduced in chapter 2 can be modeled as data flow graphs. Image comes in from a source, goes through the required processing vertices, and is finally outputted through a sink. The example pipeline shown in figure 2.1 is represented as a data flow graph in figure 3.10.

Figure 3.10 Image processing data flow graph

Capturing and processing images can be divided into multiple different use cases. Differences between use cases may be subtle or major, but nevertheless require implementations that differ from each other. Graphs provide a means to handle these different configurations.

Some of the differences may be supported by just reconfiguring the graphs while others require completely new graphs and vertices. For example, in order to obtain

better performance, some enhancements may be turned off by removing the related vertices from the graph. Vertices may also support different configuration options, for example to change the resolution or the intensity of the correction algorithms.

The following are examples of requirements in the graphs that may change from one use case to another.

- **Frame rate** is the amount of frames that pass through the processing system in a given amount of time. Usually measured as FPS (Frames Per Second) that is the average number of frames processed in a second.

- **Latency** is the amount of time that it takes for a frame to travel from a source to the sink. Can vary from one frame to another even if the average frame rate over a longer time period is relatively constant.

- **Resolution** is the amount of pixels in the images. Higher resolutions produce images with more details and allow more aggressive cropping without resulting in a pixelated image. On the downside, higher resolutions result in more requirements for processing power and memory bandwidth.

- **Image quality** is the quality of the outputted processed image. Depending on the use case, different aspects of the image quality may be required or sacrificed in favor for other requirements.

- Number of sinks can vary from one use case to another. In addition to the main image that is outputted, other versions of that image may be required. When the use of the sink is known, a less or more demanding compute path may be selected. The result may also be a side product of an intermediate algorithm in the main path.

- Additional processing may also be introduced in special imaging cases to analyze the image in ways that the standard use cases do not. For example, computer vision may perform a wide variety of algorithms to produce specific metadata from the images.

The three basic use cases in a mobile camera are examples that have different requirements from one another. When the user is preparing to take a picture, a preview of the image to be captured is shown on the screen of the device (viewfinder) before the user presses the button to do the actual capture. Since each frame is only shown on the screen for a fraction of a second, the image quality in the preview is not that important, and the resolution only needs to match the

display of the device. The main thing that matters is that the user gets real time information about what is going to be included in the captured image. Therefore, low latency and adequate frame rate is required.

With the actual still image capture, however, image quality is one of the most important factors. The captured image will be stored in the device memory in addition to showing it on the screen, and the image quality should be as good as possible. Resolution is preferably the highest available so that the images will look good on a larger screen also. Frame rate is not that important as long as an image can be acquired within a reasonable time frame. Traditionally, shutter lag is more important than the processing latency.

While the preview and capture represent the two basic use cases in a mobile camera that have different requirements, video can be considered being somewhere in the middle. In video recording, the frame rate is a constant value that needs to be acquired. Latency needs to be kept within boundaries or frames will be dropped. Image quality is made as good as is possible with the performance requirements.

Apart from the three basic use cases in mobile cameras, the potential amount of different configurations even in a mobile device is huge. Camera can be used in a wide variety of different ways. Some users may be satisfied with a recognizable face in video calls while others try to replace a professional digital camera with it. On the other hand, what humans view as a high quality image may not be true for certain algorithms trying to interpret information from it. Augmented reality provides additional overlay to the environment captured by the camera requiring recognition of the surrounding objects from the image. User recognition during login or other secure access using face detection or iris scanner needs to obtain an image from which the algorithm can recognize the user.

While there are certainly more than enough use cases in mobile cameras to make them complex, the matter is further complicated once the same or similar platforms are used in different products in the imaging context. Surveillance cameras for one may include additional intelligence to track persons or vehicles. Robots require knowledge about their environment and may need specialized cameras to obtain it. Night vision devices concentrate on providing a viewable image from an otherwise dark environment while the traditional quality of the image does not matter.

All these use cases combined with the configurability of image resolutions and other parameters provide the reason for using graphs. Vertices can be reused, replaced or reorganized. Implementations can be done on any compute resource available.

Essentially, the complexity of the underlying processing system can be handled in a single graph and be hidden from the above software layers.

# 4. VERIFICATION OF IMAGE PROCESSING GRAPHS

Each image processing graph needs to be verified in order to ensure that the graphs are working according to the specification. Verification is not a simple task, however. What to verify from the graphs and how the data interfaces can be measured in a way that supports the verification? Which methods should be used to ensure that the image quality and performance meet the requirements?

Verification in general can be split into two different categories: static and dynamic verification. Static verification (also called formal verification) means statically verifying the implementations using mathematical formulations [18]. In static verification, either two implementations are compared with each other or the implementation is otherwise showed to satisfy the specification. Static verification can theoretically show that the implementation satisfies the specification under all inputs. However, in practice it can be infeasible to convert the implementations into the required mathematical form.

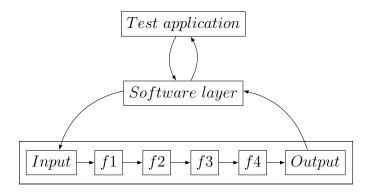

Dynamic verification (also called testing) on the other hand means verifying the implementations while the system is actually running using a finite set of test cases [18, 50]. Input is provided to the implementations and the outcome is examined. As dynamic verification only uses the input and output interfaces of the implementations, there is no need to know the internal details of the implementations, which in turn allows black box testing. Dynamic verification can only be used to verify an implementation to a certain point, as in practice a complete set of tests can be considered infinite [50]. The coverage of the test cases is limited by resources available and the test cases need to be created based on risk and prioritization.

There are several aspects to the graph verification. The functionality of the graph needs to match that of the graph specification. Performance of the graph has to be greater than or equal of what is required by the specification. The graph needs to also be stable, or at least stable enough to exceed the required criteria. Since the implementations behind the vertices are unrestricted, static verification that requires

details of the implementations is infeasible from a graph point of view. Therefore, dynamic verification suits the needs of graph verification more adequately. Naturally, this does not restrict the use of static verification separately in the development of each implementation if deemed suitable and useful.