# TALITA TOBIAS CARNEIRO DISTRIBUTION OF LOW LATENCY MACHINE LEARNING ALGORITHM

Master of Science thesis

Examiner: Prof. Timo Hämäläinen Examiner and topic approved by the Faculty Council of the Faculty of Computing and Electrical Engineering on 29th August 2018

#### **ABSTRACT**

TALITA TOBIAS CARNEIRO: Distribution of Low Latency Machine Learning

Algorithm

Tampere University of Technology Master of Science thesis, 71 pages

December 2018

Master's Degree Programme in Information Technology

Major: Pervasive Systems

Examiner: Prof. Timo Hämäläinen

Keywords: Neural Networks, Inference Accelerator, FPGA, Machine Learning, Ultra-Low

Latency, Mobile Networks

Mobile networks are evolving towards centralization and cloudification while bringing computing power to the edge, opening its scope to a new range of applications. Ultra-low latency is one of the requirements of such applications in the next generation of mobile networks (5G), where deep learning is expected to play a big role. Hence, to enable the usage of deep learning solutions on the edge cloud, ultra-low latency inference must be investigated.

The study presented here relies on the usage of an in-house framework (CRUN) that enables the distribution of acceleration on data center environment. The objective of this thesis is to leverage the best solution for the inference of a machine learning algorithm for an anomaly detection application using neural networks in the edge cloud context. To evaluate the obtained results with CRUN a comparison work is also carried out. Five inference solutions were compared using CPU, GPU and FPGA.

The results show a superior performance in terms of latency for all CRUN experiments, that basically comprehends three cases. The first one utilizing the RTL anomaly detection neural network as a baseline solution, the second using the same baseline code but unrolling the biggest layer for obtaining reduced latency and the third by distributing the neural network in two FPGAs. The requirements for this solution were to obtain latency between  $20\mu s$  to  $40\mu s$  for inference time and at least 20 000 inferences per second. These goals were categorically fulfilled for all CRUN experiments, providing 30  $\mu s$  latency in average, while the second best solution provided 272  $\mu s$ .

II

**PREFACE**

First of all, I thank God for my life and all the blessings that I have received.

This thesis work is part of a bigger project at Nokia. I would like to express my gratitude to the company for the opportunity of developing and writing my thesis, even during working hours. This support was immeasurable.

A big thank you goes to my supervisor Prof. Timo Hämäläinen for the guidance during the entire thesis writing.

I would like also to thank my colleagues in Nokia for the support and advices provided for the writing of this thesis. In special, my sincere acknowledgment goes to Petri Kärppä for valuable technical and academic guidance during this work. Also, my profound gratitude to Jouni Siirtola for the technical background and restless help with the work carried out here. I am grateful to Jouni Markunmäki for guidance and Juho Tieaho for the cooperation during this thesis work. Additionally big thanks go to Pekka Jokela, Hannu Tulla, Anssi Örn and Kalle Holma.

I deeply appreciate the support of my family, in special, my mother Nilceia de Fátima Tobias Carneiro, whose love and care has been the foundation of my life and my late father Jorge Tobias Carneiro who never, even in his wildest dreams would have thought that his own daughter would graduate in Finland.

Finally, I wish to give my deepest thank you to my partner in all aspects of my life Daniel Koslopp, whose love and support keep me alive.

Tampere, 18.11.2018

Talita Tobias Carneiro

## TABLE OF CONTENTS

| 1. | Introduction                                    | 1  |

|----|-------------------------------------------------|----|

| 2. | Mobile Networks and Cloud Computing             | 4  |

|    | 2.1 C-RAN                                       | 5  |

|    | 2.2 NFV and SDN                                 | 8  |

|    | 2.3 Deep Learning in Mobile Networks            | 9  |

| 3. | Neural Networks                                 | 13 |

|    | 3.1 Mathematical Definition                     | 14 |

|    | 3.2 Concept Definitions                         | 16 |

|    | 3.3 Training and Inference                      | 16 |

|    | 3.4 Inference's Computational Load              | 17 |

|    | 3.5 Execution Platforms                         | 18 |

|    | 3.6 Network Model Optimizations                 | 19 |

|    | 3.7 Algorithmic Optimizations                   | 22 |

| 4. | Inference Accelerators                          | 24 |

|    | 4.1 Hardware Efficient Design                   | 24 |

|    | 4.1.1 Parallelism Exploitation                  | 25 |

|    | 4.1.2 Resource Utilization                      | 26 |

|    | 4.2 System Architecture                         | 28 |

|    | 4.2.1 Hardware                                  | 28 |

|    | 4.2.2 Software                                  | 29 |

|    | 4.3 Tools and Architectures                     | 31 |

|    | 4.4 Inference Accelerators in Cloud Environment | 33 |

| 5. | Methodology                                     | 35 |

|    | 5.1 Reference Implementations                   | 35 |

|    | 5.1.1 CPU & GPU                                 | 36 |

|    | 5.1.2 Xilinx GEMX                               | 36 |

|    | 5.1.3 Xilinx SDAccel                            | 37 |

|     | 5.2    | CRUN Implementation   | 38 |

|-----|--------|-----------------------|----|

|     | 5.3    | Validation            | 40 |

| 6.  | Impl   | lementation           | 41 |

|     | 6.1    | CRUN Architecture     | 41 |

|     | 6.2    | Anomaly Detection MLP | 46 |

|     | 6.3    | RTL Implementation    | 47 |

| 7.  | Resu   | ults and Analysis     | 52 |

|     | 7.1    | Performance           | 52 |

|     | 7.2    | Resource Utilization  | 58 |

|     | 7.3    | Design Complexity     | 59 |

|     | 7.4    | Limitations           | 60 |

| 8.  | Cone   | clusions              | 61 |

| Bil | oliogr | raphy                 | 63 |

## LIST OF FIGURES

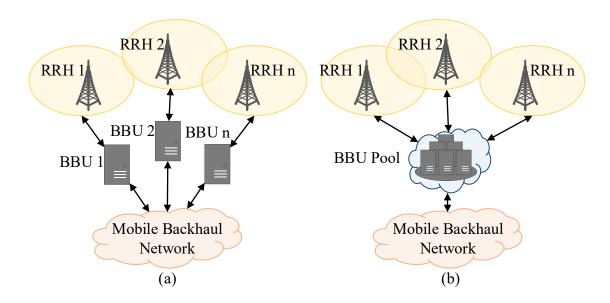

| 2.1 | Traditional and C-RAN based architecture                    | 6  |

|-----|-------------------------------------------------------------|----|

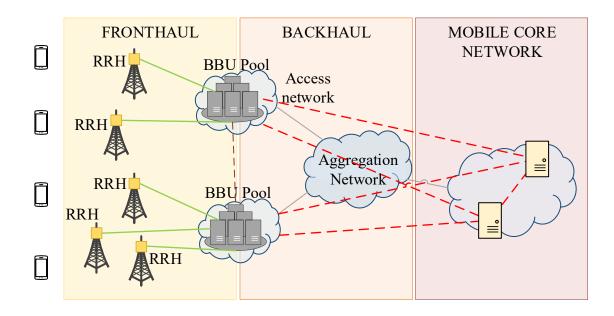

| 2.2 | C-RAN architecture                                          | 7  |

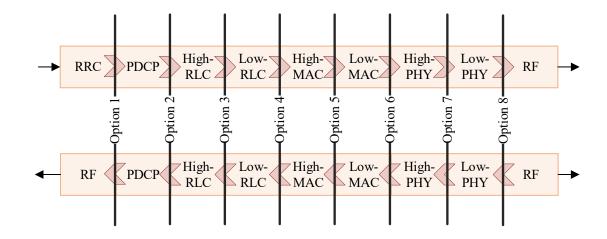

| 2.3 | Fronthaul functional split options                          | 8  |

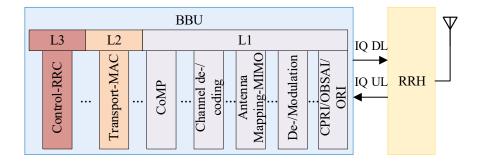

| 2.4 | Base Station functionalities                                | 11 |

| 3.1 | Two-layer neural network diagram                            | 14 |

| 3.2 | ReLU (Rectified Linear) activation function                 | 16 |

| 3.3 | Matrix multiplication for Fully Connected Layers            | 23 |

| 4.1 | Systolic Array architecture                                 | 26 |

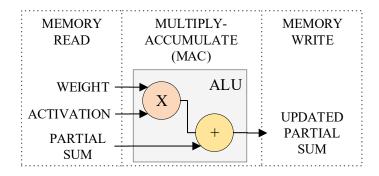

| 4.2 | Memory access for one MAC operation                         | 27 |

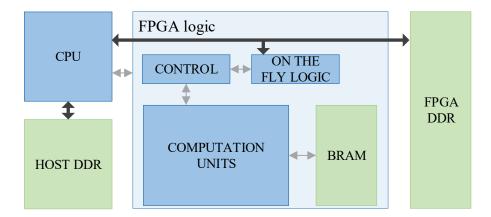

| 4.3 | Block diagram of a typical FPGA-based inference accelerator | 29 |

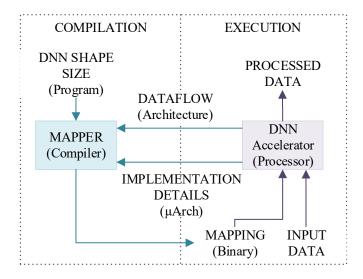

| 4.4 | Execution model analogy                                     | 30 |

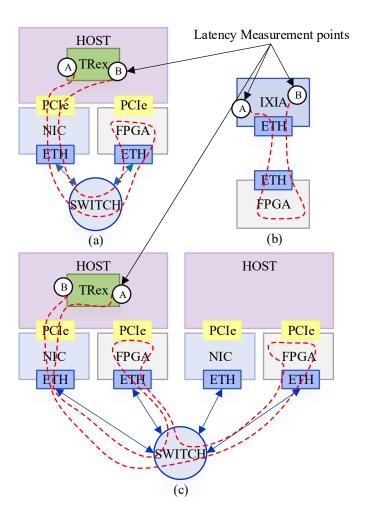

| 5.1 | CRUN test cases                                             | 39 |

| 6.1 | CRUN architecture overview                                  | 42 |

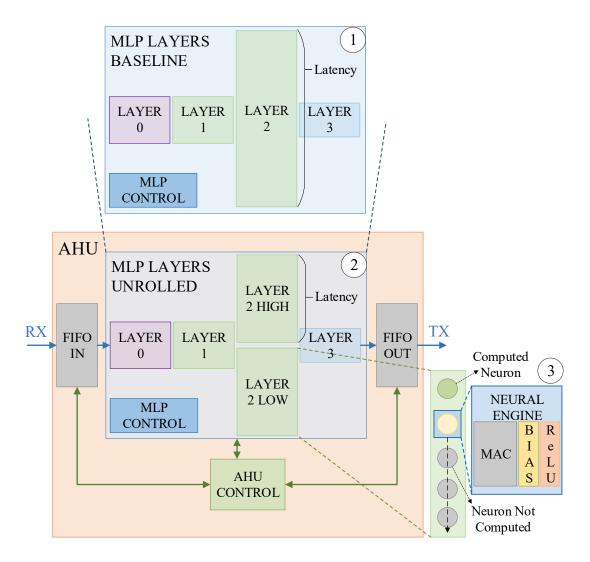

| 6.2 | CRUN FPGA architecture overview                             | 44 |

| 6.3 | CRUN Accelerator Hardware Unit interfaces                   | 45 |

| 6.4 | Distributed CRUN                                            | 46 |

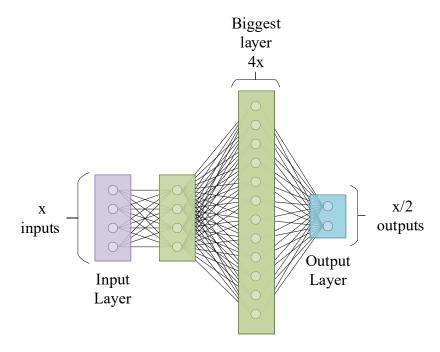

| 6.5 | Anomaly Detection MLP                                       | 47 |

| 6.6 | Hierarchical view of Anomaly Layers MLP                     | 48 |

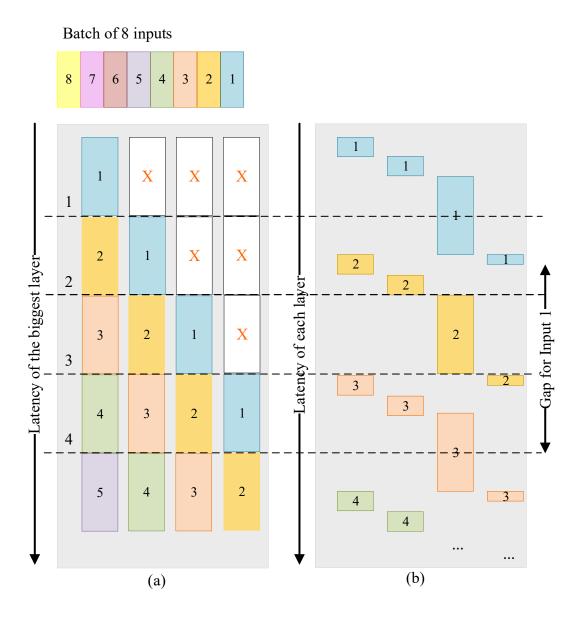

| 6.7 | Comparison between control options                          | 50 |

|     |                                  | VI |

|-----|----------------------------------|----|

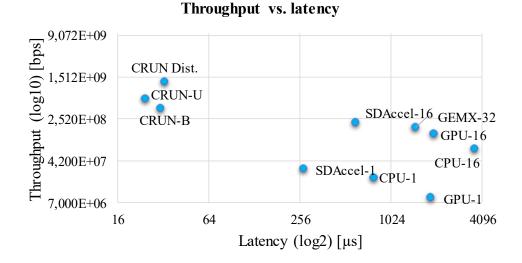

| 7.1 | Throughput vs. latency           | 54 |

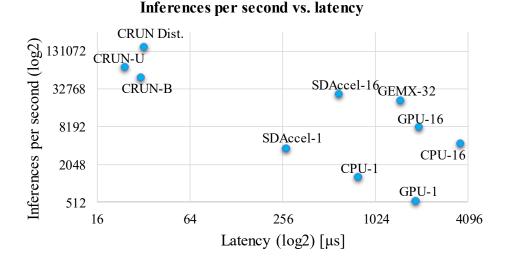

| 7.2 | Inference per second vs. latency | 57 |

## LIST OF TABLES

| 2.1 | Comparison between Cloud computing and C-RAN requirements [13].           | 8  |

|-----|---------------------------------------------------------------------------|----|

|     |                                                                           |    |

| 7.1 | Results for different implementations of anomaly detection neural network | 53 |

| 7.2 | Resource utilization for anomaly detection NN versions                    | 58 |

#### LIST OF ABBREVIATIONS AND SYMBOLS

C-RAN Cloud-based Radio Access Network

ACAP Adaptive Compute Acceleration Platform

AHU Accelerator Hardware Unit

API Application Programming Interface

AR Augmented Reality

ASIC Application-specific Integrated Circuit

AWS Amazon Web Services

BBU Baseband Unit

BLAS Basic Linear Algebra Routines

BNN Binarized Neural Networks

CNN Convolutional Neural Networks

COTS Commercial Off-The-Shelf

CPRI Common Public Radio Interface

CPU Central Processing Unit

CPU-1 CPU batch-1

CPU-16 CPU batch-16

CRUN-B CRUN Baseline

CRUN-D CRUN Distributed

CRUN-U CRUN Unrolled

CU Central Unit

DDRDouble Data RateDMADirect Memory AccessDNNDeep Neural Networks

DPDK Data Plane Development Kit

DRAM Dynamic Random-Access Memory

DSP Digital Signal Processor

DU Distributed Unit

FaaS FPGA-as-a-service

FFT Fast Fourier Transform

FIFO First In First Out

FLOP Floating-point Operations

FPGA Field-Programmable Gate Array

FPS Frames Per Second

GEMM General Matrix Multiplication

GEMX-32 GEMX batch-32

GPU Graphics Processing Unit

GPU-1 GPU batch-1 GPU-16 GPU batch-16

HBM High Bandwidth Memory

HDL Hardware Description Language

HLS High-Level Synthesis

ILA Integrated Logic Analyzer

IoT Internet of Things

IP Internet Protocol

ISA Instruction Set Architecture

LSVRC Large Scale Visual Recognition Challenge

MAC Multiply-Accumulate

MEC Multi-Access Edge Computing

ML Machine Learning

MLP Multi-Layer Perceptron

NFV Network Function Virtualization

NN Neural Networks

NPU Neural Processing Unit

NRT Non-Real Time

NVDLA NVIDIA Deep Learning Accelerator

PCIe Peripheral Component Interconnect Express

PE Processing Element

QNN Quantized Neural Networks

QoE Quality of Experience

RDMA Remote Direct Memory Access

ReLU Rectified Linear Unit

RNN Recurrent Neural Networks

ROM Read-Only Memory

RRH Remote Radio Head

RRU Remote Radio Unit

RTL Register Transfer Level

SDAccel-1 SDAccel batch-1 SDAccel-16 SDAccel batch-16

SDN Software-Defined Networking

SIMD Single Instruction Multiple Data

SIMT Single Instruction Multiple Thread

SoC System on a Chip

TNN Ternary Neural Networks

TPU Tensor Processing Unit

TTI Transmission Time Interval

VM Virtual Machine vRAN virtualized RAN

a neural network activations

A matrix A

$\alpha$  scalar for matrix multiplication

b biases B matrix B

$\beta$  scalar for matrix multiplication

C matrix C

f(x) inference computation f prediction function

fg function to be approximated

h(.) differentiable nonlinear activation function

op(.) original or transposed matrix

$\sigma$  sigmoidal output unit activation function

$egin{array}{lll} w & & \text{neural network weights} \\ x & & \text{neural network inputs} \\ y & & \text{neural network outputs} \\ \end{array}$

z second layer of the neural network

#### 1. INTRODUCTION

It is well known that the next generation of mobile networks must support an ever increasing number of mobile data traffic. It is only true that mobile communications are the world's largest technology platform [9].

The great capacity demands can only be answered with a massive evolution in mobile networks architecture. The latest trend in this context is the centralization of baseband functions that were once performed in a distributed fashion, usually very close to the antenna site [40]. This effort is done in order to provide flexibility and dynamic scalability for future applications. It also has an interest in running baseband functions not only centrally but in a virtualized environment, so commodity server hardware can be used. This architecture is commonly referred as Cloud-based Radio Access Network (or C-RAN) or as industry seems to prefer virtualized RAN (vRAN).

In order to use commodity server hardware in this context, the principles of Network Function Virtualization (NFV) must be used. However, as more and more demanding functions are virtualized, it gets more and more difficult to attend their requirements, in terms of latency and throughput for example, with Commercial Off-The-Shelf (COTS) hardware and hardware acceleration must be employed.

A promising approach is to utilize neural networks in C-RAN. Deep learning has a tremendous power when it comes to its applications. The appeal of deep neural network solutions is undeniable. Since the dramatical reduction of the error rate in the Large Scale Visual Recognition Challenge (LSVRC) [43], the interest in this field has been renewed. Machine learning has proved to be an excellent tool, part of this success is boosted exactly by Deep Neural Networks (DNNs). The major breakthroughs experienced during the last decade, especially in computer vision and natural language processing are a result of this field of research.

The DNNs ability of automatic feature extraction differs from the hand-made features or rules devised by experts and is the reason why these solutions achieve such superior performance when compared to other techniques. The algorithm is able to

1. Introduction 2

learn statistically from a large dataset the representation of the input space. This learning phase is referred as training, in which a set of examples must be used to adjust the weights that forms the model.

Once a DNN is trained, it is ready for use, so inference phase can start. These two distinct phases have different computational demands. Training requires throughput while inference is concerned with latency. In this sense, the first presents higher computational workload and is a fit for GPUs (Graphics Processing Unit), but the second although being carried out in CPUs (Central Processing Unit) and GPUs alike has gaining a rising interest for a specialized solution. The number of application specific processors for ML (Machine Learning) inference offered by industry increases all the time. These solutions come from tech giants and start-ups, in which some examples are Tensor Processing Unit (TPU) from Google, Myriad from Intel, Huawei, Cerebras, Groq and others.

In this context, industry's interest is towards faster inference rather than training. But why? It is possible to deduce that inference is the production step with DNNs. Indeed, it is only after training that the model is deployed to deliver the required predictions.

Important to highlight that, since training takes a huge amount of time and inference is where the model is put to a use, that the interest on industry is to accelerate and make better and faster predictions. Either to support the development of the Internet of Things (IoT) on the device or to boost the extensive set of applications on cloud data centers.

With this in mind, it is natural that DNN solutions can be effectively applied across the entire mobile networks architecture. However, an interesting point in Cloud RAN is in the edge cloud concept, in which the idea is to distribute cloud capabilities across the network placing computing resources at the edge of the network. In this scenario, a myriad of applications can be accelerated, ranging from baseband functions, management scope and analytics applications with the Multi-Access Edge Computing (MEC). For example, auto-encoders can be used for anomaly detection problems, a common application in mobile networks.

In order to enable the usage of deep learning inference applications in the edge cloud, one needs to investigate how to minimize the latency of such algorithms in a system level and on the applications level. Latency is important for deep learning inference, it is even more important and indisputable in the edge cloud context.

Within this scenario lies the exact goals of this thesis, the investigation of possibilities

1. Introduction 3

vs. requirements. In special, the study of the usage of an in-house framework (CRUN) that enables the distribution of acceleration on data center environment. The objective of this thesis work is to leverage the best solution for the inference of a machine learning algorithm for an anomaly detection application. The requirements for this solution are ultra-low latency between  $20\mu s$  to  $40\mu s$  for inference time and at least 20 000 inferences per second. Thus, the fifth generation of cellular networks latency demands can be fulfilled.

A comparison work is the final contribution of this exploration between five implementations, from GPPs (General Purpose Processors) architecture to a hand-optimized RTL (Register Transfer Level) neural network implementation allied with CRUN framework.

This thesis work is structured as follows. Chapter 2 discusses cloud computing in mobile networks scope, its requirements and the role of deep learning in this context, placing this thesis on this domain. In Chapter 3 the basics of deep neural networks is reviewed, presenting important concepts and the considerations when choosing a hardware platform for implementation. Following this first brief introduction to neural networks, the examination of the possible optimizations is done from a software perspective. An overview of hardware implementations of inference accelerators and the closest related works is done in Chapter 4, in which the review is divided into optimizations, tools and architectures propositions and the use of such designs in cloud computing. The methodology of this thesis is presented in Chapter 5. Subsequently, Chapter 6 summarizes the in-house infrastructure used to accelerate the example NN application over the Ethernet, the optimizing techniques utilized and the software application used for running the system. Finally, the results are presented in Chapter 7 and the comparison between different platforms and network size is discussed, as well as the considerations of the distribution of the application. Conclusions and next steps are outlined in Chapter 8.

## MOBILE NETWORKS AND CLOUD COMPUTING

The domain of this thesis work is mobile networks and its evolution towards centralization and cloudification. In special, the study of how deep learning applications can be accelerated on the edge of the network.

The needs of neural networks are diverse. In general, one of the main reasons for scaling up machine learning solutions is the inference timing constraints, which requires predictions to be made in real-time [5]. From the computational load perspective, only the inference is the object of study in this work. In this sense, its computation can be either done on the cloud or on the device [70].

The application requirements and its scope will dictate where the inference of the neural network will be processed. From the cloud viewpoint, the importance of the latency requirement is becoming crucial as applications with live streams get more and more popular for cloud service providers [17].

However, in order to fully understand the requirements which cloud computing imposes, one must first comprehend its scope. In this respect, the National Institute of Standards and Technology (NIST) definition for cloud computing is "a model for enabling ubiquitous, convenient, on-demand network access to a shared pool of configurable computing resources (e.g., networks, servers, storage, applications, and services) that can be rapidly provisioned and released with minimal management effort or service provider interaction." [51, p. 2].

In Cloud computing-based architecture for Radio Access Networks (C-RAN) there are the same interests to accelerate neural network inference workload as in traditional cloud. The tight requirements on latency appeal to a similar approach. This chapter introduces C-RAN concepts and main requirements.

2.1. C-RAN 5

#### 2.1 C-RAN

C-RAN is one of the answers for the continuous growth experienced in mobile data traffic [13]. The surge observed in mobile data transmission can be explained by the ever increasing number of smartphones and applications [83]. To put it in numbers, according to [18] the 49 exabytes ( $10^{12}$  MB) mark will be reached monthly by 2021.

The C-RAN concept addresses the challenges of adapting to a non-uniform traffic and the efficient resource utilization. In this sense, it comprises a novel mobile network architecture [13], that has evolved from the traditional distributed approach in which a base station was responsible for the baseband and the radio processing [40]. The nomenclature used can vary, but it is common to refer to the radio processing portion as Remote Radio Head (RRH) and the Baseband Unit as BBU [13].

The evolution towards C-RAN starts with the location in which RRH and BBU are placed. In a traditional distributed architecture, they can either be located at the base of the cell tower with a coaxial cable connection to the antennas, or in a split manner in which RRH is at the top of the cell tower with the antennas and the BBU is in a nearby cabinet with a fiber connection between the two [66]. From Figure 2.1 (a) the traditional approach is showed; the figure depicts the split architecture only.

The keynote in C-RAN is the capacity of centralizing the baseband processing and share its resources in a virtualized BBU pool [13], which can also be referred as vRAN. This ability employs a sophisticated communication and cooperation mechanisms between base stations [40].

In this architecture, the baseband processing units (BBUs) consist of the central pool of resources, the communication with different base stations must be made with low latencies and high throughput. The BBU pool enables the dynamic allocation of baseband processing resources to different cell sites and radio technologies [66]. The radio signals are collected from distributed antennas into remote radio heads in which they are transmitted through optical transmission network to the cloud platform [40].

Figure 2.1 shows the differences between the traditional and the C-RAN architecture. Note the centralized BBU as the resource pool. Additionally, observe the three main parts of this architecture, the RRH, BBU and the Fronthaul connections, in which the last one connects the other two components [40]. On another perspective, the Backhaul connects the BBU to the mobile core network [13]. Refer to Figure

2.1. C-RAN 6

Figure 2.1 Distributed BBU and C-RAN architecture. Adapted from [13].

#### 2.2 for Fronthaul and Backhaul connections.

The full potential of a centralized architecture can be achieved with the virtualization of BBUs. The vRAN architecture utilizes vBBUs (virtualized BBUs) deployed in centralized data centers and the RRHs still remain at the cell sites on the edge [66]. The concept is still fuzzy regarding its name, this virtualized approach could still be referred to as a C-RAN implementation.

In the C-RAN context, the baseband unit is deployed centrally at a network-edge data center [9]. In Figure 2.2 these components correspond to the BBU pool location. These facilities, when designed using cloud principles, provides the opportunity of running also multi-access edge computing (MEC) services [9]. Moreover, the RAN edge offers an ultra-low latency and high-bandwidth with real-time radio network information environment that can be used by applications and services [62].

From a cost perspective the deployment of MEC and C-RAN should be done as one. As such, since the BBU pool is already planned in C-RAN, the cost of providing additional processing (MEC) in the same facilities is lowered [65].

Considering this, C-RAN model offers an integration possibility between radio access with the rest of the telco cloud-enabled network, in which the same edge data center hosts the application logic or content on cloud infrastructure and the centralized control functions [9]. As of the writing of this work, it can be formalized, that in 5G there is a Central Unit (CU), a Distributed Unit (DU) and the Remote Radio

2.1. C-RAN 7

Figure 2.2 C-RAN mobile network. Adapted from [13].

Unit (RRU), which in 4G/LTE corresponded to the original BBU function. From the deployment point of view, this leads to several options, in which each scenario depends where each unit is located, for example the evolution from single-node in 4G to split function architecture of 5G [35].

From the function perspective, an important question emerges, what is the best functional split between these units. Academia and industry alike are concerned with the best trade-off and several propositions are made, including a flexible approach, as described by [32, 12, 50, 11].

The interest in this functional split is manifold. The reason is that as the data rates increase the conventional fronthaul implementation (using Common Public Radio Interface - CPRI) is impractical [35]. Figure 2.3 shows the optional split points.

In order to best choose the optimal split point, the trade-offs between throughput, latency and functional centralization must be taken into account. Observing Figure 2.3 it is possible to infer that moving towards a higher layer split, left-side of the picture, means fewer processing functions to be centralized but relaxed requirements when considering throughput and latency [35].

Another view to the same problem is whether to split Real-Time (RT) functions and Non-Real-Time (NRT) ones. In this sense, the former would be deployed at the antenna site for air interface resources management and the latter control functions

Figure 2.3 Optional split points. Adapted from [35].

hosted centrally [9]. In essence, the best performance gains would be observed if the entire protocol is centrally controlled, in Figure 2.3 this means Option 8. Consequently, the requirements between CU and DU would be ultra-low latency and high-bandwidth.

In order to emphasize the requirements and the challenges that they impose, table 2.1 shows the contrast between cloud computing requirements and C-RAN. It is important to highlight that this work is mainly concerned with latency, data profile and data rate, in this order of importance.

|                       | Cloud Computing         | C-RAN               |

|-----------------------|-------------------------|---------------------|

| Data rate             | Mbps range              | Gbps range          |

| Data profile          | Bursts and low activity | Constant stream     |

| Latency               | Tens of ms              | Hundreds of $\mu s$ |

| Jitter                | Tens of ms              | ns range            |

| Information Life time | Long (content data)     | Extremely short     |

| Recovery time         | s range                 | ms range            |

| Number of clients     | Thousands to millions   | Tens to hundreds    |

Table 2.1 Comparison between Cloud computing and C-RAN requirements [13].

#### 2.2 NFV and SDN

In a broader scope, C-RAN is a use case of Network Function Virtualization [33]. NFV describes a technique in which the network functions, traditionally computed in specific network hardware (i.e. bare metal), are run as application software in a general infrastructure hardware. In order to achieve this end result, a virtualization layer (hypervisor) is used for virtualizing the physical hardware resources as computing, storage and network [40].

Indeed, note how NFV is one key enabler for C-RAN architecture in this sense. Also, how the deployment of MEC and C-RAN can be carried out as one in this context. As such, in the vRAN model, the deployment of vBBUs is done on multiple NFV platforms utilizing standard x86 hardware and consolidated in central data centers [66]. A second essential concept in this scope is Software Defined Networks (SDN), which is intrinsically related to NFV. According to [53], a networking solution that combines NFV and SDN leads to a greater value resource.

SDN is a networking paradigm that provides centralized control of the network. It eases the separation of the control and data plane [21]. As a result, networks are programmable, adaptable and cost effective [40].

The decoupling of control plane and data plane is an important concept, since traditionally they were packaged into proprietary, integrated code from proprietary vendors [40]. This shift in abstraction shapes the functionality of network switches, in which they become dummy packet forwarding devices that are controlled logically by a centralized entity [13].

So far, the concepts behind cloud computing, NFV, SDN and C-RAN were introduced. Although each one of these fields seem to relate, no clear relationship was established. For that purpose, in this work, the relationship proposed by [53] is adopted. In this sense, NFV, SDN and cloud computing are abstraction of different resources, where compute is for cloud computing, network for SDN, and function for NFV [53]. As for C-RAN, it can be understood as an example of this resource abstraction endeavor.

#### 2.3 Deep Learning in Mobile Networks

The fields of deep learning and mobile networks have mainly been researched separately [83]. However, recently the emergence of a combination of these two research disciplines can be observed. For a comprehensive survey on this topic, the reader should refer to [83].

In the evolution of mobile networks, the road leads for the  $5^{th}$  generation (5G) of mobile systems. As such, the fifth-generation technologies, namely full-duplex, ultradense networks and large scale antenna systems can be facilitated in full scale by the flexibility and scalability that only a cloud-based approach as C-RAN naturally imposes [40].

Deep learning has a wide range of applications. The same assertion is true in the

scope of mobile networks [83]. To the extent of this work, the deep learning applications considered here are the ones pertinent to the edge cloud concept, introduced in sub Section 2.1.

In this context, the edge of a mobile network is not only intended for specialized processing, as it was in the past. It now offers the possibility to integrate applications with radio equipment enabling a new set of high value services [62]. Consequently, in this scenario a broad range of applications can benefit from deep learning solutions.

In the management level utilizing network-level data, as an example, the work carried-out by [63] demonstrates the use of MLPs (Multi-Layer Perceptron) for user's QoE (Quality of Experience) prediction by using average user throughput, number of active users in a cell and channel quality indicators.

Some use cases are depicted as examples in the edge cloud scenario in [62], at least two are a perfect fit for deep learning, especially CNNs (Convolutional Neural Networks), cited here:

- Augmented reality content delivery: the edge data center can provide applications performing local object tracking and local AR (Augmented Reality) content caching,

- Video analytics: by processing the video stored by the video management application to detect and notify specific configurable events.

The closer to the edge the tighter latency requirements. The mapping between use case latency and the different levels of distributed data center as possible location can be referred from [65] and [9]. Important to highlight that because the 5G central unit is also deployed in the edge data center, it is suitable for very low-latency services, as it is the case of assisted driving, which again comprehends an important deep learning application.

There is still a crucial characteristic when it comes to edge cloud responsibilities. Depending on the functional split between CU and DUs, there is more room for lower layer processing into edge data centers. Again, refer to Figure 2.3, according to [35], the choice of the optimal split point depends on the specific deployment scenario.

Figure 2.4 shows the base station functionalities separated into BBU and RRH, although no separation for CU and DU is done. Note the wide scope for opportunities of using deep learning solutions for L1, L2 and L3 processing.

Figure 2.4 Base Station functionalities. Adapted from [13].

As an example, the investigation proposed in [82] shows the usage of deep learning for channel estimation and symbol detection since DNNs present the ability for learning and analyzing characteristics of wireless channels suffering from nonlinear distortion, interference and frequency selectivity. Similar objectives were investigated in the work proposed by [54] using different machine learning approaches. This application requires very short latency and referring to Figure 2.4 would be mapped to L1 processing.

The proposition done by [60] is to interpret a communications system as an autoencoder, opening the view for the use of deep learning with the physical layer, L1 on Figure 2.4.

Finally, the efforts in using machine learning, especially deep learning, in 5G networks is also driven by industry. In [15], three examples are mentioned: beamforming scheduling; indoor positioning and downlink/uplink channel configuration.

The beamforming technology makes it possible to transmit beams of data for targeted users, which minimizes interference and efficiently uses the radiofrequency spectrum. One potential issue in using beamforming is the scheduling of such beams, a combination problem of four out of 32 beams gives 30 000 options. The usage of deep neural networks for implementing this scheduler was already claimed by industry [15]. This application corresponds to L2 in Figure 2.4. With this in mind, it is possible to infer that the latency requirements for such solution is indeed ultralow, in the extreme case every sub air interface Transmission Time Interval (TTI) corresponding to some tens of microseconds for the ML inference response.

In addition, the interested reader could refer to [36] for a bigger overview of the usage of machine learning techniques as a whole in wireless communications, not only focusing on deep learning.

In this thesis work, a real-time anomaly detection neural network for mobile network

traffic is considered. The application corresponds to the management level of mobile networks and can be mapped to the edge cloud context that in C-RAN could be deployed in the BBU Pool.

#### 3. NEURAL NETWORKS

Machine learning aims to create algorithms for making predictions based on data. In this sense, the mapping between input to output is the main task of such algorithm which is a predictive function [5].

The main division for machine learning algorithms is the nature of the training phase. There are two basic approaches, supervised learning and unsupervised learning. Supervised learning must utilize a set of training data for constructing the prediction function and apply it to the test data. The typical format for the training data is labeled examples, which comprises the data instance and the ground truth [5].

In contrast, unsupervised learning operates in a set of inputs without any labeling corresponding to it. In this case, the goal differs from supervised learning since some sense must be made from the unlabeled data [6]

Artificial neural networks (or as they commonly are referred nowadays, only neural networks) are inspired in biological structures. They are basically an attempt to model the biological information processing of the nervous system [67]. Modern NNs (Neural Networks), however, should not be understood as an accurate model for the brain, but instead as function approximation engines which the basic underlying ideas are borrowed from neuroscience [27].

In this sense, the hierarchical multi layered structure sets the pace for the transmission of information for neighbor's units and more distant ones. It is important to highlight that the parallel computation is a nature aspect in neural networks. [67].

Feedforward neural networks, also called Multi-Layer Perceptrons (MLP) are the foundation of deep learning. For a classification problem, an MLP establishes the mapping between the input and the class which the input belongs. Note from the name, feedforward, that the output of the model is not fed back into it. But this does not mean that it is not possible. In this case, the neural network is called a Recurrent Neural Network (RNN). RNNs present state of the art predictions for speech recognition tasks, for example [27]. A third common type of NNs are the Convolutional Neural Networks (CNN) that are specific MLP types with a convolutional

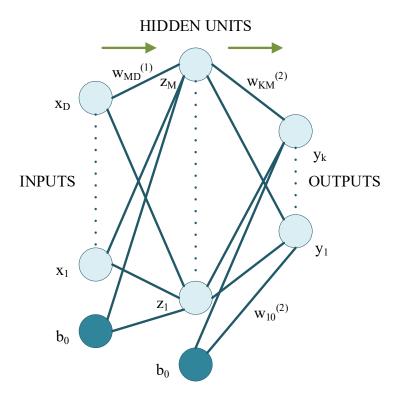

Figure 3.1 Basic two-layer neural network diagram. Adapted from [6].

layer intended for feature extraction. This set of neural networks are important for vision tasks and object recognition.

#### 3.1 Mathematical Definition

Figure 3.1 depicts the basic two-layer neural network diagram and shows the basic building blocks of a neural network.

Jumping to mathematics, one can define feedforward networks from its fellow linear models for classification and regression. For a walk-through of this process, refer to [6].

The starting point to devise the basic neural network model is given in equation 3.1, where w corresponds to the weights, b to the biases. Note the superscript (1) which corresponds to the layer of the network (in this case, the first layer). The activations correlate with the quantity a [6]. Again, refer to Figure 3.1 for reference.

$$a_j = \sum_{i=1}^{D} w_{ji}^{(1)} x_i + b_j^{(1)}$$

(3.1)

Each of the activations expressed in 3.1 are transformed by a differentiable nonlinear activation function h(.), here given by equation 3.2.

$$z_j = h(a_j) (3.2)$$

From Figure 3.1 observe the correlation with equation 3.1 and 3.2. The final network function is provided in 3.4.

The process is repeated again by linearly combining the results in z, which corresponds to the second layer of the network, this can be seen from Figure 3.1. From equation 3.3 below, b corresponds to the bias.

$$a_k = \sum_{j=1}^{M} w_{kj}^{(2)} z_j + b_k^{(2)}$$

(3.3)

A feedforward neural network is, in this sense, a series of functional transformations [6]. The expression in 3.4 shows the final form of a two-layer neural network model, where  $y_k$  give the set of network outputs and  $\sigma$  represents the sigmoidal output unit activation function, which can be used for binary classification problems. Note the matrix-matrix multiplications on equation 3.4.

$$y_k(\mathbf{x}, \mathbf{w}) = \sigma(\sum_{j=1}^{M} w_{kj}^{(2)} h(\sum_{i=1}^{D} w_{ji}^{(1)} x_i + b_j^{(1)}) + b_k^{(2)})$$

(3.4)

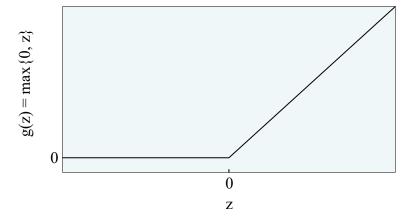

The process to choose the activation function to be used is determined by the nature of the data and follows a specific set of rules [6]. The most used activation function nowadays is the Rectified Linear Unit (ReLU), depicted in Figure 3.2. The main advice is to use ReLU as the activation function for modern neural networks [27].

This recommendation comes from the fact that ReLU is a piecewise linear function composed of two linear pieces, which makes it almost linear and as such, the optimization with gradient descent methods is straightforward [27].

In essence, the nonlinearity inserted with non-linear activation functions between fully connected layers is necessary, otherwise a multi-layer network could be arithmetically minimized to a one-layer deep neural network.

Figure 3.2 Rectified linear (ReLU) activation function. Adapted from [27].

#### 3.2 Concept Definitions

In a neural network, the first layer is commonly called the input layer, similarly the last layer is the output layer. The layers in the middle of the neural network are called the hidden layers and their relationship to the network is tightly related to training. [27]. Once again, acknowledge Figure 3.1 for reference.

Since the goal of a feedforward network is to approximate a given function fg, during the training phase the objective does not change. The training data does not specify the behavior of the hidden layers, instead the important concept here is that the hidden layers must be used at its best to approximate the function fg. Thus, simply put, the hidden layers are called as such because the output provided by them is not yet the desired approximation. [27]

The depth of the model is given by how many layers the neural network has, which directly correlates to how many processing stages it contains. From these two affirmatives, it is possible to explain two important terms. The term deep for deep learning comes from the model depth. On the other hand, multi-layer perceptron, comes from the fact that each layer resembles the perceptron model [27]. For more information on this model refer to [6].

It is important to highlight that a perceptron is only one of the many artificial neuron models proposed in 1950s and 1960s [55].

#### 3.3 Training and Inference

Deep neural networks are deployed in two phases: training and inference. Simply put, training regards to identifying the prediction function f, while inference com-

putes f(x) on a data instance x. In order to understand the computational demands of these two tasks, one must get a glimpse of the underlying concepts regarding how neural networks are trained.

Without considering the specifics of training, one can assume that it basically means an iterative procedure in which the objective is to minimize an error function by adjusting the weights in a sequence of steps. At first, the evaluation of the error function derivative with respect to the weights is carried out. In the subsequent step the weights are to be adjusted accordingly with the derivatives evaluated at the previous step. There is a distinction in these two steps, and as such different techniques are considered for each. In this regard, back-propagation can be observed for the former whilst gradient descent for the latter. Notice that many more powerful optimization techniques can be used instead of gradient descent, and its mention is just an example due to its simplest form [6]. Another technique may be stochastic gradient descent.

In a feedforward neural network, forward propagation consists of the input x being propagated through the hidden layers until it reaches the output layer producing y. In contrast, during the training phase, the back-propagation algorithm is responsible for the flowing of information backwards in the network from the cost for gradient computation in which the cost is a result of the forward propagation during training. [27]

The process of training a neural network is highly computational intensive, the task of iteratively calculating gradients and adjusting weights until the labeled data is correctly predicted is indeed exhaustive. On the other hand, when compared to the inference stage, one can only argue that inference offers a much easier task, since only the forward pass takes place.

The previous remarks are the only ones referring to training and learning step on NNs. For the remaining of the present work, all the investigation regarding neural networks will be only focused on the inference phase of deployment.

#### 3.4 Inference's Computational Load

The main achievements observed today, when referring to neural networks astonishing performance in certain applications, are basically due to two main reasons: the increasing computing power and the abundance of data. Analyzing over the last twenty years, the growth in network sizes is exponential [23]. Early networks would follow this premise, VGG would have around 2x the size of AlexNet that already

had 60M parameters [57].

It is true though that when analyzing a shorter period of time, the challenge of maintaining bearable computational workload while increasing the accuracy has been tackled by recent model approaches [2]. Consequently, these more recent DNNs are especially designed to be more efficient since there is a trend that the deeper a neural network is, the more accuracy it will provide [57].

When referring to computational workload, CNNs are the most studied subject for inference accelerators, as can be seen in [52, 48, 64, 85, 61, 22].

A CNN model comprises of convolutional layers and fully connected layers. The complexity and computational requirements of these two layers types are different. A convolutional layer is computation-centric while a fully connected layer is memory-centric. Furthermore, the former uses few parameters but needs heavy number of operations while the latter utilizes hundreds of millions of weights that are used for one time only [64].

An efficient CNN inference accelerator would take this unbalance in computation to memory-ratio and apply different techniques for each portion of the neural network. Although this work focuses on a fully connected layers network, the revision of strategies will be made in a general format along with the trends in efficient design.

There are many techniques for accelerating inference for CNNs. From the software standpoint, the goal is to compress the model, reducing the memory footprint, the number of operations while trying to maintain accuracy. On the other hand, from the hardware perspective, the objective is to design the architecture to reuse data as much as possible, increase its locality and accelerate the convolution operations. Additionally, reducing the precision is also a target for efficiently deploying these models [64].

#### 3.5 Execution Platforms

Before going deeper in the specifics of these strategies, the next paragraphs state the most important points considering GPPs (General Purpose Processors), FPGAs (Field-Programmable Gate Arrays) and ASICs (Application-Specific Integrated Circuit). For a review on related work in FPGA-based inference accelerators, please refer to the Chapter 4.

Traditional general-purpose architectures are usually the choice platform for training and predicting neural networks. In order to meet performance requirements, when talking about CPUs, they are more likely to be used in large clusters [46]. GPUs on the other hand, are well known for performing data parallel computation with high throughput for floating point in regular parallelism. However, even when increasing the number of Floating Point Operations Per Second (FLOPS/s), GPUs support only a set of native data types, which essentially means that for custom data types it may perform poorly [57]. When comparing CPU clusters with GPU, the former waste a big portion of its resourcing with synchronization between cores. Furthermore, in applications which the memory transactions are small when compared to arithmetic operations, GPUs are a better choice [46].

From a memory point-of-view, general purpose processors rely on traditional Von Neumann architecture. This means that instructions and data are stored in external memory and are fetched when needed by the software execution. The motivation for memory hierarchy lies exactly in this fact, for reducing the costly external memory operations. In this regard, however big performance a GPP may offer, the memory-processor communication is the bottleneck in such architectures. This together with the costly memory-bound deep learning operations makes the GPP performance to suffer irrecoverably [44].

When it comes to ASICs, their specific purpose nature is converted into limited programmability [56]. Although they typically provide the highest performance and energy efficiency with the smallest chip size, their design takes a substantial amount of time. In addition, after the tape out of the chip, inserting new features or finding design errors translates into a new set of masks and considerably more time for a new process. In this sense, they are only used with applications that requires a high volume of these chips, so the effect of the cost can be diminished [86].

Two important factors contribute to the advantages of FPGAs as inference's execution platform. Firstly, an FPGA device, with its reconfigurable logic offers the possibility of using different and custom data types. Secondly, they can utilize the distributed on-chip memory and pipelining, which means a great deal in feed-forward systems. Also, the possibility of partial dynamic reconfiguration plays a central role in architecture planning. But the irrefutable truth is the level of solutions tailoring, with extreme freedom for exploring optimizations [44].

#### 3.6 Network Model Optimizations

In general, the usage of floating points, although well supported by GPPs, is not an efficient implementation in ASICs and FPGAs, which are much more efficient when using fixed-point arithmetic [64]. Avoiding floating point operations is a reasonable

approach in the DNN context.

Data quantization is one of the most common methods for reducing the precision of activation values and weights without having a heavy impact in prediction accuracy [2].

The benefit of using quantization is twofold. Firstly, the use of less bits will reduce the memory footprint, its bandwidth and storage requirements. Secondly, the adoption of simpler representation will reduce the hardware cost in the operations standpoint [30].

At least two different approaches for quantization can be identified from literature, static fixed point and dynamic fixed point. In the first, the bit-width is set according to the numerical range and the precision required, thus every operand share the same scaling factor. Each number is then quantized to the nearest fixed-point representation. One identifiable problem with this approach is that the dynamic range of floating point representation is much bigger than the fixed point data, which yields in either overflow or underflow [30]. To address the problem of the first, in the second approach type, the scaling factor can differ according to the parts of the network. This is due to the fact that separate portions of a network can have different numerical range of data [2].

In addition, quantization is a method that can offer various flavors combinations. Indeed, when referring to quantized inference, the phase in which quantization is applied is also an important factor. If the objective is to reduce model size without the need of retraining the model, then post training quantization is an option, which is a simpler method yielding good results. However, when aiming at higher accuracies quantization aware training should be considered. For more information about quantization for efficient inference refer to [42].

It is indeed a trend in deep neural networks to improve efficiency by taking into use compact data types, even with floating point representation. According to [57] the usage of below 32-bit single precision floating point is the new norm.

Recently, research efforts have been directed to study the usage of extremely compact data type representation, a big portion of these works refer to Binarized Neural Networks (BNNs). These networks are proposed on the basis of using 1-bit representation for neurons and weights, in which values are constrained to +1 and -1 [57]. The impact of using this representation on FPGAs is huge. It essentially means that the multiply-accumulate (MAC) operations can be mapped to XNOR gates followed by a bit counting operation. It is irrefutable though that the performance gained

with this method is heavily translated in accuracy degradation [2].

The work proposed by [72] targets binarization for all input activations, weights and output activations. A second generation of the same proposition is done in [7], in which the support for mixed and variable precision is added, as such, it targets a bigger scope not only BNNs but also QNNs (Quantized Neural Networks).

Another effort targeting BNNs is XNOR Neural Engine [20], which is a hardware accelerator IP integrated within a microcontroller unit for low-power solution on the device.

Along the same path as BNNs, one can also find the ternary neural networks (TNNs), in these type of networks, the weights are represented by 2-bit values and are constrained to 0, +1 or -1. In cases in which there is negligible accuracy loss the neurons are not quantized.

If on one hand data quantization can be effectively used for optimization of neural network models, on the other hand the number of neurons and weights can also be optimized for efficiency purposes.

In this context, pruning is a method that relies on exploiting sparsity (i.e. the near zero values) in neurons and weights [57]. In fact, DNNs are often over-parametrized in the sense that a big portion of its parameters can be pruned because they are redundant [81]. The importance and applicability of this optimization has grown in the recent years, this is due to the broad usage of ReLU as activation function, which zeros out negative values. Consequently, the sparser a matrix the fewer operations needed for its computation [57]. The pruning for weights is also very relevant [2]. The values that are zero out are interpreted as not important and this approach can maintain the original accuracy [57].

One of the drawbacks of pruning is the irregular resultant network structure. Targeting only CNNs, CirCNN [22] presents the usage of block-circulant matrices for representing weights which reduces the storage and computational complexity without pruning.

It must be kept in mind though that sparse computation is theme that will be revisited during the hardware optimization part of this work. One can deliberately insert zeros during training while keeping the hardware architecture in mind. In this way, since zeros were allowed in specific parts and not in others, the optimization is also done in a hardware level.

The methods targeting parameter reduction are usually followed by a fine-tuning

phase in order to minimize the effect on the accuracy [2].

Sparsity exploitation means to take advantage of the intrinsic redundancy in data representation. This aspect of neural networks has been explored by some works. Proposed by [45], Stitch-X is a DNN inference accelerator that by combining spatial and temporal reduction balances dataflow complexity in face of sparsity. It utilizes a Parallelism Discovery Unit (PDU) that stitches together the input activation and weight pairs for producing reducible partial sums.

Similarly, the accelerator proposed by [84], Cambricon-X, also aims to exploiting sparsity and irregularity of NN models while also using 16-bit fixed-point representation. Related approaches can also be observed from [61, 38, 39].

#### 3.7 Algorithmic Optimizations

In order to reduce complexity, some operations can be transformed, and algorithmic optimizations applied.

When concerned about CNNs, a common approach is to instead of computing complex convolutions in the time-domain, choosing to simply calculate multiplications in the frequency-domain with Fast Fourier Transform (FFT) [81, 2]. If a more hardware-friendly manner is required then Winograd transformation can be applied [48, 58, 48, 70].

At this point, an important highlight must be made. From equations 3.1, 3.3 and 3.4, it is obvious why matrix multiplication is crucial for the computation of neural networks and the importance in optimizing these operations.

The GEMM transformation basic idea is to map convolutional and fully connected layers as General Matrix Multiplications. In the simplest format, GEMM computes the operations given in equation 3.5, where **A**, **B** and **C** are matrices,  $\alpha$  and  $\beta$  are scalars and op(.) denotes either the original or transposed matrix [25]:

$$C = \alpha \operatorname{op}(\mathbf{A}) \operatorname{op}(\mathbf{B}) + \beta \mathbf{C} \tag{3.5}$$

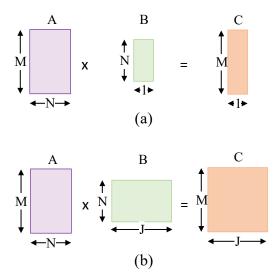

Previously, it was mentioned that the biggest portion of the weights are used by fully connected layers. This is an important fact when using GEMM implementations for computing these multiplications because batch processing can be used.

In batch processing, multiple inputs are provided instead of one, Figure 3.3 depicts

Figure 3.3 (a) Matrix-vector multiplication - Level 2. (b) Matrix-matrix Multiplication - Level 3. Adapted from [70].

this case in (b), if the inputs are the combination of vector B in (a). The throughput can be improved while memory bandwidth is maintained when instead of loading weights multiple times, they are loaded once per batch. [2].

Indeed, from Basic Linear Algebra Routines (BLAS) three canonical computation models can be performed: vector-only operations, matrix-vector and matrix-matrix operations. Note that they correspond to levels, respectively Level 1, Level 2 and Level 3. Figure 3.3 shows matrix-vector in (a) and matrix-matrix operations in (b).

The lowest level can be used to implement the other two and so forth. Each of these levels can be mapped for specific usage. On one hand, Level 3 operations are highly desirable for dense matrix-matrix calculations and perform well for batch mode, on the other hand, Level 2 is a good fit for batch-1 implementation [24].

So far, only software optimizations were discussed. Although these optimizations were placed under software, they will directly impact on the hardware used to implement the computations.

#### 4. INFERENCE ACCELERATORS

This chapter reviews hardware-based acceleration techniques and proposals for neural networks inference. As such, important aspects for a hardware efficient design and system level architecture will be discussed.

The list of works targeting deep neural networks inference accelerators is extensive. Although this is not a particularly new field of research, the first neural network FPGA implementations are dated back to 1990's [44], there was an explosion of works recently, as can be seen in [72, 7, 31, 85] and others.

However, the reviews showed in this work concentrate mainly in efforts proposed from 2014 to the present-day for three reasons. Firstly, the number of works in this field is huge, secondly, NNs have become deeper after 2014 which changed their computational requirements and thirdly, as mentioned earlier this work is not meant as a survey.

#### 4.1 Hardware Efficient Design

Recently there was a shift in the main purpose of the design of DNNs. Surely, in the early days the main objective was to achieve the maximum accuracy. While this is still true, the impact of the design in the hardware implementation is gaining more and more importance. In this sense, the codesign of DNN models and hardware can be classified as an effort for maximizing accuracy and throughput, while minimizing energy and cost. [70].

FPGAs provide a high level of flexibility for hardware implementation. However, there are at least two big challenges in FPGA based accelerators [30]:

- the current working frequency of FPGA is usually in the range of 100MHz to 300MHz, much less than general purpose architectures,

- the abstraction level for implementing neural networks on FPGAs is much lower, making it a much more difficult task.

In order to address these challenges, there are some trends in the FPGA industry to look at. The operating frequency of usual designs should have a big improvement with new technologies, as is the case of Intel's HyperFlex. Additionally, the on-chip memory and the off-chip bandwidth should increase considerably, the latter with the use of HBM (High Bandwidth Memory) technologies [57].

Regarding the second challenge, the software ecosystem for FPGAs is becoming more mature. The biggest FPGA's industry players, Intel and Xilinx, have been supporting the use of High-Level Synthesis (HLS) tools which offers the possibility of using high level abstraction languages for programming FPGAs. This support, brings the advantages of these devices to the reach of more people than only hardware experts [57].

It is important to highlight that scalability is the biggest issue when looking forward on FPGAs and deep learning. In order to achieve successful implementations, they must scale in data sizes and architectures, since the research in deep learning is still on-going and the pace in which new models and techniques are being developed is very high [44]. One may refer to this as exactly the lead which FPGAs represent.

#### 4.1.1 Parallelism Exploitation

General Purpose Processors mostly employ a temporal architecture for parallelizing computations, in the form of Single Instruction Multiple Data (SIMD) or Single Instruction Multiple Thread (SIMT) techniques, for example. In contrast, FPGA-based designs are usually constructed on top of spatial architecture for dataflow processing. The main difference between these two architectures is the data passing format. In the first, data can only be fetched from memory hierarchy and the compute element cannot communicate in a direct manner with another. In the second, data is passed from one unit to the other directly. [70].

Surely, this aspect reflects directly into DNNs efficient design. In this context, data-path optimizations can be adopted to address the problem of efficiently using FPGAs for inference accelerators.

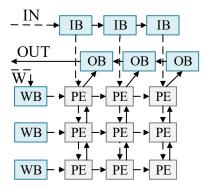

The usage of systolic arrays is well-known for this purpose. These are grid structures, usually arranged as depicted in Figure 4.1, that are formed by several processing elements (PEs). State-of-the art implementations employ a limited number of these units on the FPGA, each of these units can be reused by iterating data through them [2]. The utilization of systolic array architecture for CNNs in and end-to-end automation flow is demonstrated by [73].

Figure 4.1 Systolic array architecture. Adapted from [73].

It is important to formalize the possible sources of parallelism in DNNs in order to understand the ways of exploring it. In this context, at least two forms can be readily identified, batch parallelism and inter-layer parallelism. The former was already mentioned when discussing about matrix-matrix multiplications, but it means to serve a group of inputs with the objective of reusing data and decreasing external memory accesses. The latter refers to the scheme in which the computation is launched in a pipelined fashion. [2].

Observe that these sources of parallelism are exactly aligned with the extraction of maximum performance from a FPGA. In fact, the industry claim is to have a peak performance of over 1 TFLOP/s for the DSP (Digital Signal Processor) blocks in the FPGA. However, the task of fully pipelining and loop unrolling for maximum parallelization is not as easy as it seems. [73].

Along these lines, loop unrolling is a key technique in hardware optimization. The idea of unrolling loops in an FPGA is basically a trivial one, the downside is the trade-off between performance and resource utilization. An important side note though is that if poorly chosen the unrolling parameter can cause severe hardware underutilization. This is particularly important since different layers have very diverse loop dimension. [30].

There are many methods proposed in literature for choosing an optimal value for loop unrolling factors. The challenge is to derive a parameter that at the same time minimizes the memory access and maximize resource utilization [2].

### 4.1.2 Resource Utilization

As mentioned previously in Section 4.1, although being improved recently, the onchip memory capacity on FPGAs is still small for deep designs. This means that

Figure 4.2 Memory access in one MAC operation. Adapted from [70].

off-chip memory must be used [2]. Since this is inevitable, a caching memory hierarchy should be implemented, it is usual to have a two-level cache in FPGA-based implementations. One may question the need of such schemes, for that purpose Figure 4.2 shows the need of three memory read operations and one write per multiply-accumulate (MAC).

In this fashion, the use of a caching system is simply an exploitation of the spatial architecture provided in FPGA implementations. The other option is to utilize off-chip memories and in the case of DRAMs (Dynamic Random-Access Memory) take much more energy to access the memory than the computation itself [70].

From the same perspective, data reuse plays an important role in this scenario. Even if DRAM accesses are needed, since they are so expensive, the fetched data should be reused as much as possible. For a comprehensive explanation on data reuse schemes on dataflows, refer to [70].

To reduce off-chip memory bandwidth requirements and minimize data movement, fused-layer accelerators can be used, as first demonstrated by [3]. This technique can be combined with other optimizations, for example [85] offers the use of Winograd in its convolution blocks templates with the addition of layer fusion optimization.

It is also important to mention general FPGA-based implementation optimizations. Whenever a design is devised the target is to fully utilize the FPGA capabilities. In this sense, many important guidelines must be followed. Among those, two are absolutely important, the usage of DSP blocks and the improvement of working frequency.

In the case of DSPs, the adopted bit-width is crucial. This is because, depending on the vendor and on the FPGA, this can vary and hardened portions on FPGA in general achieves higher frequency and consequently performance. For example, the accelerator demonstrated by [31] utilizes the 8-bit fixed-point representation for packaging two operations of 8x8 bits into one DSP of the FPGA. The system presented in [64] applies dynamic-precision data quantization for VGG16 model by using an automatic flow, a small accuracy loss is introduced with the model under 8/4 bit dynamic-precision quantization.

Recently, a trend in FPGA industry is to support floating point operations natively, as is the case of Intel's Stratix10 device, offering up to 9.2 TFLOP/s of 32-bit floating point performance [57].

# 4.2 System Architecture

From a system level perspective, it is possible to identify some trends in neural networks implemented in FPGAs.

When focusing in HDL (Hardware Description Language) model-based approach, the main idea is to automate the process of generating the HDL description taking into account the selected network. This means that the generated hardware is fine-tuned for a determined neural network and the best performance can be achieved for that particular hardware [30].

Instruction based methods, on the other hand, do not modify the underlying hard-ware, thus several neural networks can run on the same hardware implementation. An application that needs neural network switching would target this implementation, since the change can be done in real-time [30].

Finally, these two methods can be combined into a solution that besides optimizing the hardware, also uses a set of instructions compiled corresponding to the network description. [30].

#### 4.2.1 Hardware

A neural network inference accelerator is typically formed by the parts showed in Figure 4.3. In a high level overview, the host CPU plays the role of a scheduler in which it will issue commands to the logic and monitors its status until the end of the computation is reached. For controlling the operation on the FPGA, a controller must be implemented, it can either be a finite state machine or an instruction decoder [30]. Some implementations can use a soft-core processor synthesized in the FPGA for this purpose, as is the case in [24].

Figure 4.3 Block diagram of a typical FPGA-based inference accelerator implementation. Adapted from [30].

From the memory viewpoint, for the reasons already referred previously, for a large model an external memory is required for holding all the needed parameters. In such cases, a memory hierarchy scheme must be devised, as for example using the external memory and the on-chip memory as cache.

Obviously, this generic system can have several modifications and optimizations depending on the main objective, its requirements. For example, in a simpler solution only one memory could be used in the entire system, which can be seen on the small configuration version of NVDLA [58]. For more advanced and high performing solutions, besides the two external memories used, a micro-controller could be placed between the CPU and the FPGA, so the host is freed from handling all the interruptions in the system as is the case in the larger configuration for [58], which could even be implemented as a soft-core processor on the FPGA.

The content of the computation units can vary abundantly, as discussed previously systolic arrays can be used to form convolutional compute engines. Inevitably, logic for the non-linearity computation and algorithmic optimizations can be added to overall structure of the FPGA. Again, an example is the NVDLA [58].

#### 4.2.2 Software

From the software perspective, the execution model of an inference accelerator can be compared to those of GPP architecture. That is because it usually involves two phases, the compilation and execution, as depicted in Figure 4.4.

Analogously to the translation of a program targeting a specific architecture i.e. x86, the compilation step targets a DNN accelerator, in which case the neural network

Figure 4.4 Execution model analogy between DNN inference accelerators and GPP. Adapted from [70].

is translated into a hardware-compatible computation mapping [70]. Note that in this phase, or even before it, several neural network optimization techniques (as described in Sections 3.6 and 3.7) can and should be applied to deliver the best hardware friendly version possible.

Observe from the diagram in 4.4 that the mapper, in the compilation phase, needs as input the hardware implementation details. This is a crucial step in producing high-performing accelerators.

Additionally, it is important to notice that commonly an intermediary representation is needed to pass the model of the neural network to the accelerator. This representation is usually very different from the original model, for example, it can have a fused layers implementation, as proposed by [3]. The objective of this method is to reduce the use of external memory usage and as such improve the performance of the design.

To address the same problem, it is also possible to use a persistent approach, in order to pin the models in the on-chip memory of the FPGAs. This approach must be supported by an entire infrastructure at scale, since if only the on-chip memory is used, large models cannot fit in one device but can fit across several FPGAs. Microsoft's project Brainwave targets exactly that.

### 4.3 Tools and Architectures

One of the main concerns in implementing efficient inference accelerators in FPGAs is the heavy and difficult task of doing so. In this context, to ease this process, many works provide frameworks for automatically generating the underlying hardware description. This is the case of [72], further extended in [7]. FINN is a framework targeting Binarized Neural Networks inference accelerators on FPGAs, a custom architecture is built specifically for a given topology. The accelerator generation process uses two inputs, the trained BNN and an FPS target for the final implementation.

Also relying on data quantization technique allied with a design flow proposition, Angel-Eye presented by [29] targets the mapping of CNN onto embedded FPGAs. The input to the flow is CNN model from Caffe that is quantized and fine-tuned to increase accuracy, in the next step an instruction sequence is devised through a compiler for the execution of the model. The underlying hardware implementation is parameterized and runtime configurable.

In a similar manner, the framework proposed by [85] addresses the generation of efficient CNN models for domain-specific applications on FPGA. The key component on this framework is the hardware design template used with Winograd optimized convolution blocks and fused-layers approach. Transfer learning is used for fine-tuning the trained input model for a given application. In this sense, the inputs for this design flow are the domain knowledge, pre-trained models, the platform specifications and the requirements. As a result, the optimized model design is generated.

Another approach for abstracting these difficulties, is the use of Instruction Set Architecture. Cambricon, proposed by [47] is an instruction set specific for neural networks accelerators, it comprises the usage of a load-store architecture with 64-bit instructions devised from the study of NN techniques. Indeed, no vector register file is used to supporting common computations on NN, so the data is kept in on-chip memory being visible from the programmer perspective.

The combination of an Instruction Set with a framework targets an even bigger scope. These solutions offer the possibility of completely disengaging programmers from hardware design. The work presented by [68] has as inputs a pair of (DNN, FPGA), in which the DNN model is specified by a high-level programming interface, i.e. similar to Caffe description, and is further translated into a macro dataflow Instruction Set Architecture (ISA). Similar approaches are proposed by [28, 49, 28].

Another important aspect is the system solution in which these inference accelerators are deployed.

The approaches described so far usually present high flexibility of implementation, either regarding the DNN models supported or the target hardware platform. The work proposed by [52], NEURAghe, is aimed at Zynq SoCs (System on a Chip) and investigates the usage of the ARM cores with a convolution specific processor deployed on the reconfigurable logic. The ARM host program is automatically generated for the execution of the fully-connected layers and data marshaling.

This is one of the several examples targeted to SoCs solutions focusing on embedded architectures for NN acceleration. One can also mention [29] and [39] as recent approaches in this context.

In this sense, when one proposes an FPGA-Based inference accelerator it is usually designed to be a co-processor. One can either use SoCs that integrates multi-core processors, memory interfaces and reconfigurable logic on the same board, for an embedded approach or target the usage of the pair host and FPGA. This last approach utilizes PCIe I/O bus for communication between the host and the FPGA device, as is the case in [28]. Observe that these two types of system implementation can be interchangeable by some modifications.

The important point here is that all these implementations are usually targeted for real-time mobile applications, that are performed on the device. From the server point of view, [29] arguments that aiming at a specific network implementation is a good choice for achieving extreme hardware performance, but a problem when targeting real-time mobile applications that run on the device. This work agrees with this sentence, a specific neural network is indeed implemented for extreme performance purposes targeting a cloud environment structure.

The oldest work cited here is DaDianNao [14] and its correlation to the present work is symbolic. Motivated by the memory storage and bandwidth requirements in DNNs, as well as its correspondent limitations, the authors propose the usage of a multi-chip system, in which each on-chip storage could be used for implementing the biggest DNNs architectures. The proposed architecture is named a supercomputer for its capacity. Note that the underlying idea of scaling-up Deep Neural Networks across several chips is basically the core of a cloud computing environment.

### 4.4 Inference Accelerators in Cloud Environment

From the inference accelerators perspective, they are usually designed as embedded applications targeting real-time solutions, which is the interest of academia, as discussed in the previous paragraphs. When it comes for a cloud environment, two examples will be exposed here.

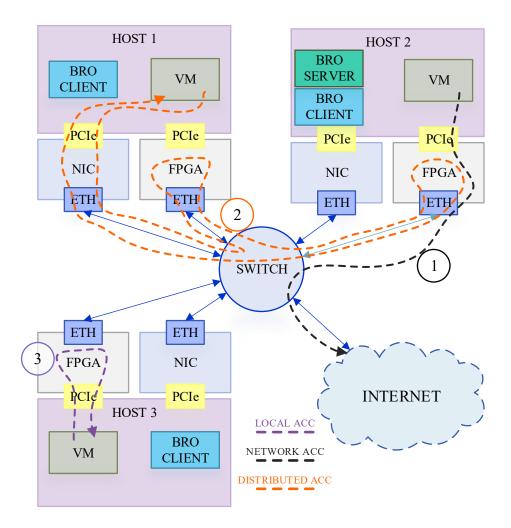

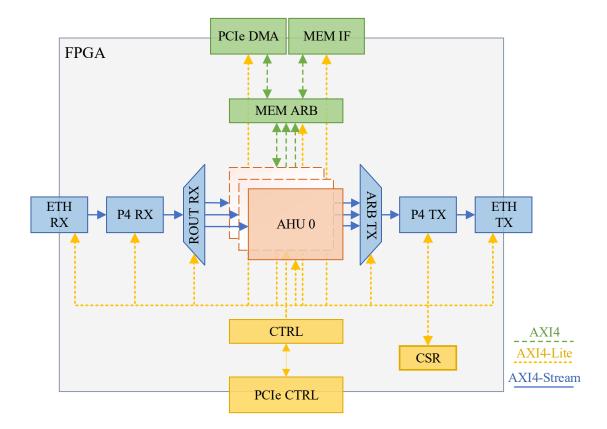

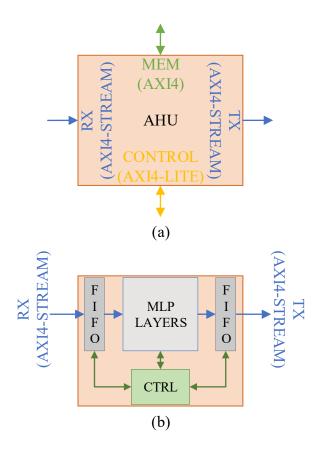

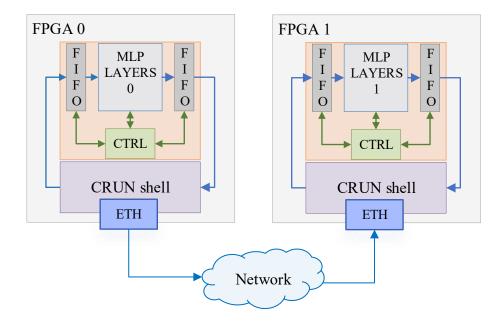

Google's TPU [37] is a custom ASIC designed to be a coprocessor on the PCIe I/O bus for easier integration with existing servers. The main objective was to run inference models to reduce the host CPU interactions in this process, also to present flexibility for several and evolving DNNs. The core of this accelerator is a Matrix Multiply Unit, fitting the highest level of canonical computation model, Level 3, as described in Sections 3.6 and 3.7. The instructions are sent from the host and allocated in an instruction buffer. The NN is compiled from TensorFlow to an API that can run either on GPUs or TPUs. The TPUs were deployed since 2015 in data centers for inference acceleration and can use big batch sizes for improving performance.