# MOHAMMAD HOSSEINVAND DESIGN AND IMPLEMENTATION OF MIMO OFDM IEEE802.11N RECEIVER BLOCKS ON HETEROGENEOUS MULTICORE ARCHITECTURE

Master of Science Thesis

Examiners: Prof. Jari Nurmi M.Sc. Sajjad Nouri

Examiners and topic approved by the Faculty Council of the Faculty of Computing and Electrical Engineering on 30th of May 2018

## ABSTRACT

MOHAMMAD HOSSEINVAND: Design and Implementation of MIMO OFDM

IEEE802.11n Receiver Blocks on Heterogeneous Multicore Architecture

Tampere University of Technology

Master of Science Thesis, 61 pages

October 2018

Master's Degree Programme in Communications And Computer Networks Engineering

Major: Communication Systems and Networks

Examiners: Prof. Jari Nurmi

M.Sc. Sajjad Nouri

Keywords: Software-Defined Radio, WLAN, OFDM, MIMO, Heterogeneous, Applicationspecific Accelerator, Multicore, FFT, HARP, RISC Processor, Network-on-Chip, CGRA, COFFEE, FPGA, Reconfiguration, Time Synchronization, Frequency Offset Estimation,

Channel Estimation, Symbols Demapping

In this thesis, the performance of a heterogeneous multicore platform in terms of technical capability is evaluated. Therefore, the choice of architecture in general can be based on a set of diverse applications. Selected applications can be parallel or serial in nature. Applications evaluation are often based on various performance metrics including the resource utilization and execution time. The wireless communication systems are expanded to accelerate their functions execution in both software and hardware. The embedded systems which involve several types of communication systems perform a large number of computations which require short execution time and minimized power consumption. Also, there is a growing demand for application-specific accelerators aiding general-purpose. One feasible way is to use heterogeneous multi-core platforms. Furthermore, many application-specific accelerators are loosely connected with each other.

In this study, the implementation of Multiple-Input Multiple-Output (MIMO) Orthogonal Frequency Division Multiplexing (OFDM) receiver is evaluated by applying a Heterogeneous Multicore Architecture (HMA). The MIMO OFDM receiver is composed of computationally intensive and general-purpose processing tasks and can serve maximum coverage for evaluation of the HMA. The receiver blocks are designed by crafting template-based Coarse-grained Reconfigurable Array (CGRA) devices. In this case study, four streams (antennas) are proposed in order to process the data over CGRAs simultaneously. HMA nodes will be reconfigured at run-time in different blocks of the receiver. In this experimental work, according to the performance of each CGRA, the collective performance of the entire platform as well as NoC traffic is recorded considering the number of clock cycles and also several highlevel performance criteria. The implementation of OFDM receiver scaled CGRAs to various dimensions. The data can also be exchanged between diverse nodes on the NoC structure by utilizing direct memory access (DMA) devices independently.

# **PREFACE**

This thesis work presented here was accomplished in the Laboratory of Electronics and Communications Engineering at Tampere University of Technology, Tampere, Finland to pursue a Master of Science degree in the Information Technology Program in 2018.

At first, I would like to acknowledge my mother Soudabeh Memar, my father Asadollah Hosseinvand and my sister Maryam Hosseinvand for their patience and consistent struggle, passionate love, and tremendous support in all moments throughout my life to bring me up to a stage, at which I became able to conduct this thesis and write it. It is clear to me that I owe all my accomplishments to them and without their support, all this would not have been possible.

I would like to express my deepest gratitude and respect to my supervisor Prof. Jari Nurmi, who made possible accomplishment of this research work at Tampere University of Technology as well as he welcomed me in his research group, always his expertise, motivation and patience was a great value for my Master thesis. In addition, I appreciate his support, which helped me manage the achievement of my Master thesis.

I am also thankful to M.Sc. Sajjad Nouri, who guided me to the first steps, plus for being my helpful colleague, introducing a new topic to me for thesis and collaborating in this research work under his supervision as well as for all his support and advices, which led to carry out this thesis. It was an incredible delight for me to work under his supervision and I had this chance to learn a lot from him.

I am really thankful to Prof. Roberto Garello for being my supervisors at Politecnico di Torino, Turin, Italy for the given opportunity, to believe in my abilities to do my thesis abroad, his enthusiastic support and always guided me to choose the best decision. I express my thanks to Dr. Daniel Riviello for providing valuable comments through this research.

I would like to express my warmest thanks to my dear friend, Yekta Lajevardi for endless support and for helping me to stay positive and focused. I am thankful to her for being an honest and lovely friend.

I am also grateful to my friend, Javad Malek Shahkoohi for long support and advices given through all the ups and downs of my studies. He has been my very caring and amazing friend.

I would like to extend my gratitude to my friends at Tampere University of Technology, Ritayan Biswas, Alberto Brihuega García, Marcelo Fabian Trujillo Fierro, Bahareh SadeQian, Danial Parsa, Farhad Javanmardi, Kamran Mohamadi, Mohammad Pourabed, Mehrdad Nahalparvari, Anastasia Yastrebova, Antonio Manlio D'Agostino, Giulia Sanfilippo, Amir Mehmansefat and AmirHossein Moshfeghifar for their friendship and good moments we have shared together and also, for their invaluable support throughout my Master degree. Living in Tampere would have been too colorless without you.

Tampere, October 2018 Mohammad Hosseinvand

منگفتم کفتنی فارو تو ہم ہرگز نیرسیدی...

"I never told you what I should have and you have never asked"

- Ardalan Sarfaraz

I dedicate this thesis to my father and my mother, whose love and affection, support, encouragement, motivation and prayers of day and night make me capable to get honor and achievement.

# TABLE OF CONTENTS

| 1. | Introduc | ction                                          | 1  |

|----|----------|------------------------------------------------|----|

|    | 1.1 Ob   | jective and Scope of Thesis                    | 2  |

|    | 1.2 Th   | esis Outline                                   | 2  |

| 2. | Literatu | re review                                      | 4  |

|    | 2.1 Pro  | ocessor/Co-processor Models                    | 4  |

|    | 2.2 Re   | configurable Devices                           | 5  |

|    | 2.2.1    | Fine-Grained Devices                           | 5  |

|    | 2.2.2    | Middle-Grained Devices                         | 6  |

|    | 2.2.3    | Coarse-Grained Devices                         | 6  |

|    | 2.3 Mu   | ılti-core Platforms                            | 6  |

|    | 2.3.1    | MORPHEUS                                       | 7  |

|    | 2.3.2    | P2012                                          | 8  |

|    | 2.3.3    | NineSilica                                     | 8  |

|    | 2.3.4    | RAW                                            | 8  |

| 3. | OFDM     | WLAN Overview                                  | 9  |

|    | 3.1 MA   | AC Frame Structure for WLAN Standards          | 10 |

|    | 3.2 Ph   | ysical Layer Specifications for WLAN Standards | 16 |

|    | 3.2.1    | Time Synchronization                           | 21 |

|    | 3.2.2    | Frequency offset Estimation                    | 24 |

|    | 3.2.3    | FFT                                            | 25 |

|    | 3.2.4    | Channel Estimation                             | 26 |

|    | 3.2.5    | Symbols Demapping                              | 28 |

| 4. | Platform | n Architectures                                | 29 |

|    | 4.1 Co   | arse-Grained Reconfigurable Arrays             | 29 |

|    | 4.1.1    | CGRA Execution Flow                            | 30 |

|    | 4.2 He   | terogeneous Accelerator-Rich Platform          | 31 |

|    | 4.2.1    | Internal Structure of NoC                      | 32 |

| 5.  | Desi   | gn and Implementation of IEEE 802.11n on template-Based CGRA | 34 |

|-----|--------|--------------------------------------------------------------|----|

|     | 5.1    | Time Synchronization                                         | 34 |

|     | 5.2    | Frequency Offset Estimation                                  | 37 |

|     | 5.3    | Fast Fourier Transform                                       | 40 |

|     | 5.4    | Channel Estimation                                           | 43 |

|     | 5.5    | Symbols Demapping                                            | 49 |

| 6.  | Integ  | gration of Baseband Processing Blocks on HARP                | 54 |

| 7.  | Mea    | surements and Estimation                                     | 57 |

| 8.  | Con    | clusions and Future Work                                     | 59 |

| Bil | oliogr | aphy                                                         | 61 |

# LIST OF FIGURES

| 2 | 2.1  | MORPHEUS architecture                                                                   | 7  |

|---|------|-----------------------------------------------------------------------------------------|----|

|   | 3.1  | IEEE 802.11n PPDU formats in Legacy, Mixed and Green-field                              | 10 |

|   | 3.2  | PLCP Preamble for OFDM training structure                                               | 12 |

|   | 3.3  | Subcarrier frequency allocation for $40.0~\mathrm{MHz}$ with $128~\mathrm{subcarriers}$ | 14 |

| 9 | 3.4  | Block diagram of IEEE 802.11n transmitter [44]                                          | 16 |

| Ç | 3.5  | Block diagram of IEEE-802.11n receiver [10]                                             | 16 |

| į | 3.6  | natural order and Gray coding of QAM modulation                                         | 17 |

| į | 3.7  | Cyclic Prefix (CP) in OFDM Symbol                                                       | 18 |

| į | 3.8  | Transmit spectrum of OFDM (PDS) based on IEEE $802.11n$ standard                        | 20 |

| į | 3.9  | Block diagram of correlation algorithm for time synchronization $\dots$                 | 22 |

|   | 3.10 | O Cyclic prefix (CP) correlation along with SNR 20 dB                                   | 23 |

| į | 3.11 | Linear interpolation algorithm to perform the channel estimation                        | 26 |

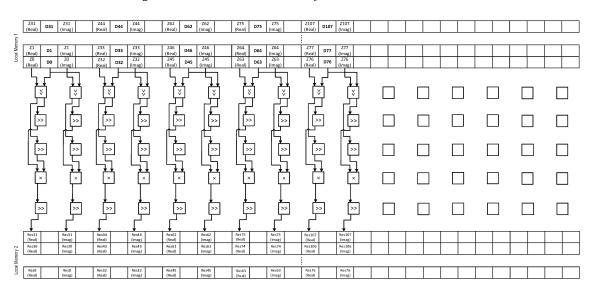

| 4 | 1.1  | The scalable template-based CGRA architecture                                           | 30 |

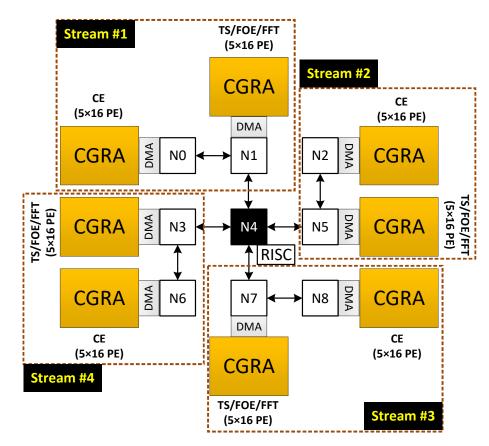

| 4 | 1.2  | Heterogeneous Accelerator-Rich Platform (HARP) [33]                                     | 31 |

| 4 | 1.3  | A view of master and slave node of HARP [78]                                            | 33 |

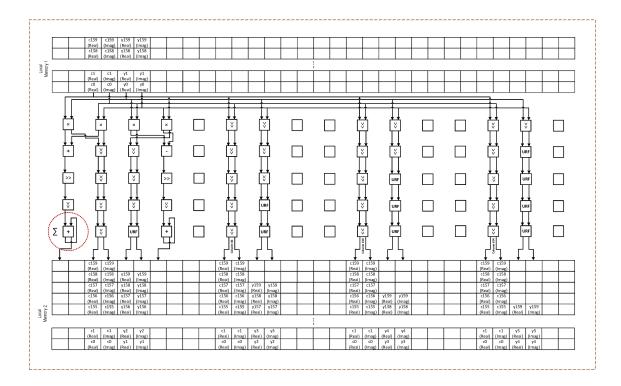

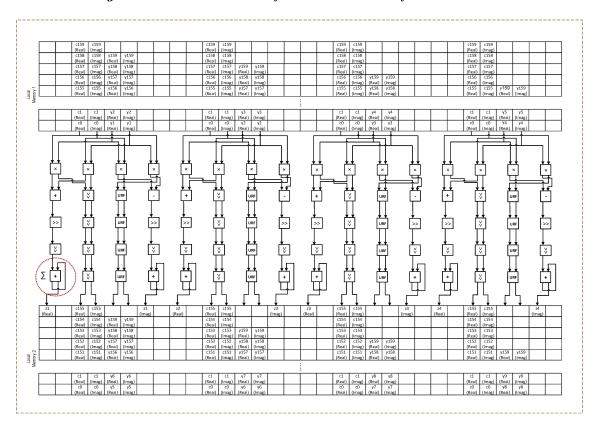

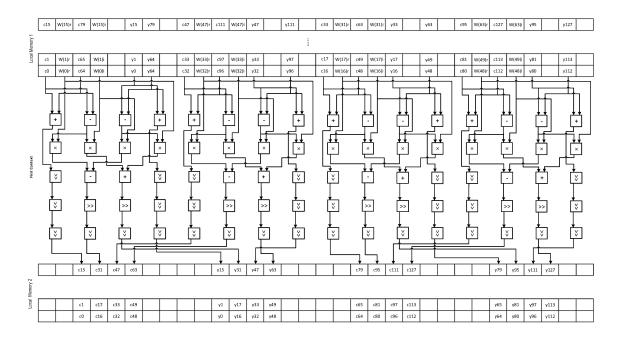

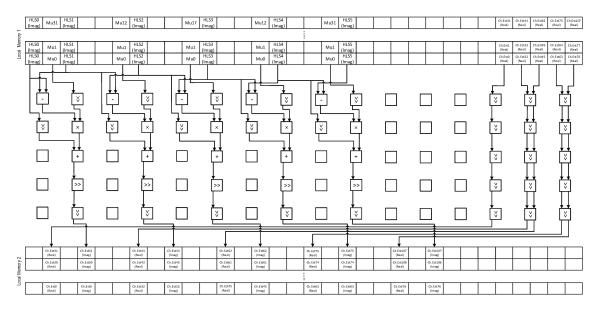

| Ę | 5.1  | Second context for the calculation of the correlations                                  | 35 |

| ٠ | 5.2  | Third context for the calculation of the correlations                                   | 35 |

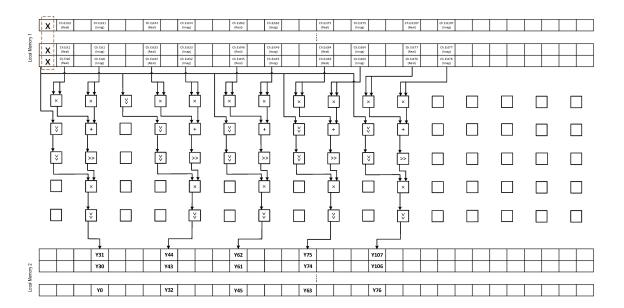

| Ę | 5.3  | The context for the multiplication between a signal and its complex conjugation         | 38 |

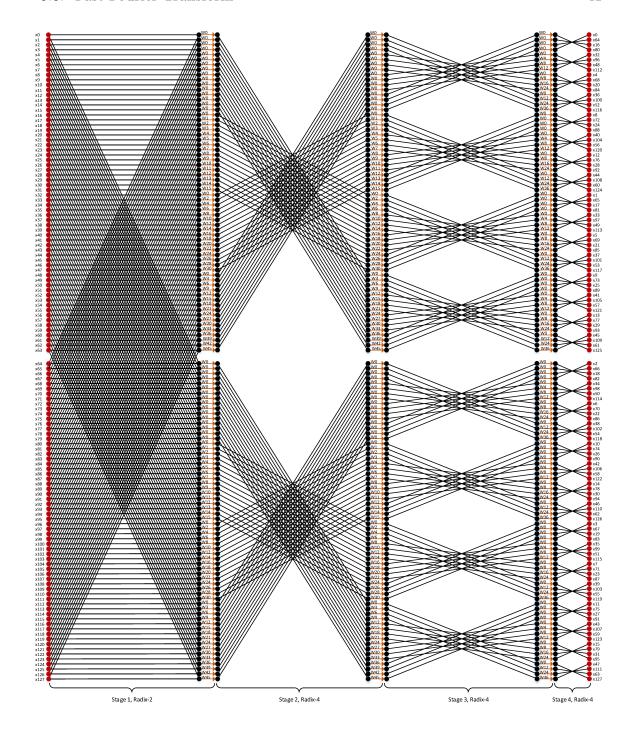

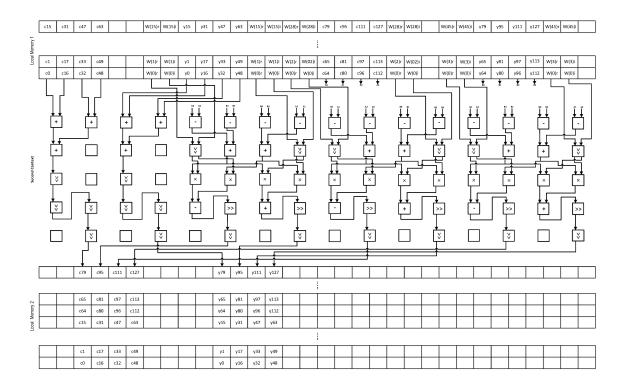

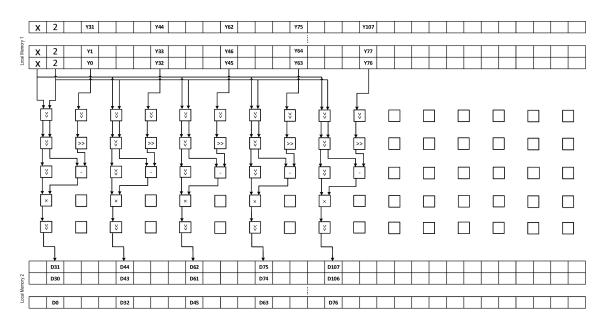

| ŀ | 5.4  | Fast Fourier Transform                                                                  | 41 |

| 5.5  | The first context includes four radix-2 butterflies                           | 42 |

|------|-------------------------------------------------------------------------------|----|

| 5.6  | A radix-4 butterfly for the second context                                    | 43 |

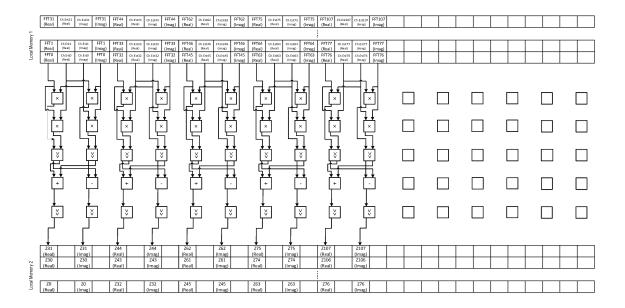

|      | Linear Interpolation algorithm based on pilot-assisted for Channel Estimation | 44 |

| 5.8  | Second context of the channel estimation                                      | 45 |

| 5.9  | First context of the Linear Interpolation                                     | 46 |

| 5.10 | Second context of the Linear Interpolation                                    | 46 |

| 5.11 | First context of the Newton-Raphson method                                    | 48 |

| 5.12 | Second context of the Newton-Raphson method                                   | 48 |

| 5.13 | Sixth context of the channel estimation                                       | 49 |

| 5.14 | Seventh context of the channel estimation                                     | 49 |

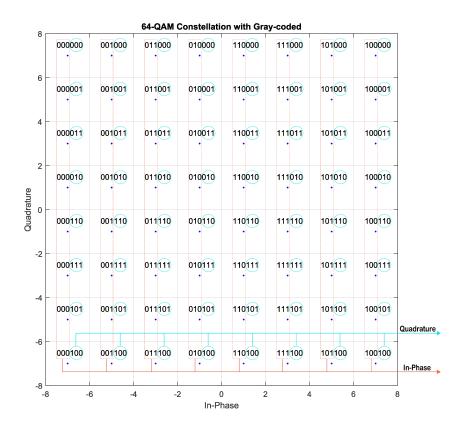

| 5.15 | Decision regions of 64-QAM Gray-coded constellation                           | 50 |

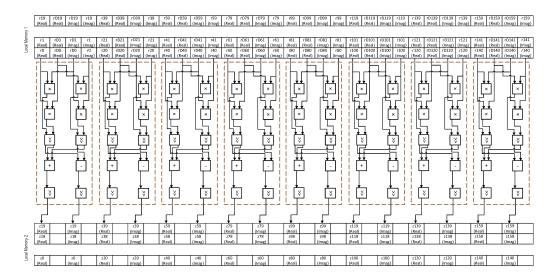

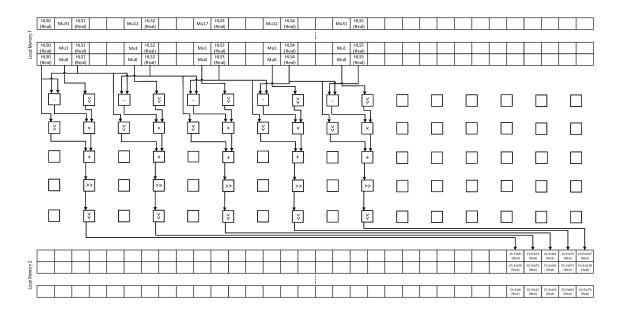

|      | Abridged general view of IEEE 802.11n MIMO receiver on HARP platform          | 54 |

# LIST OF TABLES

| 3.1 | Standards for OFDM WLANs [42]                                                                                                                                                                                                                                                 | 10 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Pilot specific values for 40.0MHz [44]                                                                                                                                                                                                                                        | 15 |

| 3.3 | IEEE 802.11n OFDM parameter values [45]                                                                                                                                                                                                                                       | 15 |

| 5.1 | Different types and lengths of FFT and their complexity in number of stages and in number of operations per butterfly [10]                                                                                                                                                    | 42 |

| 5.2 | Clock cycles (cc) based on the type of FFT accelerator and length [10].                                                                                                                                                                                                       | 43 |

| 5.3 | 64-QAM constellation mapping with gray coded                                                                                                                                                                                                                                  | 51 |

| 6.1 | The required clock cycles at different stages for data transfer and processing. In the table, D. Mem, Trans and Exe. are referring to Data memory, Transfer and Execution respectively, while Clock cycles with * sign indicate data transfer from CGRA to Node's data memory | 56 |

| 7.1 | Summary of resource utilization based on the breakdown of node-by-node for Stratix-V (5SGSED8N3F45I3YY) FPGA device                                                                                                                                                           | 58 |

| 7.2 | Dynamic power of each CGRA node and the NoC                                                                                                                                                                                                                                   | 58 |

# LIST OF ABBREVIATIONS AND SYMBOLS

ACK ACKnowledgment

ADC Analog-to-Digital Converter

AGC Automatic Gain Control

ALM Adaptive Logic Module

ALU Arithmetic Logic Unit

ALUT Advanced Look-Up Table

ASIC Application Specific Integrated Circuit

ASK Amplitude Shift Keying

ATM Asynchronous Transfer Mode AWGN Additive White Gaussian Noise

BER Bit Error Rate

BPSK Binary Phase Shift Keying

CC Clock Cycle

CCB Core Configuration Block

CE Channel Estimation

CFO Carrier Frequency Offset

CGRA Coarse Grain Reconfigurable Array

CIR Channel Impulse Response

CISC Complex Instruction Set Computing

CP Cyclic Prefix

CPU Central Processing Unit

CREMA Coarse grain REconfigurable array with Mapping Adaptiveness

DAC Digital-to-Analog Converter

DC Delay and Correlate

DFT Discrete Fourier Transform

DMA Direct Memory Access

DSP Digital Signal Processor

FEC Forward Error Correction Code

FireTool Fleld programming and REconfiguration management Tool

FPU Floating Point Unit

FF Flip Flop

FFT Fast Fourier Transform

FOE Frequency Offset Estimation FIR Finite Impulse Response

FPGA Field Programmable Gate Array

FSK Frequency Shift Keying

FSM Finite State Machine

FU Functional Unit

Gbps Giga Bit Per Second

GCC GNU Compiler Collection

GI Guard Interval

GOPS Giga Operation Per Second GPP General Purpose Processor GUI Graphical User Interface

HDD Hard Decision-based DetectionHDL Hardware Description Language

HMA Heterogeneous Multicore Architecture

HW HardWare I In-Phase

IEEE Institute of Electrical and Electronics Engineers

IDFT Inverse Discrete Fourier Transform

IFFT Inverse Fast Fourier Transform

I/O Input/Output

IP Intellectual Property

I/Q In-phase and Quadrature-phase

ISI Inter-Symbol Interference LTS Long Training Symbols

LUT Look Up Table

MAC Medium Access Control MCM Multi-Carrier Modulation

MIMO Multiple-Instruction Multiple-Data

MIMO Multiple-Input Multiple-Output

ML Maximum Likelihood

MPSoC Multi Processor System-on-Chip

MT Mobile Terminal

MVM Matrix Vector Multiplication

NOP No-OPeration NoC Network-on-Chip

OFDM Orthogonal Frequency Division Multiplexing

PAPR Peak-to-Average Power Ratio

PCB Peripheral Control Block

PE Processing Elements

PN Pseudo Noise

PPDU Physical Protocol Data Unit PSDU Physical layer Service Data Unit PSK Phase Shift Keying

PTS Partial Transmit Sequences

Q Quadrature-phase

QAM Quadrature Amplitude Modulation QPSK Quadrature Phase Shift Keying

RF Radio Frequency

RISC Reduced Instruction Set Computing

RPU Reconfigurable Processing Unit

RTL Register Transfer Level

RTOS Real-Time Operating System SDD Soft Decision-based Detection

SDR Software Defined Radio

SER Symbol Error Rate

SIMD Single-Instruction Multiple-Data

SISO Single-Input Single-Output

SLM SeLected Mapping

SNR Signal-to-Noise Ratio

SoC System-on-Chip

STS Short Training Symbols

TUT Tampere University of Technology

TS Time Synchronization

VC Virtual Carrier

VHDL Very-high-speed integrated circuit Hardware Description Language

VLIW Very Long Instruction Word

WiFi Wireless Fidelity

WLAN Wireless Local Area Network

## 1. INTRODUCTION

Today's human society is reliant on computers more than ever before. Their use in the everyday life of the human society has lead to scientific advancements, events as well as new fields of science, which have prompted the formation of modern world. An integrated part of modern life is communication which has evolved greatly throughout the years. The latest means of communication is mobile phones which are categorized into embedded systems. Embedded processors are dominant in communication systems such as mobile phones in which short execution time is highly desired. Embedded processors are expected to run many concurrent applications. Reconfigurability is a solution for achieving the goal of short execution time, since many embedded applications are computationally intensive. At the same time power dissipation must be limited. Over the years, there has been a pattern to increase the performance of the system by scaling the frequency of single-core architectures. This led to considerable increase in power dissipation. This issue has caused vendors to offer multicore systems. However, Dark-Silicon [37] is a critical issue in multicore systems. We could overcome the Dark-Silicon challenge by introducing many application-specific accelerators that provide high performance at low frequencies.

In this thesis, the focus is on the template-based Coarse-Grained Reconfigurable Arrays (CGRAs), to generate special-purpose accelerators. These platforms have relatively low power consumption. CGRAs are recommended since they operate at very low frequencies while they can yield enormous performance improvements. CGRAs are reconfigurable and are programmed using a high level language such as C. Also, they contain many specialized accelerators and are designed in a way to perform massively-parallel tasks in critical applications.

Moreover, there are many heterogeneous platforms which have almost identical design philosophies, e.g. NineSilica [1], Platform 2012 [2] and MORPHEUS ([3], [4]). According to the guidelines published in [5], this study uses heterogeneous platform in an accurate testing condition to identify possible architectural problems. The tested units are Orthogonal Frequency Division Multiplexing (OFDM) receiver blocks which are computationally complex tasks. Time Synchronization (TS) and Fast Fourier Transform (FFT) are examples of computationally intensive tasks. In

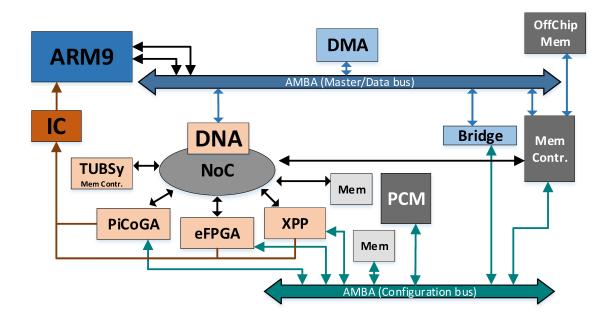

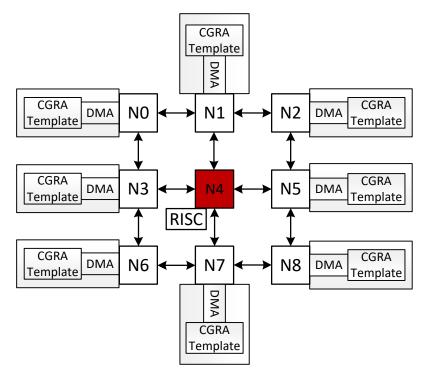

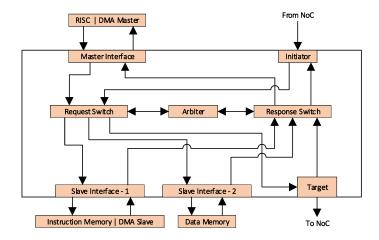

addition, OFDM application as a test was used to evaluate the ability of the platform's general-purpose processing for algorithms like CORDIC algorithms and the Taylor series. The RISC processor performs general-purpose tasks while OFDM-specific tasks are carried out by the CGRA, and the two are interconnected using a Network-on-Chip (NoC) for complete OFDM functionality. Heterogeneous Multicore Architecture (HMA) platform used in this thesis has been designed to maximize computing resources to enhance the performance of many particular algorithms of various types. Heterogeneous Accelerator Rich Platform (HARP) is a specific instance of HMA platforms. It has nine nodes placed in a  $3\times3$  topology.

The HARP platform includes a RISC core which performs two specific tasks; it acts as a system controller and distributes the configuration streams as well as the data to all other nodes that are interconnected through the NoC platform. After the configuration and data distribution tasks, the RISC core performs general computations and enforces synchronization between the nodes. All OFDM receiver block accelerators are designed based on the template-based CGRAs. Lastly, the OFDM receiver is evaluated to determine that it supports many communication systems algorithms.

# 1.1 Objective and Scope of Thesis

In this thesis, the feasibility of implementation and design of scalable CGRAs for MIMO OFDM running on a heterogeneous accelerator-rich platform is studied. This research work explores general issues as well as generation of application-specific accelerators for Software-Defined Radio (SDR) baseband processing utilizing the CGRA template. They are integrated with each other and then to a RISC core on a NoC. This thesis will be expanded to measurement, estimation and mapping of intensive signal processing algorithms. The main objectives of this thesis are to design and implement specific accelerators for an OFDM receiver baseband in a MIMO setup. The designed accelerator performance for each OFDM receiver block regarding the clock cycles, the use of resources and also the maximum operating frequency by synthesis on the family of Altera Stratix-IV FPGAs is addressed.

#### 1.2 Thesis Outline

The thesis consists of chapters as follows; Chapter 2 overviews the literature. Chapter 3 presents the main part of OFDM system based on IEEE 802.11n standard where various approaches are explained for each OFDM receiver block. Chapter 4 describes

1.2. Thesis Outline 3

the platform architecture and template-based CGRAs. Additionally, the whole performance of the HARP platform and the nodes of NoC is explained completely. In Chapter 5, the design and execution of MIMO OFDM receiver blocks are explained by employing template-based CGRAs. Then Chapter 6 explains the integration of baseband processing blocks on HARP and the distribution of data between different nodes. Chapter 7 covers measurement and estimation of different levels of HARP related performance metrics. Finally, the last chapter presents the conclusion and future work.

# 2. LITERATURE REVIEW

Nowadays, the computationally intensive tasks are allocated to Multi-processor System-on-Chip (MPSoC) or accelerators based on the processor/co-processor model. Moreover, Coarse-Grained Reconfigurable Array (CGRA) is one of the most powerful classes of accelerators, which is suitable for signal processing applications by providing high throughput and parallelism. CGRAs contain a lot of gates, which makes sense when they are used most of the time [7]. BUTTER [8], Morphosys [12], ADRES [13] and PACT-XPP [14] are examples of CGRA. In order to complete different applications at the same time, the CGRAs working as coprocessors should be combined to make a heterogeneous multicore platform [15].

# 2.1 Processor/Co-processor Models

This section will briefly discuss processor and co-processor models. Regarding the history of the processors, it can be seen that single-core processors were used for the general-purpose approach of numerous applications. Additionally, it was used in some proprietary accelerators, including audio, video, etc. as well as computationally intensive applications. Throughout the years, different processors for a various set of requirements have appeared. It can be seen that Very Long Instruction Word machines (VLIW) have been grown in large-scale parallel applications [17]. Also, to support high-grade communication mobile applications, a combination of VLIW and Digital Signal Processing (DSP) architecture was developed by supporting multiple applications simultaneously [18].

Loosely Coupled (LC) accelerators communicate easily with a low bandwidth, which allows multiple accelerators to be connected to the processor. This model of accelerators can be obtained by connecting the accelerator to a system bus, on a local node or remote network. In this case, multiple accelerators can exchange data with each other, as well as they can also work concurrently. As a prototype of a loosely coupled architecture on NoC, the platform P2012 [2] can be expressed.

In the Tightly Coupled (TC) model, accelerators have high bandwidth for communication with the processor. This makes it possible to provide faster data transmis-

sion as well as synchronization. In this model, using a dedicated co-processor bus or directly integrating an accelerator in the processor data-path are viable solutions. A CGRA can be an example of an accelerator tightly coupled to a processor, which can utilize a network of switched interconnections.

# 2.2 Reconfigurable Devices

In recent years, reconfigurable architectures have become more popular platforms due to particular capabilities and abilities to perform computational tasks. Reconfigurable architectures have different levels of parallelism. Reconfigurability means modifying their functionality at run-time for various applications. Regarding the characteristics of reconfigurable computing systems, some of the most significant features can be as follows [20].

- **Reconfigurability:** This refers to altering the internal architecture for the purpose of running various applications at a high degree of performance.

- Computation Model: The computational models such as Single-Instruction Multiple-Data (SIMD) or Multiple-Instruction Multiple-Data (MIMD) can be used. Moreover, some systems may follow the Very Long Instruction Word (VLIW) model.

- Granularity: Refers to the data size for operations of Reconfigurable Processing Unit (RPU) of a system.

Considering a wide range of different models of reconfigurable devices, the reconfigurable devices can be categorized according to their granularity level into three different classes; Fine-Grained, Middle-Grained and Coarse-Grained [3].

#### 2.2.1 Fine-Grained Devices

The FPGAs have been in the market for a few decades. They are well suited for fine-grained reconfigurable architectures. Logic Element (LE) is the smallest unit of processing in an FPGA which is composed of a Look-Up Table (LUT), a few Flip-Flops (FFs), 2-to-1 multiplexers and some logic gates. Two notable FPGA vendors are Xilinx [22] and Altera [21]. For Altera, the goal is to reach at higher synthesis frequencies in their tools, while Xilinx focuses on resource utilization [23]. MOLEN model is another fine-grained device which operates as a co-processor to a General-Purpose Processor (GPP) ([24], [25]).

#### 2.2.2 Middle-Grained Devices

The word length of middle-grained devices is less than or equal to 8. On the other hand, irregular subword-length calculation increases trouble in the mapping of the algorithm, when the processing width is increased. There is a good compromise between the area and performance in this model. One of middle-grained devices is PiCoGA-III, which includes a matrix of Reconfigurable Data-path Units (RDUs), each of them composed of a 4-bit LUT, 4-bit ALU and 4-bit integer and Galois field multiplier [27], [28].

#### 2.2.3 Coarse-Grained Devices

One of the most successful platforms in the academic research and industrial environment is CGRAs due to their high-level of granularity and also the number of diverse applications that can be targeted on them without difficulty. In fact, CGRAs have a record of processing numerous data parallel applications for academic research, e.g., Image and video processing ([8], [29]), Finite Impulse Response (FIR) filtering [30], Wideband Code Division Multiple Access (WCDMA) cell search [31] and Turbo Codes [32]. Applying the CGRAs provides access to a large bandwidth and high throughput. However, CGRAs can engage a wide area of a few million gates and have potentially high transient power dissipation [26]. XPP-III is one of the coarse-grained devices. Another CGRA platform is Adjustable Dynamic Embedded System (ADRES) as a reconfigurable array of 8 × 8 elements, which is strongly integrated with a VLIW processor [13]. Each of the processing elements in the ADRES includes Functional Units (FUs) and Register Files (RFs) linked to a mesh topology. The ADRES particular instances can be produced by utilizing an XML-based architecture specification language.

#### 2.3 Multi-core Platforms

In this section, we will focus on the subject of multi-core platforms, consisting of both homogeneous and heterogeneous core models. In homogeneous model, the cores are all similar, in heterogeneous they are of different types. Additionally, other features of multi-core platforms (homogeneous and heterogeneous) are that they are C-programmable but heterogeneous platform cores may need extra customized tools compared to a simple compiler in C language, with data flow-level support. The following section will introduce some of the state-of-the-art platforms in detail.

Figure 2.1 MORPHEUS architecture [4]

#### 2.3.1 MORPHEUS

MORPHEUS ([3], [4]) is an integrated platform containing three different models: a fine-grained, middle-grained and coarse-grained reconfigurable accelerator while all of them are Heterogeneous Reconfigurable Engines (HREs). These devices are called FlexEOS, DREAM and XPP-III, and they can communicate together over an NoC. One of the suitable cases for fine-grained algorithms is the FlexEOS. Also, FlexEOS is an SRAM-based scalable FPGA that is programmable in VHDL. DREAM is a middle-grained reconfigurable DSP core that can carry out general-purpose processing by using a 32-bit RISC processor. PiCoGA core is a medium-grained reconfigurable array composed of 4-bit oriented ALUs, where up to four configurations may be kept concurrently in shadow registers [4].

XPP-III is one of the architectures of data processing based on CGRA and it can provide highly parallel processing performance. Also, XPP-III is a model of heterogeneous reconfigurable processor architecture composed of a dataflow array and VLIW processor. Figure 3.1 shows the MORPHEUS architecture. The Morpheus platform is a complex System-on-Chip that performs run-time programmability at different levels to provide a competitive computing solution [4] and dynamic reconfigurability.

#### 2.3.2 P2012

Another homogeneous multi-core platform is P2012 including 16 general-purpose processors divided into four clusters communicating with each other by using a NoC ([2], [34]). Moreover, all the processors are locally synchronous in a cluster [2]. In other clusters, processors are globally asynchronous. The P2012 platform has been tested for algorithms related to signal processing.

#### 2.3.3 NineSilica

NineSilica [1] is a homogeneous MultiProcessor System-on-Chip (MPSoC) platform. NineSilica platform includes a network of nine nodes placed in a mesh topology of  $3\times3$  processing nodes (PNs) with three rows and three columns. The interconnection between PNs is done by a hierarchical Network-on-Chip (NoC). Each node of NoC includes a 32-bit COFFEE RISC processor. All the nodes can exchange data by packet switching technique [26]. Also, NineSilica is programmable in C language. Ninesilica architecture indicates that MPSoC can obtain high parallelization efficiency [35]. Many software-defined radio applications such as correlations and FFT can be designed and implemented over the NineSilica platform. The HARP platform used in this study is a heterogeneous derivative of NineSilica.

#### 2.3.4 RAW

Reconfigurable Architecture Workstation (RAW) is composed of 16 slices of 32-bit MIPS2000 processors arranged in a 4×4 array ([36], [37]). The use of NoC has facilitated communication between processors. RAW provides both a static (determined at compile-time) and a dynamic network (determined at run-time: wormhole routing for the data forwarding) [38]. Its characteristics are similar to a reconfigurable fabric. Furthermore, programmable NoC in RAW has employed only one communication resource, resolving the wire selection problem from routing [38].

# 3. OFDM WLAN OVERVIEW

One of the spread spectrum techniques is Orthogonal Frequency-Division Multiplexing (OFDM). It divides the available bandwidth into several narrow-band channels, with orthogonal carriers. This modulation performs multiplexing operations by using frequency division. The orthogonality concept in frequency division refers to orthogonal signals, which returns to a mathematical definition in which, if two sinusoidal functions are multiplied, then the integral of this product is zero in any period of time. In fact, OFDM is a method of the general digital multi-carrier modulation to reach higher data rates close to the Shannon limit [42]. The advantage of this method is to send the data in parallel and to overcome the frequency selective fading because in this case, every part of the data is carried over a small range of frequency band. This kind of fading on this small interval practically appears linearly and can be compensated until the signal is eventually extracted.

The main benefits of using the OFDM method are its frequency selective fading due to multi-path propagation in wireless communication systems, narrowband interference, and reduction of the Inter-Symbol Interference (ISI). This means that the ISI can be decreased by transmission of several parallel symbols and increasing the symbol duration [43]. OFDM splits a higher bit rate encoded data stream into different streams of lower bit rate, then transmits them in parallel on different subcarriers all of which are orthogonal with respect to each other [39]. It is necessary to explain that for the purpose of maintaining orthogonality, both transmitter and receiver must use the same modulation method.

The benefits of OFDM are high spectral efficiency, adaptive modulation, and robustness against narrow-band co-channel interference [40]. Also, its disadvantages include the loss of efficiency due to the Cyclic Prefix (CP) and sensitivity to doppler shift [40]. The following section describes the OFDM structure consisting of transmitter, channel and receiver based on IEEE 802.11n specifications.

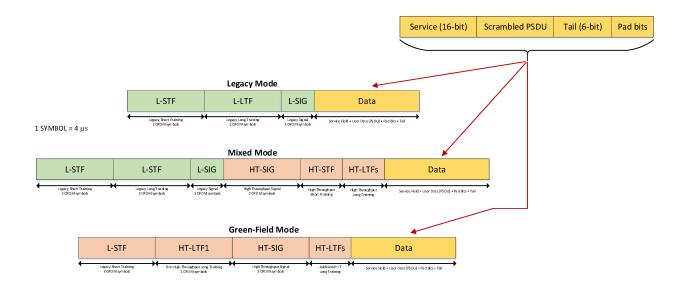

Figure 3.1 IEEE 802.11n PPDU formats in Legacy, Mixed and Green-field modes [44]

#### 3.1 MAC Frame Structure for WLAN Standards

At present, there are three types of generally accepted WLAN standards in the world. They differ only in Medium Access Control (MAC). For this purpose, table 3.1 lists these standards [42]. The first two options are applied in Europe and North America, and the last option is used in Japan. IEEE802.11 will be explained in detail below.

| No | Standards  | No | Type of MAC                                            |

|----|------------|----|--------------------------------------------------------|

| 1. | IEEE802.11 | 1. | Distributed MAC on the basis of Carrier Sense Multiple |

|    |            |    | Access/Collision Avoidance (CSMA/CA) protocol          |

| 2. | HIPERLAN/2 | 2. | Centralized mode and scheduled MAC by means wireless   |

|    |            |    | Asynchronous Transfer Mode (ATM)                       |

| 3  | MMAC       | 3  | Both the MACs listed above                             |

Table 3.1 Standards for OFDM WLANs [42]

Since the packet is transmitted, Mobile Terminal (MT) must wait for an Acknow-ledgment frame (ACK) that is required to avoid collisions. The received packet file header consists of information about the transfer rate, payload length, and transmission model, which is a modulation method.

According to the IEEE 802.11n specifications, MIMO OFDM receiver baseband processing is designed onto the HARP platform [33]. MIMO OFDM is a propitious technique to reach at high data rate, which includes benefits such as resilience to frequency selective fading caused by the multi-path propagation and to ISI [42].

Also, receiver generally carries out Time Synchronization (TS), Frequency Offset Estimation (FOE), Channel Estimation (CH), FFT and Symbols Demapping based on this standard. Predefined samples in preamble are known to the receiver [33]. Short training symbols can be used for packet detection, frequency offset estimation and timing synchronization. Furthermore, the long training symbols are used for channel estimation. The following subsections give a detailed explanation of these operations [33].

The structure of the IEEE 802.11n MAC frame is illustrated in Figure 3.1. The IEEE 802.11n standard supports the legacy IEEE 802.11a/b/g Physical Protocol Data Unit (PPDU) formats. In the IEEE 802.11n specifications, the PPDU can have several formats [44], depending on the abilities of the transmitter device such as:

- Non-High Throughput (Non-HT) Legacy mode: Composed of the preamble, which uses short and long training symbols as well as support for this format is compulsory for IEEE 802.11n standard. In addition, this may occur as either 20.0 MHz Bandwidth or a 40.0 MHz Bandwidth.

- $\circ$  20.0 MHz: The signal has 64 subcarriers with 4 pilots. pilots are inserted in subcarriers  $\pm 21$  and  $\pm 7$ . The signal is transmitted on sub-carriers -26 to -1 and +1 to +26 in the legacy mode.

- **40.0 MHz:** For this model, two adjacent 20.0 MHz channels are employed. The signal has 128 subcarriers with 6 pilots. Pilots are inserted in subcarriers  $\pm 53$ ,  $\pm 25$  and  $\pm 11$ . Also, the signal is transmitted on subcarriers -58 to -2 and +2 to +58.

- HT-Mixed mode: Preamble consist of the Non-HT short and long training symbol, which can be decoded by legacy mode in IEEE 802.11a/g. The HT-Mixed mode is compatible with IEEE 802.11a/g PLCP headers. Among other features of this mode, transmissions can occur both in 20.0MHz and 40.0MHz channels.

- **HT-Greenfield mode:** HT packet does not require a legacy compatible part to be transferred. As a result, the maximum data throughput is much higher.

The various parameters in the headers are [75]:

• Rate (4 bits): Signifies the type of modulation (8 combinations) and data Forward Error Correction (FEC) coding.

Figure 3.2 PLCP Preamble for OFDM training structure [44]

- Length (12 bits): Number of octets (bytes) carried in the Payload in Physical Layer Service Data unit (PSDU).

- Tail (6 bits): Utilized for SIGNAL symbol FEC decoding.

- Service (16 bits): To synchronize the descrambler, bits from 0 to 6 should be set to zeros and reserve the last 9 bits for subsequent purposes.

- Parity (1 bit): Parity-check on RATE + LENGTH data.

- Pad bits: Variable-length field needed to guarantee that the non-HT and HT-Data data field, including an integer number of symbols.

Figure 3.2 shows the PLCP header includes a preamble, signal and data field. There are 10 short training symbols and 2 long training symbols in the preamble. It can be noted that the length of both training symbols is 8.0  $\mu$ s with the total time of 16.0  $\mu$ s.

L-STF consists of a sequence of tones, which belong to the values +1+j and -1-j. These tones are performed on a small part of the sub-carrier, whilst the other sub-carriers will reach zero. The reasons behind this choice are that there are properties of best correlation and also low peak-to-average power ratio, which means L-STF is actually used for automatic gain control in MIMO transmission, as well as for fine-tuning the time synchronization. Furthermore, a 128-point IFFT is essential for the purpose of making a time domain sequence in the transmitter side. L-STF is known for the receiver side. For instance, time acquisition or packet detection are done by utilizing its properties of correlation peaks [43]. In addition, due to the iteration of the samples, frequency offset estimation is required, which will be described later. The sequences in frequency domain for the 20.0MHz and the 40.0MHz bandwidths are similar to the ones in the IEEE 802.11n specification as shown in Equations 3.1

and 3.2 [44].

Long Training Sequence (LTS) for 40.0MHz bandwidth mode is another preamble sequence, which has similar long symbols T1 and T2 as in Figure 3.2, as well as a guard interval (GI2) with duration of 1.6  $\mu$ s ahead of these two symbols for coping with the phenomenon of Inter-Symbol Interference (ISI). Both T1 and T2 symbols take 3.2  $\mu$ s, which means that the duration of the long training sequence (LTS) is equivalent to 8.0  $\mu$ s.

$$T_{Long} = 1.6 + 2 \times 3.2 = 8.0$$

Furthermore, T1 and T2 will be defined in the frequency domain with 115 sub-carriers, which are modulated instead of 57 sub-carriers in 20.0MHz (based on the definitions of the legacy long training). The resulting sequence is as follows [45]

Channel estimation (CE) is done in IEEE 802.11n specification utilizing the LTF fields at the beginning of each packet as well as LTF fields will be applied for more precise time synchronization and frequency offset estimation [43].

The next field in the PLCP header is the signal field containing information about TXVECTOR length and coding rate. The signal field in legacy mode informs to the receiver about the type of modulation used in the system and also the rate of coding along with the packet data length. The L-SIG field is composed of an OFDM

Figure 3.3 Subcarrier frequency allocation for 40.0 MHz with 128 subcarriers [44]

symbol, which is always BPSK modulated, as well as the length of OFDM symbol is  $4.0~\mu s$  in legacy mode. The High Throughput Signal (HT-SIG) field is composed of the information about the burst. It operates the same task as the L-SIG field unless used with one of the HT modes. In that case, it operates two OFDM symbols.

For a 40.0MHz transmission, there are 114 subcarriers in each data OFDM symbol that contains 108 data subcarriers and 6 pilot subcarriers. In other words, six of the subcarriers are allocated to pilot signals for the purpose to create the coherent detection, robust against phase noise and frequency offsets. As it should be noted, in order to prevent the production of spectral lines, pilots are produced as a sequence of pseudo-binary. Thus, pilot signals should be inserted in subcarriers  $\pm 53$ ,  $\pm 25$  and  $\pm 11$ . Based on Figure 3.3, it can be seen as the sub-carrier frequency allocation.

Equation 3.4 shows the pilot sequence for symbol n and space-time stream  $i_{STS}$  [44].

Here the patterns  $\Psi_{i_{STS}}^{(N_{STS})}$  are determined in Table 3.2 [44] and  $n \oplus a$  symbol represents the integer number a of the module. The point is that there is a different pilot pattern for each space-time stream. These patterns are cyclically rotated over the symbols. Subsequently, according to the design parameters in this thesis, the contribution of the pilot sub-carriers for each OFDM symbol is generated by Fourier

| $N_{STS}$ | $i_{STS}$ | $\Psi^{(N_{STS})}_{i_{STS},0}$ | $\Psi^{(N_{STS})}_{i_{STS},1}$ | $\Psi^{(N_{STS})}_{i_{STS},2}$ | $\Psi^{(N_{STS})}_{i_{STS},3}$ | $\Psi^{(N_{STS})}_{i_{STS},4}$ | $\Psi^{(N_{STS})}_{i_{STS},5}$ |

|-----------|-----------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| 1         | 1         | 1                              | 1                              | 1                              | -1                             | -1                             | 1                              |

| 2         | 1         | 1                              | 1                              | -1                             | -1                             | -1                             | -1                             |

| 2         | 2         | 1                              | 1                              | 1                              | -1                             | 1                              | 1                              |

| 3         | 1         | 1                              | 1                              | -1                             | -1                             | -1                             | -1                             |

| 3         | 2         | 1                              | 1                              | 1                              | -1                             | 1                              | 1                              |

| 3         | 3         | 1                              | -1                             | 1                              | -1                             | -1                             | 1                              |

| 4         | 1         | 1                              | 1                              | -1                             | -1                             | -1                             | -1                             |

| 4         | 2         | 1                              | 1                              | 1                              | -1                             | 1                              | 1                              |

| 4         | 3         | 1                              | -1                             | 1                              | -1                             | -1                             | 1                              |

| 4         | 4         | -1                             | 1                              | 1                              | 1                              | -1                             | 1                              |

Table 3.2 Pilot specific values for 40.0MHz [44]

transform of sequence  $P_{-58,58}$  based on Equation 3.5.

Table 3.3 IEEE 802.11n OFDM parameter values [45]

| Parameter                            | $\mathbf{Non}	ext{-}\mathbf{HT}_{(20.0MHz)}$     | $\mathrm{HT}_{(20.0MHz)}$           | $\mathbf{HT}_{(40.0MHz)}$            |

|--------------------------------------|--------------------------------------------------|-------------------------------------|--------------------------------------|

| FFT length                           | 64                                               | 64                                  | 128                                  |

| $N_{SD}$ : No.data carriers          | 48                                               | 52                                  | 108                                  |

| $N_{SP}$ : No. pilot carriers        | 4                                                | 4                                   | 6                                    |

| $N_{ST}$ : Total no. carriers        | 52                                               | 56                                  | 114                                  |

| $\Delta_f$ : Carrier spacing         | 312.5 kHz                                        | $312.5~\mathrm{kHz}$                | $312.5~\mathrm{kHz}$                 |

| $T_{DFT}$ : IDFT/DFT period          | $3.2~\mu \mathrm{s}$                             | $3.2~\mu \mathrm{s}$                | $3.2~\mu \mathrm{s}$                 |

| $T_{GI}$ : Guard interval            | $0.8 \; \mu \mathrm{s} = T_{DFT}/4$              | $0.8~\mu\mathrm{s}$                 | $0.8~\mu \mathrm{s}$                 |

| $T_{GI2}$ : Double GI                | $1.6~\mu s$                                      | $1.6~\mu \mathrm{s}$                | $1.6~\mu s$                          |

| $T_{L-STF}$ : L-STF duration         | $8.0 \ \mu \mathrm{s} = T_{DFT}/4$               | $8.0~\mu \mathrm{s}$                | $8.0~\mu \mathrm{s}$                 |

| $T_{L-LTF}$ : L-LTF duration         | $8.0~\mu\mathrm{s} = 2 \times T_{DFT} + T_{GI2}$ | $8.0~\mu \mathrm{s}$                | $8.0~\mu \mathrm{s}$                 |

| $T_{SYM}$ : OFDM symbol duration     | $4.0~\mu\mathrm{s} = T_{DFT} + T_{GI}$           | $4.0~\mu \mathrm{s}$                | $4.0~\mu$                            |

| $T_{L-SIG}$ : L-SIG field duration   | $4.0 \ \mu \mathrm{s} = T_{SYM}$                 | $4.0~\mu \mathrm{s}$                | $4.0~\mu$                            |

| $T_{HT-SIG}$ : HT-SIG field duration | N/A                                              | $8.0~\mu \mathrm{s} = 2~T_{SYM}$    | $8.0~\mu \mathrm{s}$                 |

| $T_{HT-STF}$ : HT-STF field duration | N/A                                              | $4.0~\mu \mathrm{s}$                | $4.0~\mu \mathrm{s}$                 |

| $T_{HT-LTF}$ : HT-LTF field duration | N/A                                              | $4.0 \text{ or } 8.0 \ \mu\text{s}$ | $4.0 \text{ or } 8.0 \ \mu \text{s}$ |

The types of modulation of data can be BPSK, QPSK, 16QAM and also 64QAM. They are similar for each burst, as well as the length of IFFT per symbol that is 128. Based on the 40.0MHz transmission for all 128 subcarriers, the frequency range

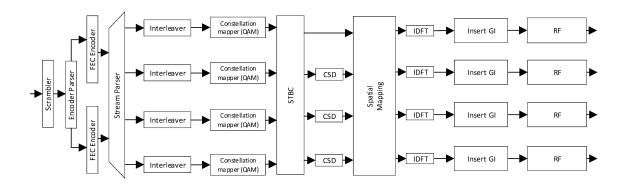

Figure 3.4 Block diagram of IEEE 802.11n transmitter [44]

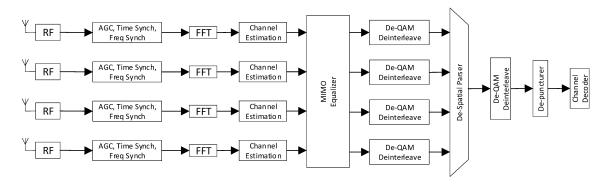

Figure 3.5 Block diagram of IEEE-802.11n receiver [10]

of each subcarrier is 312.5 kHz. According to Table 3.3, the timing parameters associated with the IEEE 802.11n signal are listed for different conditions [45].

# 3.2 Physical Layer Specifications for WLAN Standards

In broadband communication system, nowadays, OFDM is vastly utilized to tackle the frequency-selective fading. The transmitter, receiver and channel are blocks of an OFDM system. In IEEE 802.11n specification, the transmitter and receiver blocks are shown in Figures 3.4 and 3.5. The scrambler block that reduces the probability of long sequences of zeros or ones [45]. The encoder parser which de-multiplexes the scrambled bits among  $N_{ES}$  (number of FEC encoders). Forward Error Correction (FEC) encoder block is used for controlling errors in data transmission. The stream parser splits the encoder's output into blocks which are sent to ( $N_{SS}$  number of spatial streams) different interleaver and mapping devices. To avoid long sequences of adjacent noisy bits, the interleaver block interleaves the spatial stream bits. Also, the constellation mapper maps the sequence of bits in each spatial stream to constellation points. For each spatial stream, the modulation is carried out separately.

The modulation processes are two-dimensional, they are used for carrier waves of

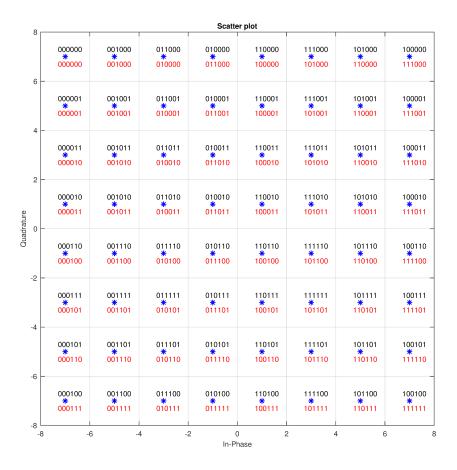

Figure 3.6 QAM naturally ordered (Red color) and Gray coded (Black color)

In-phase (I) and Quadrature (Q). Equation 3.6 shows a QAM modulation which is a combination of two modulations, Phase Shift Keying (PSK) and Amplitude Shift Keying (ASK). Moreover, 64-QAM modulation is used in this thesis work.

$$s(t) = I_k cos(\omega_c t) - Q_k sin(\omega_c t) = A_k cos(\omega t + \phi_k)$$

(3.6)

By designating a mapping, all constellation points must be labeled. There are two ways to consider to solve this issue; Grey-coding (Black color) or by natural order (Red color) as illustrated in Figure 3.6. However, there are variations between these two ways. Natural coding allows decimal numbers ordered from 0 to 63, but in Gray-coding, the adjacent representations (symbols) differ by only one bit. Therefore, two-bit errors which are also the most typical type of error between neighboring points can be reduced by applying Gray-coding, which reduces Bit Error Rate (BER) and Symbol Error Rate (SER) [42].

Then there is the space-time block coding (STBC), which is a method used in wireless communications systems to transmit multiple copies of a data stream among

Figure 3.7 Cyclic Prefix (CP) in OFDM Symbol [45]

a number of antennas. In IEEE 802.11n, STBC is applied to extend the spatial stream to double their number of space-time streams (STBC is not always used). In the cyclic shift diversity (CSD) block, cyclic shifts are used to avoid unintentional beam-forming. The values of the shifts used in the preamble fields and the data field may be different. Then, in the spatial mapper block, it can be stated that spatial mapper extends the space-time streams into a number of transmit chains.

The next block and one of the most important ones is the Inverse Discrete Fourier Transform (IDFT) that will be briefly described below. With the help of IDFT, a block of constellation points in frequency domain is converted to a time domain block. On the other hand, Discrete Fourier transform (DFT) is defined as X(k) in the frequency domain based on Equation 3.7 and also according to the sequence of N samples x(n) in the time domain. Based on Equation 3.8 [40], IDFT is used to calculate x(n) from X(k).

$$X_k = \frac{1}{\sqrt{N}} \sum_{n=0}^{N-1} x(n) e^{-j2\pi kn/N}$$

(3.7)

$$x_n = \frac{1}{\sqrt{N}} \sum_{k=0}^{N-1} X(k) e^{j2\pi nk/N}$$

(3.8)

Therefore, IFFT is done on the frequency domain QAM subcarriers to produce time domain sum of sinusoids. Subsequently, these operations will be reversed in the receiver side in order to retrieve the original data by using the Fast Fourier Transform (FFT).

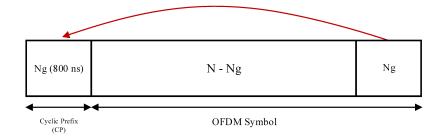

The next block is Guard Interval (GI) Block. When the IFFT is carried out, GI or CP will be added to the IFFT output [42]. In other words, guard interval insertion prepends to the symbol a circular extension of itself as shown in Figure 3.7. Accordingly, to add a CP, 32 samples (0.8  $\mu$ s) from the end of the OFDM symbol are annexed to the beginning of the OFDM symbol. The OFDM symbols must be

coordinated by a GI or CP to resist InterSymbol Interference (ISI) as well as time synchronization errors [45]. It should be noted that the ISI is basically created by receiving multiple copies of the transmitted signal due to multi-path effects and channel dispersion [47].

To clarify the issue, it will be assumed that there are two OFDM symbols, the last part of the first OFDM symbol makes interference with the first part of the second OFDM symbol upon it is received. Thus, according to the above-mentioned conditions, the amplitude and phase of the sub-carriers may deviate. Subsequently, the cyclic prefix is very important in terms of solving this problem. The delay portion of the first OFDM symbol is absorbed through the cyclic prefix of the second OFDM symbol [48]. In the windowing section, it is optionally used for smoothing the edges of each symbol in order to increase the spectral decay. After adding CP, preambles are produced which consists of short and long training symbols. Also, before transmitting the signal on the air interface by antennas, the signal must be converted from digital to analog through a digital-to-analog converter (DAC). Since the samples go through the DAC, a renovation filter is needed to eliminate the replication of the spectrum, which makes the design of this model much simpler.

In the cellular wireless communications, the transmission channel causes various unwanted changes in the signal of information resulting from reflections and diffractions. Indeed, these changes may cause noise, interference, cancellation and distortion in the systems. In addition, the channel can be described as a linear time-invariant transfer function with Additive White Gaussian Noise (AWGN). The received signal is as y(t) = x(t) + n(t), because the noise n(t) is added to transmitted original signal x(t). The signal-to-noise ratio (SNR), the signal strength to noise, is measured in (dB) unit. Based on Equation 3.9, SNR is the ratio between the power of the transmitted signal and the undesirable noise.

$$SNR_{dB} = 10\log_{10}\left(\frac{P_{signal}}{P_{noise}}\right) = 10\log_{10}(P_{signal}) - 10\log_{10}(P_{noise})$$

(3.9)

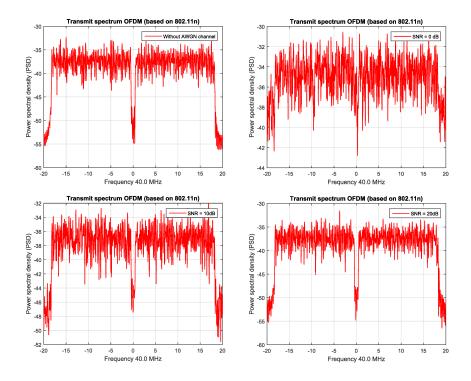

Figure 3.8 shows the Power Spectral Density (PSD) of the OFDM system in terms of the amount of SNR according to the IEEE 802.11n. PSD is the frequency response of a random or periodic signal. It tells us where the average power is distributed as a function of frequency. In other words, PSD is distribution of power, and it can be calculated by Fourier Transform of auto-correlation function of the signal. Therefore, the quality of the signal is improved by increasing SNR.

The first parts of the receiver are mostly used to detect the synchronization, estimate

Figure 3.8 Transmit spectrum of OFDM (PSD) based on IEEE 802.11n standard

the channel and equalize the symbols, whereas the remaining of the receiver blocks must be done in reverse order in the transmitter. The analog signal received for the first time is sampled and converted to a digital signal by an Analog to Digital Converter (ADC). The gain will be adjusted to an appropriate input signal level by employing the Automatic Gain Control (AGC). When the ADC is accomplished, the next block has the task of detecting packets and time synchronization. Generally, detection of the packet serves to detect the beginning of the packet, which can be performed by utilizing correlation with the short training symbols. Additionally, the time synchronization could be done using the VHT-STF field that can determine the starting point of received packets by the correlation the delayed version of itself or the inbound packet with known training symbols.

After removing the cyclic prefix, frequency offset estimation is needed to estimate the amount of frequency offset that is added to the transmitted signal on the channel, which means that the frequency offset is estimated from the VHT-STF field and corrected for the entire stream of data. Then, the stream is divided into symbols and the guard interval is removed.

The next block is channel estimation for estimating the channel impulse response by comparing the received pilots and known transmitted ones. The channel estimation of MIMO is carried out by using the VHT-LTF fields. These training symbols are

transmitted in each stream with various polarities, making them orthogonal to each other, and then the receiver has the ability to perform a channel estimation evaluation for each sub-carrier separately. Once pilots are the same in all streams, it can be stated that they are not orthogonal to each other. On the other hand, channel estimation for the subcarrier of pilots cannot be estimated by utilizing the VHT-LTF as the other subcarriers. As an alternative, interpolation between surrounding subcarriers is used to estimate the channel for the subcarriers of the pilot.

In the following receiver blocks, a linear equalization algorithm employs a reverse of the frequency response of the channel to the received signal using a Zero-Forcing equalizer [45]. Based on this model of the equalizer, it will eliminate the whole of ICI and it is ideal when the channel is without noise. When the channel is in noisy environments, the zero-forcing equalizer amplifies the noise strongly at frequencies where the channel response has a low magnitude. The equalizer converts a number of multiplexed received chains into a number of equalized space-time streams where each space-time stream provides a pilot tracker.

In the next block, the demodulation extracts the original transmitted bits from the received modulated constellations and the deinterleaver reverses the process of interleaving. Interleaver block interleaves the bits of each spatial stream to prevent long sequences of adjacent noisy bits. The block deinterleaver performs the inverse operation of the interleaver. Also, the demodulated bits are crossed through the stream departer. In the last stages, the data bits are depunctured with appending dummy zeros in the locations where encoded bits were punctured, and the symbols are transformed into a bit stream.

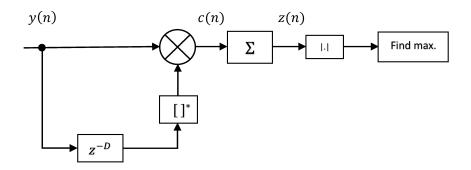

# 3.2.1 Time Synchronization

In OFDM systems, the time estimation block is used for two specific tasks which are packaging detection and symbol timing synchronization. When there is no information about the starting point of the received packet, packet detection will be required for OFDM systems. Also, in order to find the exact start point of the OFDM symbols which determines the true position of FFT window, time synchronization is needed [55]. Correlation algorithm implies to the similarity between two signals. There are two types of correlations which are auto-correlation algorithm and cross-correlation algorithm.

An auto-correlation algorithm is the correlation between a signal with its delayed version or its shifted version. The cross-correlation algorithm refers to the correlation between two different signals. Also, correlation algorithm is intensive when it is

Figure 3.9 Block diagram of correlation algorithm for time synchronization [55]

computed in time domain. So, different fast algorithms are carried out to reduce the time consumed. Packet detection is determined by applying delay and correlation [42]. The output of this algorithm,  $c_n$  is shown in Equation 3.10.

$$c_n = \sum_{k=0}^{L-1} y_{n+k} y_{n+k+D}^*$$

(3.10)

Note that  $y_n$  shows the received packet, D equals 32 (in IEEE 802.11n with 64-QAM modulation) and L stands for the length of correlation. The time synchronization block can be implemented by using two different methods as follows [54]; first, using special symbols like training symbols or null symbols, second, cyclic prefix (CP) or Guard Interval (GI) correlation algorithm. The start point of the actual data including OFDM symbols can be detected by transmitting a particular symbol, that is known to the receiver, by the transmitter in the first method. The end of short or long training symbols of a received data packet which can be seen in Equation 3.11 is used for timing synchronization in IEEE 802.11n.

$$z_n = \sum_{k=0}^{L-1} y_{n+k} t_n^* \tag{3.11}$$

Note that  $y_n$  is the received signal,  $t_n$  stands for the known symbols and (\*) shows the complex conjugate operation. As the most common way in OFDM systems, cyclic prefix method is applied when the data content is not clear. Since CP or GI is used for combatting against Inter-symbol interference (ISI). Figure 3.9 shows the signal flow structure. The amount of delay  $z^{-D}$  equals CP length which is 32 according to IEEE 802.11n standard specifications. An output  $c_n$  and  $z_n$  which are given by

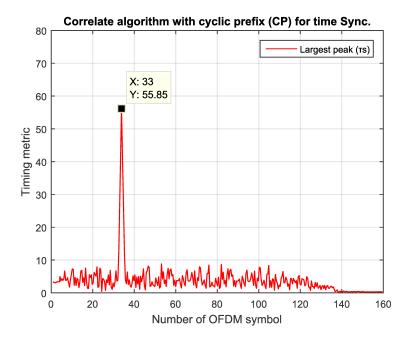

Figure 3.10 Cyclic prefix (CP) correlation along with SNR 20 dB

Equations 3.12 and 3.13 are produced in this method.

$$c_n = c_n y_{n-D}^* (3.12)$$

$$z_n = \sum_{i=0}^{L-1} c_{i+n} \tag{3.13}$$

Depending on Equation 3.14, when the correlation finishes, its largest peak should be taken to estimate the index of time offset specifying the first FFT window edge.

$$\hat{\tau_s} = \underset{n}{\operatorname{argmax}} \mid z_n \mid \tag{3.14}$$

Treatment of  $|z_n|$  in a noisy channel with no multipath propagation can be observed in Figure 3.10. If there is not any multipath propagation and received data symbol length in IEEE 802.11n equals 160 (128 FFT and 32 CP), the data symbol correlated with itself has one peak  $(\hat{\tau}_s)$  such that the length of the cyclic prefix equals the peak location minus one. Corresponding to cyclic prefix removal, samples before the peak value are skipped when the time offset is found.

•

## 3.2.2 Frequency offset Estimation

FOE will be discussed in this section according to IEEE 802.11n standard. OFDM waveform is made of multiple sinusoidal components. Before transmission, a signal is upconverted to carrier frequency. The received signal on the receiver is downconverted to demodulation from the same carrier frequency prior. The OFDM's sensitivity to carrier frequency offset is one of its drawbacks which causes device impairments [42]. Based on Equation 3.15,  $f_{\Delta}$  is the difference between the carrier frequencies on the transmitter and receiver side.

$$f_{\Lambda} = f_{Tx} - f_{Rx} \tag{3.15}$$

There are many reasons that might create a Carrier Frequency Offset (CFO) in OFDM systems because of either inconformity of frequencies between the oscillators of the transceivers or because of the Doppler spread [56]. As result of the CFO, the rotation of demodulated symbols in the constellation or ISI [53] can be noticed. Frequency synchronization should be performed very precisely at the receiver for the purpose of preventing losing orthogonality between the samples while frequency offset measurement in time domain could be done by applying maximum likelihood estimator. For this reason it is possible to use short training sequences with the duration of  $0.8\mu s$  each. Let us presume that  $x_n$  is our transmitted signal, then passband signal  $y_n$  could be modeled from the complex baseband one as

$$y_n = x_n e^{j2\pi f_{Tx} nT_s}, (3.16)$$

Here  $f_{Tx}$  is carrier frequency of the transmitter. As mentioned before, upon receiving signal, it should be downconverted to baseband signal  $r_n$  with a carrier frequency  $f_{Rx}$  that can be seen from Equation 3.17. Moreover,  $f_{\Delta}$  refers to frequency offset.

$$r_n = s_n e^{j2\pi f_{\Delta} n T_s} \tag{3.17}$$

Frequency offset that can be gained from Equation 3.18, is calculated by the same delay and correlate method.

$$y_{\hat{\tau}} = \sum_{n=0}^{L-1} r_n r_{n+D}^* = \sum_{n=0}^{L-1} s_n s_{n+D}^* e^{j2\pi f_{\Delta} n T_s} e^{-j2\pi f_{\Delta} (n+D) T_s}$$

$$= e^{-j2\pi f_{\Delta} D T_s} \sum_{n=0}^{L-1} |s_n|^2$$

(3.18)

Where D is 32  $(0.8\mu s \times 40MHz(f_s))$  according to IEEE 802.11n standard. FOE can be expressed based on Equation 3.19 when multiplication between the received signal and the complex conjugation of its delayed version is done.

$$\hat{f}_{\Delta} = -\frac{1}{2\pi DT_s} \angle y_{\hat{\tau}},\tag{3.19}$$

Consider  $T_s$  as the sampling period and  $\angle$  as the angle of  $y_{\hat{\tau}}$ , that is a correlation output in the last equation. Based on Equation 3.20, frequency offset correlation is gained by using Frequency Offset Estimation (FOE) and multiplied by the received signal. Here  $r_n$  as the corrected signal, n stands for the sample index and N is the number of samples in a symbol.

$$r_n' = r_n \times e^{-j2\pi f_{\Delta} \frac{n}{N}} \tag{3.20}$$

### 3.2.3 FFT

The most time consuming and computationally intensive block is FFT. The 128-point FFT has to be implemented within 4  $\mu s$  [12] according to IEEE 802.11n standard. The DFT will be obtained as the following Equation 3.21 [57].

$$X_{[k]} = \sum_{n=0}^{N-1} x_{[n]} W_N^{nk}$$

(3.21)

Where k=0,1,2,...,N-1 and  $e^{-j2\pi\frac{nk}{N}}$  refers to the twiddle factor for  $W_N^{nk}$ . DFT complexity is equal to  $O(N^2)$  and for FFT is  $O(\frac{N}{2}Log_rN)$ . The FFT block is expressed based on Equation 3.22 for radix-2.

$$X_{[k]} = W_N^k \sum_{m=0}^{\frac{N}{2}-1} x_{[2m+1]} W_N^{2mk} + \sum_{m=0}^{\frac{N}{2}-1} x_{[2m]} W_N^{2mk}$$

(3.22)

Also, Equation 3.23 is used for radix-4.

$$X_{[k]} = \sum_{n=0}^{\frac{N}{4}-1} x_{[n]} W_N^{nk} + W_N^{\frac{Nk}{4}} \sum_{n=0}^{\frac{N}{4}-1} x_{[n+\frac{N}{4}]} W_N^{nk}$$

$$+ W_N^{\frac{Nk}{2}} \sum_{n=0}^{\frac{N}{4}-1} x_{[n+\frac{N}{2}]} W_N^{nk} + W_N^{\frac{3Nk}{4}} \sum_{n=0}^{\frac{N}{4}-1} x_{[n+\frac{3N}{4}]} W_N^{nk}$$

$$(3.23)$$

Figure 3.11 Linear interpolation algorithm to perform the channel estimation [33]

### 3.2.4 Channel Estimation

Channel impairments may need correction because the transmitted symbols will be affected by various impairments while passing through the wireless channel. The frequency spectrum of received signal should be determined [42] when data symbols are recovered after FFT which is found by a channel estimation block. Received and demultiplexed OFDM block can be expressed according to the following Equation 3.24.

$$Y_n = X_n H_n + N_n \tag{3.24}$$

Where  $H_n$  refers to the channel response,  $N_n$  is the additive noise and n stands for the number of subcarrier. There are two ways of performing channel correction [40], one way is to estimate channel attempts to correct  $H_n$ , and the other way is to equalize the channel attempts in order to correct  $Y_n$  according to  $X_n$ . There are many different methods to compute channel estimation such as Pilot-assisted linear interpolation and Least Square (LS) [61]. There are some training symbols in WLAN OFDM such as pilots which are mostly known for the receiver [59]. Six specific values are adjusted as pilots between data subcarriers in the transmitter, as mentioned in IEEE 802.11n specifications. At first, a diagonal matrix in the receiver side, O, is formed from transmitted pilots to accomplish the channel estimation. The matrix O expressed as

$$O = \begin{bmatrix} O_{1,1} & 0 & 0 & \cdots & 0 \\ 0 & O_{2,2} & 0 & \cdots & 0 \\ 0 & 0 & O_{3,3} & \cdots & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & 0 & 0 & O_{j,j} \end{bmatrix}$$

(3.25)

Subsequently, the Channel Impulse Response (CIR) will be gained by:

$$\tilde{H}_i = O^{-1} P_{Rx},$$

(3.26)

Here  $P_{Rx}$  refers to the received pilot, which may be noisy,  $\hat{H}_j$  is representing the received pilot for channel impulse response (CIR) and j stands for the number of pilots. One of the methods for estimating the channel is using the linear interpolation algorithm, which can be seen in Figure 3.11 [60]. Furthermore, the linear interpolation algorithm is the approximate model of value in any position between two samples and due to pilot overhead on the receiver side, this method is used to solve this problem. The two sequential known pilot subcarriers in the linear interpolation are used to specify the channel response for data subcarriers. Then, the intermediate estimates will be assessed through the linear sum of known elements on both sides. The channel estimation at the data sub-carriers k will be expressed as follows [61]:

$$mL < k < (m+1)L \tag{3.27}$$

Here mL and (m+1)L are two points. Also, using a linear interpolation method in [61] can be expressed as:

$$H(n) = H(mL+1), 0 < l < L$$

$$= \left( \left( H_j(m+1) - H_j(m) \right) \times \frac{m}{L} \right) + H_j(m)$$

(3.28)

Since linear interpolation is one of the easiest methods and the samples connect to each other with a straight line, then Equation 3.29 can be expressed based on the (interp function in the Matlab) [51] by extending Equation 3.28, where  $\hat{H}_n$  refers to the channel frequency response of all subcarriers.

$$\hat{H}_n = \sum_{a=1}^{N_p - 1} \sum_{b=1}^{P_l} \left( \left( \tilde{H}_j(a+1) - \tilde{H}_j(a) \right) \times \frac{b-1}{P_l} \right) + \tilde{H}_j(a)$$

(3.29)

$N_p$  is the number of pilots and  $P_l$  refers to the data length between two successive pilots. In order to rectify OFDM symbols carrying noisy data by channel equalization, the channel frequency response must be estimated. Then the obtained  $Y_n$  symbols are similar to the  $X_n$  data. This procedure can be implemented as a result of the received signal divided by its channel frequency response, as shown in Equation 3.30.

$$\hat{Y}_n = \frac{Y_n}{\hat{H}_n} \tag{3.30}$$

## 3.2.5 Symbols Demapping

The last part of the OFDM receiver is demapping of the symbols. After performing all the synchronization and demodulation operations, demapping step will be run. Then, the true value of received data bits should be determined. The main purpose of demapping symbols is to transform received data symbols to data bits without loss of accuracy. Moreover, 64-QAM modulation was used based on IEEE 802.11n specification for this thesis work. Decisions about received data bits should be taken according to the system modulation. Also, decisions are divided into two parts, soft decisions and hard decisions [42].

- Hard Decision: If the number of transferred data bits is identical to the number of received data bits, a hard decision demodulator will be used and if the received data bits are noisy, a Gaussian cloud in the constellation points will be made by them. The difficulty is to decide on transferred data symbols related to the received data bits in this part. Maximum-likelihood decision says that allocation of bits will be carried out by hard decision if the constellation points and received bits are close to each other.

- Soft Decision: Soft Decision implies to use information bits about forwarded symbols which will give acceptable results in performance related to execution complexity [62].

When received data symbols are demapped to data bits, the quality of OFDM systems is measured in terms of bit error rate (BER). A part of bits that has errors over the total transmitted bits is called BER and it is varying as SNR changes. It reduces while SNR increases [64]. Moreover, BER is related on modulation type for the equal SNR.

## 4. PLATFORM ARCHITECTURES

The HARP platform is an experimental platform which permits to integrate at most nine NOC nodes, with the node in the center combined with a RISC core named COFFEE [65]. Other than the fact that a RISC core it is beneficial for general-purpose processing, it is necessary to be programmable and having constant supervision of the platform. Moreover, AVATAR accelerator can be combined with other nodes to speed up the tasks which are intense computationally.

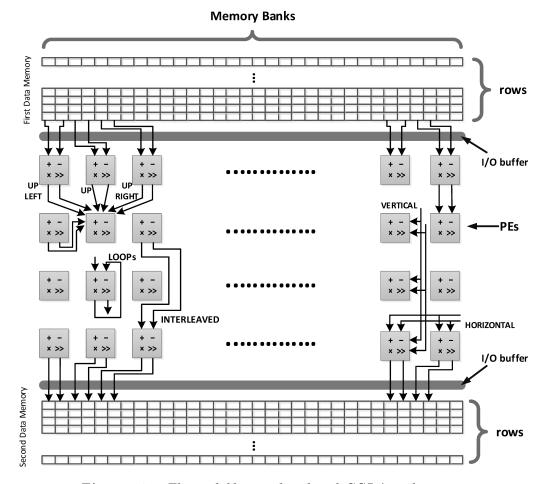

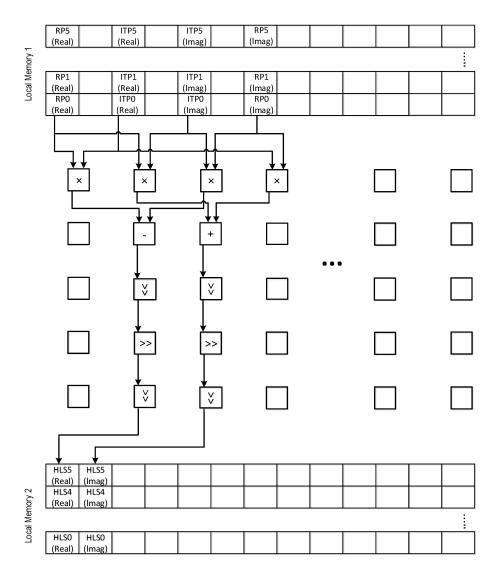

## 4.1 Coarse-Grained Reconfigurable Arrays

As illustrated in Figure 4.1, CREMA and AVATAR accelerators have similar architectural attributes, and the only difference between them is their sizes that are modified according to the applications which are proposed. CREMA consists of R rows  $\times$  8 columns of PEs whereas AVATAR that is the developed version of CREMA has R rows  $\times$  16 columns of PEs. Also, CREMA contains 32-bit local memories of size  $16 \times 256$  while the size of each local memory is  $32 \times 512$  for AVATAR. I/O buffers insert the data among local memories and the PEs. In CREMA, I/O buffers contains sixteen  $16 \times 1$  multiplexers and sixteen 32-bit registers, and the size is twice for AVATAR. The data that is processed into the local memories during an operation is loaded and stored on the PE array sequentially by applying Direct Memory Access (DMA) device [66].

AVATAR is a highly parallel template-based CGRA [66]. The computationally intensive cores are run by the accelerators generated by AVATAR, while the general-purpose processing is carried out by COFFEE that can be programmed in C. The DMA is interconnected with COFFEE, I/O peripherals and system memory through a matrix of switched interconnection. Each PE operates on two 32-bit operands and performs integer and floating-point computations. Furthermore, PE core components might be divided to two major parts: firstly, the Functional Units (FU), secondly, the control blocks of configuration. A PE includes a LookUp Table (LUT), addition, subtraction, shifter, multiplication, instant register and floating point logic that is selectable at design time based on the processing needs of the application. Figure

Figure 4.1 The scalable template-based CGRA architecture.

4.1 shows how each PE in a CGRA has point to point connection with neighboring PEs.

#### 4.1.1 CGRA Execution Flow

Placement and routing for any particular application must be done by respecting its algebraic expressions. The context describes the interconnection between the PEs and the operation to be performed by each PE at any clock cycle. Configuration words are saved at system start-up and all PEs have their own memory. Also, configuration words apply to PE arrays with a pipelined structure [67] by DMA device and each of them shows an operation and address field. By using C language, it is possible to program the control flow of AVATAR accelerators, COFFEE RISC core performs the control operation and writes control words to the control registers of the CGRA accelerators. Depending on the configuration data in the CGRA, the context changes. Therefore, whenever replacement of existing configuration stream is required, reconfiguration will be performed. Here is a list of execution flow [33]:

Figure 4.2 Heterogeneous Accelerator-Rich Platform (HARP) [33].

- 1. The DMA device at the system start-up time will facilitate the configuration data loading in the CGRA.

- 2. The data to be processed is loaded into the local memories of the CGRA.