#### SAKARI LAHTI INTEGRATION OF PROCESSOR AND SYSTEM-ON-CHIP TOOLS Master's thesis

Examiners:

Professor Timo D. Hämäläinen, Dr. Tech. Erno Salminen. Examiners and topic approved by the Faculty Council of the Faculty of Computing and Electrical Engineering on 9 October 2013.

### TIIVISTELMÄ

TAMPEREEN TEKNILLINEN YLIOPISTO Tietotekniikan koulutusohjelma LAHTI, SAKARI: Prosessori- ja system-on-chip-työkalujen yhteiskäyttö Diplomityö, 60 sivua, 0 liitesivua Kesäkuu 2014 Pääaine: Ohjelmoitavat alustat ja laitteet Tarkastajat: Prof. Timo D. Hämäläinen, TkT Erno Salminen Avainsanat: TTA, TCE, IP-XACT, Kactus2, C-to-VHDL, FPGA, SoC

Siirtoliipaistuun arkkitehtuuriin (engl. transport-triggered architecture, TTA) perustuvat suorittimet tarjoavat tehokkaan välimallin ratkaisun luotaessa IP-komponentteja System-on-chip -piireihin. TTA-suorittimien avulla suunnittelutyö on huomattavasti vaivat-tomampaa ASIC-lähestymistapaan verrattuna, ja toisaalta taloudellisempi ja tehokkaampi toteutus on mahdollinen kuin käyttäen yleiskäyttöisiä suorittimia.

Tässä diplomityössä tutkitaan tapoja nopeuttaa suunnitteluvuota käytettäessä TTAsuorittimia SoC-suunnittelutyössä. Esitetyt vuot yhdistävät "TTA-based Co-design Environment" -työkalupaketin (TCE) käytön Kactus2 IP-XACT-suunnitteluympäristön kanssa. IP-XACT-standardi ja Kactus2-työkalu helpottavat eri valmistajien tarjoamien IP-komponenttien toisiinsa yhdistämistä ja konfiguroimista, kun taas TCE-työkalut tarjoavat nopean ja tehokkaan reitin C-kielestä VHDL:ään.

Tässä työssä esitellään kolme TTA-käyttötapausta: valmiiksi tehtynä kiinteänä kiihdyttimenä, yleiskäyttöisenä suorittimena, ja räätälöitynä sovelluskohdistettuna suorittimena. Lisäksi työssä käydään läpi instanssikohtaisen datan käsittelyä IP-XACT:ssa. Suunnitteluvuot käydään askel askeleelta läpi jokaisen käyttötapauksen osalta, esimerkkitapaus esitellään, ja jokaiseen askeleeseen käytetty suunnitteluaika arvioidaan.

Vuot sisältävät 15-18 askelta ja niiden yhteydessä käytetään 8-12:ta eri ohjelmaa käsitellyistä ohjelmistotyökalupaketeista. Jos C-lähdekoodi ja IP-XACT-kirjasto ovat valmiina, insinööri voi toteuttaa FPGA-pohjaisen monisuoritinlaitteen alle 4 tunnissa ilman mittavaa aiempaa laitteistosuunnittelukokemusta. Tulosten perusteella esitellään lisäkehitysehdotuksia TCE-työkaluihin ja Kactus2:een.

### ABSTRACT

TAMPERE UNIVERSITY OF TECHNOLOGY Degree Programme in Information Technology **LAHTI, SAKARI**: Integration of Processor and System-on-Chip Tools Master of Science Thesis, 60 pages, 0 Appendix pages June 2014 Major Subject: Programmable platforms and devices Examiners: Prof. Timo D. Hämäläinen, Dr. Tech. Erno Salminen Keywords: TTA, TCE, IP-XACT, Kactus2, C-to-VHDL, FPGA, SoC

Transport-triggered architecture (TTA) processors provide an efficient middle-ground in creating intellectual property (IP) components for system-on-chip (SoC) designs. Using TTAs, the design effort is greatly reduced compared to ASIC approach, and a more economic and efficient implementation is possible than when using a general purpose processor.

This Thesis examines ways to accelerate the design flow when using TTA processors in SoC designs. The proposed flows combine the use of the TTA-based Co-design Environment (TCE) tool set and Kactus2 IP-XACT design environment. The IP-XACT standard and the Kactus2 tool make it easy to integrate and configure IP components from multiple vendors, whereas the TCE tools provide a fast and efficient path from C to VHDL.

The Thesis presents three use cases for TTA: as a ready-made fixed accelerator, a general purpose processor, and a tailored application-specific processor. Moreover, management of instance-specific data in IP-XACT is discussed. For each use case, the design flows are presented in detail step-by-step, a case example is presented, and the design time spent on each step is evaluated.

The flows contain between 15 and 18 steps and use between 8 and 12 different program tools from the studied tool sets. Provided that C source codes and IP-XACT library are available, a non-HW oriented engineer can implement an FPGA based multiprocessor product in less than 4 hours. Based on the results, further development suggestions for the TCE tools and Kactus2 are made.

### PREFACE

This Master of Science Thesis was written in the Department of Pervasive Computing at Tampere University of Technology during the fall of 2013 and the spring of 2014. The bulk of the research took place during the spring of 2012. The research results were published in the following conference article and this Thesis expands and elaborates upon the paper:

Lauri Matilainen, Sakari Lahti, Otto Esko, Erno Salminen, Timo D. Hämäläinen. Integration of TTA processor tools to Kactus2 IP-XACT design flow. Norchip, Copenhagen, Denmark, November 12-13 2012. 6 pages.

I wish to thank Lauri Matilainen, Joni-Matti Määttä and Antti Kamppi for valuable help with Kactus2 and Otto Esko and Pekka Jääskeläinen for similar help with the TCE tools. I am also thankful to my parents and friends for being there and enriching my life during all these years. Most of all, I am grateful to my supervisor Timo D. Hämäläinen who was exceptionally patient, friendly and helpful during the struggle to give birth to this Thesis.

I see great potential in both Kactus2 and the TCE tools. Hopefully, this Thesis provides at least some modest benefit to their developers.

May 14, 2014

Sakari Lahti

# CONTENTS

| 1    | Introduction                       |                                                                 |    |  |  |

|------|------------------------------------|-----------------------------------------------------------------|----|--|--|

| 2    | Overv                              | riew of TCE and Kactus2                                         | 5  |  |  |

|      | 2.1                                | TCE Overview                                                    | 5  |  |  |

|      |                                    | 2.1.1 Principles of a TTA processor                             | 5  |  |  |

|      |                                    | 2.1.2 TCE tools                                                 | 7  |  |  |

|      | 2.2                                | Kactus2 overview                                                | 9  |  |  |

|      |                                    | 2.2.1 The IP-XACT/IEEE1685 Standard                             | 11 |  |  |

|      |                                    | 2.2.2 Kactus2 IP-XACT extensions                                | 14 |  |  |

|      | 2.3                                | About instance management in IP-XACT                            | 17 |  |  |

|      |                                    | 2.3.1 Creating a new IP-XACT component from a template or draft | 17 |  |  |

|      |                                    | 2.3.2 Completing instance-specific data into IP-XACT design     | 18 |  |  |

|      | 2.4                                | Summary of the Tools                                            | 18 |  |  |

| 3    | TTA A                              | AS a fixed accelerator IP block                                 | 20 |  |  |

|      | 3.1                                | IP block design                                                 | 22 |  |  |

|      | 3.2                                | SoC design                                                      | 25 |  |  |

| 4    | TTA as a general purpose processor |                                                                 |    |  |  |

|      | 4.1                                | Processor design                                                | 29 |  |  |

|      | 4.2                                | SoC design                                                      | 31 |  |  |

| 5    | TTA a                              | s an ASIP                                                       | 33 |  |  |

|      | 5.1                                | Template processor design                                       | 36 |  |  |

|      | 5.2                                | 5.2 ASIP and SoC design                                         |    |  |  |

| 6    | An ill                             | ustrative example with crc                                      | 39 |  |  |

|      | 6.1                                | Template component creation                                     | 39 |  |  |

|      | 6.2                                | Using the component in a SoC design                             | 41 |  |  |

| 7    | Desig                              | n flow Evaluation                                               | 46 |  |  |

|      | 7.1                                | TTA as a fixed accelerator IP block                             | 46 |  |  |

|      | 7.2                                | TTA as a general purpose processor                              |    |  |  |

|      | 7.3                                | TTA as an ASIP                                                  | 50 |  |  |

| 8    | Concl                              | usions                                                          | 53 |  |  |

|      | 8.1 General remarks                |                                                                 |    |  |  |

|      | 8.2                                | Suggestions for future development of the tools                 | 54 |  |  |

|      |                                    | 8.2.1 Suggested modifications to the TCE tools                  | 55 |  |  |

|      |                                    | 8.2.2 Suggested modifications to Kactus2                        |    |  |  |

| Refe | rences.                            |                                                                 | 57 |  |  |

## LIST OF TERMS AND ABBREVIATIONS

| ASIP               | Application-specific instruction-set processor. A processor whose instruction set is tailored to benefit a certain application.                                                  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CPU                | Central processing unit. A hardware component that<br>processes the instructions of a computer program<br>performing basic arithmetical, logical and input/output<br>operations. |  |  |

| Custom FU          | Custom function unit. An FU that has been customized to perform a specific task that is not needed in all TTAs.                                                                  |  |  |

| DSP                | Digital signal processing. Mathematical manipulation<br>of information in discrete form used to modify or<br>improve it in some way.                                             |  |  |

| FPGA               | Field-programmable gate array. An integrated circuit designed to be configured by a designer after manufacturing.                                                                |  |  |

| FU                 | Function unit. A basic component within a TTA processor performing operations when it is triggered by incoming data.                                                             |  |  |

| GPP                | General purpose processor. A processor designed for running arbitrary applications.                                                                                              |  |  |

| GPU                | Graphics processing unit. An electronic circuit designed to rapidly manipulate memory to accelerate the creation of images intended for output to a display.                     |  |  |

| HDL                | Hardware description language. A computer language<br>used to program the structure, design, and operation of<br>electronic circuits. Examples: VHDL and Verilog.                |  |  |

| HLL                | High-level language. A programming language with strong abstraction from the details of the HW platform.                                                                         |  |  |

| HLS                | High-level synthesis. An automated design process that interprets an algorithm and creates digital HW that implements it.                                                        |  |  |

| HW                 | Hardware. Any physical digital electronic component.                                                                                                                             |  |  |

| IP block/component | Intellectual property block/component. A reusable HW component that is the intellectual property of one party.                                                                   |  |  |

| IP-XACT            | An XML format that defines and describes electronic components and their designs.                                                                                                |  |  |

| IP-XACT library | An organized collection of IP-XACT metadata of HW and SW components and designs saved on disk that can be accessed from Kactus2.                             |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Kactus2 library | See IP-XACT library.                                                                                                                                         |  |  |

| Metadata        | "Data about data." Contains concise information about<br>the important aspects of data.                                                                      |  |  |

| MP-SoC          | Multiprocessor SoC. A SoC design that contains multiple processors.                                                                                          |  |  |

| OSAL            | Operation set abstraction layer. A database in TCE that contains the static properties and simulation behavior of operations.                                |  |  |

| RISC            | Reduced instruction set computing. A CPU design philosophy with relatively few and simple instructions.                                                      |  |  |

| RTL             | Register-transfer level. A design abstraction which<br>models a synchronous digital circuit in terms of the<br>flow of digital signals between HW registers. |  |  |

| SoC             | System-on-chip. An integrated circuit that integrates<br>all components of an electronic system into a single<br>chip.                                       |  |  |

| SW              | Software. Any program or part of program that can be processed by a CPU.                                                                                     |  |  |

| ТСЕ             | TTA-based co-design environment. A tool set for designing and programming customized TTA processors.                                                         |  |  |

| TTA             | Transport-triggered architecture. A CPU design in which programs directly control the internal transport buses of processors.                                |  |  |

| VLIW            | Very long instruction word. A processor architecture designed to take advantage of instruction level parallelism.                                            |  |  |

| VLNV            | Vendor-library-name-version. A system for identifying HW and SW components by their vendor, library, name and version number.                                |  |  |

| VLSI            | Very-large-scale integration. A process of creating an integrated circuit by combining thousands of transistors into a single chip.                          |  |  |

| XML             | Extensible markup language. A markup language that defines a set of rules for encoding documents in a format that is both human- and machine-readable.       |  |  |

# LIST OF FIGURES

| Figure 1: A SoC architecture for MPEG-4 encoder with performance profiling suppor                                                                                         |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| [2, p. 2]                                                                                                                                                                 |     |

| Figure 2: Comparison of choices for implementing an application function                                                                                                  |     |

| Figure 3: A sample TTA processor architecture [21, p. 11]                                                                                                                 |     |

| Figure 4: The TCE design flow [21, p. 9]                                                                                                                                  |     |

| Figure 5: The general design flow and scope of Kactus2                                                                                                                    |     |

| Figure 6: Kactus2 views of the library, SoC design and system design. The SoC desig contains processors, buses and other components from the library. The processors have |     |

| SW components mapped to them in the system design where also interprocessor SW                                                                                            |     |

| communication channels are defined                                                                                                                                        |     |

| Figure 7: IP-XACT-based design flow                                                                                                                                       |     |

| Figure 8: IP-XACT components, design and design configurations                                                                                                            | .13 |

| Figure 9: Component and design hierarchy in IP-XACT                                                                                                                       | .14 |

| Figure 10: Top-level aspects in Kactus2 design flow                                                                                                                       | .14 |

| Figure 11: a) Standard IP-XACT way for including SW. b) Consequence: HW                                                                                                   |     |

| component library grows                                                                                                                                                   | .15 |

| Figure 12: a) SW as IP-XACT components and mapping from HW to SW. b)                                                                                                      |     |

| Consequence: composed designs from generic HW and SW components                                                                                                           | .15 |

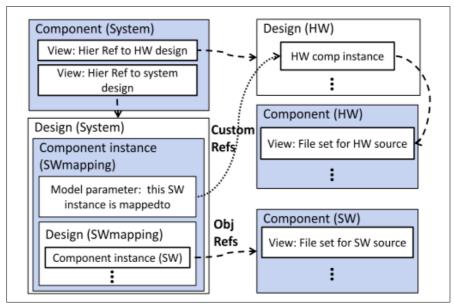

| Figure 13: Mapping between HW and SW with system design                                                                                                                   | .16 |

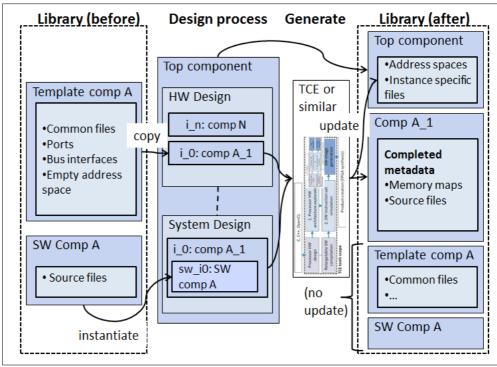

| Figure 14: Completing a template component                                                                                                                                | .17 |

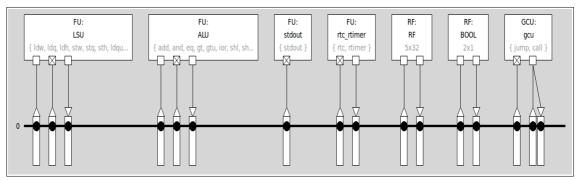

| Figure 15: The template processor architecture as seen in ProDe. Input ports with "X"                                                                                     | ,   |

| denote ports that trigger the FU                                                                                                                                          | 39  |

| Figure 16: The values given in the ports editor in Kactus2. Only the mandatory values                                                                                     | S   |

| have been entered for these simple ports                                                                                                                                  | 40  |

| Figure 17: The values given in the bus interface editor for the clock bus in Kactus2                                                                                      | 40  |

| Figure 18: The component view of the finished TTA template component                                                                                                      | .41 |

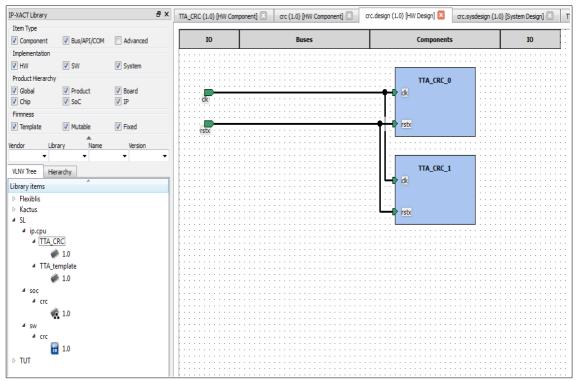

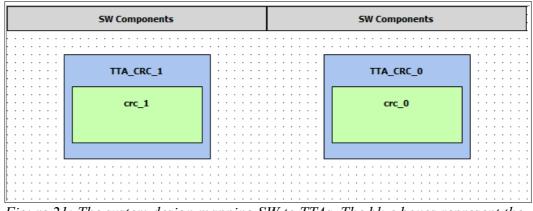

| Figure 19: The library (in the left) and the HW design with two TTA instances                                                                                             | .42 |

| Figure 20: The Kactus2 views editor for the simple TTA core                                                                                                               | 43  |

| Figure 21: The system design mapping SW to TTAs. The blue boxes represent the TT                                                                                          |     |

| and the green boxes the SW                                                                                                                                                |     |

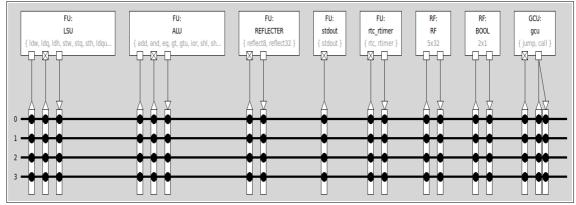

| Figure 22: The architecture of the TTA customized for CRC calculation                                                                                                     | 44  |

|                                                                                                                                                                           |     |

# LIST OF TABLES

| Table 1: The various TCE tools used in this work. The tools either have a graphical us | ser    |

|----------------------------------------------------------------------------------------|--------|

| interface (GUI) or execute from the shell command line (CLI). Output file format is a  | lso    |

| specified. [21, p. 10]                                                                 | 8      |

| Table 2: Standard IP-XACT objects and Kactus2 extended IP-XACT objects. Objects        |        |

| that are not relevant to this Thesis are marked with an asterisk                       | .16    |

| Table 3: Summary of the TCE tools and Kactus2                                          | .19    |

| Table 4: The design flow phases of a fixed accelerator IP block design and integration | 1.     |

| Phases F1-F11 contain the IP block design and phases F12-F15 integration into a SoC    |        |

| design and implementation on a FPGA                                                    | .20    |

| Table 5: The design flow phases of a general purpose TTA processor design and          |        |

| integration. Phases G1-G9 contain the processor design and phases G10-G18 the SoC      | (<br>/ |

| design and implementation on a FPGA                                                    | .27    |

| Table 6: The design flow phases of a template TTA processor creation                   | .34    |

| Table 7: The design flow phases of a custom processor creation and integration         | .34    |

| Table 8: Time-usage estimations of each phase in the design flow of TTA as a fixed     |        |

| accelerator IP block (as in Table 4)                                                   | .46    |

| Table 9: Time-usage estimations of each phase in the design flow of TTA as a general   |        |

| purpose processor (as in Table 5)                                                      | .48    |

| Table 10: Time-usage estimations of each phase in the design flow of a template TTA    |        |

| processor creation (as in Table 6)                                                     | .50    |

| Table 11: Time-usage estimations of each phase in the design flow of a custom TTA      |        |

| processor creation and integration (as in Table 7)                                     | .51    |

| Table 12: Summary of the properties of the design flows                                | .53    |

|                                                                                        |        |

## **1** INTRODUCTION

System-on-chip (SoC) integrates dozens of intellectual property (IP) components into a single chip, typical applications including telecommunication and multimedia [1]. Designing complex SoCs requires an efficient reuse of existing hardware (HW) and software (SW) components and modern design tools which enable automation. For example, the interface between HW and SW, verification, design space exploration, and product data management are very important tasks. At the same time, the required processing requirements are high while the available power budget is very limited, especially in mobile devices.

In addition to fixed HW accelerators which handle the most demanding processing, there are from a few to dozens of programmable processors, and consequently a large fraction of design costs are associated with embedded SW. Such a heterogeneous processing approach provides an affordable balance between performance and development costs.

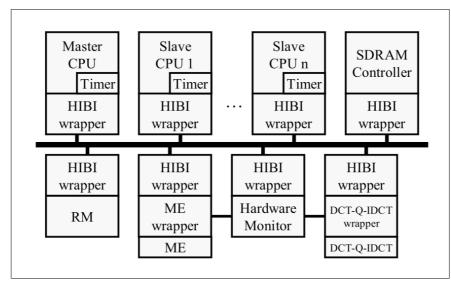

Figure 1 presents an example of a typical SoC architecture [2]. The SoC implements an MPEG-4 video encoder application on FPGA with multiple processors (CPUs) that run the application SW, two HW accelerators (ME and DCT-Q-IDCT) for resource-intensive parts of the encoding algorithm, a memory controller, a resource manager (RM) to arbitrate the processors' access to the HW accelerators, and a hardware monitor to collect data on the performance of the accelerators. In this SoC, the various components are connected by an on-chip communication network called HIBI [3] which is implemented by the wrappers connected to each component. Furthermore, the HW accelerators require their own wrappers since they have interfaces that are incompatible with HIBI. The wrappers also manage the dataflow considerations to and from the accelerators. Even this relatively simple SoC demonstrates how the design process can grow complex and thus error-prone unless rigorous designing principles are followed with efficient auxiliary program tools.

Today's SoCs are typically manufactured with 28 nm technology and can contain one or more central processing units (CPU), a graphics processing unit (GPU), internal memory blocks, external memory controllers, digital signal processors (DSP), and various external interfaces for different industry standards. In addition, application domain specific modules and accelerators are common. To give an example of a modern SoC is Qualcomm's Snapdragon 800 MSM8974 targeted for smartphones and tablets, which contains a 2.3 GHz quad-core CPU, a 450 MHz GPU, a 600 MHz DSP, a 32-bit dual-channel LPDDR3 memory controller, and radio modules for WiFi, Bluetooth and GPS

among other components [4]. This SoC has seen wide use in the mobile devices industry.

*Figure 1: A SoC architecture for MPEG-4 encoder with performance profiling support [2, p. 2].*

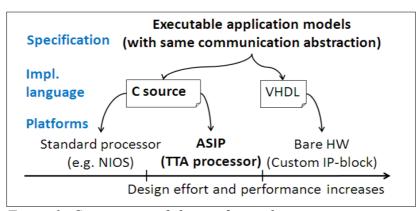

Field-programmable gate array (FPGA) is a common SoC platform whose customizability makes it an attractive option for many design problems. Figure 2 shows the different approaches to implement an application on an FPGA. The starting point is a description of the application as an executable model in C language that abstracts the communication between application functions. The first, quickest implementation option is the compilation of the C code into NIOS [5] or other general purpose processor (GPP). If the performance is not satisfactory, the next option is to use an application specific instruction-set processor (ASIP), such as a transport-triggered architecture (TTA) processor [6; 7]. The last and most laborious option is to implement bare HW by converting the algorithms into synthesizable register-transfer level (RTL) description with VHDL.

*Figure 2: Comparison of choices for implementing an application function.*

As a rough estimate, if the GPP should take 1 day, ASIP could take 2 days and RTL more than 10 days to implement. Based on a set of experiments, if the performance of NIOS is normalized to 1, a TTA can be 4x faster and RTL 2–50x faster [2]. Thus, the ASIP approach is often the most practical option since it provides a good effort-performance ratio and completely avoids or greatly reduces VHDL coding.

There are plenty of existing SoC design flows, which can be divided into high-level synthesis (HLS) approaches and integration environments. In HLS, a designer describes the application in a high-level language (HLL) such as C, SystemC or MATLAB, and the HLS tool maps this description to HW constructs as efficiently as possible. In addition to faster time-to-market, another advantage of these design methodologies is that they usually require less HW design expertise, allowing people with SW engineering skills to produce HW IP components with adequate performance. These flows are sometimes referred to as "C-to-VHDL". A popular way of implementing HLS for FPGAs is to use soft-core processors with varying degrees of configurability [7; 8; 9; 10; 11]. For example, about 4x speedup over basic reduced instruction set computing (RISC) processor was reported in [10].

Numerous SoC integration environments exist and recently they have started utilizing the IEEE1685/IP-XACT XML metadata standard as well [12; 13; 14; 15]. The goal is to packetize all reusable IPs into a library to simplify integrating and configuring them. The necessary information includes, among others, port interfaces, file sets, available parameters, and optional generator scripts. Tools can then automatically generate a structural top-level VHDL, compilation scripts, header files for SW developers, and so on. Furthermore, the vendor/library/name/version (VLNV) identifiers of all IP-XACT objects aid in version and product data management. The most important objects are component (for example CPU), interface definitions (for example AMBA [16]) and design which is a hierarchical description of the component instances and their connections.

This Thesis combines the two approaches (HLS and SoC integration environments) by focusing on enhancing the SW integration in Kactus2 design flow [17; 18; 19] using TTA processors. The approach is based on the IP-XACT standard which is originally purposed for HW IP block integration. Kactus2 expands on this, allowing capturing for example the structure of the SW stack, its mapping into processors and memory map design. The goal is to help SW engineers to implement FPGA applications by integrating TTA tools into the Kactus2 IP-XACT design environment.

The TTA tool package developed at the Tampere University of Technology is called the TTA-based Co-design Environment (TCE). Previously, there has been no formal research on how to combine the TCE and Kactus2 design flows. This work considers three different use cases of designing and integrating TTA processors with the TCE tools and Kactus2. The first case is where the TTA processor is purposed as a fixed accelerator IP block. That is, the processor will perform a single task in the most efficient way and it is not re-programmable. In the second case, the TTA is designed to be a GPP similar to NIOS. In the final, and most important case, the TTA is stored in IP library as a template component that can be reused and customized as an ASIP. The aim of the Thesis is to provide clear and efficient design flows for integrating the TCE and Kac-tus2 use in these three cases.

The rest of the work is organized as follows. Chapter 2 provides an overview of the TCE tools and Kactus2. Chapters 3, 4 and 5 present the use cases and the related design flows of TTA as a fixed accelerator IP block, GPP and ASIP, respectively. Chapter 6 contains an illustrative example of the ASIP design flow. Chapter 7 evaluates the design flows from the perspective of time-usage, and finally, Chapter 8 provides the conclusions drawn from the work.

### 2 OVERVIEW OF TCE AND KACTUS2

This work combines the use of two separately developed, freely available, open-source design environments: TTA-based Co-design Environment and Kactus2 used for IP integration.

#### 2.1 TCE Overview

#### 2.1.1 Principles of a TTA processor

The TCE tools are based on TTA processors [6], which follow the principle that computation occurs as a side effect of data transports (it can be thought that TTA is an extreme version of a RISC processor having only one instruction, *move*). Each function unit (FU) within the processor has a specific input port that triggers computation within the unit when data arrives in the port. The FUs are connected by one or more transport buses, and each instruction word of a program defines the data transfers within each bus. This allows for strong instruction level parallelism like in the very long instruction word (VLIW) processors [20]. The number of simultaneous operations within the processor is limited only by the number of transport buses. Furthermore, unlike in conventional processors, it is not always necessary to write output back to a register file as the output of a FU can be directly sent to the input port(s) of the FU that needs it. This is called software bypassing, which can significantly relieve register file port pressure and consequently energy consumption.

Thanks to transport triggering, the control logic of the processor is usually simpler than in conventional processors. Many of the control decisions that are normally made at run time can be fixed when compiling the program. This, however, means that a program compiled for a certain TTA processor is unlikely to work on any other processor since the compiled program code assumes a fixed FU and bus architecture.

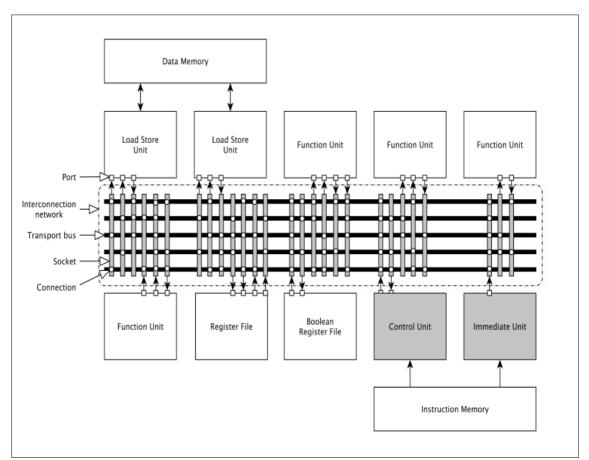

Figure 3 shows the basic architecture of a TTA processor. The sockets in the Figure define which FUs are connected to which transport buses, and furthermore they enable and disable the connections within, according to the program that is being run. Essentially, a TTA program is just a set of instructions about which connections are enabled on each clock cycle. Data flows based on the currently enabled connections and operations are triggered within FUs when new data arrives in their triggering input ports.

Figure 3: A sample TTA processor architecture [21, p. 11].

The TTA paradigm is ideal for ASIPs. The processor design model is flexible and straightforward as the main tasks are selecting the FUs and their connections, which are easy to modify thanks to the TCE tools that are discussed in the next subsection. Custom HW accelerators can be created to handle computation-intensive operations, but this is not necessary with all applications.

A comparison of performance between a simple TTA processor and various soft-core processors for several applications was performed in [10]. The TTA processor that was implemented with the TCE tools and the soft-core processors (NIOS II/f and two MicroBlaze configurations) were synthesized and run on FPGA. The results showed that the TTA processor outperformed the soft-core processors provided by major vendors on average by a factor of 1.5 to 2 when measuring speedup but even 4x speedups were measured.

TTA processors are best suited for signal processing and data flow -type applications that can be run to completion without external interrupts. Applications requiring interrupts are difficult to support since moves of one operation can span multiple instruction words, so all of the processor state cannot be represented by the registers alone, but also includes state inside execution units. Fortunately, the drawbacks of TTAs are usually not issues with ASIPs where there is often no need to run multitasking operating systems.

#### 2.1.2 TCE tools

The TCE tools are being developed at the Department of Pervasive Computing at Tampere University of Technology. Their goal is to enable an effortless design flow of programmable TTAs and to provide compilers for certain HLLs (currently C/C++ and OpenCL) to avoid writing arduous assembly code for TTA processors.

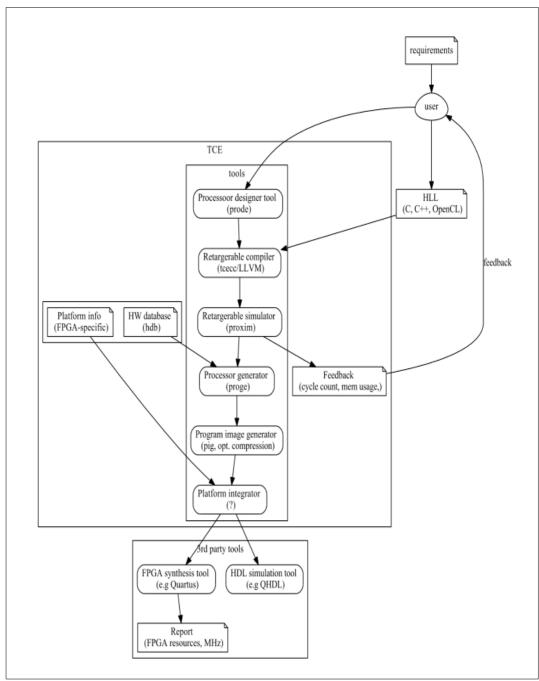

Figure 4 shows the TCE design flow which is described in an abbreviated form here. More comprehensive information can be found in [21].

Figure 4: The TCE design flow [21, p. 9].

In the first phase, the user creates a starting point processor architecture using the *Processor Designer*<sup>1</sup> tool (*ProDe*), or selects an existing architecture. He then compiles the given HLL program for the processor using a retargetable<sup>2</sup> compiler (*TCECC*). The user can then use a processor simulator program (*Proxim* or *TTASim*) to find data about cycle count and FU utilization among other things. Based on this feedback, he can change the architecture until he finds one with sufficient performance. The *Automatic Design Space Explorer* tool (*Explore*) can be used to partially automate this iterative process. After this, he can select the VHDL implementations for the FUs from the HW database (HDB) using *ProDe*.

The same FU can have different implementations in the HDB which decouples the functionality and implementation of the FUs. This is a useful property since the database can have different implementations for different FPGA families, among others.

The *Processor Generator* (*ProGe*) creates synthesizable VHDL code based on the architecture and implementation mapping, and it also includes the *Platform Integrator* which can be used to create synthesis settings and integrate the TTA with the memory components of a given FPGA board. The *Platform Integrator* can also create an IP-XACT description of the TTA with the *KoskiIntegrator* option.

In the last phase, the actual program binaries are generated using the *Program Image Generator* (*PIG*). It can create plain binary as well as various FPGA vendor specific RAM formats. Synthesis and simulation are done using FPGA specific third-party tools.

Other TCE tools include the *Operation Set Abstraction Layer Editor (OSEd)* which can be used to add information on various custom operations that the FUs may perform to the corresponding database. The *HDBEditor* is used to modify hardware databases that contain the VHDL files of FU implementations. *Estimate* can be used to approximate physical properties of TTAs, such as area, maximum clock frequency and energy consumption. Table 1 summarizes the TCE tools.

Table 1: The various TCE tools used in this work. The tools either have a graphical user interface (GUI) or execute from the shell command line (CLI). Output file format is also specified. [21, p. 10]

| Tool   | Purpose                                          | Туре | Output file(s) |

|--------|--------------------------------------------------|------|----------------|

| ProDe  | Define FUs, registers, interconnects of TTA core | GUI  | ADF            |

| TCECC  | Compile software                                 | CLI  | TPEF           |

| Proxim | Simulate TTA cores                               | GUI  | report         |

<sup>1</sup> Throughout this work, the various TCE tools are identified with italic font.

<sup>2</sup> Retargetability means that the compiler needs to know the target architecture which can change from compilation to compilation.

| Tool                         | Purpose                                         | Туре          | Output file(s)        |

|------------------------------|-------------------------------------------------|---------------|-----------------------|

| TTASim                       | Simulate TTA cores                              | CLI           | report                |

| OSEd                         | Operation set abstraction layer database editor | GUI           | operation<br>database |

| Estimate                     | Estimate physical properties of TTAs            | CLI           | report                |

| HDBEditor                    | HW implementation database editor               | GUI           | HDB                   |

| ProGe /<br>generateprocessor | Generate HDL                                    | CLI<br>(+GUI) | VHDL                  |

| PIG / generatebits           | Generate program image                          | CLI           | for example<br>MIF    |

| Platform Integrator          | Interface with memories, generate IP-<br>XACT   | CLI           | XML, project files    |

#### 2.2 Kactus2 overview

Kactus2 is a tool set for designing embedded products, especially FPGA-based multiprocessor SoCs (MP-SoC) [22]. It uses the IEEE1685/IP-XACT XML metadata and design methodology, but extends the IP-XACT usage to upper product hierarchies and HW/SW abstraction with Multicore Association MCAPI [23].

Kactus2 enables drafting and specifying from scratch block diagram blueprints for product boards, chips, SoCs and IPs and get them stored in IP-XACT format. It also allows packetizing IP for reuse and exchange by, for example creating "electronic data sheets" of existing IPs for library as templates and blocks ready for integration. Finally, it can be used in designing MP-SoC products by creating HW designs with unlimited hierarchy, and system designs that map SW to HW. Product creation is further supported by tools that automatically generate everything needed for HDL synthesis and SW build, such as top-level VHDL and Altera Quartus II project files. However, IP functionality and binaries/executables cannot be created directly in Kactus2, although there is a clear path from Kactus2 to other tools.

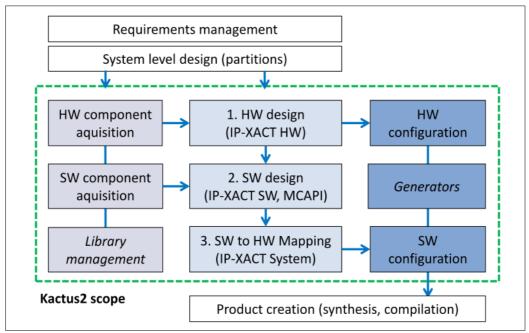

Figure 5 depicts the scope of Kactus2 and the key tasks within it. The starting point can be formal, executable models or other means of documentation on required functionality. System level design creates HW and SW partitions using for example model based tools. HW and SW components are acquired, either by creating new or reusing existing ones from a library. Metadata can be used as specification for new components.

Figure 5: The general design flow and scope of Kactus2.

The integration order is following: First HW component integration, then SW architecture design, mapping of SW components to HW instances, and finally configuring both HW and SW components for product creation. The flow describes primarily SoC design, but the phases can be applied to other levels of product hierarchy as well. For example, when "board" is the outcome, design information is related to PCB schematic, layout, part lists, silkscreens, and process-related information like test setups, test programs and test data patterns.

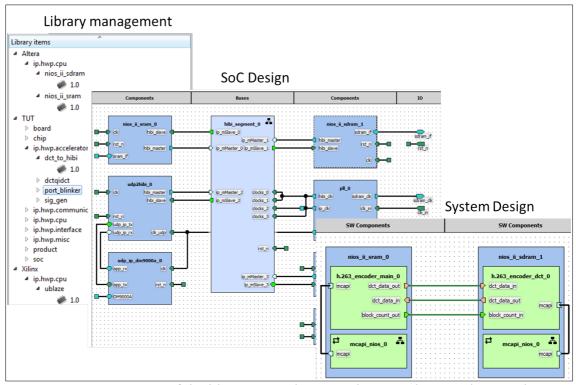

Figure 6 shows sample views from Kactus2 related to a SoC design. In the left is shown the IP-XACT library that contains all HW and SW components and designs. In the middle is the SoC (HW) design containing processors and other components along with their connecting buses. In the right is the system design where the processors have SW components mapped on them and SW communication channels are defined. Furthermore, each HW and SW component in the library or in a design can be opened and configured separately.

Figure 6: Kactus2 views of the library, SoC design and system design. The SoC design contains processors, buses and other components from the library. The processors have SW components mapped to them in the system design where also interprocessor SW communication channels are defined.

#### 2.2.1 The IP-XACT/IEEE1685 Standard

Kactus2 utilizes the IP-XACT/IEEE1685 standard that was first developed by the SPIRIT Consortium and approved as IEEE1685 in 2009. IP-XACT is an XML format that describes very-large-scale integration (VLSI) HW IP blocks to enable automated configuration and integration through tools. The scope of IP-XACT is on the IP and SoC levels, but in Kactus2 the standard is applied also to other levels, aiming at product level information management.

A core concept in IP-XACT is metadata which means data about data content. Kactus2 uses metadata for describing components and designs. Metadata for a component is a formal, vendor- and technology-independent description of the component that includes references to source files and other related information. Components are in practice HW blocks and SW code in different abstraction and granularity levels. For a design, metadata is a formal structural description that includes references to component metadata, tools, configurations and other design-related information.

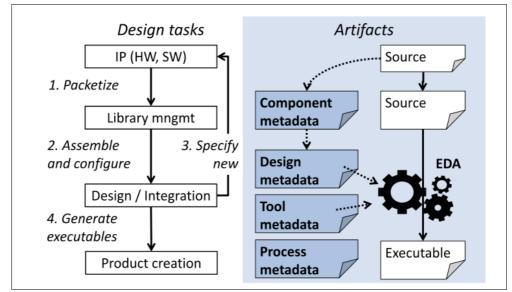

Figure 7 summarizes the main IP-XACT design steps. The sources are encapsulated and separated from the IP description. This means that the HDL source code is embedded via links to the source file in metadata file. IP blocks are assembled together in a design, which is a structural description of the system. IP blocks as well as the design itself may have generic parameters, which are configured using generators that are typically scripts. The final configured IP-XACT design can be seen as "instructions" on how to create an executable. In Kactus2, IP-XACT metadata is also used backwards as specification for a new IP block not yet existing.

Figure 7: IP-XACT-based design flow.

*IP-XACT objects* are XML metadata files representing SoC components, structure, and configurations. IP-XACT design environment handles these objects, but not directly the source files. The final design including all components and their connections is also an object itself. IP-XACT objects are uniquely identified and referred to by a tuple {V,L,N,V} stating Vendor-Library-Name-Version. All VLNV tuples are unique, independent of what kind of IP-XACT objects they identify. The XML file name and its location on disk are not defined themselves.

A SoC design flow may use several models for the same IP block or design, starting from high-level abstract models down to implementation accurate models. Typically, models are separately stored and each might have a different description language (for example UML, SystemC, VHDL). IP-XACT can include all different abstraction level descriptions in one metadata object. Instead of several separate objects, there can be only one with several options. This helps keeping the library coherent and help automating the path from specification to implementation. IP-XACT also supports mixed abstraction levels at the same time.

An *IP-XACT component* is a general placeholder describing all IP block types like processors, memories, accelerators and building blocks for buses and various interfaces. A component contains independent elements that can be referenced between each other.

*Views* are used to represent different roles of the component. Example views include "RTL implementation", "documentation" and "SW implementation."

Components are connected using *bus interfaces*, *bus definitions*, and *abstraction definitions*. Bus interface defines a grouping of ports, with ports allowed to be included in multiple different bus interfaces. Bus definition specifies general bus properties like whether bus is addressable and what kind of connections are allowed. Abstraction definition defines logical bus signals and constraints related to them such as bus width and direction of logical signals. A *port map* defines the mapping between physical and logical signals.

*File sets* and *file set groups* are folder and file collections that can be associated to views. Example file set groups include "application," "interrupt," and "device driver." File sets include information about used tools, description languages and instructions on how to handle files.

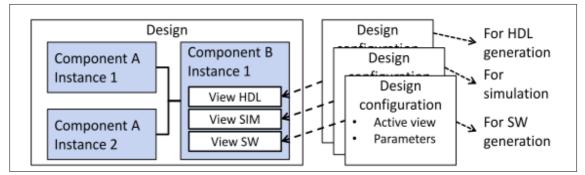

An *IP-XACT design* is like a traditional schematic of components. It describes a list of component instances, their configuration, and connections to each other. For a design, several *design configurations* exist for different purposes. Figure 8 illustrates the relationship between components, designs and design configurations.

Figure 8: IP-XACT components, design and design configurations.

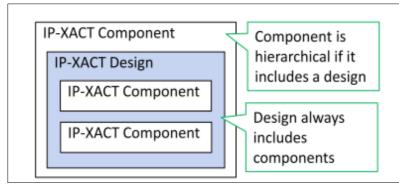

A hierarchy of designs is implemented as follows (see also Figure 9):

- IP-XACT designs never refer to other designs. Instead, a design always refers to components that are instantiated into design.

- The design must be wrapped inside a component in order to use it as a sub-design. Thus, an IP-XACT component refers to an IP-XACT design.

- An IP-XACT design can always be used as an IP-XACT component.

Figure 9: Component and design hierarchy in IP-XACT

#### 2.2.2 Kactus2 IP-XACT extensions

IP-XACT was originally purposed for HW descriptions. Kactus2 extends this to use SW and system-level descriptions to apply IP-XACT to its design flow and to make IP-XACT easier to use. Information on these extensions can be found for example in [24] and [25], but the key points are summarized below.

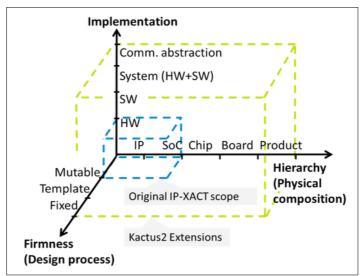

The Kactus2 design flow manages three top-level aspects:

- *Product hierarchy:* This defines the scope of the work.

- *Implementation:* All objects are categorized according to HW, SW, system (HW and SW mappings), and communication abstraction.

- *Firmness:* Each library object is one of the following: Mutables are reusable components that can be modified. Templates must be saved to a new version prior to use. Fixed have all parameters determined for frozen product releases.

Standard IP-XACT elements are used to describe the above top-level aspects. Comparison of the original scope of IP-XACT and these aspects is shown in Figure 10.

Figure 10: Top-level aspects in Kactus2 design flow.

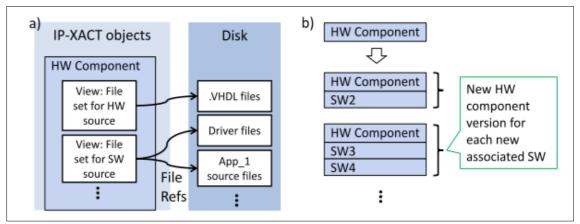

A standard IP-XACT HW component may include references to SW through *model views* and file sets pointing to files on disk. In the worst case, a new HW component version is needed every time the component is instantiated in a new design with new related SW (Figure 11). In Kactus2, this is avoided by creating IP-XACT objects also for *SW components*.

*Figure 11: a) Standard IP-XACT way for including SW. b) Consequence: HW component library grows.*

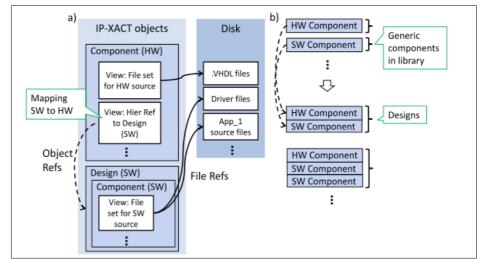

With separated HW and SW components, designs can be composed without adding design-specific files and elements to HW components as shown in Figure 12. However, referencing to SW from HW components is still allowed, but now *object references* are used (references between VLNVs). Using this mechanism, the mapping from HW component to SW component is made through *SW design*. SW design may include only one instantiated SW component, or there can be several SW components of its own hierarchy.

Figure 12: a) SW as IP-XACT components and mapping from HW to SW. b) Consequence: composed designs from generic HW and SW components.

To instantiate HW and SW components on the same IP-XACT design, a *system design* is defined. It is a SW design that includes mappings of SW component instances to HW component instances. Since IP-XACT does not specify HW/SW mappings, a *model parameter* is added to each SW component for the mapping that is configured in system design (Figure 13).

Figure 13: Mapping between HW and SW with system design.

To summarize, the mapping of SW to HW can be done either by component hierarchical model view specified in a HW component ("from HW to SW") or by instantiated component model parameter specified in a system design ("from SW to HW").

Table 2 collects the standard IP-XACT objects and Kactus2 extended IP-XACT objects together. Objects that are not relevant to this work have been omitted from the explanations in this chapter.

| <b>IP-XACT standard objects</b> | New Kactus2 objects                          |  |  |

|---------------------------------|----------------------------------------------|--|--|

| HW component, HW design         | SW component, SW design                      |  |  |

| HW design configuration         | API definition* (SW)                         |  |  |

| Bus definition                  | COM definition* (SW, HW)                     |  |  |

| Abstraction definition          | System design (SW architecture mapped to HW) |  |  |

| Generator chain*                | System component (SW architecture)           |  |  |

*Table 2: Standard IP-XACT objects and Kactus2 extended IP-XACT objects. Objects that are not relevant to this Thesis are marked with an asterisk.*

### 2.3 About instance management in IP-XACT

The standard IP-XACT integration flow starts from reusable components that are instantiated, connected, and configured in an IP-XACT design. Unfortunately, the standard has problems with instance-specific definitions. Although generics and connections are well defined, for example address spaces and SW components are not. The basic question regards which values to store to the reusable component and which to the instances. Two approaches are considered in the following.

#### 2.3.1 Creating a new IP-XACT component from a template or draft

Figure 14 depicts a design process with templates or incomplete components in the beginning. A template is a component that is never used as such in a design; it is like an abstract base class in programming. In this example, the IP-XACT library includes a few TTA template components that define only the information common to all instances that are generated from them, like generators, and which connection is used with an onchip network, and if an external memory interface is used (SRAM or DRAM). User makes a copy of the template, gives it a new VLNV, and instantiates it in the HW design.

Figure 14: Completing a template component.

Kactus2 also offers an option to "draft" new components. User just adds an empty component, connects it to others and defines a VLNV identifier. The necessary interface types are detected automatically and serve as part of the requirements for the IP development team. This is one way of creating a TTA template component for the library.

In Figure 14, source files are added to the new component A\_1 later by a component specific generator. However, in the worst case the library will contain as many components as there are instances in various designs.

#### 2.3.2 Completing instance-specific data into IP-XACT design

Figure 14 also depicts the second approach where instance-specific data is stored to the place of the instantiation, that is to the SoC. As a specific example, one can consider the address space definition that can be added to master interfaces in IP-XACT. It defines what kind of segments the component can access using a certain interface. Thereby, address space naturally depends on the design where the component is instantiated. Address space should not be confused with the memory map that describes which registers of a component are visible to others, which is usually not instance-specific information.

Again, the designer creates a HW design with all the necessary IPs followed by an optional system design phase. The example assumes that template comp A has an empty address space defined at first. The segments of the address space are then determined based on the other components in the HW design. The complete address space is used in SW compilation and stored to a top-level HW component (for example SoC) which refers to the HW and system designs. The same principle applies to SW mapping data.

Moreover, if VHDL files of an IP are automatically generated based on a few instance-specific parameters (for example data width, cache size, #FUs), they could be stored into the top component's file set as well. The reusable component holds only the generator script, interfaces, parameter list, and documentation. Each instance defines the parameter values for the generator which produces the implementation files. This approach encapsulates the TTA-instance-specific values and files to the SoC component without augmenting the library with numerous components.

#### 2.4 Summary of the Tools

Table 3 contains a summary of the primary properties of the TCE tools and Kactus2 for quick reference.

Table 3: Summary of the TCE tools and Kactus2.

|                         | TCE tools                                                                                           | Kactus2                                                                         |

|-------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Purpose                 | Designing and programming<br>customized processors based on<br>the transport triggered architecture | Designing, specifying and<br>managing embedded products,<br>especially MP-SoCs. |

| Platform                | Linux                                                                                               | Linux and Windows                                                               |

| Developer               | Tampere University of<br>Technology                                                                 | Tampere University of<br>Technology                                             |

| Home page               | http://tce.cs.tut.fi/index.html                                                                     | http://funbase.cs.tut.fi/#main                                                  |

| License                 | MIT License                                                                                         | GPL2 General Public License                                                     |

| Implementation language | C, C++, Python                                                                                      | C, C++/Qt5                                                                      |

| Lines of code           | 217,000                                                                                             | 274,000                                                                         |

The lines of code includes comment lines. The tools are constantly evolving so the most current information can be found on their respective web sites.

## 3 TTA AS A FIXED ACCELERATOR IP BLOCK

Thanks to the TCE tools, one can efficiently develop various fixed TTAs each tailored to a certain application. These can be saved to the IP-XACT library, and the integrator can drag and drop them into a SoC design like any other IP component. There is only minimal if any processor configuration by the user. The processor's IP-XACT component metadata includes the VHDL source files for HW, and SW source code and memory image maps of the program it executes. This use case is natural in a situation where the processor design and SoC design are done by a different person, although both can be designed by the same engineer as well. The design flow for this use case is described after Table 4 which summarizes it.

| #  | Phase                                                           | Input                                                              | Tools                                                | Output                                 |

|----|-----------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------|----------------------------------------|

| F1 | SW application<br>design and testing<br>on a PC <i>or</i> reuse | Application<br>specification<br>documents <i>or</i><br>reused code | SW code<br>writing tools,<br>testing<br>environment  | Platform-independent<br>SW source code |

| F2 | Initial TTA<br>processor design                                 | HW<br>specification<br>documents,<br>requirements of<br>SW         | ProDe                                                | Initial processor ADF                  |

| F3 | Program<br>compilation for<br>initial TTA                       | Initial processor<br>ADF, source<br>code files                     | TCECC                                                | Initial TPEF                           |

| F4 | Design space<br>exploration                                     | Initial ADF,<br>Initial TPEF                                       | Proxim,<br>TTASim, ProDe,<br>TCECC, OSEd,<br>Explore | Final processor ADF                    |

Table 4: The design flow phases of a fixed accelerator IP block design and integration. Phases F1-F11 contain the IP block design and phases F12-F15 integration into a SoC design and implementation on a FPGA.

| #      | Phase                                                                                                      | Input                                                                    | Tools                                                                              | Output                                                                                                                                               |  |

|--------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| F5     | C code modification<br>and compilation for<br>TTA                                                          | Platform-<br>independent SW<br>source code                               | SW code<br>writing tools,<br><i>TCECC</i>                                          | TTA-tailored C<br>source code files,<br>final TPEF                                                                                                   |  |

| F6     | <i>Optional:</i> VHDL<br>implementation for<br>FUs if not already in<br>HDB                                | FU<br>requirements                                                       | VHDL writing<br>tools,<br><i>HDBEditor</i>                                         | VHDL files for FUs,<br>edited HDB                                                                                                                    |  |

| F7     | FU implementation mapping                                                                                  | Final ADF,<br>HDB                                                        | ProDe                                                                              | IDF                                                                                                                                                  |  |

| F8     | Estimation of physical properties                                                                          | Final ADF, IDF,<br>final TPEF                                            | Estimate                                                                           | Estimation results                                                                                                                                   |  |

|        | Either F9 if the estim                                                                                     | ation results are s                                                      | atisfactory or bac                                                                 | ck to F4 if not                                                                                                                                      |  |

| F9     | Either F9.a or F9.b                                                                                        |                                                                          |                                                                                    |                                                                                                                                                      |  |

| F9.a   | Processor, memory<br>controller, and top-<br>level entity<br>generation with<br><i>Platform Integrator</i> | Final ADF, IDF,<br>final TPEF,<br>memory<br>specifications               | Platform<br>Integrator                                                             | Top-level and<br>hierarchical VHDL<br>files of the processor<br>and memory<br>controllers, top-level<br>entity VHDL, FPGA<br>synthesis project files |  |

| F9.b.1 | Manual processor generation                                                                                | Final ADF, IDF                                                           | ProGe                                                                              | Top-level and<br>hierarchical VHDL<br>files of the processor                                                                                         |  |

| F9.b.2 | Manual memory<br>controller<br>generation                                                                  | Memory<br>specifications                                                 | VHDL writing<br>tools or target<br>platform's<br>memory<br>controller<br>generator | Memory controllers'<br>VHDL files                                                                                                                    |  |

| F9.b.3 | Manual top-level<br>entity VHDL<br>generation                                                              | Top-level<br>VHDL files of<br>the processor<br>and memory<br>controllers | VHDL writing<br>tools                                                              | Top-level entity<br>VHDL                                                                                                                             |  |

| F10    | Memory image generation                                                                                    | Final ADF, Final<br>TPEF                                                 | PIG                                                                                | Instruction and data<br>memory images in<br>chosen format                                                                                            |  |

| F11    | Either F11.a or F11.b                                                                                      |                                                                          |                                                                                    |                                                                                                                                                      |  |

| F11.a  | IP-XACT<br>component creation<br>(if <i>KoskiIntegrator</i><br>was not used in F9)                         | All files created<br>in the previous<br>steps,<br>documentation          | Kactus2<br>component<br>creation wizard                                            | IP-XACT component<br>of the TTA in library                                                                                                           |  |

| #     | Phase                                                                                 | Input                                                                                                                     | Tools                                                                           | Output                                                        |

|-------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------|

| F11.b | IP-XACT<br>component<br>augmentation (if<br><i>KoskiIntegrator</i> was<br>used in F9) | IP-XACT file<br>created by<br><i>KoskiIntegrator</i> ,<br>all files created<br>in the previous<br>steps,<br>documentation | Kactus2                                                                         | Augmented IP-<br>XACT component of<br>the TTA in library      |

| F12   | SoC design                                                                            | IP-XACT files<br>of the TTA and<br>other<br>components in<br>the design                                                   | Kactus2                                                                         | Kactus2 HW design                                             |

| F13   | Top-level VHDL<br>generation of the<br>HW design                                      | Kactus2 HW<br>design                                                                                                      | Kactus2                                                                         | Top-level VHDL of<br>the HW design                            |

| F14   | FPGA synthesis<br>project file<br>generation                                          | Kactus2 HW<br>design                                                                                                      | Kactus2 (for<br>Quartus II) or<br>target platform's<br>SoC designing<br>program | FPGA synthesis<br>project files                               |

| F15   | FPGA synthesis and programming                                                        | All the VHDL<br>files, memory<br>image files,<br>FPGA synthesis<br>project files                                          | FPGA synthesis<br>and<br>programming<br>tools                                   | The entire design<br>synthesized and<br>programmed on<br>FPGA |

### 3.1 IP block design

The initial part of the flow is the same as in Section 2.1.2, but it is described in more detail here. An even more detailed description can be found in [21], along with information on how to use the various tools mentioned here.

The flow begins with writing or reusing a C program code that performs the specified functionality of the accelerator block. The code doesn't need to be customized for TTA at this point, and indeed it should be tested on a workstation PC for correct functionality. If in the final product, the processor takes external input from for example a program running on another processor, it should be provided by the program itself at this point. In other words, the external I/O is emulated in the program. If possible, dummy values may be used.

When the SW code is ready, a starting point architecture of the TTA is created. This is done using the *ProDe* tool. The starting point architecture should contain at least the

minimum resources required to run the program. External I/O functionality can be omitted at this point. The end result is saved in an architecture definition file (ADF).

In the next phase, the program is compiled for the architecture using the *TCECC* compiler. The C source code files and the ADF file are given as parameters to the compiler, and the compiled TTA program is saved in the TTA program exchange format (TPEF) file. This is not a bit image that can be run on a physical platform, but it is used in simulating the program on the target TTA.

There are two instruction set simulator options, either *Proxim* that has a graphical user interface or *TTASim* which is command-line based. Both provide statistics about the cycle counts and utilization of FUs. The designer then modifies the TTA architecture based on the simulation results and specified performance and resource-usage requirements. The basic optimization options include modifying the algorithm itself at code level, adding more resources to the TTA (FUs, register files, buses), and adding custom operation FUs to the TTA. Details on performing these optimizations are outside the scope of this work but they can be found in [21, Section 3.1]. This design space exploration is an iterative process where different TTA architectures are created and tested until a satisfactory one is found. The *Explore* tool can be used to partially automate this process.

The designer should add any FUs related to external HW (for example various external I/O components) to the architecture at this point. If their implementation does not yet exist, he needs to add the related custom operations to the TCE's operation set abstraction layer (OSAL) using *OSEd*, map them to FUs and create the VHDL implementation of the FUs.

After finding a suitable architecture, the C code needs to be modified to be run on the TTA processor. Specifically, any input and output to/from the processor's internal custom FUs and I/O units needs to be handled in the C code using macros defined in the "tceops.h" library that includes a corresponding macro for each operation in OSAL. The modified code is compiled to create the final TPEF file.

The next phase is to create a VHDL implementation of the processor. First, each FU in the TTA needs to be mapped to a HW implementation. The implementations are stored in the TCE's HW database (HDB). There can be several different implementations for the same FU that differ in resource usage and target platform. If some FUs don't have an implementation in the HDB, they must be created by writing the VHDL and adding information on them to the HDB using the *HDBEditor* tool. The implementation mapping is performed using *ProDe*, and the result is saved in the implementation definition file (IDF).

With the implementation mapping, it is possible to use the *Estimate* tool to provide estimates on the energy consumption, die area, and maximum clock rate of the TTA. The final ADF, IDF and TPEF files are given as input parameters to the *Estimate* tool. If the output report contains unsatisfactory results, the flow returns to design space explo-

ration where the architecture, SW code and/or FU implementations are modified until the results improve, whereupon the designer can move on to the processor generation phase.

The TCE tools contain the *Platform Integrator* that is part of the *ProGe* tool. It supports automated integration of TTA cores to different FPGA platforms. The design flow divides in two parts here, depending on whether there is support for the target platform in the *Platform Integrator*.

If the *Platform Integrator* can be used, the final phases of the processor generation are rather straightforward. The user invokes the command-line version of the *ProGe* tool and gives to it as parameters the ADF, IDF and TPEF files, and parameters defining target platform and the type of instruction and data memory used. The *Platform Integrator* saves the processor's VHDL implementation files in a specified folder, creates memory controller VHDL, a top-level entity and even project files for FPGA synthesis with default pin-mappings. It should be noted that if the *Platform Integrator* is used, the processor's internal component implementations must be selected from the platform-specific options in the HDB. Currently, there is *Platform Integrator* support for Altera's Stratix II DSP Pro board and Stratix III FPGA Development Kit board. The *Platform Integrator* can also create an Altera SOPC Builder [26] component from a TTA processor, and a HIBI bus compatible processor.

If the *Platform Integrator* does not support the target platform, then the processor, the memory controllers, and the top-level VHDL entity must be created manually. The processor is generated either directly using *ProDe* or with the command-line *ProGe* tool. The ADF and IDF files are given as parameters and the VHDL implementation of the processor is saved in the target directory by the tool. The memory controllers, and the top-level entity connecting the TTA to the memory controllers and containing ports for external signals are created by hand. Another option is to use the *Platform Integrator* anyway, and then modify the automatically generated files to support the target platform.

The *PIG* tool is used to create a bit image of the program which can be uploaded to the target platform's memory for execution. It is invoked from the command-line with the "generatebits" command, and the ADF and TPEF file and the chosen instruction and data memory formats are given as parameters.

The *Platform Integrator* has an option that generates the IP-XACT file of the processor automatically. This *KoskiIntegrator* adds all the relevant data to the IP-XACT except for file sets containing source code and other documentation files which must be manually added with Kactus2. When *KoskiIntegrator*, which requires Altera FPGA and HIBI support, cannot be used, Kactus2 can create the IP-XACT file with an integrated component creation wizard. The user adds the relevant files (VHDL, program code, documentation, and so on) to the file sets and writes a description of the component in the corresponding field. The IP-XACT component is then automatically created based

on the top-level VHDL component. The created component is saved in the IP-XACT library for integration and use in designs. There, it is seen as any fixed IP block. All TTA instances created from the same component are identical and run the same code.

### 3.2 SoC design

The use of the previously created TTA IP block component is straightforward in Kactus2. The SoC designer simply drags and drops the component from the library to his HW design and connects it to other components. Its functionality is fixed so the only customization can be done on SoC level.

The top-level VHDL file of the HW design is created automatically by the Kactus2 VHDL generator. Kactus2 also creates the FPGA synthesis file automatically for Altera's Quartus II program. If it is not used, the project file must be created using the target platform's SoC designing program. The entire design is now ready to be synthesized and programmed on FPGA using the platform-specific tool.

## 4 TTA AS A GENERAL PURPOSE PROCESSOR

In this use case, the TTA processor is used like any GPP. Hence, in the library it is an IP-XACT component which includes a CPU element but not a fixed program image. The processor is instantiated in a HW design and SW code is mapped to it in a Kactus2 system design. Existing SW code can be reused from the library or it can be created from scratch. Once the SW code is mapped to the TTA instances, the *TCECC* and *PIG* tools are invoked for each processor-program pair to generate program images.