# TERO IHAMÄKI FPGA BASED ETHERNET MEDIA LEVEL TESTER

Master's thesis

Examiner: Timo D. Hämäläinen

#### **ABSTRACT**

TERO IHAMÄKI: FPGA based Ethernet media level tester

Tampere University of Technology

Master of Science Thesis, 67 pages, 3 Appendix pages

April 2018

Master's Degree Programme in Information Technology

Major: Embedded Systems

Examiner: Professor Timo D. Hämäläinen

Keywords: FPGA, VHDL, Ethernet, testing, debugging, monitoring, low level

Ethernet is a mature technology with wide usage area in devices communicating with each other. Internet of Things is constantly increasing the number of devices in the world-wide network. Security of aspects of these devices should be considered carefully, creating the need to test devices on Ethernet level.

This thesis presents design and implementation of a test device functioning on media level of Ethernet. By modifying, injecting and monitoring Ethernet frames transmitted on the communication media, the functionality of a device under testing can be debugged and tested in different situations. The test device is a multi-purpose communication tester, providing several possible usage areas, but is originally developed for debugging and testing purposes for a custom communication protocol used in Ethernet based automation system. At the time of writing this, the tester is already in use as a part of other test equipment of the automation system.

The tester is implemented using existing automation device, consisting four Ethernet ports and an FPGA chip. All functionality is implemented on FPGA, making the implementation work on the hardware level. This brings new possibilities compared to testing Ethernet devices with multifunctional processor based design. The tester is to be connected to the communication media between the tested devices. In a normal situation, the tester device is routing unmodified frames through it with only insignificant delays, making it invisible to surrounding devices. However, based on user commands, frames can be modified runtime or inject new frames to inputs of a device under testing.

There are some related commercial Ethernet testing devices already on the market. However, those are found to be expensive and does not provide similar features for frame modifying than the device introduced here. Main drivers for the project was to develop low cost or free testing and monitoring device with the possibility to update the features based on needs found in future.

The thesis presents basics of Ethernet with two lowest OSI-layers, functional principles of FPGA chips and other needed aspects on theory level. The theory is then followed by introducing functionalities, design, and implementation of the device. Afterwards, we take a look at the actual tests, how those function and observations noticed during testing. Lastly, we summarize briefly the thesis and consider the possible future development of the project.

### TIIVISTELMÄ

Tero Ihamäki: FPGA based Ethernet media level tester

Tampereen teknillinen yliopisto Diplomityö, 67 sivua, 3 sivua liitteitä Huhtikuu 2018

Tietotekniikan diplomi-insinöörin tutkinto-ohjelma

Pääaine: Sulautetut järjestelmät Tarkastaja: Timo D. Hämäläinen

Avainsanat: FPGA, Ethernet, VHDL, testaus, debuggaus, monitorointi

Ethernet on pitkään käytössä ollut ja laajasti vakiintunut kommunikaatiomedia. Internet of Things (IoT) laitteet kasvattavat verkkoon liitettyjen laitteiden määrää entisestään. Näiden laitteiden tietoturvaan täytyisi kiinnittää erityistä huomiota, synnyttäen tarpeen laitteiden testaamisella Ethernetin laitteistotasolla.

Tässä diplomityössä on rakennettu Ethernetin laitteistotasolla toimiva testaus- ja monitorointijärjestelmä. Muuttamalla ja lisäämällä uusia paketteja sekä monitoroimalla Ethernet väylää voidaan väylälle liitettyjä laitteita testata ja selvittää niissä piileviä ongelmia. Laite tarjoaa monikäyttöisen, useaan eri sovellusympäristöön käytettävän vaikka olikin alun perin suunniteltu automaatiojärjestelmässä testilaitteiston. käytettävän Ethernet pohjaisen kommunikaatioprotokollan testaukseen. kirjoitettaessa testauslaitetta käytetään jo muun testausympäristön tukena automaationjärjestelmää testattaessa.

Testauslaite on toteutettu olemassa olevan automaatiojärjestelmässä käytettävän sulautetun laitteen päälle, joka sisältää neljä Ethernet porttia ja FPGA piirin. Kaikki toiminnallisuus on toteutettu FPGA piiriä käyttäen, joten laitteisto toimii käytännössä rautatason toteutuksena. Tämä tuo uusia mahdollisuuksia Ethernet laitteiden testaukseen verrattuna perinteiseen prosessoriarkkitehtuuriseen tapaan. Testauslaite kytketään Ethernet-mediaan testattavien laitteiden väliin. Toteutettu laitteisto modifioi verkkoliikennettä reaaliaikaisesti käyttäjän komentojen mukaisesti. Muun ajan Ethernet väylälle liitetty laite pysyy näkymättömissä muulta verkolta reitittäen verkolla liikkuvat paketit lävitseen, aiheuttaen vain merkityksettömän viiveen.

Joitakin vastaavia laitteita on jo olemassa markkinoilla, jotka ovat kuitenkin hyvin kalliita eivätkä vastaa ominaisuuksiltaan tässä työssä esitettyä laitetta. Työn tärkeimpinä tavoitteina oli kehittää edullinen tai jopa ilmainen testaus- ja monitorointijärjestelmä, jota voidaan päivittää käyttäjäkokemusten perusteella.

Työssä esitellään Ethernetin kaksi alinta OSI-kerrosta, FPGA-piirin toimintaperiaate sekä muita työn tekemiseen vaadittavia tietoja teorian tasolla. Lisäksi esitellään toteutetun testauslaitteen perusperiaatteita ja arkkitehtuuria. Tämän jälkeen esittelemme toteutettuja testejä, näiden käyttöä ja huomioita testejä tehdessä. Lopuksi esittelemme tulokset ja loppupäätelmät sekä mietimme mahdollisia kehityskohteita.

### **ALKUSANAT**

Tämä diplomityö on tehty Tampereen teknillisen yliopiston tietokonetekniikan laitokselle. Työn ohjaamisesta vastasi Timo D. Hämäläinen. Työn aikana sain ohjaajilta arvokkaita neuvoja sekä ohjausta työn tekemiseen. Kiitokset läheisilleni ja ystävilleni sekä erityisesti tyttöystävälleni tuesta ja kannustuksesta.

Tampereella, 22.4.2018

Tero Ihamäki

### **CONTENTS**

| 1. | INTE              | RODUCT                 | ION                                                          | 1   |  |  |

|----|-------------------|------------------------|--------------------------------------------------------------|-----|--|--|

| 2. | THE               | ORY                    |                                                              | 4   |  |  |

|    | 2.1               | Ethernet               |                                                              |     |  |  |

|    |                   | 2.1.1                  | Overview                                                     | 4   |  |  |

|    |                   | 2.1.2                  | Media-independent interface (MII)                            | 6   |  |  |

|    |                   | 2.1.3                  | Frame structure                                              | 9   |  |  |

|    |                   | 2.1.4                  | Internet protocol v4 (IPv4) and User datagram protocol (UDP) | .10 |  |  |

|    |                   | 2.1.5                  | Address Resolution Protocol (ARP)                            | .11 |  |  |

|    | 2.2               | FPGA                   |                                                              | .12 |  |  |

|    |                   | 2.2.1                  | Hardware description language                                | .14 |  |  |

|    |                   | 2.2.2                  | Clocking and metastability                                   | .15 |  |  |

|    |                   | 2.2.3                  | Implementation process and simulation of FPGA                | .17 |  |  |

| 3. | PRODUCT OVERVIEW  |                        |                                                              |     |  |  |

|    | 3.1               | Develo                 | pment environment                                            | .19 |  |  |

|    | 3.2               | Usage o                | overview                                                     | .20 |  |  |

|    | 3.3               | Tests ar               | nd features                                                  | .22 |  |  |

|    |                   | 3.3.1                  | Preamble and start frame delimiter (physical layer)          | .24 |  |  |

|    |                   | 3.3.2                  | Destination address (data link layer)                        | .24 |  |  |

|    |                   | 3.3.3                  | Source address (data link layer)                             | .24 |  |  |

|    |                   | 3.3.4                  | EtherType and length (data link layer)                       | .25 |  |  |

|    |                   | 3.3.5                  | Payload modifying (data link layer)                          | .25 |  |  |

|    |                   | 3.3.6                  | Frame check sequence (data link layer)                       | .25 |  |  |

|    |                   | 3.3.7                  | InterPacket Gap length                                       | .25 |  |  |

|    |                   | 3.3.8                  | Send a custom frame from a file                              | .26 |  |  |

|    |                   | 3.3.9                  | Runt frames                                                  | .26 |  |  |

|    |                   | 3.3.10                 | Swap order of frames                                         | .26 |  |  |

|    |                   | 3.3.11                 | Delay selected number of frames                              | .27 |  |  |

|    |                   | 3.3.12                 | Delay all frames                                             | .27 |  |  |

|    |                   | 3.3.13                 | DoS with blocking all communication                          | .27 |  |  |

|    |                   | 3.3.14                 | DoS with allowing all communication                          | .28 |  |  |

|    |                   | 3.3.15                 | Drop frames                                                  | .28 |  |  |

|    |                   | 3.3.16                 | Invert single bit from frame                                 | .28 |  |  |

| 4. | DES               | [GN                    |                                                              | .29 |  |  |

|    | 4.1               | Communication protocol |                                                              |     |  |  |

|    | 4.2               | 2 Data flow            |                                                              |     |  |  |

| 5. | IMPI              | IMPLEMENTATION         |                                                              |     |  |  |

|    | 5.1 Communication |                        |                                                              |     |  |  |

|    |                   | 5.1.1                  | UDP/ARP receiver                                             | .36 |  |  |

|    |                   | 5.1.2                  | UDP/ARP transmitter                                          | .37 |  |  |

|     |       | 5.1.3   | Instruction decode                        | 38 |

|-----|-------|---------|-------------------------------------------|----|

|     |       | 5.1.4   | Receive and transmit FIFOs                | 39 |

|     |       | 5.1.5   | Reconciliation layer                      | 39 |

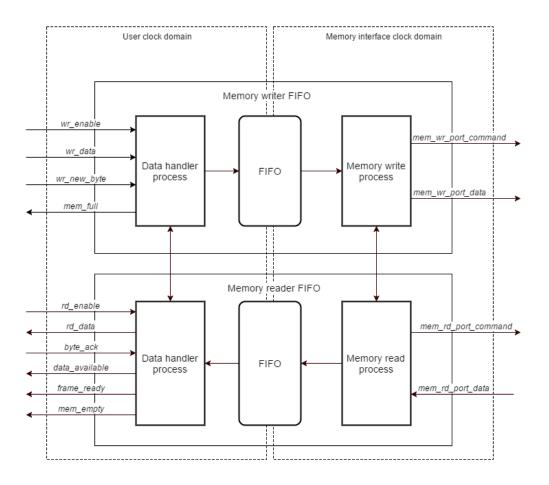

|     | 5.2   | Memor   | ry control                                | 39 |

|     |       | 5.2.1   | Memory Interface Generator (MIG)          | 40 |

|     |       | 5.2.2   | Memory FIFOs                              | 40 |

|     |       | 5.2.3   | Memory input/output multiplexer           | 43 |

|     | 5.3   | Ethern  | et modifier                               | 43 |

|     |       | 5.3.1   | Data receiver and pre-process             | 43 |

|     |       | 5.3.2   | Test selector multiplexers                | 44 |

|     |       | 5.3.3   | Post-process and test supporting features | 44 |

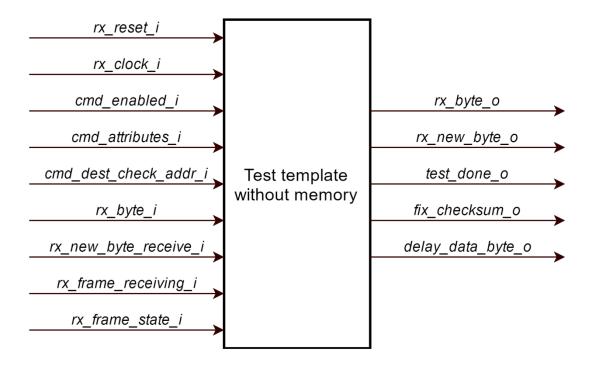

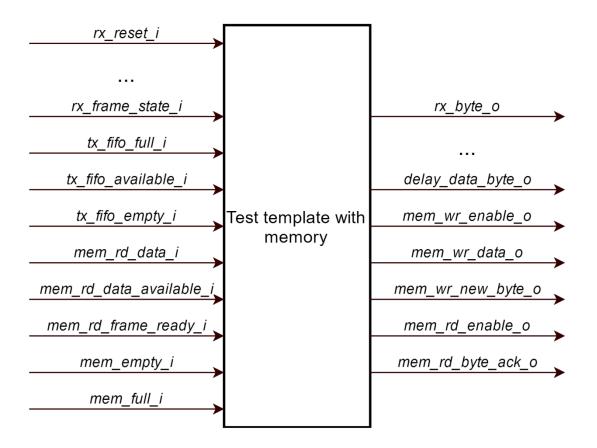

|     |       | 5.3.4   | Test blocks                               | 45 |

| 6.  | TEST  | Γ RESUI | LTS AND OBSERVATIONS                      | 49 |

| 7.  | CON   | CLUSIC  | ONS                                       | 57 |

| BIE | 3LIOG | RAPHY   |                                           | 59 |

|     |       |         |                                           |    |

#### **ABBREVIATIONS**

ASIC application specific integrated circuit

CLB configurable logic block CRC cyclic redundancy check

DDR double data rate

FF flip-flop

FIFO first-in-first-out

FPGA field programmable gate array

HSR High-availability Seamless Redundancy

IEEE Institute of Electrical and Electronics Engineers

IOT Internet of Things

IP Internet Protocol

IPG InterPacket Gap

ISO International Organization for Standardization

LUT look-up table

MAC media access control

MII media independent interface

MITM man-in-the-middle (attack)

OSI Open Systems Interconnection

PHY physical (layer)

RAM random access memory RX receive, reception

TCP Transmission Control Protocol

TX transmit, transmission UDP User Datagram Protocol

VHDL Very High Speed Integrated Circuit Hardware Description Lan-

guage

### 1. INTRODUCTION

From the beginning of the introduction of the Internet in the 1960s, the number of electronic devices connected and communicating with each other has been rising rapidly. In 2017, almost half of world habitants are using Internet and more than 80 % in developed countries [6]. Internet of Things (IoT) boom in the late 2010s marked another remarkable rise in a number of devices. Devices are no longer controlled only when humans are controlling those, but instead, information is shared automatically between devices as well. Suddenly many the of most traditional consumer appliances like TVs, refrigerators, cars and even toothbrushes are connected to the Internet and sharing information to cloud services. When companies are pushing more and more devices to the Internet, profits are often prioritized over security aspects. When the amount of Internet devices increases, increases also a number of possible targets to be attacked and hacked. [4] Hacking consumer devices usually places the individual and his/her personal information in danger, but when considering technology in industrial areas like power plants, the danger rises to national or even global level [5].

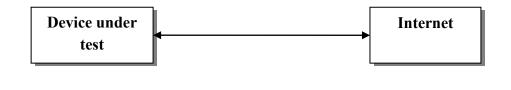

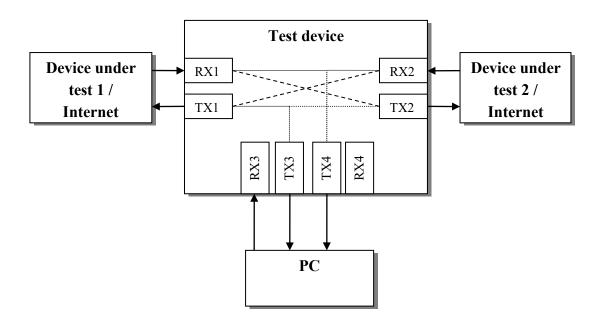

The goal of the thesis is to introduce one concrete approach to improve security aspects of the devices pushed to the Internet. All the devices that are connected are relying on same principles of sharing information by sending and receiving data packets through communication media. By injecting a device acting as a tester to the communication media level itself, the devices using the communication media can be tested by monitoring and modifying the data packets on the media. This way inputs and outputs of a device can be tested in its real usage environment. Usage and connectivity example can be seen in Picture 1.1. This thesis introduces a test device with twisted pair cabling Ethernet ports, but also devices with wireless media WLAN (wireless local area network) can be tested if connection media is first converted to Ethernet e.g. by using a router.

Picture 1.1 Overview of the test system

In order to test in Ethernet media level, a hardware level system design is needed to avoid long delays introduced by the tester itself. Traditional approach using the software on microprocessors is not fast enough, because functions, like reading memory and handling interrupts, introduce too much delays. With microprocessors, different functionalities have to compete for available resources, which will delay throughput from input to output further every time a new piece of functionality is added. That is a common problem for all sequential systems like microprocessors, a problem that won't be truly solved even by adding a higher and higher performance processors.

However, designing system in hardware offers a new kind of approach by providing a parallel handling of data throughput for different parts of functionalities. In the past designing a system in a hardware has been cumbersome and only a talent of a few. However, designing and implementing digital systems in hardware has become easier after the introduction of programmable hardware logic and hardware description languages. Many design aspects and challenges in the implementation of a digital circuit with Application Specific Integrated Circuit (ASIC) can be abstracted away when using Field Programmable Gate Arrays (FPGA). In terms of digital circuits, using areas of FPGA circuits are almost limitless, as FPGA can implement basically any digital circuit. Compared to ASIC, FPGA also provides the possibility to update the features afterwards. This said, ASIC was not considered as an implementation technology, as FPGA is more suitable and readily available technology for this project.

The test device project was ordered by an international industrial company working in the area of engine mechanics. Products of the company also include automation system for monitoring and controlling the engine products. The automation system consists of several embedded device communicating with each other and with computers using communication media. Previously Controlled Area Network (CAN) bus was used for the communication purposes, but as the amount of data is increasing, the CAN bus is replaced by Ethernet media providing more communication bandwidth. The nature of usage of the automation system forces it to be as robust as possible, introducing a need for a test system injecting unexpected anomalies to the communication media and test the ability of automation system to cope with such situations. During the development of the communication protocol used in the automation system, problems of lost frames were faced. Means to monitor the communication media is required to solve these problems. On the other hand, a way to reproduce and create seen and unseen problems with the protocol requires a way to modify frames or inject completely new frames would have been highly useful during the development. The test device implemented for this thesis is supposed to tackle all these issues.

A development board for the test device development project is provided also by the company. The development board is actually an embedded device used as a part of the automation system, which will be re-used for a completely different purpose in this project than what it was originally designed for. However, apart from various other inputs, outputs, and even a microcontroller, the device also consist four Fast Ethernet 100 Mb/s physical layer transceivers with RJ45 ports and an FPGA chip with straight connections to the transceivers. So it is also an ideal device for this project, even though it does consist one major restriction as well. The Ethernet speeds in this project are limited to Fast Ethernet 100 Mb/s category, ruling out commonly used Gigabit Ethernet with 1000 Mb/s speeds.

Work on this thesis has been mostly focused on implementation of the test device. The purpose of this document is to describe fundamentals of the system. Firstly we go through the theory used around the system, describing used technical aspects. Secondly, we go through features and facts of the system, giving a technical overview of architectural and algorithmic decisions. Lastly, we will show results of the project with example tests, as well as observations and possible next steps with the implementation.

### 2. THEORY

To understand the implementation aspects of the test device with the usage of FPGA technology, a preview of the used technologies will be needed. We will first look into Ethernet technologies used in the test system. After that, we will focus on fundamentals of programmable hardware in terms of FPGA technology, how it works and what kind of design aspects is needed.

#### 2.1 Ethernet

Group of technologies of Ethernet is standardized by IEEE. The first standard for IEEE Std 802.3 was introduced in 1983 with a half-duplex communication at a maximum data rate of 10 Mb/s [8]. After that, the Ethernet technology has been advancing with a full-duplex operation and higher data rates up to 10000 times the original 10 Mb/s, with new 100 Gb/s standard. Robust performance and constant development have placed Ethernet to dominant technology in local area networks (LAN) with wide usage in the industry as well. The latest IEEE standard revision is IEEE Std 802.3-2015, published in 2016.

#### 2.1.1 Overview

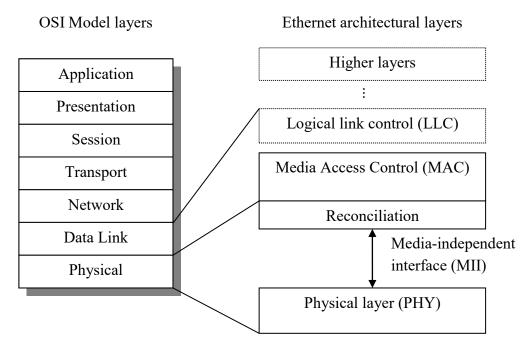

Hardware level testing of Ethernet can be concentrated on two lowest layers of ISO Open Systems Interconnection model (OSI model, ISO/IEC 7498-1 [9]). The goal of OSI model is to abstract communication system to a layered presentation based on different functionality and protocols used in each layer. The model is divided into seven abstraction layers, lowest being a physical layer (PHY). PHY is responsible to handle transmission of opaque data from the device to another through a physical medium. The second layer in OSI model is a data link layer, providing means of encapsulating data into frames to be communicated over the PHY. Data link layer also has other responsibilities like detecting errors during transmissions and addressing nodes connected to the networks. Data link layer is divided into two sub layers, media access control (MAC) and logical link layer (LLC). From these two only MAC layer is mandatory from Ethernet point of view, LLC layer being unspecified among IEEE Std 802.3 standard. Architectural model of Ethernet described in IEEE Std 802.3 standard is intentionally similar with physical and MAC sub layer in the OSI model, as shown in Picture 2.1.

Picture 2.1 IEEE 802.3 Ethernet layer architecture. Adopted from [7].

Layers communicate only with layers directly above and below them and as interfaces between them are supposed to be kept unchanged, internal implementation of the layer can be changed freely. Thus, one implementing, for example, a MAC layer to a device does not have to consider the internal implementation of the PHY. Conceptually MAC layer is only sending and receiving single bits, which introduces the need for slim reconciliation layer between MAC sub layer and Media-Independent Interface to capsulate single bits into a format accepted by MII. Media-independent interface is on the other hand used to hide the implementation of different PHY devices, making it possible to intermix PHYs with separated MAC device. MII implementation is tied into PHY implementation, but in practice, all PHY devices supporting same transmission speeds will use same MII interface, thus the name media-independent. [7] Because Ethernet technology is based on the layered architecture, a developer does not need to know the inner functionality of physical layer level device in case MAC and PHY is separated in the design. Knowing interface of the PHY device is enough to connect MAC and implement a working Ethernet device.

IEEE 802.3 specifies many physical layer technologies. The most used are 100BASE-TX and 1000BASE-T. Both are base on twisted-pair Category 5 copper cabling, but latter uses four pairs instead of two in the former [10]. Also, 10 Mb/s transmission, 10BASE-T, was based on same shielded twisted-pair cabling, but newer technologies have taken over and not used widely anymore. The cabling method described under

standard ANSI/TIA/EIA-568-A is the most widely used Ethernet media technology and used in this thesis project as well.

Auto-negotiation feature available in PHY is made to select the highest speed possible between linked devices. It is fully backwards compatible, meaning that Gigabit device can communicate with old devices using 10 Mb/s speeds by using fastest possible common speed of 10 Mb/s. The half-duplex mode was first a dominant but has now been almost completely been replaced with full-duplex mode. In half-duplex one communication bus was shared with all linked devices, resulting in collisions of Ethernet frames when more than one linked device started transmission at the same time. Collisions were handled with a procedure called carrier sense multiple access with collision detection (CSMA/CD). Simply put, this rather complex mechanism made the linked devices to listen to changes in voltage in the cable segment. If a cable segment seemed to be at idle, the device could start the transmission. However, if another device started a transmission at the same time, a collision could be noticed from abnormalities in the voltage levels. After collision detection a jam signal is sent to cable segment making all participants wait for a random time before sending again, thus making new collision quite improbable. Collisions, of course, affect also the average speed of the cable segment, halting all communication when a collision is detected. Thus greater amount of linked devices on a cable segment affected negatively on Ethernet speeds. Full-duplex mode, on the other hand, allows communications in both directions at the same time, making collisions physically impossible. On the down-side full-duplex mode needs two twisted-pair cables instead of one in half-duplex. Nevertheless, the gains on full-duplex are far more superior, making it possible to utilize full 10/100/1000 Mb/s speeds to both directions and making communication protocol much simpler.

### 2.1.2 Media-independent interface (MII)

As stated in the previous chapter, the media-independent interface is located between MAC and physical layer. MAC layer is often integrated to the same integrated circuit (IC) with the PHY, but as in our device, those can be separated as well and connected together with electrical wiring on a circuit board. To send and receive data using physical layer device with MAC sub layer implementation, it is mandatory to understand basics of MII.

Throughout the years various different MII designs have been introduced by IEEE standardization organization as well as telecommunication industry. The designs differ by a number of input and output pins, clocking speed for data sampling on the interface and supported data rates. Different MII implementations can also transmit data on either both clock edges, which is called double data rate (DDR), or only with rising clock edge on single data rate (SDR) implementation. Increasing data rate on the interface forces design either to use more pins, higher clock speeds, double data rate, or a combination of these three. In Table 1 is shown the most common MII interfaces.

Table 1 MII interfaces overview

| Name                                              | Data<br>rate<br>[Mb/s] | Number<br>of pins | Clock<br>rate<br>[MHz] | DDR |

|---------------------------------------------------|------------------------|-------------------|------------------------|-----|

| MII  Media-independent interface                  | 10, 100                | 16                | 25                     | No  |

| RMII Reduced media-independent interface          | 10, 100                | 8                 | 50                     | No  |

| GMII Gigabit media-independent interface          | 1000                   | 24                | 125                    | No  |

| SGMII Serial gigabit media-independent interface  | 10, 100,<br>1000       | 4                 | 625                    | Yes |

| RGMII Reduced gigabit media-independent interface | 10, 100,<br>1000       | 12                | 125                    | Yes |

| TBI Ten-bit interface                             | 1000                   | 24                | 125                    | No  |

Selecting MII affects overall hardware level pin count and chip size on the system design. In recent years MII, GMII, and TBI have been giving way to reduced interfaces with lower pin count. This happens due to ASICs associated with MIIs are often required to have an increasing number of peripheral ports even though dye sizes are getting smaller, thus requiring as low interface pin counts from peripherals as possible [11]. On the other hand, smaller chip sizes allow higher clock rates as clock routing lengths will reduce, thus higher needed interface clock rates are usually not a problem. Still, MII designs with higher pin counts like MII and GMII still have uses in several areas. FPGA chip implementing associated MAC is often one of those.

Using high clock rates on FPGA can be often an issue as clock routing can get complicated at least in big designs. Thus it is often a good trade-off in FPGA to use more interface pins, allowing bigger designs with lower clock rates. This is also the case in the system presented in this thesis, using a separate physical layer device providing Fast Ethernet speeds at 100 Mb/s and MII interface (without any prefix) to be used with

FPGA implementing the MAC layer. More about FPGA design fundamentals will be presented in chapter 2.2.

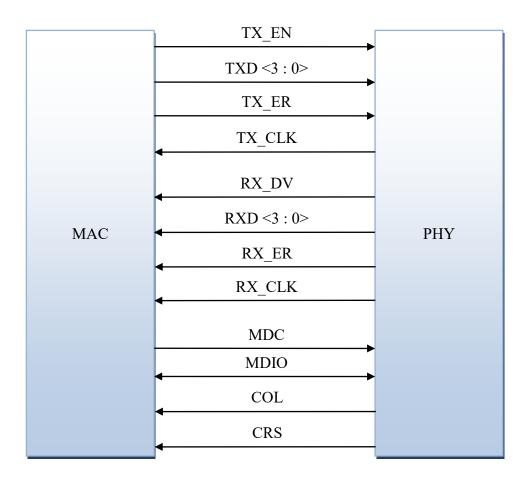

Media-independent interface (MII) is the oldest of the presented interfaces and defined in IEEE 802.3 standard chapter 22 [7]. It was defined for Fast Ethernet family with 100 Mb/s speed and also supports older 10 Mb/s speed. Selecting the speed is made possible with the auto-negotiation feature, but it can be also forced to a selected data rate through MII management interface (MIIM). An overview of media-independent interface signals is illustrated in Picture 2.2.

Picture 2.2 Media-independent interface signals Adopted from [7].

Full-duplex operation is enabled in MII with completely separate transmit and receive data paths. These data paths named TXD and RXD are both 4 bits wide. The data is synchronized with rising edges of TX\_CLK and RX\_CLK respectively. TX\_CLK and RX\_CLK are fed by PHY, so MAC has to synchronize its data handling functions with these external clocks. Clocks have a frequency of 25 MHz when operating at speed 100 Mb/s and 2.5 MHz when using 10 Mb/s speed. When sending data with TXD, TX\_EN signal has to be asserted and otherwise de-asserted. TX\_ER signal is optional and can

be asserted if MAC notices some issue during transmitting a frame. If TX\_ER is asserted, PHY will deliberately corrupt the ongoing frame so that receiver notices the frame is not valid. When RXD has valid received data, RX\_DV bit is asserted. RX\_DV will stay set for the whole frame and new four bit chunk of data can be read with every rising edge of RX\_CLK. RX\_ER bit can tell MAC that the received frame is corrupted and should be discarded. CSR and COL signals are meaningful with half-duplex operation only and used with CSMA/CD feature. CRS (carrier sense) is set when communication medium is in use and COL is set when a collision is detected on the medium. MDC and MDIO signals are related to MII management interface. It is a serial bus used to control PHY features like auto-negotiation, speed, full-/half-duplex mode, perform a reset and detect if a link has been established.

#### 2.1.3 Frame structure

In the layered Ethernet architecture, media access control layer was separated from other layers, meaning the same conceptual MAC layer is used with all Ethernet variants. This means that the one Ethernet and MAC frame format presented here is applicable to all transmission technologies and speeds, making the media access control device design much simpler without a need to consider all possible associated technologies. IEEE Std 802.3 describes the standardized Ethernet frame structure and is shown in simplified form in Picture 2.3.

| / bytes  | 1 byte | 6 bytes                | 6 bytes           | 2 bytes         | 46 to 1500 bytes | 4 bytes                             |

|----------|--------|------------------------|-------------------|-----------------|------------------|-------------------------------------|

| Preamble | SFD    | Destination<br>Address | Source<br>Address | Type/<br>Length | Data             | Frame<br>Check<br>Sequence<br>(CRC) |

Picture 2.3 Ethernet frame. Adopted from [10][7].

The frame starts with a preamble, with 7 bytes of concurrent one and zero bits (10101010). In old 10 Mb/s systems, this was used to detect the start of frame and synchronize for receiving the frame at the PHY. In never systems constant signaling is used and detection of frame start is done with other means, but preamble is still kept to keep the frame structure intact [10]. Preamble stops with start frame delimiter (SFD), setting last two bits as ones (10101011) to detect frame starts. The actual frame starts right after SFD byte, having 6-byte destination and source MAC addresses at the beginning. Every Ethernet device has individual MAC address, which can be used to target a frame to a specific device. Type/length field is used to either specify the length of the frame or contain a MAC client protocol indication. If value is 1536 or above, field is interpreted as Ethertype. Values of 1500 and below is assumed to contain frame size in bytes instead. Some fundamental EtherType values are represented in Table 2.

**Table 2** EtherType examples

| EtherType | Protocol                                                |

|-----------|---------------------------------------------------------|

| 0x0800    | Internet Protocol version 4 (IPv4)                      |

| 0x0806    | Address Resolution Protocol (ARP)                       |

| 0x86DD    | Internet Protocol version 6 (IPv6)                      |

| 0x88F7    | Precision Time Protocol (PTP) over Ethernet (IEEE 1588) |

| 0x892F    | High-availability Seamless Redundancy (HSR)             |

One Ethernet frame can contain a maximum of 1500 bytes of data payload and a minimum of 46 bytes. If a client wants to send less than 46 bytes of data through Ethernet, MAC layer needs to add padding to the payload so that at least 46 bytes of data will be sent. The frame is ended with 4 bytes long Frame Check Sequence (FCS), using a widely used error-detecting algorithm called Cyclic Redundancy Check (CRC). The 4 byte CRC value is computed as a function of the contents of MAC frame, from destination address to end of data, thus excluding the FCS itself. Transmission errors like single flipped bits can usually be noticed with frame check sequence algorithm [12].

The frame is ended when TX\_EN signal is set low. In practice, in 10 Mb/s systems the signal in Ethernet channels is put to idle and in faster systems, a specific end symbol is sent by PHY [10]. Special symbols are possible because a total of 5 bits are used to represent 4 actual data bits on Ethernet bus, giving room to symbols that have a specific meaning other than data bits. These specific meanings include the start of the stream, stop of the stream, transmit error, idle and sleep. Definitions of 5-bit encoding symbols can be found e.g. from Spurgeon [10].

IEEE Std 803.2 defines InterPacket Gap (IPG) in clause 4.2.3.2.2 [7]. It states that between every Ethernet frame a minimum duration of 96 bit times of inactivity is required.

# 2.1.4 Internet protocol v4 (IPv4) and User datagram protocol (UDP)

As the communication from a user PC to a test device is using User Datagram Protocol (UDP), it is beneficial to take a look briefly at this higher level protocol as well. UDP works on transport layer of the OSI model. Thus under UDP frame header, a network layer protocol from OSI model is needed as well. We will focus on Internet protocol v4 (IPv4) as it the most common and used in our device as well.

The UDP protocol is connectionless communication model, which exposes applications using it to some degree of unreliability of the frames. There is no guarantee that the frames sent will reach the destination through automatic re-transmission of lost frames and ordering of the frames might differ from the original. However, as a trade-off, we get a minimal and simple protocol with a wide support from readymade software libraries and simple usage.

Offsets Octet Octet Bit 14 15 DSCP 0 0 IHL ECN Total Length Flags Fragment Offset Identification 32 Time To Live Protocol Header Checksum 12 96 Source IP Address 16 128 Destination IP Address 20 160 Source Port Destination Port 192 Length Checksum Data User Datagram Protocol Internet protocol v4

**Table 3** IPv4 and UDP headers. Adopted from [12]

Table 3 shows Internet Protocol header containing a UDP frame as enclosed data. These will be then enclosed to the data field of the MAC frame presented in section 2.1.3. MAC frame type field is set to 0x0800 to define IPv4 as an enclosed protocol. Protocol field of IPv4 header contains number 0x11 (17) to identify UDP protocol respectively. IPv4 and UDP headers contain source and destination IP address and port field to identify correct device and application when sending and receiving data to and from device to device. Detailed information and description of header fields can be found e.g. from Tanenbaum & Wetherall [12].

### 2.1.5 Address Resolution Protocol (ARP)

IPv4 and UDP protocols cannot be used without implementing address resolution protocol as well. For UDP packet to reach successfully its destination it needs to know destinations MAC address, IP address and port number. Without these e.g. Windows machines doesn't approve sending a packet even if the user would know all of the needed addresses. Thus, if the control application is trying to send a control message to the test device, it will first send an ARP request if the test devices MAC address is unknown to it. However, ARP protocol is fairly straightforward and possible to be implemented in FPGA as well. If the source device needs to know the MAC address of another device having a specific IP address, it sends an ARP request broadcasted to all devices in the network. If another device in the network notices it owns the IP address, it will reply to the source device with another ARP frame with its own IP and MAC addresses filled in. [22]

| Offsets | Octet | 0                                             | 1                       |

|---------|-------|-----------------------------------------------|-------------------------|

| Octet   | Bit   | 0 1 2 3 4 5 6 7                               | 8 9 10 11 12 13 14 15   |

| 0       | 0     | Protocol type (PTYPE)                         |                         |

| 2       | 16    | Hardware address length                       | Protocol address length |

| 4       | 32    | Operation (OPER)                              |                         |

| 6       | 48    | Sender hardware address (SHA) (first 2 bytes) |                         |

| 8       | 64    | (next 2 bytes)                                |                         |

| 10      | 80    | (last 2 bytes)                                |                         |

| 12      | 96    | Sender protocol address (SPA) (first 2 bytes) |                         |

| 14      | 112   | (last 2 bytes)                                |                         |

| 16      | 128   | Target hardware address (THA) (first 2 bytes) |                         |

| 18      | 144   | (next 2 bytes)                                |                         |

| 20      | 160   | (last 2 bytes)                                |                         |

|         |       |                                               |                         |

Table 4. ARP frame [24]

#### 2.2 FPGA

176

192

22

24

FPGA can be thought as an application specific integrated circuit (ASIC), which application is to produce a hardware that can be programmed after manufacturing to realize the desired functionality. FPGA is composed of generic logic blocks in which combinatorial logic is programmable, as well as programmable interconnections to other logic blocks. Complex digital circuit can be created by combining these small configurable logic blocks (CLB) with programmable interconnections. To communicate with peripherals connected to the FPGA chip, there are I/O blocks as a third basic element.

Target protocol address (TPA) (first 2 bytes)

(last 2 bytes)

Picture 2.4 shows the relation between these elements.

Picture 2.4 Basic elements of FPGA [2]

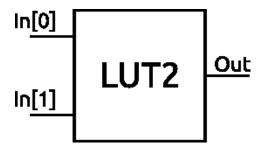

Logic blocks are main components of the FPGA and the choice between different FPGA chips is often based on the number of available logic blocks. The more the available logic blocks, the bigger and more complex functionality the FPGA chip can implement. The logic block can be thought to consist of series of flip-flops which will remember their previous state, as well as combinatorial logical operands like AND, OR, NAND, and XOR. However, in practice logic blocks don't contain actual combinatorial logic, but rather a small chunk of RAM memory which will implement a look-up table (LUT) [18]. As a simplified example, we'll take a look at 2-input LUT in Picture 2.5.

Picture 2.5 2-input LUT [3]

It is important to understand that because the LUT is implemented using RAM, the output can be set to any value. Thus, it can implement any logic gate, but also other things like shift-registers or RAM. As an example, Table 5 shows a 2-input LUT implementing an AND logic gate.

| Address (In([1:0]) | Value (Out) |

|--------------------|-------------|

| 00                 | 0           |

| 01                 | 0           |

| 10                 | 0           |

| 11                 | 1           |

**Table 5** 2-input LUT implementing AND gate

Needless to say, a real FPGA chip uses LUTs with n-inputs and one CLB contains several LUTs. Further, modern FPGA chip can contain millions of CLBs.

While CLBs handle the logic in FPGA, interconnection routes signals between CLBs and to and from I/O blocks. Routing comes in different types, including shorter and lower speed connections connecting CLBs together, as well as long horizontal and vertical lines spanning the chip. With long, global and high speed connections it is possible

to maintain low-skew in clock signals throughout the whole chip and ensure global signals passing data from one end of the chip to other within a clock cycle.

Additionally, to these three basic elements of routing, logic blocks and I/O blocks, FPGA chips usually consist a defined number of fixed components, providing often used functionalities like arithmetic operations and memory circuits. With the usage of these highly optimized fixed blocks scattered throughout FPGA chip, it is possible to reduce the size of the system design and optimize performance. An FPGA synthesis tool often handles optimizing the logic placement so that these functions are taken into use the optimal way, but might need some additional information so that for example array of bit vector is can be utilized as memory. FPGA vendors provide also ready-made FPGA blocks to be used for often used but complex functionalities like memory controllers, digital signal processing blocks or data bus implementations to use as a part of the design.

By using these sets of components it is possible to construct bigger entities, finally forming a final circuit. By connecting the created circuit to another component through I/O blocks to for example external memories, peripherals or general purpose microcontrollers, the FPGA design can act not as a separate system, but as a part of a bigger system on a chip. In modern technology industry, it is common to use an FPGA chip with a multipurpose microcontroller, FPGA handling time-critical parts of the functionality while microcontroller handles the generic part of software [2]. FPGA vendors offer also ready-made soft processors running on FPGA itself, offering same generic software possibilities without a separate microcontroller.

Generally speaking, using FPGA chips instead of ASIC designs is beneficial when production amounts are small, time-to-market is wanted to be kept low, the product is not needed to be optimized for size or power consumption or updatability or bug fixing is required after putting the product on market. Designing cost of ASIC is often multiplications of those on FPGA designs, but on the other hand manufacturing costs with ASIC are usually smaller at least with big quantities. General purpose processors, on the other hand, can offer many similar features than FPGA with lower cost, but in areas that require concurrent execution, these two aren't even competitors. [1]

### 2.2.1 Hardware description language

Cost benefits of the FPGA design derive from a used process in developing a device. Logics and functionality of a designed chip are described using hardware description language (HDL), which has many similarities with traditional general-purpose programming languages. It uses similar kind of imperative and procedural structures as many other programming languages, thus implemented system doesn't need to be designed in logic port level but abstracted to a level of normal e.g. mathematical expressions and conditional statements. There are two major hardware description languages,

VHDL and Verilog. We will concentrate on Very High Speed Integrated Circuit Hardware Description Language, which is shortened to VHDL for obvious reasons. It is standardized as IEEE 1076. A practical introduction to the language offers, for instance, Kafig in [19], while a thorough discussion of all aspects can be found in "The Designer's Guide to VHDL" [20] by Ashenden.

### 2.2.2 Clocking and metastability

Probably the biggest difference between traditional software programming languages and hardware description languages is transparency for clock signals. Most of the functionalities done with hardware description languages have to be synchronized with clock signal edges, thus needing a slightly different mindset compared to programming a multipurpose processor. This is mandatory as with HDL we are designing a digital circuit instead of software and processing in the components happens synchronously with a clock in the FPGA.

Synchronization with clock signals can rise problems unknown to a programmer used to develop software to general purpose processors. One of the most problematic situations can occur when working in multiple clock design and passing signals and data from clock domain to another. If done wrong, this can cause random error situations hard to debug and locate.

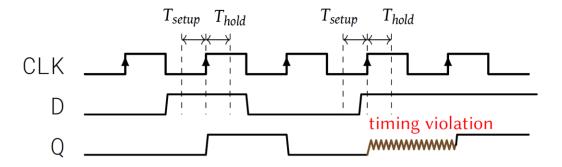

A root cause of the problem is named metastability, a physical phenomenon found in digital devices. For example, a D-type flip-flop samples its data at every rising clock edge. For the data sampling to be successful, flip-flop needs data to be stable for some time before and after the clock edge. The time before clock edge is commonly called setup time T<sub>setup</sub> and time after clock edge is hold time T<sub>hold</sub> [14]. If these timings are violated, the flip-flop may enter a metastable state and the output of the flip-flop will be undefined. Output can stay between valid 0 or 1 states or oscillate between those values [14]. Picture 2.6 shows an example of the metastability state in flip-flops output Q issued by timing violation in input D.

**Picture 2.6** Metastability in flip-flops output Q

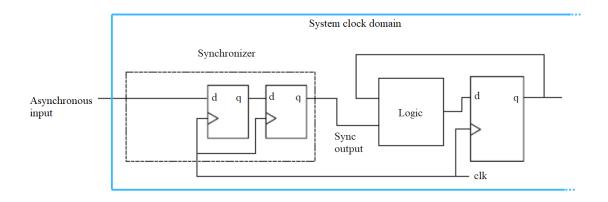

When another component is then using the output of a flip-flop in a metastable state, it can interpret the (voltage) value either logical 0 or 1, resulting in possible undefined errors in the system [14]. In theory metastable state can continue indefinitely, but in practice, it has been noticed that the probability of a component stabilizing its state increases exponentially over time. If there is not known phase difference between the clocks from where and to signals are to be synchronized, it is not possible to make fail proof implementation of a signal synchronizer. As Kleeman et al. stated: "it is generally accepted that a perfect synchronizer cannot be physically realized." [23]. Because the system cannot be made totally free from metastability issues, it should be made as metastability tolerant as possible [15]. For this purpose, commonly used technique is to use synchronizers when passing signals from clock domain to another. The purpose of the synchronizers is to synchronize asynchronous signal to system clock by just providing enough time for the metastable condition to be resolved before using it in the system [15]. Most commonly used synchronizer is two-FF synchronizer, shown in Picture 2.7

Picture 2.7 Two-FF synchronizer [15]

Using two-FF designs are enough in most cases, but in the second flip-flop can get the metastable state as well even though the probability is very small. Adding more chained

flip-flops to the synchronizer increases mean time between failure (MTBF) rate, but also increases delay even further from two clock cycles of two-FF design.

The two-FF synchronizer is usable only for single bit synchronization because concurrent synchronizers cannot guarantee to deliver separate bits at the same time to the following logic. For data other means of synchronization is required. One of the simplest methods is to let the data be asynchronous, but synchronize only "data valid" bit from clock to another. When this control signal is synchronized, it can be assumed that the data is stabilized as well due to the synchronization delay time. However, when multiple adjacent data chunks are needed to be transferred at a maximum throughput in an asynchronous environment, some kind of acknowledgement signal is needed to be synchronized from data receiver to sender as well to tell a data chunk read is completed. This is forming a so-called hand shaking protocol [15]. To maximize data throughput further, a first-in-first-out (FIFO) buffer can be used. In FIFO design writer can push data to the buffer without waiting for every separate acknowledgement from the reader if there is available space in the FIFO. Addresses of the FIFO can then be synchronized by using "grey code" method where only a single bit of the address changes at a time. Using these methods it is possible to create an asynchronous FIFO for data transferring with separate write and read side clocking. A full and empty signal, as well as approximation of data amount in the FIFO, is possible to be implemented as well for flow control purposes.

Implementing such behavior can get rather complicated. However, FPGA vendors usually provide readymade solutions for generating asynchronous FIFOs in user design for free of charge. If used clock speeds on both sides of the FIFO are same, reading can be done at full clock frequency after an initial waiting time for first data chunk. A usable feature for FIFOs is also first-word fall-through (FWFT), which makes the first chunk of data to be usable in the following logic before explicitly reading the data out from the buffer first. For next data to be seen in the output an acknowledgement for the first one is needed to be given.

### 2.2.3 Implementation process and simulation of FPGA

Even though designing systems for FPGA still brings up these challenges from logic gate level, it is also clear that with HDL implementing systems has become easier not only with ease of design but also from a verification point of view. For VHDL codes it is possible to use e.g. peer-review methods in the code level itself. For VHDL code to be used in the FPGA, it is first needed to be synthesized, a term relative to compilation in terms of traditional programming languages. The synthetization also gives errors and warnings regarding syntax errors in the VHDL codes.

Before loading the design to FPGA, the design can be simulated first. Simulator mimics the functionality of the FPGA device and can give a visual representation of digital sig-

nal states of the device in function of time. By investigating the internal digital signal state of a function block under consideration, the developer can spot possible logical errors from the design without debugging the design in actual hardware. Simulation usually requires at least one test bench, which is defining external inputs and outputs states for the testable system. This means, for example, defining external clock and reset signals and peripheral input states in regards to the clock states. Often it is also common to define separate test benches for different function blocks of the design and checking outputs of the system with a function of inputs to automatically check passing or failing of a test case. This can be compared to unit testing in general software programming. Test benches can be run after changing the implementation to check that nothing has been broken between the development steps. As with unit testing, it is often beneficial to write the test benches even before the actual functionality.

It should be noted still that the simulation environment gives an ideal representation of a logical behavioral model of the device and doesn't necessarily expose all errors found in the real device. One good example of this is the metastability issue discussed in section 2.2.2. Also, even though testing in the simulation is run successfully, it is possible that the actual implementation of FPGA logic placement and routing fails. This can happen for example because the routing tool cannot implement clock routing that can meet timing requirements of the design or just by running out of LUT components of the FPGA chip, just to name a few. However, if the routing and placement are successful, the compilation tool gives a report for example of used resources of the FPGA chip and clocking characteristics. As a final output, the synthetization tool gives an FPGA placement and routing description file which contains information how to use registers, LUTs and connecting wiring in the FPGA chip. FPGA chip is programmed using this description file to construct FPGAs logic cells and interconnect wirings in right order to achieve designed hardware system.

### 3. PRODUCT OVERVIEW

### 3.1 Development environment

The primary customer for the project is a major industry company. Their main products are controlled with automation system containing embedded devices. One of the main requirements for the project was to use one of these devices designed originally for control automation purposes, but still containing all needed components for the Ethernet tester device as well. All it needed was a complete FPGA redesign and implementation. There was also already available a method to update FPGA chip with new FPGA configuration binary, which helped slightly to get first versions of the tester up and running. At the beginning of the project, it was also found out that it was even more beneficial to use older prototypes of the automation device, which were unusable for the original use but still totally fine for tester purpose.

The automation device has following technical details:

- FPGA chip, Xilinx XC6SLX150 [21]

- Spartan-6 Series

- o 184304 slice registers

- o 92152 slice LUTs

- o 4824 Kb RAM blocks

- o 180 DSP48A1 slices, each containing 18 x 18 multiplier, an adder, and an accumulator

- DDR2 memory, Micron Technology Inc. MT47H128M16RT-25E AAT

- o Size 2 Gb

- o Width x16

- o Clock rate 400 MHz

- 4 x Ethernet PHY, Texas Instruments DP83848T

- o Fast Ethernet 10/100 Mb/s

- o MII interface

The device has lots of other features as well like separate microcontroller and different kinds of I/Os, but those are not used in this project and thus not needed to go through here.

FPGA development was done with Xilinx ISE design software. There is also a newer version of FPGA development environment available from Xilinx, called Vivado Design Suite, but it does not support Spartan-6 series devices and thus cannot be used here.

FPGA simulation was done with ISim HDL simulator, which was installed together with Xilinx ISE. During the development ISim had serious stability issues so, for example, ModelSim might have been better for the purpose. The actual VHDL coding was done with XEmacs text editor even though Xilinx provides an editor with ISE as well. XEmacs was selected because its wide VHDL support giving fundamental features like automatic indentation, color coding, and auto-complete, just to name a few.

A PC tool for controlling the test device was implemented with Qt and C++. Qt is a fairly popular cross-platform application framework, which also includes easy to use UDP packet sending and receiving libraries as well as providing GUI designer with a reasonable learning curve. Qt and C++ are also widely used in the customer's other projects and was the clear choice for that reason as well.

### 3.2 Usage overview

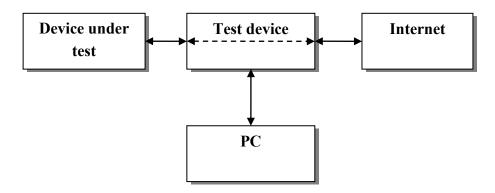

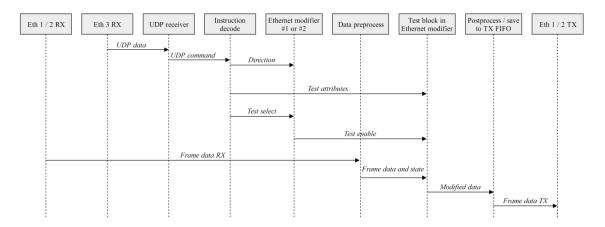

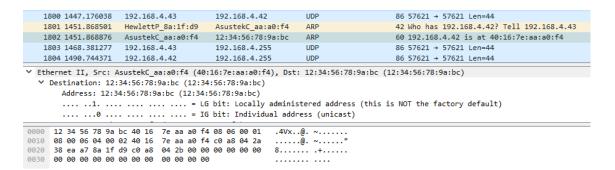

The test device is supposed to be connected between the two devices communicating using Ethernet. The device itself has four Ethernet ports providing TX- and TX+ pins and RX- and RX+ pins. Of course, commonly used RJ-45 connector can be connected to the pins with custom made cabling for easy connectivity to existing systems. Two of the Ethernet ports are connected to PC and are used to monitor Ethernet frames from tested communication line receive and transfer end of the test device. This means that frames are duplicated and rerouted on the fly to monitoring PC even though it might not be part of the tested local area network (LAN) itself. One of the Ethernet ports going to PC is also used to send control and command frames to the test device for user interaction.

Picture 3.1 Test device connections

Picture 3.1 shows used connections for the test device. Received frames from RX1 or RX2 are transmitted from ports TX2 or TX1 respectively. Additionally for monitoring purposes, based on user selection of modifying/monitoring direction, received frames are rerouted to TX4 from either RX1 or RX2 port. Respectively outgoing frames from either TX1 or TX2 are rerouted to TX3. RX3 port is used to send control and command frames to the test device.

When the test device is started, it is first needed to set MAC and IP addresses for the device. Otherwise, it couldn't respond to ARP requests sent by control PC and direct communication between those two couldn't be established. Control PC is able to select MAC and IP addresses for the test device and send those to the test device using Ethernet broadcast MAC and IP addresses. By defining a frame identifier to used communication protocol it is possible to distinguish address setting frame from other broadcasted frames. Communication protocol will be defined in more detail in chapter 4.1.

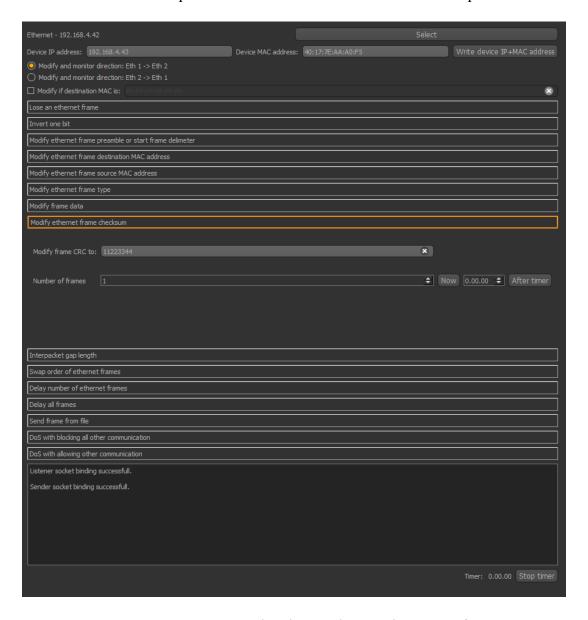

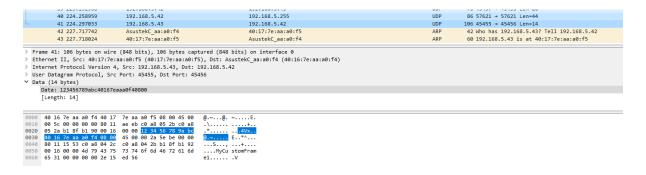

Picture 3.2 Command and control PC tool user interface

Picture 3.2 shows the user interface for controlling the test device from PC. First, the user selects Ethernet interface connected to test devices Ethernet port 3. Device IP address is filled automatically to adjacent address from selected interface IP address, but it can be modified freely if needed. A test MAC address is filled in by default, but it can be modified also in cases of possible address collisions. After initialization of addresses, the device is ready to be used. The following chapter will define features available in the test device.

#### 3.3 Tests and features

Testing an Ethernet frame consist tests that are focused on the physical and data link layers on the OSI stack. In theory, most of the modified packets should be blocked already on physical or data link layers by receiving hardware, if frame check sequence is not modified at the same time when modifying frame data bits. Thus, if hardware handling the communication is working correctly modified packets within the tests should not stress CPU, but rather drop the frames before reaching upper layers in the OSI stack. In many cases, an operating system or application receiving the packets will request retransmission in case a missing packet is noticed. Also, the sender can notice missing acknowledgement from the receiver and send again individually. However, there are many ways to handle modified packets and the purpose of these tests is to check that participants handling the communication recover reasonably from unexpected error situation.

Many of the errors simulated by the tests are usually not possible to happen when communicating software parts are functioning normally and correctly. However, often it is not enough to assume tested software gets only valid data, but it is also feasible to test the software from other security aspects, like man-in-the-middle (MITM) attack or misbehaving transmitter software. In MITM attack a malicious third party takes control of the communication channel and can eavesdrop and modify victims' communication traffic [17]. This is why tests include also functionalities like changing the address on the fly and manipulating FCS to match with modified data.

Several tests that are not actually physical or data layer related, but still tightly connected to Ethernet communication is also implemented. These tests simulate possible real life scenarios that might cause unexpected behavior in receiving end device. These tests modify mostly entire frames instead of individual bytes or bits in the frames.

Lastly, some general testing and debugging tools are also implemented within the device. These are introduced to help in the development and debugging of new network devices by providing a view on ongoing frames and injecting user defined frames to the communication line.

Some features are not tests itself, but rather support the tests to provide more possibilities in the testing process. These features are listed below.

- 1. The direction of the modified packets can be altered. This means that user can select if incoming or outgoing packets from the testable device will be modified. This can provide more useful if there is a network with two or more testable devices and the testing device is placed in between of the communication media. This feature is available for all tests as well as monitoring.

- 2. A user can set a timer to trigger a test after a defined time has elapsed. This feature is available for all tests.

- 3. Frame check sequence (CRC) can be modified also to match new data bytes in a modified frame. This way also the modified frames get through cyclic redundancy check, which is often done already in hardware level and possibly to the application under testing. This is available for most of the tests that are modifying data bytes in the frames.

- 4. The user can set the test to only take place for frames sent to a defined destination MAC address. This will help to target only specified test subject device especially when test area consists more than one devices. This is available for many of the tests, where implementation was possible without big sacrifices in terms of code complexity (from development time perspective) and delaying test frames. This feature will be called conditional frame modifying in the next chapters.

- 5. The user can modify a defined amount of consecutive frames with one modifying test command. All consecutive frames are modified with the same manner described by the test.

- 6. The direction of modified packets can be changed on the fly. This means that if Ethernet frames coming from device A are modified when going to device B, when the direction is changed, frames coming from device B to device A is modified instead.

- 7. All transmitted frames from the test device are also transmitted from the Ethernet port used for controlling the device additional Ethernet port to the user PC for monitoring purposes. Additional fourth Ethernet port is used to send all Ethernet frames that are seen on receiving port of modified direction. These are especially useful to see the contents send on communication media with an external test computer with an appropriate monitoring application like Wireshark.

- 8. Advanced monitoring feature sends monitored frames encapsulated to UDP frame to allow seeing also broken frames in user PC. If UDP frames sent to valid MAC, IP and port combination, broken frames can be received in a listening socket on user PC without interruptions from e.g. frame checksum check in lower layers.

- 9. IP and MAC addresses of the control port of the test device can be modified.

In next chapters, all currently available tests are described in detail. If some of the supportive features are not available for a specific test, it is explained why it is left out.

### 3.3.1 Preamble and start frame delimiter (physical layer)

The user can modify next incoming Ethernet frame to consist selected amount of preamble nibbles (half a byte, 4 bits). The user can also select if start frame delimiter byte is sent or not with the next incoming frame.

The preamble is used for Ethernet physical layer hardware to detect incoming frame and synchronize receive data with receive clock. Amount of preamble bytes can be selected between a range of 0 - 38 nibbles. The amount is handled as nibbles to increase resolution, but also because fast Ethernet physical layer hands data over in 4 bit chunks, thus making the implementation slightly easier.

The conditional frame modifying is not supported by this test. The reason is that the preamble that is supposed to be modified, comes before destination address. Thus implementation would require buffering of data, which also means delaying of the frame. Implementation of conditional frame modifying feature could be done, but it was decided to be left out to avoid delaying of the frame.

### 3.3.2 Destination address (data link layer)

The user can modify destination MAC address of a next incoming frame to a user given 6 byte hexadecimal value. This can be used to test for example what happens when an Ethernet frame meant to be sent to device A is sent to other device B, because of a software bug or a man-in-the-middle attack. In theory physical and data layers should discard the frame before reaching upper layers to stress CPU of the testable device. When testing, it can be beneficial to turn on automatic frame check sequence correction to make sure frame is not discarded because of invalid CRC bytes.

Contrary to the preamble and start frame delimiter test, conditional frame modifying is supported here even though it does require buffering and delaying of the frame. Buffering is mandatory because destination address has to be first checked for a possible match before actually modifying the data. Amount of delaying buffering space is defined based on need, which is currently at a maximum of six bytes.

### 3.3.3 Source address (data link layer)

The user can modify source MAC address of a next incoming frame to a user given 6 byte hexadecimal value. Depending on the application that the frame is used for, this might or might not have an impact on testable device behavior.

### 3.3.4 EtherType and length (data link layer)

The user can modify EtherType or length field. Check behavior when unknown/unsupported Ethernet frame type is sent.

When used as EtherType, the length of the frame is determined by other means. Modern Ethernet PHYs uses special symbols to signal frame start and stop, but size can be also calculated based on the location of the SFD byte and InterPacket Gap. Length can be also defined in upper layers, but physical or data link layers will not handle those bytes. Thus, it is fairly possible that no frames will be discarded based on type/length field if frame check sequence is corrected.

### 3.3.5 Payload modifying (data link layer)

Modifying payload is done by giving an offset from payload start to bytes that will be modified, a number of bytes to replace with given data and the data actual data bytes. A maximum number of data bytes is restricted to 6 mainly to save logic gates in FPGA due to the handling of the data. Data amount could be easily expanded if there are free logic gates to use.

### 3.3.6 Frame check sequence (data link layer)

Modify frame check sequence value. The receiver will probably discard the frame due to invalid CRC if frame check sequence handling is implemented correctly at the testable device. Because correct place of FCS bytes will be known only after frame stop has been detected, 4 bytes will have to be buffered from the modified frame. When frame end is detected, buffered bytes will be swapped to user selected ones.

### 3.3.7 InterPacket Gap length

Modify InterPacket Gap (IPG) length. According to IEEE 802.3 standard, Ethernet devices should allow minimum idle time of 96 bit times. Bit time is a time respective to sending one bit on the medium. For 100 Mbit/s Fast Ethernet, this means the idle time of minimum  $0.96~\mu s$ .

However, due to nature of the test, some restrictions have to be defined when modifying InterPacket Gap. To make the gap according to user defined length, data should be available for two consecutive frames. Normally cannot happen if gap length is shortened below minimum stated length in the standard and even with longer gap times would require incoming frames at close to maximum bandwidth throughput. To make the feature reliable, the previous frame have to be buffered to memory. When the second frame receiving starts, the first frame is started to be read from memory while the second is written to memory. After complete send of the first frame, the second

frame is sent from memory as quickly as possible, allowing a gap of user specified time. However, there is still some minimum modified gap length time, restricted by delays introduced by reading the memory. The minimum gap length time could be made smaller with aggressive caching when reading the memory.

#### 3.3.8 Send a custom frame from a file

The user can define any custom Ethernet frame in a text file format, which will be sent from the testing device. The frame will be read from a file, encapsulated in a UDP packet and sent to the testing device through command Ethernet port. Frame check sequence is also calculated automatically and appended to a defined frame, so the user doesn't have to calculate it manually.

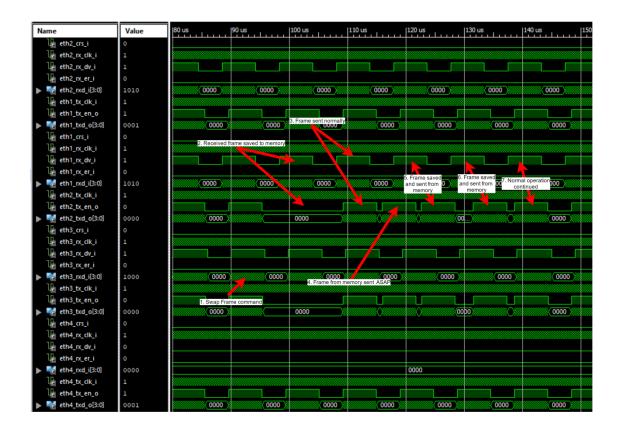

When custom Ethernet frame is received on the testing device, it will be saved straight to DDR memory. As soon as there is no ongoing receive towards the testable device, the custom frame will be read from memory to transmit Ethernet port and send to testable device. If any data is received during transmitting custom frame, it will be buffered to DDR memory instead. That is because the custom frame has to be sent completely before continuing normal operation. After the custom frame is sent, normal frames will be read from memory and ingoing frames will be buffered as well. This will be continued for so long that memory will be emptied from all data. Thus no frames will be lost from the communication media, but frames that should be forwarded at the same time with custom frame will be delayed by the amount of custom frame length.

The maximum length for the custom frame is restricted to largest commonly approved UDP data size of 512 bytes guaranteed to be sent without frame fragmentation. This is because currently UDP protocol handler implemented in test device does not support reconstructing of fragmented UDP packets.

#### 3.3.9 Runt frames

A runt frame is an Ethernet frame with less that 64 bytes of length, which is defined as minimum length in IEEE 802.3 standard [10]. This test can be achieved easily by using custom frame sending and defining custom frame in the file shorter than 64 octets.

### 3.3.10 Swap order of frames

With this test, the user can swap the order of two consecutive Ethernet frames going to the testable device. When the test is started, the first incoming frame is taken from communication media and saved to DDR memory. Next frame is then received and transmitted normally, after which frame that is saved to memory is sent, thus swapping frames order. It is also possible to set a number of frames that are saved to memory before normal frame transmit, thus more than one frame can be swapped with the one that

comes after those. Swapping frame also means that the frames that are saved to memory are delayed.

### 3.3.11 Delay selected number of frames

The user can delay a selected number of frames from communication media for a selected amount of time. After test started, a selected amount of frames are saved to memory and not transmitted yet. With the start of the first frame that is saved to memory, also a timer is started. After the selected amount of frames are saved to memory, all incoming frames are transmitted normally to the testable device. When the timer has elapsed, saved frames are read and sent from memory in the order those arrived at the test device. Any incoming frames are buffered to memory while saved frames are sent to avoid losing any frames from communication media. The maximum amount of frames are set to 255 to fit the amount in 8 bits. Delay time is given in milliseconds and longest time is set to 65535 milliseconds, to fit the delay time in 16 bits. Amount limitations come from FPGA bus width, which requires setting some limit to the used byte amount. However, there is plenty of room to increase it if needed.

### 3.3.12 Delay all frames

This test is same than delaying a selected number of frames, but instead of giving a number of frames, all data is delayed for given amount of time. This means that there will be no incoming frames to a testable device for given amount of time, but after that, all data that were supposed to come during that time will be transmitted to a testable device with maximum speed allowed by available bandwidth. All frames are saved to memory during the time period and while reading the saved memory, all incoming frames are also buffered to memory to be sent in incoming order. This means that emptying the memory might take quite some time, at least if bandwidth usage is close to maximum with normal communication as well. Delay time is given in milliseconds and longest time is set to 65535 milliseconds, to fit the delay time in 16 bits.

### 3.3.13 DoS with blocking all communication

The user can simulate Denial of Service (DoS) attack, where one valid Ethernet frame is multiplied to a test device transmit port with maximum bandwidth throughput and send to testable device. This test uses a custom frame from file functionality, so the user can define the frame that will be flooded to the testable device. The user can also set attack length in milliseconds, maximum being 65535 milliseconds. With DoS attack simulation blocking all other communication, all other frames that would come through test device receive to transmit port is lost, so only user defined frames are received in the testable device when the test is ongoing.

### 3.3.14 DoS with allowing all communication

This test simulates DoS attack by sending one custom frame with maximum bandwidth throughput but allows also normal communication frames to the testable device through. Basically, this means that whenever there is an idle time in communication media (apart from InterPacket Gap) custom frames are sent. If any normal communication frames are received during transmission of a custom frame, it will be buffered to memory, allowing the custom frame to be sent completely first.

### 3.3.15 Drop frames

With this test, it is possible to drop one or more frames from communication media completely. The user simply sets a number of frames that will be lost, and when the test is started, a defined number of frames are not routed from the test device receive port to transmit port.

### 3.3.16 Invert single bit from frame

The test simulates external transmission failures that might happen due to bad cables or external interference to the communication media. Test inverts one user defined bit from a frame. The user can define which bit will be inverted, giving an offset bit count from either frame start, source address start, type start, or data start. Automatic checksum fixing is not available for this test as the purpose is to simulate normal transmission errors.

# 4. DESIGN

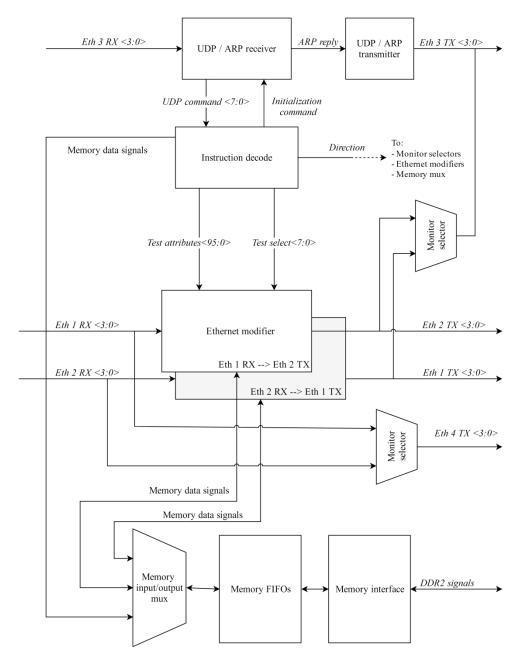

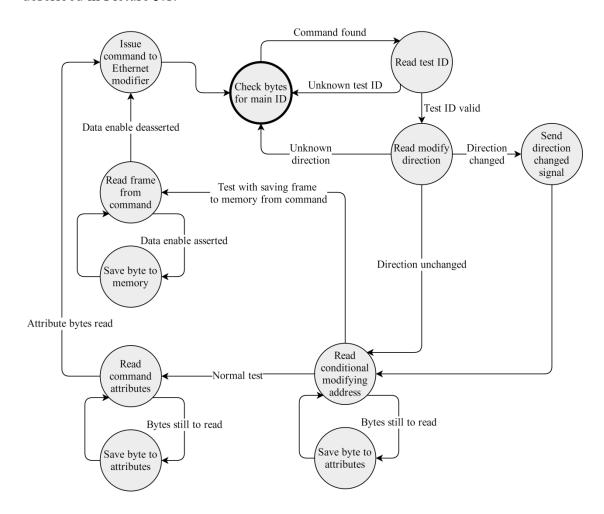

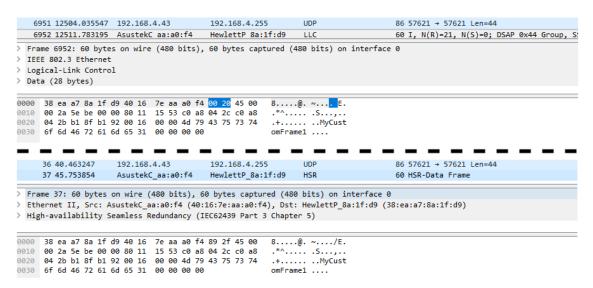

As with other software development projects, designing good software architecture for the system is often even more crucial than the actual implementation in FPGA projects. Bad architecture and design in FPGA development process increase complexity, decreases maintainability and updatability and possibly takes more resources. Picture 4.1 shows high level architecture design of the implemented Ethernet tester.

Picture 4.1 Architecture of Ethernet tester

Ethernet modifier Test select <7:0> Test attributes <95:0> Test Eth RX Eth TX Data TX double Test selector Postprocess preprocess FIFO implementations muxes Memory read. write

More detailed view from Ethernet modifier block is shown in Picture 4.2

Picture 4.2 Ethernet modifier block architecture

One of the core requirements for the project was to be easily updateable with new tests and features. To add a new test to the system, one must add implementation in three places:

- 1. Add command parsing, detection, and control for the new test in instruction decode block.

- 2. Implement the actual test in a new VHDL code block. Most of inputs and outputs of the new test will probably have the same format as other existing tests, so existing ones can be used as a template.

- 3. Route inputs and outputs for the new test correctly using multiplexing functionality based on a command input from instruction decode block.

Functionalities around tests are purposely kept as generic as possible so that those can be used with new tests without much effort. As there are already a relatively big set of tests available, new tests can be implemented without going into too many details for the whole system, but just copying existing tests and modifying from there. Multiplexing functionality also helps to feed data to correct places with only adding new enumerated IDs to control signals of the multiplexers.