# Farid Shamani DESIGN OF A FLEXIBLE TIMING SYNCHRONIZATION SCHEME FOR COGNITIVE RADIO APPLICATIONS

Master of Science Thesis

Examiners: Prof. Jari Nurmi

Dr. Roberto Airoldi

Examiners and topic approved by the

Faculty Council of the Faculty of

Computing and Electrical Engineering

on 9 October 2013.

#### **ABSTRACT**

TAMPERE UNIVERSITY OF TECHNOLOGY

Master's Degree Programme in Information Technology

SHAMANI, FARID: DESIGN OF A FLEXIBLE TIMING SYNCHRONIZA-TION SCHEME FOR COGNITIVE RADIO APPLICATIONS

Master of Science Thesis, 75 Pages

November 2013

Major: Digital and Computer Electronics

Examiners: Prof. Jari Nurmi Dr. Roberto Airoldi

Keywords: Software Defined Radio, Cognitive Radio, Synchronization, Flexible Timing

Synchronization, FIR Filters, Partial Reconfiguration

Advancements in wireless technology have increased different applications to demand higher data rate wireless access. Spectrum scarcity has come more into picture day by day. In this case, Cognitive Radios (CR)s are new emerged promising technology which are an alternative solution to use spectrum more efficiently. In concept, CR is defined as an intelligent wireless device which is always alerted about its environment by continuously sensing the spectrum as well as having the ability to dynamically adopt its radio parameters. Although, CRs can mitigate spectrum scarcity to some extent, a variety of challenges have emerged of which synchronization is one the most prominent.

This thesis first presents some of common synchronization techniques used in conventional receivers and, based on them, presents a flexible timing synchronization scheme in which the CR receivers are able to adopt their radio parameters with new information regarding to the spectrum.

The core content of the synchronizer is based on Finite Impulse Response (FIR) filter which performs as a multicorrelator on demand. To do so, different synchronization architectures have been applied to the design, including Multiplier-Less based correlator as well as Transposed, Sequential and Pipelined Direct Form FIR filters. Consequently, all the architectures are compared to each other in terms of power consumption, chip area, maximum frequency, etc. Compiled results show that the best strategy is to employ Multiplier-Less based multicorrelator as the fundamental functional unit of the synchronizer.

The aforementioned synchronization block is implemented on an Altera family FPGA board series Stratix-V. All the components are written in VHDL language and simulated through ModelSim software. Quartus-II version 12.1 environment is used to compile simulated codes.

#### **PREFACE**

This thesis is done as a completion of the Master of Science degree in department of Electronics and Communications Engineering at Tampere University of Technology.

I would like to give my sincere gratitude to Professor Jari Nurmi for the given opportunity; who made it possible for me to do my research work beyond his support. I would like to express my deep appreciations to Dr. Roberto Airoldi for all his precious and friendly support and advices which led to accomplish this thesis. Many many thanks to Jari Nurmi's team, specially Tapani Ahonen, Waqar Hussain and Leyla Ghazanfari for their supportive cooperations.

I would like to express all my deepest acknowledgments to my family Masoud, Ada, Saeed, Sepide, Saghar and specially my Mother. Who I am today and whatever I have achieved, it is just because of them. Without their non-stop support, nothing would have been possible.

I would like to extend my appreciation to all my friends at Tampere University of Technology in particular Orod Raeesi, Kamiar Radnosrati, Saeed Afrasiabi, Nader Daneshgar, Mona Aghababaee for their warm friendship and nice moments we have shared together. The warmest gratitudes to Vida Fakour Sevom for being right beside me and never let me down in all ups and downs.

Finally, I am grateful again to my brother Saeed and my sister Ada for their unutterable support. Special thanks to my sister-in-law Shide for every little things she has already done for me.

Tampere, November, 2013 Farid Shamani

# **CONTENTS**

| 1. | Introduc | etion                                                          | 1  |

|----|----------|----------------------------------------------------------------|----|

|    | 1.1 Mc   | otivation                                                      | 1  |

|    | 1.2 Th   | esis Outline                                                   | 2  |

| 2. | Wireless | Communication Systems                                          | 3  |

|    | 2.1 Sin  | gle-Carrier Modulation                                         | 3  |

|    | 2.2 Mu   | ultiple Access Methods                                         | 4  |

|    | 2.2.1    | Frequency Division Multiple Access (FDMA)                      | 4  |

|    | 2.2.2    | Time Division Multiple Access (TDMA)                           | 5  |

|    | 2.2.3    | Code Division Multiple Access (CDMA)                           | 7  |

|    | 2.3 Mu   | ulti-Carrier Modulations                                       | 8  |

|    | 2.3.1    | Orthogonal Frequency Division Multiplexing (OFDM)              | 8  |

|    | 2.3.2    | Non-Contiguous Orthogonal Frequency Division Multiplexing (NC- |    |

|    |          | OFDM)                                                          | 13 |

|    | 2.4 Int  | roduction to Cognitive Radio (CR)                              |    |

|    | 2.4.1    | What is Software Defined Radio (SDR)                           | 16 |

|    | 2.4.2    | What is Cognitive Radio (CR)                                   | 17 |

|    | 2.4.3    | Evolution of Radio Technology                                  | 17 |

|    | 2.4.4    | Dynamic Spectrum Access (DSA)                                  | 18 |

| 3. | Synchro  | nization                                                       | 21 |

|    | 3.1 Eff  | ects of Poor Synchronization                                   | 21 |

|    | 3.2 Syı  | nchronization Errors                                           | 22 |

|    | 3.3 OF   | DM Synchronization Issues                                      | 23 |

|    | 3.3.1    | Synchronization Methods                                        | 25 |

|    | 3.3.2    | Overview of 802.11a Packet Structure                           | 30 |

|    | 3.4 OF   | DM Synchronization Steps                                       | 32 |

|    | 3.4.1    | Coarse Symbol Timing Detection                                 | 32 |

|    | 3.4.2    | Fine Symbol Timing Detection                                   | 35 |

|    | 3.5 NC   | C-OFDM Systems                                                 | 37 |

|    | 3.5.1    | NC-OFDM synchronization issues                                 | 38 |

|    | 3.5.2    | Primary User Filter                                            | 42 |

|    | 3.5.3    | NC-OFDM Synchronization Steps                                  | 42 |

| 4. | State of | Art in Synchronizer Architecture                               | 45 |

| 5. | FPGA I   | mplementation of Multicorrelator                               | 49 |

|    | 5.1 Des  | sign Implementation Issues                                     | 49 |

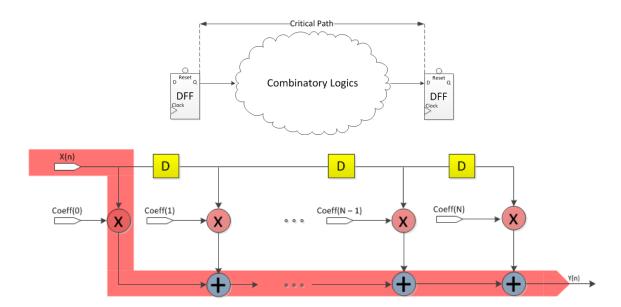

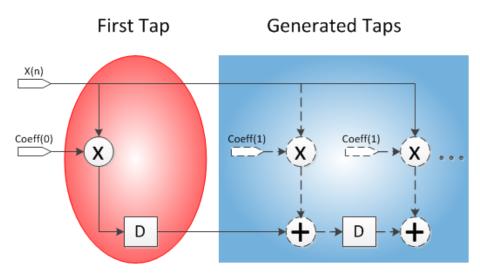

|    | 5.2 FII  | R Filter                                                       | 49 |

|    | 5.2.1    | Sequential Direct Form FIR Filter Architecture                 | 51 |

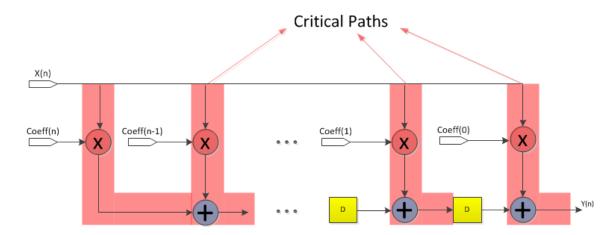

|    | 5.2.2    | Transposed FIR Filter Architecture                             | 53 |

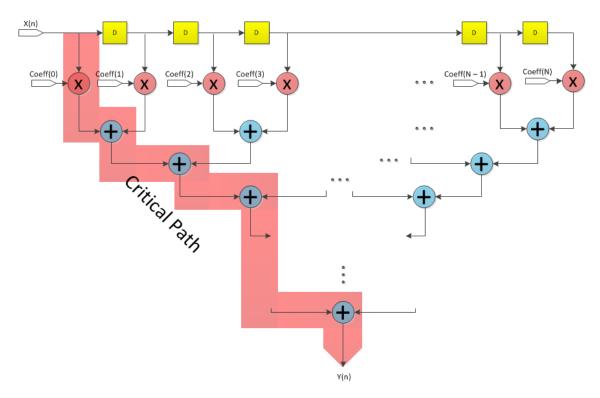

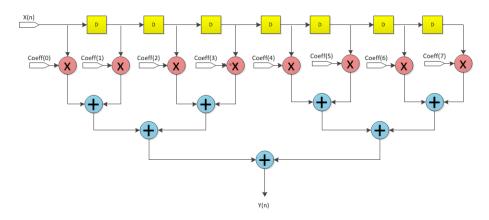

| 5.2.3      | Parallel FIR Filter Architecture         | 54 |

|------------|------------------------------------------|----|

| 5.3 De     | esign Implementations                    | 56 |

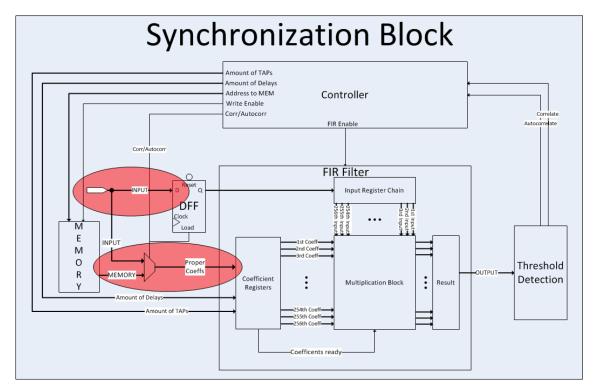

| 5.3.1      | Input Classifications                    | 57 |

| 5.3.2      | Memory Block                             | 58 |

| 5.3.3      | Threshold Detection Block                | 59 |

| 5.3.4      | Controller Block                         | 59 |

| 5.3.5      | FIR Filter Core                          | 59 |

| 5.4 Co     | ompilation Results                       | 63 |

| 5.5 Pa     | rtial Reconfiguration                    | 63 |

| 5.5.1      | Partitioning for Partial Reconfiguration | 64 |

| 5.5.2      | Wrapper Logic                            | 65 |

| 5.5.3      | Freeze Logic                             | 66 |

| 5.5.4      | Partial Reconfiguration Host             | 66 |

| 6. Conclus | ${f sions}$                              | 69 |

| References |                                          | 71 |

# LIST OF FIGURES

| 2.1  | Basic Single-Carrier Modulation Methods [9]                               |

|------|---------------------------------------------------------------------------|

| 2.2  | Principles of Frequency Devision Multiple Access                          |

| 2.3  | Principles of Time Devision Multiple Access                               |

| 2.4  | Principles of Code Division Multiple Access                               |

| 2.5  | (a)Conventional non-overlapping multi-carrier modulation. (b)Overlapping  |

|      | multi-carrier modulation. [6, p.26]                                       |

| 2.6  | Comparison between (a) single-carrier FSK modulation and (b) multi-       |

|      | carrier OFDM modulation                                                   |

| 2.7  | OFDM transceiver architecture [4, p. 38]                                  |

| 2.8  | Inter-Carrier Interference due to frequency offset [7, p. 432] 11         |

| 2.9  | Structure of an OFDM block with cyclic prefix                             |

| 2.10 | (a) Illustration of ISI due to multipath delay; (b) zero-padding guard    |

|      | interval to avoid lSI; (c) guard interval with cyclic prefix to eliminate |

|      | ISI and ICI [6, p. 28]                                                    |

| 2.11 | (a) OFDM and (b) NC-OFDM schemes                                          |

| 2.12 | NC-OFDM transceiver architecture                                          |

| 2.13 | CR and its relation to SDR                                                |

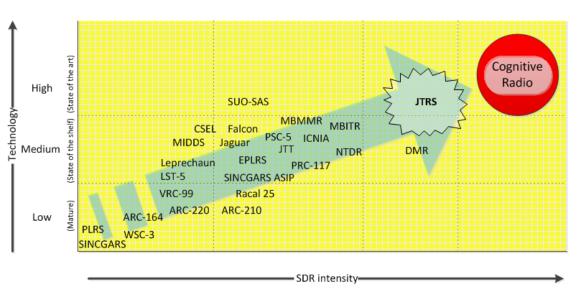

| 2.14 | Radio technology evolutions [23]                                          |

| 2.15 | Spectrum utilization snapshot at Berkeley [22, p. 163] 19                 |

| 2.16 | Spectrum utilization by employing DSA technology [1, p. 151] 20           |

| 3.1  | Effect of bad synchronization (the effect of external impairments, such   |

|      | as noise, have not been considered)                                       |

| 3.2  | 802.11a packet structure                                                  |

| 3.3  | Synchronization based on received signal energy                           |

| 3.4  | Incoming signal lost within the noise due to the low SNR                  |

| 3.5  | Principle of double slide window packet detection                         |

| 3.6  | 802.11a preamble structure [8, p. 51]                                     |

| 3.7  | Synchronization Based on preamble structured packet                       |

| 3.8  | Autocorrelation of the preamble [25, p.67]                                |

| 3.9  | (a) Sampling without CFO, (b) Effect of CFO                               |

| 3.10 | (a) Sampling without CPE and (b) Effect of CPE                            |

| 3.11 | Coarse symbol timing detection algorithms                                 |

| 3.12 | Two switch channel model                                                  |

| 3.13 | Out-Of-Band control systems                                               |

| 3.14 | Received waveform containing transmitted signal (a) before matched        |

|      | filter and (b) after matched filter                                       |

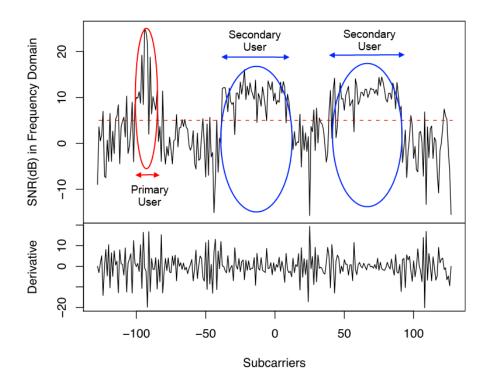

| 3.15 | NC-OFDM synchronization steps                                       | 42 |  |

|------|---------------------------------------------------------------------|----|--|

| 3.16 | 6 NC-OFDM waveform occupancy by primary and secondary user [37] .   |    |  |

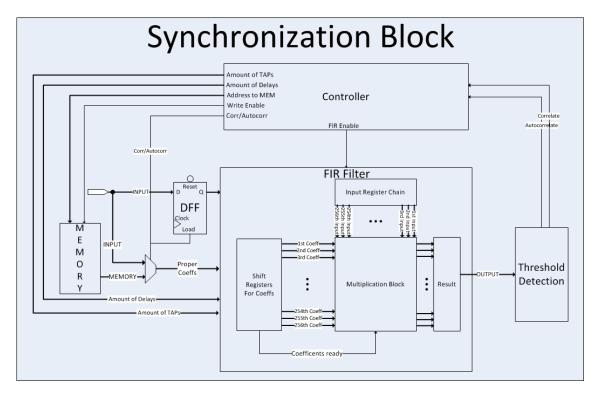

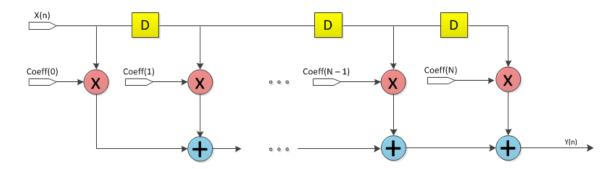

| 5.1  | Synchronization block architecture                                  | 50 |  |

| 5.2  | Sequential direct form FIR filter architecture                      | 51 |  |

| 5.3  | Critical path flown in the design                                   | 53 |  |

| 5.4  | Transposed direct form FIR filter architecture                      | 54 |  |

| 5.5  | Parallel direct form FIR filter architecture                        | 55 |  |

| 5.6  | Parallel direct form FIR filter with $N=8$                          | 55 |  |

| 5.7  | Pipelined direct form FIR filter with $N=8$                         | 56 |  |

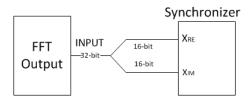

| 5.8  | Synchronizer inputs                                                 | 57 |  |

| 5.9  | Splitting 32-bit signal into two 16-bits signals                    | 57 |  |

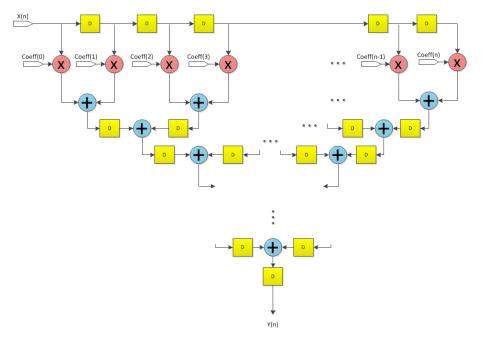

| 5.10 | Creating several copies of a process using GENERATE command         | 60 |  |

| 5.11 | Part of the code where an N-tap Transposed Direct Form (TDF)        |    |  |

|      | Finite Impulse Response (FIR) filter are created using GENERATE     |    |  |

|      | command                                                             | 61 |  |

| 5.12 | Truncation of 32-bit temporary result to 16-bit final result        | 61 |  |

| 5.13 | Part of the code where an N-tap Parallel Direct Form (PDF) FIR      |    |  |

|      | filter are created using GENERATE command                           | 62 |  |

| 5.14 | Configuring data flow (a) SCRUB and (b) AND/OR modes $\ \ .$        | 65 |  |

| 5.15 | Wrapper logic scheme for (a) Persona-1 uses all three ports and (b) |    |  |

|      | persona-2 uses two ports                                            | 66 |  |

| 5.16 | Schematic of a freeze logic                                         | 66 |  |

| 5.17 | Representation of (a) internal host and (b) external host           | 67 |  |

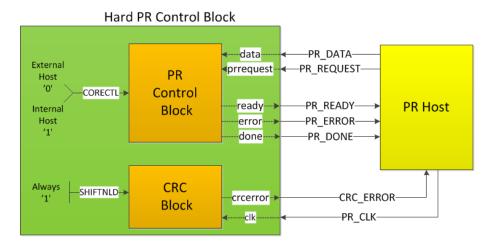

| 5.18 | How the Partial Reconfiguration (PR) host can be connected to the   |    |  |

|      | hard PR control block                                               | 68 |  |

#### LIST OF ABBREVIATIONS

**ALMs** Adaptive Logic Modules

**APP** A Posterior Probability

**ASIC** Application Specific Integrated Circuit

**ASK** Amplitude Shift Keying

AWGN Additive White Gaussian Noise

**CDMA** Code Division Multiple Access

**CFO** Carrier Frequency Offset

CIR Channel Impulse Response

CLB Configurable Logic Block

**CP** Cyclic Prefix

**CPE** Carrier phase Error

CPLD Complex Programmable Logic Device

CR Cognitive Radio

CRC Cyclic Redundancy Check

**DC** Delay and Correlate

**DFF** D-Flip-Flop

**DFT** Discrete Fourier Transform

**DSA** Dynamic Spectrum Access

**DSP** Digital Signal Processor

**DVB-T** Digital Video Broadcasting-Terrestrial

**EDA** Electronic Design Automation

**EDGE** Enhance Data GSM Environment

FCC Federal Communication Commission

FDMA Frequency Division Multiple Access

FFT Fast Fourier Transform

FIR Finite Impulse Response

FPGA Field Programmable Gate Arrays

FSK Frequency Shift Keying

FZC Frank-Zadoff-Chu

Gbps Giga Bit Per Second

**GI** Guard Interval

**GPP** General Purpose Processor

**GSM** Global System for Mobile

**HDD** Hard Decision-based Detection

**HDL** Hardware Description Language

I In-phase

IC Integrated Circuit

ICI Inter-Carrier Interference

**IEEE** Institute of Electrical and Electronic Engineers

**IDFT** Inverse Discrete Fourier Transform

IFFT Inverse Fast Fourier Transform

I/O Input/Output

**IP** Intellectual Property

I/Q In-phase and Quadrature-phase

**ISI** Inter-Symbol Interference

JTAG Joint Test Action Group

LABs Logic Array Blocks

LDPC Low-Density Parity-Check

**LEDs** Light-Emitting Diodes

LEs Logical Elements

LO Local Oscillator

LTI Linear Time Invariant

LTS Long Training Symbols

**LUT** Look Up Table

MAC Multiplier-Accumulate

ML Maximum Likelihood

M-L Multiplier-Less

MMSE Minimum Mean Square Method

NC-OFDM Non-Contiguous Orthogonal Frequency Division Multiplexing

**OFDM** Orthogonal Frequency Division Multiplexing

OOB Out-Of-Band

PAL Programmable Array Logic

PAPR Peak-to-Average Power Ratio

**PCI** Peripheral Component Interconnect

**PDF** Parallel Direct Form

PLA Programmable Logic Array

**PLL** Phase-Locked Loop

PN Pseudo Noise

PR Partial Reconfiguration

**PSK** Phase Shift Keying

**Q** Quadrature-phase

**QAM** Quadrature Modulation

RAM Random Access Memory

**RPDF** Retimed-Pipelined Direct Form

SCO Sampling Clock Offset

**SDD** Soft Decision-based Detection

**SDF** Sequential Direct Form

SDMA Space Division Multiple Access

SDR Software Defined Radio

SINR Signal to Interference and Noise Ratio

**SNR** Signal-to-Noise Ratio

SoC System-on-Chip

**SRAM** Static Random Access Memory

STO Symbol Timing Offset

STS Short Training Symbols

**TDF** Transposed Direct Form

TDMA Time Division Multiple Access

VC Virtual Carrier

VCD Value Change Dump

VHDL Very-high-speed integrated circuit Hardware Description Language

WiMAX Worldwide Interoperability for Microwave Access

WCDMA Wide Code Division Multiple Access

WiFi Wireless Fidelity

WLAN Wireless Local Area Network

**ZP** Zero Padding

**ZP-OFDM** Zero Padding Orthogonal Frequency Division Multiplexing

#### 1. INTRODUCTION

Wireless data communication networks are one of the major concerns of developed countries with respect to the finite resource of radio spectrum. Therefore, several challenges where the physical layer is more involved have come into picture in order to use spectrum as efficient as possible. Variety of applications have occupied the entire spectrum including financial transaction, social interactions, security, etc. Although, both wired and wireless devices are capable of performing various services, such as audio and video broadcasting, web browsing, etc, with rapid evolution of microelectronics, wireless transceivers surrogated the traditional wired systems due to being more versatile as well as being portable. However, spectrum scarcities are increased more and more in that case [1]. At the moment, most of the prime spectrum has been assigned to so called primary user or licensed user and it is bothersome to find some free spectrum for new wireless applications.

#### 1.1 Motivation

Since 1991, the development of Software Defined Radio (SDR) has been enabled in which the transceiver carries out the entire baseband processing in software. SDR defines a radio platform in which, at least, a portion of the implementation is held in software. In other words, any waveform can be applied to any frequency band. In general, standard patterns such as IEEE-802.11a/b/g based in software, can be easily replace in an SDR platform, while in traditional systems a complete replacement of the radio frequency hardware is needed. Therefore, in order to swap from a standard to another one, an expensive hardware upgrade should be performed. [1]

The basic idea of the Cognitive Radio (CR), which can be implied as an intelligent and advanced version of SDR, was proposed in 1998 and published in in 1999 by Joseph Mitola and Gerald Q. Maguire [2]. In principle, CR is a platform which can rapidly change its operating parameters by considering new environment characteristics. CR changes corresponding parameters in such a way that the user is not even notified. It is a new promising technology capable of detecting particular unused segments of the radio spectrum and employs them for secondary usage without interfering with the licensed users.

Although the above mentioned approaches look simple, several obstacles pose challenges from both sender and receiver point of view. One of the major concerns 1. Introduction 2

in a CR receiver is to establish an accurate and robust synchronization scheme. In other words, how the receiver should be notified that in which frequency bands the transmitter is transmitting.

This thesis developed a new technique where the receiver distinguishes the characteristics of the secondary transmitter without any prior knowledge about the frequency band and the standard employed by the secondary user. Once the presence of a secondary transmitter is discovered, the receiver adopts its primary parameters to that of the transmitter.

#### 1.2 Thesis Outline

This thesis is organized as follows:

Chapter 2 focuses on different types of modulation including single-carrier, multi-carrier and multiple access methods. Although single-carrier modulations are primary modulation techniques, CR technology is based on multi-carrier modulations. Therefore, in order to know how an accurate synchronization can be established, two major multi-carrier techniques are explained in detail. Thereafter, the concepts of SDR, CR and Dynamic Spectrum Access (DSA) methods are studied.

Chapter 3 concentrates more on synchronization issues. Followed by a brief introduction to the context of synchronization, different effects of bad synchronization are studied. Explanations regarding how, where and when the synchronization should be performed are narrowed to multi-carrier techniques.

Chapter 4 discusses previous implementations of the synchronizer with respect to their limitations and the state of art in synchronization architecture.

Chapter 5 explains different implementations of the synchronizer. The development kit is based on Altera Stratix-V family Field Programmable Gate Arrays (FPGA). The fundamental core of the synchronization block is studied step by step. This chapter completely investigates new emerged PR feature. Eventually, the compilation results related to each implementation are discussed in several tables.

Chapter 6 summarizes the entire work with respect to different implementations of the synchronization block. This chapter also compares results with each other and discusses about the trade-off between them.

## 2. WIRELESS COMMUNICATION SYSTEMS

The pervasive applications of wireless communication in modern society have led to several fields of research in which the physical layer is more involved. The harsh nature of channel with respect to different type of impairments threatening the signal, including scattering, reflection and diffraction, robust modulation, synchronization, channel estimation, etc, can only be few examples of above-mentioned concerns. [4]

Since this thesis is more dealing with synchronization scheme for CR systems based on Non-Contiguous Orthogonal Frequency Division Multiplexing (NC-OFDM), in order to understand the entire concept, single-carrier modulation techniques are briefly discussed. Then few basic Multiple Access methods are presented. Next, the principle of multi-carrier modulations in context of Orthogonal Frequency Division Multiplexing (OFDM) will be covered in detail, and, finally, before proceeding to the concept of CR, NC-OFDM will be studied.

## 2.1 Single-Carrier Modulation

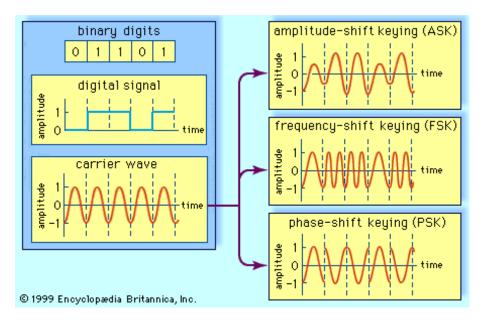

The basic idea of the digital communication is to transmit information from sender to receiver via a propagation channel. Modulation, in brief, is the process in which the information signal, which is considered as the message signal, propagates through the channel after being multiplied by the carrier signal [5]. Figure 2.1 illustrates three main digital single-carrier modulation methods. According to [9], fundamental digital single-carrier modulation methods are listed as follows:

- Amplitude Shift Keying (ASK): When the amplitude is the element to be varied.

- Frequency Shift Keying (FSK): When the frequency is considered to be varied for signal carrier.

- Phase Shift Keying (PSK): When the phase is the candidate to be varied.

- Quadrature Modulation (QAM): When both amplitude and the phase are candidates to be varied, thereby two In-phase (I) and Quadrature-phase (Q) components are produced.

Figure 2.1. Basic Single-Carrier Modulation Methods [9].

## 2.2 Multiple Access Methods

In contrast to wired systems, spectrum is a scarce resource in wireless system. In single-carrier modulation, data bits are modulated and the new produced modulated signals are transmitted sequentially through the spectrum. According to [6], single-carrier modulation not only wastes the frequency band due to its low data rate, but also requires a complex channel equalization. Furthermore, in most wireless systems there is a high demand of having multiple devices communicating in the same area. However, mostly, a certain frequency band is assigned to specific applications, due to scarcity of the spectrum, which can not be extended easily. Therefore multiple access techniques should be provided to use frequency band as efficiently as possible while it permits simultaneous communications of many users. The following subsections cover different multiple access methods [7].

## 2.2.1 Frequency Division Multiple Access (FDMA)

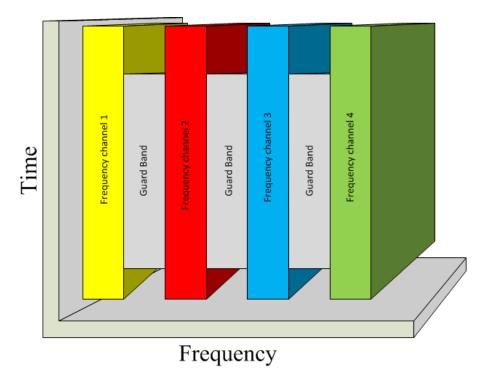

Frequency Division Multiple Access (FDMA) is the first and the simplest multiple access method. As it is depicted in Figure 2.2, a dedicated frequency band exists for each user in which the entire spectrum is exerted and will be released by the user [7]. This multiple access technique has the following advantages and disadvantages:

#### Advantages:

- Low complexity due to simple synchronization algorithm.

- No fading occurs during the transmission, due to using narrower frequency

Figure 2.2. Principles of Frequency Devision Multiple Access

band compared to other multiple access methods. Thus, very simple equalization is required.

• Since the transmission is continuous, a simple tracking algorithm is required.

#### Disadvantages:

- Unused frequency bands, which is the major concern in spectrum efficiency, stay idle which result in wasting the spectrum.

- Guard bands are needed to cope with interferences caused by the adjacent frequency bands

- Sensitive to multipath effects.

- No frequency diversity due to narrow band.

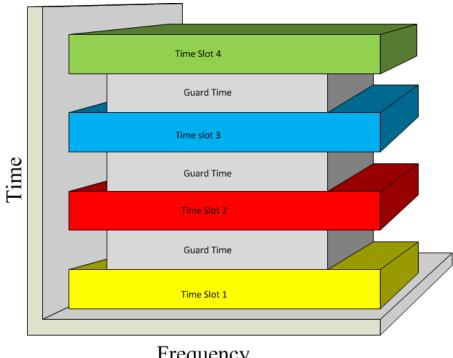

## 2.2.2 Time Division Multiple Access (TDMA)

However, Time Division Multiple Access (TDMA) is quite similar to FDMA, instead of allocating a narrow frequency band for a long time to a certain user, the whole frequency band is dedicated to the same user in a certain time known as time slot [7]. In other words, the time unit is divided into N time slots, each of which is assigned to a different user who is eligible to transmit over the entire frequency band. Figure

Frequency

Figure 2.3. Principles of Time Devision Multiple Access

2.3 shows the concept of TDMA modulation. There are several advantages and disadvantages for TDMA similar to that of FDMA.

#### Advantages:

- Occupying a larger amount of frequency bandwidth results in exploitation of the frequency diversity.

- More flexibility compared to FDMA in terms of efficient usage of the bandwidth.

- Achieving a higher data rate by employing several time slots for a single user.

#### Disadvantages:

- Since the transmission is non-continuous, a precise synchronization is needed for each time slot.

- The duration of time slots needs to be optimized. In case of a short time slot, a large percentage of the time is wasted for synchronization. On the other hand, a long time slot produces longer latency.

- Time guards are required similar to that of FDMA.

- Adaptive channel equalization is always needed.

Figure 2.4. Principles of Code Division Multiple Access

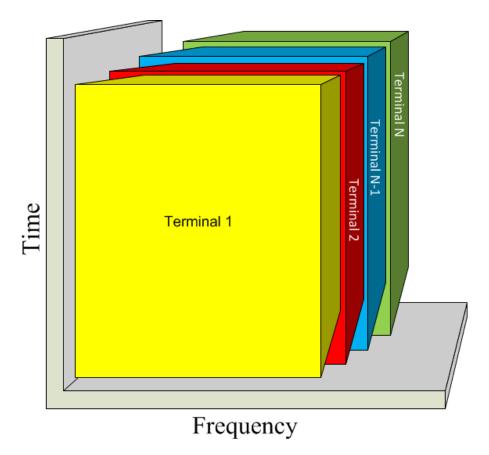

## 2.2.3 Code Division Multiple Access (CDMA)

In addition to drawbacks of FDMA and TDMA access methods, another constraint induced researchers to develop Code Division Multiple Access (CDMA) access technique. Those methods could only serve finite number of users due to the limited available frequency bands or time slots. In other words, if all the frequency channels or time slots have been completely assigned to the users, a new incoming request should remain on hold until one of the channels or the slots is released.

As Figure 2.4 shows, in CDMA technique all the terminals are transmitting on the same frequency at the same time (while preserving the entire bandwidth), multiplied with a unique *signature*, also known as chip code, for each user. Thus, various users are able to communicate simultaneously at the same time. At the receiver, the desired signal can be demodulated by correlating the received signal with the chip code known by the receiver. At this point, other received signals are considered as interference from the receiver's point of view. This process is called *code acquisition*. There are several advantages and disadvantage by employing CDMA multiple access method, as well.

#### Advantages:

- Since all the terminals are using the same frequency band, no synchronization is needed.

- Huge code space makes the maximum number of users to be, theoretically, infinite.

- Interference caused by other terminals behave like noise.

#### Disadvantages:

- Precise power control is needed to compensate far-away low power users and prevent them from being blocked by near users (Near-Far problem).

- Chip timing is difficult to be acquired and maintained.

- Chip sequences of different users must be orthogonal to each other in order to have successful demodulation.

#### 2.3 Multi-Carrier Modulations

Multi-carrier modulation is a method of transmitting a high speed data stream by splitting it into several sub streams and sending each of them over a separate carrier signals and, therefore, allowing system to support multiple users at the same time. The individual carriers have narrow bandwidth while the composite signal has a wide bandwidth. In this section, one of the most famous multi-carrier modulations named OFDM is investigated in detail.

## 2.3.1 Orthogonal Frequency Division Multiplexing (OFDM)

OFDM is a robust technique used in many recent standardized wireless systems in order to achieve higher data rate as well as combating frequency selective fading while the synchronization is preserved at a satisfactory level. Only few subcarriers are distorted over deep fading or narrow band channels which can be compensated using error control mechanisms such as forward error correction. [12]

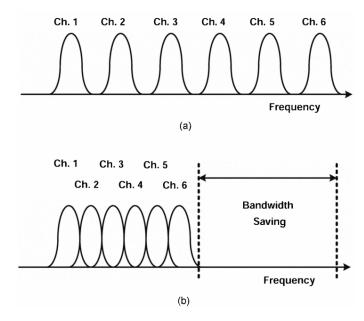

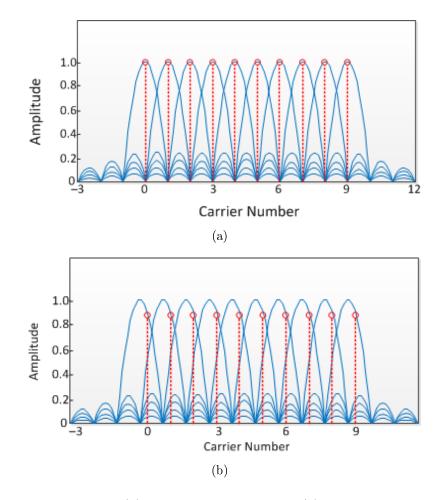

In principle, a high speed data stream is divided into  $N_u$  parallel substreams modulated onto  $N_u$  orthogonal subcarriers. It can be said that the OFDM is a hybrid of multi-carrier modulation and single-carrier FSK modulation [4]. Figure 2.5 shows how OFDM modulation saves the bandwidth by overlapping the adjacent subchannels while the orthogonality is preserved. In addition, Figure 2.6 illustrates how OFDM modulation is able to serve multiple users in the same frequency band as dedicated to single carrier FSK modulation.

Figure 2.5. (a) Conventional non-overlapping multi-carrier modulation. (b) Overlapping multi-carrier modulation. [6, p.26]

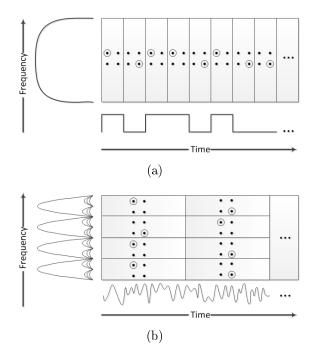

Figure 2.6. Comparison between (a) single-carrier FSK modulation and (b) multi-carrier OFDM modulation.

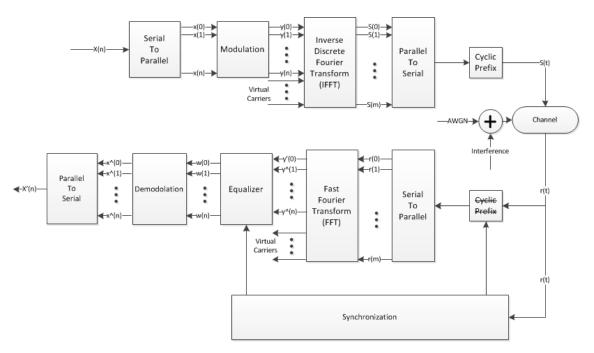

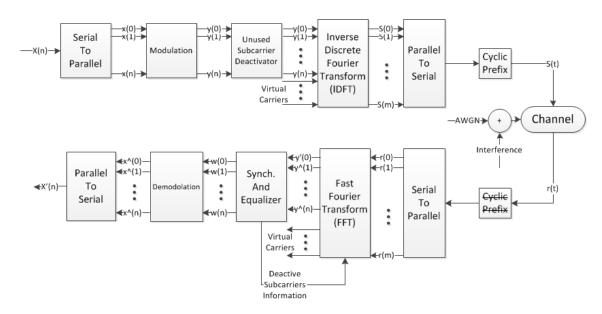

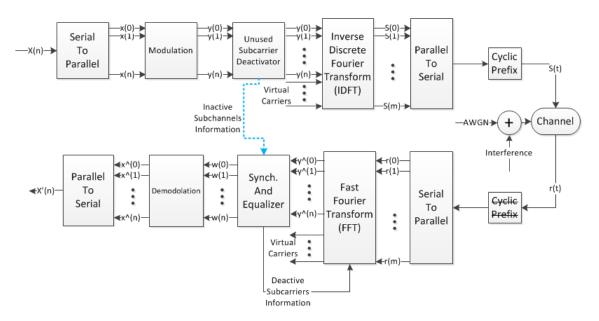

An architecture of an OFDM transceiver is shown in Figure 2.7. A high-speed data stream X(n) is demultiplexed into  $N_u$  parallel ones  $x^{(k)}(n), k = 0, \ldots, N_u$  by employing a serial to parallel converter to form a set of data subcarriers. Then each of them is individually modulated using either QAM or PSK modulation and produces  $y^{(k)}(n), k = 0, \ldots, N_u$  [1]; typically, as long as the receiver knows the modulation pattern, each subcarrier is modulated with the same constellation [11].

Figure 2.7. OFDM transceiver architecture [4, p. 38]

After the modulation is done, baseband OFDM waveform  $s^{(\ell)}(n), \ell = 0, ..., N$  can be constructed as a N-input Inverse Discrete Fourier Transform (IDFT) unit with  $N \geq N_u$  defined as Equation (2.1).

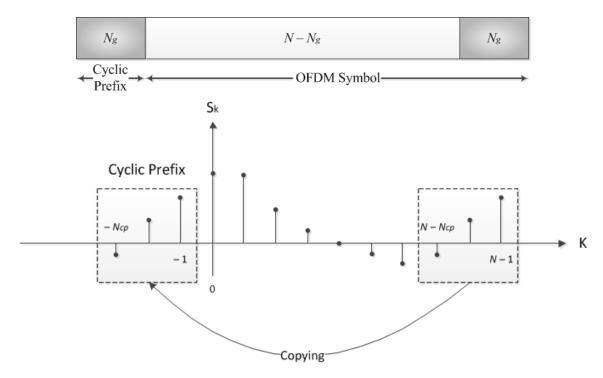

The  $N-N_u$  unused inputs of the IDFT are set to zero and they are called Virtual Carrier (VC) which, typically, are dedicated to be used as guard bands in order to avoid interferences caused by transmission power of the adjacent subcarriers. This phenomenon is also known as Inter-Symbol Interference (ISI) and will be addressed later on. In general, IDFT can be implemented using an Inverse Fast Fourier Transform (IFFT) function. Finally, a Cyclic Prefix (CP) is added before converting the subcarriers to the composite signal s(n). [4]

$$s^{(\ell)}(n) = \frac{1}{N} \sum_{k=0}^{N-1} y^{(k)}(n) e^{j2\pi k\ell/N}$$

(2.1)

At the receiver, first the CP is removed from the received signal r(n). Next, a conversion between serial stream to parallel streams is applied by employing a serial to parallel demultiplexer. Then, with respect to Equation (2.2), the information can be extracted by performing Discrete Fourier Transform (DFT) function on the received parallel waveforms where  $r^{(\ell)}(n)$  are parallel input streams. DFT can be performed using a Fast Fourier Transform (FFT) function which produces  $\hat{y}^{(k)}(n)$ . Subcarriers are then equalized in order to compensate distortions caused by the channel. The equalized sub carriers  $\omega(n)$  are then demodulated and, finally, serial steam x'(n) is obtained using a parallel to serial converter on the parallel streams

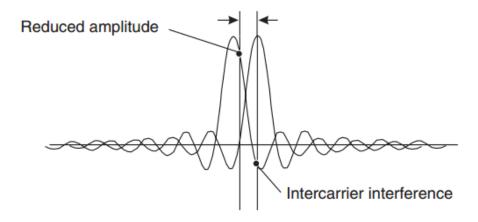

Figure 2.8. Inter-Carrier Interference due to frequency offset [7, p. 432]

$x^{(k)}(n)$ . [4]

$$\hat{y}^{(\ell)}(n) = \sum_{\ell=0}^{N-1} r^{(\ell)}(n)e^{(-j2\pi k\ell/N)}$$

(2.2)

Guard Interval (GI): In wireless systems, the receiver might receive several copies of transmitted signal due to the multipath effects in which the original signal is arrived on time and the rest will be received by a small amount of delay. This phenomenon is called ISI where the tail of the first symbol is collided with the beginning of the second one which leads to destroy the entire symbol.

In order to cope with ISI, a Guard Interval (GI) with the length  $N_g$  is inserted to the first segment of each OFDM symbol. The length of the GI should be more than the length of the delay spread of the channel. For this reason, a degree of delay spread should always be considered while an OFDM symbol is constructed. [7]

During the guard interval, the transmitter sends a null waveform called Zero Padding (ZP). Although, Zero Padding Orthogonal Frequency Division Multiplexing (ZP-OFDM) has a simple and low power structure, it introduces another phenomenon called Inter-Carrier Interference (ICI) in which the orthogonality between subcarriers is destroyed due to receiving several copies of the time shifted ZP-OFDM waveform. Figure 2.8 depicts ICI caused by one subcarrier which affected many adjacent subcarriers. In order to eliminate the effect of ICI, a CP illustrated in Figure 2.9 is combined with the zero padding part which is exactly a duplication of a certain part from the end of the OFDM waveform to its beginning [6]. Figure 2.10 shows the whole above-mentioned scenario.

Similar to other single-carrier and multiple access methods, OFDM has its own advantages and disadvantages listed as following: [13]

#### Advantages:

Figure 2.9. Structure of an OFDM block with cyclic prefix

Figure 2.10. (a) Illustration of ISI due to multipath delay; (b) zero-padding guard interval to avoid lSI; (c) guard interval with cyclic prefix to eliminate lSI and ICI [6, p. 28].

- Efficient use of bandwidth.

- Suitable for high data rate transmission.

- More resistance to frequency selective fading.

- Simple channel equalization technique compared to other techniques.

- Less sensitive to sample timing offset.

- Elimination of ISI and ICI problems due to the use of CP.

#### Disadvantages:

- Peak-to-Average Power Ratio (PAPR) problem, having an amplitude with a large dynamic range due to the superposition of N sinusoidal signals on different subcarriers.

- Sensitive to carrier frequency offset.

- Extra overhead introduced by the CP.

## 2.3.2 Non-Contiguous Orthogonal Frequency Division Multiplexing (NC-OFDM)

All of the techniques which are discussed so far, operate on contiguous spectrum frequencies. For example, a transceiver with 5 MHz bandwidth can operate, only if it detects an idle contiguous 5 MHz bandwidth among the whole spectrum. On the other hand, a narrow-band transceiver which has employed a 5 MHz bandwidth of the frequency band for transmitting 500 kHz, is wasting up to 90% of the scarce wireless bandwidth resource. Therefore, another multi-carrier modulation technique is needed to use these white spaces over the spectrum in such an optimum way not to interfere with adjacent users. [15]

In particular, the new technique must be agile enough to enable unlicensed users operate within unused spectrum dedicated to the licensed users while not interfering with the incumbent users. Moreover, it should be capable of handling high data rates transmission. One technique which meets all these criteria is a variant of OFDM modulation called NC-OFDM. In comparison with other techniques, NC-OFDM is capable of deactivating subcarriers which interfere with transmission of other users [1]. Figure 2.11 shows the difference between OFDM and NC-OFDM techniques.

Fundamental principles of NC-OFDM are quite similar to that of OFDM system. As depicted in 2.12, a high-speed data input X(n) is demultiplexed into  $N_u$  parallel data streams  $x^{(k)}(n), k = 0, \ldots, N_u$  using a serial to parallel converter to form a set

Figure 2.11. (a) OFDM and (b) NC-OFDM schemes.

of data subcarriers. Then each one of these  $x^{(k)}(n)$  is individually modulated using either QAM or PSK modulation and produce  $y^{(k)}(n), k = 0, ..., N_u$ . At this point, a total number of unused subcarriers are deactivated by employing, for example, a controller unit. Next, baseband OFDM waveform  $s^{(\ell)}(n), \ell = 0, ..., N$  can be constructed as a N-input IFFT unit with  $N \geq N_u$ . The  $N - N_u$  unused inputs of the IFFT are set to zero and use as virtual carriers dedicated to be used as guard bands. Finally, a CP is added before subcarriers convert to the composite signal s(n). [1]

At the receiver, The cyclic prefix is removed from the received signal r(n) first. Next, a conversion from a serial stream to parallel streams is applied by employing a serial to parallel demultiplexer. Then, the information can be extracted by performing a FFT on the received parallel waveform where  $r^{(\ell)}(n)$  are parallel input streams produce  $\hat{y}^{(k)}(n)$ . Subcarriers are then synchronized and equalized in order to compensate the distortion caused by the channel. The equalized sub carriers  $\omega(n)$  are then demodulated and finally a serial steam x'(n) is obtained using a parallel to serial converter on parallel streams  $x^{(k)}(n)$ . [1]

Basically, by taking into account both Figure 2.7 and Figure 2.12, a fundamental difference can be seen between OFDM and NC-OFDM receivers which is the synchronization part. In contrast to OFDM where the synchronization is done before performing FFT, in NC-OFDM receiver the synchronization performed while the

Figure 2.12. NC-OFDM transceiver architecture

FFT is done. This trivial change in NC-OFDM system emerges challenges for receiver designers [1]. One of these challenges is how to keep the receiver synchronized with transmitter which is studied in detail at synchronization section.

Similar to other modulations, NC-OFDM contains some advantages, in addition to that of OFDM, and some drawbacks listed as following [16]:

#### Advantages:

- It is capable of turning off subcarriers across its transmission which are potentially interfere with adjacent subcarriers.

- NC-OFDM supports a high aggregate data rate using the rest of activated subcarriers.

#### Disadvantages:

- FFT pruning algorithms should be applied to compensate the effect of deactivated subcarriers on computation time.

- Synchronization scheme poses a lot of challenges, since the situation of the carrier frequency might be altered at any time.

- PAPR problem still exists.

- Precise synchronization requires more power consumption.

## 2.4 Introduction to Cognitive Radio (CR)

New evolutions in wireless communication technology have increased the demand of a more flexible, adoptable and intelligent transceivers due to the scarcity of wireless spectrum. Although, data communication networks are one the major challenges of developed countries with respect to the finite resource of the radio spectrum, wireless transceivers are more versatile and portable than the traditional wired systems. Before stepping forward to the concept of CR, It is crucial to address principle of SDR first.

## 2.4.1 What is Software Defined Radio (SDR)

With rapid evolution of microelectronics, wireless transceivers surrogated the traditional wired system due to be more versatile as well as being portable. Since 1991, the development of SDR has been enabled in which the transceiver carries out the entire baseband processing in software. SDR defines a radio platform in which, at least, a portion of the entire implementation is held in software. In a technical view, any waveform can be applied for any frequency band which permits the transceiver to be operated as a multi-function, multi-band and multi-mode wireless device. [18]

Over the years, the radio community has realized that most of the radio functions can be handled in the software. In general, wireless standards, such as IEEE-802.11a/g/n, which are based in software can be easily swapped in and out in an SDR platform. In traditional systems, a complete replacement of the radio frequency hardware is required in order to switch from a particular standard to another one which undergoes an expensive upgrade [1]. In an SDR platform, most of the signal processing is done in programmable processing technologies including General Purpose Processor (GPP), programmable System-on-Chip (SoC), Digital Signal Processor (DSP) and FPGA. Generally, architectural complexity of a SDR platform is more limited to run-time requirements and high computational workload of the algorithms. However, the scaling of the silicon technology permits to employ more number of the transistors for implementing computationally intensive architecture [19].

According to [20], two major advantages of SDR are, first, flexibility where the transceiver simply switches between channels and the second one is adaptability where the radio parameters, including channel modulation, frequency, power and bandwidth, can be simply changed due to the radio environment. Similar to other type of new evolved technologies, SDR platforms emerged from military researches and were then employed for civil usages. In general, SDR is the core enabler for a new technology named CR.

## 2.4.2 What is Cognitive Radio (CR)

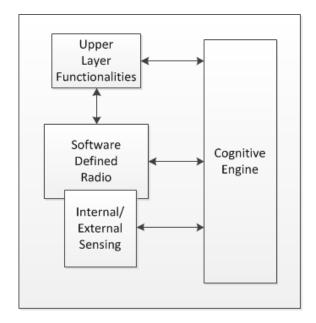

The basic idea of CR, which can be implied as an intelligent version of SDR, was proposed by Joseph Mitola in 1998 and published in by Mitola and Gerald Q. Maguire in 1999 [2]. CR is basically an SDR platform which can rapidly change its operating parameters by considering new circumstances and criteria. In contrast with SDR, in CR these parameters are changed in such a way that its user is not even noticed. Technically, CR is smart enough to decide how, where and when it uses the spectrum without any prior knowledge. As Simon says in [21], "Cognitive radio is an intelligent wireless communication system that is aware of its surrounding environment (i.e., outside world) and uses the methodology of understanding-by-building to learn from the environment and adapt its internal states to statistical variations in the incoming RF stimuli by making corresponding changes in certain operating parameters (e.g., transmit-power, carrier-frequency, and modulation strategy) in real-time, with two primary objectives in mind:

- highly reliable communications whenever and wherever needed;

- efficient utilization of the radio spectrum.

Six key words stand out in this definition: awareness, intelligence, learning, adaptivity, reliability, and efficiency." Figure 2.13 shows how CR is in relation to SDR. Based on that, cognitive engine is responsible to optimize and control SDR by simultaneously learning the environment using a sensing unit. Moreover, cognitive engine must be aware of hardware resources as well as other input parameters. Therefore, SDR becomes a flexible and common radio platform capable of supporting multiple standards, for example Global System for Mobile (GSM), Enhance Data GSM Environment (EDGE), Worldwide Interoperability for Microwave Access (WiMAX), Wireless Fidelity (WiFi) and Wide Code Division Multiple Access (WCDMA), as well as operating over a wide range of frequencies with different type of modulation techniques such as Space Division Multiple Access (SDMA), TDMA and OFDM [22].

## 2.4.3 Evolution of Radio Technology

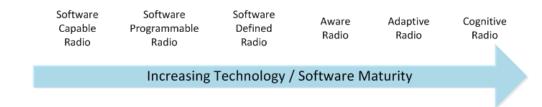

Figure 2.14 shows the evolution of radio technology. An Aware Radio has sensors which enables the device to be aware of the environment. An Adaptive Radio is not only aware of its environment, but also is capable of changing its behavior in response. The final stage is CR. According to Polson's opinion in [23], CR is carrying the following characteristics:

• Sensors creating awareness in the environment.

Figure 2.13. CR and its relation to SDR

- Actuators enabling interaction with the environment.

- Memory and a model of the environment.

- Learns and models specific beneficial adaptations.

- Has specific performance goals.

## 2.4.4 Dynamic Spectrum Access (DSA)

Due to propagation characteristics of the electromagnetic waves, a wide range of frequencies between 10 MHz to 6 GHz are suitable for wireless communication purposes. Although, this frequency range seems to be sufficient, a massive number of users are transmitting over the entire spectrum with, almost, the same transmission scheme. Therefore, since 1994 an American national organization called Federal Communication Commission (FCC) has conducted 33 spectrum auctions worth over 40 Billion dollars to some particular owners. A few of these spectrum owners examples are AM, FM, TV broadcast operators, telecommunication network operators, etc (also are known as licensed users or primary users).

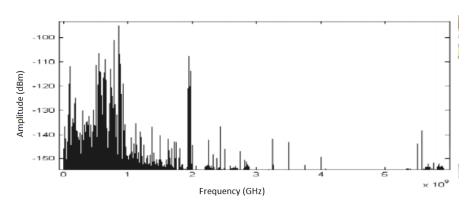

An investigation in United States of America estimates that only 15% of the bandwidth is used in most of the cases. Figure 2.15 depicts how the primary user wastes the entire licensed bandwidth by not using the whole spectrum efficiently. Consequently, researchers focused more on a secondary usage of the bandwidth for unlicensed users over the licensed spectrum as their main objective, since almost none of licensed users are using the whole dedicated spectrum and only use particular

Figure 2.14. Radio technology evolutions [23]

Figure 2.15. Spectrum utilization snapshot at Berkeley [22, p. 163]

part of the bandwidth. These efforts led to employ white-spaces as a secondary solution to be used for unlicensed users of what it is currently considered as DSA. The key motivation for DSA comes from the fact that the spectrum assigned to the licensed transmission band is not exploited to its full extent at all times. [7]

With recent developments in CR technology both licensed and unlicensed users can simultaneously communicate over the licensed spectrum as long as the unlicensed user respect to the right of incumbent licensed holder. In principle, full CR, also known as Mitola radio, is capable of adopting ALL transmission parameters, in-

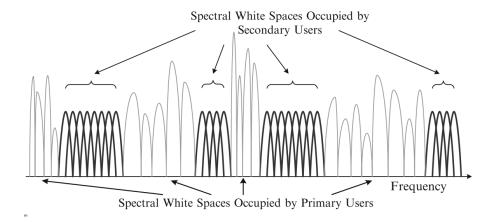

cluding modulation format, accessing method, coding, center frequency, bandwidth, transmission times, etc, which is more likely to be as a science fiction view due to implementation complexities. Therefore, DSA is a spectrum sensing cognitive radio which only adapts the transmission frequency, bandwidth and time according to the environment circumstances [7]. Figure 2.16 illustrates how DSA enables the secondary usage of the licensed spectrum within white spaces without interrupting the primary user.

Traditionally, spectrum sharing between primary and secondary users was done manually. Secondary user monitored the primary user spectra and then intended to transmit over the whitespace or spectral holes. DSA extends this process by automating the processes of monitoring, selecting and using. Moreover, the frequency bands assigned to the secondary user must have the least probability of interfering with incumbent user. Therefore, a robust, accurate and reliable modulation technique performs a significant role at this stage. One of the most robust modulation candidates, which meets above-mentioned characteristics, is NC-OFDM due to its capability of turning off a portion of subcarriers interfering with the primary user and operates over a subset of non-contiguous subcarriers.

Figure 2.16. Spectrum utilization by employing DSA technology [1, p. 151]

#### 3. SYNCHRONIZATION

In each digital communication system, synchronization is an essential mechanism in order to fetch useful data from the received signal. So far, designing a robust and accurate synchronization algorithm has been one of the major challenge for design engineers. Synchronization is the process in which the receiver firstly detects any incoming data from the received signal and secondly distinguishes both the beginning and the end of the received packet.

Although there are several methods to establish a reliable synchronization for different modulation schemes, since the goal of this thesis is to present a flexible timing synchronization scheme for cognitive radio applications, synchronization issues regarding to OFDM as well as NC-OFDM are studied.

NC-OFDM is an extension of OFDM technique in which unused subcarriers can be deactivated in order to eliminate any interferences with the primary user. Therefore, for understanding synchronization techniques related to NC-OFDM system, a deep understanding of what happens in OFDM synchronization is strongly required before stepping forward to NC-OFDM systems.

Most of the synchronization algorithms designed for single-carrier and other multi-carrier techniques are unusable for OFDM and, consequently, NC-OFDM systems due to the nature of its frequency domain. One of the most important constraints which is different in OFDM technique is the fact that the synchronization can be established either in time- or frequency-domain. This level of flexibility is not available in other modulation methods. Hence, a tradeoff between lower computational complexity and higher performance exist between different synchronization algorithms.

## 3.1 Effects of Poor Synchronization

In digital transmission, the data bit streams are represented in discrete-time signal format while all the physical media are able to communicate over the continuous-time format due to their nature. Moreover, most of the transmission media are inefficient to transmit baseband signals. Therefore, the digital baseband signal should be converted into continuous-time waveform and then modulated to a higher frequency signal before propagating through the channel. Wireless receivers are equipped with a Local Oscillator (LO) whose carrier frequency and phase are the same as that of

the signal in received waveform. Thus, the original signal can be driven out from the received signal by executing an accurate sampling of the clock frequency and phase on incoming signal. This process seems to be simple enough, synchronization issues emerge from this point which the researchers are still involved with to some extent. Unfortunately, the receiver is unsynchronized with the transmitter and it should be synchronized for each transaction.

The following issues are most important impairments threatening a proper synchronization [6].

- Carrier frequency/phase errors caused LO clock.

- LO not only can not maintain the frequency and the phase, but also suffers from time variant phase noise.

- Additional phase rotation introduced in LO due to unknown propagation delay between sender and receiver.

- Frequency shift caused by Doppler effect.

- Cross-coupling of I/Q signals, also known as IQ imbalance, due to the frontend electronic mismatches.

## 3.2 Synchronization Errors

Synchronization errors can be yielded in either time, frequency or both. The basic concept in synchronization is that the receiver must know when to run the sampling process on the incoming wave stream. The sampling must be done exactly at the same time as it is supposed to be. Any alteration in sampling time causes the receiver to lose the data, miss the packet and terminate the transmission, meaning to waste the bandwidth. Therefore, perfect synchronization is one of the main concerns from the receiver's perspective. In the following, some major sources of synchronization impairments are explained briefly: [6]

- Carrier Frequency Offset (CFO): Causes the received signal to be rotated with a magnitude of  $\Delta_f$ .

- Carrier phase Error (CPE): Introduces additional phase rotation of magnitude  $\phi(t)$  to the received signal.

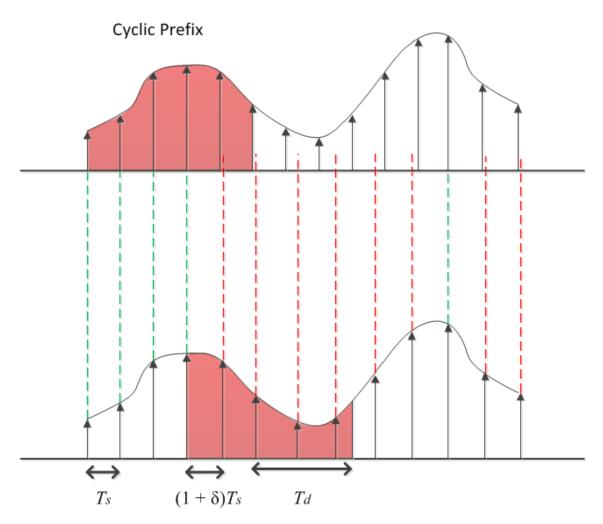

- Sampling Clock Offset (SCO): Is caused by performing a sampling of a period  $(1 + \delta)T_s$  instead of  $T_s$  on the received continuous-time signal.

- Symbol Timing Offset (STO): Occurs when the receiver loses the actual boundary of the received waveform.

Figure 3.1. Effect of bad synchronization (the effect of external impairments, such as noise, have not been considered)

• IQ imbalance: Generates gain/phase mismatch in up/down conversions of I/Q paths.

The effect of a bad synchronization due to the SCO and STO errors are illustrated in Figure 3.1. As it can be seen, sampling at  $(1 + \delta)T_s$  interval caused the rest of the sampling process to be inaccurately done. Moreover, symbol boundary does not meet the criteria at all by the receiver either.

## 3.3 OFDM Synchronization Issues

Synchronization errors can be yielded in time, frequency or both. Although, single carrier modulations are more sensitive to time-domain errors (where OFDM has more resilience), OFDM suffers from frequency errors raised by performing FFT due to its frequency domain nature [6]. Equation (3.1) and (3.2) are used to approximately estimate the degradation caused by CFO and CPE for single carrier

| Preamble | Physical<br>Layer<br>Header | Data Field |

|----------|-----------------------------|------------|

|----------|-----------------------------|------------|

Figure 3.2. 802.11a packet structure

and OFDM modulations, respectively where  $\Delta_f$  is the magnitude of CFO and  $\beta$  is a function of oscillator linewidth [25].

$$D \approx \begin{cases} \frac{10}{ln10} \frac{1}{3} (\pi \Delta_f T)^2 & \text{Single Carrier} \\ \frac{10}{ln10} \frac{1}{3} (\pi \Delta_f T)^2 \times SNR & \text{OFDM} \end{cases}$$

(3.1)

$$D \approx \begin{cases} \frac{10}{ln10} \frac{1}{60} (4\pi\beta T) \times SNR & \text{Single Carrier} \\ \frac{10}{ln10} \frac{11}{60} (4\pi\beta T) \times SNR & \text{OFDM} \end{cases}$$

(3.2)

Type of transmission is one of important issues in synchronization. Usually data is transmitted in either packet based or frame based format. In packet based systems, such as Institute of Electrical and Electronic Engineers (IEEE) 802.11a/g/n Wireless Local Area Network (WLAN), user data is divided into several so called packets with a limited size.

As shown in Figure 3.2, each packet starts with a known sequence named preambles which facilitate the synchronization process. Following by, a header which is consists of important information such as modulation order, code rate, etc. Finally, the user data is composed to form a complete packet. With this compressed structure the receiver does not have sufficient time to detect the signal. Therefore, the estimation and compensation processes for each error which might have occurred at the received signal must be done immediately. Since the FFT is completed after several cycles due to the heavy workload of computations in frequency domain, it is more likely to exploit time-domain synchronization in most of the receivers. Furthermore, periodic repetition of the preamble at the beginning of each packet, which has a good autocorrelation property, assists synchronization of OFDM packet-based system to be performed in time-domain.

In frame based OFDM systems, such as Digital Video Broadcasting-Terrestrial (DVB-T), data are transmitted continuously. Therefore, receiver has more time to

perform synchronization. Thus, receiver designers are more flexible to perform the synchronization in either time-domain or frequency-domain.

## 3.3.1 Synchronization Methods

As soon as the receiver is turned on, it should start searching for OFDM symbols in the received signal. According to the Equation (3.3), where  $\omega(n)$  is the amount of Additive White Gaussian Noise (AWGN), when no incoming signal is transmitted by the transmitter, the magnitude of the received signal is equal to noise level.

$$y(n) = \omega(n) \tag{3.3}$$

As soon as the sender starts transmission, as it can be seen from Equation (3.4), the magnitude of received signal is equal to the amount of AWGN plus the signal s(n) which should be detected by the receiver. [22]

$$y(n) = s(n) + \omega(n) \tag{3.4}$$

According to above-mentioned descriptions, there are several algorithms designed to perform synchronization in OFDM modulation as following:

- Received Signal Energy Detection.

- Double Sliding Window Packet Detection.

- Preamble Structured Packet Detection.

#### Received Signal Energy Detection

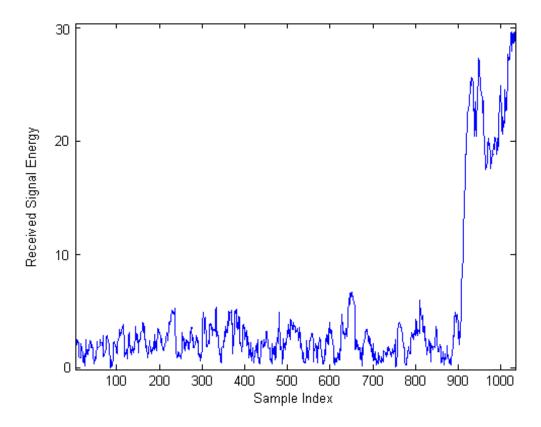

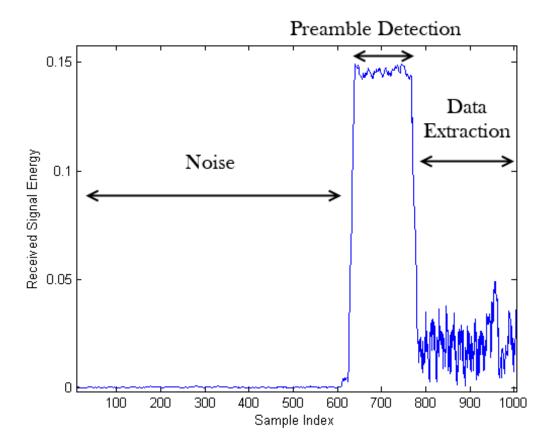

This is the simplest packet detection algorithm to find the starting edge of the received signal by simultaneously measuring incoming signal energy. According to Equation (3.5), the received signal energy  $m_n$  is the summation of received signal energy over a window of length L. In other words, the calculation of  $m_n$  is a moving sum of received signal energy also known as sliding window. Figure 3.3 depicts how synchronization is performed based on received signal energy method. Whenever the received signal energy exceeds a particular threshold point, the receiver assumes an incoming transmission is ongoing. [8]

$$m_n = \sum_{k=0}^{L-1} r_{n-k} \times r_{n-k}^* = \sum_{k=0}^{L-1} |r_{n-k}|^2$$

(3.5)

Although, the hardware implementation of this synchronization method is so simple due to running only one multiplication per sample, it requires a large memory to

Figure 3.3. Synchronization based on received signal energy

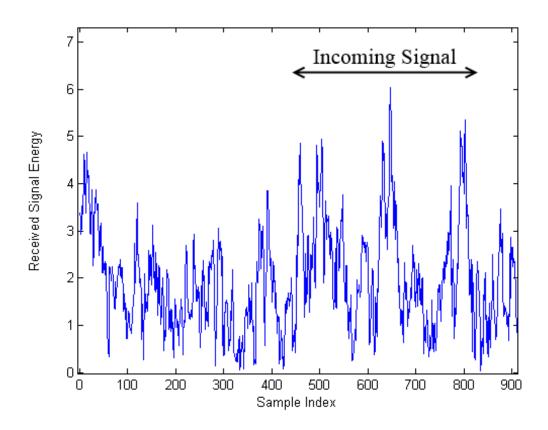

store all values of received signal. Another shortcoming is that the value of the threshold depends on the received signal energy. Therefore, it is hard for designers to set a fixed threshold value. If the value is set to high, the received signal might not be detected due to the low transmitter power; if the value is set lower than what it should be, the packet can not be detected in noisy channels due to the low Signal-to-Noise Ratio (SNR). In other words, in both scenarios the entire signal is either assumed as noise and will not be detected or lost within the noise. Figure 3.4 shows how signal is lost within the noise due to the low SNR.

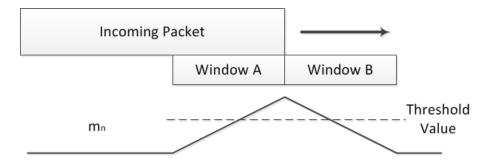

#### **Double Slide Window Packet Detection**

The basic concept of the double sliding window packet detection method is quite similar to received signal energy method. Figure 3.5 shows steps in which two sliding windows calculate the presence of any incoming packet. Based on Equations (3.6) and (3.7), In this method instead of estimating received signal energy just in one time, two sliding windows are employed to measure total energy of the incoming signal simultaneously. According to Equation (3.8), the threshold value is determined based on the maximum energy contained in both windows. [8]

Figure 3.4. Incoming signal lost within the noise due to the low SNR

Figure 3.5. Principle of double slide window packet detection

$$a_n = \sum_{m=0}^{M-1} r_{n-m} \times r_{n-m}^* = \sum_{m=0}^{M-1} |r_{n-m}|^2$$

(3.6)

$$b_n = \sum_{l=1}^{L} r_{n+l} \times r_{n+l}^* = \sum_{l=0}^{L} |r_{n+l}|^2$$

(3.7)

$$m_n = \frac{a_n}{bn} \tag{3.8}$$

As Figure 3.5 shows, when the value of  $m_n$  reaches to its maximum, it means that window A contains both signal and noise whereas window B contains only noise. Equation (3.9) shows the amount of SNR estimated at the peak level where S is the

Figure 3.6. 802.11a preamble structure [8, p. 51]

energy of signal and N is the magnitude of noise. This approach is suitable where the receiver has no prior information about when data is transmitted by the sender.

$$m_{peak} = \frac{a_{peak}}{b_{min}} = \frac{S+N}{N} = \frac{S}{N} + 1$$

(3.9)

#### Preamble Structured Packet Detection

What is Preamble: To aim synchronization process, a train of predefined bits called preamble are added to the beginning of each packet which is known by both sender and receiver. Since preamble is considered as an additional overhead to the header, its contents as well as its length must be carefully designed in order to provide significant information required for the synchronization process.

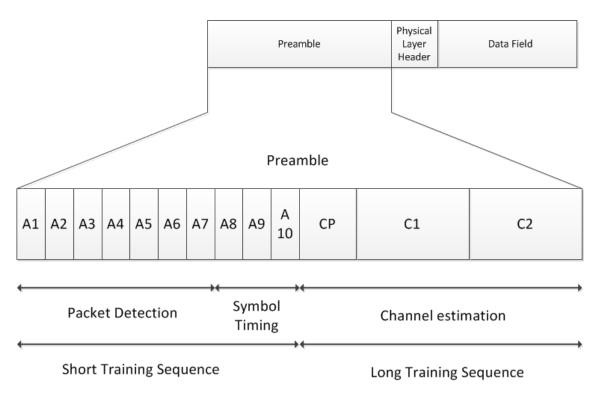

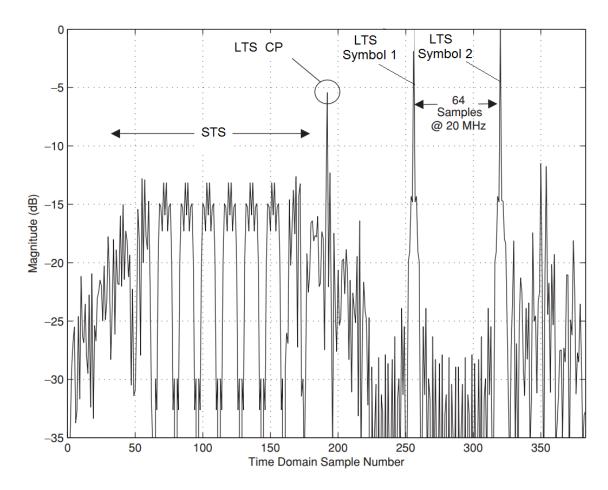

As it is shown in Figure 3.6, a preamble is composed of two major parts separated by a CP in between. First part,  $A_1$  to  $A_{10}$ , is called Short Training Symbols (STS), each of them composed of 16-bit sample. Following by, a 32-bit sample CP is inserted to compensate ISI introduced by STS. Conceptually, this CP is considered as a guard band preserving Long Training Symbols (LTS) from be distorted by channel impairments. Second part,  $C_1$  and  $C_2$ , consists of two identical 64-bit long samples known as LTS. Moreover, having this structure for the preamble, receiver is able to simply detect any incoming signal even in low SNR environments.

Overall, this method is an extension of double slide window packet technique by

Figure 3.7. Synchronization Based on preamble structured packet

taking advantage of 10 periodical STS at the beginning of each packet. Figure 3.7 illustrates how much preamble structured packet is accurate more than previous methods [8]. Equations (3.10), (3.11) and (3.12) were proposed by Schmidl and Cox in [24] and show how preamble assists synchronization, where  $c_n$  is the autocorrelation,  $p_n$  is the energy and  $m_n$  is the threshold value of the received data stream, respectively.

$$c_n = \sum_{k=0}^{L-1} r_{n+k} \times r_{n+k+D}^* \tag{3.10}$$

$$p_n = \sum_{k=0}^{L-1} r_{n+k+d} \times r_{n+k+D}^* = \sum_{k=0}^{L-1} |r_{n+k+D}|^2$$

(3.11)

$$m_n = \frac{|c_n|^2}{(p_n)^2} \tag{3.12}$$

## 3.3.2 Overview of 802.11a Packet Structure

IEEE 802.11a is the basic standard mostly used in packet systems. Therefore, an overview of the packet structure might be generalized for other standards (such as 802.16, 802.22, etc). This standard is categorized as packet-based systems. In those systems, as it has been mentioned earlier, sender splits its data into several packets and then transmits them as quick as possible. Moreover, each packet composed of preamble, data, service field, padding, etc, should be transmitted in a certain time.

This standard specifies a 2.4 GHz OFDM based operating frequency which splits signal over 64 separate subcarriers where 12 subcarriers are usually used as guard band and the 52 remaining subcarriers are employed to transmit preamble, data, etc. This operating frequency enables data transmission at a rate of 6, 9, 12, 18, 24, 36, 48, or 54 Mbps where 6, 12, and 24 Mbps data rates are mandatory. Four subcarriers out of 52 subcarriers are employed as pilot subcarriers which are references to disregard frequency-phase shifts-rotations of the signal during transmission. Remaining 48 subcarriers are used to transmit information in parallel streams in which each subcarrier is spaced by a 0.3125 MHz Subcarrier frequency spacing  $\Delta_f$  (A total of 20 MHz for 64 subcarriers). Table 3.1 shows IEEE 802.11a timing analysis [26]. According to that, receiver has only  $4\mu s$  to detect and decode the entire packet. This is one of the reasons why synchronization in OFDM is performed in time-domain.

Table 3.1. IEEE 802.11a Timing Analysis

| Index | Parameter                    | Abbreviation       | Value                                            |

|-------|------------------------------|--------------------|--------------------------------------------------|

| 0     | Total Subcarriers            | N                  | 64                                               |

| 1     | Usable Subcarriers           | $N_{ m tot}$       | 52                                               |

| 2     | Data Subcarriers             | $N_{\mathrm{D}}$   | 48                                               |

| 3     | Pilot subcarriers            | $N_{\mathrm{p}}$   | 4                                                |

| 4     | Subcarrier Frequency Spacing | $\Delta_f$         | 0.3125 MHz                                       |

| 5     | IFFT/FFT Duration            | $T_{ m FFT}$       | $3.2\mu s$                                       |

| 6     | Preamble Duration            | $T_{\mathrm{p}}$   | $16 \ \mu s(\frac{1}{\Delta_f})$                 |

| 7     | OFDM Symbol Duration         | $\mathrm{T_{sig}}$ | $4 \mu s(T_{GI} + T_{FFT})$                      |

| 8     | Guard Interval Duration      | ${ m T_{GI}}$      | $0.8 \ \mu s(\frac{T_{FFT}}{4})$                 |

| 9     | Training Symbol GI Duration  | $\mathrm{T_{GT}}$  | $1.6 \ \mu s(\frac{T_{FFT}}{2})$                 |

| 10    | Symbol Interval              | $T_{\mathrm{sym}}$ | $4 \mu s(T_{GI} + T_{FFT})$                      |

| 11    | STS Duration                 | $T_{STS}$          | $8 \mu s (10 \times (\frac{T_{\text{FFT}}}{4}))$ |

| 12    | LTS Duration                 | $T_{LTS}$          | $8 \mu s (T_{GT} + 2 \times T_{FFT})$            |

Short Training Sequence : STS is composed of ten repetitions of a 0.8  $\mu$ s symbol based on sequence given at Equation (3.13). The sequence is started from -26th subcarrier and ended to 26th subcarriers. Subcarriers -32 to -27 as well as 27 to 32 are used as the guard bands. The sequence is chosen to have good autocorrelation properties together with low PAPR. While the correlation peaks are used as an initial estimation for packet detection along with coarse frequency estimation and timing synchronization, the delayed responses degrade its throughput. Packet detection, which is achieved by correlating signal with a delayed version of itself, commonly said as autocorrelation due to the repetitive nature of STS. Frequency estimation is done by measuring in phase differences between two samples which are separated by 0.8  $\mu$ s. [25]

$$S_{-26,26} = \sqrt{\frac{13}{6}} \{ 0, 0, 1 + j, 0, 0, 0, -1 - j, 0, 0, 0, 1 + j, 0, 0, 0, -1 - j, 0, 0, 0, 0, -1 - j, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, -1 - j, 0, 0, 0, -1 - j, 0, 0, 0, 0, 1 + j, 0, 0 \}$$

$$(3.13)$$

Long Training Sequence: LTS is composed of two 3.2  $\mu$ s symbols, based on sequence given at Equation (3.14), appended by a 1.6  $\mu$ s which is a replication of the last half of the long training symbols. Hence the total length of the LTS will take 8  $\mu$ s to be transmitted. Similar to STS, LTS begins from -26th subcarrier to 26th subcarrier. LTS may be used for more precise time acquisition due to the transition between STS and LTS. LTS along with with STS are used for a more accurate fine frequency estimation. Figure 3.8 depicts how synchronization is performed using STS and LTS. [25]

Figure 3.8. Autocorrelation of the preamble [25, p.67]

## 3.4 OFDM Synchronization Steps

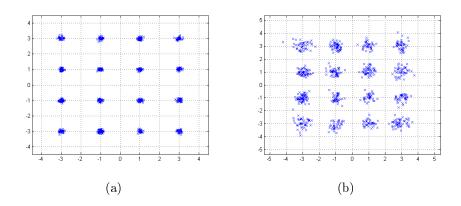

As earlier discussed, OFDM suffers from frequency-domain errors rather than timedomain errors. In that case, OFDM is vulnerable to CFO and CPE which cause  $\Delta_f$  and, subsequently,  $\phi(t)$  to the received signal. Figure 3.9 shows how existence of CFO introduces a shift of magnitude  $\Delta_f$  to the receiver in which the subcarriers lose their orthogonality with the receiver filter.

As previously mentioned, another issue which is a threat in OFDM systems is CPE. The presence of any offset in symbol timing causes phase noises. In simplest form, failure to detect the proper symbol boundaries introduces a phase noise where the constellation points are dispersed as it is illustrated in Figure 3.10.

Basically, synchronization in time-domain is performed in two phases called *coarse* symbol timing detection and fine symbol timing detection.

## 3.4.1 Coarse Symbol Timing Detection

The first phase to detect and extract the incoming signal waveform from the received signal is called coarse symbol training detection. In this regard, several methods

Figure 3.9. (a) Sampling without CFO, (b) Effect of CFO

Figure 3.10. (a) Sampling without CPE and (b) Effect of CPE.

have been proposed. Coarse symbol timing detection is achieved by using one of the following methods: [6]

#### Delay and Correlate

The very straightforward algorithm for symbol timing detection is Delay and Correlate (DC). The principle of the DC algorithm is to detect the maximum autocorrelation of the signal based on Equation (3.15), where  $z_m$  is the received time-domain signal, R is the repetition interval and L is the separation between two symbol intervals.

$$\Phi_{DC}(m) = \left| \sum_{r=0}^{R-1} z_{m-r} z_{m-r-L}^* \right|,$$

$$\hat{m}_{DC} = \arg\max_{m} \Phi_{DC}(m). \tag{3.15}$$

Although DC algorithm is simple in term of complexity, it has two major draw-backs. Firstly, the peak magnitude of  $\Phi_{DC}$  varies due to different signal powers. Secondly, when the autocorrelation of the repetitive periods is done, the edge of the correlator output, specially in noisy environments, is not dropped sharply. In other words, it will take some time for a signal to reach to its lower level from the peak.

#### Maximum Likelihood Metric

According to the Equation (3.16), principle of Maximum Likelihood (ML) algorithm is based on the assumption that the received signal is uncorrelated except for some replicas. This method is less reliable than other proposed algorithms, due to the high complexity of the hardware, which calculates magnitude of SNR ( $\rho$ ), as well as number of errors caused by bypassing SNR estimation. Equation (3.17) is an special case of ML, also known as Minimum Mean Square Method (MMSE), while magnitude of SNR is infinite.

$$\Phi_{ML}(m) = 2 \left| \sum_{r=0}^{R-1} z_{m-r} z_{m-r-L}^* \right| - \frac{\rho}{1+\rho} \sum_{r=0}^{R-1} \left( |z_{m-r}|^2 + |z_{m-r-L}|^2 \right)$$

$$\hat{m}_{ML} = \arg \max_{m} \Phi_{ML}(m). \tag{3.16}$$

$$\Phi_{MMSE}(m) = \sum_{r=0}^{R-1} |z_{m-r}|^2 + \sum_{r=0}^{R-1} z_{m-r-L}^2 - 2 \left| \sum_{r=0}^{R-1} z_{m-r} z_{m-r-L}^* \right|$$

$$\hat{m}_{MMSE} = \arg\max_{m} \Phi_{MMSE}(m). \tag{3.17}$$

#### Normalized Metrics

Schmidl and Cox in [24] proposed a group of timing detection algorithms known as preamble (which was discussed earlier). As Equation (3.18) shows, maximum  $\Phi_s(m)$  is achieved at the end of the preamble where two sequences of identical N/2 samples are used. According to [6], Minns et al. proposed a more general preamble structure consisting of U identical segments which are varied in polarization. In case of U = 4 the preamble structure is given as Equation (3.19) where A is the segment consisting of N/4 samples.

$$\Phi_s(m) = \frac{\left| \sum_{r=0}^{N/2-1} z_{m-r} z_{m-r-N/2}^* \right|^2}{\left( \sum_{r=0}^{N/2-1} |z_{m-r}|^2 \right)^2}$$

(3.18)

$$\begin{bmatrix} -A & A & -A & -A \end{bmatrix} \tag{3.19}$$

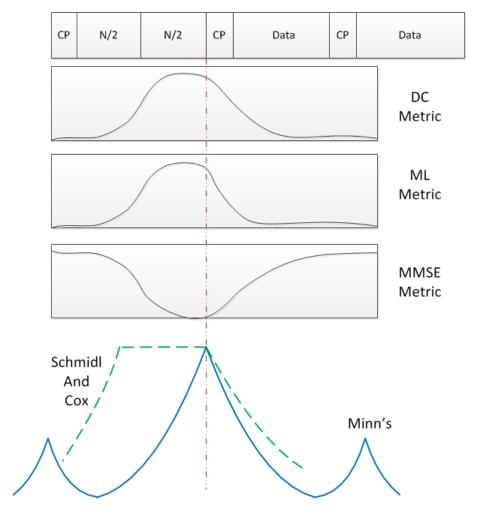

As it is illustrated in Figure 3.11, a common phenomenon, which is the existence of a wide plateau, appears in all DC,ML,MMSE and in Schmidl's algorithms to some extent. When the number of identical preambles exceeds more than two segments, for example STS repetition in 802.11a, a wide plateau is created at the correlator output. Theoretically, this plateau indicates an ISI-free region to the FFT. In reality, additive noise widens the area of plateau. In that case, it is worth mentioning that the longer period in preamble, the larger FFT window, the more accurate detection. Eventually, Minn's algorithm defers any plateau and has a sharp peak in its metric. [6]

## 3.4.2 Fine Symbol Timing Detection

As it is discussed in previous section, coarse symbol timing detection algorithms are only able to obtain timing information out of the received signal approximately. Thus, large timing errors might still exist. Therefore, in order to obtain accurate timing, another precise approximation is required which is called fine symbol timing detection. [6]

As previously said, *TIME* is a crucial issue in packet-based systems. Therefore, ISI-free DFT window should be prepared as soon as possible to perform channel estimation and packet header extraction in next steps. If fine symbol timing detection is not acquired in time, additional delay lines should be considered to buffer the input signal. Similar to coarse symbol timing detection algorithms, there are few

Figure 3.11. Coarse symbol timing detection algorithms

algorithms proposed to obtain fine symbol timing detection as following

#### Time-domain Cross Correlation

Usually, fine symbol timing detection, in order to obtain Channel Impulse Response (CIR), is performed by matching time-domain received signal with a preamble waveform. In other words, instead of autocorrelating a noisy received waveform with a delayed version of itself, which is apparently noisy as in coarse symbol timing detection algorithms, a clean preamble waveform is correlated with the noisy received signal. The optimal timing estimation can be obtained according to Equations (3.20) and (3.21) where Q is the total length of preamble and  $p_q$  denotes the preamble samples. As a new approach, a threshold point can be set considering correlator which responses to any magnitude greater than the threshold point. [6]

$$\Phi_{zp}(m) = \sum_{q=0}^{Q-1} z_{m+q} P_q^*$$

(3.20)

$$\hat{m}_{MAX} = \arg\max_{m} \Phi_{zp}(m) \tag{3.21}$$

#### Frequency Response Estimate

Another approach is to perform an IFFT in order to extract CIR information. According to Equation (3.22), CIR  $\hat{\mathbf{h}} = [\hat{h}_{-N/2}\hat{h}_{N/2+1}\dots\hat{h}_{N/2-1}]$  can be obtained, where  $\mathbf{F}^{-1}$  denotes an  $N \times N$  IFFT matrix,  $\mathbf{z}$  is a set of received frequency domain subcarriers and  $\mathbf{X}$  is a diagonal matrix whose *i*th diagonal element is the transmitted signal at *i*th subcarrier. Once  $\hat{h}_m$  exceeds a predefined threshold, m is considered as the symbol timing. Since IFFT requires extra operations, a long latency is introduced in this case.

$$\hat{\mathbf{h}} = \mathbf{F}^{-1} \times \mathbf{X}^{-1} \times \mathbf{z} \tag{3.22}$$

#### Frequency-Domain Phase Shift

Conceptually, adjacent subcarriers suffer from similar channel fading. Useful information for fine symbol timing detection are only provided if the effect of channel fading is compensated. According to Equation (3.23), symbol timing offset  $\hat{m}_{PS}$  is obtained where  $\angle(.)$  is the phase of complex number,  $Z_k$  is the received frequency-domain signal and  $X_k$  is the transmitted frequency-domain signal of the kth subcarrier. [6]

$$\hat{m}_{PS} = \frac{N}{2\pi} \angle \left( \sum_{k} (Z_{k+1} Z_k^*) (X_{k+1} X_k^*)^* \right)$$

(3.23)

Nevertheless, all fine symbol timing detection algorithms can not handle received signals with large CFO. Therefore, before using these algorithms, CFO must be compensated in advance.

## 3.5 NC-OFDM Systems

NC-OFDM is a promising technique in CR systems to avoid any interference with the primary user, in which only unused subcarriers are employed to be transmitted. In NC-OFDM based CR systems, secondary transmitter instead of using a set of contiguous subbands might employ a variety of non-contiguous subbands due to the licensed user activities.

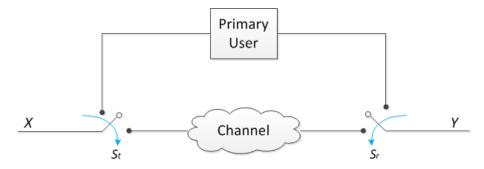

According to [27] in NC-OFDM systems, each subchannel is modeled as a two-switch channel in which the switch will open as soon as a primary user is detected. Figure 3.12 depicts how a subchannel is employed as a two-switch channel model.

Figure 3.12. Two switch channel model

This approach can be explained considering Equation (3.24) where signals X and Y are transmitted and received signal, respectively; N denoted as AWGN,  $S_t$  and, subsequently,  $S_r$  are transmitter and receiver switches  $\in \{0, 1\}$ . Therefore, it might happen that the sender and the receiver experience different wireless environment and, consequently, there is no guarantee that a subband occupied for secondary transmission still stays synchronized [28].

$$Y = (XS_t + N)S_r (3.24)$$

## 3.5.1 NC-OFDM synchronization issues

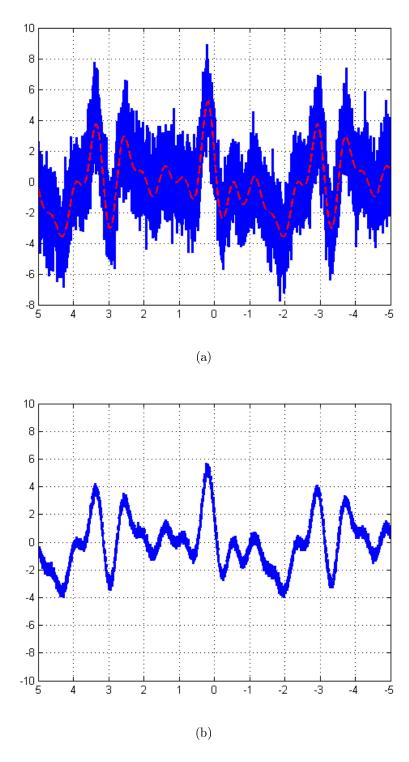

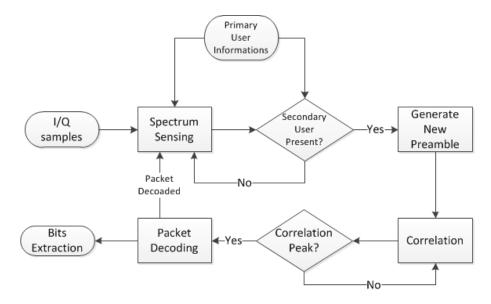

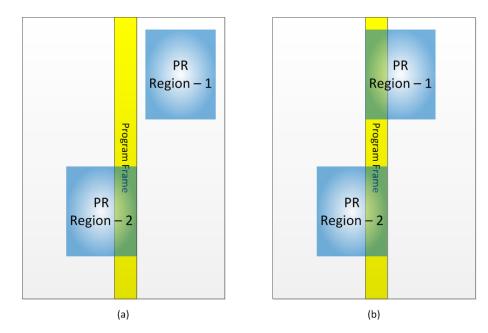

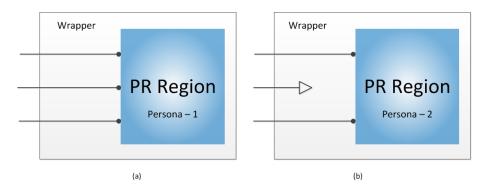

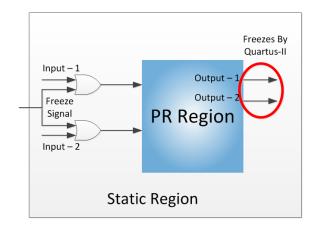

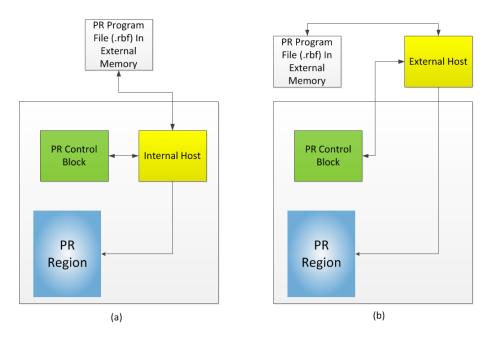

Theoretically, synchronization in OFDM systems can be done either in time-, frequency-domain or both. In reality, the reason why most of the OFDM systems prefer to perform synchronization in time-domain is lack of time due to the packet-based system nature. As soon as the receiver is powered up, it should start autocorrelating and crosscorrelating on received waveform to extract useful information using preamble structure.