# JAN LIPPONEN DATA TRANSFER OPTIMIZATION IN FPGA BASED EMBEDDED LINUX SYSTEM

Master of Science Thesis

Examiner: D.Sc. Timo D. Hämäläinen Examiners and topic approved by the Dean of the Faculty of Computing and Electrical Engineering on 30th November 2017

## **ABSTRACT**

**JAN LIPPONEN**: Data transfer optimization in FPGA based embedded Linux system

Tampere University of technology

Master of Science Thesis, 69 pages, 10 Appendix pages

May 2018

Master's Degree Programme in Electrical Engineering

Major: Embedded Systems

Examiner: D.Sc. Timo D. Hämäläinen

Keywords: SoC, embedded Linux, FPGA, DMA, data transfer

The main goal of this thesis was to optimize the efficiency of data transfer in an FPGA based embedded Linux system. The target system is a part of a radio transceiver application receiving high data rates to an FPGA chip, from where the data is made accessible to a user program using a DMA operation utilizing Linux kernel module. The initial solution, however, used excessive amounts of CPU time to make the kernel module buffered data accessible by the user program. Further optimization of the data transfer was required by upcoming phases of the project.

Two data transfer optimization methods were considered. The first solution would use an architecture enabling the FPGA originating data to be accessed directly from the user program via a data buffer shared with the kernel. The second solution utilized a DMAC (DMA controller) hardware component capable of moving the data from the kernel buffer to the user program. The second choice was later rejected due to high platform dependency on such an implementation.

A working solution, for the shared buffer optimization method, was found by going through Linux memory management related literature. The implemented solution uses the *mmap* system call function to remap a kernel module allocated data buffer for user program access. To compare the performance of the implemented solution to the initial one, a data transfer test system was implemented. This system enables pre-defined data to be generated in the FPGA with varying data rates. It was shown in the performed tests that the maximum throughput was increased by ~25% (from ~100 MB/s to ~125 MB/s) using the optimized solution. No exact maximum data rates were discovered because of a test data generation related constraint.

The increase in throughput is considered as a significant result for the radio transceiver application. The implemented optimization solution is also expected to be easily portable to any Linux system.

## TIIVISTELMÄ

JAN LIPPONEN: Datasiirron optimointi FPGA mikropiiriin pohjautuvassa sulautetussa Linux-järjestelmässä

Tampereen teknillinen yliopisto

Diplomityö, 69 sivua, 10 liitesivua Toukokuu 2018

Sähkötekniikan diplomi-insinöörin tutkinto-ohjelma

Pääaine: Sulautetut järjestelmät

Tarkastaja: D.Sc. Timo D. Hämäläinen

Avainsanat: SoC, sulautettu Linux, FPGA, DMA, datasiirto

Tämän diplomityön tavoitteena oli optimoida datasiirron tehokkuus FPGA-mikropiiriin perustuvassa sulautetussa Linux-järjestelmässä. Työn kohdejärjestelmä on osa radiovastaanotin -sovellusta, joka vastaanottaa suuria määriä dataa FPGA- mikropiirille. FPGA:lta data tehdään käyttäjäohjelman hyödynnettäväksi käyttäen oikosiirtoa (DMA) hyödyntävää Linux-ytimen laiteohjainta. Alkuperäinen toteutus käytti kuitenkin suuren määrän suoritinaikaa tämän datan viemiseen laiteohjaimelta käyttäjäohjelmalle ja projektin tulevat vaiheet vaativat datasiirron optimointia.

Työssä päätettiin tutkia kahta eri optimimointimenetelmää. Ensimmäinen ratkaisu käyttäisi arkkitehtuuria, joka mahdollistaisi FPGA:lta lähtöisin olevan datan käytön suoraan käyttäjäohjelmassa Linux-ytimen kanssa jaetun datapuskurin kautta. Toinen ratkaisusuunnitelma hyödynsi DMAC (oikosiirto-ohjain) komponenttia, joka kykenee toteuttamaan datan siirron laiteohjaimelta käyttäjäohjelmalle. Tämä ratkaisumalli kuitenkin myöhemmin hylättiin sen aiheuttaman laitteistoriippuvuuden takia.

Toimiva ratkaisumalli jaetulle datapuskurille löytyi käymällä läpi Linuxin muistinhallintaa käsittelevää kirjallisuutta. Toteutettu ratkaisu hyödynsi *mmap* systeemikutsua Linuxin ytimessä varatun muistipuskurin muokkaamiseksi käyttäjäohjelmasta hyödynnettäväksi. Toteutetun ja alkuperäisen ratkaisun suorituskykyjen vertaamista varten toteutettiin datasiirto-testijärjestelmä. Tämä järjestelmä mahdollistaa ennalta määritetyn datan tuottamisen FPGA:lla vaihtelevilla siirtonopeuksilla.

Toteutetuissa testeissä todennettiin, että järjestelmän maksimaalinen tiedonsiirtonopeus kasvoi noin 25 prosenttia (~100 megatavusta sekunnissa ~125 megatavuun sekunnissa) käyttäen optimimoitua ratkaisua. Tarkkoja maksimaalisia tiedonsiirtonopeuksia ei pystytty todentamaan testidatan tuottamiseen liittyvän rajoituksen takia.

25 prosentin lisäys maksimaaliseen tiedonsiirtonopeuteen nähtiin kohdejärjestelmän kannalta merkittävänä tuloksena. Toteutetun optimimointiratkaisun odotetaan myös olevan helposti vietävissä mihin tahansa Linux-järjestelmään.

#### **PREFACE**

In spring 2017, I received an email seeking for embedded developers to work in a project described as an "engineer's dream" by our embedded segment manager. Little did I knew what would come when I clicked the "reply" button. I am grateful that I was given the opportunity by Wapice Ltd to be part of this project and to learn from the best. At the time, Xilinx technologies, the Yocto Project and Linux kernel module development were new things to me, but under the guidance of Jouko Haapaluoma I gained high-level knowledge on all these areas.

This thesis is highly grounded on the knowledge gained from the "engineer's dream" and I want to express my gratitude to all parties involved in the project that has taken me from the depths of the Linux kernel to shores of Hailuoto – both being places I have never been in before. This project has given me the courage to call myself an embedded software developer.

Tampere, 22.5.2018

Jan Lipponen

# **CONTENTS**

| 1. | INTR                    | RODUCT                        | [ION                            | 1  |  |  |

|----|-------------------------|-------------------------------|---------------------------------|----|--|--|

| 2. | LINU                    | LINUX ON EMBEDDED SYSTEMS     |                                 |    |  |  |

|    | 2.1                     | Embedded system features      |                                 |    |  |  |

|    | 2.2                     | Choosing between OS and no-OS |                                 |    |  |  |

|    | 2.3                     | Linux features                |                                 |    |  |  |

|    | 2.4                     | Linux 1                       | hardware abstraction            | 8  |  |  |

|    |                         | 2.4.1                         | Address spaces                  | 9  |  |  |

|    |                         | 2.4.2                         | Process/kernel model            | 10 |  |  |

| 3. | LINUX DEVICE DRIVERS    |                               |                                 |    |  |  |

|    | 3.1                     | Modules                       |                                 |    |  |  |

|    | 3.2                     | Device and driver types       |                                 |    |  |  |

|    | 3.3                     | Interrupt handling            |                                 |    |  |  |

|    | 3.4                     | Memor                         | ry allocation                   | 16 |  |  |

|    |                         | 3.4.1                         | Slab layer                      | 17 |  |  |

|    |                         | 3.4.2                         | kmalloc()                       | 19 |  |  |

|    |                         | 3.4.3                         | vmalloc()                       | 20 |  |  |

|    |                         | 3.4.4                         | ioremap()                       | 21 |  |  |

|    | 3.5                     | Direct                        | memory access                   | 21 |  |  |

|    |                         | 3.5.1                         | DMA Mapping                     | 22 |  |  |

| 4. | FPGA BASED SOC-PLATFORM |                               |                                 |    |  |  |

|    | 4.1                     | Field p                       | rogrammable gate arrays         | 25 |  |  |

|    |                         | 4.1.1                         | FPGA comparison to other ICs    | 25 |  |  |

|    |                         | 4.1.2                         | General FPGA architecture       | 26 |  |  |

|    |                         | 4.1.3                         | FPGA clocking                   | 30 |  |  |

|    |                         | 4.1.4                         | FPGA programming                | 30 |  |  |

|    | 4.2                     | Xilinx                        | Zynq-7000 devices               | 31 |  |  |

|    |                         | 4.2.1                         | 8                               |    |  |  |

|    | 4.3                     | FPGA based DMA transfer       |                                 |    |  |  |

| 5. | DAT                     | DATA TRANSFER OPTIMIZATION    |                                 |    |  |  |

|    | 5.1                     | Test sy                       | stem components                 | 36 |  |  |

|    |                         | 5.1.1                         | Sample generator                | 38 |  |  |

|    | AXI4-                   |                               | Stream interface                | 40 |  |  |

|    |                         | 5.1.2                         | Vivado design with AXI DMA core | 44 |  |  |

|    |                         | 5.1.3                         | AXI DMA cyclic module           | 47 |  |  |

|    |                         | 5.1.4                         | DMA test program                | 51 |  |  |

|    | 5.2                     | Sequer                        | nce diagram and analysis        | 54 |  |  |

|    |                         | 5.2.1                         | Performance                     |    |  |  |

|    | 5.3                     | Data tr                       | ansfer optimization methods     | 55 |  |  |

|    |                         | 5.3.1                         | Coherent DMA buffer             | 56 |  |  |

|    |                         | 5.3.2                         | mman implementation             | 58 |  |  |

| 6.                                            | EXPERIMENTS AND ANALYSIS                         | 63 |  |  |  |  |

|-----------------------------------------------|--------------------------------------------------|----|--|--|--|--|

|                                               | 6.1 TLAST positioning test                       | 64 |  |  |  |  |

|                                               | 6.2 Performance test                             | 66 |  |  |  |  |

| 7.                                            | CONCLUSIONS                                      | 68 |  |  |  |  |

| 8.                                            | BIBLIOGRAPHY                                     | 70 |  |  |  |  |

|                                               |                                                  |    |  |  |  |  |

| APPENDIX A: The sample clock generator module |                                                  |    |  |  |  |  |

| APPENDIX B: The counter data generator module |                                                  |    |  |  |  |  |

| APPENDIX C: The sample generator module       |                                                  |    |  |  |  |  |

| APF                                           | PENDIX D: AXI DMA platform device probe function |    |  |  |  |  |

| APF                                           | PENDIX E: AXI DMA callback and read functions    |    |  |  |  |  |

# LIST OF FIGURES

| Figure 1.  | A generic embedded system structure, adapted from [1, p. 12]        | 4  |  |

|------------|---------------------------------------------------------------------|----|--|

| Figure 2.  | High-level overview of the Linux system structure, adapted from [7, |    |  |

|            | p. 6]                                                               | 9  |  |

| Figure 3.  | Application program-process relation, context switches and a        |    |  |

|            | hardware interrupt                                                  | 11 |  |

| Figure 4.  | The slab allocator interfacing the slab layer subsystem, adapted    |    |  |

|            | from [10, p. 247]                                                   | 18 |  |

| Figure 5.  | The general purpose caches of an ARM based Linux system             | 19 |  |

| Figure 6.  | Functional block diagram of a typical SoC circuit, adapted from     |    |  |

|            | [13, p. 4]                                                          | 24 |  |

| Figure 7.  | General FPGA structure, adapted from [16, p. 3]                     | 27 |  |

| Figure 8.  | A simplified LC element, adapted from [14, p. 74]                   |    |  |

| Figure 9.  | A Boolean function represented by graphical logic gates             |    |  |

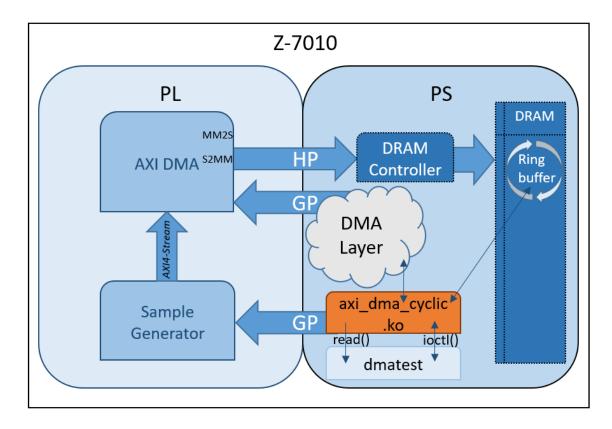

| Figure 10. | The implemented DMA test system on a Z-7010 based MicroZed          |    |  |

|            | board                                                               | 37 |  |

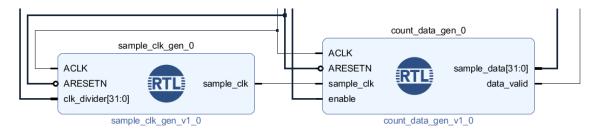

| Figure 11. | The sample generator submodules as graphical blocks                 | 39 |  |

| Figure 12. | An AXI4-Stream wave diagram with 5 signals and counter data         |    |  |

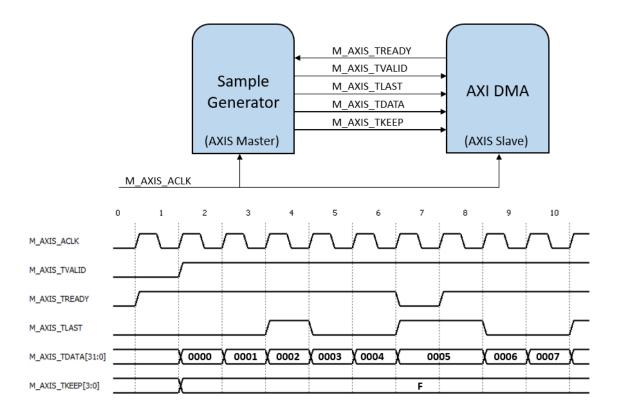

|            | payload, adapted from [24, p. 86]                                   | 41 |  |

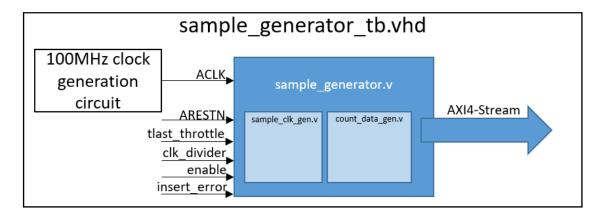

| Figure 13. | The sample generator test bench simulation showing the AXI4-        |    |  |

|            | Stream protocol circuit output                                      | 43 |  |

| Figure 14. | Clock division wave diagram                                         | 44 |  |

| Figure 15. | The DMA test system as Vivado block design                          | 46 |  |

| Figure 16. | The Vivado's address editor tab associated with the test system     | 47 |  |

| Figure 17. | Illustration of a DMA ring buffer with concurrent writer and a      |    |  |

|            | reader                                                              | 50 |  |

| Figure 18. | The DMA test system control sequence diagram                        | 54 |  |

| Figure 19. | The discussed data transfer optimization methods                    |    |  |

| Figure 20. | The TLAST positioning test results using 22.222 MB/s data rate      | 65 |  |

| Figure 21. | The performance test results                                        | 66 |  |

### LIST OF ABBREVIATIONS

ACP Accelerator coherency port

AMBA Advanced microcontroller bus architecture

API Application programming interface ASIC Application-specific integrated circuit ASSP Application-specific standard part AXI Advanced eXtensible interface AXI GP AXI general purpose interface AXI HP High-performance AXI port BRAM Block random-access memory **CLB** Configurable logic blocks

CPLD Complex programmable logic device

CPU Central processing unit

DLL Digital delay-locked loop

DMA Direct memory access

DMAC Direct memory access controller DRAM Dynamic random-access memory

DSP Digital signal processor / digital signal processing EEPROM Electrically erasable programmable read-only memory

FIFO First in, first out

FPGA Field programmable gate array

GB Gigabyte (10<sup>9</sup> bytes)

GiB Gibibyte (2<sup>30</sup> bytes)

GP General purpose

GPIO General purpose input/output GPL GNU general public license HDL Hardware description language

HP High-performance

I/O Input/output

IC Integrated circuit

IOCTL Input/output control

IOMMU Input/output memory management unit

IoT Internet of things

IP Intellectual property

IRO Interrupt request

ISA Industry standard architecture ISR Interrupt service routine

LC Logic cell

LE Logic element

LUT Lookup table

MAC Multiply and accumulate

MIPS Millions of instructions per second

MM2S Memory-mapped to stream

mW Milliwatt

OCM On chip memory

OS Operating system

PC Personal computer

PCI Peripheral component interconnect

PL Programmable logic

PLD Programmable logic device

PLL Phase-locked loop PS Processing system

RAM Random-access memory ROM Read-only memory

S2MM Stream to memory-mapped SCSI Small computer system interface

SoC System on a chip

SPARC Scalable processor architecture SRAM Static random-access memory TCP Transmission control protocol

UDP User datagram protocol USB Universal serial bus

VHDL VHSIC hardware description language

## 1. INTRODUCTION

Embedded systems are everywhere and as technology advances devices powerful enough running a full operating system, such as Linux, become available to low cost applications. One of the biggest motivations in using an OS (operating system) in embedded applications is their networking capabilities. Embedded systems often interact with other systems through networking interfaces, or through internet, but implementing a hardware dependent bare metal networking software is often undesirable. Linux is a well-supported open source operating system kernel distributed under GNU General Public License version 2, making it an adjacent choice to many embedded applications.

Linux based systems are usually built respecting the kernel space / user space division; the kernel space software entities interacting with system hardware, the device drivers, are separated from user space applications. Eventually, this creates a need for transferring data from kernel space to user space. A system using a camera module could work in this manner; if a user application should request a picture frame from a camera peripheral, it cannot interface the camera peripheral directly, but sends a request for the kernel. The kernel then takes care of the transaction with the camera module via a device driver, after which the frame is transferred to the requesting user application.

Applications performing high amounts of data transfer between the kernel space and the user space can produce high stress on the system processor, thus limiting the achievable data rate to/from a user application. This was the scenario in a customer project at Wapice Ltd. The customer's radio transceiver application was producing high amounts of data from an FPGA chip to a kernel space allocated buffer using a FPGA implemented DMA controller. It was initially known, that transferring this data from the kernel space allocated buffer to a user space application was the bottleneck of the system and optimizing this step was the goal of this thesis.

Two kernel space to user space data transfer optimization possibilities were initially decided to be implemented; one with a shared data buffer enabling the FPGA originating data to be accessed straight from a user space application, and one using a DMAC hardware component capable of this data transfer on behalf of the system processor. The latter was later rejected because of high platform dependency of such an implementation.

To implement such advanced data transfer scheme, comprehensive studies on Linux kernel related topics was carried out. In Chapters 1-3 the reader is introduced to embedded Linux systems and the essential parts of memory management and DMA operation theory

are presented to create grounds for an optimization implementation. In Chapter 4 the FPGA technology is discussed and the reader is familiarized with the target device architecture. A data transfer test system is then constructed in Chapter 5 and a data transfer optimization implementation is introduced. An optimization method is then tested and the results are analyzed in Chapter 6. Finally, the Chapter 7 concludes the thesis.

# 2. LINUX ON EMBEDDED SYSTEMS

An embedded system can be defined as a combination of system hardware, software and additional mechanical or electronic components designed to fulfill a predefined task. Couple of examples of such systems are an electric toothbrush and a microwave oven. These devices are widely used in society by millions of users, but few come to think that there is a CPU running software behind their operation. A contrast to an embedded system is a PC (personal computer), also known as general-purpose computer, which does not have any predefined task and the final operation of the machine is up to the end user of each device. [1, p. 9]

Very often an embedded system is part of a larger system; one embedded system might be in charge of controlling the brakes of a modern car while another displays the fuel level on the dashboard and third controls the electronic fuel injection. Subsystems within a larger system may – or may not – be aware of each other. In the given example one can easily reason that the fuel injection should be cut off when a driver hits the breaks but this should not affect the fuel level display. [1, p. 9]

Typically, when talking about computer systems, one tends to think about PCs and widely used PC operating systems (OS) such as Windows and macOS, the market leaders of desktop operating systems, but an embedded system may lack of OS entirely because of low hardware capabilities [2]. Many embedded applications do not need an OS to fulfill their purpose; software needed to operate an electric toothbrush may be simple enough to run without OS services like task scheduling, memory management or hardware abstraction. This situation can, however, change if the toothbrush needs provide networking capabilities, like some wireless communication interface.

This chapter introduces the reader to some general features found in embedded systems, introduces the motivation in the use of a well-known operating system and finally takes a brief look into Linux kernel architecture aspects important for the rest of the thesis.

# 2.1 Embedded system features

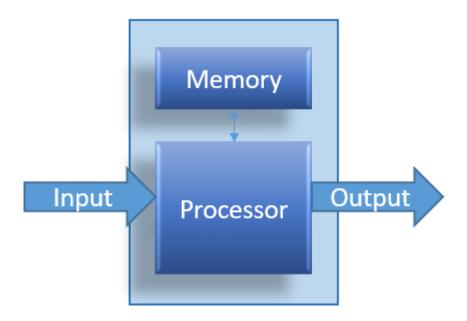

All embedded systems including software also contain a processor, ROM (read-only memory), where the executable code is stored, and RAM (random-access memory) for runtime data manipulation by the processor. One or both of these memory types may be external memory chips depending on the systems memory demands. An embedded system also contains some sort of I/O (input/output), like pushbuttons (input) leading to desired function of a MP3 player and sound coming out of the headphones (output). [1]

The input of a system could also be a sensor, a touch screen or a data link from another system – or combination of any of these. The system output usually goes to a display or to another system via a data link or the output makes changes to the physical world. So far, we can illustrate a generic embedded system with a block diagram seen in the Figure 1. [1, p. 12]

*Figure 1.* A generic embedded system structure, adapted from [1, p. 12].

The block diagram seen in Figure 1 is also eligible to describe the working of a PC, but it should be emphasized that embedded systems are designed to function with some specific kind of I/O to perform some predefined task, in contrast to PC's virtually unlimited use cases with alternating amount of I/O peripheral devices. Every unique embedded system must meet different kind of design constraints and especially commercial products have trade-offs between production cost and other desirable attributes like processing power and memory capacity [1, p. 14]. The production cost can be one of many design requirements an embedded system must meet.

Common embedded system design features with requirements include [1, pp. 14-15]:

#### 1. Processing power

The maximum workload that the main chip needs to handle. One way to measure the processing power of a processor is the MIPS (millions of instructions per second) rating. Another important feature is the processor's *word length* that can range from 4 to 64 bits. Many embedded systems are built with cheaper 4-, 8- and 16-bit word length processors.

## 2. Memory capacity

The amount of memory needed to hold the executable software and the data

used to produce the output data. The output data may not be continuously exported from the system, but can also be written to a long term memory for later export.

#### 3. Number of units

The amount of units expected to be produced. This affects the production cost and development cost trade-off. It may not be cost-effective to develop custom hardware for a low-volume product, for example.

#### 4. Power consumption

The amount of power the device needs for its operation. This is especially important for battery powered devices. Power consumption can also affect device features like heat production, device weight, size and mechanical design.

#### 5. Development cost

The cost of hardware and software engineering.

#### 6. Production cost

The cost of system hardware production.

### 7. Lifetime

The required time for a device to stay operational.

## 8. Reliability

The operational reliability of a system. For example, it is not necessarily unacceptable for your toothbrush to have a minor malfunction every now and then, but your car's brakes ought to be working 100 percent of the time.

In addition to these common requirements an embedded system faces functional requirements that gives the system its unique identity. [1, p. 16] After all the common and functional requirements of a system have been specified, a system designer needs to architect the implementation. One important design choice is between including an operating system or not.

# 2.2 Choosing between OS and no-OS

It is common for system designers to initially think that a design solution without an operating system, often called as a "no-OS" or as a "bare metal" system, is lighter, and thereby faster, and more robust than a system with an OS [3]. Functionality of the first operating systems was just to virtualize the system hardware with a collection of hardware controlling routines. This enabled easier development of software and still today every functionality of any system is possible to be implemented with a bare-metal application

[1]. Therefore, it is simple to conclude that an operating system produces unnecessary memory footprint and that it cannot introduce as high performance as a bare metal solution would. However, it was showed in white paper (WP-01245-1.0) by Altera Corporation that with modern technologies this is not necessarily the case [3].

High performance and low jitter are especially important qualities in *real-time* systems where failure to meet a jitter deadline can result in severe outcomes like injury or death. In 2014, Altera Corporation published a white paper comparing real-time performance between a hand-optimized bare-metal and a high-level operating system solutions using Cyclone V SoC (system on a chip) including an ARM Cortex-A9 processor. It was showed in the white paper that, given the complexities of a modern multi-core application processor, the bare-metal solution did not introduce any performance advantage compared to the OS based solution. It was also noticed that it is remarkably difficult to create optimized bare-metal solution, for such a modern processor, without the use of a modern OS. [3]

In the terms of performance, most operating systems are developed to take full advantage of multiple different processor architectures and it saves time not be obligated to redevelop optimized bare-metal solutions [3]. One of these OS provided processor architecture depended services is called *scheduling*. Scheduling enables execution of multiple programs seemingly in parallel even with a unicore processor [1]. With a unicore processor the programs are actually executed in turns scheduled by the operating system scheduling algorithm.

A bare-metal solution may still be a good choice for simple enough applications but as the complexity grows beyond that of a LED blinker or an electric toothbrush the OS based solution is usually a better choice [1]. Well known operating systems offer wide software support for variety of different devices and, in the best case scenario, the hardware of the used platform may already be fully abstracted by the OS offered device drivers. By using a proven OS the system designer may concentrate on system-level optimization [3].

When choosing between a bare-metal solution and an OS based solution, the system designer should consider all the system related constraints from hardware requirements to application complexities. Another important service offered by many operating systems is the *networking stack*, needed for communications between computer systems, and is often not desirable to be implemented from scratch [1]. One operating system with such capability is Linux. The Linux OS supports in addition to traditional internet protocols, such as TCP (transmission control protocol) and UDP (user datagram protocol), many other interconnection options enabling communications between all conceivable computers and operating systems [4, p. 733]. This is one of the reasons Linux is found in millions

-

<sup>&</sup>lt;sup>1</sup> Systems that have to respond to an external input within a finite and specified time period [6, p. 12]. Further real-time system characteristics are out of scope of this thesis.

of devices working in wide range of different tasks from wristwatches to mainframe computers [4, p. 1].

#### 2.3 Linux features

Linux is a member of Unix-like operating systems and it was originally developed by Linus Torvalds in 1991 for IBM-compatible personal computers with Intel 80386 microprocessors. Over the years hundreds of developers have worked with Linux in order to make it available on multiple processor architectures such as Hewlett-Packard's Alpha, Intel's Itanium, AMD's AMD64, PowerPC and IBM's zSeries. One of major benefits of Linux is that its source code is distributed under GNU General Public License (GPL) and is open to everyone. Linux includes the features of modern Unix OS such as a virtual file system and virtual memory, lightweight processes, Unix signaling, support for symmetric multiprocessor systems, and so on. [5, pp. 1-2]

The Linux kernel has multiple favors in comparison to many of its commercial competitors [5, pp. 4-5]:

- Linux is cost-free

It is possible to install the whole system just with the cost of hardware.

- Linux is fully customizable Compilation options enable customization of the kernel by choosing just needed features. Furthermore, thanks to GPL, the kernel source code itself can be modified.

- Linux runs on inexpensive, low-end hardware platforms

It is possible to implement a network server with a system based in the Intel 80386 with only 4 MB of RAM.

- Linux is powerful

Linux has been developed to be highly efficient and many design choices have been rejected because of their negative impact on performance.

- Linux is stable

Linux systems have a very low failure rate and maintenance time.

- Linux kernel can be very small and compact

The Linux kernel and some system programs used in this thesis only need 9.76 MB of memory without any particular image size optimization.

- Linux is highly compatible with other operating systems

Linux is able to mount filesystems, for example, from Microsoft Windows, Mac OS X, Solaris and SunOS. Linux supports multiple network layers and using suitable libraries it can run some programs originally not written for Linux.

## Linux is well supported

Linux community serves back questions usually within hours after sending them to newsgroups / mailing lists and new hardware drivers are often made available within couple of weeks after new hardware products are introduced to the market.

An operating system build on top of the Linux kernel is called a *Linux distribution* and all the distributions have their strengths and weaknesses in the target hardware and application. Different distributions include different kind of a set of system software depending on the target platform and the user preference. AsteriskNOW, for example, is a functionally specialized distribution developed to enable the user to easily create a voicemail or a FAX server. The best known general desktop distributions, like Ubuntu and Debian, are not well suited for embedded systems and it is more typical to use a platform specialized distribution, or to build a custom one. [6, pp. 923-925]

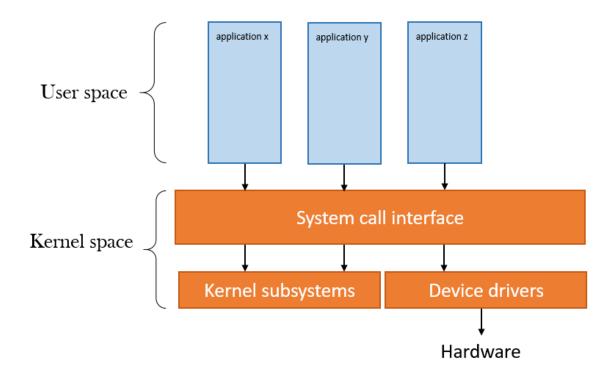

### 2.4 Linux hardware abstraction

In some operating systems it is allowed for the user software to directly access the system hardware but in Unix-like operating systems, such as Linux, this is restricted and the OS hides the physical components from the user. When a user application needs to access a hardware resource it requests this from the operating system and if the request is granted by the OS kernel, it interacts with the hardware on behalf of the application. A request for the kernel is called a *system call*. [5, pp. 8, 11] This basic structure of a Linux system can be illustrated with Figure 2. To understand the role of a system call we first need to take a look into how Linux handles memory address spaces and how programs are run in a Linux system.

Figure 2. High-level overview of the Linux system structure, adapted from [7, p. 6].

## 2.4.1 Address spaces

The word length of a CPU determines the maximum of manageable *address space*. For example, with a word length of 32-bits there is  $2^{32}$  bytes = 4 GiB (Gibibyte) of manageable memory. The conventional units, such as GB (Gigabyte) =  $10^9$  bytes, are not usable for precise description because they are concluded from decimal powers [4, p. 7]. However, the conventional units are used throughout this thesis for better readability and because it is a custom to use the conventional units when measuring data transfer speed with *bit rate*, defined in ISO/IEC 2382:2015 standard as bits per second [7].

The address space is not actually related to the amount of physical RAM used in the system and therefore it is known as the *virtual address space*. In Linux, the virtual address space is divided in the *user space* and in the *kernel space* with an architecture dependent ratio so that the user space extends from 0 to TASK\_SIZE – an architecture specific constant. In 64-bit machines this may be more complicated because it is common to use less than 64 bits for addressing to actually manage their enormous potential virtual address space. The amount of address space will still be more than the amount of physical RAM. Both the physical memory and the virtual address space are divided in equal size portions called *pages*. The physical pages are usually referred to as *page frames* so that the word *page* is reserved to describe the virtual memory pages. [4, pp. 8, 10, 11]

The kernel and CPU handles the relation between virtual address space and physical memory by allocating virtual addresses to physical addresses via *page tables*. The virtual

memory pages are said to be *mapped* to physical page frames and this addressing information is then stored to the page tables. The simplest implementation for a page table structure would be an array with entries for each page pointing to an associated page frame. Page tables are actually more complicated but further architecture behind the page tables is out of scope of this thesis. [4, pp. 8, 10, 11]

Although a Linux system uses the same RAM for storing the kernel code (managing the system hardware) and for the user applications, it is possible to restrict the user applications from performing hardware access with a simple rule: code that is stored in user space is never allowed to read or to manipulate data stored in kernel space. The user space applications still need to be able to somehow use hardware recourses. All modern processors introduce different kind of privilege levels for code execution and this is exploited in the *process/kernel* model. [9, p. 8]

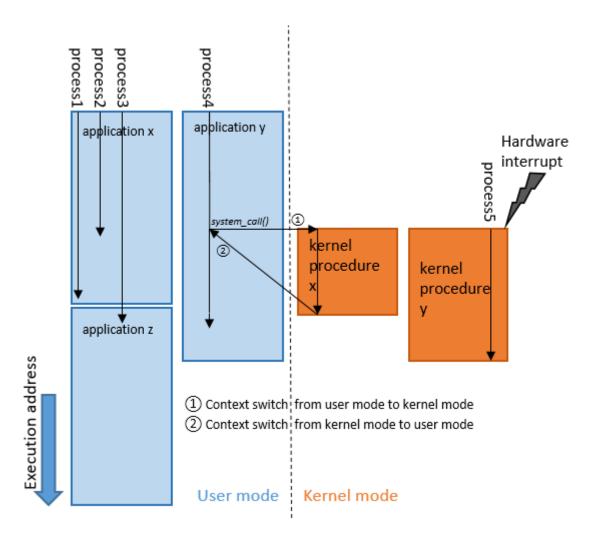

#### 2.4.2 Process/kernel model

In modern operating systems the restriction of user space program access to kernel space is enforced by hardware features. The hardware introduces two *execution modes* for the CPU: a non-privileged mode (*user mode*) and a privileged mode (*kernel mode*) for user programs and for the kernel, respectively. [5, p. 8]

This procedure is exploited in the process/kernel model, adopted by the Unix-like systems, where all the running processes have the illusion being the only process in the system with exclusive access to OS services [5]. A *process* is a common abstraction for all operating systems and it is defined as "an instance of program in execution" or as the "execution context" of a program; a program can be executed concurrently by multiple processes and a process can execute multiple programs sequentially, as seen in Figure 3. [5, p. 8]

When user space application process makes a request to the kernel via a system call, the execution mode is switched from user mode to kernel mode and the process continues to execute a kernel procedure to fulfill its request. This way, the operating system is said to act within the execution context of the process. Switches between user mode and kernel mode are also called *context switches*. When the request is fulfilled, the hardware is forced back to user mode and the process continues its execution from an instruction after the system call. A context switch of a process is illustrated in Figure 3 with a process called the "process4". [5, pp. 10, 11]

**Figure 3.** Application program-process relation, context switches and a hardware interrupt.

The kernel code can also by activated asynchronously by hardware interrupts and is then said to be run in *interrupt context*. Hardware interrupts are generated by system hardware or peripheral devices, like a keyboard, and their purpose is to notify the kernel that they have induced something that the kernel should react to. The main difference to *process context* is that when the kernel code is executed in interrupt context the user space portion of virtual address space must not be accessed. This is because of the fact that a hardware interrupt can occur at any time; it is unlikely that a user space process active at the time of the interrupt has anything to do with the cause of the interrupt and therefore the kernel must not have any effect to the current state of the user space. The interrupts invoke special kind of kernel code called *interrupt service routines* or *interrupt handlers* that take appropriate action to handle the situation the hardware has notified the kernel about. [4, p. 9]

The main advantage in the use of asynchronous hardware interrupts is that no CPU time is wasted while waiting something to happen. For example, it would not make sense to poll the status of a keyboard endlessly in a loop. In contrast, the status can be checked

only when a button is pressed and an interrupt is generated by the keyboard, invoking an interrupt handler taking appropriate actions [4, pp. 395-396]. How the interaction with a peripheral device actually happens is a responsibility of a kernel *device driver*. The device drivers are kernel programs that allow the kernel to interact with different kind of hardware and they make the largest part of the Linux kernel sources [4, p. 471].

The Linux kernel is, of course, composed of many more different kind of components and procedures to handle the running kernel; such as scheduling, the virtual file system, process management and networking. This chapter was just to give the reader a brief insight to the most important features for this thesis.

## 3. LINUX DEVICE DRIVERS

In an Unix system nearly every system operation is ultimately associated with a physical device. Only with the exception of the processor, memory and some few other hardware entities, all the device controlling is performed by device specific code called a device driver and the kernel must include these pieces of code for every peripheral in the system. This task is called *device control*, one of the main tasks of the Linux kernel. [9, p. 5]

The device drivers have a very special role in the kernel. They are the abstraction layer making the hardware respond to an internal programming interface, consequently hiding the hardware specific operation. This programming interface uses driver independent standardized calls known as system calls and mapping these calls to interact with system hardware is the main task of a device driver. The programming interface enables the drivers to be built separately from the kernel and to be used only when needed by plugging them into the kernel at runtime as *modules*. [9, p. 1]

In this chapter we have a brief look into different Linux device driver types and discuss some common features a device driver needs to implement. Our understanding about the Linux kernel is strengthened by looking into interrupt handling and memory management features. Lastly, the single most important system hardware feature for the thesis is discussed; the direct memory access (DMA) operation.

## 3.1 Modules

Modules are software entities that can be dynamically added to a running kernel [9, p. 5]. The modules offer an efficient way adding functionality, for example device drivers and filesystems, to the system kernel without the need of rebuilding the kernel or rebooting the system [4, p. 473]. The dynamic loading of modules is carried out by the *insmod* program that links the object file of a module into the kernel. Once linked, the object file can be unlinked with the *rmmod* program [9, p. 5].

After a module is loaded to the kernel it waits to service future requests that can be invoked by other modules and processes. This approach is similar to the event driven programming and while applications are not necessarily event-orientated, every module is. Another difference to user applications is that while an application can be lazy on resource release while exiting, a module needs to carefully release every resource it reserved at initialization time. Otherwise these resources will linger in the system unsupervised until the system is booted. [9, p. 18]

Modules also offer a convenient approach to device driver development. It would be time consuming to rebuild the kernel – with the source code of the device driver under development – every time a developer wants to test his/her modifications with the target platform [9, p. 18]. Device drivers permanently compiled into the kernel are not covered in this thesis because the implementation part only uses the module approach.

## 3.2 Device and driver types

A Linux system identifies its devices from three fundamental device types and utilizes them by corresponding drivers [9, pp. 6-7]:

#### • Character device

A character device, commonly abbreviated as *char device*, is a device entity that is interfaced as stream of bytes. Char devices are accessed via filesystem nodes, one example being the text console (/dev/console). Usually a char driver implements at least system calls *open*, *close*, *read* and *write*. A char device behaves much like a regular file in the filesystem but while one can move forward and backward in a file, a char device usually acts as a data channel only enabling sequential access.

#### Block device

A block device is an entity capable of hosting a filesystem and is also, like a char device, accessed by a filesystem node under the /dev directory. An example of a block device is a disk storage. In most Unix systems access to a block device is restricted to whole blocks of 512 bytes, or a larger power of two, but in Linux any number of bytes can be read and can be written to a block device. As result, a block device looks exactly like a char device to the user. They differ only in the way the kernel interfaces and manages the data of a block device and therefore completely different interfacing implementation is needed for a block driver.

#### • Network interface

All network transactions are performed through a device capable of exchanging data with another host and these devices are called interfaces. Usually these devices are hardware devices but there is also pure software implemented interfaces, for example the *loopback* interface. A network device is solely responsible for sending and receiving data packets used in networking without knowing about the connections and the networking subsystem in the kernel – one driving the network device. Because a network interface is not a stream-oriented device, it is not easily mapped to a node in a filesystem and the kernel uses packet transmission related function calls to access a network device driver instead of *read* and *write* used with char and block drivers.

It is not restricted to write a device driver implementing more than one these devices but this is not considered as good practice. Writing a module implementing multiple devices has negative effects on code scalability and extendibility. [9, p. 5]

Driver modules can also be classified by the functionality of devices they work on through additional layers of kernel support subsystems. For example, every universal serial bus (USB) device is controlled by a USB driver module that is a module working within a USB subsystem. Nevertheless, the USB device shows up in the filesystem as a char device or a block device in case the USB device happens to be a serial port or a USB memory card reader, respectively. Furthermore, if the USB device is a networking device, like a USB Ethernet adapter, it will show as a network interface. [9, p. 7]

## 3.3 Interrupt handling

As stated before, hardware interrupts are the way for peripheral devices to notify the processor that something has happened and that the processor should act accordingly. This functionality, called *interrupt handling*, is implemented by the device drivers. Basically, the job of a driver is to register a handler function, called the *interrupt handler*, for its device to take appropriate actions when the device generates an interrupt to the system. These functions have some limitations on the actions they can perform due to the way they are run in the Linux system. [9, p. 258]

The peripheral device slots include electronic lines to a component used to send interrupt requests to a device called the *interrupt controller*. This controller then forwards these requests to the interrupt inputs of the CPU. This way the peripheral devices are not actually able to force the interrupts on the CPU, but rather request them from the above component and these requests are known as *interrupt requests* or IRQs. Each interrupt has a unique number and a corresponding IRQ number that the kernel uses to look up an interrupt handler associated with device responsible for the request. The conversion between the IRQ number and the interrupt number is carried out by the interrupt controller and often these terms are used interchangeably. [9, pp. 849, 850]

In case the processor receives an IRQ having no associating interrupt handler the kernel simply acknowledges the interrupt and ignores it. The registration of a handler is expected from the modules. The interrupt lines may also be shared between multiple modules, following a procedure called *interrupt sharing*. In both cases, the IRQ is requested by the driver module with the *request\_irq()* function, defined in *linux/interrupt.h>*, which should be called after the device is opened (used) for the first time and before the hardware is allowed to produce interrupts. This is because of the limited amount of interrupt lines. If the request for an IRQ would be issued at module initialization time, the driver could waste this valuable resource if it is rarely used, especially if the driver does not support interrupt sharing. [9, pp. 259, 261]

There are some restrictions implementing an interrupt handler that must be taken into account. Because these handler functions are not run in the process context, they must not change data between user space. The handlers also can never perform any actions that could sleep, like a *wait\_event* call, memory allocation with any other flag than *GFP\_ATOMIC*, or a semaphore locking. Furthermore, handlers cannot call the *schedule()* function [9, p. 269]. This limitation originates from the fact that interrupt handlers should always be executed in minimum amount of time; system malfunctions may occur if a second interrupt is received while the first one is still being handled and it can lead to a kernel deadlocking, in the worst case scenario. This can be avoided by disabling interrupts during the handler execution but then interrupts essential for the system operation may be lost and this approach is avoided whenever possible [9, p. 849]. Often the handlers, however, need to perform lengthy tasks in response to a device interrupt. Therefore the need for minimal execution time and considerable work load conflict with each other. This dilemma is resolved in Linux by splitting the interrupt handler into two halves called the *top half* and the *bottom half* [9, p. 275].

If an interrupt handler is divided in two halves the one registered to an IRQ number with the *request\_irq()* is called the top half and is responsible for responding to an interrupt as fast as possible. Before exiting, the top half schedules the more time consuming work to be executed later, by the bottom half, at some safer time. In a typical use case the top half saves data received from the interrupt responsible device to a buffer, schedules the bottom half and exits. The bottom half can then perform the rest of the required work at some later time. This could include awaking of a process in need for the buffered data or starting a new I/O operation, for example. [9, p. 275]

The above procedure enables the top half to handle a new interrupt at same time the bottom half is still executing. An example exploiting a common top half / bottom half division is a network interface; the top half of an interface handler just retrieves the data on arrival of a new packet and pushes it to the protocol layer for later processing by the bottom half. The bottom half can be scheduled as a *tasklet* function or as a *workqueue* function using the *tasklet\_schedule()* and the *schedule\_work()* functions, respectively. The biggest difference between these two functions is that *tasklets* run in a software interrupt context and the *workqueues* in the context of a special worker process, thus enabling sleeping. Even though a *workqueue* runs in a process context it does not enable user space data transfer. [9, pp. 275-277]

# 3.4 Memory allocation

Allocating memory in the kernel is not as easy as it is in user space programs. This is because the kernel cannot easily deal with memory allocation errors and most of the time cannot sleep while allocating memory. Due to these limitations allocating memory is more complicated in the kernel than it is in user space. [10, p. 231]

The translations between virtual and physical memory is performed by a hardware component called memory management unit (MMU). The MMU maintains the system's page tables in page-sized granularity. The size of a page varies between architectures and many even support multiple page sizes. Majority of 32-bit and 64-bit architectures use 4 KB and 8 KB pages, respectively. The kernel represents every physical page – or page frame – with page structs, defined in *linux/mm\_types.h>*. These structs hold valuable information of each page frame, one being the count of how many references there is in the system to the page frame in question. [10, pp. 231-232]

The kernel provides multiple interfaces to perform memory allocation and ultimately all of these interfaces allocate memory with page-sized granularity. Behind the scenes all the interfaces for memory allocation use a low-level mechanism with a core function *alloc\_pages()*, defined in <*linux/gfp.h>*, with its variants and corresponding memory freeing functions. The freeing functions must be carefully used only to free pages previously allocated to avoid hanging the kernel, something that cannot happen in user space. [10, pp. 235, 237]

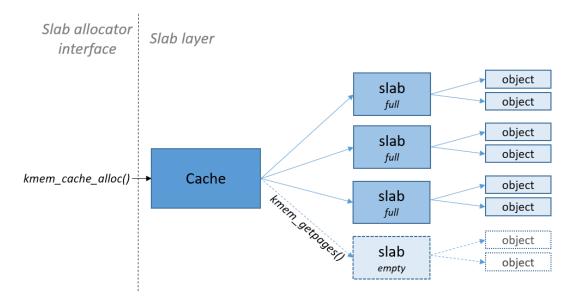

## 3.4.1 Slab layer

Allocating and freeing different kind of data structures is a common operation inside the kernel [10, p. 246]. Being limited only to page-sized allocations introduces a problem; allocating full pages for small data structures leads to memory wastage. If a structure composed of two 32-bit integer values is needed in the kernel code, allocating of a full page of 4 KB for this structure would introduce unacceptable waste of memory [4, p. 257]. This problem causes the need for Linux to be able to handle smaller memory entities than a page. One common solution is the *slab layer*.

The slab layer uses groupings called *caches* for different kind of object types like *process descriptors* and *inodes*. These cachees are further divided into *slabs* that are composed of one or more contiguous page frames and hold a number of equally-sized objects of cache specified type. The slabs are marked as full, partial or empty, representing the availability of objects in any given slab. The slab layer is managed by an interface exported to the entire kernel, known as the *slab allocator*, enabling creation and destruction of new caches and allocation and freeing objects from these caches. For example, obtaining an object from a cache is requested with the *kmem\_cache\_alloc()* function, defined in <*li>linux/slab.h>*. The kernel returns a pointer to already allocated, but unused object primarily from a partial slab or secondarily from an empty slab. If no free objects are available, the slab layer internally creates a new slab using the *kmem\_getpages()* function, defined in <*mm/slab.c>*, which ultimately calls the kernel page allocator \_\_get\_free\_pages(). This way the management of caches and their associated slabs is handled by the internals of the slab layer, as seen in the Figure 4. [10, pp. 246-249]

**Figure 4.** The slab allocator interfacing the slab layer subsystem, adapted from [10, p. 247].

The slab layer works as sort of a specialized allocator for objects of cache specified type and creation of new caches is supported by the slab allocator interface. Caches are desirable for objects that are frequently allocated and freed in the kernel. When the code needs a new instance of a data structure defined by a cache it can simply grab one from a partial slab without the need for memory allocation. After the code is done with the structure it is released back to the slab, in contrast to memory deallocation. This way the slab layer also works as a *free list*, enabling caching of frequently used structures increasing performance and decreasing memory fragmentation<sup>2</sup>. [10, pp. 245-246, 249]

The slab layer also introduces a family of *general purpose caches* [10, p. 246]. The size of objects inside these caches vary from  $2^5$  up to  $2^{25}$  bytes in length. The upper limit can considerably vary between different architectures and systems [4, p. 261]. In an x86 or ARM based system, with the page size of 4 KB, a common upper limit is 4 MB, or  $4 * 2^{20}$  B = 4 MiB to be exact [11]. These general purpose caches create the basis for the *kmalloc()* function, the preferred interface for kernel allocations, implemented on top of the slab layer alongside with the slab allocator. The slab caches of a given Linux system are listed in the */proc/slabinfo* utility. For example, the general purpose caches of one ARM based Linux system are identified with a "kmalloc" prefix and are listed in the Figure 5.

<sup>&</sup>lt;sup>2</sup> Memory fragmentation is a memory management problem where several page frames are free, but scattered in the physical address space. Contiguous memory blocks are desirable for the system performance. [4, p. 15]

```

kmalloc-4194304

kmalloc-8192

kmalloc-2097152

kmalloc-4096

kmalloc-1048576

kmalloc-2048

kmalloc-524288

kmalloc-1024

kmalloc-262144

kmalloc-512

kmalloc-131072

kmalloc-256

kmalloc-65536

kmalloc-192

kmalloc-32768

kmalloc-128

kmalloc-16384

kmalloc-node (64 bytes in length)

```

Figure 5. The general purpose caches of an ARM based Linux system.

## 3.4.2 kmalloc()

The operation of the *kmalloc()* function, also defined in *linux/slab.h>*, is similar to that of *malloc()* routine used in user space memory allocation. The only exception is that *kmalloc()* uses additional flags to indicate the type of memory requested and how it should be allocated. The *kmalloc()* is the preferred interface for most memory allocations performed in the kernel. [10, p. 238]

The *kmalloc()* function call uses two parameters: requested size of the memory in bytes and *gfp\_t* type flags defined in <*linux/types.h*>. The flags are divided in three groups [10, pp. 238-239, 241]:

#### Action modifiers

The action modifier flags tell the kernel how the requested memory should be allocated. For example, if memory is allocated in interrupt context no sleeping is allowed.

#### • Zone modifiers

The zone modifier flags specify the part of physical memory the allocation should be performed on. In Linux, the physical memory is divided in four primary memory zones with different kind of properties.

#### Types

The type flags are combinations of action and zone modifiers for certain type of memory allocations. This simplifies the process of providing the *kmalloc()* with multiple flags as often only one type flag is needed.

The most common allocation of kernel memory is carried out in process context in a situation that can sleep if necessary. A correct type flag for this case is the *GFP\_KERNEL*

flag that is actually a combination of action modifiers \_\_GFP\_WAIT, saying that the allocator can sleep, \_\_GFP\_IO, saying that the allocator may start disk I/O and \_\_GFP\_FS saying that the allocator can start filesystem I/O. Most of the time the zone modifiers are not needed because the allocations can be made to any memory zone, as it is the case with the GFP\_KERNEL type allocation. Combining the modifiers into a type flag is just a basic ORing operation. A kmalloc() function call

$$ptr = kmalloc(size, \__GFP\_WAIT \mid \__GFP\_IO \mid \__GFP\_FS);$$

is then equal to

$$ptr = kmalloc(size, GFP\_KERNEL);$$

Another important type flag is the *GFP\_ATOMIC*; it can be used in interrupt handlers and bottom halves because it specifies an allocation that cannot sleep. [10, p. 242]

When the memory is allocated successfully the kernel returns a pointer to a physically contiguous memory region that is at least the size requested. This is because the memory is allocated from the slab layer subsystem's general purposes cache; the requested size is actually rounded up to the closest matching general purpose cache. If the allocation should fail, a NULL pointer is returned. The memory allocated by the *kmalloc()* is released with the *kfree()* function. [10, pp. 238, 246]

## 3.4.3 vmalloc()

The biggest difference between the *kmalloc()* and the *vmalloc()* function, defined in <*linux/vmalloc.h>*, is that while the *kmalloc()* allocates physically (and virtually) contiguous memory, the *vmalloc()* allocates memory that is only promised to be virtually contiguous. This is also how the user space *malloc()* function works; the memory pages returned are contiguous in the virtual address space of the processor but not necessarily in the RAM. [10, p. 244]

On many architectures the hardware devices do not understand the virtual addresses because they reside – from the kernel point of view – behind the memory management unit, thus requiring physically contiguous memory allocations in case they need to work with memory locations. In contrast, memory regions used only by the software, like some process-related buffers, can be just virtually contiguous. Still, the *kmalloc()* is the preferred method allocating memory in the kernel and the *vmalloc()* is usually used only when absolutely necessary. This is mainly due to the worse performance of the allocation; the *vmalloc()* needs to work with page table entries to make physically noncontiguous page frames contiguous in the virtual address space. [10, p. 244]

The *vmalloc()* is typically used in situations requiring a large portion of memory. For example, modules are loaded into memory allocated with the *vmalloc()* [10, p. 244]. This is because the allocation builds a virtual memory region by suitably editing free page

table entries, thus not being limited to the maximum size of any slab layer defined object like the *kmalloc()*. In theory, the upper limit of the *vmalloc()* is the amount of available RAM in the system [11].

Memory allocation with the *vmalloc()* might sleep and therefore it cannot be called from interrupt context – or any other situation where blocking is not permitted. It only takes in one parameter: the amount of desired memory in bytes. [10, pp. 244-245] If the allocation is successful, a pointer to a virtually contiguous memory region, at least the size requested, is returned and in case of an error a NULL pointer is returned instead. Because the *vmalloc()* is page orientated, the allocation is actually rounded up to the nearest whole amount of pages. The memory allocated by the *vmalloc()* is released with the *vfree()* function. [9, pp. 225-226]

## 3.4.4 ioremap()

In some situations physical memory outside the address range of the kernel page tables is allocated for devices at boot time. This can be the case, for example, with a PCI (peripheral component interconnect) video device's frame buffer. For a driver to be able to access this already allocated buffer it can call the *ioremap()* function that like *vmalloc()*, builds new page tables. But, unlike the *vmalloc()*, it does not allocate any memory but returns a special virtual address that enables access to a specified physical address range. This address should not be used to directly access memory as it was a pointer. Rather, specialized I/O functions, like the *readb()*, should be used with the address retrieved by the *ioremap()*. This address is released by the *iounmap()* function.

# 3.5 Direct memory access

DMA is a hardware operation allowing system peripherals to transfer their data to and from the system memory without any need for processor intervention. Systems peripherals capable of such operation are also known as DMA controllers. Because using this method can eliminate much computational overhead, it can greatly increase the system performance and the data throughput. [9, p. 440]

The DMA transfer from a device can happen in two different ways; either the software asks the device to transmit data or the device asynchronously writes data to the system. The first case can be summarized in following steps [9, p. 441]:

- 1. A process calls the *read* system call of a device and the driver of the DMA capable device instructs the device to transfer its data to a pre-allocated DMA buffer. The process that invoked the *read* is put to sleep.

- 2. The DMA capable device writes its data to the buffer and generates an interrupt after it is done.

3. The interrupt handler of the driver awakens the process put to sleep in step 1, which is then able to read the data.

In the second scenario the DMA controller usually expects to have access to a circular buffer, also called a *ring buffer*, to write its data asynchronously to a next available buffer in the ring and raises an interrupt to notify that there is now data available in the ring. [9, p. 441].

## 3.5.1 DMA Mapping

Using DMA operations is ultimately based on allocating a buffer and passing it to a DMA capable device. Allocating a DMA buffer is possible with the *kmalloc()* or the *get\_free\_pages()* functions. If the DMA capable device is known to be limited to 24-bit addressing, like the ISA (industry standard architecture) devices, a *GFP\_DMA* type flag needs be passed to the allocator, forcing the allocation to happen from a DMA memory zone that is addressable with 24-bits. [9, pp. 442-444]

However, a DMA capable device, connected to some interface bus, uses physical addresses, unlike the program code allocating the buffer. Actually, the device uses *bus addresses*, rather than physical addresses, because in some architectures the interface bus is connected to special circuitry that converts I/O addresses to physical addresses. It takes some special functions to convert the virtual address returned by an allocator to a bus address. Using these functions is strongly discouraged. The correct way is to use a generic *DMA layer*, offered by the Linux system, which handles the conversion. [9, pp. 442-444]

The generic DMA layer offers a bus- and architecture-independent approach creating a device driver utilizing hardware capable of DMA operations. It includes a mapping operation, called a *DMA mapping*, which generates the bus address usable by the device from the allocated buffer. Through these mappings also *cache coherency* can be managed. *Cache memory* is a feature found in modern processors that stores copies of recently used memory locations in a CPU cache, boosting system performance. This may introduce problems, however, if main memory is accessed without the CPU knowing about it, as it is with the DMA operation. [9, pp. 445-446]

The generic DMA layer is interfaced by the *DMA API* (application programming interface) defining the needed DMA mapping functions in *linux/dma-mapping.h>*. The DMA API introduces two different kinds of mappings: *consistent*, also known as *coherent*, and *streaming* DMA mappings. The consistent mapping automatically takes care about the cache coherency problem so that the device and the CPU both see the updates they make without any software flushing operations. In contrast, the streaming DMA mapping requires the user to take care of flushing the cache. The interfaces for this mapping type were designed in a way that they can fully utilize whatever optimization the

hardware allows. DMA mapping can be performed with the <code>dma\_alloc\_coherent()</code> (consistent) and the <code>dma\_map\_single()</code> (streaming) functions and unmapping with the <code>dma\_free\_coherent()</code> and the <code>dma\_unmap\_single()</code> functions, respectively. On success, they both return a <code>dma\_addr\_t</code> type DMA handle that is usable by the DMA device. In case of the streaming mapping, the cache coherency must be taken care of by calling the <code>dma\_sync\_single\_for\_cpu()</code> and the <code>dma\_sync\_single\_for\_device()</code> functions accordingly. [12]

In case very small DMA mappings are required, the user should consider using a *DMA pool*. The DMA pool, defined in *linux/dmapool.h>*, is an allocation mechanism for small, consistent mappings. The mappings performed by the *dma\_alloc\_coherent()* may be limited to minimum size of one page and in case the driver needs smaller DMA areas, a DMA pool should be used [9, p. 447]. A DMA pool works much like the slab allocator, but instead of using the *get\_free\_pages()* function it uses the *dma\_alloc\_coherent()* internally [12].

The above discussed streaming type DMA mapping methods requires physically contiguous memory allocated by the *kmalloc()* or the *get\_free\_pages()* functions. In some situations, however, the buffers needed in the DMA can reside different parts of the physical RAM. They could be mapped individually and then the DMA operations could be sequentially performed on each buffer. This problem is resolved by a special type of streaming DMA mapping called the *scatter/gather* mapping. Many DMA controllers accept so called *scatterlists*, consisted of array pointers and lengths, and transfer everything in the list as one DMA operation, introducing better performance. In a system that uses mappings between bus addresses and page frames, a scatterlist can also be arranged in a way that discontiguous page frames look contiguous to the device. The scatterlist is defined in <*asm/scatterlist.h*>. [9, p. 450]

After the scatterlist is created, the scatter/gather mapping is carried out by the  $dma\_map\_sg()$  function taking in the scatterlist as one of the parameters. If the system has an I/O memory management unit (IOMMU), the  $dma\_map\_sg()$  programs the unit's mapping registers so that, in the best case scenario, the device thinks that one block of contiguous memory was received. Because the scatter/gather is a type of streaming DMA mapping, the user needs to take care of cache coherency by calling the  $dma\_sync\_sg\_for\_cpu()$  and  $dma\_sync\_sg\_for\_device()$  functions accordingly. A scatter/gather mapping is released with the  $dma\_unmap\_sg()$  function. [9, p. 451]

## 4. FPGA BASED SOC-PLATFORM

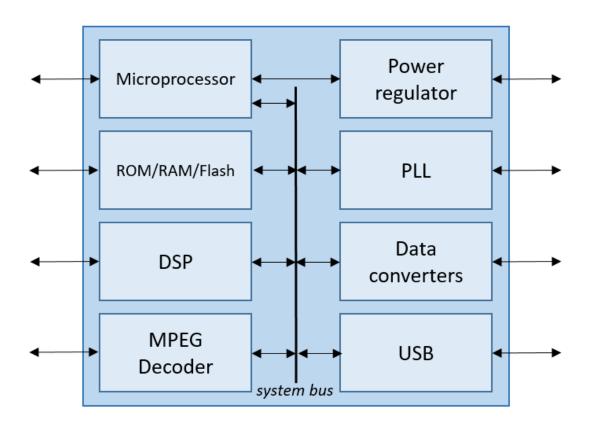

A computer, with all its components, or some other electronic system implemented on a single integrated circuit can be referred to as a system-on-a-chip (SoC). Figure 6 shows an example of a typical SoC system illustrated in functional blocks connected with some system bus architecture. In addition to a processor and embedded memory units, a typical SoC includes some communication peripherals, like wired USB connections or wireless communication ports, a PLL (phase-locked loop) for system timing, data conversion blocks like analog-to-digital (A/D) and digital-to-analog (D/A) converters and digital signal processor (DSP) circuits. [13, p. 5]

**Figure 6.** Functional block diagram of a typical SoC circuit, adapted from [13, p. 4].

A common task for a SoC based system is digital signal processing application such as imaging, software defined radio or a radar. The algorithms needed in digital signal processing can be very demanding in the means of processing power and traditionally these algorithms are run on dedicated components called digital signal processors (DSP) [14, pp. 4-5]. This operation is known as *hardware acceleration*, where some specific functions of an application, with high performance demands, are performed with hardware

components instead of the CPU [6, p. 9]. The DSPs can also be replaced with more general purpose circuits known as FPGAs (Field programmable gate array). A modern FPGA has a capability to be programmed to perform just about any digital operation imaginable and they can outperform the fastest DSP chips by a factor of 500 or more. Due to their lowering price and high usability the FPGAs are becoming increasingly attractive for embedded system applications [14, p. 5].

The demands for the SoC hardware are, of course, application specific and the hardware and the software should be considered as a whole when designing an embedded system. Especially in low production volume products it is often desirable to keep the custom hardware development at minimum and to use verified commercial components. Furthermore, in high performance applications demanding hardware acceleration, a SoC containing a FPGA circuit may be a cost-effective choice.

In this chapter some common FPGA architecture features are discussed and the SoC platform used in the implementation part of the thesis is presented.

## 4.1 Field programmable gate arrays

The field programmable gate arrays are digital *integrated circuits* (IC) containing programmable logic blocks, connected by configurable interconnects, enabling such devices to be programmed to perform various, user defined, tasks. The "field programmable" part of the name refers to the fact that FPGA's are programmable "on the field", in contrast to devices configured by manufacturer. [14, p. 1]

While FPGAs do not necessarily offer the fastest available clock rate among ICs, it may be possible to achieve superior performance due to their parallel architecture, especially suitable to signal processing applications. Still, a specialized hardware component often outperforms a FPGA. The greatest advantage FPGAs bring to system design is flexibility. It is their reconfigurability capabilities together with the high processing power that makes FPGAs considerable choice in many applications. [15, p. 8]

# 4.1.1 FPGA comparison to other ICs

Other kind of "in field" programmable ICs do exist; PLD's (programmable logic device) also have manufacturer defined architecture but are programmable by the end user to perform different kind of functions. These devices, however, contain relatively limited number of programmable logic, therefore only being capable of small and simple functions [14, p. 2]. Because of this limitation, the PLD manufactures developed CPLDs (complex programmable logic device), which can be thought as multiple PLDs in a single chip, connected by a programmable interconnect. These devices actually have some overlap with the FPGAs in potential applications. FPGAs still tend to outperform CPLDs in register-heavy, pipelined applications and in applications dealing with high speed input

data streams. Additionally, FPGA's architecture is more flexible and usually offers a denser circuit (more gates in a given area) and they have become the industry standard, or "de facto", in large programmable logic designs [1, pp. 244-246].

In contrast to "in field" programmable ICs there are ASICs (application-specific integrated circuit) and ASSPs (application-specific standard part). These circuits can contain hundreds of millions logic gates and carry out extremely large and complex functions. Both of these circuits are based on the same manufacturing processes and they are both custom-designed to serve some specific application, the only difference being that ASICs are designed and built for a specific company, but ASSPs are marketed to multiple customers. These circuits both overcome FPGAs in the number of transistors, complexity and performance. On the downside they are very expensive and time-consuming to develop and they are not reconfigurable after they are built.

FPGA features lie in between of those introduced by CPLDs and ASICs; they are reconfigurable like PLDs, but can contain millions of logic gates, enabling implementation of large and complex designs, like ASICs. In comparison to ASICs the design changes and overall development is easier and faster with FPGAs leading faster time to market. The FPGAs are also cheaper to develop; no expensive toolsets for ASIC designs are required and developers may test their hardware and software designs on FPGA-based test platforms, without the need for non-recurring engineering. On the other hand, after development, ASIC circuits are cheaper to produce and this is especially notable in large scale production. [14, pp. 2-3]

FPGAs can also be used in prototyping. Since it is cheaper and faster to develop an application, in need for hardware accelerated parts, with a FPGA circuit, the product may be developed using a FPGA and later produced with an ASIC [1, p. 245]. The choice between FPGAs and ASICs eventually comes down to tradeoffs between development and production costs, demands on time to market and future product support and development needs. The FPGA circuits become especially favorable in low volume projects with fast time to market needs and limited development resources.

#### 4.1.2 General FPGA architecture

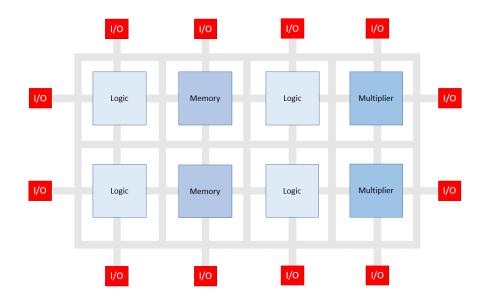

The FPGAs consist of an array containing varying type and number of programmable logic blocks such as general logic, multiplier and memory blocks. These blocks are connected by a configurable routing fabric so that different blocks can be programmably interconnected. The array is connected to the outside world through surrounding programmable I/O blocks. This general structure is illustrated in the Figure 7. [16, p. 3]

Figure 7. General FPGA structure, adapted from [16, p. 3].

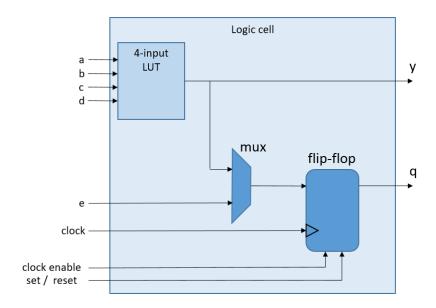

These logic blocks are built from more basic elements, often called logic cells (LC) or logic elements (LE), depending on the vendor. An LC could, for example, consist of a LUT (lookup table) with 4 bit wide input, a multiplexer and a register. A LUT is also capable of acting as a 16x1 bit RAM element or a 16-bit shift register and the register can be configured as a flip-flop or as a latch. When configured as a flip-flop (clocked register), the register can also be configured to be triggered by a rising edge or by a falling edge of an input clock signal [14, p. 74]. A simplified version of an LC, with a flip-flop configured register, can be illustrated with the Figure 8. It should be noted that this assembly is just an illustration of a simplified LC architecture. Actual architecture of these low-level FPGA elements may differ even between different device families from the same vendor and in advanced FPGA families the internal structure of these elements can be quite complicated [15, p. 25].

Figure 8. A simplified LC element, adapted from [14, p. 74].

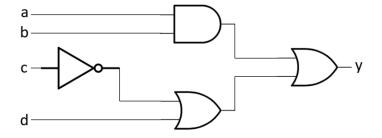

The LUT seen in Figure 8 can be used to implement a Boolean function with 4 or fewer inputs and the output of the LUT can be fed out of the LC or into a register through a multiplexer [15, p. 25]. For example, the LUT could be configured to perform the following Boolean function:

$$y = (a \& b) | (!c | d)$$

, where "&" is used as logical AND, "|" as logical OR and "!" as logical NOT operator. This function can also be represented with graphical logic gates as illustrated in Figure 9.

Figure 9. A Boolean function represented by graphical logic gates.

The Boolean function can be configured into the LUT as seen in Table 1.

| Table 1. | Representation of a LUT configured to perform the Boolean function |

|----------|--------------------------------------------------------------------|

|          | $y = (a \& b) \mid (!c \mid d).$                                   |

| а | b | С | d | у |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

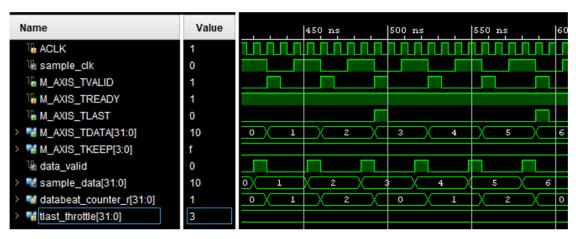

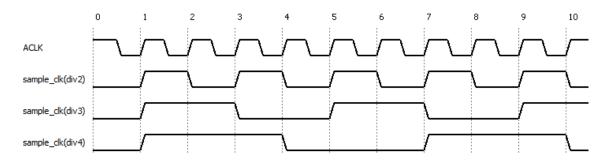

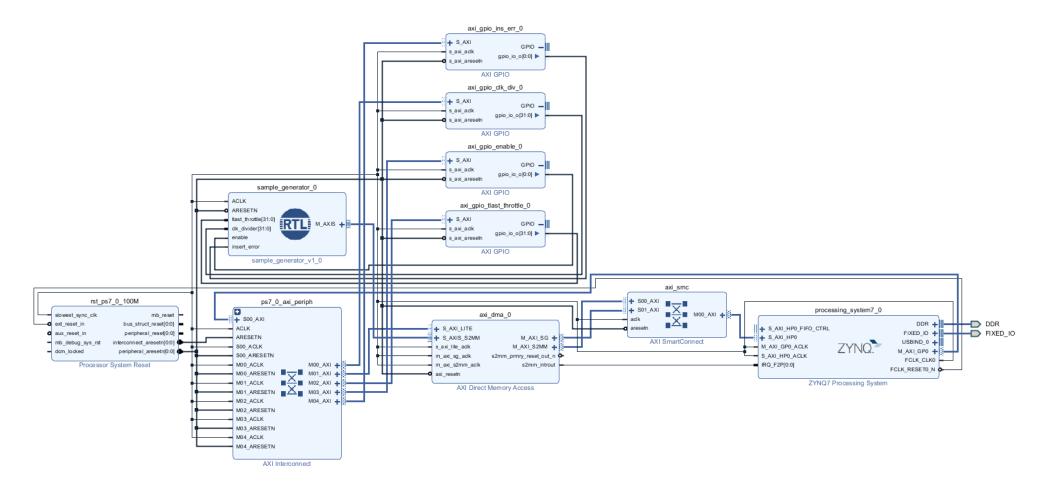

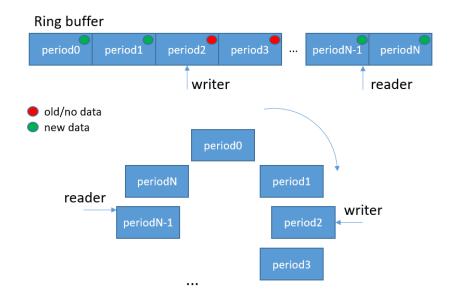

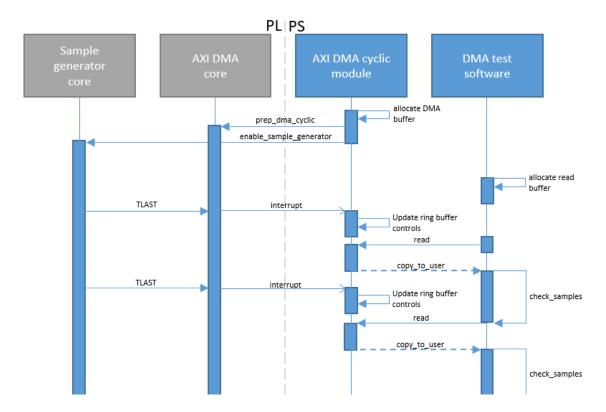

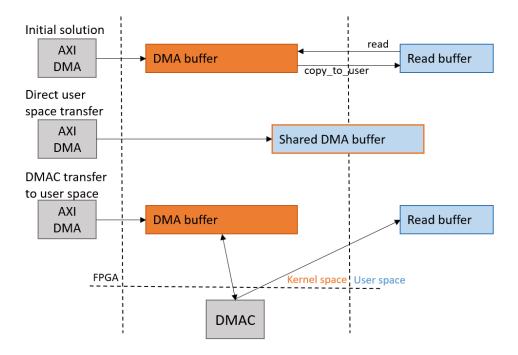

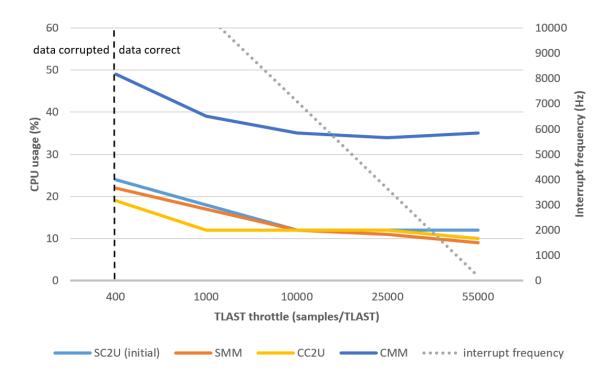

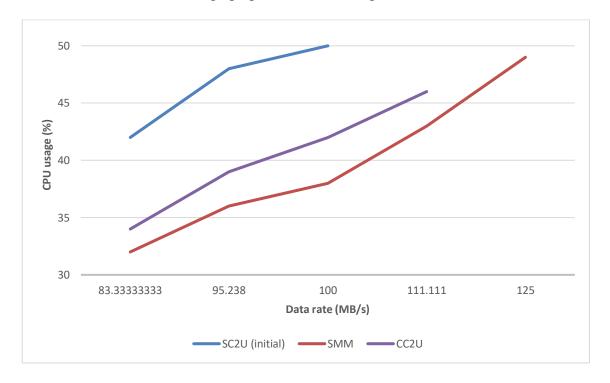

| 1 | 0 | 0 | 0 | 1 |