Juha Arvio

# Augmenting IP blocks for verification and optimization

**Master of Science Thesis**

Examiners: Dr. Tech. Erno Salminen Prof. Timo D. Hämäläinen Subject approved by Faculty of Computing and Electrical Engineering Council meeting on 04.04.2012

## Tiivistelmä

#### TAMPEREEN TEKNILLINEN YLIOPISTO

Sähkötekniikan koulutusohjelma **Arvio, Juha**: Augmenting IP blocks for verification and optimization Pääaine: Digitaali- ja tietokonetekniikka Diplomityö, 79 sivua Tarkastajat: Tek. Toht. Erno Salminen, Prof. Timo D. Hämäläinen Avainsanat: Metadata, verifiointi, optimointi

Helmikuu 2012

Digitaalisten IP-lohkojen verifiointi on aina ollut haasteellista. Modelsimin kaltaisilla softasimulaattoreilla voidaan verifioida aika perusteellisesti yksinkertaiset lohkot, joihin löytyy suoraviivaiset testisyötteet. Valitettavasti monimutkaisten järjestelmäpiirien simulointi softasimulaattorilla voi kestää päiviä ellei viikkoja. Lisäksi jokaiselle lohkolle, tarkasteltavassa järjestelmäpiirissä, on löydyttävä toimiva simulointimalli. Nykyaikaisia ohjelmoitavia FPGApiirejä voidaan kylläkin monitoroida reaaliaikaisesti Alteran Signal Tap II:n tapaisilla työkaluilla, mutta tämän kaltaisilla työkaluilla voidaan monitoroida vain pieniä määriä signaaleja lyhyellä aikavälillä.

IP-informaatiorekisterit (IIR) luotiin ylittämään nämä esteet. Näitä rekistereitä käytetään tallentamaan tietoa jota saadaan IP-lohkoista sekä järjestelmäpiireistä kokonaisuutena. Tämä tieto voi olla joko staattista tai dynaamista, toisin sanoen se on luotu joko ennen järjestelmäpiirin käyttämistä oikealla alustalla tai sen aikana. Tätä tietoa voidaan käyttää moneen tarkoitukseen, kuten yksittäisten IP-lohkojen ja kokonaisten järjestelmäpiirien verifiointiin.

Tämän työn esimerkkitapauksessa on kolme osaa joissa tutkitaan tarkemmin kolmea näistä tarkoituksista Terasicin toisen sukupolven kehitys- ja opetuskäyttöön tarkoitetulla FPGA-kortilla. Tähän fyysiseen alustaan integroitiin kaksi järjestelmää. Ensimmäiseen kaksiuloitteiseen grafiikkajärjestelmään lisättiin informaatiorekistereitä jotka keräsivät siitä tietoa. Toinen järjestelmä taas keräsi tämän tiedon ja välitti sen eteenpäin.

Rekistereiden staattista käyttöä identifioimiseen tutkittiin esimerkkitapauksen ensimmäisessä osassa. Toinen ja kolmas osa hyödynnettiin rekistereiden dynaamisen puolen tutkimiseen tarkastelemalla niiden käyttöä verifioinnissa ja optimoinnissa. Jokainen näistä eri puolista paljastui hyväksi lisäavuksi digitaalisten piirien suunnitteluun.

### Abstract

#### TAMPERE UNIVERSITY OF TECHNOLOGY

Master's Degree Programme in Electrical Engineering **Arvio, Juha**: Augmenting IP blocks for verification and optimization Major: Digital- and Computer Systems Master of Science Thesis, 79 pages Examiners: Dr. Tech Erno Salminen, Prof. Timo D. Hämäläinen Keywords: Metadata, verification, optimization

#### February 2012

The verification of digital intellectual property (IP) blocks has always been a challenge. Simple IP blocks with straightforward test inputs, can be quite thoroughly verified with software simulators such as Modelsim. But the verification of a complex System-on-Chip (SoC) on a software simulator can last days or even weeks, and that assumes that every IP on the SoC has a working simulation model. Although modern programmable chips can be monitored in real time with tools like Altera's Signaltap II, they still only offer monitoring capabilities for a limited amount of signals and for a limited amount of time.

To overcome this deficiency, IP information registers (IIR) were developed for this thesis. These registers are used to store information pertaining to the IPs and the SoC as a whole. The information can be static or dynamic, ie. generated before or during run-time. The information itself can be used for many different purposes along with the verification of single IPs or whole SoCs.

The case study in this thesis has three parts where three of those purposes are examined with Terasic's second generation development and education (DE2) board. This physical platform was fitted with two systems, a 2D graphics system embedded with information registers and a system to monitor the first one using these registers.

The first part examined the identification aspects with static information whereas the second and third part examined the dynamic aspects of the information registers with their verification and optimization capabilities. Each of these aspects was deemed to offer a good service for developers designing digital circuits.

# Preface

This Master of Science thesis was written at the Department of Computer Systems, Tampere University of Technology. The work for this thesis was partly done for the Funbase project which was funded by TEKES, and spanned from spring 2010 to spring 2012.

I would like to thank all my co-workers for providing a good working environment. Specifically two persons gave me valuable advice on completing this thesis. These two were Dr. Tech. Erno Salminen and Dr. Tech Timo Hämäläinen.

Tampere, February 28, 2012

Juha Arvio

Multiojankatu 28 D 29

33850 Tampere

Finland

# Contents

| 1. | Intro            | oduct | tion1                                                  |

|----|------------------|-------|--------------------------------------------------------|

| 2. | Meta             | adata | a4                                                     |

|    | 2.1.             | Requ  | uirements from/to IP vendors4                          |

|    | 2.2.             | Desi  | gn time information4                                   |

|    | 2.3.             | Run   | time information5                                      |

| 3. | Syst             | tem-o | on-Chip design flow6                                   |

|    | 3.1.             | FunB  | Base SoC design flow                                   |

|    | 3.1.1            |       | Design tools                                           |

|    | 3.1.2            |       | Hardware integration flow9                             |

|    | 3.1.3            | 5.    | Software integration flow11                            |

|    | 3.2.             | FunB  | Base hardware platform                                 |

|    | 3.3.             | Alter | ra tools used in FunBase                               |

|    | 3.4.             | Thirc | d party tools used in FunBase                          |

|    | 3.5.             | Thirc | d party IPs used in FunBase                            |

|    | 3.6.             | Impr  | oving the integration of Altera tools to FunBase17     |

|    | 3.6.1.<br>3.6.2. |       | SOPC builder integration approach one19                |

|    |                  |       | SOPC builder integration approach two19                |

|    | 3.6.3            | 5.    | SOPC builder integration approach three20              |

|    | 3.6.4            | ŀ.    | SOPC builder integration conclusion20                  |

|    | 3.7.             | FunB  | Base case study                                        |

|    | 3.7.1            |       | Image residual with different hardware architectures21 |

| 4. | IP in            | form  | nation registers23                                     |

|    | 4.1.             | Verif | fication and optimization flow25                       |

|    | 4.2.             | Reso  | ources                                                 |

|    | 4.2.1            |       | Register and interconnection types26                   |

|    | 4.2.2            |       | General information registers27                        |

|    | 4.2.3            | s.    | Optional information registers29                       |

|    | 4.3.             | Supp  | oorting IP blocks                                      |

|    | 4.3.   | 1.     | Data gathering unit                        | 30   |

|----|--------|--------|--------------------------------------------|------|

|    | 4.3.   | 2.     | Data transfer unit                         | 30   |

|    | 4.3.   | 3.     | Temporary data memory                      | 31   |

|    | 4.3.   | 4.     | System IIR                                 | 31   |

|    | 4.3.   | 5.     | IP monitor                                 | 31   |

| 5. | . Bas  | sics o | f computer graphics                        | . 33 |

|    | 5.1.   | Colo   | r information                              | 34   |

|    | 5.2.   | Imag   | ge buffers                                 | 34   |

|    | 5.3.   | 2D g   | raphics elements                           | 35   |

|    | 5.3.   | 1.     | Sprites                                    | . 35 |

|    | 5.3.   | 2.     | Tiles                                      | 36   |

|    | 5.4.   | Grap   | hics memory, etc                           | 36   |

|    | 5.5.   | Vide   | o signals                                  | . 37 |

| 6. | . IP i | nforn  | nation register case study                 | . 39 |

|    | 6.1.   | Test   | setup hardware                             | 40   |

|    | 6.1.   | 1.     | DE2 board                                  | 40   |

|    | 6.1.   | 2.     | Samsung SyncMaster 957MB monitor           | 41   |

|    | 6.2.   | Alte   | a IPs used in the test setup               | 41   |

|    | 6.2.   | 1.     | Nios II processor                          | 41   |

|    | 6.2.   | 2.     | SDRAM controller                           | 42   |

|    | 6.2.   | 3.     | FLASH controller                           | 42   |

|    | 6.3.   | IPs d  | esigned for the test setup                 | 42   |

|    | 6.3.   | 1.     | Nios II monitor                            | 42   |

|    | 6.3.   | 1.1.   | Log registers                              | 43   |

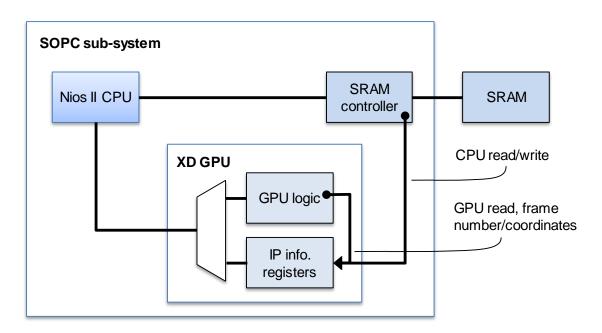

|    | 6.3.   | 2.     | XD GPU                                     | 45   |

|    | 6.3.   | 3.     | SRAM controller                            | 46   |

|    | 6.4.   | Test   | setup software                             | 47   |

|    | 6.5.   | Exan   | nining IP information register usages      | 48   |

|    | 6.5.   | 1.     | Scanning for IIR enabled IP blocks         | 49   |

|    | 6.5.   | 2.     | Determining memory related timing problems | 50   |

|    | 6.5.3 | 3.    | Verifying SRAM timings                       | 51  |

|----|-------|-------|----------------------------------------------|-----|

|    | 6.5.4 |       | Sharing an external memory                   |     |

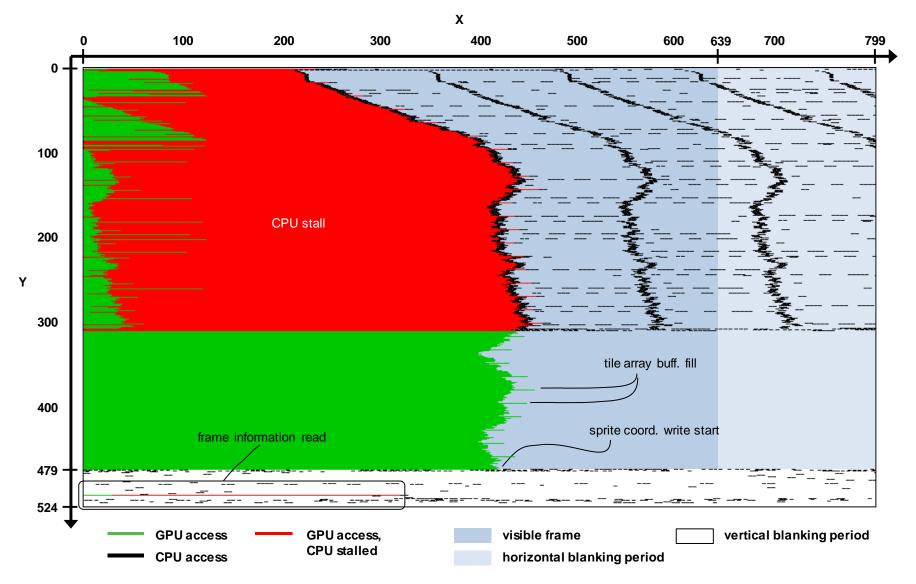

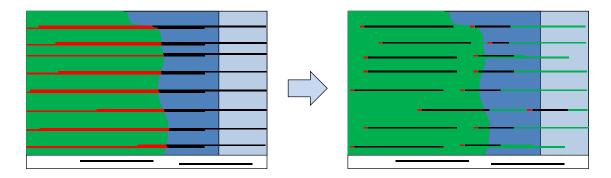

|    | 6.5.5 | 5.    | Acquiring usage patterns for the shared SRAM | 55  |

|    | 6.5.0 | 6.    | Optimizing the use of the shared SRAM        | 59  |

| 7. | Cor   | nclus | ions                                         | .60 |

|    | 7.1.  | HDL   | files                                        | 61  |

|    | 7.2.  | Harc  | dware resource usage                         | 62  |

|    | 7.3.  | Soft  | ware files                                   | 64  |

|    |       |       |                                              |     |

# List of figures

| Figure 1.1 - Simplified structure of a SoC                                                     | 1  |

|------------------------------------------------------------------------------------------------|----|

| Figure 1.2 - Structure of an FPGA chip                                                         | 2  |

| Figure 3.1 - FunBase SoC design flow                                                           | 7  |

| Figure 3.2 - Kactus tool                                                                       | 8  |

| Figure 3.3 - KoskiGUI tool                                                                     | 9  |

| Figure 3.4 - Hardware integration flow                                                         | 10 |

| Figure 3.5 - Software integration flow                                                         | 11 |

| Figure 3.6 - FunBase hardware platform                                                         | 13 |

| Figure 3.7 - SOPC builder                                                                      | 14 |

| Figure 3.8 - Quartus II EDA tool configuration                                                 | 15 |

| Figure 3.9 - Quartus II                                                                        | 16 |

| Figure 3.10 - Improving the integration of the SOPC builder to the Kactus tool                 | 18 |

| Figure 3.11 - Calculation of a residual from two images                                        | 21 |

| Figure 3.12 - Image residual with different hardware architectures                             | 21 |

| Figure 4.1 - IP block with embedded information registers                                      | 24 |

| Figure 4.2 - A test setup with IP information registers                                        | 24 |

| Figure 4.3 - Verification and optimization flow with IP information registers                  | 25 |

| Figure 4.4 - IP information registers in IP block's memory space                               | 27 |

| Figure 5.1 - Image generation methods                                                          | 33 |

| Figure 5.2 - Example of a 4-bit color palette                                                  | 34 |

| Figure 5.3 - A character made of 8x8 sprites                                                   | 36 |

| Figure 5.4 - A 16x10 tile array made of 16x16 tiles                                            | 36 |

| Figure 5.5 - Image displayed on a CRT monitor                                                  | 37 |

| Figure 5.6 - Monochrome video signals                                                          | 38 |

| Figure 6.1 - Case study test setup                                                             | 39 |

| Figure 6.2 - DE2 development and education board                                               | 41 |

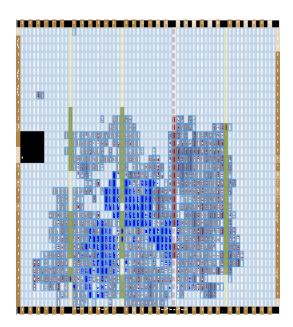

| Figure 6.3 - Screenshot of XD GPU demo                                                         | 48 |

| Figure 6.4 - Case study part 1 printout                                                        | 50 |

| Figure 6.5 - Monitoring the Nios II CPU                                                        | 52 |

| Figure 6.6 - GPU and CPU memory usage pattern, GPU has top priority                            | 54 |

| Figure 6.7 - XD GPU IP information register connections                                        | 55 |

| Figure 6.8 - CPU and GPU memory usage pattern, GPU has top priority                            | 58 |

| Figure 6.9 - Arbitrating access times                                                          | 59 |

| Figure 7.1 - Resource usage for the IIR blocks on the left, monitoring CPU, etc. on the right. | 64 |

# List of tables

| Table 4.1 - IP information register types                           | 26 |

|---------------------------------------------------------------------|----|

| Table 4.2 - General information register layout                     | 28 |

| Table 4.3 - Optional information register usages                    | 29 |

| Table 5.1 - Line and frame buffer sizes                             | 35 |

| Table 6.1 - Nios II monitor information register layout             | 43 |

| Table 6.2 - Log register commands                                   | 44 |

| Table 6.3 - Log status structure                                    | 44 |

| Table 6.4 - Example of event based log content                      | 45 |

| Table 6.5 - Example of periodic log content                         | 45 |

| Table 6.6 - XD GPU information register layout                      | 46 |

| Table 6.7 - SRAM information register layout                        | 47 |

| Table 6.8 - Address space for the data gathering unit's Nios II CPU | 49 |

| Table 6.9 - Log data during crash                                   | 53 |

| Table 6.10 - Shared SRAM log event format for frame start           | 56 |

| Table 6.11 - Shared SRAM log event format for intra frame events    | 56 |

| Table 7.1 - Case study parts                                        | 60 |

| Table 7.2 - IIR block lines of code                                 | 61 |

| Table 7.3 - XD GPU lines of code                                    | 62 |

| Table 7.4 - IP block resource usage                                 | 63 |

| Table 7.5 - Software lines of code                                  | 65 |

# Abbreviations

| 2D    | Two dimensional                          |

|-------|------------------------------------------|

| ASIC  | Application Specific Integrated Circuit  |

| CPU   | Central Processing Unit                  |

| CRT   | Cathode Ray Tube                         |

| DAC   | Digital to Analog Converter              |

| eCos  | embedded Configurable operating system   |

| fifo  | first in, first out                      |

| FPGA  | Field Programmable Gate Array            |

| Gbps  | Giga bits per second                     |

| GPU   | Graphics Processing Unit                 |

| GUI   | Graphical User Interface                 |

| HD    | High Definition                          |

| HDL   | Hardware Design Language                 |

| HIBI  | Heterogeneous IP Block Interconnect      |

| HW    | Hardware                                 |

| ID    | Identification                           |

| IDE   | Integrated Development Environment       |

| I/O   | Input / Output                           |

| IP    | Intellectual Property                    |

| IIR   | IP Information Registers                 |

| JTAG  | Joint Test Action Group                  |

| LUT   | Look-Up table                            |

| Mutex | Mutual exclusion                         |

| OS    | Operating System                         |

| PC    | Personal Computer                        |

| PPU   | Pixel Processing Unit                    |

| RAM   | Random Access Memory                     |

| RTL   | Register-Transfer Level                  |

| RTOS  | Real Time Operating System               |

| SDRAM | Synchronous Dynamic Random Access Memory |

| SRAM  | Static Random Access Memory              |

| SoC   | System-on-Chip                           |

| SUT   | System-Under-Test                        |

| SOPC  | System-On-Programmable-Chip              |

| SW    | Software                                 |

| Tcl   | Tool Command Language                    |

| TTA   | Transport Triggered Architecture         |

|       |                                          |

| University of Technology | TUT Tampere |

|--------------------------|-------------|

| University of Technolog  | TUT Tampere |

USB Universal Serial Bus

VGA Video Graphics Array

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

XML Extensible Mark-up Language

## 1. Introduction

In the early years of semiconductor design, companies developed digital logic for their internal use. The design of these intellectual property (IP) blocks was widely protected and they were rarely licensed to third parties. But as the complexity of semiconductor chips has dramatically increased, the development of digital IP blocks has become ever so challenging. This has lead in the past decade into the increase in the reuse of these IP blocks [gsa].

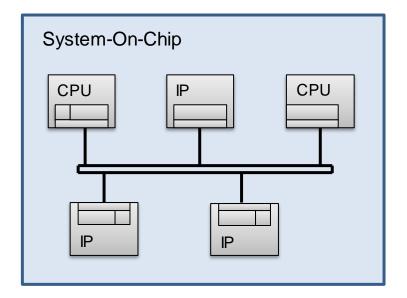

Additionally, these blocks are more and more used to construct customised chips that include many different IP blocks in them. These constructs are referred to as System-on-Chips (SoC), because of the way they implement a fully working system on a chip as opposed to constructing the system of individual components [nul06]. A simplified illustration of a SoC can be seen in Figure 1.1.

Figure 1.1 - Simplified structure of a SoC

The design of a hardware (HW) IP block, such as a microprocessor or a hardware accelerator, always includes the verification of its design. The importance of verification is steadily increasing as the complexity of the IP blocks and systems increase [keut00, keat02]. The first step to verify the correct behaviour of a design is to simulate it in a test bench on a program like Modelsim [model12]. The main hardware description languages (HDL) supported by Modelsim are verilog [ver95] and very high-speed integrated circuit HDL (VHDL) [vhd94].

However, there is also a need to test the IP block in the target platform which may not be feasible with software (SW) based simulation. For example, certain clocking and power-saving modes are hard to verify in simulation. Moreover, simulation models of external components, such as memories and network interfaces, might be missing. Additionally, simulation of a basic hardware platform with one or more SoCs can take days or even weeks to complete. This makes the iteration process of the verification almost impossible. To overcome these problems, the designer needs a way to construct a test platform before the application specific integrated circuit (ASIC) is produced of the SoC.

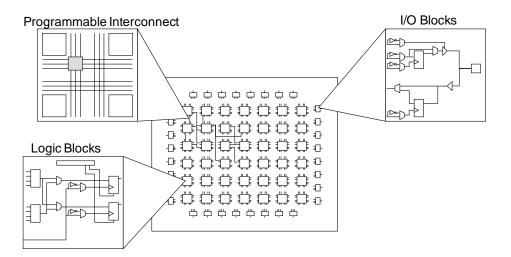

In 1984, Altera introduced the first reprogrammable logic device to the world called the EP300 which was a major improvement for prototyping [alt12]. Since then, the transistor counts of digital devices have increased significantly. From the 21st century, the chips have been large enough so that hardware designers have had the opportunity not only to synthesize single IP blocks but even whole systems on a chip. Nowadays, it's common practise to test IP blocks and systems with a field programmable gate array (FPGA) or an array of them. Figure 1.2 presents a simplified structure of an FPGA chip.

Figure 1.2 - Structure of an FPGA chip

The goal of this thesis is to utilize these modern programmable devices in SoC design. Moreover, IP components are augmented with special *information registers* to identify, verify and optimize their functionality and the system as a whole. These registers are examined thoroughly in chapters four and six.

The work presented in this thesis is carried out during a project called Function Based Platform (FunBase) [fun12]. It is a project that has been created specially from the need of the small to middle sized companies to design and create their own hardware platforms with the same kind of modern design flow that is used to create software.

The objective of the project is to develop a design flow and tools which enable the creation of an FPGA based product much faster and with less effort than before. The design flow also ensures that the development costs are low enough for the small and middle sized companies. In addition, the design flow helps companies with little or no expertise in hardware to create their own systems [kam11, sal11].

It's essential that a company's IP block is packetized so that it can be effortlessly sold and integrated as a part of another system. A company can also purchase IPs from other vendors to be used in their own systems. The project also aims to develop a physical platform to which end user defined functions can be created from modular software and hardware components. Further information of the FunBase project and its design flow can be read in the next chapter.

This thesis is partitioned into seven chapters. The first one is this brief introduction. The second chapter delves a little into the concept of metadata. Chapter 3 explores the tools and methods used in SoC design flow. Chapter 4 studies the concept of IP information registers. Basic concepts of computer graphics are described in chapter 5, and the practical usages IP information registers are explored in chapter 6. Finally, chapter 7 makes conclusions of the usability of these registers.

## 2. Metadata

The term *metadata* refers here to general information about IP components in addition to its source code. This information includes for example, interface specifications, documentation, lists of needed files, tool environment and so on. Most of it is created at design-time but some parts are defined at runtime.

#### 2.1. Requirements from/to IP vendors

Before the actual design of a target system can be started, the requirements for the product must be obtained and accurately defined according to the needs of the customer. After these requirements are known, requirements for the system and its functions can be defined.

The underlying components or IPs which then carry out these functions can be selected from these requirements. The possible vendors for these IPs are then narrowed down to the best ones.

The requirements for the IPs include the required functionality, performance, cost, size etc.

#### 2.2. Design time information

Design time information is information about the implemented system and its components. IP-XACT is a standardized format for capturing it [ipxact10]. Usually, part of the needed IP blocks exist already before the system design starts. Some of these are IPs developed previously in the company and a part is obtained from third party IP vendors.

The components or IPs have information about them that is needed for integrating them into the target system. This design time information includes the *vendor*, *library*, *name and version* (VLNV) of the IP. Information which is important for the integration of the hardware IP to the system include the signal widths and their names, maximum synthesizable speed for a specific FPGA chip or ASIC process, size and power usage of the IP on the specific FPGA etc.

This design time information is not used to verify their functionality but to integrate the IP to the target system.

#### 2.3. Run time information

Run time information is retrieved from the target system by monitoring it somehow.

Physical logic analyzers can be used to do the monitoring. This is however limited to the signals that can be physically probed by the analyzer and any of the internal signals of the chips containing the digital circuits cannot be directly monitored.

Fortunately Altera provides a way to record the signals within a FPGA chip with their SignalTap II Logic Analyzer tool [sig11]. This real time monitoring tool has limited time length for the snapshot(s) of the signal traffic inside the FPGA and also a limited amount of signals that can be monitored at the same time. A typical snapshot has a few dozen signals captured for few thousand cycles. This comes from the simple fact that FPGA chips have limited amount of internal memory and logic elements and a good part of this resource will already be consumed by the actual SoC synthesized to the FPGA. The physical system which has the FPGA has to also be connected directly to a PC so this method is limited to be used in the developer's work space.

# 3. System-on-Chip design flow

Large companies have enough designers to create hardware systems with the old way of designing digital circuits. The IP blocks which are designed this way are often ad-hoc in nature and are only used in the original system for which they were created. However, with a little more planning these digital IPs can be reused in later systems.

Software designers have long been using object oriented programming with different software layers. This has reduced the development costs because software can be reused in the future assuming that the documentation of the functionality is good.

#### 3.1. FunBase SoC design flow

At the heart of the FunBase SoC design flow is the idea that the system specification is divided into different *functional blocks* rather than the actual hardware or software blocks [keut02, san07]. This abstraction provides the flexibility for the developers to design systems which can be later mapped into many different physical platforms. For example, the functionality to calculate a residual image from two input images can be mapped into a software, a hardware or a mixed hardware/software implementation based on the performance and resource usage requirements.

As FunBase is a project in progress there will be later revisions of the design flow but the general idea will remain the same. This thesis describes the first version of the design flow.

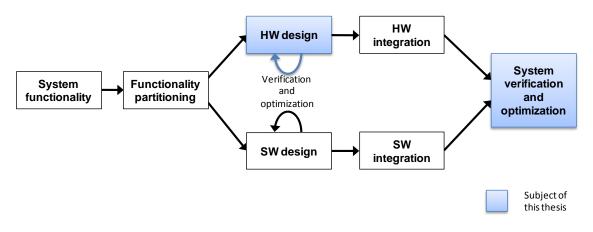

Figure 3.1 - FunBase SoC design flow

The FunBase SoC design flow can be separated in to five parts as illustrated in Figure 3.1. The system's and its components' functionality is defined first. After this the functionalities are partitioned into different hardware and software components. Next, the required hardware and the software components are designed which also includes the verification and optimization of these individual components. After this, the hardware and software are integrated to the system with the FunBase tools and lastly the whole system is verified and optimized. This thesis focuses in improving the processes of hardware and system verification and optimization.

#### 3.1.1. Design tools

The design tools used in the FunBase flow include software which were originally developed at the Tampere University of Technology (TUT), within Altera corporation and the open source community. The tools originating from TUT will be further developed as the project continues.

These tools include Kactus, Library manager, Component Editor, KoskiGUI and several generators created for KoskiGUI [kos09, kam11]. Most of these tools were written in programming languages that either use a virtual machine or run time interpretation to execute the code. This ensures the software's easy portability to several different operating systems including Windows, Linux and Unix. For example the graphical interfaces for the tools were written in Java and the generators run in KoskiGUI were written in scripting languages like Tcl and Python.

Several tools from Altera are also used. These include Quartus II, SOPC builder, FPGA programmer, nios2-downloader and nios2-terminal among others [asoft12].

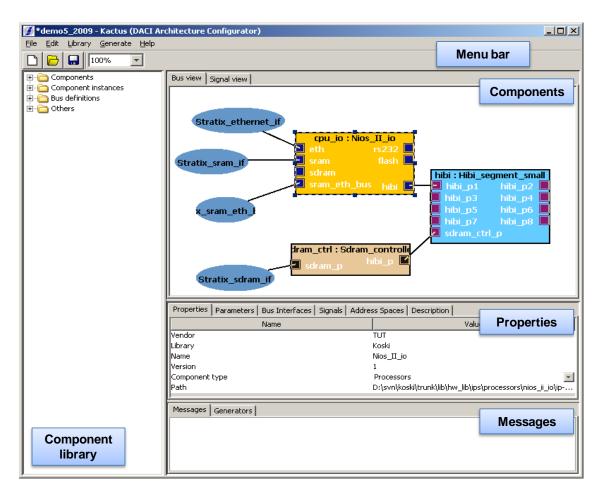

Kactus is a graphical tool written in Java that is used to integrate components to a target hardware platform. It also generates the structural top level description of the hardware platform which is later used in KoskiGUI. The hardware platform consists of components and their connections described in IP-XACT format [ipxact10]. The generated design file for the platform is also in IP-XACT. The user interface for the Kactus tool consists of five sections which can be seen in Figure 3.2. These sections include the menu bar, component library, components, properties and messages section.

Figure 3.2 - Kactus tool

The menu bar is used to create and open projects, configure the program, start the generation of the hardware platform, etc. Components and connections can be selected from the component library and dragged to the components section to create a new architecture. Properties, parameters and other options related to the components can be set in the properties section and any messages related to the generation of the architecture can be seen in the messages section.

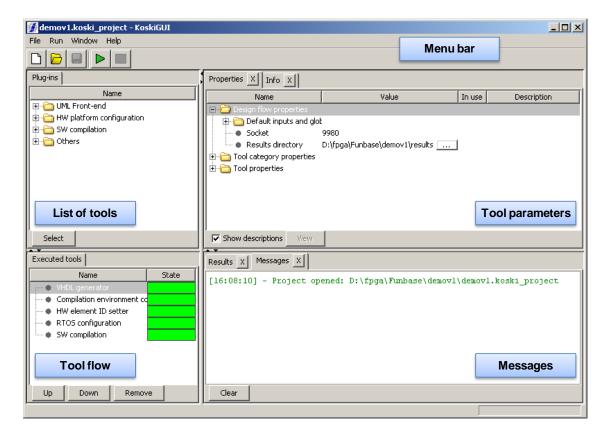

The IP-XACT descriptions for the IP blocks can be created with the Component editor which is launched from the KoskiGUI. It is also possible to create the descriptions with the Eclipse IP-XACT plugin or any other extensible mark-up language (XML) editor including basic text editors. A figure showing KoskiGUI and its main sections can be seen in Figure 3.3.

Figure 3.3 - KoskiGUI tool

KoskiGUI is the tool where the automated generation of hardware description language (HDL) files and compilation of the software code is done. It has five tools which are used for VHDL generation, configuring the compilation environment, setting the HW element identifications (ID), real time operating system (RTOS) configuration and SW compilation.

The IP library is governed with a separate tool called Library Manager. The developer can easily add, remove and modify the IPs in the library with it. This tool is not mandatory but it simplifies and speeds up the design process.

Altera's Quartus II is used to create the blank synthesis project which is later needed by the KoskiGUI. In the first version of the FunBase design flow, Quartus II is also used to synthesize the hardware system to the target FPGA. Other synthesis tools may also be used in later revisions of the design flow. Nios2-download is used in the prototype phase of the FunBase flow to download the software to the Nios II processors on the FPGA. Nios2-terminal is used to debug the system via JTAG-UARTs.

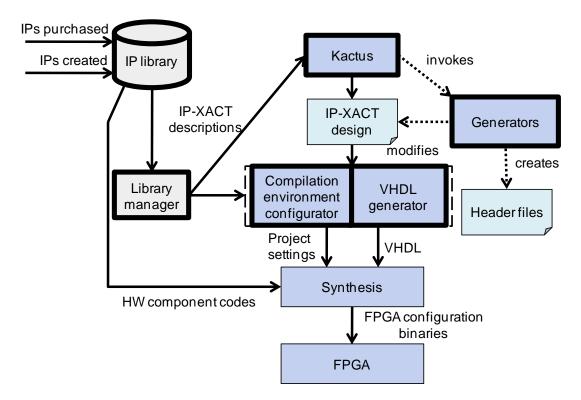

#### 3.1.2. Hardware integration flow

First step in the hardware integration flow, which can be seen in Figure 3.4, is the gathering of all of the necessary hardware IPs to the IP library. These IPs can be added to the library with

the Library Manager. If an IP does not exist in the library it must be created and packetized so that it can be added to the library. It is also possible to purchase already made IPs and packetize them if they were not done according to the FunBase flow.

Figure 3.4 - Hardware integration flow

The main part of packetizing a hardware IP block is to create an IP-XACT description for it. The description includes the vendor name, library name, name of the component and the version. VHDL signal widths must be assigned manually in the first version of the SoC design tools. Bus interfaces are also created to map the VHDL signal names to the logical ones. After the IP-XACT XML file is created it can also be validated separately by the XML validator. This is also done by the VHDL generator in the KoskiGUI but it is better to validate the file as soon as possible.

After the IP is packetized, it is added to the IP library. To create a library component with the Library Manager the developer needs to set the ID, name and the path for the component. The hardware codes along with the IP-XACT definition must be added to the component. Software drivers can also be added.

When all of the required IP blocks are in the library, the developer proceeds to describe the HW platform with the Kactus tool. It has a very intuitive graphical interface where the developer simply adds the IP blocks and the connectors between them to describe the system. After the system is done, it will generate the necessary IP-XACT design needed by KoskiGUI.

In the next step of the integration flow, Quartus II is used to create a blank synthesis project. After this, KoskiGUI is used to run the necessary generators. These generators include the VHDL generator which as the name implies generates the necessary VHDL files required by the synthesis. More specifically it generates all of the VHDL files needed to connect the IP blocks in to a system. Compilation environment configurator and HW element ID setter also modify the VHDL files as is required by the functionality of the system.

The final step in the hardware integration flow is the synthesizing and fitting of the VHDL files to the target FPGA. This is done with the Quartus II tool from Altera.

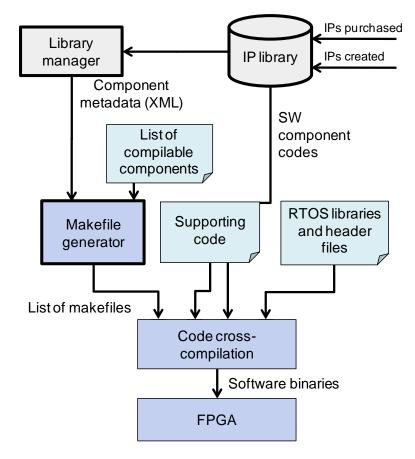

#### 3.1.3. Software integration flow

The software integration flow has fewer phases which use FunBase specific tools as the software industry has long had good tools to automate the design flow of software. A figure illustrating the flow can be seen in Figure 3.5. The software and hardware integration flows also have some overlapping like the adding of the software drivers for the hardware IP blocks in Library manager.

Figure 3.5 - Software integration flow

Version one of the FunBase SoC design flow can use three kinds of processing environments in the target system. These include a Nios II processor [nios11] with an eCos RTOS [ecos11], a transport triggered architecture (TTA) processor [tta11] with no RTOS and a personal computer (PC) environment with an Intel x86 compatible processor running Windows. The PC environment is only used as a part of the target systems in this early stage of the SoC flow but as the FunBase project continues it will be replaced with an embedded processor board with an Intel Atom processor running a Linux RTOS.

Actually, the eCos RTOS will not either be used in later revisions of the SoC flow as there is not a need to have multiple processors running a fully fledged RTOS. The removal of the eCos RTOS decreases unnecessary software overhead and thus the performance of the processor(s) is increased. Another improvement is achieved as the software run on the processor has smaller size.

The software integration flow starts the same as the hardware one with the gathering of the IP blocks needed by the target system. These are then integrated into larger software blocks which are run by the different processors in the system.

After this the RTOS environments are configured by the RTOS configuration tool in the KoskiGUI. And finally all of the software is compiled by the SW compilation tool.

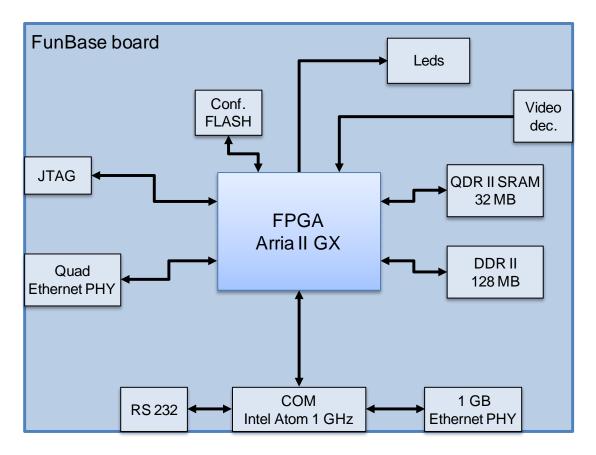

#### 3.2. FunBase hardware platform

Microteam [micro12] which is one of the FunBase partner companies designed a baseboard which can be used as a physical platform for the FunBase SoC design flow. The core of the FunBase baseboard is an Arria II GX FPGA chip manufactured by Altera [arria11]. It is a mid-range FPGA designed for transceiver applications and offers up to 3.75 Gbps of input/output (I/O) bandwidth. As can be seen from Figure 3.6 the board has extensive amount of high speed interfaces to meet the requirements of a broad range of systems. Smaller and less complex boards can and will be later designed based on this baseboard.

Figure 3.6 - FunBase hardware platform

#### 3.3. Altera tools used in FunBase

As the FPGA chips used at TUT are primarily manufactured by Altera there are several tools made by them that are used in the FunBase design flow. Many of them integrate easily to the flow but as can be read in the next section of this thesis there is one that does not.

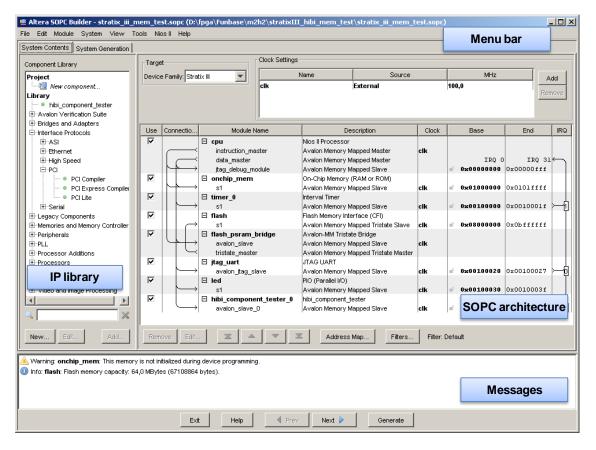

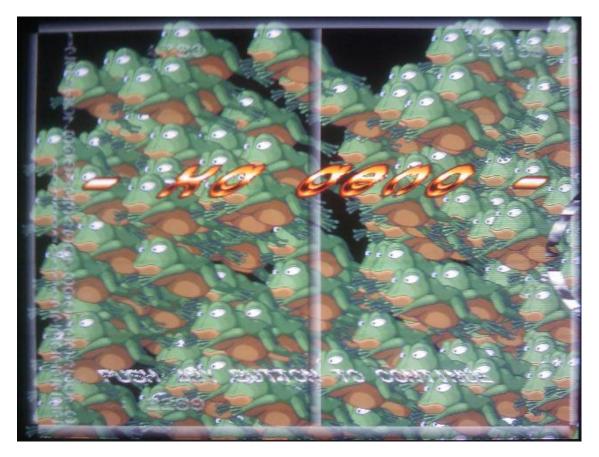

SOPC builder is a hardware design tool which is used to create SOPC sub-systems. These sub-systems comprise of one or multiple Nios II processors and the accompanying peripherals used by the processor(s). In short, SOPC builder can be described as a tool to create soft-core microcontrollers for Altera's FPGAs. The graphical user interface (GUI) of the SOPC builder can be seen in Figure 3.7. A SOPC sub-system is created by adding IP blocks from the IP library section to the SOPC architecture view. In this view the blocks can be configured and mapped into memory regions seen by the CPU(s). The HDL and some configuration files for the system is created by clicking the generate button at the bottom of the GUI. Messages related to the generation and design of the system can be seen in the messages section.

Figure 3.7 - SOPC builder

Quartus II is mostly used to synthesize and program the hardware design of a SoC to an FPGA. However, it is also a hardware design tool and it can be compared with the KoskiGUI tool excluding the software functionality. Like KoskiGUI, it can be used to integrate different tools for the SoC design flow. These tools can be either Altera's own or third-party tools. A dialog showing the third party EDA tool configuration in Quartus II is shown in Figure 3.8.

| ettings - xd_fe_test                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                        |                                                                                      |                                                                  | [                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------|

| Category:                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                        |                                                                                      |                                                                  |                        |

| General     Files     Libraries     Device     Operating Settings and Conditions     Compilation Process Settings     EDA Tool Settings                                                                                                                                                                                                                                                                                                                      | EDA Tool Settings<br>Specify the other EDA tools of<br>on a Tool Type below or selected<br>EDA Tool or to specify option<br>EDA tools: | ect a page under EDA 1                                                               |                                                                  |                        |

| Design Entry/Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                       | Tool type                                                                                                                              | Tool name                                                                            | Format(s)                                                        | Run tool automatically |

| <ul> <li>Simulation</li> <li>Timing Analysis</li> <li>Formal Verification</li> <li>Physical Synthesis</li> <li>Board-Level</li> <li>Analysis &amp; Synthesis Settings</li> <li>Fitter Settings</li> <li>Timing Analysis Settings</li> <li>Assembler</li> <li>Design Assistant</li> <li>SignalTap II Logic Analyzer</li> <li>Logic Analyzer Interface</li> <li>Simulator Settings</li> <li>PowerPlay Power Analyzer Settings</li> <li>SSN Analyzer</li> </ul> | Design Entry/Synthesis<br>Simulation<br>Timing Analysis<br>Formal Verification<br>Physical Synthesis<br>Board-Level                    | Design Compiler<br>ModelSim<br>PrimeTime<br>Conformal LEC<br>Synplify Premier<br>n/a | EDIF<br>Verilog HDL<br>Verilog HDL<br>n/a<br>r/a<br>FPGA Xchange |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |                                                                                      |                                                                  | OK Cancel              |

Figure 3.8 - Quartus II EDA tool configuration

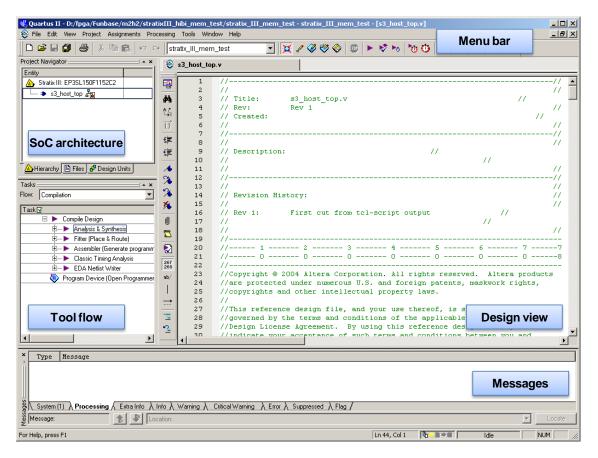

Tools launched from Quartus II are used to integrate, design and verify the architecture of a single SoC that is synthesized to an FPGA chip. It can also be used to create the top level design of the SoC either with a graphical block diagram file or a text based HDL file. SOPC subsystem(s) can be added to this top level design along with other IP blocks. An illustration showing Quartus II and its main sections can be seen in Figure 3.9.

Figure 3.9 - Quartus II

Command line tools like nios2-download and nios2-terminal are used to debug the software on the Nios II processor(s).

Altera's SOPC builder is used to manually create SOPC systems which include one Nios II processor and IP blocks used by the processor. At the time of writing this thesis there have been four of these SOPC systems created for FunBase SoCs. These include three systems specifically made for Altera's Stratix II development board and one for the lower end DE2 development board. In these systems, a Nios II processor is used for fast processing with minimal amount of supporting IPs, a similar setup but with faster memory for the processor, a system with a slower clocked processor but more external communication interfaces and finally a similar system for the DE2 than the previous one. As can be clearly seen, this type of generation of multiple SOPC systems with each one differing little from the other leads to the result that each SOPC system has to be manually created just for one specific platform and this does not fit with the FunBase SoC design flow. Improvements to this SOPC builder integration issue are explored in the next sub-chapter.

#### 3.4. Third party tools used in FunBase

Initially, Nios II processors are used to run software within an eCos RTOS. This RTOS is configured and the software library components are generated manually with the *ecosconfigtool* [ecos11]. The eCos RTOS has to be configured and generated for each of the different SOPC systems. This leads to a similar problem as was earlier described with the SOPC system generation. Fortunately for the FunBase project, it has been decided that the eCos RTOS is not really needed and will be replaced with a software model without a fully fledged RTOS.

In the future, the Nios II integrated development environment (IDE) is used to create the software library files. UCos II RTOS could also be used. Nios II IDE can be controlled by command line tools so integrating it to the FunBase SoC flow is fairly easy.

#### 3.5. Third party IPs used in FunBase

These IPs include memory controllers, timer units, jtag-uarts, etc. Researchers at TUT have done some IPs which are used in the SOPC environment but they can also be used outside it with small modifications.

All of the IPs provided by Altera require some kind of generation. A part of the IPs can be generated outside the SOPC environment with the Megawizard tool included in Quartus II but the rest have to be generated into a SOPC system.

The SOPC IP blocks are manually designed by using the graphical user interface (GUI) of the SOPC builder.

#### 3.6. Improving the integration of Altera tools to FunBase

Since the tools for the Altera corporation and the FunBase flow were developed separately, there is bound to be some overlapping between them. The best example of this overlap is Altera's SOPC builder tool.

The SOPC systems created with the SOPC builder tool cannot be modified directly by the first generation FunBase tools. Hence, they are treated as any other IP block the internal structure of which cannot be changed with the FunBase tools. It can be said that they have even less adaptability than most IP blocks because they do not even have parameters to configure like many IP blocks.

These two reasons make the integration of IP blocks with an Avalon switch fabric interface require more knowledge about Altera's tools along with more work. To improve the situation, the tools have to be better integrated as a part of the FunBase SoC design flow.

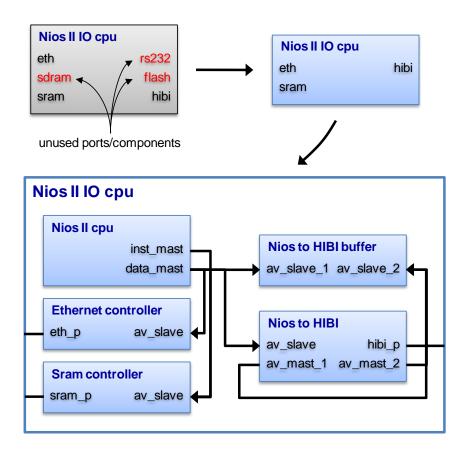

To better integrate the SOPC tool to the FunBase flow, SOPC blocks have to be customizable with the Kactus tool. An example illustration of how the presentation of a SOPC block would be changed in a future version of Kactus is given in Figure 3.10. The grey CPU block indicates the situation as of now and the blue one is how the block would look like in the new version of Kactus with the internal architecture of the SOPC block hidden. The big transparent block shows what the SOPC block would look like with the internal architecture revealed. By enabling the Kactus tool to customize the SOPC blocks, any unnecessary components within the blocks can be removed. This is also shown in the figure below.

Figure 3.10 - Improving the integration of the SOPC builder to the Kactus tool

There are basically three different approaches for implementing this customization and improving the integration. The first one includes generating a large SOPC system which contains all the IPs that cannot be generated with the Megawizard in Quartus II and using these IP blocks with a Wishbone bus or similar. Similarly in the second approach one large SOPC system is designed but from which the Kactus tool will disable all the unnecessary IPs and then generate this customized system. The third approach would be to create a generator for the

SOPC system configuration file so that the Kactus tool could build any SOPC system which can be created with the actual SOPC builder.

#### 3.6.1. SOPC builder integration approach one

Many of the IPs used in SOPC systems can only be generated within one. To use them outside they must be first generated into a SOPC system. After this the generated HDL file for the particular IP can be used to instantiate the IP outside the SOPC system it came from.

In this approach IPs and all their variations, which can only be generated with the SOPC builder, are generated into HDL files as was earlier described. These IPs are then packetized the same way any other IP is packetized for the FunBase SoC design flow.

This way of dealing with the SOPC builder integration problem would unfortunately create other problems and limitations that would have to be dealt with. These IPs would have an Avalon interface but no Avalon bus and the required arbitrators. Fortunately the Avalon interface is very similar to the Wishbone interface so the IP blocks could be connected to a Wishbone bus in a pretty straightforward manner. Wrappers could also be made to interface them with a Heterogeneous IP Block Interconnection (HIBI) bus [sal01].

There would be one major limitation with this approach. The IPs could not be configured like they can be with the SOPC builder so that multiple variations would have to be made to compensate for this. For example, many variations of the Nios II processor with different cache sizes and other properties would have to be generated beforehand. Memory controller variations for each different type of external memory would also have to be made. Considerable time would also have to be committed to packetize all these components.

For all these reasons, this approach would not obviously fit with the targets of the FunBase SoC design flow.

#### 3.6.2. SOPC builder integration approach two

The second approach adds a new feature to the Kactus tool. The developer could add a configurable SOPC system to the Kactus project and decide what components would be generated into it.

To enable the creation of this new feature, one large SOPC system would initially be designed but only one variation of each of the IPs would be placed in the system. This system would then be treated as a starting point from which a modified SOPC system would be generated according to the developer's decisions.

After the developer had made the SOPC system along with the components outside it, the Kactus tool would then modify the base SOPC system configuration file and initiate the generation of this modified SOPC system. The modification would simply include three kinds of operations. First the Kactus tool could disable any unnecessary components, secondly it could make copies of the components and finally it could change the configuration parameters of the components. As a result, Kactus could make any SOPC system which included the components found in the base SOPC system.

In this approach the Avalon bus would not have to be replaced and more importantly excessive time used for generating and packetizing the IPs could be avoided. Considerable work would still have to be done so that Kactus could make the required modifications to the SOPC system's configuration file.

#### 3.6.3. SOPC builder integration approach three

The last approach adds the ability to fully create a SOPC system configuration file to Kactus. This would include the most work of all of the three different approaches and it would not necessarily offer significant advantages over the second approach.

#### 3.6.4. SOPC builder integration conclusion

As a conclusion, it can be said that the second approach is the one to go for. If it would not be sufficient for some reason, the work put to adding the SOPC system configuration file modification function to the Kactus tool could be continued and full generation of the configuration file could be achieved.

#### 3.7. FunBase case study

To demonstrate the main capability of the FunBase SoC design flow an example system is created. As was earlier stated in this chapter, the main idea of the FunBase SoC flow is to treat parts of a system as functions rather than actual hardware or software components. This way the functions can be later mapped to the actual components based on the requirements and limitations of the target platform.

#### 3.7.1. Image residual with different hardware architectures

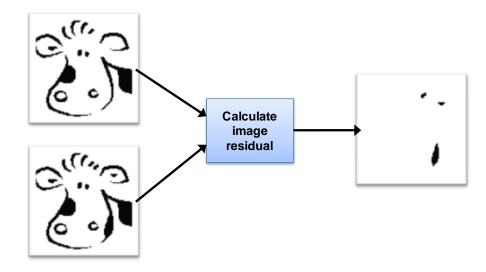

This case study deals with a system capable of producing a residual image of two input images. The residual of two images shows the differences between them. An illustration of this functionality is given Figure 3.11.

Figure 3.11 - Calculation of a residual from two images

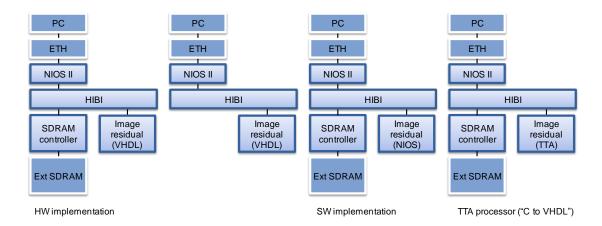

Four different hardware architecture variations are created to demonstrate the function abstraction capability of the FunBase SoC design. The structure of these architectures is depicted in Figure 3.12.

Figure 3.12 - Image residual with different hardware architectures

In these architectures, the image residual function stays unchanged as the underlying implementation changes. The function is implemented with two hardware only, one software only and a mixed hardware/software implementation. In the hardware only implementations, the image residual function is performed with a hardware component with and without using an

external SDRAM chip. The software implementation uses a Nios II processor with SDRAM and the mixed implementation uses a TTA processor with SDRAM. This specific TTA processor was developed at TUT and is generated from C software source files into a hardware accelerated version of the software.

## 4. IP information registers

As was already discussed in the introduction for this thesis, traditional software simulation offers the possibility to examine signals through relative long time periods but extra effort is needed to create the simulation models for the whole range of hardware components. If the simulation models for the components behave the same way as their physical counterparts, the registertransfer level (RTL) simulation provides a view to the system's signals on a clock cycle level. But as the system is simulated on this level, the time needed to carry out a sufficiently long simulation can be measured in days or even weeks. This of course makes it practically impossible to iterate the verification process with these kinds of simulations, as was already noted.

The other way currently to verify the behavior of a system is to use some kind of hardware probing. Altera provides a tool for this called the SignalTap II Logic Analyzer. With this tool, signals can be probed directly from an FPGA chip at runtime. There are though a couple of critical disadvantages with this method. Only a small group of signals over a short time period can be examined at a time due to the finite logic cell and routing resources of the FPGA chip. Also if the design of a SoC consumes nearly all of these resources it will be impossible to use this kind of probing.

It would be good to have the means to record events and information from a physical prototype through long time periods [sal11].

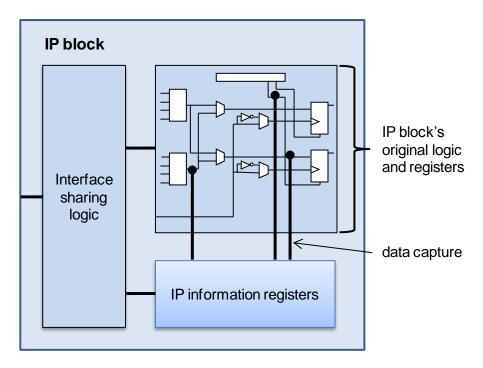

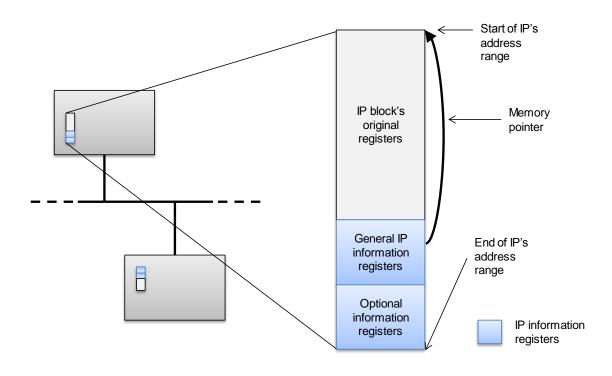

To achieve this goal, the specification for these information registers, which are embedded to IP blocks, were developed for this thesis. These registers are added alongside the pre-existing ones and are filled with important information from the blocks and the system at run time. This information is used to check the IP blocks and the system for possible error events which may significantly aid the verification process. Information is also used to optimize the performance. Additionally the registers can be used to identify IP blocks and their place on a CPU's address map. An illustration of what the architecture of an IP block with embedded IP information

registers (IIR) looks like is given in Figure 4.1. The bus interface is on the left. Information registers are distinct from the regular ones in this example and hence, separate logic for interface sharing (arbitrator) is needed.

Figure 4.1 - IP block with embedded information registers

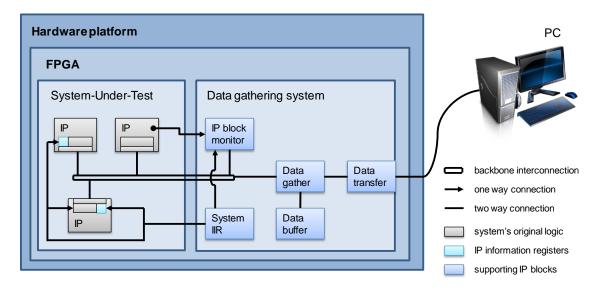

A simplified test setup using the information registers is depicted in Figure 4.2. The setup includes a System-Under-Test (SUT), a data gathering system attached to it and a PC to analyze the data.

Figure 4.2 - A test setup with IP information registers

#### 4.1. Verification and optimization flow

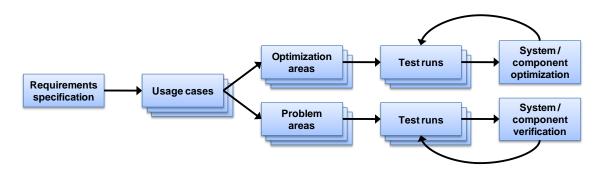

The flow for the verification and optimization process using the IP information registers is depicted in Figure 4.3. In this flow, a set of usage cases are defined from the requirements specification for the system. Possible optimization areas for the system and the IP blocks are explored and defined from the usage cases. And if any problem areas can be found they are also defined. After this, concrete plans for test runs for the system are specified.

Figure 4.3 - Verification and optimization flow with IP information registers

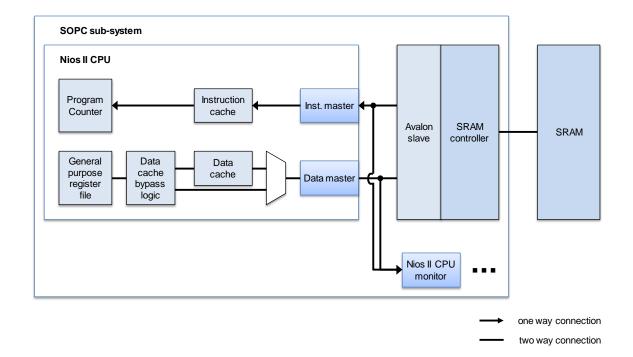

After the test run is initiated, the data gathering system periodically accesses the IP blocks and reads the contents of their information registers. After this, the gathered data is stored in a temporary data storage unit and sent to the developer's PC for analysis after the test run has completed.

Any parts not up to the original specification or any areas for optimization are addressed by the developer. After the possible corrections and optimizations are made, the same test run is repeated to analyze the outcome of these changes. This process is then iterated as many times it is necessary to achieve the wanted results.

#### 4.2. Resources

One needs some extra logic and routing resources from an FPGA chip to instantiate the required components for information gathering. These components can be divided into IP information registers and supporting IP blocks. These registers and blocks can be seen in the earlier Figure 4.2. As can be seen from the figure, the data gathering unit is attached to the same backbone interconnection that connects the SUT's IP blocks. This way there is no need for an additional bus to be used to retrieve the data from the information registers.

External IP block monitors can also be attached to the backbone bus to monitor IP blocks with no embedded information registers.

A version of the test setup with a dedicated IP information bus could be later designed to gather information which requires continuous monitoring along with a high data bandwidth.

### 4.2.1. Register and interconnection types

The term register is used loosely in this thesis as there can be multiple physical registers or even on-chip memories behind them. A register is only used to describe an entry point for the underlying memory.

IP information registers come in three main types which include regular, fifo and special header registers. These registers are described in Table 4.1.

| Register type | R/W/C | Description                                                                                         |

|---------------|-------|-----------------------------------------------------------------------------------------------------|

| Regular       | R/W/C | A single word                                                                                       |

| Fifo          | R     | The number of words is known and only words containing the actual values are stored                 |

| IIR header    | R     | The words are stored normally and a word with all bits set to one indicates the end of the register |

Table 4.1 - IP information register types

Regular registers can be subjected to three kinds of operations which include reading (R), writing (W) and clearing (C) the information on the register. A register can be either writable or clearable but not both. A register's content is cleared by writing any word to the register. No specific word is defined to reduce the amount of needed logic.

Fifo registers are associated with the logging capabilities in certain information registers. These fifo registers act as read only sources for the data stored by the logging logic. Finally the read only IIR header register has special functionality which allows it to change its contents during sequential accesses. IIR header registers are further described in the next sub-chapter.

The register map of an IIR enabled block is divided into three different parts as can be seen in Figure 4.4. These parts include the IP block's original registers, the general information registers and the optional information registers. The structure and functionality of these registers are described in later sub-chapters.

Figure 4.4 - IP information registers in IP block's memory space

## 4.2.2. General information registers

The general information registers contain registers to identify the parent IP block along with other miscellaneous data and functionality.

To comply with the specification, an IP block has to reserve a continuous address space for at least the general information registers which are described in Table 4.2. Offsets are given as 32-bit words. This address space can reside anywhere within the IP block's greater address space.

| Offset | R/W/C | Name                     | Description                                             |

|--------|-------|--------------------------|---------------------------------------------------------|

| 0x00   | R     | IIR1 header              | A 32-bit header that inverts its byte ordering on reads |

| 0x01   | R     | IIR type                 | 0: internal IIR, 1: external IIR                        |

| 0x02   | R     | IP reg. offset / address | Memory pointer in Figure 4.4                            |

| 0x03   | R/W   | IP reset                 | Can be used to reset the IP-block                       |

| 0x04   | R     | Instance number          | Number to distinguish different instances of IIR blocks |

| 0x05   | R/W   | Mutex                    | Used in multi-master systems                            |

| 0x06   | R     | VLNV                     |                                                         |

|        | R     |                          | Four ascii strings separated by null bytes              |

| 0xXX   | R     | VLNV                     |                                                         |

| 0xXX   | R     | Extra information        | Optional information, fill with zeros if not used       |

Table 4.2 - General information register layout

The arbitrary placement of this address space is enabled by the IIR1 header register which is a special read only register used to identify the address space. This register returns a 32-bit ascii string reading "IIR1" on first access, and a "1RII" string on second access. Successive accesses will repeat the same alternating pattern. Using this unique characteristic, a processor can scan its full address space looking for IIR enabled IP blocks.

The second register contains three bits of information about the IIRs and the parent block. If the first bit on this register is one, the IIR block is external but otherwise it resides inside the parent IP. Secondly, the parent IP has accessible registers if the second bit is one. For example a Nios II CPU has not got any registers accessible outside and therefore its external IIR block has this bit set to zero. Lastly, if the third bit of this register is set to one the parent IP can be set to a reset state and the reset register on the IIR block is enabled. The SRAM controller used in this thesis cannot be set to a reset state and has this bit set to zero.

The information on the previous register determines how the third register is interpreted and it either has an IP register offset or an address. If the IIR block is internal this register provides the offset pointing to the parent block's registers otherwise it provides a direct address to the registers. The direct address has to be set manually before synthesis. If the IP block has not got any accessible registers this register is set to zero.

An IIR enabled IP block has usually two reset signals. A system reset which comes from outside of the IP and an internal IP reset signal coming from the IP reset register. The fourth register is this reset register which can set the parent IP block to a reset state for example to recover from an error event. The reset is active high and it should normally be set to low at system reset.

If the IIR block of an IP is accessed by more than one component on the system, a multiple access mutex has to be implemented on that block. The mutex is the fifth register and it has to be used when accessing registers which operation has to be uniform and to ensure that when one block (e.g. a Nios II CPU) is accessing the registers no other component will interfere with the access.

The VLNV registers have four ASCII strings of basic information concerning the IP block and its creator. The strings are null terminated and include the vendor name, the library name, the name of the component as well as the component's version.

Lastly, the extra information registers are optional and can be used to store additional information pertaining to the parent IP or the IIR block. The string on the registers is null terminated and has to be filled with zeros if not in use. Useful information on these registers could for example be the design date of the parent IP.

#### 4.2.3. Optional information registers

The optional information registers reside right after the general information registers and accommodate registers specific to the IP block. These registers mainly provide functionality to verify and optimize the IP block and the system. Other useful functions like usage statistics are described in Table 4.3.

| Usage        | Example                                                                        |  |  |

|--------------|--------------------------------------------------------------------------------|--|--|

|              | Log to examine CPU crashes                                                     |  |  |

| Verification | Number of faulty write or read accesses done to IP block                       |  |  |

|              | Clock cycles without write or read accesses done to IP block                   |  |  |

| Optimization | Log to optimize shared memory usage                                            |  |  |

|              | Number of write or read accesses done to IP block                              |  |  |

| Statistics   | Number of cycles/frames from reset                                             |  |  |

| Statistics   | Bytes written to frame/line buffer in a frame/period of frames (eg. fill rate) |  |  |

|              | Log to store unused frame/line buffer cycles                                   |  |  |

Table 4.3 - Optional information register usages

The log registers which can be present in the optional information registers are described further in chapter 6.

## 4.3. Supporting IP blocks

There are five different kinds of supporting IP blocks defined in this specification: the data gathering unit, data transfer unit, data buffer, system IIR and the external IP block monitor. These were previously illustrated in Figure 4.2.

#### 4.3.1. Data gathering unit

To transfer the data from the IP information registers to the developer, a data gathering mechanism has to be implemented. There are basically two different approaches to implementing this mechanism.

Both approaches include a data gathering unit on the FPGA and a connection from this unit to the PC. The first approach sends data continuously to the PC whereas in the second approach the data is written to a data buffer during the monitoring and sent to the PC after the monitoring ends. The second approach might be the only viable one if the data bandwidth for the gathered information is too large to be sent in real time. Unfortunately this approach is not always practical in systems meant for the end user market.

The data gathering unit can either be a processor or a custom data gathering component.

#### 4.3.2. Data transfer unit

To transfer the data to the PC and the developer, a connection is naturally required for it. Additionally to interface this connection to the FPGA, a controller for the connection has to be included. These two blocks form the data transfer unit.

Depending on the bandwidth and other requirements for the connection, some of the following connections can be considered: a USB connection with a virtual JTAG UART, a USB connection with a proprietary transfer protocol, a serial RS232 connection or an ethernet connection. JTAG UARTS and RS232 connections are traditionally quite slow (in the order of 100 kbs) [tex02] and therefore are not sufficient for many systems. A USB connection on the other hand can vary from the slow 1.0 standard (1.5 Mbs) to the ultra high speed standard of 3.0 (4.8 Gbs). As the 3.0 standard is quite new and not mature, the transfer speed of a USB connection is practically limited to the speed of the 2.0 standard (480 Mbs) [usb11]. An ethernet connection can have a maximum speed varying from 10 Mbs to 10 Gbs. Though ethernet controllers for the basic customer market support only up to 1 Gbs speed [eth08].

#### 4.3.3. Temporary data memory

The temporary data memory comprises of an actual physical memory and its controller. The unit is used if the gathered data is sent to the PC after the monitoring is done. Of course the system must have a memory with extra space and bandwidth on it. Considering the latter two requirements, this will not usually be plausible to be used on a product that is used by the end user.

This unit can be really useful when a system is verified or optimized on a development platform and the collected information requires high data bandwidth. It subsequently removes the need for a high bandwidth connection to the PC because the data does not need to be transferred in real time.

#### 4.3.4. System IIR

A system IIR is a special IIR block that has information pertaining to the system and also provides services to regular IIR blocks. In the first version of the IIR specification, it provides a service with its embedded system counter.

The system counter is very basic in its functionality but it still offers one of the main functions of the IP information registers which is the ability to store timestamps in the log registers. It is constructed of only one 32 or 64-bit wide counter. This counter is set to zero when the system reset is active and incremented by one on every clock cycle when the system reset is inactive. The counter is then connected to all of the IIR blocks that have log register(s).

Additionally the VLNV registers on the system IIR can be used to discern if a program run on the system's CPU was meant for the system, as is done on the first part of the usage case in chapter six. This functionality can be especially useful for developers dealing with FPGAs who can accidentally use either a wrong FPGA configuration or a wrong program.

#### 4.3.5. IP monitor

An additional IP monitor is needed for each IP block that does not have information registers and cannot be modified for some reason. For example a Nios II processor can only be monitored by an external IP monitor because the HDL of the Nios II processor is encrypted and therefore not modifiable. This kind of an IP monitor implements all the required information registers. The VLNV registers of such a monitor should be filled with information associated with the monitored IP block.

# 5. Basics of computer graphics

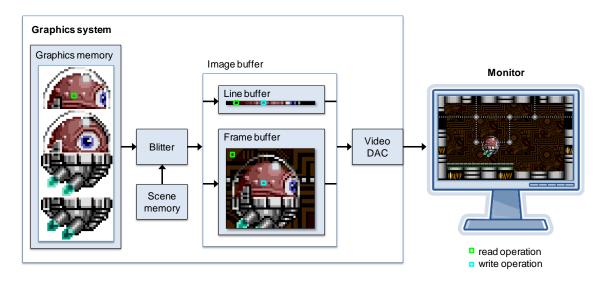

One needs to know the basics of computer graphics to understand how IP information registers can be used to optimize a 2D graphics system in the case study for this thesis. There are many different kinds of methods and hardware designed to generate computer graphics, but there is a set of basic concepts behind them [ake08, eck01].

This chapter describes a part of these concepts along with the basic functionality of computer monitors and the graphical elements used in line buffer based graphical processing units (GPU).

Every graphics system consists of five main components. These include the graphics memory, blitter, scene memory, image buffer and the digital to analog converter (DAC). These components are shown in Figure 5.1. The contents of the graphics memory and image buffers are only partially visible to save space.

Figure 5.1 - Image generation methods

## 5.1. Color information

Every pixel on an image buffer has to be described as a binary number. The color of the pixel can either be directly read from this number or can be derived from this number using a color palette [eck01]. Many of the devices intended for customer markets from the 1970s to the start of the 1990s recorded the pixels' color information as index number tied to a color palette. Figure 5.2 shows 4-bit color palette with 16 different colors.

| 0 1 2 3   | 4 5 6 7     |

|-----------|-------------|

| 8 9 10 11 | 12 13 14 15 |

Figure 5.2 - Example of a 4-bit color palette

The colors of pixels are usually coded in RGB format where every color consists from a combination of three base colors (red, green and blue). If every one of these base colors is described with 8 bits, the pixels colours consists of a combined 24 bits which can define 16 million of different colors. This color format is in wide use in modern graphics systems.

## 5.2. Image buffers

An image buffer is an area of memory where a processor or a GPU can store a part or the whole displayed image. The GPU reads this image buffer in the pace the processor has instructed and sends the color information to the DAC. The DAC then converts the information into an analog signal that is relayed to the monitor.

Digital circuits that generate pixel based 2D images can be divided into two categories based on which kind of an image buffer it uses for the generated image. As can earlier be seen in Figure 5.1, these buffers include the line and the frame buffer [adv84]. Both of these buffers have advantages and disadvantages associated with them.

Japanese game company Namco developed the first line buffer based graphics system for the arcade game Galaxian in 1980 [adv84]. The 8 and 16-bit videogame consoles used mainly this technology until the early 1990s. This buffer type is still used in some modern video signal processors like the YGV629 [yam08] from Yamaha and MB88F332 [fuj09] 'Indigo' from Fujitsu. It needs less memory than the frame buffer and can be implemented in onchip-memories, but it also makes the generation of the image harder and more restricted.

A frame buffer which stores the entire image, makes the image generation easier and less restricted than with a line buffer. But unlike the line buffer it cannot be practically implemented in a SoC and needs an external memory. This makes it the more expensive approach.

Nowadays memories are fairly cheap and modern day GPUs use mainly frame buffers to generate the displayed image. More specifically they usually use double buffering to achieve a clean looking moving image. A GPU implementing double buffering writes the next displayed image to one buffer while the image currently being displayed is read from the other buffer. These two buffers are then switched as the next image is started to be displayed. The same kind of double buffering can also be used with line buffers.

Image size directly defines the needed line or frame buffer size. Table 5.1 shows the double buffered line and frame buffer sizes for four common video standards [vga, atsc08, ebu10].

| Video<br>standard | Image<br>dimensions | bytes/pixel | line buffer<br>size* (bytes) | frame buffer<br>size* (bytes) | proportional<br>frame buffer<br>size |

|-------------------|---------------------|-------------|------------------------------|-------------------------------|--------------------------------------|

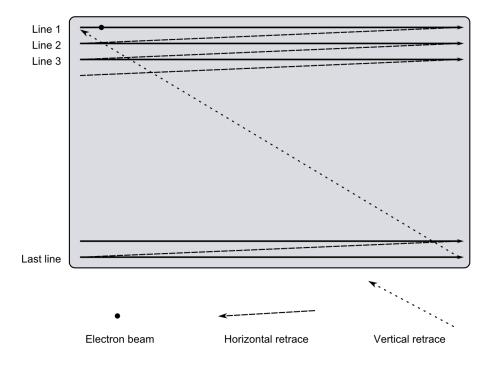

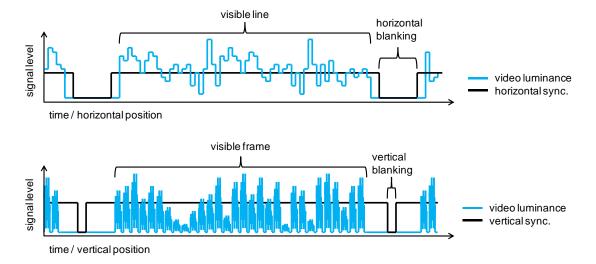

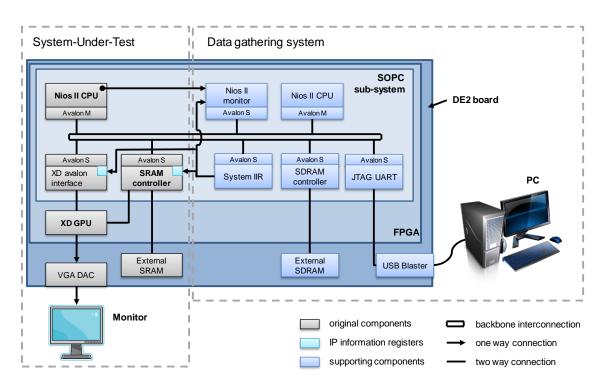

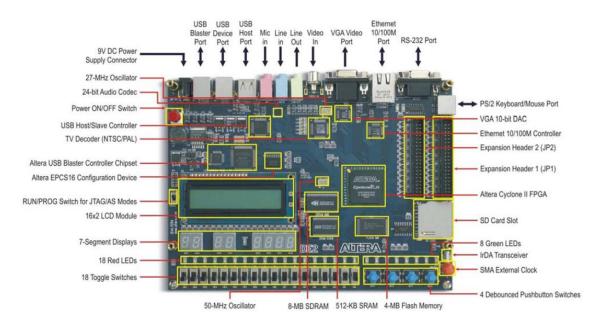

| VGA               | 640*480             | 4           | 5 120                        | 2 457 600                     | 480                                  |