## Achieving saturation in vertical organic transistors for organic light-emitting diode driving by nanorod channel geometric control

Chang-Hung Li, Fabrice Stehlin, Kai-Ruei Wang, Yu-Hsin Lin, Fernand Wieder, Olivier Soppera, Hsiao-Wen Zan, and Hsin-Fei Meng

Citation: Appl. Phys. Lett. 102, 163305 (2013); doi: 10.1063/1.4802999

View online: https://doi.org/10.1063/1.4802999

View Table of Contents: http://aip.scitation.org/toc/apl/102/16

Published by the American Institute of Physics

## Articles you may be interested in

Polymer space-charge-limited transistor

Applied Physics Letters 88, 223510 (2006); 10.1063/1.2207838

An all  $C_{60}$  vertical transistor for high frequency and high current density applications

Applied Physics Letters 101, 213303 (2012); 10.1063/1.4767391

Polymer space-charge-limited transistor as a solid-state vacuum tube triode

Applied Physics Letters 97, 223307 (2010); 10.1063/1.3513334

Reduced hole injection barrier for achieving ultralow voltage polymer space-charge-limited transistor with a high on/off current ratio

Applied Physics Letters 95, 203305 (2009); 10.1063/1.3261749

Vertical organic light-emitting transistor showing a high current on/off ratio through dielectric encapsulation for the effective charge pathway

Journal of Applied Physics 121, 024502 (2017); 10.1063/1.4974008

Polymer hot-carrier transistor

Applied Physics Letters 87, 253508 (2005); 10.1063/1.2149219

## Achieving saturation in vertical organic transistors for organic light-emitting diode driving by nanorod channel geometric control

Chang-Hung Li, <sup>1</sup> Fabrice Stehlin, <sup>2</sup> Kai-Ruei Wang, <sup>1</sup> Yu-Hsin Lin, <sup>3</sup> Fernand Wieder, <sup>2</sup> Olivier Soppera, <sup>2,a)</sup> Hsiao-Wen Zan, <sup>1,b)</sup> and Hsin-Fei Meng<sup>3,c)</sup>

<sup>1</sup>Department of Photonics and Institute of Electro-Optics, National Chiao Tung University, 1001 Ta Hsueh Rd., 300 HsinChu, Taiwan

<sup>2</sup>Institut de Science des Matériaux de Mulhouse (IS2M), CNRS-UMR 7361, Université de Haute Alsace, 15 rue Jean Starcky, Mulhouse, France

<sup>3</sup>Institute of Physics, National Chiao Tung University, 1001 Ta Hsueh Rd., 300 HsinChu, Taiwan

(Received 7 February 2013; accepted 10 April 2013; published online 25 April 2013)

When conventional field-effect transistors with short channel length suffer from non-saturated output characteristics, this work proposed a vertical channel transistor to operate like a solid-state vacuum tube and exhibit good saturated curves. We utilized deep ultra-violet interference lithography to produce ordered grid-like metal to control the potential profile in vertical channel. We compared experimental and simulated characteristics to investigate the keys to achieve saturation. Finally, with an optimized design, a vertical organic transistor is used to drive a solution-processed white-light organic light-emitting diode to perform a luminescence control (0–260 cd/m²) with a 3.3-V base potential swing. © 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4802999]

Solution-processed organic transistors have attracted lots of attentions due to the low-cost and low-temperature process for the potential applications on flexible electronics and active-matrix organic light-emitting diode (OLED). The low mobility of organic semiconductor materials, however, limits the output current in conventional organic field-effect transistor (OFET). To increase the output current, OFETs with submicron-meter short channel length were demonstrated. The accompanying short channel effects, however, cause non-saturated output characteristics. For OLED driving, stable output current from the driving transistor is required by controlling the gate bias. It is difficult to use short-channel OFETs with non-saturated output characteristics for OLED driving.

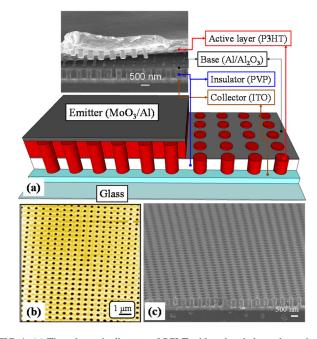

To deliver high current at low operation voltage, several kinds of organic transistors with vertical short channel were also developed.<sup>6,7</sup> In our previous work, we demonstrated the best solution-processed vertical-channel organic transistor, space-charge-limited transistor (SCLT), to deliver 50 mA/cm<sup>2</sup> (high enough for OLED driving) at 2 V with an on/off current ratio larger than 10000.8 Such transistor operates like a solidstate vacuum tube. Several previous studies on such transistor reported non-saturated output characteristics. Here, we first investigate the key to obtain saturated output curves of SCLT. To specifically analyze the geometric effect, we produce SCLT with ordered channel openings (diameter changes from 450 nm to 300 nm) by using interference lithography. Without opening accumulation, a very good match between experimental and simulated (TCAD SILVACO ATLAS software) output characteristics can be observed for various geometric designs. Increasing the distance between emitter electrode and base electrode can effectively turn nonsaturated output characteristics to become saturated output The schematic diagram of SCLT with ordered channel openings is shown in Fig. 1(a). Using poly(3-hexylthiophene) (P3HT) as the p-type channel material, holes are injected from emitter electrode into P3HT and flow through

FIG. 1. (a) The schematic diagram of SCLT with ordered channel openings. (b) The AFM image of the well-ordered porous structure of the substrate after aluminum wet etching. (c) The SEM image of the substrate after oxygen plasma etching.

characteristics. Increasing aspect ratio of the vertical channel is also critical for suppressing the off-state current. Finally, we reduce opening diameter into 100-nm by using colloidal lithography and produce SCLT with highly saturated output characteristics within a cross voltage as 15 V. With a 8-V total cross voltage, the SCLT is then connected with solution-processed white-light OLED to perform a luminescence control (0–260 cd/m²) with a 3.3-V base potential swing.

a) olivier.soppera@uha.fr

b)hsiaowen@mail.nctu.edu.tw

c)meng@mail.nctu.edu.tw

vertical channel to arrive collector electrode. Porous base electrode is used to control the potential profile inside the openings and hence control the on and off states of the vertical channel. Diameter of the openings significantly influences the base control over the vertical channel. In our previous work, colloidal lithography with polystyrene (PS) spheres is used to produce the channel openings. The accumulation of PS spheres causes variation of opening diameter. Here, to perform an exact analysis with a well-controlled opening diameter, ordered channel openings are fabricated by using interference lithography. No accumulation of the opening can be observed.

The fabrication process is briefly introduced below while the detailed description is provided in supplementary material. We first prepared a glass substrate with patterned indium tin oxide (ITO) as the collector (C). Then, we spun cross-linkable poly(4-vinyl phenol) (PVP) with the thickness ranged from 200 to 500 nm as the organic insulator. After that, a 40-nm-thick aluminum (Al) as the base (B) was deposited onto PVP by thermal evaporation. A Zr-based sol-gel negative tone resist was spun onto Al with a soft baking at 100 °C for 1 min. Then, ZrO<sub>2</sub> porous structure was formed by using interference lithography with a deep-ultraviolet (DUV, wavelength 193 nm) light source. Details of the Zr sol-gel preparation and the DUV interference irradiation were addressed in Ref. 12 and in supplementary material. 11 The interest of this home-made photoresist is to fulfill the requirements in terms of resolution, adhesion in the Al layer, and resistance to etching. With a fixed pitch as 600 nm, the diameter of hole was changed from 450 nm to 300 nm. The Al inside hole region was etched by standard wet etchant, and a porous grid-like Al metal sheet was formed. Then, we used oxygen plasma to etch through the PVP layer to fabricate the vertical cylindrical hole. An Al<sub>2</sub>O<sub>3</sub> thin film was formed on the surface of grid-like Al after the oxygen plasma treatment. ZrO2 above Al was also removed by oxygen plasma. Figure 1(b) shows the atomic force microscope (AFM) image of the well-ordered porous structure of the substrate after aluminum wet etching. Figure 1(c) shows the scanning electron microscope (SEM) image of the substrate after oxygen plasma etching, ordered vertical cylindrical holes are observed. After the vertical channel was formed, we immersed the samples into octadecyltrichlorosilane (OTS-18) for 2 h to form self-assemble monolayer (SAM) on the substrate. Then, P3HT as active layer was coated on the template by blade-coating as in our previous works. The SAM treatment enhances the pore-filling and the inter-chain order of P3HT. Finally, the emitter (E) electrode (bilayer of MoO<sub>3</sub> as 10 nm and Al as 100 nm) was deposited by thermal evaporation to finish the transistor with an active region as 1 mm<sup>2</sup>.

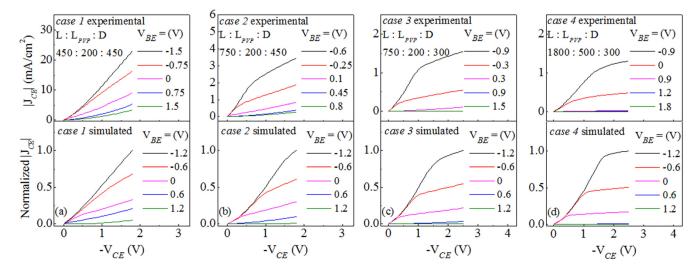

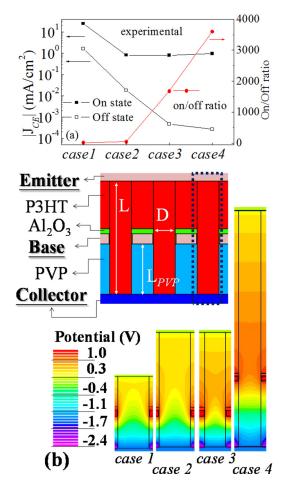

The influence of geometric design on the saturation behavior is first investigated. We produce SCLT with 4 different geometric designs. The experimental output characteristics of these 4 SCLTs are shown in upper part of Figs. 2(a)-2(d), respectively. The corresponding simulated output characteristics are shown in lower part of Figs. 2(a)-2(d), respectively. Commercial TCAD SILVACO ATLAS software is used with parameters given in Ref. 13. For simulated results, we want to focus on observing the output current behavior and to ignore the discrepancy of the current amount in different cases. Hence, simulated output characteristics were normalized to the highest current value. In case 1, opening (pore) diameter (D) is 450 nm, PVP thickness ( $L_{PVP}$ ) is 200 nm, and P3HT thickness (i.e., the vertical channel length, L) is equal to the pore diameter as 450 nm. Both experimental and simulated results show poor non-saturated curves. Then, in case 2, we increase P3HT thickness to be 750 nm and keep pore diameter as 450 nm and PVP thickness as 200 nm. Slightly saturated output characteristics can be obtained in Fig. 2(b). To improve the leakage current in the off state, which will be addressed more in the following section, we reduce pore diameter to be 300 nm in case 3 (PVP = 200 nm, P3HT = 750 nm). Slightly saturated curves are observed in Fig. 2(c). Finally, with 300-nm pore diameter, we increase PVP thickness to be 500 nm and P3HT thickness to be 1800 nm in case 4. A very good saturated output curves are achieved in both experimental and simulated results (Fig. 2(d)). The reason to design  $L_{PVP}$  as 500 nm instead of 200 nm in case 4 is because of the leakage control.

FIG. 2. The output characteristics of the (a) case 1, (b) case 2, (c) case 3, and (d) case 4. Experimental and simulated curves are shown in upper part and lower part, respectively. The parameters used in TCAD simulator are given in Ref. 13.

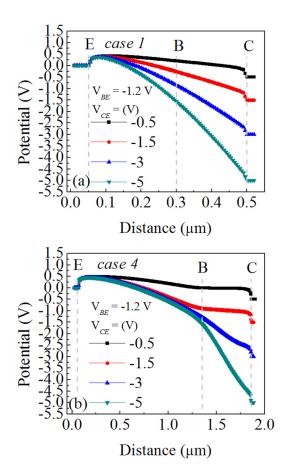

According to simulated results (not shown), when using  $L_{PVP}$  as 200 nm, well saturated output curves in case 4 can still be obtained. However, simulated leakage current becomes two orders higher than that of case 4 with 500 nm  $L_{PVP}$ . This result indicates that large  $L/L_{PVP}$  ratio leads to poor base control. Hence, in our experiment,  $L/L_{PVP}$  is controlled to be smaller than 4. The influence of geometric design on saturation characteristics can be further investigated by observing the two-dimensional potential profile in the vertical channel. The potential distributions from emitter to collector across the central vertical channel of case 1 and case 4 are compared in Figs. 3(a) and 3(b), respectively. Detailed comparisons of 4 cases are in supplementary material. SCLT is operated in ON state while  $V_{BE}$  is -1.2 V and  $V_{CE}$  changes from  $-0.5 \,\mathrm{V}$  to  $-5 \,\mathrm{V}$ . In case 1, potential is almost linearly distributed from emitter to collector, indicating an almost uniform electric field in the whole vertical channel. Such a channel potential distribution is similar to the "linear-mode operation" in field-effect transistor. Changing  $V_{CE}$  from  $-0.5 \,\mathrm{V}$  to  $-5 \,\mathrm{V}$  increases the vertical field and increases vertical channel current; no saturation region can be obtained. In case 4, when  $V_{CE}$  changes from  $-1.5 \,\mathrm{V}$  to  $-5 \,\mathrm{V}$ , the increased voltage drop appears close to collector electrode, and the potential distribution from emitter to base is almost non-altered. This potential distribution is similar to the "saturation-mode" operation in field-effect transistor. The potential profile between emitter and base is

FIG. 3. The potential distributions from emitter to collector across the central vertical channel of (a) case 1 and (b) case 4. The parameters used in TCAD simulator are given in Ref. 13. Detailed comparisons of 4 cases are in supplementary material.<sup>11</sup>

controlled mostly by  $V_{BE}$  and is almost independent of  $V_{CE}$ . A saturated behavior can thus be achieved. The obvious difference between Fig. 3(a) and Fig. 3(b) reveals the fact that the potential near base electrode is strongly dependent on geometric design of the vertical channel. We have reported that the operation principle of SCLT is a solid-state vacuum tube. In a vacuum tube, the potential profile near grid metal can be represented by a linear combination of grid and collector voltages as  $\lambda V_{GE} + V_{CE}$ , where factor  $\lambda$  depends on geometric design. Here in this work, when the potential near base electrode is roughly represented by  $\lambda V_{BE} + V_{CE}$ ,  $\lambda$  is increased from case 1 to case 4.

The geometric design in the 4 cases also significantly influences the off state of SCLT. The experimental on-state current, off-state current, and the on/off current ratio of the 4 cases are plotted in Fig. 4(a). Changing geometric design from case 1 to case 4 effectively reduces off-state current from  $1 \text{ mA/cm}^2$  to  $10^{-4} \text{ mA/cm}^2$ . Similar trend can be observed in simulated results as shown in supplementary material. The two-dimensional potential profiles in the vertical channel of the 4 cases biased in off state are compared in Fig. 4(b).  $V_{CE}$  is -1.5 V and  $V_{BE}$  is 1.2 V. Off state current is determined by the peak potential in vertical channel. Comparing case 1 and case 2, peak potentials are almost identical and are close to 0.49 V, indicating that these two cases both exhibit high off-state current. When reducing

FIG. 4. (a) The experimental on-state current, off-state current, and the on/off current ratio of the 4 cases. (b) The simulated two-dimensional potential profiles in the vertical channel of the 4 cases biased in off state.

pore diameter in case 3, the peak potential increases to be 0.67 V, representing the reduction of off-state current. In case 4, the PVP thickness is increased (i.e., the aspect ratio of the vertical cylinder is increased), and the P3HT thickness increases to be 1800 nm. The peak potential increases to be 0.95 V. The simulated off-state current is  $4.4 \times 10^{-9}$  mA/cm². Experimental off-state current is  $2.6 \times 10^{-4}$  mA/cm² and is dominated by parasitic leakage path through PVP layer.

It is briefly summarized that, in SCLT, both saturation characteristics and on/off current ratio are significantly influenced by geometric design. Increasing distance between emitter and base improves the saturation phenomenon in output curves. Creating high aspect ratio in the vertical nanometer cylinder (i.e., reducing pore diameter and increasing the thickness of PVP and the vertical channel length) is important for suppressing the off-state current to obtain a high on/ off current ratio. It is noted, however, increasing the vertical channel length also leads to a decrease of the output current. Hence, there should be a compromised geometric design. Due to the limitation of current set-up of interference lithography, the minimum pore diameter for ordered structure is 300 nm in this study. For SCLT with ordered channel openings (with opening diameter as 300 nm), well saturated output curves and a high on/off current ratio as 3600 can be achieved (data provided in supplementary material<sup>11</sup>).

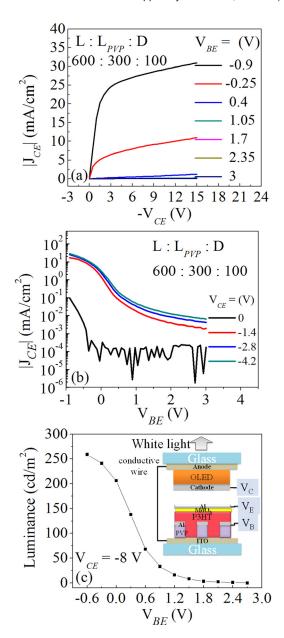

Finally, utilizing the principles obtained above, we fabricate SCLT for OLED driving. From case 1 to case 4, saturated output curves and low off-state current can be obtained when increasing the ratio between channel length (L) over the diameter of the vertical channel (D). In case 4, we increase the channel length to be 1800 nm with the hole diameter as  $300 \, \text{nm}$ , L/D reaches 6. The increase of channel length, however, degrades the amount of the output current at a fixed bias voltage. The output current of case 4 is  $1.3 \,\mathrm{mA/cm^2}$  at  $V_{CE} = -2.5 \,\mathrm{V}$ . Such an output current is not enough to drive OLED. To increase the output current while remaining good saturation behavior and low leakage current, we use colloidal lithography method to scale down the diameter of the hole (i.e., the diameter of the PS sphere) as 100 nm. To keep L/D as high as 6, the transistor exhibits Las 600 nm as follows. Detailed process steps are given in supplementary material. With PVP = 300 nm and P3HT = 600 nm, very well saturated output curves of SCLT within  $V_{CE} = 15 \text{ V}$  is obtained as shown in Fig. 5(a). Output current as  $31 \,\text{mA/cm}^2$  can be obtained at  $V_{CE} = -15 \,\text{V}$  and  $V_{BE} = -0.9 \text{ V}$ . Transfer characteristics with on/off current ratio as 9400 are also shown in Fig. 5(b). The output resistance R<sub>o</sub> can be extracted by the inverse of the slope of the output curves in Fig. 5(a). We define the output resistance in linear region as  $R_{ol}$  and in saturation region as  $R_{os}$ . Extracted  $R_{ol}$  and  $R_{os}$  for 1 cm<sup>2</sup> active region are 60  $\Omega$  and 2340  $\Omega$ , respectively. For active region as 1 mm<sup>2</sup> in this work,  $R_{os}$  are 234 k $\Omega$ . Then, SCLT (with 1 mm<sup>2</sup> active region) is connected with solution-processed OLED with 4 mm<sup>2</sup> active region. We use white light OLED, and the detailed process condition is given in supplementary material. 11 As shown in Fig. 5(c), with a total cross voltage as 8 V, luminescence of OLED can be well controlled by SCLT base voltage. When  $V_{BE}$  changes from 2.7 V to

FIG. 5. (a) The output characteristic and (b) transfer characteristic of the optimized SCLT. (c) The luminance of solution-processed white-light OLED as a function of base bias of SCLT. SCLT is connected to W-OLED by wire.

$-0.6 \,\mathrm{V}$ , luminescence changes  $0 \,\mathrm{cd/m}^2$  to  $260 \,\mathrm{cd/m}^2$ , sufficient for general display application.

In conclusion, we fabricate a vertical channel polymer transistor, SCLT, with well-saturated output characteristics. The saturated behavior enables SCLT to be practically applied for OLED driving. The saturation behavior is obtained by suitably controlling the geometric design of the vertical channel. Increasing distance between emitter to base can change non-saturated curves into saturated curves. High aspect ratio in vertical channel also greatly suppresses the channel leakage current. In this work, we particularly utilize DUV interference lithography to fabricate SCLTs with well-ordered nanometer pore structure in the base electrode. Without leakage current due to the pore accumulation, we obtain a very good match between experimental results and simulated results to verify the operation principles in SCLT. Finally, an optimized solution-processed

SCLT demonstrates a 15 V voltage endurance, a saturated output curves with a high output resistance as  $234 \, \mathrm{k}\Omega$ , a high-enough output current as  $31 \, \mathrm{mA/cm^2}$ , and a high enough on/off current ratio as 9400. The optimized SCLT is then connected with solution-processed white-light OLED to control luminescence  $(0-260 \, \mathrm{cd/m^2})$  with a 3.3-V voltage swing in  $V_{BE}$ .

The authors gratefully thank the French ministères des Affaires Etrangères (MAE) et de l'Enseignement Supérieur et de la Recherche (MESR), Région Alsace in France and the National Science Council under Grant NSC 101-2120-M-009-010-CC1 in Taiwan for the financial support.

- <sup>5</sup>S. Scheinert, T. Doll, A. Scherer, G. Paasch, and I. Hörselmann, Appl. Phys. Lett. **84**, 4427 (2004).

- <sup>6</sup>K. Fujimoto, T. Hiroi, K. Kudo, and M. Nakamura, Adv. Mater. 19, 525 (2007).

- <sup>7</sup>D. Kim, J. Jeong, H. Im, S. Ahn, H. Jeon, C. Lee, and Y. Hong, Org. Electron. **12**, 1841 (2011).

- <sup>8</sup>H. W. Zan, Y. H. Hsu, H. F. Meng, C. H. Huang, Y. T. Tao, and W. W. Tsai, Appl. Phys. Lett. **101**, 093307 (2012).

- <sup>9</sup>Y. C. Chao, M. C. Ku, W. W. Tsai, H. W. Zan, H. F. Meng, H. K. Tsai, and S. F. Horng, Appl. Phys. Lett. **97**, 223307 (2010).

- <sup>10</sup>Y. C. Chao, M. C. Niu, H. W. Zan, H. F. Meng, and M. C. Ku, Org. Electron. 12, 78 (2011).

- <sup>11</sup>See supplementary material at http://dx.doi.org/10.1063/1.4802999 for the detail of "devices fabrication procedure" and "simulation and experimental characteristics of SCLTs."

- <sup>12</sup>H. Ridaoui, F. Wieder, A. Ponche, and O. Soppera, Nanotechnology 21, 065303 (2010).

- $^{13}$ The SCLT characteristics simulation is made based on the device structure shown in Fig. 4(b). The opening diameter is controlled from 450 to 300 nm. The highest occupied molecular orbital and lowest unoccupied molecular orbital levels of P3HT are 5 and 3 eV. The work function of emitter and collector are 5.2 and 5.1 eV. The hole mobility and electron mobility are  $10^{-4}$  and  $10^{-6}\,\mathrm{cm^2/V\,s}$ .

<sup>&</sup>lt;sup>1</sup>G. Horowitz, Adv. Mater. **10**, 365 (1998).

<sup>&</sup>lt;sup>2</sup>J. N. Haddock, X. Zhang, S. Zheng, Q. Zhang, S. R. Marder, and B. Kippelen, Org. Electron. 7, 45 (2006).

<sup>&</sup>lt;sup>3</sup>J. Z. Wang, Z. H. Zheng, and H. Sirringhaus, Appl. Phys. Lett. **89**, 083513 (2006).

<sup>&</sup>lt;sup>4</sup>M. D. Austin and S. Y. Chou, Appl. Phys. Lett. **81**, 4431 (2002).