# Technical Report: Unifying Simulatability Definitions in Cryptographic Systems under Different Timing Assumptions (Extended Journal Version)\*

Michael Backes Saarland University backes@cs.uni-sb.de

April 17, 2007

#### Abstract

The cryptographic concept of simulatability has become a salient technique for faithfully analyzing and proving security properties of arbitrary cryptographic protocols. We investigate the relationship between simulatability in synchronous and asynchronous frameworks by means of the formal models of Pfitzmann et al., which are seminal in using this concept in order to bridge the gap between the formal-methods and the cryptographic community. We show that the synchronous model can be seen as a special case of the asynchronous one with respect to simulatability, i.e., we present an embedding from the synchronous model into the asynchronous one that we show to preserve simulatability. We show that this result allows for carrying over lemmas and theorems that rely on simulatability from the asynchronous model to its synchronous counterpart without any additional work, hence future work on enhancing simulatability-based models can concentrate on the more general asynchronous case.

Keywords: Probabilistic systems, security, simulatability, cryptography, synchronous / asynchronous

### **1** Introduction

In recent times, the analysis of cryptographic protocols has been getting more and more attention, and the demand for general frameworks for representing cryptographic protocols and the security requirements of cryptographic tasks has been rising. Existing framework are either motivated by the complexity-theoretic view on cryptography, which aims at proving cryptographic protocols with respect to the cryptographic semantics, or they are motivated by the view of the formal-methods community, which aims at capturing abstractions of cryptography in order to make such protocols accessible for formal verification. Frameworks built on abstractions of cryptography will be further dealt with in the related literature along with a discussion on the cryptographic justification of these abstractions.

For living up to the probabilistic nature of cryptography, a framework for dealing with actual cryptography necessarily has to be able to deal with probabilistic behaviors. The standard understanding in well-known, non security-specific probabilistic frameworks like [3, 4] is that the order of events is fixed by means of a probabilistic scheduler that has full information about the system. In contrast to that, the standard understanding in cryptology (closest to a rigorous definition in [5]) is that the adversary schedules

<sup>\*</sup>Earlier versions of this paper appeared in [1, 2].

everything, but only with realistic information. This corresponds to making a certain subclass of schedulers explicit for the model from [3]. However, if one splits a machine into local submachines, or defines intermediate systems for the purposes of proof only, this may introduce many schedules that do not correspond to a schedule of the original system and therefore just complicate the proofs. The typical solution is a distributed definition of scheduling which allows machines that have been scheduled to schedule certain (statically fixed) other machines themselves.

Based on these requirements, several general definitions of secure protocols were developed over the years, e.g. [6, 7, 8, 9, 10, 11, 12, 13, 14, 15], with many individual extensions in subsequent papers, e.g., [16, 17], which are all potential candidates for such a framework. To allow for a faithful analysis of cryptographic protocols, it is well-known that such models not only have to capture probabilistic behaviors, but also complexity-theoretically bounded adversaries as well as a reactive environment of the protocol, i.e., continuous interaction with the users and the adversary. Unfortunately, most of the above work does not live up to these requirements in spite of its generality, mainly since it concentrates on the task of secure function evaluation, which does not capture a reactive environment. Currently, the models of Pfitzmann et al. [10, 13, 15] and Canetti [14], which have been developed concurrently but independently, seem to be establishing themselves as the standard models for sound protocol analysis and design.

Regarding the underlying definition of time, such models can be split into synchronous and asynchronous ones. In synchronous models [10], time is assumed to be expressible in rounds, whereas asynchronous scenarios [13, 14, 15] do not impose any assumption on time. This makes asynchronous scenarios attractive since no assumption is made about network delays and the relative execution speed of the parties. Moreover, the notion of rounds is difficult to justify in practice as it seems to be very difficult to establish them for the Internet for example. This attractiveness is substantiated by a large body of literature on asynchronous cryptographic protocols, e.g., [18, 19]. However, time guarantees are sometimes explicitly desired, e.g., on when a process can abort. Hence assumptions have to be made in this case, which induce a certain amount of synchrony again. This sometimes makes a synchronous assumption of time nevertheless necessary in practice, e.g., in Kerberos [20].

Hence researchers usually restrict their attention to one definition of time, or they are driving doubletracked by maintaining two separate models which, however, presupposes proving every theorem for both models. This is not nice. An alternative approach, taken in this work, is to show that the synchronous model can be regarded as a special case of an asynchronous one, and hence does not have to be further advanced separately, but still can be used to conveniently express synchronous protocols.

Although this idea might not be surprising, it is very difficult to achieve since it turns out that carrying over general results from the asynchronous to the embedded synchronous model presupposes the possibility of (at least partially) reversing the considered embedding. Recall that suitable frameworks, especially the framework of Pfitzmann et al., have a distributed scheduling which significantly complicates this reversion.

Formally, a special case means that there is an embedding from the synchronous model into the asynchronous model that preserves a desired property. Which property has to be preserved depends on the goals to strive for. For cryptographic protocols, the property of *simulatability* stands out. Simulatability captures the notion of a cryptographically secure implementation and serves as a link to the formal-methods community, which typically only hold a top-level view of cryptography, where cryptographic primitives are replaced by deterministic abstractions. A more comprehensive discussion of simulatability and its relationship to protocol verification work done by the formal-methods community is given in the paragraph on related literature below.

In the following, we investigate the synchronous and asynchronous models of Pfitzmann et al. [10, 13, 15], which are seminal in using the concept of simulatability to bridge the gap between the formal-methods and the cryptographic community. We show that the synchronous model can be embedded in the asynchronous model such that simulatability is preserved by this embedding, i.e., if two systems fulfill the sim-

ulatability relation in the synchronous model, their respective images fulfill the relation in the asynchronous model and vice versa. We show that this result allows for carrying over lemmas and theorems from the asynchronous case to the synchronous case without proving them twice, hence future work on enhancing simulatability-based models can concentrate on the more general asynchronous case. We are confident that this result helps to make future protocol analysis in these models more convenient and more efficient.

Moreover, we believe that our approach for establishing the embedding and its properties can be successfully used for other models with only minor changes. Especially the asynchronous model of Canetti is surely worth to be investigated. However, his corresponding synchronous model [12] is still specific for secure function evaluation; hence adopting it to a reactive environment is a necessary prerequisite for this future work. The lack of such a reactive synchronous model was – besides the fact that the models of Pfitzmann et al. are more rigorously defined than the one of Canetti – our main reason why we decided to base our work on the model of Pfitzmann et al.

**Related Literature.** If cryptographic protocols should be verified using formal methods, some kind of abstraction is needed as the underlying reduction proofs of cryptography are still out of scope of current verification techniques.<sup>1</sup> This abstraction is usually based on the so-called Dolev-Yao abstraction [24], which considers cryptographic primitives, e.g., E for encryption and D for decryption, as operators in a free algebra where only predefined cancellation rules hold. For instance, twofold encryption of a message m does not yield another message from the basic message space but the term E(E(m)). A typical cancellation rule is D(E(m)) = m. This abstraction simplifies proofs of larger protocols considerably, and it gave rise to a large body of literature on analyzing the security of protocols using techniques for formal verification of computer programs (a very partial list of work includes [25, 26, 27, 28, 29, 30, 31, 32, 33, 34]).

Since this line of work turned out to be very successful, the interesting question arose whether these abstractions are indeed justified from the view of cryptography, i.e., whether properties proved for the abstractions are still valid for the cryptographic implementation. Such cryptographic underpinnings of a Dolev-Yao model were first addressed by Abadi and Rogaway in [35]. However, they only handled passive adversaries and symmetric encryption. The protocol language and security properties handled were extended in [36, 37], but still only for passive adversaries. This excludes most of the typical ways of attacking protocols, e.g., man-in-the-middle attacks and attacks by reusing a message part in a different place or a concurrent protocol run. A full cryptographic justification for a Dolev-Yao model, i.e., for arbitrary active attacks and within arbitrary surrounding interactive protocols, was first given in [38, 39], with extensions in [40, 41].<sup>2</sup> It supports nested operations in the intuitive sense; operations that are performed locally are not visible to the adversary. It is secure against arbitrary active attacks, and works in the context of arbitrary surrounding interactive protocols. This holds independently of the goals that one wants to prove about the surrounding protocols; in particular, property preservation theorems for the simulatability definition we use have been proved for integrity, fairness, liveness, and non-interference [44, 45, 46, 47, 48, 49]. Moreover, tailored tool support for this library was subsequently added [50, 51]. Based on the specific Dolev-Yao model whose soundness was proven in these papers, several well-known security protocols were proved in a computationally sound manner [52, 53, 54, 55, 56, 57]. This shows that in spite of adding certain operators and rules compared with simpler Dolev-Yao models (in order to be able to use arbitrary cryptographically secure primitives without too many changes in the cryptographic realization), such a proof is possible in the style already used in

<sup>&</sup>lt;sup>1</sup>Efforts are also under way to formulate syntactic calculi for dealing with probabilism and polynomial-time considerations, in particular [21, 9, 22, 23] and, as a second step, to encode them into proof tools. However, this approach can not yet handle protocols with any degree of automation. Generally it should be seen as complementary to, rather than competing with, the approach of getting simple deterministic abstractions of cryptography and working with those wherever cryptography is only used in a blackbox way.

<sup>&</sup>lt;sup>2</sup>In more recent work, drawing upon insides gained from the proof of the cryptographic library, we showed that widely considered symbolic abstractions of hash functions and of the XOR operation cannot be proven computationally sound in general, hence indicating that their current symbolic representations might be overly simplistic [42, 43].

automated tools, only now with a sound cryptographic basis. Another cryptographically sound proof of this protocol was concurrently developed by Warinschi [58]. The proof establishes a stronger security property but is conducted from scratch in the cryptographic approach which takes it out of the scope of formal proof tools. Laud [59] has presented a cryptographic underpinning for a Dolev-Yao model of symmetric encryption under active attacks. His work enjoys a direct connection with a formal proof tool, but it is specific to certain confidentiality properties, restricts the surrounding protocols to straight-line programs in a specific language, and does not address a connection to the remaining primitives of the Dolev-Yao model. Herzog et al. [60, 61] and Micciancio and Warinschi [62] have recently also given a cryptographic underpinning under active attacks. Their results are considerably weaker than the one in [38] since they are specific for publickey encryption; moreover, the former relies on a stronger assumption whereas the latter severely restricts the classes of protocols and protocol properties that can be analyzed using this primitive. Section 6 of [62] further points out several possible extensions of their work which all already exist in the earlier work of [38]. Guttman et al. [63] show that the probability of two executions of the same protocol – either executed in a Dolev-Yao-like framework or using real cryptographic primitives - may deviate from each other at most for a certain bound. However, their results are specific for the Wegman-Carter system so far. Moreover, as this system is information-theoretically secure, its security proof is much easier to handle than primitives with security guarantees only against computationally bounded adversaries since no reduction proofs against underlying number-theoretic assumptions have to be made. Some further approaches for special security goals or primitives are [64, 37].

The first full justification of a Dolev-Yao model presented in [38] was achieved by exploiting the concept of simulatability, which serves as a cryptographically sufficient relationship between abstract specifications and cryptographic implementations, i.e., abstractions which can be shown to simulate a given implementation in a particular sense are known to be sound with respect to the security definitions of cryptography. Simulatability was first invented for multi-party function evaluation [65, 6, 8, 7, 12], i.e., systems with only one initial input set and only one output set. An extension to a reactive scenario, where participants can make new inputs many times, e.g., start new sessions like key exchanges, was first fully defined in [66], with extensions to asynchronous systems in [13, 14, 15]. Each of the three considered models was already successfully used to built up sound abstractions of various cryptographic primitives like secure channels [13, 14], certified mail [67], or key exchange [68, 69].

Comparing the models of Canetti and Pfitzmann et al., we can first state that both models enjoy very general composition theorems (where the first composition theorems in [70, 13] were superseded by the theorem in [14], and again by the one in [71]). Now on the one hand, Canetti's model has been used to address more abstractions of stand-alone cryptographic primitives so far like secure multi-party computation [72] or commitments [73]. On the other hand, the asynchronous model of Pfitzmann et al. was used to solve the long-standing open problem of justifying a Dolev-Yao type model of cryptography as used in virtually all automated protocol provers: the aforementioned *cryptographic library* from [38]. This library is a flexible toolbox for constructing abstract nested cryptographic terms and for using them in arbitrary protocols, together with a cryptographic realization provably secure under arbitrary active attacks in the standard model of cryptography. Together with composition and preservation theorems of the underlying model, the library serves as the foundation for machine-assisted reasoning about cryptographic protocols while nevertheless providing a provably secure implementation. Furthermore, the models of Pfitzmann et al. are more rigorously defined and early examples of tool-supported proofs in their models exist [16, 44], using PVS [74].

**Outline.** In Section 2 we review the reactive models for synchronous and asynchronous time. In Section 3, we explain how the embedding works and give a rigorous definition. Starting with a proof sketch of the first embedding theorem in Section 4 (there will be two of them) and some lemmas capturing essential steps in

the theorem's proof, we fade to the embedding theorems in Section 5. In conjunction, both theorems allow for carrying over theorems from the asynchronous to the synchronous case, which is shown in Section 6 by means of an example.

## 2 Review of the Reactive Models in Synchronous and Asynchronous Networks

In this section we review the synchronous and the asynchronous model for probabilistic reactive systems as introduced in [10] and [13, 15], respectively. Several definitions are only sketched, whereas those that are essential for understanding our upcoming results are given in full detail. To simplify the basic understanding of these models, we start with an informal overview of the more complex asynchronous model and the distributed scheduling scheme.

#### 2.1 Informal Overview of the Asynchronous Model

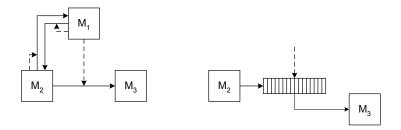

We consider sets of asynchronously communicating probabilistic state machines; such sets are called *collections* of machines. The left-hand side of Figure 1 sketches a collection of three machines connected via channels represented by solid arrows. To model asynchronous timing, messages sent between the machines stay on their respective channel until they are scheduled. Technically, each channel contains an additional machine called a buffer, which stores messages in transit. This is shown on the right-hand side of Figure 1. When  $M_2$  sends a message to  $M_3$ , this message is stored in the buffer. An incoming message at a clock channel for the buffer, represented by the dashed arrow, is interpreted as a number *i*, and the *i*-th message in the buffer is removed and output to  $M_3$ . Buffers need not be specified explicitly; a completion operator adds all necessary buffers to a collection of normal machines.

A distributed scheduling scheme that allows for expressing all realistic scenarios is achieved by allowing a machine that has been scheduled to schedule certain other machines itself. This is done by giving the machine the control over the clock channels of certain buffers. In Figure 1, the machine  $M_1$  can schedule messages sent from  $M_2$  to  $M_3$ , while the channels between  $M_1$  and  $M_2$  show procedure-call-style local interaction. Where one wants to express that an adversary schedules everything, one simply gives the adversary all the scheduling rights. Problems with purely adversarial scheduling were already noted in [75]; hence they schedule secure channels with uniform probability before adversary-chosen events. However, that introduces a certain amount of global synchrony. Furthermore, the considered model does not require local scheduling for all secure channels; they may be blindly scheduled by the adversary (i.e., without even seeing if there are messages on the channel). For instance, this models cases where the adversary has a global influence on relative network speed.

Probability spaces for runs are defined in detail for such collections of machines, as well as the view of a subset of the machines. These definitions are useful beyond the more security-specific system classes considered later. Further, the Turing-machine realization and runtime considerations are defined in this generality.

Security-specific *structures* are defined as collections of machines with distinguished service ports for the honest users. Such structures are augmented by arbitrary machines H and A representing the honest users and the adversary, who can interact. One then speaks of a *configuration*. In the presence of adversaries, the structure of correct machines running may not be the *intended structure* that the designer originally planned. For instance, some machines might have been corrupted; hence they are missing from the actual structure and the adversary took over their connections. This is modeled by defining a *system* as a set of possible actual structures.

Figure 1: A collection of three machines is shown on the left. Solid arrows represent channels. The dashed arrow depicts that  $M_1$  schedules messages on the channel from  $M_2$  to  $M_3$ . Each channel implicitly contains a buffer for storing messages in transit, shown on the right.

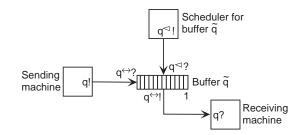

Figure 2: Ports and buffers.

#### 2.2 General System Model

In the following we consider a finite alphabet  $\Sigma$  and some special symbols  $!, ?, \stackrel{\leftrightarrow}{\leftrightarrow}, \stackrel{\triangleleft}{\notin} \Sigma$  that will be used to express different ports of machines. For  $s \in \Sigma^*$  and  $l \in \mathbb{N}_0$ , we define  $s \lceil l$  to be the *l*-letter prefix of *s*.

Machines can exchange messages with each other via *ports*. Intuitively, a port is a possible attachment point for a channel when a machine of Figure 1 is considered in isolation. As in many other models, channels in collections of machines are specified implicitly by naming conventions on the ports. Figure 2 gives an overview of the naming scheme; it can be seen as a yet more detailed view of the right-hand side of Figure 1. The name of a port (here q) serves as an identifier and will later be used to define which ports are connected to each other. Inspired by the CSP-notation [76], input and output ports are represented by the symbols ? and !, respectively. These ports are used for "usual" message transmission, whereas the ports  $q^{\leftrightarrow}$ ?,  $q^{\leftrightarrow}$ !,  $q^{\triangleleft}$ ?, and  $q^{\triangleleft}$ ! are used for the distributed scheduling. In the following, we call the port  $q^{\triangleleft}$ ! the *clock-out port* for buffer  $\tilde{q}$ . In the synchronous model, buffers do not exist nor do the "scheduling" ports  $q^{\leftrightarrow}$ ?,  $q^{\leftrightarrow}$ !,  $q^{\triangleleft}$ ?, and  $q^{\triangleleft}$ !.

As the *low-level complement*  $q^c$  of a port q (either in- or output port) we denote the port with which it connects according to Figure 2, i.e.,  $q^{\triangleleft !c} := q^{\triangleleft ?}$ ,  $q!^c := q^{\leftrightarrow ?}$ ,  $q^{\leftrightarrow !c} := q^?$ , and vice versa. The *high-level complement*  $q^C$  of a port q denotes the connecting port without the buffer, i.e.,  $q!^C = q$ ? and vice versa. For a set or a sequence P of ports, let in(P) and out(P) denote the subset or subsequence of P consisting of the input ports or the output ports of P, respectively.

After introducing ports, we now define *machines*. The primary machine model is probabilistic statetransition machines, similar to probabilistic I/O automata as in [77, 78]. Other terms for such machines are extended finite-state automata or state-transition machines. For the computational complexity aspects, implementations of such machines are defined by probabilistic interactive Turing machines. Turing machines are not used as the sole or primary model, in contrast to prior cryptographic literature, because the I/O automata allows for expressing non-cryptographic protocol parts and abstractions from cryptography in a well-defined way unencumbered with Turing-machine details. This is important for the desired accessibility of the resulting model to existing theorem provers and model checkers. The model makes one addition to individual machines compared with other I/O automata models, in order to enable machines to have polynomial runtime independent of their environment without being automatically vulnerable to denial-of-service attacks by long messages: It allows state-dependent *length bounds* on the inputs that a machine will read from each channel.

A machine has a *sequence of ports*, containing both input ports and output ports, and a set of *states*, comprising sets of *initial* and *final states*. If a machine is switched, it receives an input tuple at its input ports and performs its *transition function* yielding a new state and an output tuple in the deterministic case, or a finite distribution over the set of states and possible outputs in the probabilistic case. Furthermore, each machine has state-dependent bounds on the length of the inputs accepted at each port to enable flexible enforcement of runtime bounds. The parts of an input that are beyond the length bound are ignored. The value  $\infty$  denotes that arbitrarily long inputs are accepted.

#### Definition 2.1 (Machines) A machine is a tuple

#### $M = (name_M, Ports_M, States_M, \delta_M, l_M, Ini_M, Fin_M)$

of a name name<sub>M</sub>  $\in \Sigma^+$ , a finite sequence  $Ports_M$  of ports, a set  $States_M \subseteq \Sigma^*$  of states, a probabilistic state-transition function  $\delta_M$ , a length function  $l_M : States_M \to (\mathbb{N} \cup \{\infty\})^{|in(Ports_M)|}$ , and sets  $Ini_M$ ,  $Fin_M \subseteq States_M$  of initial and final states. Its input set is  $\mathcal{I}_M := (\Sigma^*)^{|in(Ports_M)|}$ ; the *i*-th element of an input tuple denotes the input at the *i*-th input port. Its output set is  $\mathcal{O}_M := (\Sigma^*)^{|out(Ports_M)|}$ . The empty word,  $\epsilon$ , denotes no in- or output at a port.  $\delta_M$  maps each pair  $(s, I) \in States_M \times \mathcal{I}_M$  to a finite distribution over  $States_M \times \mathcal{O}_M$ . If  $s \in Fin_M$  then  $l_M(s) = (0, \ldots, 0)$ ; if  $I = (\epsilon, \ldots, \epsilon)$  then  $\delta_M(s, I) = (s, (\epsilon, \ldots, \epsilon))$ deterministically. Inputs are ignored beyond the length bounds, i.e.,  $\delta_M(s, I) = \delta_M(s, I \mid l_M(s))$  for all  $I \in \mathcal{I}_M$ , where  $(I \mid l_M(s))_i := I_i \mid l_M(s)_i$  for all i.

In the text, we often write "M" also for  $name_{\mathsf{M}}$ . For a set  $\hat{M}$  of machines, let  $\mathsf{ports}(\hat{M})$  denote the set of ports of all machines  $\mathsf{M} \in \hat{M}$ . We call a machine  $\mathsf{M}$  a *black-box submachine* of a machine  $\mathsf{M}'$  if the machine  $\mathsf{M}'$  has access to the state-transition function  $\delta_{\mathsf{M}}$  of  $\mathsf{M}$ , i.e., it can execute  $\delta_{\mathsf{M}}$  for the current state of the machine and arbitrary inputs. In order to concisely denote specific input and output tuples of a machine  $\mathsf{M}$ , we introduce some additional notation. Let  $(\mathsf{p}_1?,\ldots,\mathsf{p}_n?) := \mathsf{in}(Ports_{\mathsf{M}})$ , let  $P := (\mathsf{p}_{i_1}?,\ldots,\mathsf{p}_{i_j}?)$ denote a subsequence of  $(\mathsf{p}_1?,\ldots,\mathsf{p}_n?)$ , and let  $(v_i)_{i\in\{1,\ldots,j\}} \in (\Sigma^*)^j$ . If the sequence of input ports of  $\mathsf{M}$  is clear from the context, we define  $\mathcal{I}_{\mathsf{p}_{i_1}?=v_1,\ldots,\mathsf{p}_{i_j}?=v_j}$  to be the tuple  $\mathcal{I}$  of length n with  $\mathcal{I}_{i_l} = v_l$  for all  $l \in \{1,\ldots,j\}$  and  $\mathcal{I}_l = \epsilon$  for all  $l \in \{1,\ldots,n\} \setminus \{i_1,\ldots,i_j\}$ . In the special case P = () or  $v_i = \epsilon$  for all i, i.e., in case of an all-empty input, we write  $\mathcal{I}_{\epsilon}$ . Outputs are defined similarly.

For computational aspects, a machine M is regarded as implemented by a probabilistic interactive Turing machine as introduced in [79]. We refer to [15] for the precise definition of the implementation. The main reason to introduce a Turing-machine realization of the machine model is to define complexity notions. A machine is called *polynomial-time* if its Turing machine implementation only needs time polynomial in its initial worktape content, independent of all inputs on communication tapes, i.e., if there exists a polynomial Q such that all possible runs of the Turing machine are of length at most Q(k), where k is the length of the initial worktape content.

After introducing individual machines, we now focus on *collections* of finitely many machines, with the intuition that these machines interact. A collection C of machines is a finite set of machines with pairwise different machine names and disjoint sets of ports. A port of a collection is called *free* if its connecting port is not in the collection. The free ports of a collection C are denoted as free(C). Given a collection of machines in the asynchronous model, we want to add buffers for all channels to model asynchronous timing. This is modeled by the *completion* [C] of a collection C. The completion is the union of all machines of C

and the buffers needed for every channel. In the asynchronous model, a collection C is called *closed* if its completion [C] has no free ports except a special master clock-in port clk<sup>4</sup>?, i.e., free([C]) = {clk<sup>4</sup>?}. When we define the interaction of several machines, the master clock-in port will belong to a distinguished machine called the *master scheduler* which is used to resolve situations where the interaction cannot proceed. In the synchronous case, we demand free(C) =  $\emptyset$ .

For security purposes, special collections are needed, because an adversary may have taken over parts of the initially intended system, e.g., different situations have to be captured depending on which and how many users are considered as being malicious. Therefore, a system consists of several possible remaining structures.

**Definition 2.2 (Structures and Systems)** A *structure* is a pair  $struc = (\hat{M}, S)$  where  $\hat{M}$  is a collection of non-buffer machines called *correct machines*, and  $S \subseteq \text{free}(\hat{M})$  is called *specified ports*. If  $\hat{M}$  is clear from the context, let  $\bar{S} := \text{free}(\hat{M}) \setminus S$ . We call  $\text{forb}(\hat{M}, S) := \text{ports}(\hat{M}) \cup \bar{S}^C$  the *forbidden ports*, i.e., those ports that the honest user is forbidden to have. A *system Sys* is a set of structures. It is polynomial-time iff all machines in all its collections  $\hat{M}$  are polynomial-time.

The separation of the free ports into specified ports and others is an important feature of the upcoming security definitions. The specified ports are those where a certain service is guaranteed. Concretely, specified ports will later be used to connect a user machine to the structure.

Note that this definition is valid for both the synchronous and the asynchronous case. In particular, buffers do not have to be explicitly included in the specification of a system, e.g., in the specification of a cryptographic protocol that one wants to analyze, but the completion operator will be used instead. The different timing assumptions stem from the different definitions of runs which we will introduce in the following.

A structure can be completed to a *configuration* by adding machines H and A, modeling the joint honest users and the adversary, respectively. The machine H is restricted to the specified ports S, A connects to the remaining free ports of the structure and both machines can interact, e.g., in order to model active attacks. In the asynchronous case, buffers are additionally added to close the collection. Moreover, the initial state of all machines is isomorphic to the natural numbers which allows for letting the machines run on input the same security parameter in the subsequently described run algorithm.

**Definition 2.3 (Configurations)** A configuration of a system Sys is a tuple  $conf = (\hat{M}, S, H, A)$  where  $(\hat{M}, S) \in Sys$  is a structure,  $\hat{M} \cup \{H, A\}$  is a closed collection,  $ports(H) \cap forb(\hat{M}, S) = \emptyset$ , and  $Ini_{\mathsf{M}} = \{1\}^*$  for all  $\mathsf{M} \in \hat{M} \cup \{\mathsf{H}, \mathsf{A}\}$ . The set of configurations is written Conf(Sys). The set of configurations of Sys with polynomial-time user H and adversary A is called  $Conf_{\mathsf{poly}}(Sys)$ . The index  $_{\mathsf{poly}}$  is omitted if it is clear from the context.  $\diamond$

### 2.3 Capturing Asynchronous Runs

For a configuration, both models define a probability space of runs (sometimes called *traces* or *executions*). In the asynchronous model, the collection contains a unique master scheduler X since the collection is closed. Machines switch sequentially, i.e., we have exactly one active machine M at any time. If this machine has clock-out ports, it can select the next message to be delivered by scheduling a buffer via one of these clock-out ports. If a message exists at the respective position of the buffer's internal queue, it is delivered by the buffer and the unique receiving machine is the next active machine. If M tries to schedule multiple messages, only one is taken, and if it schedules none or the message does not exist, the master scheduler X becomes active.

**Definition 2.4 (Asynchronous Runs and Views)** For a given configuration  $conf = (\hat{M}, S, H, A)$  with master scheduler X (which is uniquely determined by having the master-clock in-port clk<sup>4</sup>?), set  $\hat{C} := [\hat{M} \cup \{H, A\}]$ . Runs and their probability spaces are defined inductively by the following algorithm for each tuple  $ini \in \{(1^k)_{M \in \hat{M} \cup \{H, A\}}\} \subset \times_{M \in \hat{C}} Ini_M$  of initial states of the machines of  $\hat{C}$ .

The probability space of *runs* is defined inductively by the following algorithm. It has a variable r for the resulting *run*, an initially empty list, a variable M<sub>CS</sub> ("current scheduler") over machine names, initially M<sub>CS</sub> := X, and treats each port as a variable over  $\Sigma^*$ , initialized with  $\epsilon$  except for clk<sup> $\triangleleft$ </sup>? := 1. Probabilistic choices only occur in Phase (1).

- 1. Switch current scheduler: Switch machine  $M_{CS}$ , i.e., set  $(s', O) \leftarrow \delta_{M_{CS}}(s, I)$  for its current state s and input port values I. Then assign  $\epsilon$  to all input ports of  $M_{CS}$ .

- 2. Termination: If X is in a final state, the run stops.

- Buffer messages: For each simple output port q! of M<sub>CS</sub>, in their given order, switch buffer q with input q<sup>↔</sup>? := q!, cf. Figure 2. Then assign ε to all these ports q! and q<sup>↔</sup>?.

- 4. *Clean up scheduling:* If at least one clock-out port of  $M_{CS}$  has a value  $\neq \epsilon$ , let  $q^{\triangleleft}!$  denote the first such port and assign  $\epsilon$  to the others. Otherwise let  $clk^{\triangleleft}? := 1$  and  $M_{CS} := X$  and go back to Phase (1).

- 5. Scheduled message: Switch  $\tilde{q}$  with input  $q^{\triangleleft}$ ? :=  $q^{\triangleleft}$ ! (cf. Figure 2), set q? :=  $q^{\leftrightarrow}$ ! and then assign  $\epsilon$  to all ports of  $\tilde{q}$  and to  $q^{\triangleleft}$ !. Let  $M_{CS}$  := M' for the unique machine M' with q?  $\in$  ports(M'). Go back to Phase (1).

Whenever a machine (this may be a buffer) with name  $name_{\mathsf{M}}$  is switched from (s, I) to (s', O), we add a *step*  $(name_{\mathsf{M}}, s, I', s', O)$  with  $I' := I \lceil_{l_{\mathsf{M}}(s)}$  to the run r, except if s is final or  $I' = (\epsilon, \ldots, \epsilon)$ . This gives a random variable for each tuple *ini*, i.e., for each value k of the security parameter denoted as  $run_{conf,k}$ . Hence we obtain a family of random variables

$$run_{conf} = (run_{conf,k})_{k \in \mathbb{N}}.$$

The view of a subset  $M \subset \hat{C}$  in a run r is the restriction of r to M, i.e., the subsequence of all steps  $(name_{\mathsf{M}}, s, I, s', O)$ , where  $name_{\mathsf{M}}$  is the name of a machine  $\mathsf{M} \in M$ . This gives a family of random variables

$$view_{conf}(M) = (view_{conf,k}(M))_{k \in \mathbb{N}}.$$

For a singleton  $M = \{H\}$  we write  $view_{conf}(H)$  instead of  $view_{conf}(\{H\})$ .

$\diamond$

This still rather informal definition of runs can naturally be formalized using transition probabilities, which induce probability spaces over the finite sequences of steps similar to Markov Chains. The extension to infinite sequences can then be achieved using well-established results of measure theory and probability theory, cf. Section 5 of [80]. It is further easy to show that views of polynomial-time machines are of polynomial size, i.e., that the length of any trace that occurs with non-zero probability according to the considered view is bounded by a polynomial in the security parameter.

#### 2.4 Capturing Synchronous Runs

In the synchronous model, ports, machines, collections, structures, and systems are defined similar to the asynchronous model. The only exception is that there are no clock ports and no buffers, which have only been included to model asynchronous timing, i.e., corresponding ports p? and p! are directly connected. The main difference is the definition of runs. Instead of our asynchronous run algorithm (cf. Definition 2.4),

runs are defined using *rounds* which is the usual concept in synchronous scenarios. Every global round is again divided into n so-called subrounds, and there is a mapping  $\kappa$ , called *clocking scheme*, from the set  $\{1, \ldots, n\}$  into the powerset of considered machines, i.e., the machines of the structure, the user, and the adversary.  $\kappa(i)$  denotes which machines switch in subround i. After finishing the n-th subround, the run starts the first subround of the next global round. At the beginning of each subround, all messages from the previous subround are transported from the output ports to the connected input ports. After that, each machine of  $\kappa(i)$  switches with its current inputs yielding a finite distribution over the set of states and the set of possible outputs.

**Definition 2.5 (Clocking Scheme)** A clocking scheme  $\kappa$  for a configuration  $(\hat{M}, S, H, A)$  and  $n \in \mathbb{N}$  is a mapping from the set  $\{1, \ldots, n\}$  to the powerset of  $\hat{M} \cup \{H, A\}$ , i.e., it assigns each number a subset of the machines.

**Definition 2.6 (Synchronous Runs and Views)** Given a configuration  $conf = (\hat{M}, S, H, A)$  along with a clocking scheme  $\kappa$  for  $n \in \mathbb{N}$ , runs are defined as follows: Each global round *i* has *n* subrounds, where we denote the *j*-th subround of global round *i* by [i.j]. In subround  $j \in \{1, \ldots, n\}$  all machines  $M \in \kappa(j)$  switch simultaneously, i.e., each state-transition function  $\delta_M$  is applied to M's current input yielding a new state and output (probabilistically). The output at a port p! is available as input at p? until the machine with port p? is switched. If several inputs arrive until that time, they are concatenated. Similar to the asynchronous case, this gives a family of random variables

$$run_{conf,\kappa} = (run_{conf,\kappa,k})_{k \in \mathbb{N}}.$$

More precisely, each *run* is a function mapping each triple  $(M, i, j) \in \hat{M} \cup \{H, A\} \times \mathbb{N} \times \{1, \ldots, n\}$  to a quadruple (s, I', s', O) of the old state, inputs (with  $I' := I \lceil_{l_M(s)}$  again), new state, and outputs of machine M in subround [i.j], with  $I' \equiv \epsilon$ ,  $O \equiv \epsilon$ , and s = s' if M is not switched in this subround. The *view* of a subset  $M \subset \hat{M} \cup \{H, A\}$  in a run r is the restriction of r to  $M \times \mathbb{N} \times \{1, \ldots, n\}$ . This gives a family of random variables

$$view_{conf,\kappa}(M) = (view_{conf,\kappa,k}(M))_{k \in \mathbb{N}},$$

and we omit the subscript  $\kappa$  if it is clear from the context.

Again, the view of a polynomial-time machine can easily be shown to be of polynomial size.

*Remark 2.1.* Alternatively, we can consider runs as a sequence of seven-tuples (M, i, j, s, I', s', O) for ascending values of i and j. More formally, we first have all tuples (M, 1, 1, s, I', s', O) for  $M \in \kappa(1)$ . The order of these tuples can be chosen arbitrary since they switch simultaneously and do not influence each other. After that, we have the steps (M, 1, 2, s, I', s', O) for all  $M \in \kappa(2)$  and so on, until we finally have steps of the form (M, 1, n, s, I', s', O) for all  $M \in \kappa(n)$ . We then continue with (M, 2, 1, s, I', s', O) etc. Obviously, this characterization of runs is equivalent to the original one (we just expanded the function), but it is better suited for relating synchronous runs and "corresponding" asynchronous runs, which we will do in our upcoming proofs.

Instead of arbitrary clocking schemes as in the above definition of runs, the authors of [10] focus on only one special clocking scheme  $\kappa$ , given by  $(\hat{M} \cup \{H\}, \{A\}, \{H\}, \{A\})$ . Clocking the adversary between the correct machines is the well-known model of "rushing adversaries", where [81] is the earliest reference that we are aware of. In [10], it has been shown that this clocking scheme does not restrict the possibilities of the adversary, hence we can use it without loss of generality. Moreover, we restrict ourselves to those configurations where the honest user and the adversary are only connected via one duplex channel. This is indeed no restriction to generality in the synchronous model, because outputs at several ports to the same

$\diamond$

machine can simply be concatenated using a separation symbol and decomposed again, respectively. In the following, we give these two channels fixed names  $p_{A_{-}H}$  and  $p_{H_{-}A}$ , i.e.,  $p_{A_{-}H}!$  sends messages from A to H and vice versa.

#### 2.5 Simulatability

The definition of one system securely implementing another one is based on the common concept of *simulatability*. Simulatability essentially means that whatever might happen to an honest user in a real system  $Sys_{real}$  can also happen in an ideal (abstract) system  $Sys_{id}$ : For every structure  $struc_1 \in Sys_{real}$ , every user H, and every adversary A<sub>1</sub>, there exists an adversary A<sub>2</sub> on a corresponding ideal structure  $struc_2$  such that the view of H is indistinguishable in the two configurations. Indistinguishability (" $\approx$ ") is a well-defined cryptographic notion from [82]. We only give the definition of computational indistinguishability; a more comprehensive definition is given in the Appendix.

**Definition 2.7 (Computational Indistinguishability)** Two families  $(var_k)_{k\in\mathbb{N}}$  and  $(var'_k)_{k\in\mathbb{N}}$  of random variables (or probability distributions) on common domains  $D_k$  are *computationally indistinguishable* (" $\approx$ ") if for every algorithm Dis (the distinguisher) that is probabilistic polynomial-time in its first input,

$$|P(\mathsf{Dis}(1^k,\mathsf{var}_k)=1) - P(\mathsf{Dis}(1^k,\mathsf{var}_k')=1)| \in NEGL^3$$

Intuitively, given the security parameter and an element chosen according to either  $var_k$  or  $var'_k$ . Dis tries to guess which distribution the element came from.

Corresponding structures in the simulatability definition are designated by a function f from  $Sys_{real}$  to the powerset of  $Sys_{id}$ . The function f is called *valid* if it maps structures with the same set of specified ports, so that the same user can connect. For many systems there is only one possible mapping that meets this requirement, because the service ports of the structures correspond one-to-one to different sets of non-corrupted machines. This mapping is then called *canonical*. We only give the definition of simulatability based on computational indistinguishability, which captures the most common case when applying simulatability to cryptographic protocols. A more comprehensive definition based on the remaining notions of indistinguishability is again postponed to the Appendix; our results hold as well for this more general definition.

**Definition 2.8 (Simulatability)** Let systems  $Sys_1$  and  $Sys_2$  with a valid mapping f be given. We say  $Sys_1 \ge^f Sys_2$  (at least as secure as) if for every polynomial-time configuration  $conf_1 = (\hat{M}_1, S, H, A_1) \in Conf(Sys_1)$ , there exists a polynomial-time configuration  $conf_2 = (\hat{M}_2, S, H, A_2) \in Conf(Sys_2)$  with  $(\hat{M}_2, S) \in f(\hat{M}_1, S)$  (and the same H) such that  $view_{conf_1}(H) \approx view_{conf_2}(H)$ .

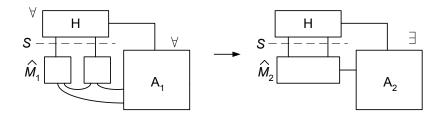

This is shown in Figure 3. In the following, we augment  $\geq$  with a subscript <sub>sync</sub> or <sub>async</sub> to distinguish the definition of the synchronous and asynchronous case. In a typical ideal system, each structure contains only one machine TH called trusted host, which serves as an ideal functionality of the real system. The machine TH is usually deterministic and maintains a very simple transition function, hence validation based on this ideal functionality is in scope of current verification techniques.

<sup>&</sup>lt;sup>3</sup>The class *NEGL* denotes the set of all negligible functions, i.e.,  $g: \mathbb{N} \to \mathbb{R}_{\geq 0} \in NEGL$  if for all positive polynomials Q,  $\exists k_0 \forall k \geq k_0: g(k) \leq 1/Q(k)$ .

Figure 3: Overview of the simulatability definition.

### **3** Idea and Definition of the Embedding

The informal idea of the embedding  $\varphi_{Sys}$  is to add an explicit master scheduler that should simulate the synchronous run induced by the given clocking scheme. However, due to the general distributed scheduling (cf. Definition 2.4), leaving the actual machines unmodified leads to non-simulatable situations, as these machines can clock themselves without ever giving control to this explicit master scheduler.

Hence, we first define a mapping  $\varphi_M$  from "synchronous" machines, i.e., from machines that do not have any of the scheduling ports but only ports for usual message transmission, to "asynchronous" machines, i.e., to machines which might additionally have clock-out ports.

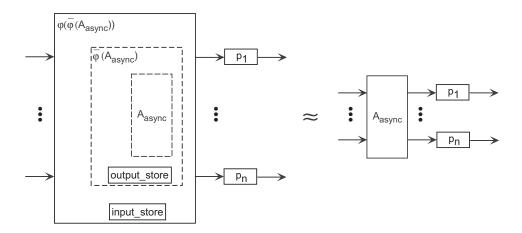

Intuitively, this mapping surrounds single synchronous machines with an "asynchronous coat". More precisely, if a synchronous machine makes a transition, it obtains all inputs at once that arrived since its last scheduling, whereas in asynchronous scenarios, these inputs come one by one and have to be processed in several transitions. Thus, the surrounding asynchronous machine stores all inputs internally, until it is asked to perform the transition of its synchronous submachine. It then schedules this submachine with the collected inputs and forwards its outputs. As these asynchronous machines do not produce any clock outputs, the master scheduler can try to simulate the synchronous time by a suitable scheduling strategy.

**Definition 3.1 (Mapping**  $\varphi_M$ )  $\varphi_M$  is a mapping on single synchronous machines that assigns every machine  $M_{sync}$  an asynchronous machine  $M_{async} := \varphi_M(M_{sync})$  by the following rules:

- The ports of M<sub>async</sub> are given by  $Ports_{M_{async}} := Ports_{M_{sync}} \circ (p_{M_{sync}}?)$ , where  $\circ$  denotes concatenation of sequences.

- Internally, M<sub>async</sub> maintains arrays (*input\_store*<sub>M<sub>sync</sub>,p?</sub>)<sub>p?∈in(Ports<sub>M<sub>sync</sub>)</sub> over Σ\* initialized with ε everywhere, which are used for storing incoming messages at each port of M<sub>sync</sub>.

</sub>

- $M_{async}$  has the machine  $M_{sync}$  as a blackbox submachine, i.e., it has its transition function  $\delta_{M_{sync}}$ .

- Internally, M<sub>async</sub> maintains a superset of the states of M<sub>sync</sub> (the additional states are only used to model appropriate length functions). Moreover, the initial and final states of both machines are equal.

- On input i at p? ≠ p<sub>Msync</sub>?: It concatenates i to the element of input\_store<sub>Msync,p</sub>?, i.e., it stores all inputs until the machine M<sub>sync</sub> is eventually switched. The length function for such a port p? is defined as l<sub>Msync</sub>(s)<sub>p</sub>? |input\_store<sub>Msync,p</sub>?|, where l<sub>Msync</sub>(s)<sub>p</sub>? is the length function of the machine M<sub>sync</sub> at port p? in its current state s and |input\_store<sub>Msync,p</sub>?| is the number of elements in input\_store<sub>Msync,p</sub>?

- On input i at p<sub>M<sub>sync</sub></sub>?: It applies the state transition function δ<sub>M<sub>sync</sub></sub> on the contents of the arrays input\_store<sub>M<sub>sync</sub></sub>, p? yielding a tuple (s', O). M<sub>async</sub> now assigns ε to input\_store<sub>M<sub>sync</sub>,p?</sub> for all p? ∈ in(Ports<sub>M<sub>sync</sub></sub>), switches to the state s' and outputs the tuple O. The length function for this port is defined to be zero if the lists input\_store<sub>M<sub>sync</sub>,p?</sub> are empty for all ports p?; otherwise it is

the runtime of  $M_{sync}$ . This case corresponds to the scheduling of the synchronous machine; the port  $p_{M_{sync}}$ ? will be connected to the explicit master scheduler.

For a set  $\hat{M}$  of synchronous machines, we define  $\varphi_{\mathsf{M}}(\hat{M}) := \bigcup_{\mathsf{M}_{\mathsf{sync}} \in \hat{M}} \varphi_{\mathsf{M}}(\mathsf{M}_{\mathsf{sync}}).$

$M_{async}$  is polynomial-time by construction iff  $M_{sync}$  is polynomial-time, since the machine  $M_{async}$  only performs a polynomially bounded number of steps between two transitions of  $M_{sync}$  (which is especially ensured by the used length functions), since both machines always stay in the same state after a transition of the blackbox submachine, and finally since their final states are equal. We stress that making the outer machine  $M_{sync}$  polynomial-time for a polynomial submachine is not as easy as one might expect, e.g., as the outer machine may be triggered exponentially often at one port without causing the submachine to switch. Note further that the length functions of  $M_{async}$  are always large enough by construction that inputs of  $M_{async}$  are not ignored respectively truncated if they would be fully read by the machine  $M_{sync}$ .

Based on this definition, we now formalize the desired mapping  $\varphi_{Sys}$  on synchronous systems.

**Definition 3.2 (Mapping**  $\varphi_{Sys}$ ) Let an arbitrary synchronous system  $Sys_{sync} = \{(\hat{M}_{sync}, S_{sync}) | sync \in I\}$  for a finite index set I and a clocking scheme  $\kappa$  be given. We then define

$$\varphi_{Sys}(Sys_{\mathsf{sync}}) := \{ (\varphi_{\mathsf{M}}(\hat{M}_{\mathsf{sync}}) \cup \{\mathsf{X}_{\mathsf{sync},\kappa}\}, S_{\mathsf{sync}}) \mid \mathsf{sync} \in I \}$$

The machine  $X_{sync,\kappa}$  is an explicit master scheduler that has to be added to the considered structure to model the synchronous clocking scheme  $\kappa$  in the asynchronous system. Its ports are given by

- $\{c|k^{\triangleleft}?\}$ : The master clock-in port.

- $\{p^{\triangleleft} \mid p! \in Ports_{\hat{M}_{sync}}\}$ : Ports for clocking all output ports of the given structure.

- {p<sup>4</sup>! | p?  $\in$  free $(\hat{M}_{sync})$ }: Ports for clocking inputs of the systems (either made by H or A).

- { $p_{A,H} \triangleleft !, p_{H,A} \triangleleft !$ }: Ports for clocking the connection between A and H.<sup>4</sup>

- { $p_M$ !,  $p_M^{\triangleleft}$ ! | M  $\in (\hat{M}_{sync} \cup \{H, A\})$ }: Ports for clocking, i.e., giving control to, each machine.

The length functions are always set to infinity for all ports. Internally, it maintains a variable *local\_rnd* over  $\{1, \ldots, n\}$  and a variable *global\_rnd* over  $\mathbb{N}$  both initialized with 1. For the sake of readability, we describe the behavior of  $X_{sync,\kappa}$  using "for"-loops. This is just a notational convention that should be understood as follows: every time  $X_{sync,\kappa}$  is scheduled, it performs the next step of the loop.

- Schedule Current Machines: For all machines M ∈ κ(local\_rnd) output (global\_rnd, local\_rnd) at p<sub>M</sub>!, 1 at p<sub>M</sub><sup>⊲</sup>!. The order of the switched machines can be chosen arbitrary.

- 2. Schedule Outgoing Buffers: For all  $M \in \kappa(local\_rnd)$  output 1 at every port  $p^{\triangleleft}!$  with  $p! \in Ports_M$ . Here, the order of the switched machines can only be chosen arbitrary with the restriction that output ports of the adversary are scheduled first if  $A \in \kappa(local\_rnd)$ .<sup>5</sup>

- 3. Switch to next Round: Set  $local\_rnd := local\_rnd + 1$ . If  $local\_rnd > n$ , set  $global\_rnd := global\_rnd + 1$  and  $local\_rnd := 1$ . Go to Phase (1).

<sup>&</sup>lt;sup>4</sup>Note, that  $X_{sync,\kappa}$  is defined independent from the honest user H and the adversary A, so it cannot know their ports. We therefore restricted the configuration to a fixed number and fixed names of ports between H and A (cf. Section 2.4).

<sup>&</sup>lt;sup>5</sup>Without this restriction, the behavior of the adversary at its switching time could depend on outputs of machines scheduled in the same subround, which would lead to non-simulatable situations.

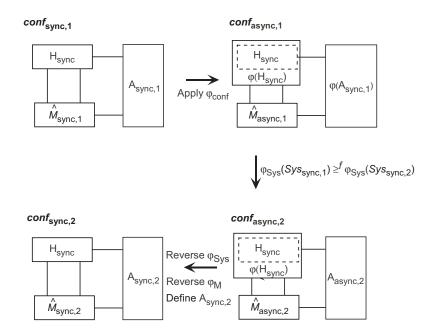

Figure 4: Synchronous Simulatability derived by Asynchronous Simulatability.

$\diamond$

To put it all into a nutshell, the specific master scheduler simulates the clocking scheme  $\kappa$  by first scheduling the machines that ought to switch in the particular subround (Step 1) and afterwards scheduling all buffers that could be influenced by outputs of these machines (Step 2). Finally, it switches to the next subround (Step 3) and continues with the first step again.

Moreover, we define a mapping  $\varphi_{conf}$  on synchronous configurations of a system Sys, i.e., configurations which consist of synchronous machines only, by

$$\varphi_{conf}(\hat{M}_{\mathsf{sync}}, S_{\mathsf{sync}}, \mathsf{H}, \mathsf{A}) := (\varphi_{\mathsf{M}}(\hat{M}_{\mathsf{sync}}) \cup \{\mathsf{X}_{\mathsf{sync},\kappa}\}, S_{\mathsf{sync}}, \varphi_{\mathsf{M}}(\mathsf{H}), \varphi_{\mathsf{M}}(\mathsf{A})),$$

with  $X_{sync,\kappa}$  given as in  $\varphi_{Sys}$  for the particular structure. We will in the following simply write  $\varphi$  instead of  $\varphi_{Sys}, \varphi_M$ , and  $\varphi_{conf}$  if its meaning is clear from the context.

### 4 Preliminary Work for the Embedding Theorems

We now have to prove that the function  $\varphi$  has the desired properties with respect to simulatability, i.e.,

$$\varphi_{Sys}(Sys_{\mathsf{sync},1}) \geq_{\mathsf{async}} \varphi_{Sys}(Sys_{\mathsf{sync},2}) \Rightarrow Sys_{\mathsf{sync},1} \geq_{\mathsf{sync}} Sys_{\mathsf{sync},2}$$

This captures the content of our first embedding theorem. Unfortunately, the converse direction does not hold, but our second embedding theorem will state a weaker version that is still sufficient for our purpose.

#### 4.1 **Proof Overview**

Before we turn our attention to the auxiliary lemmas for the embedding theorems we exemplarily present an informal description of the proof of the first embedding theorem. The proof consists of four steps. A graphical illustration is given in Figure 4. 1. Starting with a synchronous configuration  $conf_{sync,1} \in Conf(Sys_{sync,1})$ , we apply our embedding function  $\varphi_{conf}$  which yields an asynchronous configuration  $conf_{async,1} \in Conf(\varphi_{Sys}(Sys_{sync,1}))$ . We now define a mapping  $\sigma$  on the runs of the asynchronous system yielding runs of the synchronous system. Intuitively,  $\sigma$  "compresses" an asynchronous run to its synchronous counterpart, which consists of fewer steps. We then show in Theorem 4.1 that

$$view_{conf_{sync,1}}(\mathsf{H}_{sync}) = \sigma(view_{conf_{async,1}}(\varphi(\mathsf{H}_{sync}))).$$

2. We can now apply our precondition  $\varphi_{Sys}(Sys_{sync,1}) \geq_{async}^{f} \varphi_{Sys}(Sys_{sync,2})$  yielding an indistinguishable configuration  $conf_{async,2} \in Conf(\varphi_{Sys}(Sys_{sync,2}))$ , i.e.,  $view_{conf_{async,1}}(\varphi(H_{sync})) \approx view_{conf_{async,2}}(\varphi(H_{sync}))$ . We then show that

$$\sigma(view_{conf_{async,1}}(\varphi(\mathsf{H}_{sync}))) \approx \sigma(view_{conf_{async,2}}(\varphi(\mathsf{H}_{sync}))).$$

3. We finally reverse the function φ by removing the coating of the user and that of the machines of the structure. Since we do not know anything about the newly derived adversary A<sub>async,2</sub>, i.e., in particular it is not required that it fits the structure imposed by the mapping φ, we define a new adversary A<sub>sync,2</sub> using A<sub>async,2</sub> as a black-box submachine, and we will show in Theorem 4.2 that

$\sigma(view_{conf_{async,2}}(\varphi(\mathsf{H}_{sync}))) = view_{conf_{sync,2}}(\mathsf{H}_{sync}).$

4. Altogether, transitivity of the relation  $\approx$  implies

$$view_{conf_{sync,1}}(\mathsf{H}_{sync})) \approx view_{conf_{sync,2}}(\mathsf{H}_{sync}).$$

We first take a look at the runs in a synchronous system  $Sys_{sync}$  and in its asynchronous counterpart  $Sys_{async} := \varphi(Sys_{sync})$ . In the following, we will simply write S instead of  $S_{sync}$ , because the set of specified ports is not influenced by the mapping  $\varphi$ .

#### 4.2 Compressing asynchronous runs to synchronous counterparts

In the following, let an arbitrary synchronous system  $Sys_{sync}$  with a clocking scheme  $\kappa$  and an arbitrary configuration  $conf_{sync} = (\hat{M}_{sync}, S, H_{sync}, A_{sync}) \in Conf(Sys_{sync})$  be given. Moreover, let an asynchronous configuration  $conf_{async}$  be given which fits the form  $conf_{async} = (\varphi(\hat{M}_{sync}) \cup \{X_{sync,\kappa}\}, S, \varphi(H_{sync}), A')$  (i.e.,  $\varphi(conf_{sync})$  but with an arbitrary adversary).<sup>6</sup>

First of all, note that runs of  $conf_{async}$  always have a prescribed structure induced by the behavior of the master scheduler  $X_{sync,\kappa}$ : they are built by "blocks". The steps  $(M_{sync}, i, j, s, \mathcal{I}, s', \mathcal{O})$  of the machines  $M_{sync} \in \hat{M}_{sync} \cup \{H_{sync}\}$  switched in round [i.j] in the synchronous run are represented by the following two blocks in the asynchronous run.

- The first block consists of the steps induced by clocking the machines φ(M<sub>sync</sub>) with M<sub>sync</sub> ∈ κ(j) and A' if A<sub>sync</sub> ∈ κ(j), i.e., Step (1) in the definition of X<sub>sync,κ</sub>. More precisely, the block is built by |κ(j)| sub-blocks, one for every switched machine. Every sub-block is built by the following steps.

- The first step of the sub-block is always  $(X_{sync,\kappa}, s_1, \mathcal{I}_{clk^{\triangleleft}?=1}, s'_1, \mathcal{O}_{p_{M_{sync}}!=(i,j), p_{M_{sync}^{\triangleleft}!=1})}$  for two arbitrary states  $s_1, s'_1$  of  $X_{sync,\kappa}$ , i.e., the master scheduler schedules the machine  $\varphi(M_{sync})$  respectively A'.

<sup>&</sup>lt;sup>6</sup>Note that we investigate the more general case here that A' can be chosen arbitrarily instead of being the embedded adversary  $\varphi_{M}(A)$ . This generality will be helpful during the upcoming proofs.

- After that, we have the transition of the scheduled buffer.

- We now have to distinguish the following two cases:

- If  $M_{sync} \neq A_{sync}$ , there is a step  $(\varphi(M_{sync}), s, \mathcal{I}_{p_{M_{sync}}?=(i,j)}, s', \delta_{M_{sync}}(input\_store_{M_{sync}}))$ and steps for the receiving buffers.

- If M<sub>sync</sub> = A<sub>sync</sub>, we have a step (A', s, *I*<sub>pA<sub>sync</sub>?=(*i*,*j*)</sub>, s', *O*). If *O* ≠ *O*<sub>ε</sub> we have steps for the receiving buffers. If there are nonempty outputs at ports p! and p<sup>⊲</sup>! (which has to be a self-loop because there are no free clock-in ports in the system), there is furthermore a clocking step for this particular buffer. In this case, the adversary is scheduled again, so this sub-point of the block is repeated until the self-loop of the adversary either ends or it is repeated forever in case of divergence, i.e., we obtain a step (A', s', *I*', s'', *O*) where *I*' is now given by *I*' := *I*<sub>p?=O<sub>pl</sub> and so on.</sub>

- The second block consists of the steps induced by clocking the outgoing messages of the switched machines, i.e., Step (2) in the definition of X<sub>sync,κ</sub>. Now the buffers of the output ports are switched by the master scheduler. This is done similar as in the first part with the restriction that output ports of A' are clocked first if A<sub>sync</sub> ∈ κ(j). The block again has |κ(j)| sub-blocks built by the following steps.

- The first step of the sub-block is given by (X<sub>sync,κ</sub>, s<sub>1</sub>, *I*<sub>clk<sup>d</sup>?=1</sub>, s'<sub>1</sub>, *O*<sub>p<sup>d</sup>!=1</sub>) for the first output port p! ∈ ports(M<sub>sync</sub>) and two arbitrary states s<sub>1</sub>, s'<sub>1</sub> of X<sub>sync,κ</sub>.

- The step of the clocked buffer.

- In case of a nonempty output let M' denote the unique machine with  $p? \in ports(M')$ . We now have to distinguish two cases:

- If  $M' \neq A'$ , there is a step  $(M', s, \mathcal{I}', s', \mathcal{O}_{\epsilon})$ , where  $\mathcal{I}'$  consists of the output of  $\varphi(M_{sync})$  at p!.

- If M' = A', we obtain a step  $(A', s, \mathcal{I}', s', \mathcal{O})$ , where  $\mathcal{I}'$  consists of the output of  $\varphi(M_{sync})$  respectively A' at p!. If  $\mathcal{O} \neq \mathcal{O}_{\epsilon}$  we have steps for the receiving buffers. If  $\mathcal{O}$  has a clocked self-loop, we proceed identical to the first block.

- The three previous steps are repeated for every output port of every machine  $M_{sync} \in \kappa(j)$ .

After this detailed description of the run, (i.e., its blocks) the mapping  $\sigma$  can be defined. Informally, it combines the blocks of all machines  $M_{sync} \in \kappa(j)$  yielding the synchronous steps of every machine  $M_{sync}$  that switches in the *j*-th subround of the particular global round.

**Definition 4.1 (Mapping**  $\sigma$ ) Let an arbitrary synchronous system  $Sys_{sync}$  with a clocking scheme  $\kappa$  and an arbitrary configuration  $conf_{sync} = (\hat{M}_{sync}, S, H_{sync}, A_{sync}) \in Conf(Sys_{sync})$  be given. For a given asynchronous configuration  $conf_{async}$  which fits the form  $conf_{async} = (\varphi(\hat{M}_{sync}) \cup \{X_{sync,\kappa}\}, S, \varphi(H_{sync}), A')$ , we define the mapping  $\sigma$  on the runs of  $conf_{async}$  by the following algorithm. The algorithm has internal arrays  $(inputs_{M,p?})$  for  $M \in \varphi(\hat{M}_{sync}) \cup \{\varphi(H_{sync}), A'\}$  and  $p? \in in(Ports_M)$ . It goes from block to block modifying them as follows.

- 1. Every step of a buffer is deleted from the run.

- 2. The two remaining steps of the first block are modified as follows. If the scheduled machine is  $\varphi(M_{sync}) \neq A'$ , then the block is replaced by  $(M_{sync}, i, j, s, inputs_{M_{sync}}, s', \delta_{M_{sync}}(inputs_{M_{sync}}))$ . If A' is scheduled, the block is replaced by  $(A', i, j, s, inputs_{A_{sync}}, s', \mathcal{O}_{A'})$ . Here, *s* denotes the state of A' when it is switched by  $X_{sync,\kappa}$ , and *s'* and  $\mathcal{O}_{A'}$  are the state and the output of the last step of the block, respectively (In case of divergence, the algorithm for defining the mapping  $\sigma$  diverges, too.).

- 3. The algorithm starts searching through the second block doing the following. If a machine M' receives a message *i* at p? in the second block, *i* is concatenated to the array  $inputs_{M',p?}$ .

- 4. Finally, every step of the second block is deleted from the run.

Note that all necessary information (e.g.,  $M_{sync}$ , i, j, s, s' etc.) is already given by the block except for the inputs of each machine in the synchronous case. At this point, it also becomes clear why we defined the master scheduler to schedule each machine specifically with a tuple (i, j) indicating the current global and local round, since this information would otherwise not be contained in the asynchronous run.

To overcome the absence of the gathered inputs in the run, the algorithms has to collect all "partial" inputs itself in its third step, and it can use this information to calculate the outputs of each machine (although for this, it could as well use the information contained in the run). Moreover, the new blocks built by the mapping  $\sigma$  in one particular subround do not depend on the second block of this subround. The mapping  $\sigma$  is obviously also defined on the view of arbitrary subsets of machines, because the step in the first block, carrying the information of the step, and the message-receiving steps in the second block will also be part of the view of the considered machine. Furthermore, note that the mapping  $\sigma$  is explicitly defined for arbitrary adversaries A' (not only for  $\varphi(A_{sync})$ ) which we will need in Theorem 4.2. Furthermore, the following lemma establishes a computational bound on the mapping  $\sigma$  in polynomial-time configurations:

**Lemma 4.1** If  $conf_{async}$  is a polynomial-time configuration that fits the form required by Definition 4.1, then  $\sigma$  applied to the view of the honest user and the adversary is computable in polynomial-time.

*Proof.* (Lemma 4.1) In case of a polynomial configuration, especially the adversary has to be polynomialtime. This implies that there cannot be any infinite successive clocked self-loops, so the steps of every sub-block are bounded by a polynomial in the security parameter k. Moreover, both the adversary and the honest user will reach final state after a polynomial number of blocks, so the algorithm for  $\sigma$  applied to the view either of the honest user or the adversary only makes a polynomial number of transition, each one with a polynomial number of steps. This implies that  $\sigma$  is computable in polynomial-time when applied to the view of the honest user and the adversary if it is used in a polynomial-time configuration.

#### 4.3 Auxiliary Theorems

The following theorem captures the first step of our proofsketch of Section 4.1.

**Theorem 4.1** Let a synchronous system  $Sys_{sync}$ , a clocking scheme  $\kappa$ , and a configuration  $conf_{sync} = (\hat{M}_{sync}, S, H_{sync}, A_{sync}) \in Conf(Sys_{sync})$  be given, and set  $conf_{async} := \varphi(conf_{sync})$ . Then

$$view_{conf_{sync}}(\mathsf{M}_{sync}) = \sigma(view_{conf_{async}}(\varphi(\mathsf{M}_{sync})))$$

for every  $M_{sync} \in (\hat{M}_{sync}, A_{sync})$ . conf<sub>async</sub> is polynomial-time iff conf<sub>sync</sub> is polynomial-time.  $\Box$

*Proof.* Note that the view of  $\varphi(M_{sync})$  does only contain the steps of its internal blackbox function-call after being modified by the mapping  $\sigma$ . Thus, it is sufficient to show that the inputs of the blackbox call in  $conf_{async}$  and the original inputs of  $H_{sync}$  in  $conf_{sync}$  are equal. It is quite easy to see that the arrays  $input\_store_{M_{sync}}$  and  $inputs_{M_{sync}}$  are always equal if the machine  $M_{sync}$  is switched. This can easily be proven by induction over the number of (sub-)rounds. In the first round, both arrays are empty yielding a correct start of the induction. Starting with the second round, the contents of these arrays are totally

$\diamond$

determined by the inputs at the ports of  $M_{sync}$ . However, these inputs only depend on *prior* outputs of other machines M. Moreover, these outputs have to be equal because these machines used the same input tuple in both configurations, since we have  $input\_store_{M} = inputs_{M}$  for all  $M \in M$  by induction hypothesis. Therefore, the arrays  $inputs_{M_{sync}}$  and  $input\_store_{M_{sync}}$  must be equal at replacing the block by construction of the algorithm, so  $\delta_{M_{sync}}(s, inputs_{M_{sync}}) = \delta_{M_{sync}}(s, input\_store_{M_{sync}})$  also holds. We do not have to worry about the arrangement of the blocks because of the following reasons. First of all, note that we first switch all machines in a subround and schedule the outgoing messages afterwards. Moreover, messages sent by the adversary are always scheduled first if the adversary is scheduled in the considered subround. This prevents that machines which should switch simultaneously in the synchronous system influence each other in the asynchronous system in the same subround. If we did not consider this restriction, the adversary would be able to create a message that is scheduled in this particular subround, but nevertheless depends on inputs arriving in this subround.

Putting it all together, the runs induced by the mapping  $\sigma$  in  $conf_{async}$  and the original runs are equal by definition of  $\sigma$ , so we finally obtain

$$\textit{view}_{\textit{conf}_{\mathsf{sync}}}(\mathsf{M}_{\mathsf{sync}}) = \sigma(\textit{view}_{\textit{conf}_{\mathsf{async}}}(\varphi(\mathsf{M}_{\mathsf{sync}})))$$

for an arbitrary configuration  $conf_{sync} \in Conf(Sys_{sync})$ ,  $conf_{async} := \varphi(conf_{sync})$ , and an arbitrary  $M_{sync} \in (\hat{M}_{sync} \cup \{H_{sync}, A_{sync}\})$ . As a special case, this implies

$$view_{conf_{sync}}(\mathsf{H}_{sync}) = \sigma(view_{conf_{async}}(\varphi(\mathsf{H}_{sync})))$$

which finishes our proof.

After performing this first step of the proof, asynchronous simulatability can now be applied. In order to convert the derived asynchronous configuration into a synchronous configuration again (cf. Step 3 of our proofsketch), we present the following theorem.

**Theorem 4.2** Let an arbitrary synchronous system  $Sys_{sync}$  and a clocking scheme  $\kappa$  be given such that every machine and the honest user are clocked at most once between two successive clockings of the adversary. Furthermore, let an arbitrary configuration  $conf_{async} \in Conf(\varphi(Sys_{sync}))$  of the form  $conf_{async} =$  $(\varphi(\hat{M}_{sync}) \cup \{X_{sync,\kappa}\}, S, \varphi(H_{sync}), A_{async})$  be given. Then there exists an adversary  $A_{sync}$  using  $A_{async}$  as a blackbox such that for  $conf_{sync} := (\hat{M}_{sync}, S, H_{sync}, A_{sync})$ , it holds

$$view_{conf_{sync}}(\mathsf{M}_{sync}) = \sigma(view_{conf_{async}}(\varphi(\mathsf{M}_{sync})))$$

for every  $M_{sync} \in (\hat{M}_{sync} \cup \{H_{sync}\})$ . conf<sub>async</sub> is polynomial-time iff conf<sub>sync</sub> is polynomial-time.  $\Box$

Note, that the standard clocking scheme  $(\hat{M} \cup \{H\}, \{A\}, \{H\}, \{A\})$  fulfills the postulated requirement. The proof of Theorem 4.2 is quite technical and hence postponed to Appendix B for the sake of readability.

### 5 The Embedding Theorems

This section contains our two main theorems. We start with a lemma capturing some simple properties of indistinguishable random variables. The lemma is well-known and easily proved.

**Lemma 5.1** Indistinguishability of two families of random variables implies indistinguishability of any function  $\sigma$  of them. For the polynomial case, the function  $\sigma$  has to be polynomial-time computable. Moreover, identically distributed variables are indistinguishable and indistinguishability is an equivalence relation. **Theorem 5.1 (First Embedding Theorem)** Let two arbitrary synchronous systems  $Sys_{sync,1}$  and  $Sys_{sync,2}$ with clocking schemes  $\kappa_1$  and  $\kappa_2$  be given such that  $\kappa_2$  fulfills the property that every machine of the system and the user is clocked at most once between two successive clockings of the adversary. Furthermore,  $\varphi(Sys_{sync,1}) \geq_{async}^{f} \varphi(Sys_{sync,2})$  should hold for a valid mapping f. Then

$$Sys_{sync,1} \geq_{sync}^{f'} Sys_{sync,2},$$

where f' is derived from f by  $(\hat{M}_2, S_2) \in f'(\hat{M}_1, S_1) \Leftrightarrow \varphi(\hat{M}_2, S_2) \in f(\varphi(\hat{M}_1, S_1)).$

Using the result of the previous theorems, the proof will be rather simple, cf. the illustration in Figure 4. *Proof.* Let an arbitrary configuration  $conf_{sync,1} = (\hat{M}_{sync,1}, S, H_{sync}, A_{sync,1}) \in Conf(Sys_{sync,1})$  be given.

1. We apply  $\varphi_{conf}$  on  $conf_{sync,1}$  yielding a configuration  $conf_{async,1} = (\varphi(\hat{M}_{sync,1}) \cup \{X_{sync,1,\kappa_1}\}, S, \varphi(H_{sync}), \varphi(A_{sync,1})) \in Conf(Sys_{async,1})$ . According to Theorem 4.1, applying the mapping  $\sigma$  to the runs of  $conf_{async,1}$  yields

$$view_{conf_{sync},1}(\mathsf{H}_{sync}) = \sigma(view_{conf_{async},1}(\varphi(\mathsf{H}_{sync}))).$$

(1)

Moreover, if  $conf_{sync,1}$  is polynomial-time then  $conf_{async,1}$  is also polynomial-time, and the mapping  $\sigma$  is polynomial-time computable.

2. Thus, the precondition  $\varphi(Sys_{sync,1}) \geq_{async}^{f} \varphi(Sys_{sync,2})$  can be applied yielding a configuration  $conf_{async,2} = (\varphi(\hat{M}_{sync,2}) \cup \{X_{sync,2,\kappa_2}\}, S, \varphi(H_{sync}), A_{async,2}) \in Conf(Sys_{async,2})$  with

$$view_{conf_{async,1}}(\varphi(\mathsf{H}_{sync})) \approx view_{conf_{async,2}}(\varphi(\mathsf{H}_{sync}))$$

and  $\varphi(\hat{M}_{sync,2}, S) \in f(\varphi(\hat{M}_{sync,1}, S))$ . Moreover, in the computational case,  $conf_{async,2}$  is polynomial-time, so the mapping  $\sigma$  is polynomial-time computable. Using Lemma 5.1, this yields

$$\sigma(view_{conf_{async,1}}(\varphi(\mathsf{H}_{sync}))) \approx \sigma(view_{conf_{async,2}}(\varphi(\mathsf{H}_{sync}))).$$

(2)

3. We now apply Theorem 4.2 to the configuration  $conf_{async,2}$ , which yields a configuration  $conf_{sync,2} = (\hat{M}_{sync}, S, H_{sync}, A_{sync,2}) \in Conf(Sys_{sync,2})$  with

$$\sigma(view_{conf_{\mathsf{async},2}}(\varphi(\mathsf{H}_{\mathsf{sync}}))) = view_{conf_{\mathsf{sync},2}}(\mathsf{H}_{\mathsf{sync}}).$$

(3)

According to Theorem 4.2, *conf*<sub>sync,2</sub> is a polynomial-time configuration iff *conf*<sub>async,2</sub> is polynomial.

4. Now Equation 1-3 together with Lemma 5.1 imply  $view_{conf_{sync,1}}(\mathsf{H}_{sync}) \approx view_{conf_{sync,2}}(\mathsf{H}_{sync})$ . Hence,  $conf_{sync,2}$  is an indistinguishable configuration for  $conf_{sync,1}$ . Moreover, we have  $\varphi(\hat{M}_{sync,2}, S) \in f(\varphi(\hat{M}_{sync,1}, S))$ , i.e.,  $(\hat{M}_{sync,2}, S) \in f'(\hat{M}_{sync,1}, S)$  which yields the desired result  $Sys_{sync,1} \geq_{sync}^{f'} Sys_{sync,2}$ .

Note that the theorem is applicable to the standard clocking scheme. So far, we have shown that asynchronous simulatability among these asynchronous representations implies synchronous simulatability, i.e.,

$$\varphi_{Sys}(Sys_{\mathsf{sync},1}) \ge_{\mathsf{async}} \varphi_{Sys}(Sys_{\mathsf{sync},2}) \Rightarrow Sys_{\mathsf{sync},1} \ge_{\mathsf{sync}} Sys_{\mathsf{sync},2}.$$

We already briefly stated in the previous section that the converse implication does not hold in general. We had to show that for each configuration  $conf_{async,1} \in Conf(\varphi_{Sys}(Sys_{sync,1}))$  there exists an indistinguishable configuration  $conf_{async,2} \in Conf(\varphi_{Sys}(Sys_{sync,2}))$  provided that  $Sys_{sync,1} \geq_{sync} Sys_{sync,2}$ .

However, both the honest user and the adversary may have clock-out ports and they can alternately schedule each other (and also the system erratically), which we cannot capture by a fixed synchronous clocking scheme, so we cannot exploit our assumption  $Sys_{sync,1} \ge_{sync} Sys_{sync,2}$ .

Anyhow, it is sufficient for our purpose to show that the claim holds for at least those configurations where the honest user  $H_{async}$  fits the form  $\varphi_M(H_{sync})$  for a synchronous machine  $H_{sync}$ . We denote this version of simulatability for the restricted class of users by  $\geq_{async,H}$  in the sequel. Looking at the proof of the first embedding theorem, it is immediately clear that the theorem also holds for the weaker precondition  $\varphi_{Sys}(Sys_{sync,1}) \geq_{async,H} \varphi_{Sys}(Sys_{sync,2})$ , since we only need to derive an indistinguishable configuration for users of the special form  $\varphi(H_{sync})$ , and the user remains unchanged at simulatability. We can now capture the content of the second embedding theorem as

$$Sys_{sync,1} \ge_{sync} Sys_{sync,2} \Rightarrow \varphi_{Sys}(Sys_{sync,1}) \ge_{async,H} \varphi_{Sys}(Sys_{sync,2}).$$

**Theorem 5.2 (Second Embedding Theorem)** Let two arbitrary synchronous systems  $Sys_{sync,1}$  and  $Sys_{sync,2}$  with clocking schemes  $\kappa_1$  and  $\kappa_2$  be given such that  $\kappa_1$  fulfills the property that every machine of the system and the user is clocked at most once between two successive clockings of the adversary. Furthermore,  $Sys_{sync,1} \geq_{sync}^{f} Sys_{sync,2}$  should hold for a valid mapping f. Then

$$\varphi(Sys_{\mathsf{sync},1}) \geq^{f'}_{\mathsf{async},\mathsf{H}} \varphi(Sys_{\mathsf{sync},2})$$

where f' is derived from f by  $\varphi(\hat{M}_2, S_2) \in f'(\varphi(\hat{M}_1, S_1)) :\Leftrightarrow (\hat{M}_2, S_2) \in f(\hat{M}_1, S_1).$

Before we turn our attention to the actual proof, we state the following lemma which captures that we can "locally reverse" the function  $\sigma$  for the honest user.

**Lemma 5.2** Let a synchronous system  $Sys_{sync}$ , a clocking scheme  $\kappa$  and a configuration  $conf_{sync} = (\hat{M}_{sync}, S, H_{sync}, A_{sync}) \in Conf(Sys_{sync})$  be given. Let  $conf_{async} = (\varphi(\hat{M}_{sync}) \cup \{X_{sync,\kappa}\}, S, \varphi(H_{sync}), A')$  be an arbitrary asynchronous configuration. If we now have given  $\sigma(view_{conf_{async}}(\varphi(H_{sync})))$  then we can "locally reverse" the function  $\sigma$  for the view of the user, i.e., we can define a function  $\sigma_{H}^{-1}$  on the runs of the synchronous configuration, such that

$$view_{conf_{\mathsf{async}}}(\varphi(\mathsf{H}_{\mathsf{sync}})) = \sigma_{\mathsf{H}}^{-1} \big( \sigma(view_{conf_{\mathsf{async}}}(\varphi(\mathsf{H}_{\mathsf{sync}}))) \big)$$

holds. If conf<sub>async</sub> is polynomial-time, then  $\sigma_{\rm H}^{-1}$  is polynomial-time computable.

The proof of the lemma is postponed to Appendix B.