## Charge Transport in Hexagonal-Phase Core Silicon Nanowires

Marc Collette

A Thesis In the Department of Physics

Presented in Partial Fulfillment of the Requirements For the Degree of Doctor of Philosophy (Physics) at Concordia University Montréal, Québec, Canada

> July 2019 © Marc Collette, 2019

## CONCORDIA UNIVERSITY School of Graduate Studies

This is to certify that the thesis prepared

By: Mr. Marc Collette

Entitled: Charge Transport in Hexagonal-Phase Core Silicon

Nanowires

and submitted in partial fulfillment of the requirements for the degree of

### Doctor of Philosophy (Physics)

complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

Signed by the final examining commitee:

|                         | Chair           |

|-------------------------|-----------------|

| Dr. Rolf Wuthrich       |                 |

|                         | External Examin |

| Dr. Peter Grütter       |                 |

|                         | Examiner        |

| Dr. Valter Zazubovits   |                 |

|                         | Examiner        |

| Dr. Pablo Bianucci      |                 |

|                         | Examiner        |

| Dr. Gilles Peslherbe    |                 |

|                         | Co-Supervisor   |

| Dr. Oussama Moutanabbir |                 |

|                         | Supervisor      |

| Dr. Alexandre Champagne |                 |

Approved \_

Dr. Valter Zazubovits, Graduate Program Director

August 28, 2019 \_\_\_\_

Dr. André G. Roy, Dean, Faculty of Arts and Science

# Abstract

Charge Transport in Hexagonal-Phase Core Silicon Nanowires

Marc Collette, Ph.D. Concordia University, 2019

We built an atomically engineered laboratory inside a silicon nanowire (SiNW) to study fundamental transport mechanics and correlate results with crystal structure. We quantify the effects of ordered stacking faults (OSFs) present in SiNWs on their electrical transport capabilities. We use Raman spectroscopy to characterize the hexagonal-phase core structure of the Si crystal in our novel nanowires caused by the OSFs.

Our results indicate that electrical current is prevented from flowing within the hexagonal-phase core. Using OSFs to tune crystal structure in SiNWs can be used to control the effective cross-section of the nanowire without the need to change its physical dimensions.

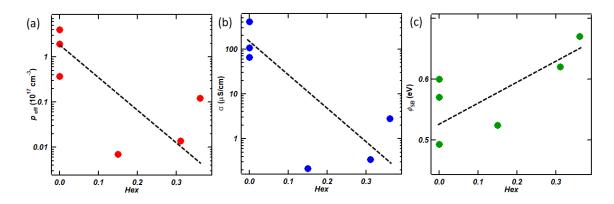

We find that the channel conductivity of field-effect transistors formed using these nanowires is decreased substantially compared to the familiar cubic phase counterpart (from roughly 100 to 1  $\mu$ S/cm). This result indicates that modulating crystal phase can be effective in tuning material conductivity, offering an additional degree of freedom in device engineering. We also show that hexagonal-core SiNWs have larger effective Schottky barriers with gold electrode contacts (from 0.48 to 0.67 eV), which increases device contact resistance.

Having a cubic-phase portion and a hexagonal-phase portion in series within a single kinked SiNW exploits this barrier asymmetry to create excellent gate-controlled and temperature-dependent rectifiers with rectifying ratios exceeding 100. Our transport model explains how the kink region also acts as a 10-nm scale diode.

These results indicate that controlling OSF density could be exploited in new device architectures and help optimize SiNWs for applications in high-impedance Schottky barrier rectifying transistors.

# Acknowledgments

I would like to thank the members of the Champagne Group at Concordia University (Andrew, Vahid, Jim, Serap, Simeon, Matthew, Gareth) and the Moutanabbir Group at Polytechnique Montréal (Samik, Dany, Simone) as this work would have been difficult without your help, guidance, expertise and motivation.

I would like to mention my colleagues from other groups, Mousa, Luc, Kathleen, Amir, as discussions with them have also been fruitful.

My co-supervisors, Alex and Oussama, have shown me how to study in the field of experimental solid-state physics and how to develop the skills necessary to produce this work.

I'd like to thank my parents for being there at all stages of my life and helping me get through my PhD.

I'm also grateful for my loving wife, Taylor, as this project would not have been completed without her. Thanks for taking care of me and making my life better. I will always be proud of you.

# Contents

| Li       | st of                 | Figure  | es                                                  | viii     |

|----------|-----------------------|---------|-----------------------------------------------------|----------|

| Li       | st of                 | Tables  | 3                                                   | x        |

| 1        | Intr                  | oducti  | on and Thesis Structure                             | 1        |

| <b>2</b> | Tra                   | nsport  | Concepts in Hexagonal-Core Silicon Nanowire Transis | -        |

|          | $\operatorname{tors}$ | 5       |                                                     | <b>5</b> |

|          | 2.1                   | Lattice | e and Band Structure                                | 6        |

|          |                       | 2.1.1   | Tuning SiNW Crystal Structure                       | 6        |

|          |                       | 2.1.2   | SiNW Band Structure                                 | 10       |

|          | 2.2                   | Intrins | ic and Extrinsic Transport Properties               | 13       |

|          |                       | 2.2.1   | Charge Carrier Densities                            | 13       |

|          |                       | 2.2.2   | Bulk Silicon Transport Properties                   | 15       |

|          | 2.3                   | Condu   | ctivity in the Fermi Gas Model                      | 16       |

|          |                       | 2.3.1   | Conductance and Conductivity                        | 17       |

|          |                       | 2.3.2   | Charge Mobility                                     | 19       |

|          | 2.4                   | Nanow   | rire Field-Effect Transistor Device                 | 21       |

|          |                       | 2.4.1   | Gate Capacitance                                    | 23       |

|          |                       | 2.4.2   | Device Switching: Transconductance and Threshold    | 26       |

|          |                       | 2.4.3   | ON-state and OFF-state                              | 33       |

|          | 2.5                   | Metal-  | Semiconductor Contact                               | 35       |

|          |                       | 2.5.1   | Charge Injection Mechanism                          | 36       |

|          |                       | 2.5.2   | Contact Resistance Parasitic Effects                | 42       |

|          |                       | 2.5.3   | Schottky Barrier                                    | 47       |

|          | 2.6                   | Rectify | ying Behavior                                       | 50       |

|          |      | 2.6.1    | Depletion Layer                                               | 51  |

|----------|------|----------|---------------------------------------------------------------|-----|

|          |      | 2.6.2    | Contact Asymmetry                                             | 54  |

| 3        | Fab  | ricatio  | on of Hexagonal-Core SiNW SB-FETs                             | 62  |

|          | 3.1  | Subst    | rate Cleaning and Coordinate Grid Fab                         | 63  |

|          |      | 3.1.1    | Wafer Cleaning and Etching                                    | 63  |

|          |      | 3.1.2    | Grid Pattern and Photolithography                             | 65  |

|          |      | 3.1.3    | Silicon Nanowire (SiNW) VLS Growth                            | 68  |

|          | 3.2  | Hexag    | gonal-Core SiNW Raman Spectroscopy                            | 71  |

|          |      | 3.2.1    | Raman Spectroscopy                                            | 73  |

|          |      | 3.2.2    | SiNW Raman Signature                                          | 75  |

|          |      | 3.2.3    | Hexagonality                                                  | 78  |

|          | 3.3  | Fabric   | eation of Electrical Contacts                                 | 80  |

|          |      | 3.3.1    | Photolithography: Stencil Method                              | 81  |

|          |      | 3.3.2    | Electron-Beam Lithography                                     | 83  |

|          |      | 3.3.3    | SiNW SB-FET Wirebonding                                       | 85  |

|          | 3.4  | Electr   | on Transport Measurements                                     | 86  |

|          |      | 3.4.1    | Circuit Optimization for Low-Noise Measurements               | 87  |

|          |      | 3.4.2    | Gate Leakage                                                  | 90  |

|          |      | 3.4.3    | Data Acquisition Procedure                                    | 92  |

| 4        | Gia  | nt Cor   | nductivity Suppression in Hexagonal-Phase Core SiNWs          | 97  |

|          | 4.1  | SiNW     | SB-FET Parameter Extraction                                   | 98  |

|          |      | 4.1.1    | Contact Properties: Contact Resistance and SB                 | 100 |

|          |      | 4.1.2    | Channel Properties: Conductivity, Mobility and Charge Density | 107 |

|          | 4.2  | Hex-C    | Core Volume Effect on Channel Conductivity                    | 114 |

|          |      | 4.2.1    | Interface Charge Traps                                        | 115 |

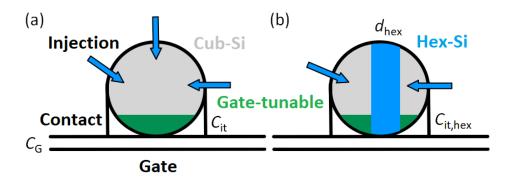

|          |      | 4.2.2    | Hex-Core SiNW SB-FET Transport Model                          | 120 |

|          |      | 4.2.3    | Channel Properties of Hex-Core SiNWs                          | 125 |

| <b>5</b> | Intr | rinsic S | SiNW Homojunction Rectifiers                                  | 129 |

|          | 5.1  |          | d SiNW FET Devices                                            | 130 |

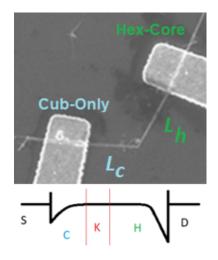

|          |      | 5.1.1    | Cub-Only/Hex-Core Homojunction                                | 131 |

|          |      | 5.1.2    | Kinked SiNW SB-FET Transport Model                            | 132 |

|          | 5.2  | Rectif   | ying Behavior in Kinked SiNWs                                 | 135 |

| 6 | Conclusion | n and Outlook                                                  | 151 |

|---|------------|----------------------------------------------------------------|-----|

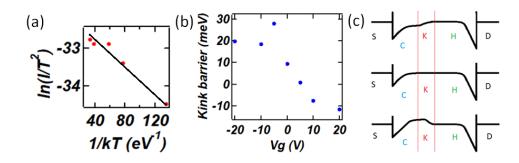

|   | 5.2.4      | Kinked SiNW SB-FET Rectifier Properties                        | 149 |

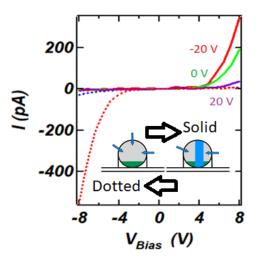

|   | 5.2.3      | Channel Asymmetry and Rectification of Homojunctions $\ . \ .$ | 144 |

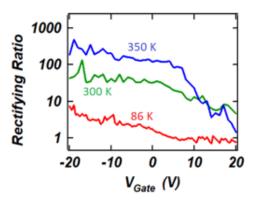

|   | 5.2.2      | Temperature- and Gate-Tunable Rectifiers                       | 138 |

|   | 5.2.1      | Characterization of Kinked SiNWs                               | 136 |

## Bibliography

154

# List of Figures

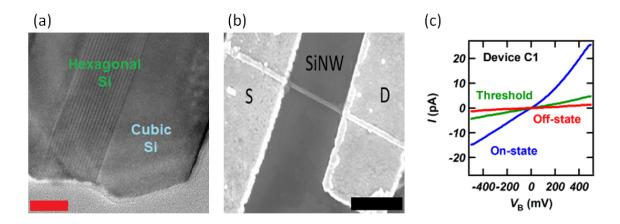

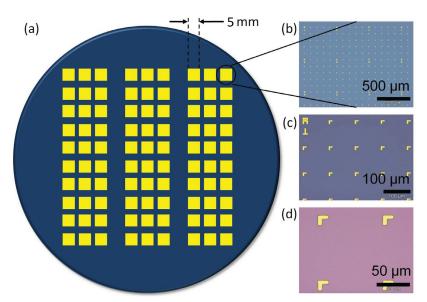

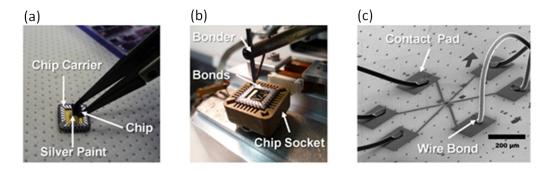

| 1.1  | Images of our SiNW SB-FET devices                                                 | 3   |

|------|-----------------------------------------------------------------------------------|-----|

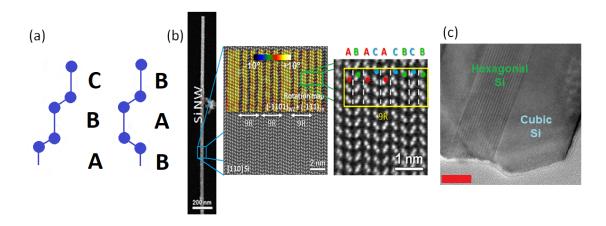

| 2.1  | Images showing the crystal structure of our SiNWs                                 | 10  |

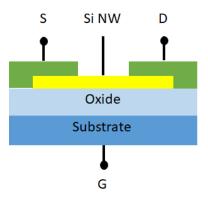

| 2.2  | Sketch of SiNW FET design                                                         | 23  |

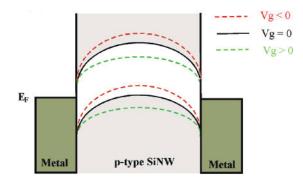

| 2.3  | Sketch of a SiNW FET device band structure                                        | 25  |

| 2.4  | Transfer characteristics and analysis of Device C1 $\ . \ . \ . \ . \ .$ .        | 27  |

| 2.5  | Image and band structure of Au-SiNW contacts                                      | 39  |

| 2.6  | Sketch showing band bending formation near contacts                               | 40  |

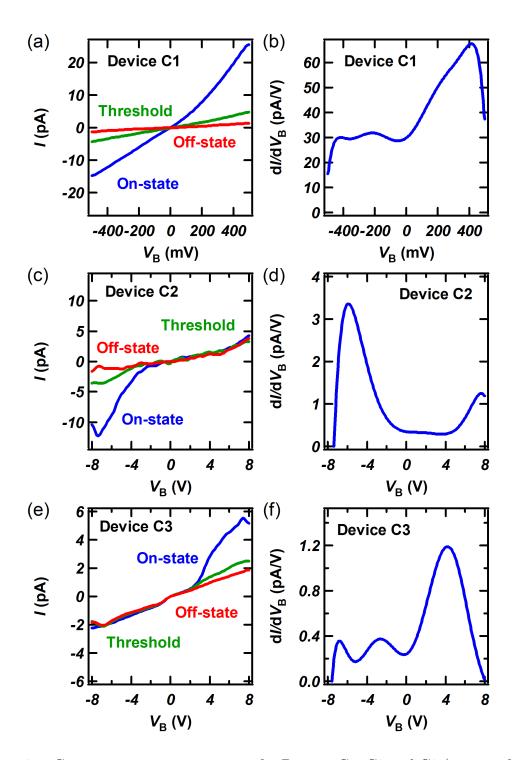

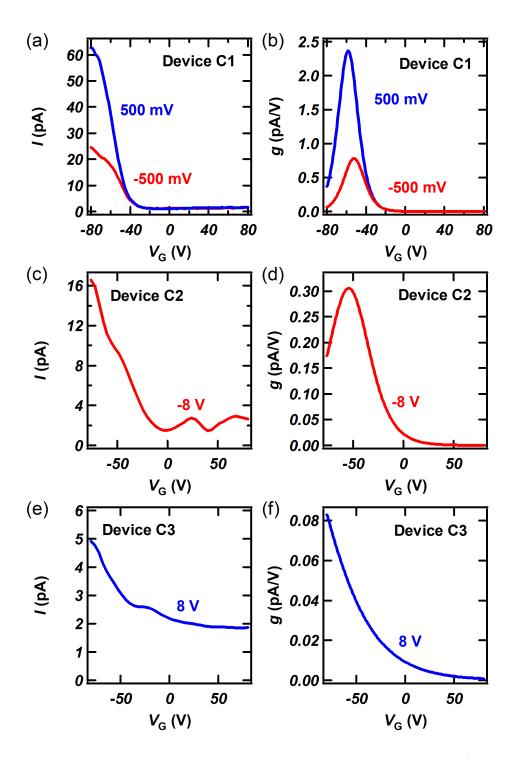

| 2.7  | Output characteristics and analysis of Device C1                                  | 55  |

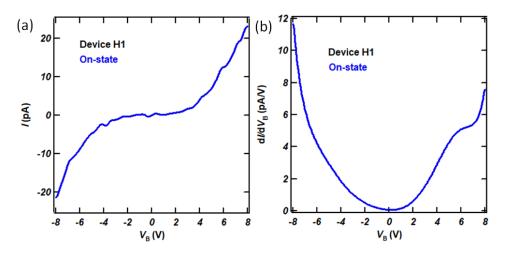

| 2.8  | Output characteristics and analysis of Device H1                                  | 58  |

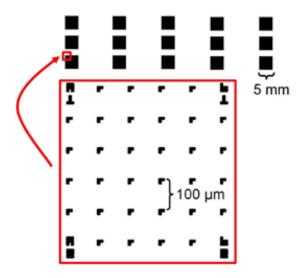

| 3.1  | Photolithography grid layout mask                                                 | 66  |

| 3.2  | Surface location grid pattern                                                     | 67  |

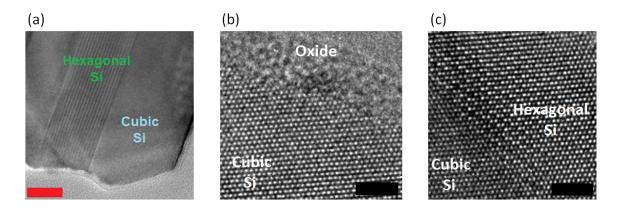

| 3.3  | TEM images showing the crystal structure of a SiNW with OSFs $~$                  | 71  |

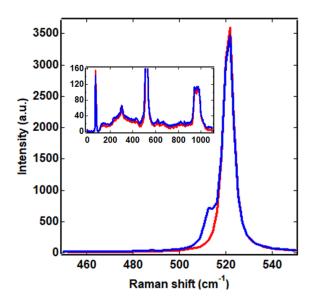

| 3.4  | Raw Raman scan data from a SiNW containing no OSFs $\ . \ . \ . \ .$              | 76  |

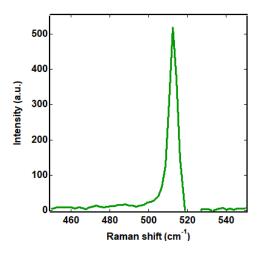

| 3.5  | Raman signature of a SiNW containing no OSFs                                      | 77  |

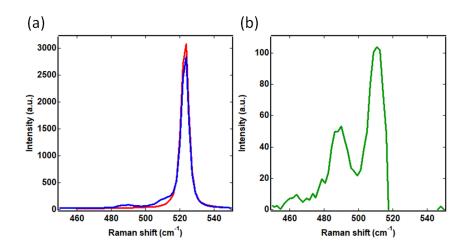

| 3.6  | Raman signature of a SiNW with OSFs                                               | 79  |

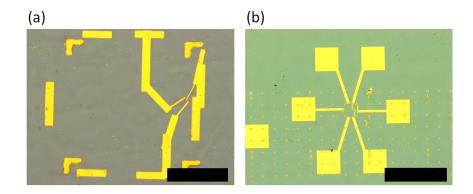

| 3.7  | EBL-defined contact patterns placed on a SiNW                                     | 85  |

| 3.8  | Wirebonding and packaging of our samples                                          | 86  |

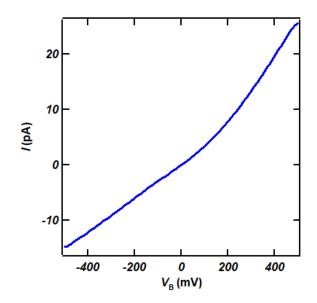

| 3.9  | Representative graph of a current vs. bias voltage data set $\ . \ . \ .$         | 94  |

| 3.10 | Representative graph of a current vs. gate voltage data set $\ . \ . \ .$         | 95  |

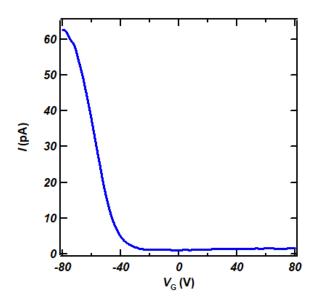

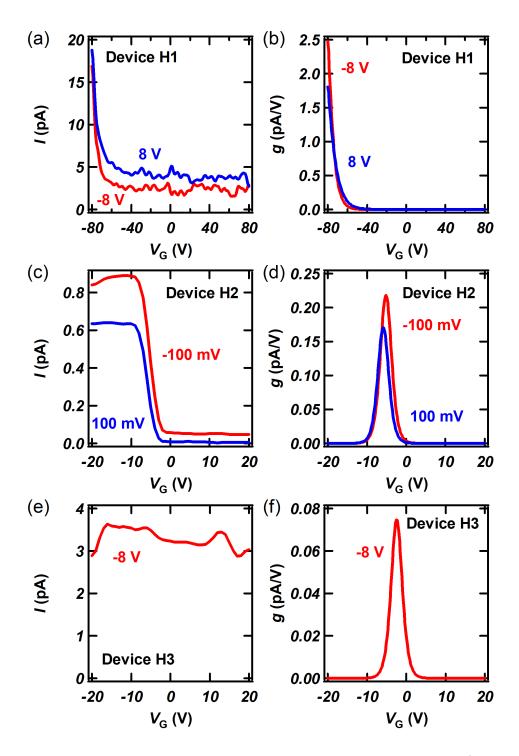

| 4.1  | Output data for Devices C1, C2 and C3 $\ldots \ldots \ldots \ldots \ldots \ldots$ | 103 |

| 4.2  | Output data for Devices H1, H2 and H3 $\ldots \ldots \ldots \ldots \ldots \ldots$ | 104 |

| 4.3  | Transfer data for Devices C1, C2 and C3 $\ldots$                                  | 109 |

| 4.4  | Transfer data for Devices H1, H2 and H3 $\ldots$                                  | 110 |

| 4.5  | Hex-Core SiNW SB-FET Transport Model                                              | 121 |

| 4.6  | SiNW SB-FET Transport Properties                                                  | 126 |

| 5.1  | SEM image of a kinked SiNW SB-FET device                                          | 133 |

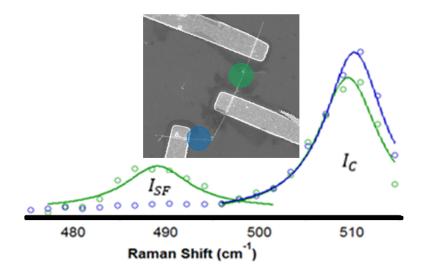

| 5.2 | Raman data of a kinked SiNW                                                   | 137 |

|-----|-------------------------------------------------------------------------------|-----|

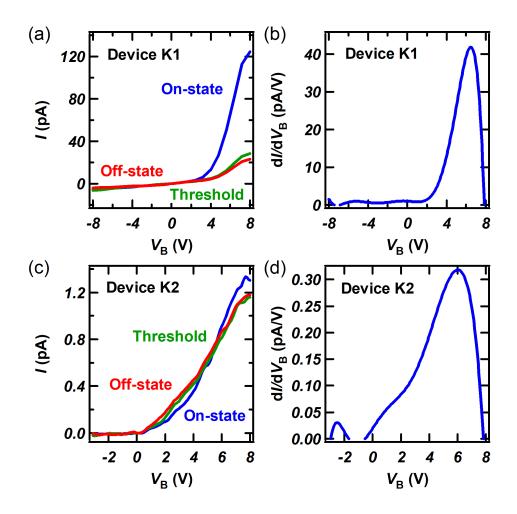

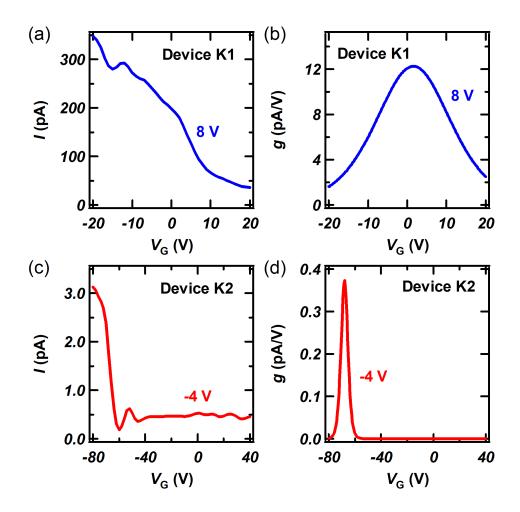

| 5.3 | Output data for Devices K1 and K2                                             | 139 |

| 5.4 | Transfer data for Devices K1 and K2 $\ldots$                                  | 141 |

| 5.5 | Temperature and gate effects on the rectifying ratio for Device $\mathrm{K1}$ | 144 |

| 5.6 | Channel asymmetry for Device K1 showing kink effect                           | 145 |

| 5.7 | Kink barrier extraction for Device K1                                         | 147 |

| 6.1 | Images of various other NW FETs found in literature                           | 153 |

# List of Tables

| 2.1 | List of Typical Material Parameter Values for Intrinsic Bulk Si at Room |     |

|-----|-------------------------------------------------------------------------|-----|

|     | Temperature (300K) Used in this Work                                    | 16  |

| 3.1 | RIE Treatment Recipes Used in this Work                                 | 65  |

| 4.1 | Dimensions and Crystal Parameters of Devices                            | 99  |

| 4.2 | Contact Parameters of Devices                                           | 106 |

| 4.3 | Channel Parameters of Devices                                           | 113 |

| 4.4 | Channel Parameters Including Oxide Trap Effects                         | 119 |

| 4.5 | Hex-Core Channel Parameters Including Interface Effects                 | 125 |

| 5.1 | Dimensions and Crystal Parameters of Kinked Devices                     | 137 |

| 5.2 | Transport Parameters of Homojunction Rectifiers                         | 140 |

| 5.3 | Channel Parameters Including Oxide Trap Effects of Kinked Devices       | 148 |

| 5.4 | Homojunction Diode Parameters                                           | 148 |

# Chapter 1

# Introduction and Thesis Structure

A large portion of the physics research in this modern technological era falls into the vast domain of condensed-matter physics. Integrated circuits have transformed our lifestyle by allowing microprocessor engineering to continuously change the landscape of modern-day electronics.

Due to its enormous abundance in nature, silicon (Si) is the material of choice for substrates and channels in micro- and nano-electronics. One of the most well studied semiconductors, Si is often used for industrial applications as it is easy to manipulate, low in cost and familiar to scientists and engineers alike [1].

Nanowire geometries are promising for next-generation field-effect transistors (FETs), as these 1D channels have advantages to the usual 2D thin films (e.g. confinement effects leading to quantum dot behavior) [1, 2]. The physics of the interplay between crystal structure and electronic properties in scaled-down devices is interesting for possible industrial applications in miniaturization [3, 4]. There is also fundamental interest in studying silicon nanowires (SiNWs). Combining ordered stacking faults (OSFs) with complex heterostructures could offer new possibilities to tune quantum dots though strain engineering [5, 6, 7, 8]. Also, suspended SiNW devices could be used for Raman thermometric measurements to determine the thermal conductivity in SiNWs with OSFs and homojunctions [9, 10, 11, 12, 13].

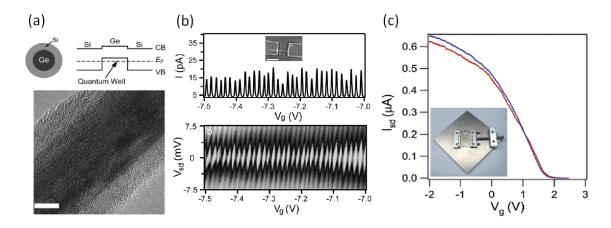

The goal of this work is to study the contact injection and channel transport properties of a novel silicon nanowire crystal structure with the use of a Schottky barrier (SB) FET device design to acquire the necessary data. Grown with ordered stacking faults, our SiNWs are used as a tool to study the fundamental physics governing charge transport mechanisms in semiconductor materials. These OSFs generate a new local hexagonal crystal phase within the usual cubic lattice by changing the Si stacking ordering inside the nanowire volume (see Fig. 1.1(a)) [14]. The electronic properties of polytype crystals have been far less studied in group IV semiconductors compared to their group III-V counterparts [15, 16, 17, 18, 19, 20]. By studying our novel hexagonal-phase SiNWs, we provide new insight into semiconductor physics.

These polytype SiNWs have distinct properties from the already known cubicphase only SiNWs. Since crystal structure affects charge carrier concentrations and band structure, the OSFs act as additional scattering sources and interface traps, hindering hole transport. This work will focus on eight SB-FET devices fabricated using SiNWs to form a channel between metal contacts (see Fig. 1.1(b)). The measurements of our SiNW SB-FET devices will be analyzed to show the impact of OSFs

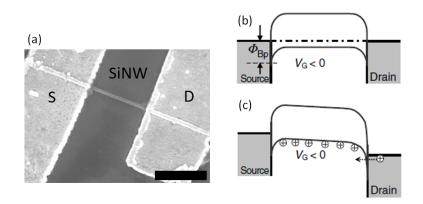

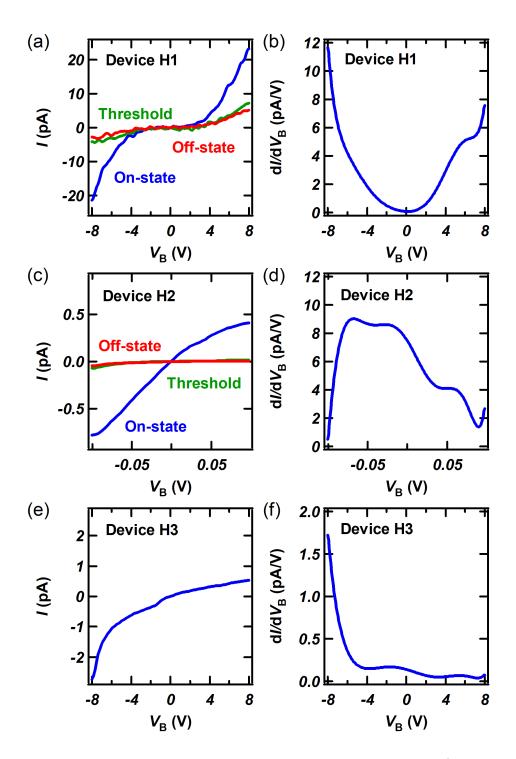

Figure 1.1: Images of our SiNW SB-FET devices. (a) TEM image of SiNW crosssection, showing hexagonal-phase Si formed by OSFs in nanowire "core", surrounded by a cubic-phase Si "shell". Scale bar 10 nm. TEM image from Moutanabbir Group archives. (b) SEM image of SiNW FET device showing a SiNW between two metal contacts (S and D). Scale bar 2  $\mu$ m. (c) Representative I - V data obtained from our SiNW SB-FET devices. Conductance can be tuned by the gate voltage by changing the state of the transistor (OFF-state in red, TH-state in green, ON-state in blue).

on various electronic characteristics (e.g. conductivity) (see Fig. 1.1(c)). Our data will show that OSFs increase device resistance, hindering hole currents by removing injection paths, effective nanowire cross-section and available charge density. By tuning OSF density along the length of a SiNW (from zero to a non-zero value), we will show how excellent rectifiers can be fabricated.

In Chapter 2, we will present the necessary theoretical background to help the reader understand our results. How we fabricated our SiNW SB-FET devices is the subject of Chapter 3. With the data acquisition process completed, Chapter 4 will present our key results on how OSFs affect hole transport through a SiNW. Then, we will show in Chapter 5 how we can engineer excellent rectifiers using kinked SiNWs by exploiting the properties of both Si crystal phases in a single device channel. The document ends with a brief chapter summarizing our work.

The following is a list of abbreviations used in this work.

| AFM                    | Atomic Force Microscopy                              |  |

|------------------------|------------------------------------------------------|--|

| APT                    |                                                      |  |

| BNC                    | Atom Probe Tomography<br>Bayonet Neill-Concelman     |  |

| CAD                    | Computer-Assisted Design                             |  |

| CVD                    | Chemical Vapor Deposition                            |  |

| DAQ                    | Data Acquisition                                     |  |

| DAQ                    | Direct Current                                       |  |

| DFT                    | Density Functional Theory                            |  |

| EBL                    | · · ·                                                |  |

| $_{\rm FET}^{\rm EBL}$ | Electron-Beam Lithography<br>Field-Effect Transistor |  |

| GUI                    |                                                      |  |

|                        | Graphical User Interface                             |  |

| HRTEM                  | High Resolution TEM                                  |  |

| IPA<br>MIDK            | Isopropyl Alcohol                                    |  |

| MIBK                   | Methyl Isobutyl Ketone                               |  |

| NW                     | Nanowire                                             |  |

| OSF                    | Ordered Stacking Fault                               |  |

| PMMA                   | Polymethyl Methacrylate                              |  |

| RIE                    | Reactive Ion Etching                                 |  |

| RF                     | Radio Frequency                                      |  |

| SB                     | Schottky Barrier                                     |  |

| SCE                    | Short Channel Effect                                 |  |

| SEM                    | Scanning Electron Microscope                         |  |

| SiNW                   | Silicon NW                                           |  |

| TAT                    | Thermally Assisted Tunneling                         |  |

| TEM                    | Transmission Electron Microscope                     |  |

| TFE                    | Thermionic Field Emission                            |  |

| UHV                    | Ultra-High Vacuum                                    |  |

| UV                     | Ultraviolet                                          |  |

| VLS                    | Vapor-Liquid-Solid                                   |  |

| WKB                    | Wentzel-Kramers-Brillouin                            |  |

| WZ                     | Wurtzite                                             |  |

| ZB                     | Zinc-Blende                                          |  |

# Chapter 2

# Transport Concepts in Hexagonal-Core Silicon Nanowire Transistors

In this chapter, we will present the concepts needed in this thesis to understand charge transport in hexagonal-core silicon nanowire (SiNW) transistors. The topics will be presented briefly, giving only what is required to move forward without full theoretical rigor. References dedicated to this subject are readily available and will be provided when relevant if additional information is desired (see Bibliography).

Section 2.1 presents the terminology that we will need to effectively discuss crystal structure, crystal defects, and electronic band structure. Using these definitions, we then present in section 2.2 the various properties of silicon crystals relevant to electronic transport in its equilibrium state. In section 2.3, we will show how the Fermi

gas model can be used to predict the conductivity of our SiNWs. In section 2.4, we will present the design and function of a field-effect transistor (FET) device fabricated using our SiNWs as the channel. This will lead to the discussion of our greatest experimental challenge in section 2.5: the metal-semiconductor contacts and the Schottky barriers (SBs). This chapter will conclude in section 2.6 with the physics of rectifying devices and how their behavior can help us understand the results presented in chapters 4 and 5.

## 2.1 Lattice and Band Structure

We will quickly go over the terminology from condensed-matter physics that will be used for the remaining of this text. This will allow us to properly define the material that is under study in this work.

#### 2.1.1 Tuning SiNW Crystal Structure

Often, a semiconducting crystal is altered to tune its transport properties (e.g. charge conductivity, thermal conductivity) by incorporating a small but known amount of impurities (atoms that differ from the crystal's atomic composition) [21]. These will act as dopants, providing additional electrons or holes to the crystal, which in turn will give the material modified extrinsic properties (which we will discuss further in section 2.2).

Another method to tune a material's transport properties is to combine various

crystals of different atomic compositions to create heterostructures [1]. The new material formed by these crystals and their interfaces will often have new and interesting properties that are not simply the combination of those from its constituents.

However, a method that is less studied is by introducing controlled defects in the crystal structure itself without changing its chemical composition [1]. As a general rule, crystal defects give unwanted properties to a material. They typically create scattering centers which will hinder charge and phonon transport through the crystal. It is much simpler to try to limit defects from occurring, instead of attempting the complicated calculations required to understand their new characteristics.

There are three main classes of crystal defects [21]. The first are point defects, where individual atoms are either missing from a point in the lattice as vacancies or are placed at incorrect locations as interstitials. For example, dopants fall into this category, as they substitute an atom from the lattice to incorporate themselves. Next are line defects, which occur when a connected set of lattice points has misplaced atoms. For example, a crystal dislocation will create a line defect and will affect the mechanical strength of the material. The last are planar defects, where an entire plane in the lattice is at fault. In this work, it is this defect class that we are interested in studying.

In its natural state, the structure of a silicon crystal is two interpenetrating facecentered cubic lattices. As seen along the (111) crystal direction, the stacking sequence of the atom planes follow the 3C symmetry, meaning that three planes are required in order to generate the cubic-phase repetition. Calling these stacks "A", "B" and "C", the 3C sequence corresponds to "...ABCABCABC..." (see Fig. 2.1(a)). If there are no planar defects in the crystal, then the sequence is uninterrupted and the lattice has the highest level of crystalline quality.

However, planar defects could appear, creating random deformations in the stacking sequence [22]. A single modification to the pure crystal stacking sequence is called a stacking fault. There are three main categories of stacking faults (SFs). The first are intrinsic SFs, where a single stack is missing from the sequence. For example, where "/" represents the SF, the sequence "...ABC/BCABC..." shows an intrinsic SF (the stack "A" is missing). The next are extrinsic SFs, where a single stack is added to the sequence. For example, in "...ABC/B/ABC...", the stack "B" is inserted incorrectly in the 3C pattern. The last are twin boundary faults, where the stacking sequence is rotated and the lattice becomes a mirror image of the regular order at the fault plane. This creates an inversion in the sequence at the twin boundary (for example, "...ABCA/ACBACB...").

Instead of allowing these defects to occur randomly, it is possible (in principle) to control the frequency and location of SFs within a crystal during formation. Under the correct growth parameters (see section 3.1.3), a crystal can be grown with a large number of SFs. If a set of multiple successive SFs is present in a given region, then they will become ordered stacking faults (OSFs). These in turn will create new ordered stacking sequences that differ from the 3C structure of the original crystal, which could correspond to a hexagonal close packed lattice. For example, they might generate a 9R pattern, meaning a repetition of nine stacks following the "...ABACACBCB..." order, giving a rhombohedral lattice. Another would be the 2H pattern, a simple hexagonal-phase lattice with the "...ABABAB..." order of two alternating stacks (see Fig. 2.1(a)).

If the stacking fault density isn't high enough, then these OSFs will simply act as defects. At least four consecutive stacking sequences are required to assign a new crystal phase [23]. In a silicon lattice, this means that a region of roughly 4 nm is required for OSFs to generate a hexagonal-phase crystal interface with the typical cubic-phase [24].

The silicon nanowires used in this work were grown by Dr. Uri Givan, a former post-doctoral researcher of Dr. Moutanabbir, at the Max Planck Institute in Germany. Using the VLS method (see section 3.1.3), our SiNWs were grown by incorporating OSFs within the lattice with the goal of generating a hexagonal-phase Si crystal (see Fig. 2.1(b)). Using TEM images, we confirm that the SiNWs have a "core-shell" structure of hexagonal-phase Si near the rectangular-shaped middle of the nanowire surrounded by cubic-phase Si near the surface (see Fig. 2.1(c)) [14, 15].

The properties of polytype nanowires having various distribution of crystal structure have already been extensively studied, especially in group III-V nanowires. In the case where two distinct elements are used to form the atomic crystal, the two equivalent symmetries for cubic and hexagonal are respectively zinc-blende (ZB) and wurtzite (WZ) [3]. Recent examples include InP nanowires and InAs nanowires [3, 4, 23].

However, theoretical studies of group IV nanowires sharing our structure are very

Figure 2.1: Transmission Electron Microscope (TEM) images showing the crystal structure of our SiNWs (a) Sketch of the 3C and 2H crystal stacking pattern. (b) High resolution TEM images showing the crystal structure of our SiNWs in various length scales. The 9R crystal stacking pattern can be identified. (c) TEM image of SiNW cross-section, showing hexagonal-phase Si formed by OSFs in nanowire "core", surrounded by a cubic-phase Si "shell". Notice that part of the hexagonal-phase Si portion is in contact with the NW surface. Scale bar 10 nm. TEM Images from Moutanabbir Group archives.

limited in literature, and experimental studies on their transport properties have not yet been published. Our novel hexagonal-core SiNWs are interesting to study, as they have a single chemical composition yet act as an inhomogeneous crystal structure [22]. This will allow us to focus on how solely the crystal structure affects the material's transport properties.

#### 2.1.2 SiNW Band Structure

Crystal defects play an important role in transport mechanisms by modifying the semiconductor's band structure. For example, local lattice modifications creates new (or removes existing) energy levels available for electrons, holes and phonons. Charge traps generated by the defects often reduce the crystal's electrical conductivity, while the addition of scattering centers alter its thermal conductivity. Moreover, the material's optical properties could also be modified. For example, new crystal vibrational modes introduced by the defects could be "Raman active", meaning detectable by Raman spectroscopy (see section 3.2.1).

As mentioned previously, with sufficient OSF density, a new crystal phase will be embedded within the surrounding lattice. In the case of our SiNWs, the hexagonalphase Si (or "Hex-Si" for short) near the middle of the NW is sandwiched by cubicphase Si (or "Cub-Si" for short) near the surface. This would introduce new properties beyond the familiar Cub-Si nanowire material (electrical, thermal and optical), both from the presence of Hex-Si and from the Hex-Si/Cub-Si interfaces.

The interface between two bulk crystal phases is called the grain boundary. The presence of grain boundaries in a material usually introduces several complications to the analysis of the physics governing the crystal's band structure. The interface is also rarely precisely defined, as it is often plagued by its own defects as the lattice of the two crystals attempt to bond with their neighboring atoms in the structure [1, 21].

A commonly found issue comes from lattice mismatch, when the lattice constants and the symmetry of both crystals are not identical. To successfully create an interface, the two crystals must bond with each other despite this mismatch, so accommodations must be made by introducing strain and deformations. The defects and dangling bonds generated at the grain boundary will lead to electron, hole and phonon scattering, which affects transport behavior [22, 25]. The Hex-Si/Cub-Si grain boundary is no exception to this phenomenon. With a lattice mismatch of 0.5% between Hex-Si and Cub-Si, it is expected that these new interfaces will affect the crystal's electrical and thermal conductivities (see section 2.6) [1, 26, 27].

To understand how the Hex-Si lattice alters the properties of our SiNWs, a description of the various energy levels available in both crystals and at the interfaces is required. One method to obtain a material's band structure is by theoretical calculations based on first-principles. Using appropriate approximations, the eigenstates of a crystal's Hamiltonian can be solved and plotted as band diagrams [26]. For example, with density functional theory (DFT) using the pseudopotential local density approximation (LDA), the electronic band structure of semiconductor heterocrystals can be predicted [24].

DFT calculations predict a type II band alignment (both valence and conduction bands are offset to higher values) at the Hex-Si/Cub-Si interface [24, 26, 28]. Using experimentally relevant NW diameter values (between 20 and 80 nm, depending on the study), it is predicted that both the maximum of the valence band and the minimum of the conduction band are offset to higher values in Hex-Si compared to an equivalent Cub-Si counterpart. If the crystal structure contains both phases, then the OSFs present in the SiNW will create shallow states within the gap of around 0.10 - 0.15 eV above the valence band in the NW core [24, 26].

## 2.2 Intrinsic and Extrinsic Transport Properties

When a crystal is pure and in thermal equilibrium, the ground-state of the semiconductor describes its intrinsic electronic transport properties. When dopants are present to alter the material's lattice structure, new extrinsic properties of the crystal will emerge. This case is of course far more interesting, as the extrinsic electronic behavior of the crystal can be modified.

The key parameter that describes a crystal's electronic properties is its charge carrier density. It is defined as the number of electrons or holes found in a unit space of volume, and denoted by n or p, respectively. In this work, cm<sup>-3</sup> units will be used when expressing charge density values, in accordance with the common unit system found in literature. How charge density is determined is the topic of this section.

#### 2.2.1 Charge Carrier Densities

For an intrinsic semiconductor, the Fermi energy  $E_F$  is somewhere in the band gap, typically near the mid-gap point. The exact value for the intrinsic  $E_F$  depends on the electron and hole effective mass (which are determined by the curvature of the conduction and valence band edges) as well as the temperature T of the crystal [21]. If the Fermi level is exactly at the mid-gap point, then the electron n and hole p densities are equal. If not, then one of the charge carrier densities will be slightly greater than the other. However, the following simple relation will be respected between electron and hole densities, where  $n_i$  is the intrinsic carrier density and can be calculated knowing the crystal's band structure.

$$np = n_i^2 \tag{2.1}$$

In the case where  $E_F$  is at the mid-gap point, we will find that  $n = p = n_i$ , according to Eq. 2.1. Furthermore, in the equilibrium state, the Fermi energy has the same value at all points in the crystal, meaning that the charge density is constant and uniform within the material.

By applying a constant electric field through the crystal, the electrons and holes will diffuse in opposite direction, creating an electric current following Ohm's Law if the crystal is part of a closed circuit. Intuitively, the value of the current will increase when charge density increases, since more carriers will be available (this will be discussed in greater detail in section 2.3).

When a semiconductor is sufficiently doped at room temperature, it is possible to know exactly the values of both charge carrier densities. For example, in the case of an n-type semiconductor, if the density of donor impurities in the crystal is N, then it can be assumed for simplicity that n = N and that p is the value given by Eq. 2.1.

However, there are a few disadvantages to controlling a semiconductor's charge densities with doping. The one most relevant to our work is that doping via ion implantation can create beam-induced damage and crystal amorphization [29]. Since our SiNWs are already grown without intentional impurities, these dopants would have to be introduced during the device fabrication process (see section 3.3), which would both complicate the procedure and risk damaging the very crystal structure we are attempting to study.

The SiNWs used in this work are grown following the VLS process (see section 3.1.3), where gold nanodroplets are used to catalyze the growth. While it was desired to grow non-intentionally doped high purity Si crystals, some Au atoms will be incorporated in our SiNWs. Otherwise undoped, these Au impurities will give the NWs a weak p-type behavior, as Au are "deep-level" acceptor impurities in Si (creating acceptor levels far from the valence band and close to mid-gap).

Another method to tune the Fermi level must be used to control charge density in our work, as the doping approach will not be appropriate for our SiNWs with OSFs. This is done using a transverse electric field through the NW cross-section generated by an electric potential called the gate voltage. This will be the subject of a later section (see section 2.4.1).

#### 2.2.2 Bulk Silicon Transport Properties

We briefly review the nomenclature of transport properties specific in Si. To start, we present the parameters of bulk Si in its familiar and usual cubic-phase lattice.

Si is by far the best-known semiconducting material. Textbooks on the subject of semiconductor or condensed-matter physics will either use Si as the primary example material or dedicate an entire chapter solely on its characteristics [21, 30, 31]. It is not difficult to find all relevant physical and chemical properties of bulk Si in literature.

The following table shows a list of the values for the relevant Si parameters that

will be needed in this work. Refer to the appropriate section of the text to find information and definitions of the various properties shown.

| Energy band gap                         | $E_g$        | 1.12  eV                                  |

|-----------------------------------------|--------------|-------------------------------------------|

| Intrinsic Fermi level energy            | $E_{Fi}$     | $0.571 \ \mathrm{eV}$                     |

| Effective mass (electron)               | $m_e^*$      | $0.33m_{e}$                               |

| Effective mass (hole)                   | $m_h^*$      | $0.50m_e$                                 |

| Relative permittivity                   | $\epsilon_r$ | 12                                        |

| Richardson constant (hole)              | $A^*$        | $4.68 \ge 10^5 \text{ A/m}^2 \text{K}^2$  |

| Scattering-limited electron velocity    | $v_{d,max}$  | $10^7 \mathrm{~cm/s}$                     |

| Mobility (electron)                     | $\mu_e$      | $1900 \text{ cm}^2/\text{Vs}$             |

| Mobility (hole)                         | $\mu_h$      | $425 \text{ cm}^2/\text{Vs}$              |

| Resistivity at intrinsic charge density | ρ            | $6.4 \ge 10^4 \Omega \mathrm{cm}$         |

| Intrinsic charge density                | $n_i$        | $1.18 \text{ x } 10^{10} \text{ cm}^{-3}$ |

|                                         |              |                                           |

| Values from $[21, 30, 31]$              |              |                                           |

Table 2.1: List of Typical Material Parameter Values for Intrinsic Bulk Si at Room Temperature (300K) Used in this Work

We can study a semiconducting crystal in a NW geometry in order to explore how these parameters differ from the bulk state. For example, we use the values in Table 2.1 to estimate the channel resistance of our SiNWs and then compare this to the measured value [32].

## 2.3 Conductivity in the Fermi Gas Model

It is now necessary to provide a transport model to be able to predict our semiconducting material's conductivity. We will take our SiNWs as diffusive channels, where the free electrons and holes within the NW drift in the orientation of the applied electric field. As long as the NW length L is larger than the mean free path l of the carriers (average distance between collision), then the Fermi gas model will adequately describe the electronic behavior of our SiNWs [21]. We will show later that this criteria is easily met in our work. In fact, all ballistic transport models are incorrect in our case and will therefore not be discussed [33].

In this section, we will provide the definitions for charge conductance, conductivity and mobility under the Fermi gas model. These will later be needed to properly understand the results obtained after completing the electronic measurements done on our SiNWs with OSFs.

#### 2.3.1 Conductance and Conductivity

We begin with the familiar macroscopic version of Ohm's Law which defines the measured resistance R when applying a voltage V through a resistor. Assuming the resistor carries constant and uniform current I, one can also express the resistance using the dimensions of the resistor (length L and cross-section A) and its resistivity  $\rho$  (a property characteristic of the material used) via  $R = V/I = \rho L/A$ .

Equivalently, these equations can be inverted to give the definitions of conductance G = 1/R and conductivity  $\sigma = 1/\rho$ . This simple Ohmic model will be used to describe the channel conductance of our SiNWs via  $G = I/V = \sigma A/L$ .

However, to understand the physics behind conductivity measurements, the microscopic version of Ohm's Law must be used. For metals (under the familiar Drude model), the relationship between effective charge density n, drift velocity  $v_d$ , electric field E and current density J also uses the concept of conductivity (where e is the elementary charge).

$$J = \sigma E = nev_d \tag{2.2}$$

For semiconductors, both electrons and holes will contribute to current, so in general both must be accounted for when using Eq. 2.2. It can easily be shown that conductivity takes the simple form  $\sigma = ne\mu_e + pe\mu_h$  in the linear regime [21].

The link between conductivity and charge density is called mobility. Note that the values for electron  $\mu_e$  and hole  $\mu_h$  mobility are not equal in general (see Table 2.1 as an example).

For large band gap  $(E_g \gg k_B T)$  p-type semiconductors (our SiNWs meet this criteria), we may ignore the electron current [33]. This will allow us to write Eq. 2.3, and it is this equation that will be used in this work when calculating charge density from the measured mobility and conductivity of our SiNWs (the subscript "h" for hole mobility is dropped) [3].

$$\sigma = pe\mu \tag{2.3}$$

Heavily doped NWs made from high quality crystals have very similar measured conductivity values, as the value of p is precisely known and controlled [34]. However, for undoped NWs (like the SiNWs used in this work), vastly different results can be obtained from even a set of seemingly similar samples. Several factors complicate the modeling of electronic transport in undoped NWs, most of which come from the NW's surface [4, 33, 34]. Impurities from the surface can act as charge traps in the form of dangling bonds, modifying the value of p at the surface compared to the bulk value. If the NW diameter is very small, then these surface effects can completely supersede all bulk properties of the material, which complicates the analysis of electronic measurements.

#### 2.3.2 Charge Mobility

In order to calculate the charge density in our SiNWs with Eq. 2.3, we acquire a measurement of conductivity and a measurement of mobility  $\mu$ . Here, we will give the microscopic definition of charge mobility according to the Fermi gas model assumptions.

To satisfy Eq. 2.2, written under the Drude model, we define charge mobility  $\mu$  as the ratio between the drift velocity gained by the charges diffusing in a material containing an electric field E and the value of that field. Since classical momentum resets after each collision, the average momentum gained by the charge between collisions is given by the impulse generated by the electric field in the time  $\tau$ .

$$\mu = \frac{e\tau}{m^*} = \frac{v_d}{E} \tag{2.4}$$

In the Fermi gas model, only the free charge carriers of effective mass  $m^*$  found near the Fermi surface  $p_F$  are relevant when discussing the electrical current formed in the material under the electric field [21]. The value of  $\tau$  represents the average time between scattering events (e.g. charge-phonon, charge-charge, charge-impurities). These charge carriers, however, have a large Fermi velocity  $v_F$ , so that  $p_F v_F = p v_d$ . This change of perspective from the Drude model for metals to the Fermi gas model for semiconductors allows us to make a link between equations such as Eqs. 2.3 and 2.4 and the measurements done on our SiNWs [30].

Charge mobility can be viewed as a material property, expressing how effectively the charge carriers of effective mass  $m^*$  will diffuse through the crystal when a voltage is applied. Mobility is a measurement of the various scattering mechanisms the electrons and holes are subject to when in motion (this information is contained in  $\tau$ ). In the linear regime, mobility will not depend on E, but under a strong field the charge carrier sea will eventually saturate to its maximum drift velocity (with  $\mu$ dropping as E increases). In bulk Si, the scattering-limited drift velocity saturates at  $10^7$  cm/s [35].

Another mechanism limiting mobility is collisions with impurities within the crystal. By doping a semiconducting NW, charge density p will increase, but this will generate additional scattering centers (the charge-phonon scattering rate increases locally near the impurity), which will lower mobility. These two competing factors must be accounted for when attempting to maximize conductivity Eq. 2.3. If these impurities are from surface states, then lowering the NW diameter will also decrease mobility [36].

Naturally, crystal defects will also play an important role in mobility. In III-V semiconductors, it is already known that polytype NWs have an undesired suppression of transport properties (e.g. conductivity), and lowering stacking fault density will

increase mobility [23]. According to Matthiessen's rule, mobility will be reduced to the value corresponding to the most dominant scattering mechanism. Our undoped intrinsic NWs are expected to have a very low mobility (several orders of magnitude lower than the bulk value, see section 4.1.2), as surface states and OSF defects will dominate transport [3, 36].

As a final note, instead of using the average time between collisions as a measurement of scattering, one could also use the average distance l (mean free path) a charge will move through the crystal before a collision using Eq. 2.5 [21].

$$l = v_d \tau = \frac{\mu}{e} \sqrt{k_B T m^*} \tag{2.5}$$

## 2.4 Nanowire Field-Effect Transistor Device

In previous sections, the formal definitions of relevant transport properties of a semiconducting crystal within the Fermi gas model were presented. We now require an applied model to link these properties to measurements done on our SiNWs in order to understand how OSFs affect charge transport.

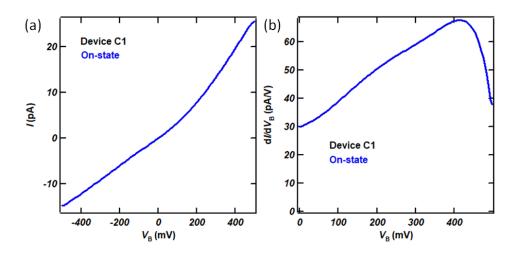

The electrical measurement setup is to simply place two metal contacts on both ends on the NW channel. When applying a bias voltage  $V_B$  on the source electrode (S), an electric field inside the NW will create a current exiting the drain electrode (D) (see Fig. 2.2). Conductivity can be measured assuming the voltage drop occurs solely in the channel (however, this will not be the case for our SiNW devices, see section 2.5 for details on how this will complicate our analysis). With Eq. 2.3, the charge density can be calculated knowing mobility which would complete the analysis of the crystal's transport properties.

The problem, of course, is that the hole mobility of our SiNWs is unknown (we can't simply take the bulk value as surface states and defects will greatly alter the value, see section 2.3.2). Furthermore, as they are undoped, the value of charge density in our SiNWs is also unknown. We require a measurement setup that permits the charge density value to be modulated by a separate tuning parameter. Studying how conductivity varies by this parameter will give us insight on which values p and  $\mu$  must take to correspond to Eq. 2.3, and how they are altered by the presence of OSFs (through the *Hex* value, see section 3.2.3 for its definition).

A device setup that satisfies this criteria is the Field-Effect Transistor (FET) setup. Since a transverse electric field can modulate the Fermi level in a semiconductor, which in turn tunes charge carrier density, a third electrode is required to generate this field in our SiNW channels. In our case, this is done with a capacitively-coupled gate electrode (G) placed under the dielectric oxide layer which supports the NW (see Fig. 2.2). By applying a gate voltage  $V_G$ , it is possible to greatly change the device resistance, creating a transistor device. Details on how to fabricate these SiNW FET devices can be found in section 3.3.

To help illustrate the concepts presented in the remaining sections of this chapter, we will use data we obtained from selected SiNW FET devices. This will allow us to simultaneously show example calculations on the presented equations while providing

Figure 2.2: Sketch illustrating the SiNW FET design. The SiNW ends are seen between the source (S) and drain (D) electrode metal thin films and the oxide layer over the substrate acting as the back-gate electrode (G).

a useful data analysis tutorial for a reader who wishes to continue this work further. Only a few examples will be used, but a full list of all analyzed SiNW devices in this work can be found in section 4.1.

#### 2.4.1 Gate Capacitance

A transistor device is a three-terminal electronic component where one electrode controls the current passing through the other two electrodes. For our FET devices, the voltage applied to the gate electrode produces an electric field affecting the current in the SiNW channel connecting the source and drain electrodes (see Fig. 2.2). It is important that the gate electrode produces an electric field inside the NW but does not supply current, meaning that there is no direct electrical connection between the gate and the channel. If a connection accidentally occurs, the functionality of the device is compromised (see section 3.4.2).

A dielectric material is placed between the gate and all other components of

the FET device to prevent this while creating the desired capacitively-coupled gate electrode. In our case, the oxide layer of the sample plays the role of the gate dielectric. Since the gate electrode is underneath the SiNW channel, our FET devices are in the "back-gate" configuration. Other gate configurations that can be found elsewhere are "top-gate" (the dielectric thin film is deposited over the nanowire) and "gate-allaround" (the NW is wrapped by the dielectric material), and they offer their own advantages and disadvantages.

The role of bias voltage is to generate the current itself and to vary the distribution of the carriers within the channel, while the role of gate voltage is to tune the current by modulating the value of p [37]. By applying the gate voltage, the gate field produced inside the semiconductor will move  $E_F$  by Coulomb interaction as long as the oxide layer has the dielectric strength necessary to carry the desired field.

For a heavily doped n-type gate electrode (the Si wafer backside) on a semiconductor (our SiNWs) FET device, positive values for  $V_G$  will move the channel's Fermi level from its original intrinsic position toward the conduction band, while negative values will move  $E_F$  toward the valence band (see Fig. 2.3). This means that tuning the gate voltage towards positive values will deplete the p-type NW, decreasing the current flowing through the channel. Tuning  $V_G$  toward more negative values will introduce additional holes in the SiNWs, increasing channel conductivity.

Fundamentally, the relationship between the charge introduced in the SiNW channel and the applied gate voltage is the gate capacitor. The oxide layer of thickness  $t_{ox}$  with permittivity  $\epsilon$  acts as the dielectric within the capacitor. This oxide layer

Figure 2.3: Sketch showing the effect of the gate electrode on the FET device band structure. The band structures of the metals are not affected by  $V_G$ . Image from [36] separates the gate electrode (a conductive plane formed by the highly doped Si wafer backside) from the NW of diameter d and length L. The gate capacitance can then be calculated using a simple cylinder-on-plane model.

$$C_G = \frac{2\pi\epsilon L}{\ln(4t_{ox}/d)} \tag{2.6}$$

The issue here is that the SiNW is not metallic, meaning that Eq. 2.6 will overestimate the value of gate capacitance (the exact value of  $C_G$  is unknown). The gate field will enter the SiNW but will not be uniform in its cross-section. The top section of the NW is unaffected by the bottom gate voltage, meaning that only a small unknown volume of the SiNW near the oxide layer can be modulated by the gate [4]. For undoped NW FET devices on a SiO<sub>2</sub> back-gate, using 1.44 as the value for the oxide relative permittivity instead of the accepted value for the oxide layer (which is 3.9) when calculating Eq. 2.6 will account for this non-uniform gate field and give a better estimate value for  $C_G$  (we will take this calculated value as having a 10% error) [34]. Furthermore, any interfaces existing in the FET device channel either between the undoped SiNW and an oxide layer (e.g. the gate dielectric or the thin thermal oxide layer around the nanowire) or between different Si phases (for example, the Cub-Si/Hex-Si interface) will generate charge traps (see section 2.1.2). These will also reduce the effective gate capacitance, modifying the estimate for  $C_G$  as the traps will act as a series capacitance to the gate capacitor [38]. For interface trap density  $D_{it}$ , expressed in number of trap states per cm<sup>2</sup> per V, the interface trap capacitance  $C_{it}$  is given by  $eD_{it}A_{it}$ , where  $A_{it}$  is the interface area. This effect will greatly impact the gate coupling efficiency to our SiNWs, especially those with OSFs.

#### 2.4.2 Device Switching: Transconductance and Threshold

With an understanding of the role the gate electrode takes on a FET device, we are now ready to present transport data obtained from measurements done on our SiNWs to demonstrate how to properly analyze the data and extract the desired parameters (e.g. mobility, conductivity). The model presented below is only applicable when the FET device is operating in its "linear" regime. In terms of the device parameters, this is where the current scales with the bias voltage (as opposed to the "barrier" and "saturation" regimes to be discussed later in the following section), where the bias voltage is much lower than the gate voltage, and only for FET devices where L is larger than both d and  $t_{ox}$  [39]. All presented SiNW FET devices in this work satisfy these conditions.

As our example, we use "Device C1" (see section 4.1 for full device list) to illustrate

our analysis of how the gate affects the current passing through a SiNW FET device. The relevant data from Device C1 is shown in Fig. 2.4. This particular device has a Cub-Si only (without any OSFs) SiNW of diameter d = 50 nm forming a  $L = 2 \ \mu \text{m}$ channel between two contact electrodes, all of which resting on a  $t_{ox} = 300$  nm oxide layer forming the back-gate dielectric. Note that L is larger than both d and  $t_{ox}$ , as required. Using Eq. 2.6 along with the appropriate modification to the accepted value of oxide permittivity (to account for the non-ideal gate electrode), we estimate the gate capacitance to be 36.5 aF (atto- is the SI prefix for  $10^{-18}$ ).

Fig. 2.4(a) shows a graph of the measured current exiting the drain electrode at a fixed bias voltage applied to the source electrode as the gate voltage is modified. An I-V curve plotted under these conditions is called a transfer curve, which is often the standard method of presenting FET data to show its proper operation.

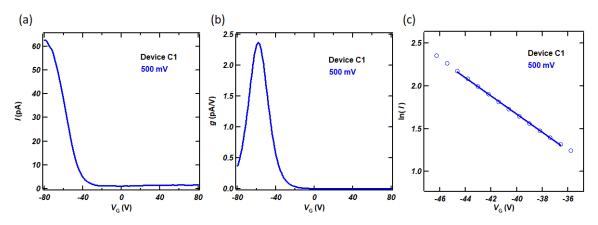

Figure 2.4: Transfer characteristics of Device C1 (see text) to demonstrate data analysis methods. All curves shown are taken at  $V_B = 0.5$  V. (a) Transfer curve showing good FET behavior as the gate voltage can effectively control the device current. (b) Transconductance curve used to identify  $g_m$  parameter. (c) Logarithm of the transfer curve in the subthreshold gate voltage range. Data points are open circles, linear fit in solid line used to extract S.

Immediately, we notice that the gate electrode can effectively tune the current

passing through the channel. The  $V_G = 0$  point describes the current that we would expect if this SiNW were not a part of a FET device but instead used as a basic resistor unit between two electrodes. With a very small current of 1.1 pA (showing the great difficulty we had in measuring our devices, see section 3.4.3) at  $V_B = 0.5$  V, we obtain a device resistance of around 455 G $\Omega$ . This value does not change appreciatively in the gate voltage range from 80 V to -20 V, but when  $V_G$  passes through -20 V towards larger negative values we see the device conductance increasing significantly. This confirms the p-type behavior expected from our SiNWs and clearly demonstrates the "switching" profile of the gate on our FET devices.

The parameter used to describe gate switching is transconductance, labeled g. As opposed to conductance G, transconductance is defined as the differential  $dI/dV_G$ and is visualized as the slope of the tangent on a transfer curve. As shown in Fig. 2.4(b), the transconductance of Device C1 is essentially zero in the gate voltage range from 80 V to -20 V, steadily increases to 2.365 pA/V around -58 V only to decrease again afterwards. This single peak behavior in g is the signature of a well-behaved FET device in the linear regime. The maximum value of transconductance at a given bias voltage  $g_m$  (the height of the peak) is of special importance to characterize a FET device.

The first use of identifying a FET device's  $g_m$  value is that it can be used to determine charge mobility [1]. Called the FET mobility  $\mu_{FET}$ , it is used as a figureof-merit for such transistor devices. In the linear regime,  $g_m$  scales with  $V_B$ , meaning that the measurement of  $\mu_{FET}$  should be insensitive to the exact choice of applied bias voltage as long as the FET is well-behaved.

$$\mu_{FET} = \frac{g_m L^2}{C_G V_B} \tag{2.7}$$

For Device C1, using  $g_m = 2.365 \text{ pA/V}$  in Eq. 2.7, we calculate a FET mobility of 5.2 x  $10^{-3} \text{ cm}^2/\text{Vs}$ . Note that this measurement was done at  $V_B = 0.5 \text{ V}$  with  $g_m$ located at  $V_G = -58 \text{ V}$ , where the bias voltage is much lower than the gate voltage, as required. Typical values in literature for  $\mu_{FET}$  found in similar FET devices made from undoped SiNWs are also in the  $10^{-3} \text{ cm}^2/\text{Vs}$  range, validating our results [36]. Only in the linear regime does the FET mobility  $\mu_{FET}$  found using transconductance measurements equal the charge mobility  $\mu$  found in the Fermi gas model equation for conductivity Eq. 2.3 [39].

The second use of identifying a FET device's  $g_m$  value is that it can be used to determine the threshold voltage  $V_{TH}$ . One of the most important values to characterize a FET device, the threshold voltage represents the gate voltage required to transition between weak and strong inversion in a semiconducting channel [40]. Visually,  $V_{TH}$ can be seen on a transfer curve at the onset of significant current flow (the device "switch" point on the  $V_G$  axis).

In order to extract a value for  $V_{TH}$ , the most widely used method is to take a linear extrapolation at the point on the transfer curve where  $g_m$  was found and calculate the point that intersects the gate voltage axis (where current equals 0) [40]. For Device C1, using  $g_m = 2.365$  pA/V and I = 33.4 pA at  $V_G = -58.3$  V, the intersect is calculated to give  $V_{TH} = -44.2$  V.

As the gate voltage approaches the threshold value, the Fermi level moves from its original position inside the gap towards the valence band edge. Assuming the semiconductor has a quadratic energy dispersion for electrons and holes (which is the case for Si), a linear relationship will exist between the gate voltage difference and the displacement of  $E_F$  within the gap. This predicts an exponential dependence on charge density with respect to  $V_G$  in the "subthreshold" regime [21].

We can quantify how effectively the gate can control the Fermi level position with a parameter called the subthreshold slope, labeled S. By plotting the transfer curve on a logarithmic scale in the subthreshold gate voltage range, we expect the curve to become a straight line, indicating that conductivity indeed has an exponential dependence on  $V_G$  in this regime (see Fig. 2.4(c)). The slope S of this line measures the gate control quality of the FET device [1, 41]. A lower value for S means a better gate control quality.

$$S = \left(\frac{\mathrm{d}\log I}{\mathrm{d}V_G}\right)^{-1} \tag{2.8}$$

Theoretically, in the absence of any impurity states or interface trap states, S becomes the lowest thermodynamically possible value of  $\ln 10k_BT/e$ , which numerically is equal to 60 mV/dec. However, any defects or oxide traps present in the FET device system will introduce additional states within the band gap that will require energy from the gate to occupy, reducing the effective gate control on channel conductivity. Measuring subthreshold slope becomes a method to measure the effects of defects and traps on conductivity in our SiNWs when S is found to be above 60 mV/dec [42]. Furthermore, the value of S in Eq. 2.8 should be insensitive to the exact choice of applied bias voltage. If S is found to depend strongly on  $V_B$ , then short channel effects (SCEs) are in play, hindering normal FET behavior [1].

For Device C1, our measurement of S from the slope of the curve in Fig. 2.4(c) gives 21.66 V/dec, a significantly larger value than 60 mV/dec. This means that our SiNW FET devices have very high defect and trap densities, greatly reducing gate control and confirming that our FET devices are far from conventional.

As the gate voltage goes beyond  $V_{TH}$ , the Fermi level enters the valence band and rapidly introduces holes in the channel. In the linear regime, the gate voltage is now simply "charging" the gate capacitor, giving us a very simple relation between gate-induced charge density  $p_G$  and the "overpower" voltage  $(V_{TH} - V_G)$  [34].

$$p_G = \frac{C_G(V_{TH} - V_G)}{LeA} \tag{2.9}$$

However, since the gate capacitor does not charge the entire cross-section A of the nanowire (only the bottom section, see section 2.4.1), this equation can only be used to estimate  $p_G$  [34]. For Device C1, at overpower voltage 14.1 V (corresponding to the point where  $g_m$  was measured), we estimate using Eq. 2.9 that  $p_G = 8.2 \times 10^{17}$  cm<sup>-3</sup>. Using Eq. 2.1, this allows us to quickly estimate that the density of electrons at this state is around a mere n = 170 cm<sup>-3</sup>. As this value is extremely lower than

p, this justifies our assumption in writing Eq. 2.3 that the electron current can be safely ignored in the linear regime. Using Eq. 2.5 and assuming  $\mu_{FET} = \mu$ , we can also quickly estimate the mean free path of the holes as l = 1.4 nm. As this value is significantly lower than L, this also justifies our use of the Fermi gas model to describe the diffusive transport of the hole current.

The gate-induced  $p_G$  is only one of the three sources of holes in the SiNW channel. The total hole density p is the sum of the initial density  $p_o$  before any gate voltage is applied (corresponding to the original Fermi level position), the hole density introduced by thermalizing traps  $p_{it}$  in the subthreshold regime and  $p_G$ .

$$p = p_o + p_{it} + p_G (2.10)$$

An estimate for  $p_o$  can be found using the intrinsic value  $n_i$  for Si and the additional holes from the impurity doping from the SiNW growth process. As p-type doping from gold atoms in Si creates a deep acceptor level near mid-gap, the maximum hole density that can be expected for  $p_o$  is around  $10^{12}$  cm<sup>-3</sup> (the minimum being the intrinsic value 1.18 x  $10^{10}$  cm<sup>-3</sup>). Further doping will come from surface traps in the subthreshold regime  $p_{it}$  (an estimate for this value would be difficult to produce) [43]. In any case,  $p_G$  can easily be much larger than the other two, which explains the jump in conductivity seen in the linear regime compared to the subthreshold regime. All three values needed in Eq. 2.10 are estimated, which makes the value of p completely unknown. It must be calculated using Eq. 2.3, which requires a precise measurement of both  $\sigma$  and  $\mu$ .

Obtaining accurate values for conductivity and mobility represents the greatest challenge that we had to surpass in this work. Not only were the measurements themselves very difficult (sub-pA currents were often found as we acquired data, creating low signal-to-noise ratios), but the analysis of the data from FET measurements on our SiNWs was greatly complicated due to the various consequences of having them undoped. Some of these obstacles have already been discussed, but the major problem came from the effects of the metal-semiconductor contacts formed when placing our source/drain electrodes on our undoped SiNWs. How we have modified the conventional FET model to account for these issues is the subject of the following section in this chapter.

#### 2.4.3 ON-state and OFF-state

A FET device has three basic modes of operation depending on the value of the gate voltage with respect to the threshold voltage. The "ON-state" is found where  $V_G$ surpasses  $V_{TH}$  and the device enters the linear regime. This state is characterized by high currents and good gate tunability (useful for applications if the device is used as a sensor). In contrast, the "OFF-state" is found where  $V_G$  is not sufficiently high enough to prevent the channel from being mostly depleted of free charge [44]. In this state, the current passing through the FET device is very low (sometimes called the "leak" current) and is almost insensitive to applied gate voltages. The "TH-state" is simply when the FET is operating at  $V_G = V_{TH}$ . Here the device has an asymmetric response to gate voltage changes and carries moderate current values.

In order to not simply guess the gate voltages required to operate our SiNW FETs and to give exact values for  $V_G$  at ON- and OFF-states, the following convention will be used in this work. The ON-state is defined at the exact overpower voltage required to reach the point where  $g_m$  is measured. By going to higher overpower values, transconductance will be lowered and will eventually drop back to near 0 values. The FET device would then leave the linear regime and enter the "saturation" region, which we must avoid in our study. For Device C1 (see Fig. 2.4), the ON-state would be found at  $V_G = -58.3$  V. The OFF-state is defined at the exact reverse overpower voltage point, meaning at the  $V_G$  value of the same voltage difference between the ON- and TH-states but on the opposite side of  $V_{TH}$ . For Device C1, as  $V_{TH}$  was calculated to be -44.2 V, this means that the OFF-state is defined at  $V_G = -30.1$  V.

As the purpose of a transistor in a circuit is to provide an ON/OFF switch by either letting the current pass through it or not, a figure-of-merit for a FET device is the ON/OFF ratio. Labeled simply as "ON/OFF", it is measured by comparing the current in the ON- and OFF-states,  $I_{ON}/I_{OFF}$  at a given bias voltage. Equivalently, the device resistance values at the ON- and OFF-states can also measure the ON/OFF ratio,  $R_{OFF}/R_{ON}$ . For Device C1, the ON/OFF ratio is found to be 14.9, a modest value.

Naturally, there are two methods to increase the ON/OFF ratio and improve the FET device's overall performance for a given semiconducting channel. The first is to increase the ON-state current by either increasing the bias voltage, increasing charge density by doping the channel, decreasing the channel length or increasing its diameter. Care must be taken, however, as doing any of these actions may incorporate new issues (e.g. shortening the channel may introduce SCEs) or not change the ON/OFF ratio at all (e.g. increasing the bias voltage may also increase the OFFstate current, doping the channel further may decrease mobility) [45]. The second method to improving ON/OFF ratios is to decrease the OFF-state current. This can be easily be achieved by reducing the effective cross-section carrying current flow (known as "pinching" the channel). As the diameter of the SiNW decreases, this will lead to reducing OFF-state current by removing leak paths often found in Si defect states [46]. This effect will be especially pronounced in our SiNWs with OSFs.

Finally, a device is called a "depletion-mode" FET if the device is in the ON-state without any gate voltages applied ( $V_G = 0$ ). It is called an "enhancement-mode" FET if the device is originally in the OFF-state. As a general rule, enhancementmode FETs are more often desired for applications, as the device is nominally OFF which reduces the power requirements to operate the transistor [27]. All of the FET devices made from our SiNWs are enhancement-mode FETs.

# 2.5 Metal-Semiconductor Contact

In order to be able to acquire FET measurements on our devices, metal contacts must be placed on both ends of our SiNWs, both to apply the bias voltage on the source electrode and to measure the current from the drain electrode. We have already discussed so far in this chapter the hole transport through the semiconducting channel, but we have yet to present the metal-semiconductor contact. Most of the fabrication and measurement challenges found in this work came from the contacts themselves, so an understanding of the transport physics at this interface is equally important.

In this section, we explain how metal-semiconductor contacts modify the energy levels of the holes inside the NW near the interface. As this will also modify charge density in the region near the contacts, these will affect device conduction by creating a new pair of parasitic resistances called the source and drain contact resistances. The section will end by presenting the parameter that best defines the contacts and characterizes their effects, the Schottky barrier.

# 2.5.1 Charge Injection Mechanism

The metal-semiconductor interface is one of the most challenging problems in device physics [47]. The reason comes from the several complications that arise from the structure around the contact region that makes predictions about the properties of the interface very difficult. These include new states in the semiconductor band gap due to its proximity to the metal interface, the amorphous oxide layer surrounding the NW sandwiched within the contacts, extra impurities adding trap states and surface roughness, just to name a few. It is very difficult and often impossible to fabricate two identical metal-semiconductor contacts, making each FET device unique. Even in seemingly perfectly similar SiNW FET devices (e.g. same channel parameter values for L, d,  $t_{ox}$ ), different contact properties between the set of devices are the reason behind the various experimental results obtained from their measurements [33]. It is of paramount importance that the contact effects on FET measurements be understood and removed from data analysis.

A first model for the structure of the contact region could be to study the simple interface between a very large metal (in the bulk state) in perfect electrical connection to a semiconducting NW. As a specific example, we take the gold thin film (assuming bulk Au properties) in contact with our SiNW as the interface of interest. Even if the Au only covers the top section of the SiNW, we define the section of the source/drain electrodes covering the SiNW and the entire nanowire volume under the metal thin film as the contact region of the FET device (see Fig. 2.5(a)).

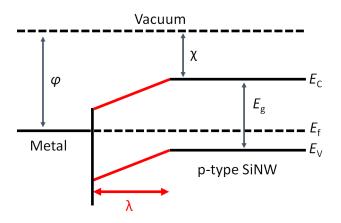

In addition to the value of the band gap  $E_g$  and the Fermi level  $E_F$ , an important parameter in a semiconductor's band structure is its electronegativity. Labeled  $\chi$ , its value is defined as the difference in energy between the vacuum level and the position of the conduction band edge. It represents the minimum energy required to create a free electron by extracting a single electron from the semiconducting material. For Si,  $\chi = 4.05$  eV [30].

For the metal, the only parameter needed is its work function. Labeled  $\phi$ , its value is defined as the difference in energy between the vacuum level and the position of the metal's Fermi level. Similarly to  $\chi$ , the work function represents the minimum energy required to create a free electron by extracting a single electron from the conducting material. For Au,  $\phi = 4.3$  eV [21].

Before making an electrical connection, when both materials are separated, the

metal's Fermi level and the semiconductor's Fermi level are not equal, in general. Using  $E_g = 1.12$  eV, and using a Fermi level 0.568 eV above the valence band edge, this makes the original position of the Fermi level of our p-type semiconductor to be 4.637 eV from the vacuum level (since  $\chi = 4.05$  eV). This value is greater than the metal's work function,  $\phi = 4.3$  eV, meaning that the Fermi level of the SiNW is below the Fermi level of the gold electrodes on a band diagram.

Once they are in contact, however, the value of  $E_F$  must be the same across the interface in the equilibrium state. Anderson's rule states that both materials must share the same vacuum level, making it possible to compare their Fermi level positions. In order to move the Fermi level, charge will be displaced through the metal-semiconductor interface. Since it is much more difficult to move the Fermi level of a metal in its bulk state than that of a semiconductor, the system will be modified such that the Fermi level of the SiNW is pushed up to match the metal's value for  $E_F$ . The higher energy holes in the valence band of the SiNW will be pushed into the metal where a much larger density of lower energy states are available. This will leave uncompensated electrons in the semiconductor, creating pairs of charges across the interface.

This process continues until the Fermi level is uniform in the entire contact region. The charge pairs at the interface will generate a dipole-like electric field in the SiNW, which will "bend" the semiconductor conduction and valence bands over a distance  $\lambda$ . The contact region extends into the SiNW over this length  $\lambda$ , after which the nanowire's characteristics become the same as those without contact effects (see sections 2.2 - 2.4) in the distance  $L - 2\lambda$  between both contacts. As holes were extracted from the semiconductor, a pair of depletion layers are formed in the SiNW of length  $\lambda$ , which will act as rectifiers (which we will discuss further in section 2.6).

The main consequence of band bending is the creation of an energy barrier formed at the metal-semiconductor interface. For holes to be injected into the SiNW from the electrode metal, they must have an energy larger than simply the difference between the metal's Fermi level and the valence band edge. This barrier will prevent current from easily passing through the contact region, acting as a series resistance to the FET device that can also be tuned by both the bias and gate voltages (see Fig. 2.5(b)-(c)).