Copyright

by

Yuxin Wang

2019

# The Thesis Committee for Yuxin Wang certifies that this is the approved version of the following Thesis:

# Extending Capability of Formal Tools: Applying Semiformal Verification on Large Design

APPROVED BY

SUPERVISING COMMITTEE:

Jacob A. Abraham, Supervisor

Andreas M. Gerstlauer

## Extending Capability of Formal Tools: Applying Semiformal Verification on Large Design

by

#### Yuxin Wang

#### **THESIS**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### MASTER OF SCIENCE IN ENGINEERING

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm May} \ 2019$

## Acknowledgments

I would like to thank my supervisor Prof. Jacob Abraham for providing me direction in this interesting domain of research and bringing me inspiration when I encountered difficulties. Also, I want to thank him for offering me the opportunity to be his teaching assistant, which helped me bolster my understanding of digital design.

I appreciate it very much that Dr. Jacob Chang, Mr. Clifford Wolf and Sharukh Shaikh provide kind help for me during my research. I also want to specially thank my parents and my boyfriend Zhengping Yu for their continuous love and support throughout my master study.

I would like to take this opportunity to specially thank Prof. Andreas Gerstlauer for taking out his valuable time to be the reader for my thesis. Extending Capability of Formal Tools: Applying

Semiformal Verification on Large Design

Yuxin Wang, M.S.E.

The University of Texas at Austin, 2019

Supervisor: Jacob A. Abraham

Simulation and formal verification (FV) are the two most commonly

used techniques for verifying a digital design described at the Register-Transfer

Level (RTL). Compared to simulation, formal verification shows an advantage

in terms of exhaustive design coverage. However, due to state-space explosion,

it is limited in size of designs that can be analyzed, and this capacity problem

remains a big issue for application in large designs, such as processors.

In this thesis, a waypoint-based semiformal verification (SFV) method

is proposed in order to extend formal tool capacity for large designs. Our algo-

rithm involves formal engines to explore traces to hit waypoints, reducing the

computation time and memory required to reach a desired state. In addition,

an automatic waypoint generation tool is developed. Criteria are developed to

identify important flip-flops in the design to generate the waypoints, based on

information from the synthesized netlist. A neural network is trained to score

vi

all the flip-flops in the target design. Based on the predicted scores, we set a threashold to select the critical flip-flops and then generate waypoint guides for RTL verification.

The process is first studied using a small FIFO example. Then an expandable end-to-end ISA verification framework designed around a RISC-V core is evaluated with the proposed SFV techniques. The results show that waypoint-based SFV and the automatic waypoint generation algorithm have great potential in RTL verification. SFV can save a substantial amount of the time and memory required to cover all important scenarios, compared to direct application of FV.

# **Table of Contents**

| Ackno   | wledgments                                           | $\mathbf{v}$ |

|---------|------------------------------------------------------|--------------|

| Abstra  | act                                                  | vi           |

| List of | Tables                                               | x            |

| List of | Figures                                              | xi           |

| Chapt   | er 1. Introduction                                   | 1            |

| 1.1     | Classic Verification Techniques                      | 1            |

| 1.2     | Verification Challenges in Modern Processors         | 4            |

| 1.3     | Semiformal Verification: Motivation and Related Work | 6            |

| 1.4     | Summary and Chapter Outline                          | 9            |

| Chapt   | er 2. Hybrid Semiformal Verification Methods         | 11           |

| 2.1     | Formal Verification Waypoints Definition             | 11           |

| 2.2     | Semiformal Technique Using Waypoints                 | 13           |

|         | 2.2.1 Finding Proper Waypoints                       | 14           |

|         | 2.2.2 Traversal Policy                               | 15           |

|         | 2.2.3 Waypoint Propagation Strategies                | 15           |

|         | 2.2.4 Algorithmic Waypoint-based SFV Flow            | 18           |

| 2.3     | A Toy Example: Synchronized FIFO                     | 21           |

| Chapt   | er 3. Automatic Generation of Guide Waypoints        | 29           |

| 3.1     | Introduction to Neural Networks                      | 29           |

| 3.2     | Why We Need Machine Generated Waypoints              | 31           |

| 3.3     | Automation Procedure                                 | 33           |

|         | 3.3.1 Extraction of Control Models                   | 33           |

|         | 3.3.2 Training Data Set Acquisition                  | 34           |

|         | 3.3.3 Finding the Critical Flip-flops               |       | . 37       |

|---------|-----------------------------------------------------|-------|------------|

|         | 3.3.4 Generating Guide Waypoints                    |       | . 39       |

|         | 3.3.5 Result Evaluation                             |       | . 43       |

| 3.4     | Other note: Coverage Metrics                        |       | . 48       |

| Chapte  | er 4. Experiments and Results                       |       | 50         |

| 4.1     | Application Guidelines                              |       | . 50       |

| 4.2     | RISC-V Verification Setup                           |       | . 51       |

| 4.3     | RISC-V Core: PicoRV32                               |       | . 54       |

|         | 4.3.1 Introduction to Experiment                    |       | . 54       |

|         | 4.3.2 Verification Ability Improvement              |       | . 56       |

| 4.4     | RISC-V Core: Rocket                                 |       | . 62       |

|         | 4.4.1 Introduction to Experiments                   |       | . 62       |

|         | 4.4.2 Initial Configuration Sequence                |       | . 64       |

|         | 4.4.3 Automatic Generated Waypoints                 |       | . 65       |

|         | 4.4.4 Notes for Temporary Results                   |       | . 66       |

| Chapte  | er 5. Conclusions and Future Work                   |       | 68         |

| Appen   | dices                                               |       | 71         |

| Appen   | dix A. Important Scripts Used in This Th            | nesis | 72         |

| A.1     | TCL Command to Run Jasper<br>Gold $\ .\ .\ .\ .\ .$ |       | . 72       |

| A.2     | Cadence Encounter Timing Analysis Script            |       | . 72       |

| A.3     | Other Codes                                         |       | . 74       |

| Appen   | dix B. Original Experiment Data                     |       | <b>7</b> 5 |

| B.1     | Original Data of PicoRV32 FV and SFV Experir        | ments | . 75       |

| B.2     | Neural Network Training Results                     |       | . 76       |

| B.3     | Automatic Waypoint Guide Report                     |       | . 90       |

| Appen   | dix C. Verilog source code                          |       | 95         |

| C.1     | Synchronized FIFO                                   |       | . 95       |

| Biblios | raphy                                               |       | 97         |

# List of Tables

| Table 2.1       | Interface of Synchronized-FIFO under verification              | 22 |

|-----------------|----------------------------------------------------------------|----|

| Table 2.2       | SVA properties checked with Synchronized-FIFO                  | 23 |

| Table 3.1       | Feature vectors of the data set                                | 35 |

| Table 3.2       | Design information for neural network training data set        | 36 |

| Table 3.3       | Neural network training parameters                             | 39 |

| Table 3.4       | Automatic generated waypoints guide                            | 45 |

| Table 3.5 ated  | Comparison between FV and SFV with automatic gener-waypoints   | 46 |

|                 | Assertions checked in formal verification on RISC-V intions    | 54 |

| Table 4.2       | CPI numbers for the individual instructions                    | 55 |

| Table 4.3       | Verification result of PicoRV32 AND instruction on server S $$ | 57 |

| Table B.1 tests | Original data collected for PICORV32 core FV and SFV           | 75 |

| Table B.2       | Neural network training result for synchronized FIFO .         | 76 |

| Table B.3       | Neural network training result for PicoRV32                    | 77 |

| Table B.4       | Neural network training result for Rocket Core                 | 80 |

# List of Figures

| Figure 1.1 fication  | Comparison between simulation-based and formal vering                                        | 2  |

|----------------------|----------------------------------------------------------------------------------------------|----|

| Figure 1.2           | Guided simulation using abstraction                                                          | 8  |

| Figure 2.1           | Multiple waypoints in formal model checking                                                  | 12 |

| Figure 2.2           | Dynamic simulation                                                                           | 17 |

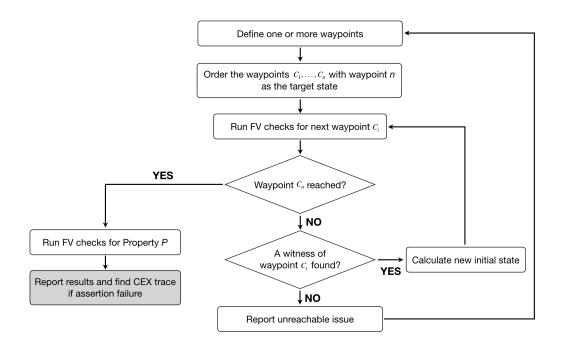

| Figure 2.3           | Algorithmic waypoints-based SFV flow                                                         | 19 |

| Figure 2.4           | Ideal runtime reduction with waypoints-based ${\rm SFV}$                                     | 21 |

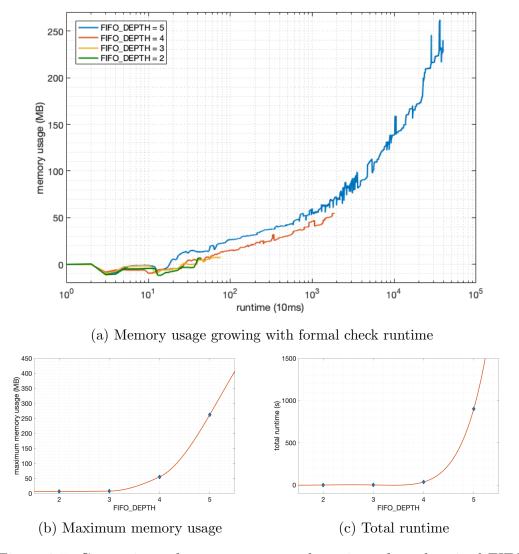

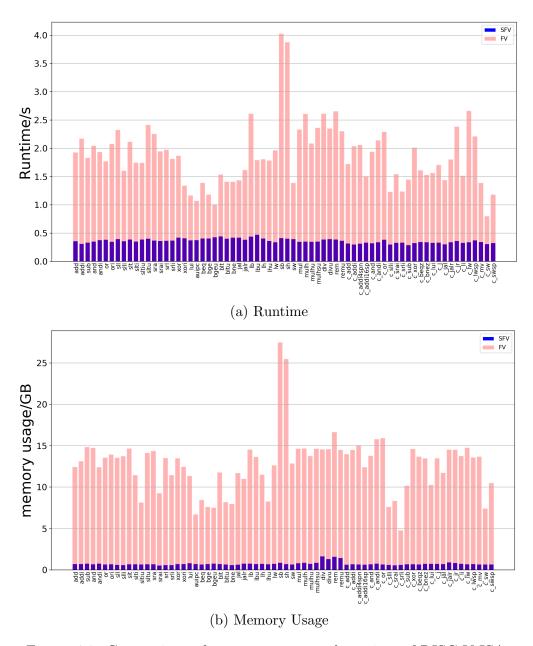

| Figure 2.5 nized 1   | Comparison of memory usage and runtime of synchro-FIFO with various FIFO_DEPTH               | 24 |

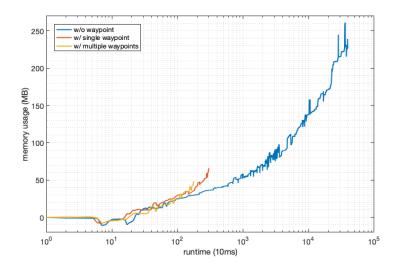

| Figure 2.6<br>FV, Sl | Comparison of memory consumption versus runtime among FV with single and multiple waypoints  | 26 |

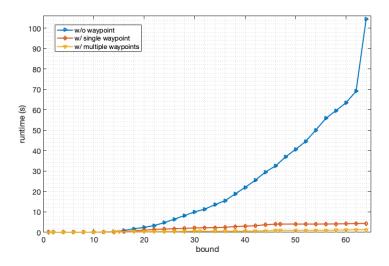

|                      | Comparison of runtime versus check bound among FV, with single and multiple waypoints        | 27 |

| Figure 2.8<br>FV, SI | Comparison of coverage percentage versus runtime among FV with single and multiple waypoints | 27 |

| Figure 3.1           | Neuron structure diagram with activation functions                                           | 30 |

| Figure 3.2           | Typical control path model                                                                   | 33 |

| Figure 3.3           | Algorithm structure of the neural network                                                    | 38 |

| Figure 3.4 predict   | Squared error between user-defined scores and machineted scores                              | 44 |

| Figure 3.5 selecte   | Runtime growth versus bound of FV, SFV with manually d, and automatic generated waypoints    | 47 |

| Figure 4.1           | RISC-V formal verification framework diagram                                                 | 53 |

| Figure 4.2<br>ISAs   | Comparison of memory usage and runtime of RISC-V                                             | 59 |

| Figure 4.3 parison   | Memory usage versus runtime of LW instruction com-                                           | 61 |

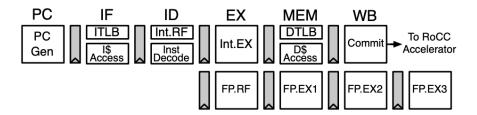

| Figure 4.4           | The Rocket core pipeline[5]                                                                  | 63 |

#### Chapter 1

#### Introduction

#### 1.1 Classic Verification Techniques

There is a desperate need for practical solutions to the problem of performing design verification using today's computing systems, since most modern digital designs are far too large for traditional tests to guarantee their correctness and safety. Two main approaches are applied in RTL verification: dynamic simulation and formal verification (FV) [2].

Simulation-based verification has been applied for a long time. This approach requires a testbench with manually designed or constrained random test vectors to propagate logic values through blocks [36]. It is acknowledged that the traditional simulation method offers the benefits of simplicity and scalability; however, it is impractical for simulation to keep up with the increasing design complexity [17], and its reliability depends on how comprehensive the stimuli are. For example, if the design under verification (DUV) state machine has 64 state variables, then the total time required to simulate vectors to cover all states will be nearly 600,000 years if each vector takes 1 ms to simulate.

Formal methods are increasingly applied in the verification of complex digital designs for their ability to detect subtle bugs [41]. The idea of formal

verification is derived from reasoning based on manipulation of formulas and logic, that is, the proof is mathematical instead of experimental [24]. Generally, the name formal can refer to many sub-topics, such as logic equivalence checking [38], model checking [9,13] (also known as functional formal analysis), and theorem proving [27]. In this thesis, we will only be dealing with formal methods using model checking.

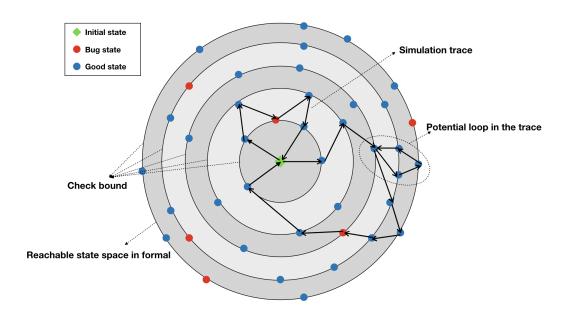

Figure 1.1: Comparison between simulation-based and formal verification

Formal model checking technique can verify Register-Transfer Level (RTL) functional correctness with a set of assertion properties without involving a testbench. Figure 1.1 shows the fundamental difference between how simulation-based verification and formal verification explore states, where each circle represents one transition step, or check bound, in formal analysis,

and the simulation trace is represented by the black arrows. Unlike simulation, where the inputs (random or targeted sequences) result in the target transitioning through different states, formal verification starts from a given initial state and analyzes target behavior under user-defined constraints to verify the assertions. Therefore it can improve verification quality by exposing corner case bugs or exhaustively proving the correctness of one property, enabling shorter design and verification time. Meanwhile, with the emergence of language standards such as SystemVerilog Assertions (SVA) to define properties, formal verification has lately become a mainstream verification method. Development of more efficient algorithms, as well as the performance improvement of CPU and memory units, also push formal tools to produce meaningful results in practical time frames.

Compared to simulation, formal techniques, such as model checking, are much more comprehensive in detecting corner case bugs because they can search for all reachable states in each step. However, formal does not scale well with large designs [17], which makes it still just one part of the solution to the massive industrial verification problems. This capacity issue is the biggest reason that prevents formal from directly replacing any simulation-based methodologies or tools. Being exhaustive, formal verification can easily run into state explosion, especially for the enormous state spaces of modern designs. In addition, it is difficult for verification engineers to evaluate the results when the formal tool cannot present determined outcomes before running out of memory or exceeding CPU time limits. These issues, which usually occur in

verification of large designs, require more effective and innovative techniques to extend the capability of formal engines while maintaining relative satisfying coverage.

#### 1.2 Verification Challenges in Modern Processors

The increasing complexity of hardware designs, especially modern processors, have been posing a lot more challenges in verification. The industry has been putting more and more resources into verification than design, yet still many projects with promising new features are dropped due to the inability to fully verify the functionality within a reasonable time period.

Despite decades of research, the exponential growth in the complexity of modern processor designs over the last decades has continued to bring huge challenges into the verification fields. There are many optimizations to improve the performance of these microprocessors such as pipelining, forwarding, branch prediction, out-of-order instruction, etc. [28]. Even with the same instruction set architecture (ISA), especially for the open source ones, such as RISC-V, vendors tend to have various implementations that focus on different aspects, such as high performance or low power consumption. All the optimizations and implementation diversities stated above have introduced extra corner cases for the design, which makes verification a critical task to guarantee system function correctness and safety.

The ultimate goal is to verify the correctness of each instruction that can cover all critical internal states of the design. The most common tests conducted for such a purpose is at the assembly level, where a sequence of instructions is fed to the core, and values of memory and registers are checked. However, all of these optimizations or different micro-architectures should not be visible to the programmer in general, which means that the overall instructions should be processed one at a time in the designated order in accordance with the ISA specifications [45]. In this case, such assembly level tests cannot locate the bugs precisely in RTL related to micro-architectures, but classic RTL verification requires a deep understanding of what internal signals in the DUV behaviors are considered as legal, which brings a lot of unnecessary work to verification teams to ensure the correctness of complex designs. This major requirement shows the importance of establishing a dependable verification method to perform an RTL end-to-end ISA verification for each design which includes all the micro-architecture behavior invisible to the programmer.

On one hand, traditional simulation-based verification requires a deep understanding of a particular implementation in order to generate the stimuli to reach those corner cases. Creating such testbench is not only hard and unreliable, but also expensive in terms of reusability, as the tests would be specifically designed for one micro-architecture [45]. Furthermore, the state space of modern processors is huge, especially for 64-bit machines; therefore it is impractical to obtain full coverage by so-called exhaustive tests. One purpose of this thesis is to come up with a verification method that is able to verify the correctness of the instruction operations with higher coverage and can also be applied to any third party implementations with relatively low

effort.

On the other hand, FV usually uses assertions to find violations of specification, which is suitable to describe correct behavior for the end-to-end approach. However, the formal engine has to go through nearly all the states in the design thus resulting in state explosion, which would overload the formal tool. Some corner case bugs for complex state machines can be very deep for formal techniques to catch. A better approach is to deal with the urgent need to solve the capacity issue in FV, which will be discussed in the next section.

There exist some tools that can perform automatic formal verification on the architectural or transaction level models such as FISACo in [39]. However, such tools still require human effort in defining informal specifications and the architecture models, which limits their application. In addition, the machine-generated properties are usually not human-readable, thus one completely depends on the soundness of the tools and it can be extremely difficult to debug if the properties themselves are buggy. In contrast, experienced verification engineers can write human-readable proofs and provide effective guidelines. Our intention is to achieve a balance between automation in the verification process and high-level user involvement.

# 1.3 Semiformal Verification: Motivation and Related Work

An integration of simulation with FV, generally referred to as semiformal verification (SFV) [1, 2, 17, 58], can have particularly preferable performance in situations where bugs are fairly deep and require thousands of cycles to execute. Semiformal verification combines the completeness of formal techniques and the capacity and ease-of-use of dynamic verification, which leverages FV in a resource-bounded approach, and thus is a key to scale FV to larger, more complex designs.

Two general semiformal techniques have been frequently investigated in the verification area. The first is referred to as augmenting simulation. In this category, dynamic simulation is first applied to reach certain intermediate state and then formal engines take over to exhaustively verify the remaining reachable states. However, formal search, in this case, would only be effective if it is triggered fairly close to the failure state. In order to relieve this limitation, some approaches of augmenting simulation include rarity-guided simulation [21] that ranks the states for later search iterations, or the automatically generated lighthouses (important intermediate states) [56] as guideposts towards the target state.

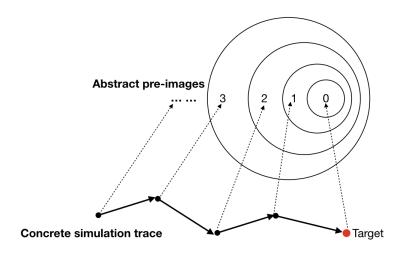

Another semiformal technique can be referred to as guided simulation. Abstraction plays a critical role in this type of methods. It is the preliminary step for formal engines to perform an exhaustive search, which partitions the reachable states into "rings" as shown in Figure 1.2 based on the depth from the target. These "rings" can be used to guide simulation towards the inner rings until it reaches the target states. However, the abstraction can sometimes be too coarse and the existence of mapping paths back to the concrete design must be taken into consideration to make sure its validity. To solve the dead-

Figure 1.2: Guided simulation using abstraction

end states in a coarse abstraction, many research efforts have been put into optimization of the abstraction methodology. One solution is to keep a record of multiples states and maintain a balance between greed and relaxation [16]. Involving domain knowledge can also be effective [15], but it requires extra efforts from engineers to manually abstract the designs. Data mining has also been investigated for example in [43] but few applications were demonstrated on industrial designs and verification testbenches. Meanwhile, localization can be used to automatically refine the abstraction [18] but the abstracted models tend to grow very quickly. One promising way to solve this explosion issue is to abstract away the data-path signals to retain only control-path registers [50, 58]. Since most bugs are bundled with control issues, verification processes that focus on exploring control states increase the likelihood to find deep bugs.

Semiformal verification can be very useful in verifying industry designs

due to its ability to expand the bug hunting capability of FV to detect deeper state failures in large designs. Although SFV is not as exhaustive as FV, it does achieve much larger coverage than simulation. In the next chapter, we will elaborate on the methodology explored in this thesis to apply semiformal techniques using waypoints as intermediate guides towards the target in complex designs.

#### 1.4 Summary and Chapter Outline

This thesis studies an SFV approach that manages to alleviate the capacity issue of formal verification for complex modern designs. Unlike some previous research that only use simple RTL modules as study cases [2], this thesis investigated an end-to-end verification framework using RISC-V cores as targets. A waypoint-based SFV algorithm with no testbench required is proposed where waypoints are important intermediate states that are selected based on specific criteria. They will serve as the "lighthouses" in the formal verification process in order to shorten the proof or counterexample exploration time, thus expanding the capacity of formal tools. The main contribution of this work is to design a new automatic waypoint generation tool using machine learning techniques, which is useful for complex DUVs as it can serve as a complement to manual waypoint selection. In addition, the data set built for automatic waypoint generation part is open source, which identifies the importance of the flip-flops based on synthesized netlist information. Both manual and automatic methods will be evaluated specifically in this work for

different design cases.

This chapter gave a brief introduction to related work on semiformal verification. The rest of this thesis is structured as follows. Chapter 2 illustrates the semiformal techniques adopted and the algorithm studied in this work using waypoint-based SFV methods. Chapter 3 introduces an automatic waypoint generation tool designed by applying neural networks to analyze the extracted control models. The RISC-V study cases and the corresponding experimental results are presented in Chapter 4. Conclusions and future work follow in Chapter 5.

#### Chapter 2

### Hybrid Semiformal Verification Methods

This chapter elaborates on the waypoint-based SFV technique that is adopted and modified in this thesis to extend the formal tool capability.

#### 2.1 Formal Verification Waypoints Definition

It has been illustrated in the previous chapter that formal verification is likely to run into capacity issues when the target state is too deep to reach within the limited amount of time and memory resources available. Corner cases usually require difficult scenarios that can only cover them when part of the design has reached a certain state, which can take a lot of cycles from the initial state. For example, in microprocessors, many interesting cases are likely to happen after the cache becomes active, and perhaps full, but it takes many cycles to write the configuration registers to enable the specific bits and many cycles to generate the memory address sequences to fill the cache.

In conventional FV, the particular state from which formal model checking starts is typically the state where the reset signal drops to be inactive. In the aforementioned example, in order to hit the interesting scenarios, the formal tool has to go through the initial sequence and then enable and fill the cache. To shorten the number of cycles necessary to get to our interesting states, we could define the intermediate state where configuration is complete as the start state for model checking. These hypothesized intermediate states are defined as "waypoints" or "lighthouses", serving as new start states, from which formal tool can search deeper until reaching the target state.

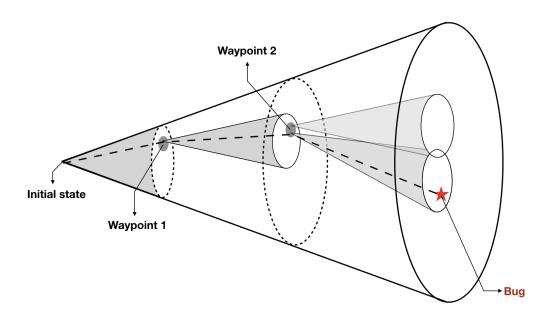

Figure 2.1: Multiple waypoints in formal model checking

Figure 2.1 illustrates the general idea of how waypoints serve as the intermediate states in SFV to find a bug. Instead of directly checking through all states for the assertions, the formal tool will only hit all or a subset of the pre-selected waypoints based on some specific search algorithms. In this scenario, two waypoints reached using simulation are used for the formal tool to re-start in order to hit the final bug state. When a certain waypoint, such

as waypoint 2 in Figure 2.1, is reasonably close to the assertion failure state, it would be much easier for the tool to hit that failure if it starts from that waypoint. Without these intermediate states, the state explosion in formal verification may make our targets unreachable. By doing so, we are able to reduce the Cone of Influence (COI) at each step. Even in the cases where no bug exists, the proof time for properties are expected to be largely reduced with the premise that these multiple COIs at each waypoint can keep appropriate coverage.

One thing requiring our attention is that the reachable state set depends on the initial state from where model checking starts. Therefore, it is important to ensure that the selected waypoints are traceable from the reset state, otherwise the SFV result could run into false negatives.

#### 2.2 Semiformal Technique Using Waypoints

The fundamental idea of applying waypoints is to use the witnesses of such state as a guide that can lead the formal proof towards the deep target state. A straightforward example of using waypoints would be a first-in-first-out queue (FIFO): if our check target is FIFO overflow, the waypoints can be set to "FIFO is 3/4 full". Or even, multiple waypoints can be selected to guide the formal tool towards the target, i.e. "FIFO is 1/4, 1/2, 3/4 full" respectively. What we have to feed the formal tool is the correct input sequence that both obeys the design specification and is able to guide the DUV towards all the waypoints.

#### 2.2.1 Finding Proper Waypoints

Waypoints can be either explicitly selected by the design or verification engineers, or automatically generated by machines using specific algorithms, for example, based on proximity metrics. From the view of the designer, user-defined waypoints are more effective and often comes naturally. It is suggested that more users tend to select waypoints manually [2].

Meanwhile, the advantage of machine-generated waypoints lies in the fact that they do not require human intervention and detailed understanding of the design specification. One intuitive method is generate waypoints that makes the pre-condition of assert properties to be true. For example, if the property looks like  $cond \mid => seq \#\#1 \ res$ , the automatically generated waypoints would be when the antecedent cond is true, or more strictly with seq being true in the successive cycle. Other machine generated methods may include, for instance, selecting waypoints that are at a specified distance from the target states from an abstract design, or based on an architecture model of the design. The main disadvantage of the automatically generated waypoints is that they are usually less efficient than their user-defined counterparts. What's more, the generated waypoints are usually large in number, which could result in expensive computation effort in ordering and reaching each waypoint, making the later process more complicated or even unfeasible. This would unnecessarily increase the verification time and effort.

One can also combine the two, conducting a mixed strategy: some explicit waypoints can be provided by user guidance whereas the others are generated by algorithms.

#### 2.2.2 Traversal Policy

The traversal policy of the waypoints also remains to be an interesting topic for discussion. It defines the order in which the waypoints are witnessed in the verification flow, which has a large influence on when the failure state of the assertion will be hit.

The most straightforward policy could traverse the waypoints in a specific order. More sophisticated policies usually involve regression in order to hit the closest waypoint to the current state or failure state. In the latter category policy, the search engine will need to continuously check whether current traverse meets the requirement for a certain period, otherwise, it will restart from the previous point and insert the latter path into a "blacklist" to avoid repeating the same path.

#### 2.2.3 Waypoint Propagation Strategies

The major categories of propagation strategies for reaching new waypoints are simulation-based and FV-based propagation. The former can be further divided into random simulation and dynamic simulation. This section will elaborate and compare the three strategies in detail.

In the random simulation policy, randomly generated stimuli are fed to DUV in order to hit the next waypoints [31]. This method is popular because it does not require the user to create simulation testbenches manually. The

external signals of the DUV are constrained with System Verilog assumptions for formal checks, and the randomly generated stimuli should respect all the assumptions. It is critical to make the correct assumptions to constrain the behavior in order to avoid false negatives. Another issue is that this policy requires consistent models in simulation and formal environments to integrate the two successfully. However, this is usually not the case. In order to improve the verification efficiency, models used in simulation and formal engines are likely to be significantly different. For instance, FV tools tend to replace parts of the logic with abstractions to fit their capacity. These difficult issues, especially in complex designs, limits the application of the random simulation policy in our case.

In the dynamic simulation policy, both the simulation environment and the simulation testbench should be involved alongside the formal verification environment. The simulation testbench needs to be run first, and then way-points are selected on the simulation traces manually or automatically based on specific rules. Within the set of selected waypoints, each one serves as a new initial state for formal verification, from which formal engine starts to search the violation of assertions. The idea of the dynamic simulation policy is shown in Figure 2.2. From the coverage point of view, the simulation trace looks "thicker", which suggests better coverage than using classic simulation methods alone. The advantage of the dynamic simulation policy is that it can model practical scenarios by designed test vectors. However, one problem remains that the FV checks are always in proximity of simulation traces,

which are generally very shallow explorations. In addition, the consistent model requirement mentioned in the context of the random simulation policy also applies here. These issues make dynamic simulation policy infeasible for verifying complex hardware designs.

Figure 2.2: Dynamic simulation

In the FV-based propagation policy, waypoints are selected manually or automatically before starting the verification flow. Those waypoints are then treated as assertions. For example, "FIFO being 3/4 full" will be represented in SVA as an assertion of "FIFO is never 3/4 full". The FV engines will search exhaustively within bounded steps to find a violation of the waypoints. The counterexample found is called a "waypoint witness", which corresponds

to the violation trace that can be used as input sequence to reach this witness point later. The biggest advantage of the FV-based propagation policy is that the verification environment required is exactly the same as that of classical FV except for the multiple re-runs based on the waypoints specification [2]. Therefore, there is no issue with model consistency, and no limitation on specified assumptions. The disadvantage for this policy is that the adjacent waypoints should be relatively close to each other, otherwise it will raise problems due to capacity issues of formal engines. There are commercial tools [44] already implemented certain engines to accelerate the proof by dynamically using proved assertions as waypoints for other property checks.

#### 2.2.4 Algorithmic Waypoint-based SFV Flow

As aforementioned, one can either automate the waypoint search or use manually selected waypoints. The algorithm we will discuss in this section is based on high-level directions provided by users, but it also works for automatic process by simply modifying the first waypoint selection step. This guidance assists the SFV search towards the desired state by encoding the waypoints with SVA as either cover or assert properties (in our case, we use assertions). After discussing the algorithm, we are going to elaborate on its effectiveness using a synchronous FIFO as an example in the next section.

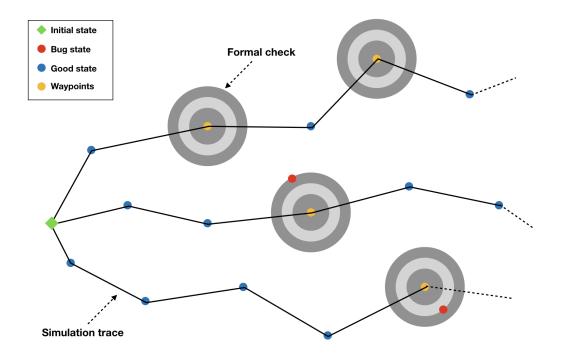

The outline flow chart of the SFV algorithm is presented in Figure 2.3. The sources of waypoints are the fundamental preconditions for the SFV flow. Given a set of waypoints  $C_1, C_2, ..., C_n$  and the target property P we

Figure 2.3: Algorithmic waypoints-based SFV flow

plan to verify, the manual waypoint traversal policy will be applied. All waypoints should be pre-ordered in sequence before starting witness checks. For each waypoint  $C_i$ , the formal engine will perform a bounded model check and search for a witness of this waypoint using a corresponding assertion  $A_i$ . An assertion "failure", in this case, should be treated as a successful witness, and the counterexample trace is generated to serve as preliminaries for calculating the new arbitrary starting state for the next run. Intermediate new initial state calculation is a critical step in this algorithm because it must satisfy all the constraints for the system, otherwise, we could end up having false failures that are unreachable or not able to hit the corner case bugs. To make sure the

new initial state is valid and compatible with the DUV, the counterexample trace is saved after each run to serve as the next input sequence to lead the design to the previously checked waypoint. Since the first counterexample trace is generated from the reset initial state, it is guaranteed that  $C_i$  is reachable if counterexamples are found. This input sequence is iteratively built upon successive waypoints witnesses, ensuring that all waypoints including the final target state are reachable from the original reset state. This algorithm rules out the possibility of bogus witnesses and counterexamples.

If a certain waypoint cannot be reached within a bounded time, the unreachability issue should be reported, and the waypoints will be re-ordered or re-selected. It is also possible to only roll back one step, using heuristic methods to specify the new waypoint. These issues will not be included in the discussion of this work but are worth studying.

The search steps are repeated as the subsequent waypoints to guide the FV engine towards deeper design behaviors. When the last waypoint  $C_n$ , also the target state condition, is reached, we run FV checks for the target property P and report the result.

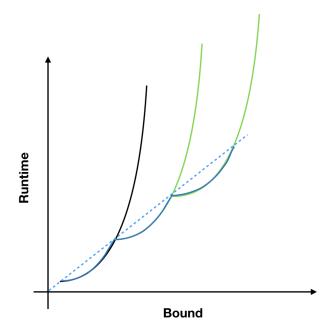

Another thing that needs to be mentioned here is that multiple threads running in parallel would result in better performance in the search. In addition, depending on how deep the target state is, single or multiple waypoints can be selected to guide the formal check to reach states that traditional FV can never reach. As shown in Figure 2.4, the black curve shows the runtime increase versus check bound for isolated FV, while the blue curve models the

Figure 2.4: Ideal runtime reduction with waypoints-based SFV

performance of waypoint-based SFV. It is clear that SFV runtime is growing linearly, while FV runtime increases exponentially, which indicates that using waypoints can greatly improve the capacity of the formal engines.

#### 2.3 A Toy Example: Synchronized FIFO

A simple synchronized First-in-first-out (FIFO) module (source code in Appendix C.1) is introduced here to verify the concepts elaborated above. The DUV interface is presented in Table 2.1, where FIFO\_DEPTH will be gradually increased in order to touch the boundary of FV capacity in our specific verification environment: running Cadence JasperGold on a server

with four Intel E5-2690 CPUs and a memory size of 8GB. In this example, Jasper Engine, Hp, Ht are used for coverage checks and Engines N, B for assertion checks.

Table 2.1: Interface of Synchronized-FIFO under verification

| Name  | Type      | Length      | Description                           |

|-------|-----------|-------------|---------------------------------------|

| clock | input     | 1           | system clock                          |

| reset | input     | 1           | high active asynchronize reset        |

| wr    | input     | 1           | write enable, rising edge active      |

| rd    | input     | 1           | read enable, rising edge active       |

| empty | output    | 1           | high active FIFO empty flag           |

| full  | output    | 1           | high active FIFO full flag            |

| din   | input     | DATA_       | data for write                        |

|       |           | WIDTH       |                                       |

| dout  | output    | $DATA_{-}$  | data for read                         |

|       |           | WIDTH       |                                       |

| DATA_ | parameter | any integer | the width data stored in FIFO         |

| WIDTH |           |             |                                       |

| FIFO_ | parameter | any integer | $2^{FIFO\_DEPTH}$ being the number of |

| DEPTH |           |             | data can fit in FIFO                  |

To make the comparison clearer, our experiments are conducted with different values of FIFO\_DEPTH and waypoint selection. Each experimental group only has one variable different from the control group. Note that although all other tasks are killed before the tests to make sure the amount of resources available is relatively stable, it is possible some resources will be occupied by other users from time to time. In order to generate results with more accuracy, multiple tests (> 3) are conducted and the results presented are the averages from these runs.

Table 2.2: SVA properties checked with Synchronized-FIFO

| Name             | Type   | Description                                      |

|------------------|--------|--------------------------------------------------|

| ck_empty_correct | assert | check the correctness of condition for empty     |

|                  |        | flag being active                                |

| ck_full_correct  | assert | check the correctness of condition for full flag |

|                  |        | being active                                     |

| ck_empty_once    | cover  | cover the case that empty flag is raised at      |

|                  |        | least once                                       |

| ck_full_once     | cover  | cover the case that full flag is raised at least |

|                  |        | once                                             |

| ck_empty_to_full | cover  | cover the case that empty flag is raised and     |

|                  |        | then full flag is raised after certain period    |

| ck_full_to_empty | cover  | cover the case that full flag is raised and then |

|                  |        | empty flag is raised after certain period        |

| ck_wr_num        | cover  | check whether write operations are executed      |

|                  |        | from zero up to an upper bound (set to be        |

|                  |        | three times more than the FIFO_DEPTH)            |

| ck_rd_num        | cover  | check whether read operations are executed       |

|                  |        | from zero up to an upper bound (set to be        |

|                  |        | three times more than the FIFO_DEPTH)            |

| ck_all_used      | cover  | check whether all the positions in FIFO are      |

|                  |        | used at least once                               |

The assert and cover properties included in the evaluation of this experiment are shown in Table 2.2, where all data are raw without post-processing. Since our goal for this test is to prove the concept that waypoints can guide large designs to reach deeper states, coverage for each spot in the FIFO is the primary check on which we are focusing. In addition, assertions for correct "full" and "empty" behaviors are also included. A list of properties written for this experiment is presented in Table 2.2, the implementation of which uses

auxiliary code to ensure the efficiency of SVA in the formal engine.

Figure 2.5: Comparison of memory usage and runtime of synchronized FIFO with various FIFO\_DEPTH  $\,$

First of all, in order to illustrate the FV capacity issue more clearly, Figure 2.5 presents the fundamental idea that both memory consumption and

runtime required for FV grows exponentially as FIFO\_DEPTH increases. One bit added to FIFO\_DEPTH shows that the number of data fit in the FIFO doubles. In the first test, all properties listed in Table 2.2 are enabled. When the size is relatively small, a formal tool can cover all properties very fast. However, if the size keeps increasing, the resources needed for full coverage are going to explode very quickly. As a matter of fact, simply increasing the FIFO\_DEPTH to 8 will result in a large number of non-deterministic cover points: our experiment shows that after a 24 hour TIMEOUT limit, only 102 out of total 256 spots in the FIFO are covered with approximately 6GB maximum memory required for the computation.

Since this example is to give the readers a general idea of how waypoint-based SFV can effectively extend the FV tool capability, the experimental group will use a medium size (FIFO\_DEPTH = 5) FIFO as our DUV. We only focus on pushing the FIFO to the full status because the FV tool will find the shortest path automatically for each property and those properties listed in Table 2.2 do not always share the same effective waypoints. This way, we only need to check  $ck\_all\_used$  and  $ck\_full\_once$  thereby simplifying the procedure to generate input sequence to hit the waypoints.

The result is presented in Figure 2.6 - 2.8. Three conditions are tested for evaluation.

- 1. Classic FV without waypoints;

- 2. SFV with single waypoint close to target state;

Figure 2.6: Comparison of memory consumption versus runtime among FV, SFV with single and multiple waypoints

### 3. SFV with multiple waypoints spread out in the design.

To validate the queue logic in stressed "full" state, waypoints are selected manually, with "3/4 full" for case 2 and "1/4 full", "1/2 full", "3/4 full" for case 3.

To clarify, the data collected includes both the process to hit the waypoints and the subsequent runs using the input sequence to cover the rest

states from there. It is clear that using waypoint-based SFV can reduce the

memory consumption enormously, as well as the check time for each step with

the FV tool going deeper. Meanwhile, the cover properties are proved to be

covered much faster using SFV than classic FV. It can also be concluded that

the deeper the FV tool goes, the longer the time it needs to complete the current check. This feature implies that our waypoint-based SFV methods can

Figure 2.7: Comparison of runtime versus check bound among FV, SFV with single and multiple waypoints

Figure 2.8: Comparison of coverage percentage versus runtime among FV, SFV with single and multiple waypoints

be especially beneficial in very large designs.

Apart from the benefits of using waypoints, it can be seen from Figure 2.6 – 2.8 that multiple waypoints can result in faster check and lower memory consumption to cover all states. However, this improvement from single waypoint to multiple ones is not as fruitful as "from 0 to 1". Considering the fact that multiple waypoint SFV requires much more effort from the user to define the intermediate states and find the correct input sequences, it is probably more effective to only involve a single waypoint if it works with the target design, whereas multiple waypoints can be applied to extremely large state machines to exploit the benefits.

Now we can draw a conclusion that waypoint-guided SFV can largely increase the capacity of the formal tools in our toy example. Even though it is a very simple FIFO module, the capacity issue easily emerges with reasonably increased FIFO depth. Considering the common designs in real applications we will be dealing with are much larger, this issue will be a severe obstacle for applying formal verification to achieve an exhaustive check. Therefore, the waypoint-guided method can be very promising in terms of its considerable coverage and capacity. In the next chapter, we will discuss the implementation of machine learning techniques to generate guidance for waypoints to assist in situations where it is difficult to define them with manageable human effort.

# Chapter 3

# **Automatic Generation of Guide Waypoints**

#### 3.1 Introduction to Neural Networks

Neural networks have been the research hot-spots in the field of artificial intelligence since the 1980s. A neural network abstracts the neural network in the human brain from the perspective of information processing, establishes a simple model, and can be used to generate different networks according to different connection methods. It has been proved that a neural network can represent arbitrary linear or non-linear functions [35], which is usually an approximation of a certain algorithm or function in nature. In the past ten years, many research efforts have been put into artificial neural networks. Neural networks have successfully solved many practical problems in the fields of pattern recognition, intelligent robots, computer vision, speech processing, etc., that are difficult for traditional algorithms to resolve [29].

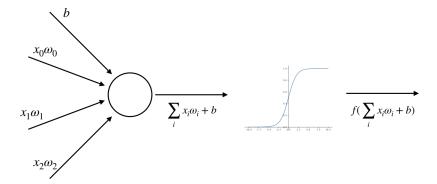

The network consists of a large number of nodes (or neurons) that are massively interconnected [49]. Each node represents a specific output function called an excitation function. A weight is assigned to each connection between every two nodes to represent the connection strength. The output of the neuron depends on the input variables, the weight value, and the excitation

Figure 3.1: Neuron structure diagram with activation functions

function. In addition, the output of the neural network is also affected by the connection pattern of the network [49].

In the neural network, the neurons in each layer are associated with functions generally referred to as "activation functions", which decide whether this neuron will be fired or activated [48]. Figure 3.1 shows the neural network structure with each neuron associated with the corresponding activation function, where x is the input vector and  $\omega$  is the weight vector from other neurons. The connection of a typical neural network will be illustrated in later section. Note that the activation functions used in this thesis are non-linear, which helps the de-linearization process of transformation in each neuron.

The neural network can be trained to learn the weight matrix that controls how variables propagate through the neurons. The optimization goal of the training is to make the prediction values as close as possible to the true value, which can be evaluated by loss function. In a regression problem, the loss function is usually measured by mean squared error (MSE), which is the average value of the sum of the squared errors between the predicted values and the true values [22].

Gradient descent (GD) is a common neural network optimization algorithm. By calculating the gradient, the parameters in the network move towards the negative direction of the gradient, so that the loss function is able to reach the minimum value locally. However, traditional GD needs to minimize the loss function on all training data. When the neural network needs to train a huge data set, the amount of computation required is very large. A compromise is to calculate the gradient of the loss function with only a subset of all the training data each time. This small amount of data is usually called a "batch", so this partition calculation method is usually referred to as batch gradient descent (BGD) [46]. BGD can greatly reduce the training time without affecting the convergence result, thus has become the mainstream to optimize parameters.

The target of our training is to minimize MSE by optimizing parameters in each layer using BGD in order to move the training results closer towards the true values.

## 3.2 Why We Need Machine Generated Waypoints

Chapter 2 presented a waypoint-based SFV algorithm to extend the capacity of formal verification of microprocessors. Despite many advantages of high-level user-selected waypoints mentioned above, it is necessary to in-

vestigate machine generated ones due to the growing number of large complex designs which are difficult to analyze by verification engineers without design details. In addition, many high-level hardware description languages, such as Chisel [7] are becoming more and more popular. In such designs, low level RTL design languages, i.e., Verilog or VHDL, are given up in exchange for a more convenient and better-structured design methodology. Therefore, it is impossible to apply high-level waypoint selection on large designs, especially those generated from higher level languages with machine-generated names for internal signals.

It is difficult to find an obvious relationship between the information that we can get from Verilog source code and whether this state is critical to be our guide waypoints. As introduced in the previous section, neural networks can extract hidden features in higher dimensions, thereby being more suitable for solving problems with hard-to-describe relationship between features and results like this.

In order to provide guidance of waypoint selection in such situations, a tool based on combined Python and Tcl is implemented to perform the automatic generation of the critical flip-flops. These critical flip-flops are then taken as guides for corresponding target states in the verification plans. This will involve a Verilog syntax analyzer and machine learning techniques. The detailed algorithm will be discussed in detail in the later sections.

## 3.3 Automation Procedure

### 3.3.1 Extraction of Control Models

Control signals are usually dominant in system behavior. In addition, control logic designs are often built around finite state machines (FSMs), in which some of the states are "idle states" that keep waiting for certain trigger signals, causing the design to be very deep and complex. Therefore, extracting control models can be the core step to solve the reachability problems in complex design verification. Meanwhile, those control signals can help to narrow down the target design size, facilitating system analysis by formal tools.

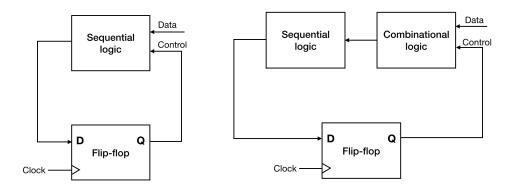

Two simple models [25, 50] shown in Figure 3.2 are elaborated here to assist the heuristic algorithm in order to make a decisions on whether a signal belongs to the control set or the data set.

- (a) Pure sequential logic

- (b) Mixed combinational and sequential logic

Figure 3.2: Typical control path model

We first consider the Verilog module in Figure 3.2a, where some flip-

flops would store their own history values, whereas, for others, their current value is computed every cycle without directly referring to their previous states. The former will be referred to as critical state registers and the latter as data registers. Usually, pure sequential logic corresponds to "always" blocks with signals sensitive to the system clock in the RTL code.

Another common situation would be the case shown in Figure 3.2b, where the output value of the flip-flop affects the sequential logic indirectly by going through combinational logic first. In this case, we need to continue exploring the assignment values in combinational logic until we reach a clocking event to determine whether this flip-flop is within the critical control flow or not.

## 3.3.2 Training Data Set Acquisition

In order to acquire data that are related to information in the control model, we need information from the synthesized netlist, which can be found, for example, using Cadence RTL Compiler (RC). This tool can perform generic synthesis and provide timing path and connection information for inputs, outputs and registers for the design system regardless of how they are implemented in the modules. In this work, only internal flip-flops are analyzed since the interface inputs and outputs usually have clear definitions based on the design specification, thus being easy to figure out whether they are critical control signals.

There are nine features for each flip-flop we obtain from the tool as

shown in Table 3.1. Some features are extracted directly from the RC tool while the others have been processed with simple arithmetic to get values in proportion.

Table 3.1: Feature vectors of the data set

| Notation | Description                                                      |  |  |

|----------|------------------------------------------------------------------|--|--|

| Rin      | The rate of input ports connected to the flip-flop over the      |  |  |

|          | total number of input ports                                      |  |  |

| Rout     | The rate of output ports connected to the flip-flop over the     |  |  |

|          | total number of output ports                                     |  |  |

| >> R     | The number of pins, ports or cells that exist in the fanin cone  |  |  |

|          | of the specified flip-flop (must be timing start points)         |  |  |

| R <<     | The number of pins, ports or cells that exist in the fanout      |  |  |

|          | cone of the specified flip-flop (must be timing end points)      |  |  |

| >> Rv    | The number of all pins, ports or cells that exist in the fanin   |  |  |

|          | cone of the specified flip-flop                                  |  |  |

| Rv <<    | The number of all pins, ports or cells that exist in the fanout  |  |  |

|          | cone of the specified flip-flop                                  |  |  |

| Loop     | Whether the specified flip-flop (or a group of flip-flops serves |  |  |

|          | different bits of the same signal) affect its own value in the   |  |  |

|          | subsequent cycle                                                 |  |  |

| Len      | The number of bits for specified signal (two-dimensional mem-    |  |  |

|          | ory storage will only be reduced to one-dimensional signal)      |  |  |

| Hier     | specify the level of submodule, with 0 being the top module      |  |  |

After data acquisition, the next step is classifying flip-flops to make up the training set. Although we would love to have two clearly distinguished categories for the signals, it is sometimes hard to completely distinguish between control and data signals. An example would be the instructions fetched in microprocessors: on one hand, they are data from memory or cache, on the other hand, they decide how the following pipeline stages work, which is more like control signal functions. Therefore, we will label each flip-flop in the training set with a score between 0 and 1 instead of directly classifying them as critical or non-critical. The continuous score is based on the control model illustrated in the previous section, but real situations are much more complex so we also involve some heuristics based on the actual behavior of the design.

Table 3.2: Design information for neural network training data set

| Design name                    | Number of FFs |

|--------------------------------|---------------|

| a25_write_back                 | 44            |

| ahb2wb                         | 84            |

| alu_with_selected_input_output | 83            |

| arbiter                        | 4             |

| asynchronized_spi              | 62            |

| axis_master                    | 15            |

| axis_arb_mux_4                 | 37            |

| axis_slave                     | 5             |

| axis_switch_4                  | 184           |

| SSP_fifo                       | 53            |

| ftdi_wb_bridge                 | 145           |

| hpdmc                          | 216           |

| i2c_controller                 | 159           |

| i2c_master                     | 150           |

| jtag                           | 70            |

| lock                           | 3             |

| o8_controller                  | 53            |

| reed_solomon_decoder           | 9228          |

| sdc_fifo                       | 771           |

| sequence_detector              | 3             |

| SSP                            | 134           |

| wishbone                       | 72            |

To gather sufficient data for training, feature extraction is performed on 22 designs, the number of flip-flops of which is listed in Table 3.2. They are either from https://opencores.org or implemented by the author; all the designs have been uploaded to the GitHub repository mentioned in Appendix A.3. The script used with the RC tool is given in Appendix A.2.

### 3.3.3 Finding the Critical Flip-flops

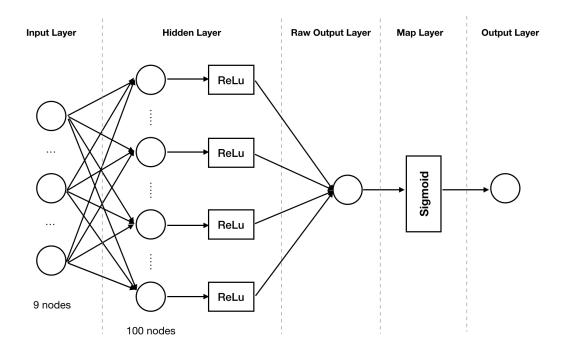

According to the aforementioned fundamental ideas, the neural network constructed for waypoint generation is illustrated in Figure 3.3. The details of each layer are as follows.

- Input layer: there are 9 nodes representing 9 features illustrated in section 3.3.2

- Hidden layer: full connection is implemented to connect the hidden layer

with input layer nodes. Only single layer is used with 100 nodes. This

can be extended to get more comprehensive training result. We choose

the most commmonly used ReLu function to be our excitation function

to perform de-linearization task.

- Raw output layer: full connection is implemented to connect the hidden layer with raw output layer. There is only one node in the raw output layer, representing the raw score from the neural network.

- Map layer: using the Sigmoid function to map the raw score  $(-\infty, +\infty)$  to the (0,1) distribution.

• Output layer: final score.

Figure 3.3: Algorithm structure of the neural network

In the training process of the model, MSE is used as the loss function, and the BGD algorithm is applied as the parameter optimization method. The equation for MSE is given in Eq.3.1, where N is the sample number in one batch,  $y_i$  is the true value, and  $\hat{y}$  is the predicted value from the neural network. The specific parameters after tuning are presented in Table 3.3. Note that the regularization coefficient is set to zero because the results imply there is no over-fitting problem. In the future, more data needs to be collected to expand the data set and further reduce the loss function.

$$MSE(y) = \frac{1}{N} \sum_{i=1}^{n} (y_i - \hat{y}_i)^2$$

(3.1)

Table 3.3: Neural network training parameters

| Parameter                       | Value |

|---------------------------------|-------|

| Batch                           | 100   |

| Base Learning Rate              | 0.8   |

| Learning Rate Attenuation       | 0.99  |

| Regularization Coefficient      | 0     |

| Training Round                  | 2500  |

| Average Moving Attenuation Rate | 0.99  |

The entire neural network is based on the *Keras* framework (Tensorflow as backend) [12]. The parameters listed in Table 3.3 are tentative results and might not represent optimal solutions.

With the trained model, test data collected from the DUV are fed to it to get the prediction results. After retrieving the score for each flip-flop, we can set a threshold to select the critical ones for later use. This threshold depends on the requirements for practical application. We will elaborate on this in later sections.

### 3.3.4 Generating Guide Waypoints

We now have the score of all Flip-flops in the target design. Based on the scores, we can set a threshold to select single or multiple flip-flops as the the critical ones, which serve as a database for the waypoint generation step. In this section, we will discuss the algorithm for single waypoint generation. Multiple waypoints generation would be similar, but with more rounds of iteration and regression in later verification because there is a higher chance that the generated waypoints are out of order or not reachable.

We will first define some notation before proceeding with our illustration of the generation algorithm. Suppose we have a model M for the FSM of our target design, we will have:

$$M = (S, I, s, \rightarrow)$$

Where S is the state variables, I stands for input variables, s is the initial state assignment, and  $\rightarrow$  represents the state transition. Note that all reachable S are correlated with at least one transition  $\rightarrow$ .

A one-step state transition can be represented with  $[S_n] \times [I] \to [S_m]$ . If we call a certain  $S_m$  "CurImg", the states  $S_n$  that can enter  $S_m$  in one clock cycle with corresponding I is defined as "PreImg"; if  $S_n$  is "CurImg", the states  $S_m$  that the "CurImg" can transfer to in one clock cycle with corresponding "I" is defined as "NxtImg".

Before starting the analysis of the Verilog source files, we need to determine the CFF pool for critical flip-flops out of all the flip-flops that we are interested in. From this stage, all operations are conducted for the flip-flops in the CFF pool.

For a specified state  $[S_i]$ , we can define the current state as "CurImg" according to the FSM transition graph. We define its "PreImg" as those states

that can directly reach CurImg state without passing through an intermediate state, and "NxtImg" as those can be directly transited from CurImg via no intermediate state. All CFF should store some values in the specified CurImg, and those flip-flop values can be calculated by parsing the information of RTL source code in the "CurImg", "PreImg" and "NxtImg".

As for the RTL code, we will use Cond to represent a condition statement, RV for right value of the assignment and LV for the left value of the assignment. In addition, we need to pay attention to NOT logic, i.e., ! and  $\sim$  symbols, of the interesting flip-flops since the reverse logic affects how we pair those values in the assignment. This feature will be used for waypoints automatically generated in the next step.

With the notation clarified above, we can provide the Algorithm 1 in pseudo code for waypoint generation based on the selected CFF and the parsed RTL code.

Assume CFF is not an empty set, a new flip-flop list X is initialized with all elements in CFF. Besides, Waypoint set is initialized as an empty set for later appending. The generation loop (Line 3) will evaluate each element x in the list X in sequence. For each x, its "Nickname" is first searched through the RTL code based on two criteria: 1) when x is the only RV in the assign statement, the corresponding LV is defined as a Nickname of x; 2) when x is directly connected to an input or output port of other modules, that port is defined as a Nickname of x. The Nicknames should be appended to list X for the exact same search in later looping starting Line 10 and Line

### Algorithm 1 Waypoints Generation

```

Require: CFF \neq \emptyset

1: X \leftarrow \forall x \in CFF

2: Waypoints \leftarrow \emptyset

3: for x \in X do

if x found as the only* RV in combinational assignment then

append LV to X

5:

end if

6:

7:

if x is directly connected to submodule ports then

append the connected port to X

8:

end if

9:

for \forall x \subset Combinational \ Logic \ do

10:

if x \in \forall Cond then

11:

append (Cond) to Waypoints

12:

end if

13:

end for

14:

for \forall x \subset Sequential \ Logic \ do

15:

if x \in \forall Cond then

16:

append (Cond) to Waypoints

17:

end if

18:

19:

if (x \in \forall RV) \cup (\text{corresponding } LV \in CFF) then

append (RV ##1 LV) to Waypoints

20:

end if

21:

end for

22:

23: end for

24: return Waypoints

```

15. The next step is analyzing the RTL code to generate waypoints. First, we go through both combinational logic (=) and sequential logic (<=) to check whether x belongs to the conditional statement, such as if and case (Line 11 and Line 16). If yes, the entire condition logic will be added to the Waypoints set. Besides, there is one more case for sequential logic where we can select waypoints: if x belongs to any RV, and the corresponding LV is

also within CFF set (Nickname excluded), then the sequence RV ##1 LV should be added to the Waypoints set (Line 19). When all elements in list X are analyzed, the loop ends and the Waypoints set is returned. In addition, the algorithm description with symbol \* can be altered to meet specific needs. We will give an example in Chapter 4.

Note that in an application of the generated waypoints, we need to add '!' if we use SVA to find the trace. No such reverse logic is needed if we use coverage properties.

It is worth mentioning that another important issue in the automatic process is how to order the generated waypoints. This order process is completed manually in this work. We suggest that future work can apply heuristic regression referring to fanin and fanout metrics to further automate this step.

### 3.3.5 Result Evaluation

To evaluate the proposed automatic waypoint generation methods, we apply the same synchronized FIFO example used in Chapter 2.

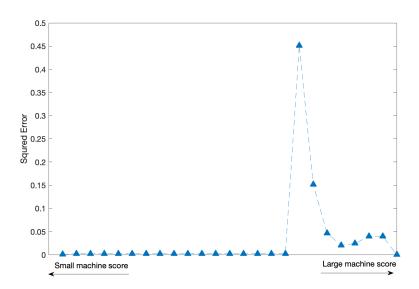

First, the neural network model is trained with the collected data set illustrated in Section 3.3.2 using *Keras*. This model is then used to score each flip-flop, which we refer to as "machine-predicted score". Meanwhile, we manually score each flip-flop as a ground-truth, which is referred to as "user-defined score". Figure 3.4 shows the squared errors between corresponding user-defined score and machine-predicted score. The machine scores increase alongside the horizontal axis from left to right, but the coordinate values are

not evenly distributed because we want to show each spot clearly. As shown in the figure, the squared errors at both ends are quite small while the median ones are relatively large. This result is acceptable because our goal is to find the critical flip-flops with a very large score. Those flip-flops belong to data path have small scores in both user-defined and machine generated cases, which are ensured to be eliminated. The only concern remaining is the middle part with large squared errors. However, scoring itself is actually ambiguous, especially for these hard-to-define flip-flops with median scores. Since even humans cannot give a clear classification, we can take them out of our consideration. The original data is attached in appendix B.2.

Figure 3.4: Squared error between user-defined scores and machine-predicted scores

A threshold should be set manually to pick the CFF set for the next step. The decision on threshold depends on practical application, but we suggest a basic rule that selected CFF should not include those with large squared errors. A fundamental way to judge whether the predicted scores are rational is to evaluate the selected CFF based on the original RTL design.

In this example, we set 0.8 as the threshold so that:

The detail of these signals can be referred to Appendix C.1. This result is consistent with our arbitrary definition of control signals in the synchronized FIFO module. These critical flip-flops will serve as the preliminary dataset for the waypoint guide generation in the next step.

We develop a Python script to perform the waypoint guidance generation for each flop in the CFF set. It also returns the interesting line in the RTL code in case users may want to check the design and introduce some human intervention in deciding waypoints. The result is presented in Table 3.4.

Table 3.4: Automatic generated waypoints guide

| CFF      | Waypoints               | line |

|----------|-------------------------|------|

| dffw1    | (dffw1) ##1 (dffw2)     | 21   |

| dffw2    | null                    | null |

| wr_reg   | $(rd\_succ == wr\_reg)$ | 91   |

| full_reg | (~full_reg)             | 99   |

The next step is applying the one or multiple waypoints from Table 3.4 to SFV flow. However, can be noticed that these waypoints could guide

the system a different direction which may not include our target states. In addition, the memory resources and time required to automatically select and order multiple waypoints can be too high. Therefore, combining automatic generation results and artificial analysis may be more effective to reach the target state.

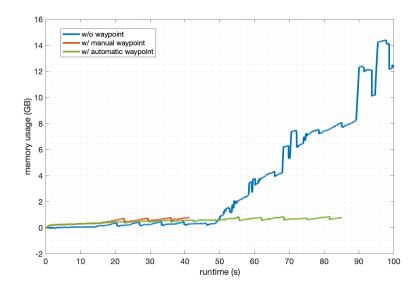

The test conducted applies a more effective direction which lets the user select and order the waypoints for our target from the guidance list. In addition, higher hierarchical conditions can be added to the waypoints to specify them in more detail. This is also a good example of the reason why human intervention is preferred even with the generated guidance list. Therefore, the waypoint can be selected as ( $\sim empty~\&\&~(wr\_reg~==~rd\_succ)$ ) to help to hit the target state faster. Besides, the same environment, running Cadence JasperGold engine Ht & Hp on the server with four Intel E5-2690 CPUs and memory size of 8GB, is used in this test. To obtain better comparison results, we take the same coverage property,  $ck\_full\_once$  and  $ck\_all\_used$  in Table 2.2, as our target states and test the amount of the time and memory needed for the formal engine to reach them.

Table 3.5: Comparison between FV and SFV with automatic generated waypoints

|                       | total runtime /s | memory consumption /MB |

|-----------------------|------------------|------------------------|

| w/o waypoint          | 149              | 251.67                 |

| w/ manual waypoint    | 4.35             | 65.96                  |

| w/ automatic waypoint | 78               | 65.68                  |

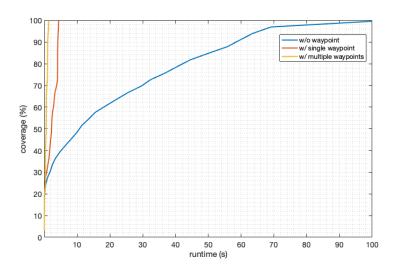

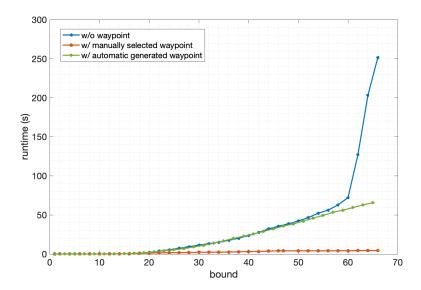

Figure 3.5: Runtime growth versus bound of FV, SFV with manually selected, and automatic generated waypoints

We compare run times between FV and SFV with automatically generated waypoints using the synchronized FIFO with FIFO\_DEPTH of 5. The result is presented in Figure 3.5 and Table 3.5, where total runtime and max memory consumption using automatic generated waypoints are significantly improved by 47.7% and 73.9% respectively compared to isolated FV. The reduction in runtime using SFV with waypoints generated by the proposed algorithm appears to be from nearly exponential to linear growth. However, it is undeniable that the manually selected results presented in Chapter 2 appear to be more effective than this automation algorithm, as shown in Figure 3.5 in terms of runtime growth. However, in the cases where the DUV design details are ambiguous or too complex, this automation method can still be of great

benefit.

## 3.4 Other note: Coverage Metrics

Besides waypoint generation automation, there are many other applications for the identified critical flip-flops, such as fault tolerance and coverage. In this section, we will discuss the application from the aspect of coverage metrics based on the critical flip-flops found from the aforementioned algorithm.

Evaluation of whether verification results give sufficient confidence regarding the correctness of the design depends heavily on the coverage metrics. Most of the mainstream verification flows use coverage metrics such as line coverage, signal coverage, branch coverage, etc., which can be generally classified into two categories: code coverage and function coverage [3]. However, many of these are ambiguous and incomplete for situations where multiple decisions on state transitions are made together. The thesis research in [25] designed an automatic coverage directives generation tool by analyzing RTL written in Verilog HDL. However, the coverage properties written in SystemVerilog bear the advantages that they can be integrated with most simulators and formal tools easily. One potential issue is that the properties generated from large designs require a huge amount of computation. The main drawback is that this process may take an impractical time to run. Even it can generate all properties within a tolerable time, the possibility of having unreachable coverage properties increases due to the large number of properties generated, and it is hard for humans to distinguish whether the unreachable coverage is due to the problem of automation tool or the deficiencies in the verification plan. Therefore, we could use the method illustrated in this chapter to find the CFF as a subset of all registers, which helps the coverage directives generation tool to focus only on the critical control flow. Even excluding the automation tool, these critical flip-flops can still serve as a good guide for manual coverage metric design.

In addition, other similar algorithms can also be applied here to automatically generate the coverage metrics guides. The only difference lies in how to select the CFF pool. The number of flip-flops selected can be very flexible since we provide a continuous scoring prediction instead of an absolute classification. Designers can choose any threshold based on their own project requirements.

# Chapter 4

# **Experiments and Results**

# 4.1 Application Guidelines

Before looking into the study cases, we will first specify the cases where the application of waypoint-based SFV flow would be more suitable and beneficial.

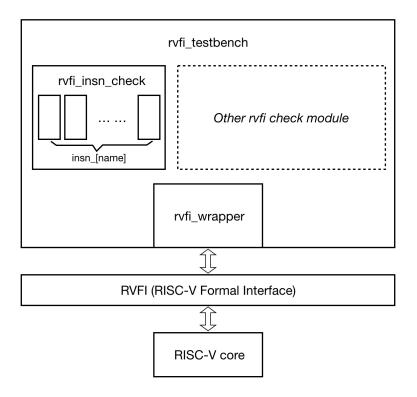

The SFV flow proposed in this work is able to largely improve the performance of verification in large design, where classic FV easily run into complexity issues. The keypoint in our SFV flow is to select the proper way-points. For example, in microprocessor verification, we could bypass the long initialization sequence through the peripheral bus to configure all the architectural registers. Another case, also for microprocessor verification, is that we can select waypoints based on the pipeline stages in order to reduce the size of the COI. For instance, if we take the state right after decoding as waypoint, we can focus on the specific instruction for verification.