Copyright

by

Vipul Goyal

2017

# The Report Committee for Vipul Goyal Certifies that this is the approved version of the following report:

# Physical Design and Verification for Microscale Modular Assembled ASIC (M2A2) Circuits

# APPROVED BY SUPERVISING COMMITTEE:

| Supervisor:    |                   |  |

|----------------|-------------------|--|

|                | S. V. Sreenivasan |  |

| Co-Supervisor: |                   |  |

|                | Mark McDermott    |  |

# Physical Design and Verification for Microscale Modular Assembled ASIC (M2A2) Circuits

by

# Vipul Goyal, B.Tech

# Report

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Master of Science in Engineering**

The University of Texas at Austin

May 2017

## Acknowledgements

I would like to thank my supervisor, Prof. S. V. Sreenivasan for giving me this great opportunity. His guidance, encouragement helped me a lot in this endeavor. I would like to express my sincere gratitude to Prof. Mark McDermott for being always available for technical discussion and providing feedback. Without his help, this report would not have been possible.

I would also like to thank project partners, Aseem Sayal, (E.C.E. Graduate Student, UT Austin) and Paras Ajay (M.E. Graduate Student, UT Austin) for all their valuable inputs. Also, I highly appreciate the effort of Shrawan Singhal (Post-Doctoral Research Fellow, M.E., UT Austin) for helping me with writing the report. I would like to extend my sincere gratitude to Nandini D Chintala, Prashant Joshi, Bhargav Bhat Bhaskar and Cadence team for giving their valuable suggestions and guidance.

Also, I'm thankful to The University of Texas at Austin for providing the required infrastructure for this project. A special thanks to all the friends and people in industry who helped me to understand the ASIC tools and flows.

#### **Abstract**

Physical Design and Verification for Microscale Modular Assembled

ASIC (M2A2) Circuits

Vipul Goyal, M.S.E.

The University of Texas at Austin, 2017

Supervisors: Prof. S. V. Sreenivasan, Prof. Mark McDermott

The overall goal of this project is to bring down the fabrication cost for low volume ASICs by introducing a novel 'pick and place' mechanism for micro-scale elements of ASICs referred to here as feedstock. This new feedstock based ASIC design flow is referred as Microscale Modular Assembled ASIC (M2A2) design flow. This report complements efforts in fabrication and other Electronic Design Automation (EDA) aspects carried out by researchers at The University of Texas at Austin studying this new mechanism for ASIC design and manufacture. For the purpose of this study, the conventional industrial practice in ASIC design flow was analyzed and modifications to that flow were explored. The initial Synthesis solution was developed using Synopsys's Design Compiler (DC) tool. However, due to the limitations of the tool, the final solution was developed based on Cadence tools. The main blocks of the design flow in this report are Synthesis and analysis of its capabilities; Conformal ECO; Post-Mask spare cell mapping; Post-Mask Clock Tree Synthesis (CTS) and Route; Post-Mask timing and

v

Design Rule Violation (DRV) fixing; and Verification. The Standard Cell-based ASIC design was used as a benchmark and it was compared to M2A2 design flow.

# **Table of Contents**

| List of Tables                                                    | X  |

|-------------------------------------------------------------------|----|

| List of Figures                                                   | xi |

| Introduction                                                      | 1  |

| Chapter 1: Synthesis                                              | 8  |

| 1.1 Defining each feedstock as a 'Standard' cell                  | 8  |

| 1.2 Experiments to define feedstock as 'Standard cell'            | 9  |

| 1.2.1 Modified Inverter Cell 'INVX1'                              | 10 |

| 1.2.2 Modified Inverter Cell with No Other Inversion Cells        | 11 |

| 1.2.3 Convert a 2-Input Cell to an Inverter                       | 11 |

| 1.2.4 Convert a 2-Input Cell to an Inverter with Single Input Pin | 12 |

| 1.2.5 Modify the 2-Input Cell with Different Functionality        | 13 |

| 1.2.6 Generating A Complex Cell                                   | 14 |

| 1.2.7 Modifying the Complex Cell                                  | 15 |

| 1.2.8 Conclusion                                                  | 15 |

| 1.3 Using .lib features to define feedstock as a cell             | 16 |

| 1.3.1 INOUT Pins Experiment                                       | 16 |

| 1.3.2 TIE-HIGH and TIE-LOW Cells Experiment                       | 16 |

| 1.3.3 Synthetic Libraries                                         | 17 |

| 1.4 Generating libraries for hierarchical cells                   | 17 |

| 1.5 Defining each feedstock as a Library                          | 18 |

| Chapter 2: ECO and Conformal ECO                                  | 20 |

| 2.1 ECO - features and limitations                                | 20 |

| 2.2 Experiments with ECO                                          | 21 |

| 2.2.1 Cell Swapping                                               | 21 |

| 2.2.2 Modifying Design's Functionality Using ECO                  | 22 |

| 2.2.3 Replacing Gate with Another Gate with Same Instance Name    | 25 |

| 2.2.4 Implementing Full Design Using Unconnected Spare Cells      | 26 |

| 2.2.5 Implementing Modified Design                             | 27  |

|----------------------------------------------------------------|-----|

| 2.2.6 Physically Aware Design Optimization                     | 29  |

| 2.2.7 Gate-Size and V <sub>T</sub> Aware Design Optimization   | 30  |

| 2.2.8 Conclusion                                               | 31  |

| 2.3 Conformal ECO                                              | 32  |

| 2.3.1 Gate-Size and V <sub>T</sub> Aware Design Optimization   | 33  |

| 2.3.2 Feedstock-Based Design Implementation                    | 34  |

| 2.3.3 Hierarchical Feedstock                                   | 35  |

| 2.3.4 Hierarchical Feedstock with Multiple Instantiation       | 38  |

| 2.3.5 Flattened Feedstock                                      | 41  |

| 2.3.6 Final Conformal ECO Flow                                 | 44  |

| Chapter 3: Physical Design – Post Mask EDI                     | 47  |

| 3.1 Placement (Spare Cell Mapping) – Post Mask EDI Flow        | 47  |

| 3.2 Clock Tree Synthesis – Post mask                           | 50  |

| 3.2.1 Generating Clock Tree through Routing                    | 51  |

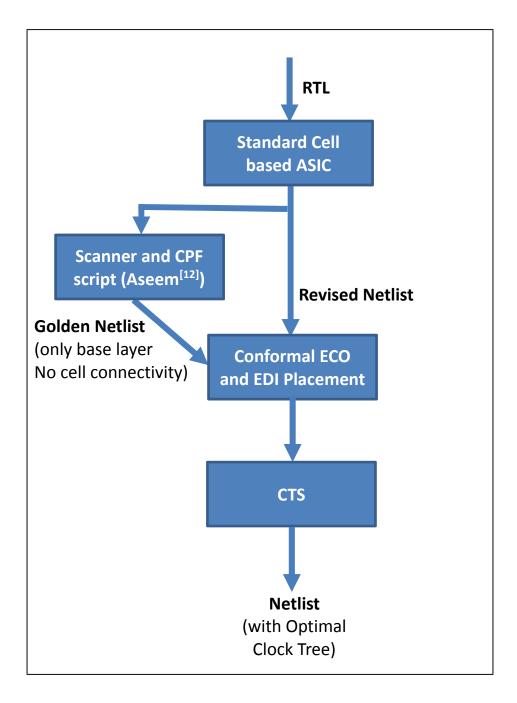

| 3.2.2 CTS with Conformal ECO                                   | 52  |

| 3.2.3 Retaining Clock Buffers in Conformal ECO                 | 54  |

| 3.2.4 Optimization Techniques                                  | 58  |

| 3.2.5 Results                                                  | 61  |

| 3.3 Timing Closure – Post mask                                 | 62  |

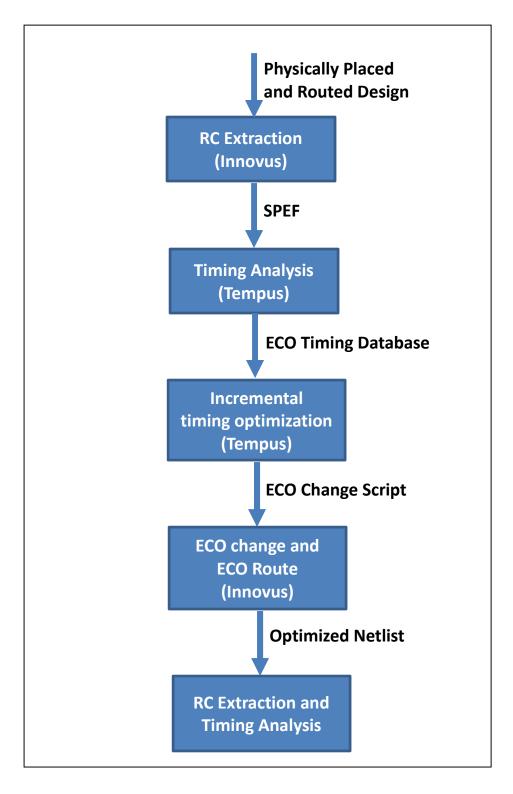

| 3.3.1 Timing Closure Using Tempus and Innovus                  | 63  |

| 3.3.2 Limitations of the Standard Flow                         | 66  |

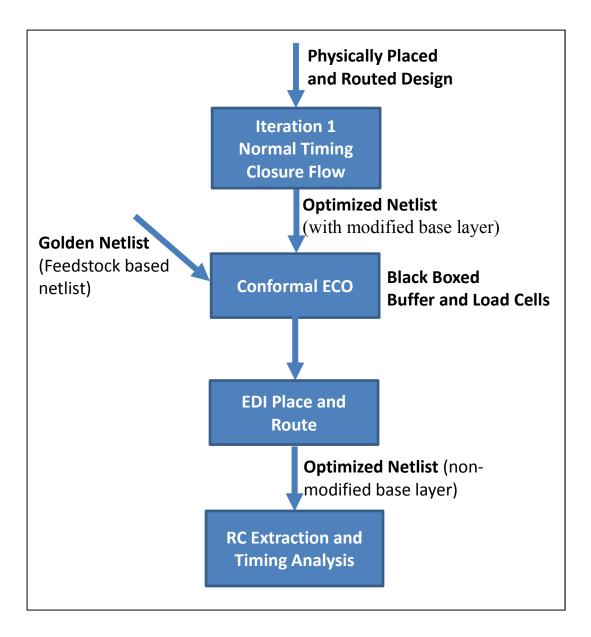

| 3.3.3 Developing the New Flow                                  | 66  |

| 3.3.4 Optimization Technique – Empty vs Conformal ECO netlist  | t67 |

| 3.3.5 Black Boxing Buffer Cells of a Particular Drive Strength | 68  |

| 3.3.6 Optimizing Critical Paths Iteratively                    | 69  |

| 3.3.7 Results                                                  | 70  |

| Chapter 4: Verification                                        | 76  |

| 4.1 Verification Flow                                          | 76  |

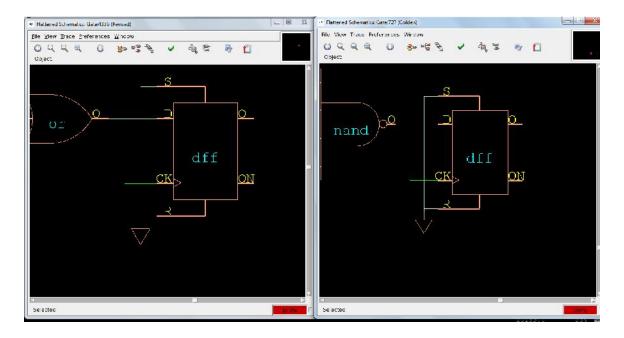

| 4.2 Debugging non-equivalent points                            | 78  |

| Conclusions | '9 |

|-------------|----|

| References  | 31 |

# **List of Tables**

| Table 1: Clock Tree Quality Metric for Different Optimizations | .61 |

|----------------------------------------------------------------|-----|

| Table 2: Timing comparison for Different Black Boxed Buffers   | .69 |

| Table 3: Timing Slack for High Performance CDL 50              | .75 |

# **List of Figures**

| Figure 1: Sample customer's RTL                                       | 2  |

|-----------------------------------------------------------------------|----|

| Figure 2: Standard Cell based design                                  | 2  |

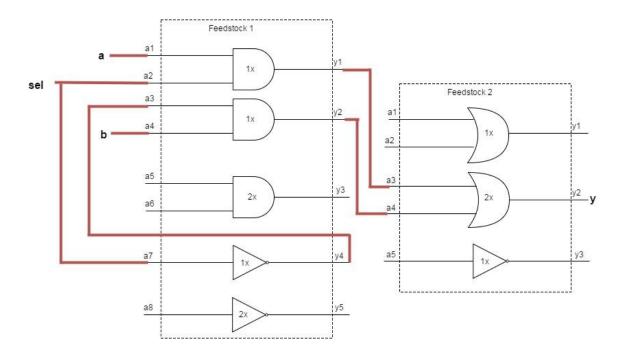

| Figure 3: Library of Feedstocks                                       | 3  |

| Figure 4: Feedstock based netlist which will be used in Conformal ECO | 4  |

| Figure 5: Getting the functionality using Conformal ECO               | 5  |

| Figure 6: Optimizing the design                                       | 6  |

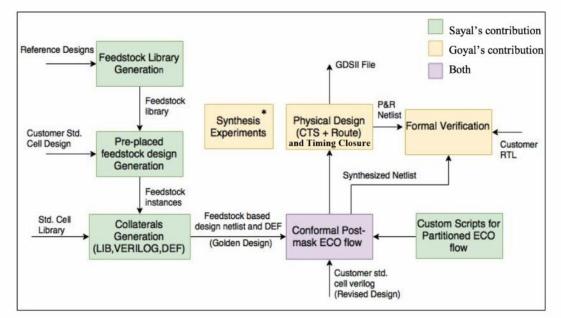

| Figure 7: Work Distribution [13]                                      | 7  |

| Figure 8: Initial design before running ECO                           | 23 |

| Figure 9: Revised design implemented by just re-routing               | 24 |

| Figure 10: Timing Report – Before Running Conformal ECO Optimizations | 33 |

| Figure 11: Timing Report – After Running Conformal ECO Optimizations  | 34 |

| Figure 12: Golden Netlist – Flattened Feedstock Based                 | 42 |

| Figure 13: Revised Netlist                                            | 42 |

| Figure 14: Final Conformal ECO Generated Netlist                      | 43 |

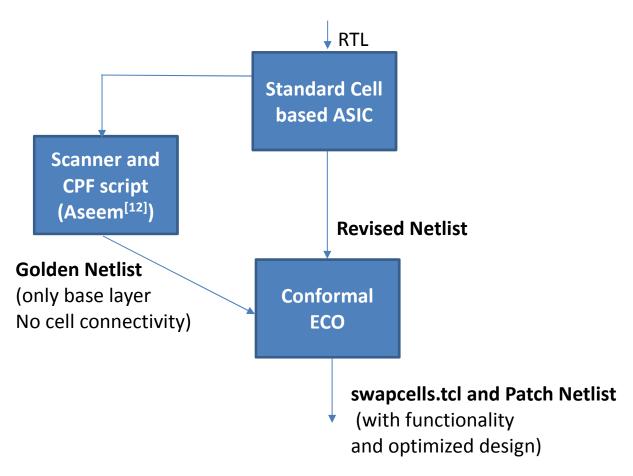

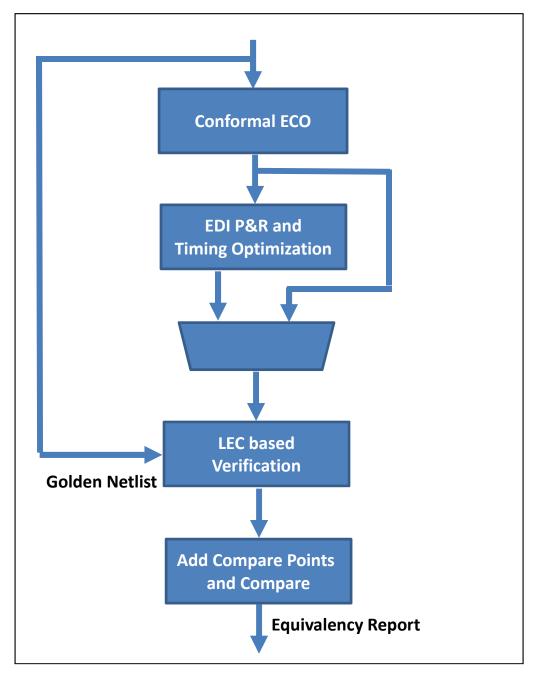

| Figure 15: Conformal ECO Flow                                         | 46 |

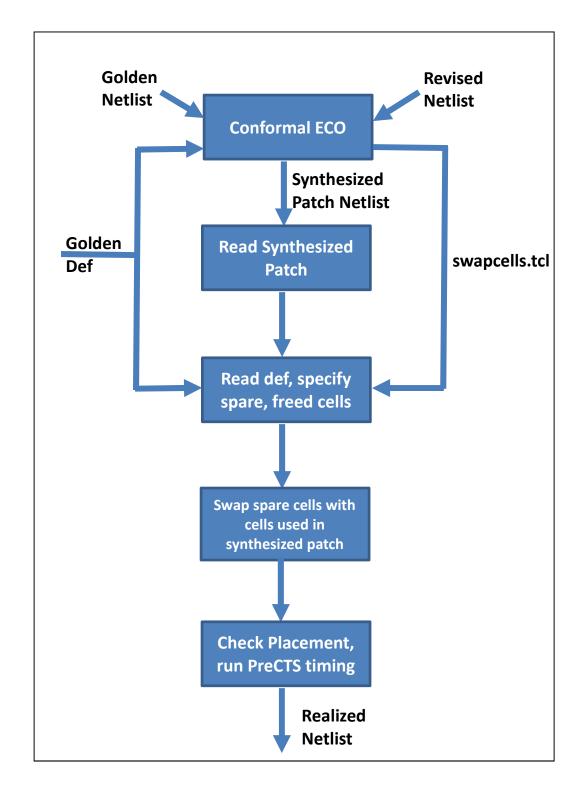

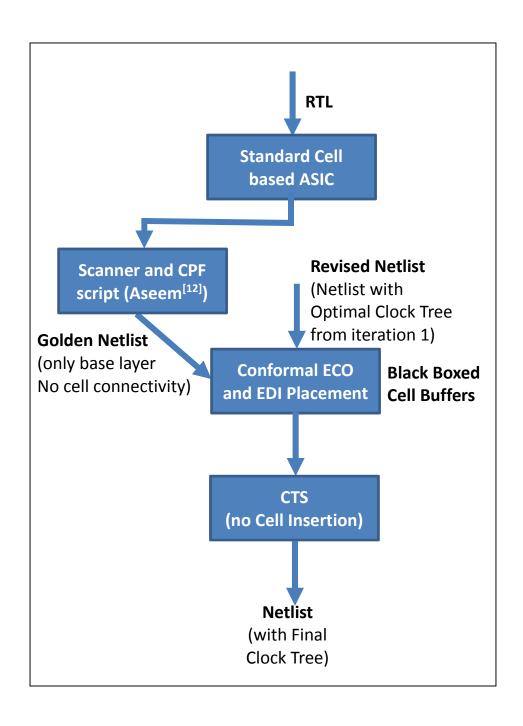

| Figure 16: Post Mask EDI Placement Flow                               | 49 |

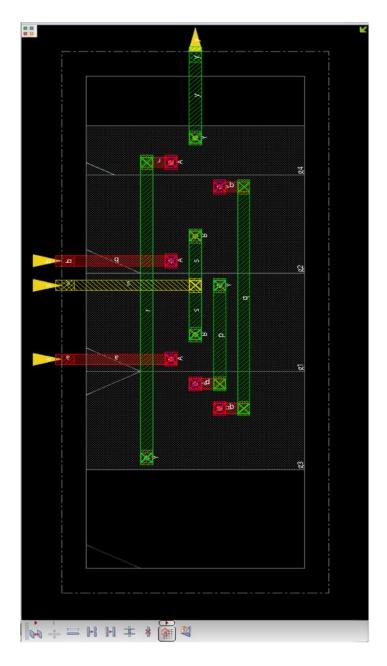

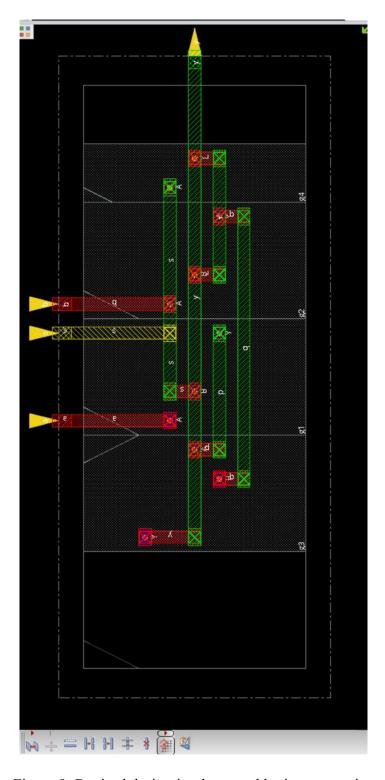

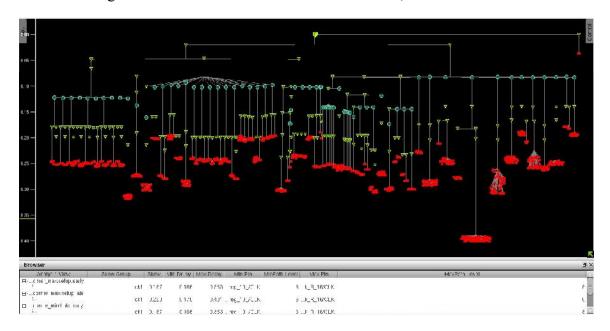

| Figure 17: Generated Clock Tree using Routing                         | 52 |

| Figure 18: Developed Post Mask CTS Flow - Iteration 1                 | 56 |

| Figure 19: Developed Post Mask CTS Flow - Iteration 2                 | 57 |

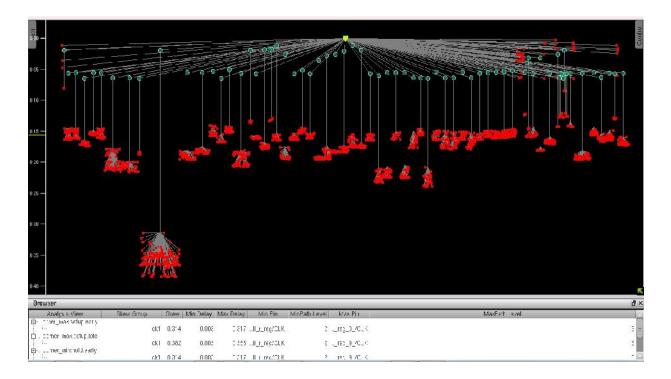

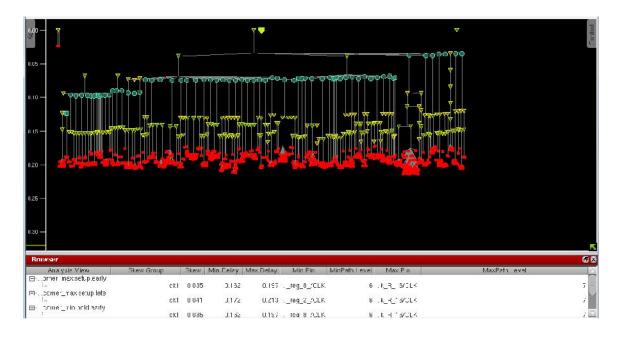

| Figure 20: Built Clock Tree (iteration 1) with Non-Movable Flops      | 58 |

| Figure 21: Built Clock Tree (iteration 1) with Movable Flops          | 59 |

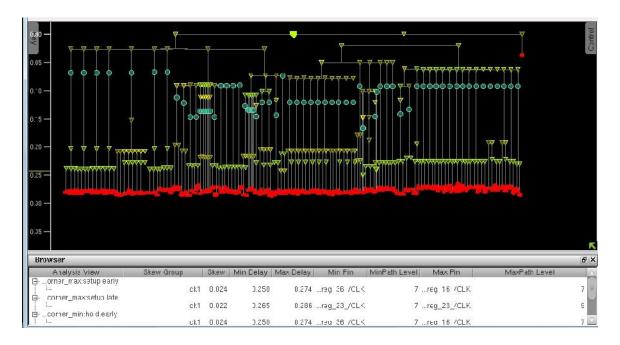

| Figure 22: With Unconnected Feedstock Netlist, as Golden Netlist      | 60 |

| Figure 23: With Conformal ECO Netlist, as Golden Netlist              | 60 |

| Figure 24: Timing Closure Flow Using Tempus and Innovus [24] | 65 |

|--------------------------------------------------------------|----|

| Figure 25: Develop Post Mask Timing Closure Flow             | 67 |

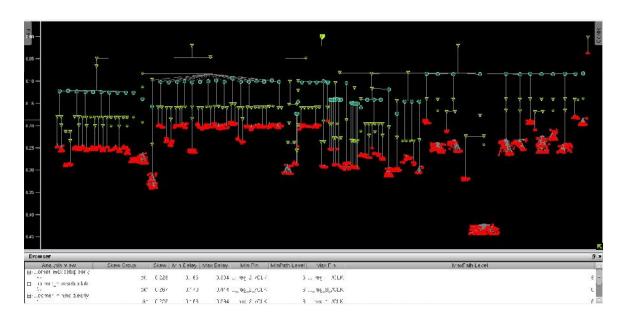

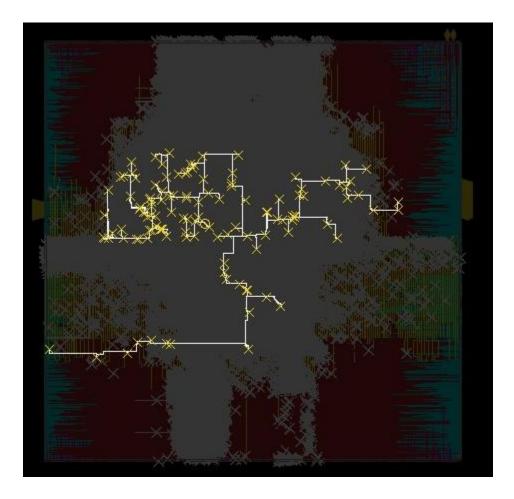

| Figure 26: Sample Net in the Initial Feedstock Based Design  | 71 |

| Figure 27: Critical Path in the Initial Design               | 72 |

| Figure 28: Same Path After Timing Optimization               | 73 |

| Figure 29: Critical Path in the Optimized Design             | 74 |

| Figure 30: Verification Flow                                 | 77 |

| Figure 31: LEC Schematic Debug Window                        | 78 |

#### Introduction

In the world of ASICs, the fabrication cost has gone up with technology scaling [1]. This is because the cost of e-beam lithography, which is used to generate masks, grows exponentially with diminishing feature size, especially for sub-50 nm technology nodes. This has a significant impact on low volume ASICs. Since their chip-count is typically in the hundreds or thousands, the fabrication cost per IC can be very high. The aim of this project is to bring down the fabrication cost of low volume ASICs without compromising on performance. Some existing solutions for low volume ASICs include structured ASIC [2,3,4,5,6,7,8] and FPGA-based flows. Although a FPGA-based flow is reconfigurable and has very less time to market, it consumes a lot of area, and suffers from low performance with high costs. On the other hand, structured ASICs have challenges with implementing a general design without negatively impacting area, performance, and power. Also, Viaprogrammable ASIC [9-10] have been tried but it has its limitation. As part of this project, we have added an extra degree of freedom to the structured ASIC flow without compromising performance, by coming up with an innovative 'pick and place' mechanism [11] of 'feedstocks' on the target SOC, for fabrication of low volume ASICs. These feedstocks are the fundamental building blocks of the ASIC design.

However, the current standard ASIC design flow needs to be modified to support feedstock-based fabrication. The first step is to design the feedstock library which will serve as the fundamental building blocks in the design. The next step is to take the

customer's design, i.e. the Register Transfer Logic (RTL) (Figure 1) and run the standard cell-based flow to meet the design requirements (Figure 2).

Figure 1: Sample customer's RTL

Figure 2: Standard Cell based design

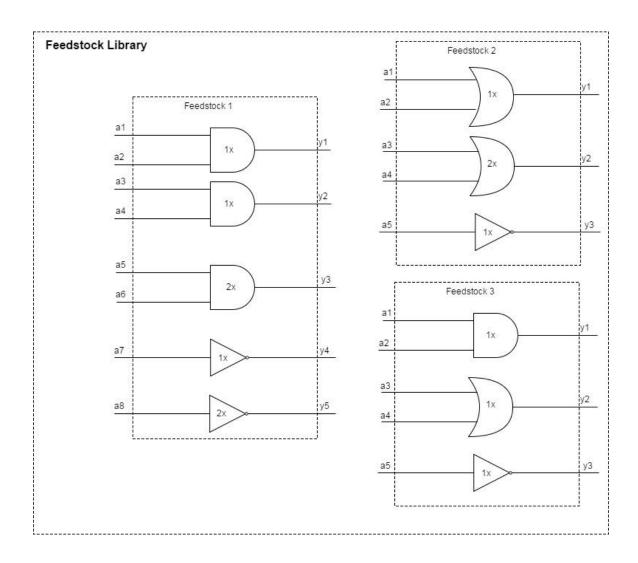

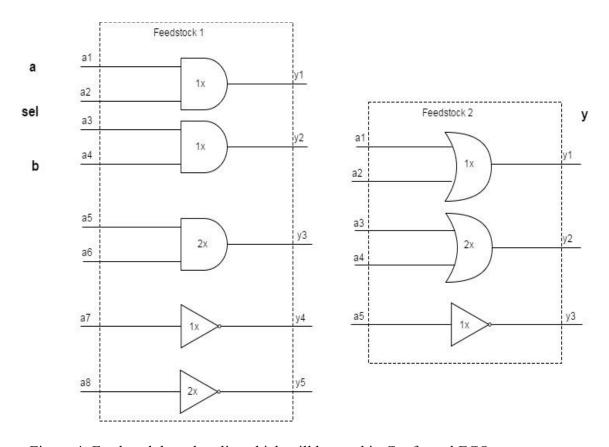

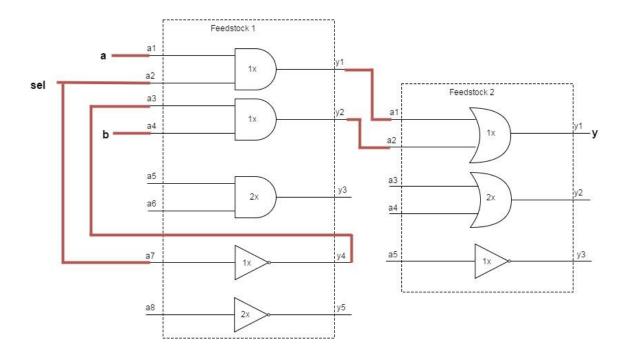

The standard cell-based design is divided into an array of windows. A scanning-based approach is adopted, wherein for each window, the best fit feedstock from the feedstock library (Figure 3) is assigned based on the physical location of cells. After the windows have been mapped to different feedstocks, the base layer is fixed and the feedstock level netlist (Figure 4) is generated. This generated netlist might have partial connectivity.

Figure 3: Library of Feedstocks

Figure 4: Feedstock based netlist which will be used in Conformal ECO

The next step in the design flow is to use Conformal ECO and import the feedstock-based netlist (Figure 4) as the golden netlist, and the standard cell-based netlist (Figure 2) as the revised netlist. In this step, all the cells in the design are defined as spare cells. However, if there is partial connectivity in the golden netlist, then only the leftover cells are defined as spare cells. After defining the spare cells, Conformal ECO attempts to simultaneously meet the functionality (Figure 5) and optimize the design. Then, the swap spare cell file is generated with one-to-one mapping between each spare cell and its corresponding usage in the design.

Figure 5: Getting the functionality using Conformal ECO

After the generation of the spare cell mapping, PostMask Place (physically mapping the spare cells) and Route (P&R) is used to route the design to get the same functionality using only spare cells. Next, a timing analysis is done to fix the timing numbers that are compromised due to the interconnect delays. If there is any negative slack, the timing and DRV violations are fixed using Tempus and Innovus. In this step, it is ensured that the base layer is not changed and that only the spare cells are used to optimize the design (Figure 6). A timing analysis is done again to check if the timing goals are met. This process is reiterated with a different set of feedstocks if, after this step, the design is not closed.

Figure 6: Optimizing the design

Finally, after the design requirements are met, verification checks are done to compare the functionality of the final design with respect to the customer's design with a provision to also compare the feedstock based netlist against the original RTL.

The M2A2 design flow has been collaboratively developed with Paras Ajay [11] and Aseem Sayal [12]. Ajay has developed the 'pick and place' mechanism to fabricate the feedstock based SOC. Sayal and I have worked on the Electronic Design Automation (EDA) design flow with the division of work shown in Figure 7. Sayal has worked on the feedstock library generation, pre-placement of the feedstocks and generation of the collaterals. He has also worked on custom scripts for partitioned ECO flow. The Conformal Post-Mask ECO flow has been done jointly. In this report, the physical

implementation has been conducted by mapping the physical locations of the spare cells to the Conformal netlist; Post-Mask CTS and Routing; Post-Mask DRV and Timing closure. Finally, Formal Verification is done to compare the functionality of the P&R netlist with the customer RTL

<sup>\*</sup>Goyal has also worked on synthesis. He has carried out experiments but has not succeeded in getting working solutions.

Figure 7: Work Distribution [13]

### **Chapter 1: Synthesis**

In the Synthesis stage of the design, the customer RTL is mapped to the fundamental blocks, called standard cells. As part of this project, it is required that these standard cells be bundled together in a single feedstock. Each feedstock can have different numbers and flavors of standard cells. Because of the pick-and-place fabrication approach, the use of any standard cell from a given feedstock requires the pick-and-place of the entire feedstock. Hence, an important optimization constraint in the Synthesis stage is the optimal use of all the cells in the chosen feedstock before adding any new feedstock in the design.

In this chapter, various experiments that were carried out on existing standard Synthesis tools [14] to check if they could meet the project's requirements, are discussed. An analysis of the current design flow is presented along with modification and limitations. While the Synthesis flow was initially developed using the DC tool of Synopsys [15] as seen in the following sections, it was later developed based on Cadence tools, given the limitations of the Synopsys tool.

#### 1.1 DEFINING EACH FEEDSTOCK AS A 'STANDARD' CELL

The first approach was to define each feedstock as a cell in the library. This approach made use of the standard flow, where a given cell could be picked any number of times based on the requirements of the design. Similarly, different feedstocks could be defined as different cells in the library. A variety of experiments were performed to see if the tool understood these feedstocks as cells.

#### 1.2 EXPERIMENTS TO DEFINE FEEDSTOCK AS 'STANDARD CELL'

As mentioned earlier, experiments were carried out to check if the Synthesis tool supported 'standard cells' with multiple independent designs. As a starting point, the synthesis of a small design was tried using these modified 'standard cells'. A normal synthesis flow was first setup with the required collaterals like lef file, tech file, and constraints being the same as in a standard cell-based design. For each experiment, a modified .lib was generated. The standard cells library was replaced with this modified library.

The basic format of a Synopsys library [16] is shown below –

```

library (<library_name>) {

cell (<cell_name>)

pin (<input pin1>) {

direction: input;

pin (<input pin2>) {

direction: input;

.....

.....<other input pins>......

pin (<output pin1>) {

direction: output;

function: <function of this pin in terms of

input pins>

pin (<output pin2>) {

direction: output;

function: < function of this pin in terms of

input pins>

.....

.....<other output pins>......

}

}

```

In this way, a new set of libraries could be generated by modifying the input/output pin list or redefining the functionality of output pins. After the required library was generated for each experiment, a flow was developed to convert the library to the .db format compatible with the Design Compiler tool of Synopsys. This flow was developed and tested on a sample test, after which the following set of experiments were conducted.

#### 1.2.1 Modified Inverter Cell 'INVX1'

In this experiment, one of the inverters in the library was replaced by a new standard cell which had two inverters in parallel. This experiment helped understand if multiple independent circuits in a standard cell could be understood by the Synthesis tool.

```

library (modified_lib) {

cell (INVX1) {

pin (A) {

direction: input;

.....

pin (B) {

direction: input;

......

pin (Y0) {

direction: output;

function: ~A

.....

pin (Y1) {

direction: output;

function: ~B

......

}

```

When this modified library was used to synthesize a given RTL, it was found that Synthesis did not consider this as an inverter, and picked other inverters to synthesize the design.

#### 1.2.2 Modified Inverter Cell with No Other Inversion Cells

In this experiment, one of the inverters in the standard cell was replaced by a new standard cell which had two parallel inverters, similar to the above experiment. Also, all the other inverters and inversion cells were removed from the library to ensure that no other inverters were picked. When Synthesis was run, it reported an error that no inverter was found in the library.

Based on the above two experiments, it can be inferred that Synthesis was not able to understand that an inverter could be located inside a cell which had 2 input pins.

#### 1.2.3 Convert a 2-Input Cell to an Inverter

In the above experiments, a new input pin was added to the existing 1-input pin cell and it was found that the cell was not usable. A possible reason could be that adding a second input pin made the cell unusable. This was further tested in an experiment where an existing 2-input pin cell was taken and its functionality changed. In this experiment, the 2-input cell (DEC24x1) with input pins A0 and A1 was modified. The modified functionality of one of the output pins was  $Y0 = \sim A0$ .

When Synthesis was run, it did not detect this modified cell as an inverter. It can be inferred that a 2-input pin cell cannot be converted to an inverter by simply modifying the functionality of an output pin.

#### 1.2.4 Convert a 2-Input Cell to an Inverter with Single Input Pin

From the above experiments, it can be concluded that the modification of the functionality of an output pin did not work. This may be because of the 'don't care' input pins making the cell unusable. In this experiment, the 2-input cell (DEC24x1) with input pins A0 and A1, was modified by removing the second input pin (A1). Also, the functionality of one of the output pins was modified to Y0 = A0. When Synthesis was run, it detected this modified cell as an inverter.

Based on the above observation it can be concluded that modifying the original 2-input cell to a one input pin cell made it a possible candidate in Synthesis's 'inverter search algorithm'. Hence, in general, removing pins from an existing cell works if the final number of input pins in the modified cell is equal to the number of variables in the functionality of the output pin.

### 1.2.5 Modify the 2-Input Cell with Different Functionality

In this experiment, a new pin, A2, was added to the modified 2-input cell from the previous experiment. The functionality of one of the output pins was also defined as Y0 = A2\*A0. In order to ensure that Synthesis does not select any other AND gate, all other AND gates were removed from the library. When Synthesis was run, it detected this

modified cell as an AND gate. Based on this experiment, it can be concluded that replacing an existing input pin with a new input pin in the cell and realizing the cell's output functionality in terms of this newly added input pin gives the desired result. In general, Synthesis would consider the modified cell in its algorithm only when the number of input pins is not more than the number of independent variables in the function which it is trying to realize.

### 1.2.6 Generating A Complex Cell

It was found from the above experiments that adding and removing pins from a cell and modifying the functionality of its output pin in terms of new pins works for simple cells like an inverter. Since the feedstock would have complex cells, it is important to validate if these modifications would also work for complex cells. In this experiment, a 4-input cell (NAND4X0) was taken and the functionality of one of the output pins was defined as Y0 = (A4'\*A3'\*A2'\*A1') + (A4\*A3\*A2\*A1). Simultaneously, a similar RTL was given to the Synthesis tool,  $y=((\sim i1\&\sim i2\&\sim i3\&\sim i4))$  (i1&i2&i3&i4))

When Synthesis was run, it successfully detected this modified cell and synthesized the RTL using this modified cell.

## 1.2.7 Modifying the Complex Cell

The complex cell generated in the above experiment was further modified by adding an extra dummy input pin to check if this extra dummy pin would cause any issues in this complex cell. The same RTL was given to the Synthesis tool,  $y=((\sim i1\&\sim i2\&\sim i3\&\sim i4) \mid (i1\&i2\&i3\&i4))$ . When Synthesis was run, this modified complex cell was not used to synthesize the RTL.

#### 1.2.8 Conclusion

Based on the above experiments, it can be concluded that the Synthesis tool first counts the total number of input variables in the logic it is trying to synthesize. Its 'cell picking' algorithm then prunes the search space by picking only those cells that do not have more input pins than the number of independent variables in the logic.

#### 1.3 Using .lib features to define feedstock as a cell

The previous experiments revealed that the Synthesis tool counts the total number of input pins of the cell being considered in its 'cell picking' algorithm. Hence, some features of the .lib file were tested to accommodate this feature of the Synthesis tool and to meet the project's requirement.

#### 1.3.1 INOUT Pins Experiment

An experiment was conducted by defining the direction of the pin while defining a gate in the library. Since a pin can have one of three possible directions- input, output or inout- defining the direction of the spare pins in a feedstock cell as inout, can help check if these pins are not counted as input pins. Thus, Synthesis was run with an RTL such that it uses that feedstock and it was found that the inout pins were still getting counted as input pins. It can be concluded that the direction of a pin as inout is not helpful.

#### 1.3.2 TIE-HIGH and TIE-LOW Cells Experiment

After the above experiment, a second option was to make use of tie-high and tie-low cells to connect to the spare pins while doing synthesis. These cells were thus, added to the library and the dont\_use option was set to false. Synthesis was then run to check if the spare pins of the feedstock would be connected with these tie-high and tie-low cells. The results indicated that the tool did not use the feedstock and synthesized the design using other fundamental gates. If the spare pins were removed from the feedstocks, then the Synthesis tool was able to use them. It can be concluded that the feedstock is not usable even after tying its spare pins to the tie cells.

#### 1.3.3 Synthetic Libraries

While defining the library, an advanced feature allowed the user to define complex cells. This feature is particularly useful when a module is repeated several times in the design, as it has a provision to include that design in the library itself as a standard cell. But, the Verilog model of the module had to be defined and 'alib' [17] for the module had to be generated for this feature to work. Then, during synthesis, if the alib library path had been defined, the synthesizer would go through the alib library along with the target and link libraries to synthesize the design. This procedure for developing a synthetic library and alib models was used for the feedstocks. However, it was observed that the spare input pins in the feedstock prevented the synthetic models of the feedstocks from getting used by the synthesizer in its mapping algorithm.

#### 1.4 GENERATING LIBRARIES FOR HIERARCHICAL CELLS

One important requirement for running a feedstock-based synthesis flow is characterizing each feedstock for timing, power, leakage, and other models. Since feedstocks were being built using standard cells, the effort of re-characterizing the feedstocks can be saved. However, a new flow which would take the Verilog model of the feedstock standard cells' libs and generate the hierarchical libs of the feedstock library, needed to be developed. Timing and power analysis was required to be done for feedstock with complex logic. For such feedstock, the flow was developed using the Primetime and PTPX tools from Synopsys. Once generated, the .libs could be converted to .db using the flow developed in previous experiments. Some components that were generated in the .lib were cell area, cell leakage, and clock model. For the input pins, the setup and hold time model was included. For the output pins, the fall/rise delay and fall/rise cell transition timing models were included.

Since there was no complex logic in the feedstock in the final approach. This developed flow would be useful when complex logic is added to the feedstock and timing and power analyses of different paths of the feedstock are needed to generate the .libs

#### 1.5 DEFINING EACH FEEDSTOCK AS A LIBRARY

From the previous experiments, it is evident that defining each feedstock as a cell did not work because the Synthesis tool's 'cell picking' algorithm considers only those cells that do not have more input pins than the number of independent variables in the logic. However, since the requirement of the project is to have multiple cells in a single feedstock, a few different approaches were developed.

In one approach, each individual feedstock was defined as a unique library with the cells in each library representing the cells present in that feedstock. Whenever a feedstock was picked, the corresponding library would be active and cells from that library would be used to synthesize the design. However, it had to be ensured that the cells could only be used as many times as their instances in the library. For example, if a feedstock A had 5 inverters, then the inverter cell could be used a maximum of 5 times when the library was called. However, the standard algorithm allowed a given cell from the called library to be used any number of times. This meant that a different approach had to be adopted to meet this requirement.

In order to ensure that none of the cells were instantiated more than their count on the feedstock, a possible approach was to set the usage of each cell in the given library to a constant. However, after going through literature and library documentation, it was found that there was no such feature. An alternate solution was to uniquely define each cell present on a feedstock, in its corresponding library. However, the problem still remained as the software allows only two knobs- dont use, and preferred [16]. Therefore,

in order to exhaustively use the cells from the library, a scanning based approach was developed, by another project member [12], wherein windows were created in the standard cell-based design and for each window, the best-fit feedstock was assigned depending on the physical location of cells. The base layer was fixed and the feedstock level netlist was generated after all the windows were mapped to different feedstocks. Finally, Conformal ECO flow was run to achieve the desired functionality.

## **Chapter 2: ECO and Conformal ECO**

In a standard ASIC design flow, the Engineering Change Order (ECO) stage is used when there are design changes in RTL that need to be incorporated after implementation of the SOC is done. ECO does logical equivalence of the original design's netlist with the modified netlist and captures the changes in the design. It then generates the patch file which represents all these changes. This patch file is synthesized using the spare cells already present in the design which precludes the physical design of the whole SOC from scratch. After the design changes are mapped to the spare cells, the synthesized cells are swapped with their corresponding spare cells. Finally, the incremental routing of theses spare cells is done.

In the M2A2 design flow, the "exhaustive usage" feature of the ECO was used to meet the design functionality. ECO has the ability to realize the changes in the design by using only the spare cells. This feature was exploited in this project. The feedstock-based netlist generated from the scanner script was given to ECO as the golden design. Since there was no connectivity in the netlist, all the cells in this feedstock-based netlist were defined as spare cells, allowing the ECO to synthesize the whole design using these spare cells. Further optimizations were performed to meet performance once the design functionality was met.

#### 2.1 ECO - FEATURES AND LIMITATIONS

Given the "exhaustive mapping" feature of the ECO described above, preliminary experiments were performed to confirm optimal synthesis, physically aware cell utilization, gate sizing and  $V_T$  cell swapping for higher performance design. Experiments were also conducted to validate if the ECO could synthesize large designs by using the

spare cells without being overwhelmed. These experiments and the inferences drawn from them are discussed in the following section.

#### 2.2 EXPERIMENTS WITH ECO

The primary inputs to run ECO are the golden netlist and the revised netlist. The golden netlist has the original design and the revised netlist has the updated design which needs to be implemented. For these experiments, the first step involved the physical implementation of the golden netlist. Based on the netlist, a floorplan was generated for each experiment followed by a 'place and route' of the golden netlist. After being physical implemented, the golden netlist was saved in .dat format to convey the physical locations of the cells to ECO. Once the .dat and revised netlist were generated, ECO was run using ecoDesign [18] in the PostMask mode. ECO would re-route the golden design and try to achieve the same functionality as the revised netlist. After developing and testing this flow on a sample test, the following set of experiments were conducted to do an in-depth analysis of ECO.

#### 2.2.1 Cell Swapping

This experiment was performed to verify the ECO flow and capture the requirements for cell swapping. The golden netlist given to the ECO had NAND and AND gates with {a, b} and {c, d} pins, respectively. The revised netlist had NAND and AND gates with swapped pins, i.e., {c, d} and {a, b} pins, respectively. Upon running ECO, it was found that cell swapping was achieved by just re-routing the design without changing the transistor layer.

# 2.2.2 Modifying Design's Functionality Using ECO

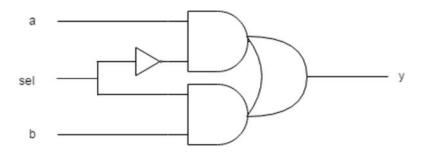

The goal of this experiment was to implement a MUX. In the golden netlist (Figure 8), all gates required to implement a MUX were present, but they were intentionally connected incorrectly. The revised netlist had the correct functionality of the MUX. ECO was able to successfully achieve the correct functionality (Figure 9) by simply re-routing the golden design. It was also observed that this process worked only when the instance name used in the revised netlist is the same as the golden netlist.

Figure 8: Initial design before running ECO

Figure 9: Revised design implemented by just re-routing

#### 2.2.3 Replacing Gate with Another Gate with Same Instance Name

In the previous experiment, it was found that the instance name should remain the same between the golden and revised netlists. The goal of this experiment was to further analyze how ECO would work if the instance name was kept the same but its functionality was changed. The experiment was conducted by naming an AND gate and an OR gate instance in the golden and revised netlists, respectively, as G1. This resulted in an error that no spare OR gate was found in the design, when the ECO was run. This was further analyzed in another experiment when a spare OR gate was added to the golden netlist as shown below.

```

//golden netlist

module TRIAL_CHIP(....);

AND2X1 G1 .....

OR2X1 G2 .....

endmodule

```

```

//revised netlist

module TRIAL_CHIP(....);

OR2X1 G1 .....

endmodule

```

Realizing that an OR gate with instance name G1 should be there in the final design, ECO checked gate G1 in the golden netlist for an OR gate, but found it to be an AND gate. It then took a spare OR gate and named that as G1 while renaming the AND gate as G1\_SPARE. This '\_SPARE' suffix is a default prefix which is added to all the freed cells. The user has the ability to provide a different suffix as well. The final generated netlist was as following.

```

//final ECO generated

netlist

module TRIAL_CHIP (....);

OR2X1 G1 .....

AND2X1 G1_SPARE...

endmodule

```

## 2.2.4 Implementing Full Design Using Unconnected Spare Cells

The goal of this experiment was to implement the complete functionality of the design with ECO only. In the golden netlist, enough spare gates were given to implement a MUX, but without any connection between the spare gates. In the revised netlist, a MUX was given, with completely different instance names from the golden netlist.

```

//golden netlist

//revised netlist

module TRIAL_CHIP (a,b,sel,y);

module TRIAL_CHIP (a,b,sel,y);

AND2X1 G1 ....

AND2X1 M1 (a, sel, a1)

AND2X1 G2 ....

M2 (sel, sel_bar)

INVX1

AND2X1 M3 (b, sel bar, b1)

AND2X2 G3 ....

OR2X1 M4 (a1, b1, y)

AND2X2 G4 ....

OR2X1 G5 ....

endmodule

OR2X2 G6 ....

INVX1

G7 .....

INVX2

G8 ....

endmodule

```

As expected, ECO exited with the error – 'Design must be placed before running ECO', because M1, M2, M3, and M4 were not present in the golden netlist.

Another experiment was run to overcome this error by keeping the same instance names between the golden and revised netlists. However, the logic functionalities for the same instance name could be different between the golden and revised netlists, as shown below.

```

//golden netlist

//revised netlist

module TRIAL_CHIP (a,b,sel,y);

module TRIAL_CHIP (a,b,sel,y);

AND2X1 G1 ....

AND2X1 G1 (a, sel, a1)

AND2X1 G2 ....

INVX1

G2 (sel, sel bar)

G3 ....

OR2X1

AND2X1 G3 (b, sel_bar, b1)

G4 (a1, b1, y)

INVX1

G4 .....

OR2X1

endmodule

endmodule

```

When ECO was run, it successfully implemented the same functionality as the revised netlist by only re-routing the design without changing the base layer. The final generated netlist was as following.

```

// final ECO generated netlist

module TRIAL_CHIP (a, b, sel, y);

AND2X1 G1 (a, sel, a1);

INVX1 G2 (sel, sel_bar)

AND2X1 G3 (b, sel_bar, b1)

OR2X1 G4 (a1, b1, y)

endmodule

```

# 2.2.5 Implementing Modified Design

In the previous experiment, it was found that ECO was able to implement the full design using unconnected spare cells. Another experiment was designed to verify cases where there might be some functionality in the initial golden netlist but which needs to be changed to a completely different design. The capability of ECO in this scenario was tested by providing an already routed design as the golden netlist, and another design in the revised netlist, as shown below.

```

//golden netlist

module TRIAL_CHIP (a,b,sel,y);

G1 (a, p);

INVX1

INVX1

G2 (b, q);

INVX1

G3 (sel, r);

INVX1

G4 (sel, y);

AND2X1 G5

... .

AND2X1 G6

AND2X2 G7

AND2X2 G8

OR2X1

G9

... .

OR2X2

G10 ....

INVX1

G11 .....

INVX2

G12 ....

endmodule

```

```

// revised netlist

module TRIAL_CHIP (a,b,sel,y);

AND2X1 G1 (a, sel, a1);

INVX1 G2 (sel, sel_bar)

AND2X1 G3 (b, sel_bar, b1)

OR2X1 G4 (a1, b1, y)

endmodule

```

In this experiment, ECO was able to implement the revised design using the spare and freed cells from the golden netlist. The generated netlist is shown below with the gates that were finally used to implement the design, shown in purple. The gates that have SPARE as the suffix are the freed cells.

```

// final ECO generated netlist

module TRIAL_CHIP (a, b, sel, y);

G1_SPARE ....

INVX1

G2_SPARE ....

INVX1

INVX1

G3 SPARE ....

G2 (sel, sel_bar)

INVX1

AND2X1 G1 (a, sel, a1);

AND2X1 G3 (b, sel_bar, b1)

AND2X2 G7_SPARE ....

AND2X2 G8_SPARE ....

G4 (a1, b1, y)

OR2X1

OR2X2

G10_SPARE ....

G11_SPARE ....

INVX1

INVX2

G12_SPARE ....

endmodule

```

It can be inferred from this experiment that each cell was taken from the revised netlist one by one, by ECO. If ECO was unable to locate an instance with the same name in the golden netlist as the picked cell, it exited with an error that design must be placed before running ECO. If it was able to find a gate with the same instance name, then it would check its functionality, and use the cell in the final design only if the functionality matched with that that of the cell in the revised netlist. If the functionalities did not match, then ECO would replace the cell with an available spare cell of the desired functionality and add a suffix (\_SPARE) to the name of this freed cell. Finally, after doing this process for all the cells in the design, ECO would re-route the design without changing the base layer.

# 2.2.6 Physically Aware Design Optimization

From the above experiments, it was also concluded that ECO had the capability to implement the functionality of the full design even if there was no connectivity in the initial design. The next step was to investigate the optimality of the design implementation by ECO. For example, for optimal implementation, ECO should select the closest spare cell, among all spare cells of the same type. This capability was tested by giving the same golden and revised netlists, as in the previous experiment. One AND gate was added to the golden netlist to check if ECO picked the closer AND gate or not.

Based on the generated re-routed design, it was found that ECO picked the closer AND gate and did not use the AND gate located farther away. Hence, it could be concluded that ECO was able to achieve physically aware design optimization.

## 2.2.7 Gate-Size and V<sub>T</sub> Aware Design Optimization

The goal of this experiment was to find whether ECO could do gate sizing or swapping of cells with different  $V_T$ , within the available spare cells. In this experiment, several spare cells with different drive strength were specified as the golden netlist. In the revised design, an un-optimized MUX design was given.

```

//golden netlist

// revised netlist

module TRIAL_CHIP(a,b,sel,y);

module TRIAL_CHIP (a, b, sel, y);

INVX1

G1 ....

AND2X1 G1 (a, sel, a1);

G2 (sel, sel_bar)

INVX1

G2 ....

INVX1

INVX1

AND2X1 G3 (b, sel_bar, b1)

G3 ....

OR2X1

G4 (a1, b1, y)

INVX1

G4 ....

endmodule

AND2X1 G5

....

AND2X1 G6

AND2X2 G7

AND2X2 G8

....

OR2X1

G9

OR2X2

G10 ....

INVX1

G11 .....

G12 ....

INVX2

endmodule

```

ECO successfully routed the design based on the revised netlist. It also optimized the design by picking closer cells, but did not optimize the timing path by picking cells of different drive strength. The generated netlist was as following.

```

// final ECO generated netlist

module TRIAL_CHIP (a, b, sel, y);

G1_SPARE ....

INVX1

G2_SPARE ....

G3_SPARE ....

INVX1

INVX1

G2 (sel, sel_bar)

AND2X1 G1 (a, sel, a1);

AND2X1 G3 (b, sel_bar, b1)

AND2X2 G7 SPARE ....

AND2X2 G8_SPARE ....

OR2X1

G4 (a1, b1, y)

OR2X2

G10_SPARE ....

INVX1

G11_SPARE ....

G12_SPARE ....

INVX2

endmodule

```

Even though spare cells of different drive strengths were available to the ECO, the cell types in the final generated netlist and the revised netlist were the same. Hence, it can be concluded from above experiment that ECO did not change the flavor of the cell and treated the cell's drive strength as golden.

#### 2.2.8 Conclusion

The above experiments reveal that the ECO has two requirements. The first requirement is that the gates needed in the new netlist should be present in the golden netlist as well. The gates could either be spare cells or used in the golden design. The second requirement is that the names of the instances in the new netlist must match the name of any one instance in the golden netlist, irrespective of the functionality or physical location of that instance. After meeting these requirements, ECO uses the spare cells and does re-routing to achieve the correct functionality.

From the optimization point of view, ECO successfully achieved physically aware optimization and picked the spare cells that were closer. However, it did not optimize the

timing path by gate sizing the cells or swapping the spare cells. It did not consider or optimize the drive strength of the cells and treated it as golden.

#### 2.3 CONFORMAL ECO

Based on the previous experiments with ECO, it was observed that ECO is a good candidate to implement the full functionality of the design. Its ability to optimize physical locations while picking the cells is a useful feature for this project. At the same time, ECO had a limitation that it would not optimize the design by gate sizing or swapping different  $V_T$  cells. This feature is extremely important for this project to enable the optimization of a high performance or low power design.

In order to overcome this limitation, a new flow was considered with Conformal ECO [19]. The Conformal ECO flow was setup by loading the golden and revised designs, that had already been flattened and uniquified. The option to add pin constraints was also added to the flow, to allow the constraint of a constant value for scan chains. Next, the logical equivalence of the golden and revised netlist was conducted at all the comparison points and a patch file was generated with all the differences. This patch file would be used to modify the golden netlist into the revised netlist.

After the patch file was generated, the list of spare cells was also provided. In the absence of any functionality in the golden design, all the cells were spare and indicated with the wildcard '\*'. Along with the spare cell list, the unique physical location of each spare cell was also given through a 'def' file. This would allow the tool to optimize the design based on the physical location of each individual spare cell. After both, the patch file and spare cells list had been provided, the patch file was optimized based on the available spare cells and their physical coordinates. The constraint file was also provided

in this step to allow the tool to know the timing constraints of the design. Conformal ECO uses the RTL Compiler (RC) to optimize the design. After doing the optimization, Conformal ECO generated the spare cell mapping file (swapcells.tcl) which mapped the spare cells to those cells that were used to implement the revised design. This spare cell mapping file would later be needed in the Encounter Digital Implementation (EDI) flow in order to re-route the design and conduct the physical design of the generated netlist.

# 2.3.1 Gate-Size and V<sub>T</sub> Aware Design Optimization

The flow described above was run to see if Conformal ECO would be able to optimize the design by doing gate sizing. The golden netlist that was provided to the Conformal tool had a number of spare cells with different drive strengths. The revised netlist had a design of a MUX, which could be further optimized by gate sizing. The timing report and timing slack of the critical path, before and after running Conformal ECO based optimization, was as following.

| Pin                | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Fanout | Load<br>(fF) |    | Delay<br>(ps) | Arrival<br>(ps) |   |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|----|---------------|-----------------|---|

| (clock vclk1)      | launch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |              |    |               | 0               | F |

| (dtmf.sdc line 19) | ext delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |              |    | +5000         | 5000            | P |

| s                  | in port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3      | 9.0          | 0  | +0            | 5000            | F |

| cfm eco patch 1/s  | 5 Table 1 Tabl |        |              |    |               |                 |   |

| m 4 SPARE/A        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |              |    | +0            | 5000            |   |

| m 4 SPARE/Y        | INVX1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1      | 2.0          | 18 | +19           | 5019            | F |

| m 2 SPARE/B        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |              |    | +0            | 5019            |   |

| m 2 SPARE/Y        | AND2X1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1      | 2.7          | 49 | +120          | 5139            | F |

| m 3 SPARE/B        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |              |    | +0            | 5139            |   |

| m 3 SPARE/Y        | OR2X1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1      | 2.0          | 50 | +148          | 5286            | F |

| m 5 SPARE/D        | DFFX1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |              |    | +0            | 5286            |   |

| m_5_SPARE/CK       | setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |              | 0  | +162          | 5448            | R |

| (clock vclk1)      | capture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |              |    |               | 5500            | F |

Cost Group : 'vclk1' (path\_group 'vclk1')

Timing slack: 52ps

Start-point : s

End-point : cfm eco patch 1/m 5 SPARE/D

Figure 10: Timing Report – Before Running Conformal ECO Optimizations

| Pin                | Туре      | Fanout          |      | Slew<br>(ps) | Delay<br>(ps) | Arrival<br>(ps) |   |

|--------------------|-----------|-----------------|------|--------------|---------------|-----------------|---|

| (clock vclk1)      | launch    |                 |      |              |               | 0               | R |

| (dtmf.sdc line 19) | ext delay |                 |      |              | +5000         | 5000            | R |

| s                  | in port   | 3               | 10.3 | 0            | +0            | 5000            | R |