## **Body Bias Generator Design for Ultra-Low Voltage Applications in FDSOI Technology**

A Master's Thesis

Submitted to the Faculty of the

Escola Tècnica d'Enginyeria de Telecomunicació de Barcelona

Universitat Politècnica de Catalunya

by

**Kenneth Palma Carmona**

In partial fulfilment of the requirements for the degree of MASTER IN ELECTRONIC ENGINEERING

**Advisor: Francesc Moll**

Barcelona, October 2019

## <u>Title of the thesis:</u> Body Bias Generator Design for Ultra-Low Voltage Applications in FDSOI Technology

Author: Kenneth Palma

Advisor: Francesc Moll

## Abstract

This thesis presents the derivation and validation processes of analytical models describing the dynamic and steady-state behaviors of CC-CP switched capacitor converters. The effects of FDSOI components in the implementation of such circuits is also addressed, studying their impact as compared to ideal models. Finally, the layout of a CMOS CC-CP in 28-nm UTBB-FDSOI technology is designed and tested against predicted functionality.

## Acknowledgements

I wish to extend my thanks to Prof. Moll, whose unrelenting correction process and patience have been fundamental to shape this thesis into something more comprehensible to the casual (and avid) reader.

Also, I want to thank Dr. Barajas for his help and teachings during the layout design process. It would have been unfeasible otherwise.

## Contents

| Abstract    |       |                                                                                   | 2    |

|-------------|-------|-----------------------------------------------------------------------------------|------|

| Acknowle    | edgei | ments                                                                             | 3    |

| List of Fig | gures |                                                                                   | 6    |

| List of Ta  | bles. |                                                                                   | 8    |

| 1. Intro    | oduct | tion                                                                              | 9    |

| 1.1.        | Tech  | nnological trends and FDSOI                                                       | 9    |

| 1.2.        | Ultr  | a-Low Voltage and Energy Harvesting                                               | . 10 |

| 1.3.        | Mot   | ivation and outline of the thesis                                                 | . 11 |

| 2. Ove      | rview | v of the Cross-Coupled Charge Pump circuit                                        | . 12 |

| 2.1.        | Prin  | ciples of Switched-Capacitor Converters                                           | . 12 |

| 2.2.        | Ope   | ration of the CC-CP                                                               | . 14 |

| 2.3.        | Cha   | rge transfer equations:                                                           | . 16 |

| 3. Disc     | rete- | Time State-Space Model                                                            | . 20 |

| 3.1.        | Proc  | cedure to derive the Discrete-Time State-Space Model                              | . 20 |

| 3.2.        | Para  | asitic capacitances effects on the dynamic model                                  | .23  |

| 3.2.        | 1.    | Parasitic capacitances impact on voltage gain:                                    | .23  |

| 3.2.        | 2.    | Parasitic effects on topology dynamics:                                           | .26  |

| 3.3.        | Dyn   | amic Model Validation:                                                            | .26  |

| 4. Stea     | idy-S | tate Analysis: mean voltage values                                                | .30  |

| 4.1.        | Mea   | an Voltage Value Validation                                                       | .31  |

| 5. Stea     | idy-S | tate Analysis: Thèvenin Model and Ripple approximation.                           | .34  |

| 5.1.        | Resi  | stive losses – CC-CP equivalent resistance.                                       | .34  |

| 5.1.        | 1.    | Fast vs Slow Switching limit                                                      | .35  |

| 5.1.        | 2.    | Equivalent resistance of a CC-CP of an arbitrary number of stages                 | .36  |

| 5.2.        | Para  | asitic Capacitances effect on the output voltage                                  | .42  |

| 5.3.        | Thè   | venin Equivalent:                                                                 | .43  |

| 5.4.        | Thè   | venin Equivalent validation                                                       | .45  |

| 5.4.        | 1.    | Effect of parasitic capacitances                                                  | .45  |

| 5.4.        | 2.    | Equivalent resistance                                                             | 46   |

| 5.5.        | Ripp  | ble Approximation                                                                 | .49  |

| 5.5.        | 1.    | Ripple equations validation                                                       | 52   |

| 6. FDS      | OI im | plementation                                                                      | 53   |

| 6.1.        |       | igning a test-bench / Experimental setting for the empirical analysis of voltage- |      |

| depen       | dent  | capacitors                                                                        |      |

| 6.1.        | 1.    | Lvtnfet / lvtpfet – Capacitive behavior                                           | 57   |

| 6            | 5.1.2.           | Egncap Behaviour5                                                                                                 | 9 |

|--------------|------------------|-------------------------------------------------------------------------------------------------------------------|---|

| 6            | 5.1.3.           | Effect of Voltage Dependent Fly-Capacitors                                                                        | 1 |

| -            | 5.1.4.<br>values | Algorithm for the determination of the Thèvenin Voltage and capacitance<br>of voltage dependent capacitors6       | 4 |

| 6.2.<br>idea |                  | xploring the behavior of Low Voltage Threshold FETs as resistive switches in an<br>I test-bench                   | 8 |

| 6            | 5.2.1.           | LVTFET empirical analysis. Test-Benches and procedures                                                            | 8 |

| -            | 5.2.2.<br>esisti | Thèvenin equivalent validation procedure in an implementation with LVTFETs a ve switches                          |   |

| 7. L         | ayou             | t design                                                                                                          | 2 |

| 7.1.         | . S              | chematic results, open circuit configuration:8                                                                    | 6 |

| 7.2.         | . S              | chematic results, with load:8                                                                                     | 7 |

| 7.3.         | . L              | ayout, open circuit configuration                                                                                 | 8 |

| 7.4          | . L              | ayout, loaded9                                                                                                    | 0 |

| 8. C         | Conclu           | usions9                                                                                                           | 3 |

| Annex        | (es              |                                                                                                                   | 5 |

| Ger          | nerali           | zed forms of Dynamic and Steady-State Models (including parasitics)                                               | 5 |

| e            | Gener            | alized form of the mean voltage9                                                                                  | 5 |

|              |                  | nic model expansion. Consideration of Inequal Capacitors, Inequal Time constants,<br>luction of parasitic effects | 6 |

| Scri         | ipts             |                                                                                                                   | 8 |

| C            | Dynan            | nic Model9                                                                                                        | 8 |

| V            | /oltag           | ge dependent capacitors                                                                                           | 0 |

| Net          | list La          | ayout Extraction                                                                                                  | 2 |

| Biblio       | graph            | ıy11                                                                                                              | 0 |

## List of Figures

| Fig. 1.1: Flipwell FDSOI transistor structure. The flipwells allow the NMOS and PMOS              |      |

|---------------------------------------------------------------------------------------------------|------|

| transistors to be biased through the BBnmos and BBpmos terminals with positive and negat          | ive  |

| voltage values respectively (forward body biasing). [4]                                           | . 10 |

| Fig. 1.2: Prospective increase in IoT devices.[5]                                                 | . 10 |

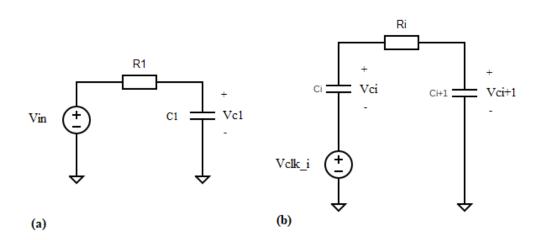

| Fig. 2.1: 1-stage equivalent Dickson Pump (charge doubler). A) General Topology. b) Phase 1       | 1, C |

| charging. C) Phase 2, C discharging with boosted voltage                                          | . 13 |

| Fig. 2.2: 1-Stage CC-CP                                                                           | . 14 |

| Fig. 2.3: Clock signals governing the behavior of CC-CP                                           | . 14 |

| Fig. 2.4: 2-Stage CC-CP schematic representation. Clock 2 is active high                          | . 15 |

| Fig. 2.5: a) Charging topology of the first fly-capacitor. B) Discharging topology of fly-capacit | or   |

| i, charging topology of fly-capacitor (i+1).                                                      | . 16 |

| Fig. 2.6: Schematic representation of one branch of a 3-stage CC-CP with resistive                |      |

| load                                                                                              | . 17 |

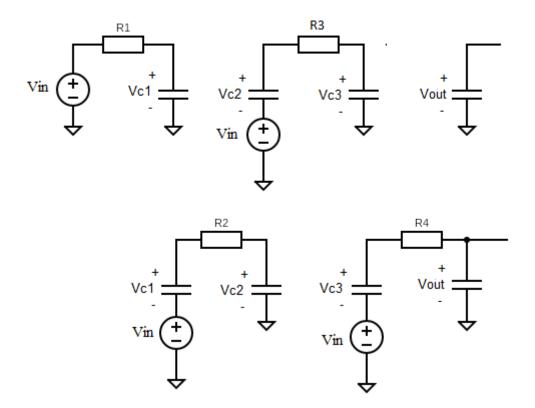

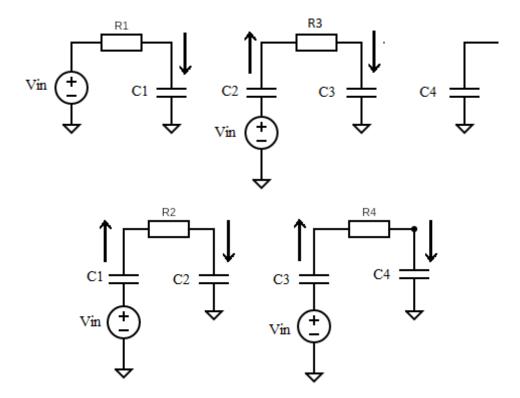

| Fig. 3.1: Circuit topologies during the first semi-period of operation. Bottom) Topologie         | es   |

| during the second semi-period                                                                     | . 21 |

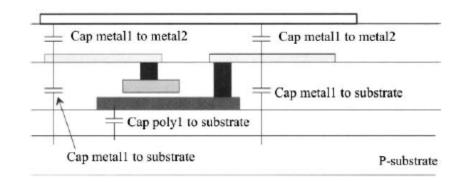

| Fig. 3.2: : [From Baker et al.]: Cross-sectional view of a capacitor implemented with             |      |

| VLSI technology, including the various sources of parasitic capacitances                          | . 23 |

| Fig. 3.3: Topology during a charging semi-period. The main capacitor lies in parallel             |      |

| with the equivalent parasitic capacitances.                                                       | . 24 |

| Fig. 3.4: Topology during a discharging semi-period. The parasitic capacitances are n             | not  |

| directly affected by the inverter.                                                                | . 24 |

| Fig. 3.5: Parasitic Voltage Divider                                                               | . 25 |

| Fig. 3.6: CC-CP topologies with top-plate parasitic capacitances.                                 | . 26 |

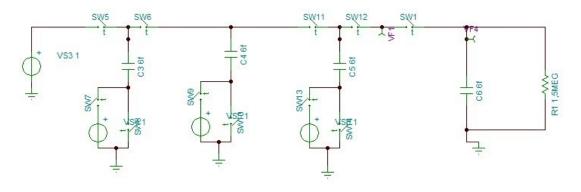

| Fig. 3.7: Schematic form used for simulation of the CC-CP.                                        | . 27 |

| Fig. 3.8: Dynamic Model Simulation. Top) Case1. Bottom) Case 2. The black line                    |      |

| corresponds to the Matlab script output. The red line, to the SPICE transient                     | . 28 |

| Fig. 4.1: Fly-capacitor waveforms in steady-state, Rload = $2M\Omega$ . Green: output capacitor.  |      |

| Black: fly-capacitor 3. Purple: fly-capacitor 2. Blue: fly-capacitor 1. The mean value is extract | ed   |

| in their respective charging period.                                                              | . 32 |

| Fig. 5.1: Switched-Capacitor circuit representation.                                              | . 34 |

| Fig. 5.2: Asymptotic and Real representations of equation (42), including their limits (from      |      |

| [12])                                                                                             | . 35 |

| Fig. 5.3: Schematic representation of a 3-stage CC-CP with resistive load                         | . 37 |

| Fig. 5.4: Charge exchange during phase 1 of operation.                                            | . 38 |

| Fig. 5.5: Charge exchange during phase 2 of operation                                             | . 38 |

| Fig. 5.6: Single Branch of a 3-Stage CC-CP. Top) Phase 1. Bottom) Phase 2. The black lines        |      |

| represent capacitive charging or discharging processes. We ignore discharging of Capacitor 4      | 1    |

| (load capacitor) as it does not discharge in a switched manner                                    | . 41 |

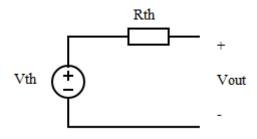

| Fig. 5.7: Thèvenin Equivalent of a CC-CP                                                          | . 43 |

| Fig. 5.8: Potential topologies of the Thèvenin Equivalent                                         | . 44 |

| Fig. 5.9: Thèvenin Equivalent under certain constraints (namely, the capacitive load is           | S    |

| much bigger than the fly-capacitors).                                                             | . 45 |

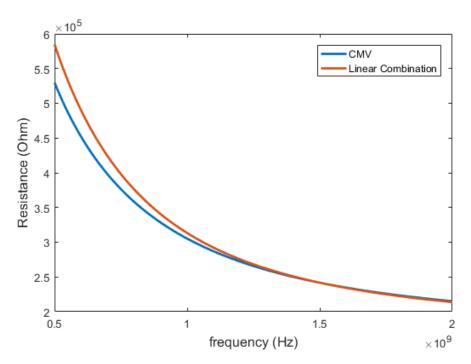

| Fig. 5.10: Resistance vs frequency comparison of the two resistance equations above               |      |

| presented. Blue- CMV method (equation (68)). Orange- Linear combination (equation (74)).          | . 48 |

| Fig. 5.11: Equivalent topology during one semi-period of operation at the load end                | . 49 |

|                                                                                                   |      |

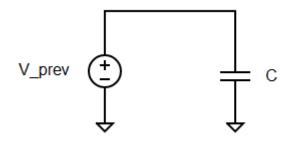

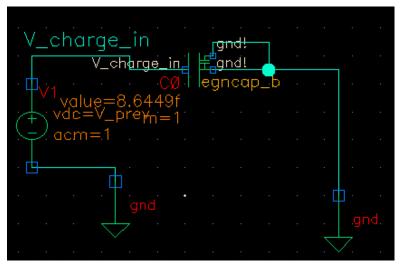

| Fig. 6.1: Equivalent DC topology of a charging capacitor in steady-state (V_prev:            |      |

|----------------------------------------------------------------------------------------------|------|

| Voltage of the Previous stage)                                                               | . 54 |

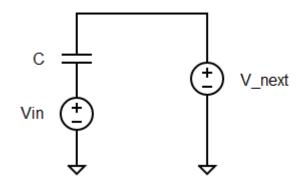

| Fig. 6.2: DC equivalent topology of a discharging capacitor                                  | . 55 |

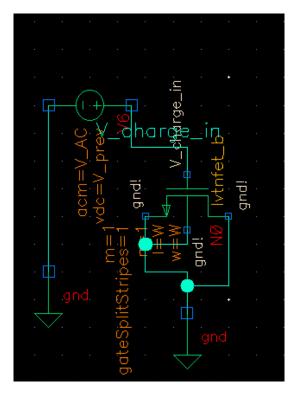

| Fig. 6.3: Testbench. Lvtnfet implemented as a capacitor, charging topology.                  |      |

| V_Charge_in represents V_prev (see Fig. 6.1)                                                 | . 55 |

| Fig. 6.4: Testbench. Lvtnfet implemented as a capacitor, discharging topology                | . 56 |

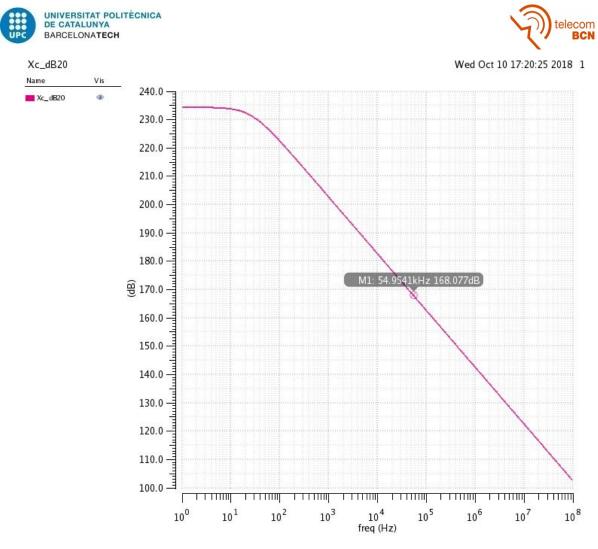

| Fig. 6.5: dB20(Xc)                                                                           | . 57 |

| Fig. 6.6: Lvtnfet Voltage-Capacitance Characteristic. Top) Charging topology. Bottom         | ו)   |

| Discharging topology                                                                         | . 58 |

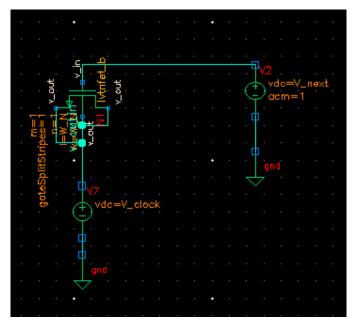

| Fig. 6.7: Egncap Test Bench. Charging topology                                               | . 59 |

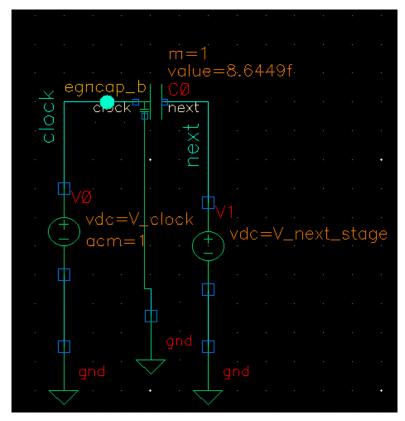

| Fig. 6.8: Egncap Test Bench. Discharging topology                                            | . 60 |

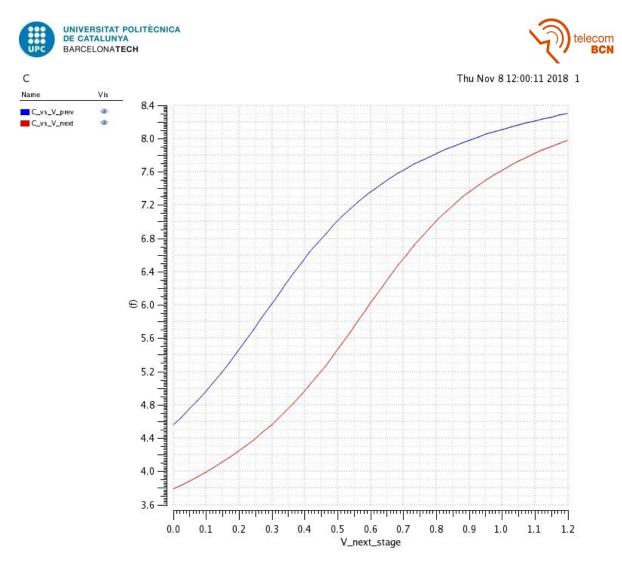

| Fig. 6.9: Egncap Voltage-Capacitance characteristcs. In blue, capacitance in the             |      |

| charging topology. In red, in the discharging topology                                       | . 61 |

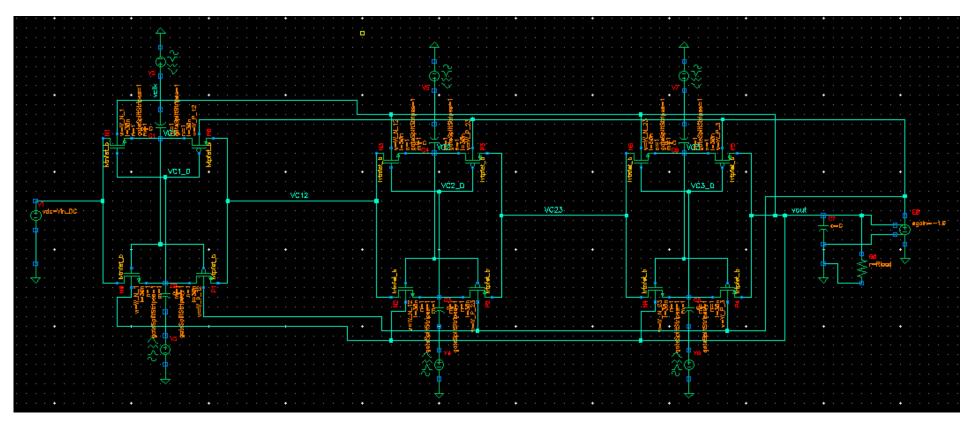

| Fig. 6.10: CC-CP Schematic implemented with FDSOI technology. The Back Bias is               |      |

| provided by the output node. In the case of the PMOS transistors, an ideal voltage           |      |

| buffer with gain -1 is used (slightly altering the real effects of the circuit). The clocks  | are  |

| implemented with out of phase square-wave generators                                         |      |

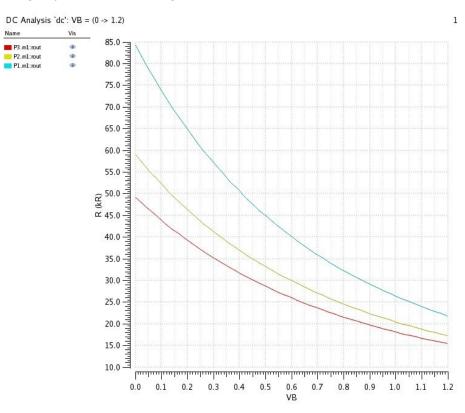

| Fig. 6.11: Transistor implemented as a resistance                                            |      |

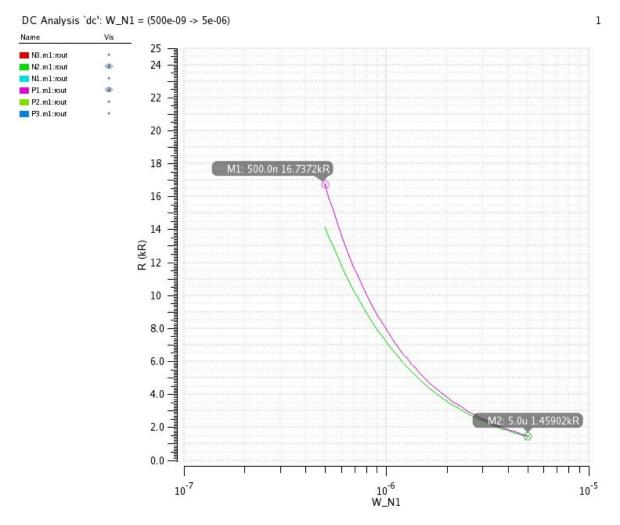

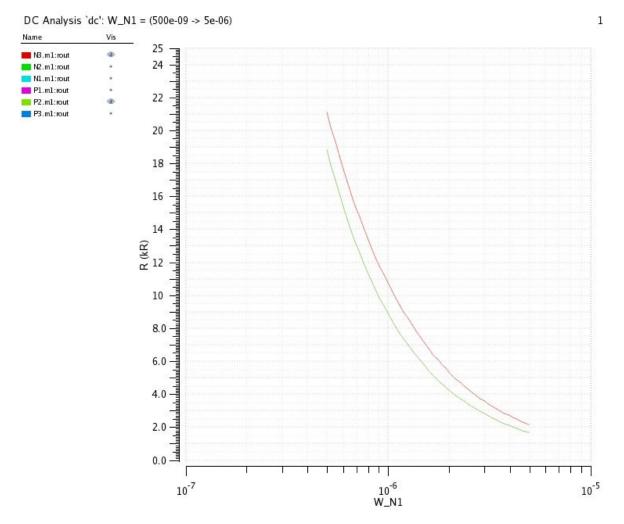

| Fig. 6.12: Resistance vs Back Bias voltage for different stages (PMOS transistors)           |      |

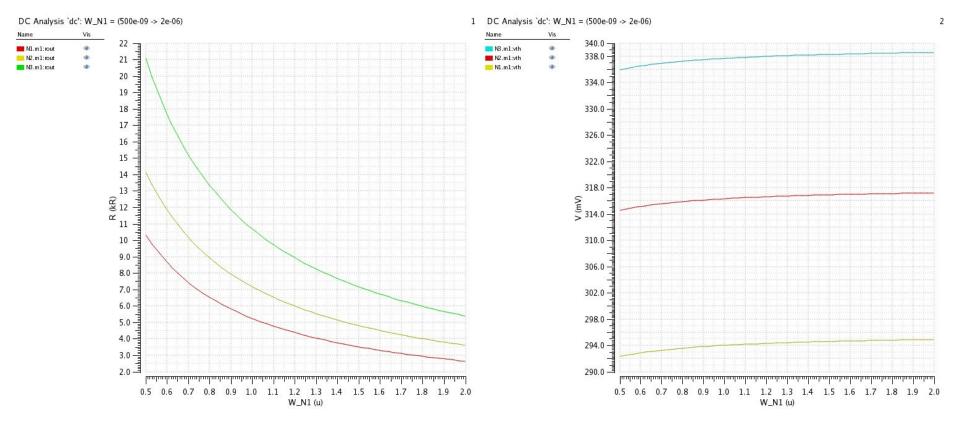

| Fig. 6.13: Resistance and Vth as a function of width for the NMOS under approximate          | ely  |

| operating conditions for all stages (N1 corresponding to the NMOS of the first stage         |      |

| and so on)                                                                                   |      |

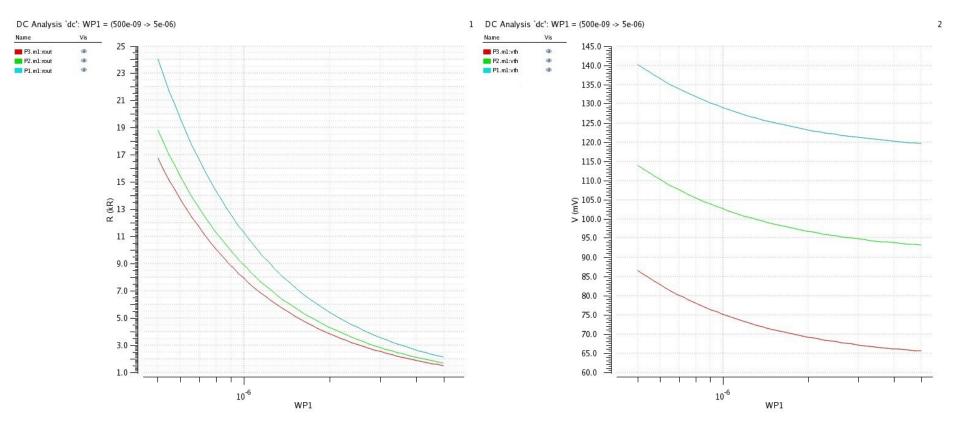

| Fig. 6.14: Resistance and Vth as a function of width for the PMOS under approximate          | əly  |

| operating conditions for all stages                                                          | . 73 |

| Fig. 6.15: Resistance vs Width of transistor pair N2-P1. In green, transistor N2. In purple, |      |

| transistor P1                                                                                | . 74 |

| Fig. 6.16: Resistance vs Width of transistor pair N3-P2. In pink, transistor N3. In green,   |      |

| transistor P2                                                                                |      |

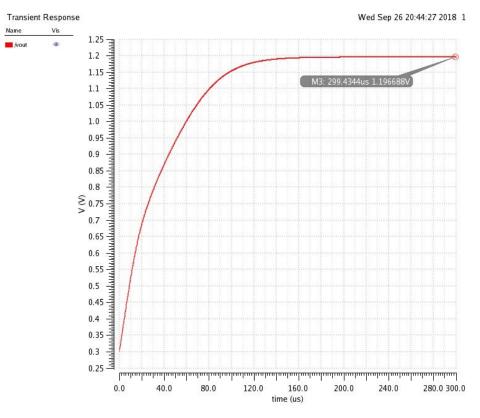

| Fig. 6.17: Open circuit transient depicting the output voltage                               | . 80 |

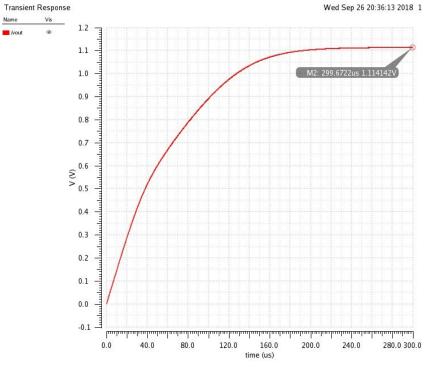

| Fig. 6.18: Loaded Circuit transient depicting the output voltage                             |      |

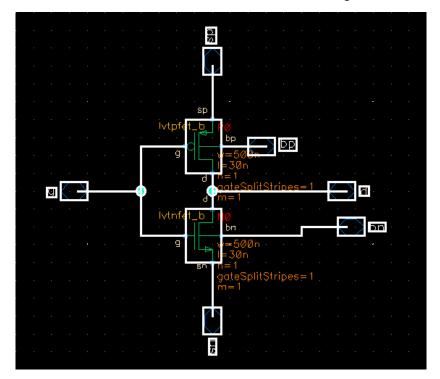

| Fig. 7.1: Schematic representation of the inverter cell.                                     |      |

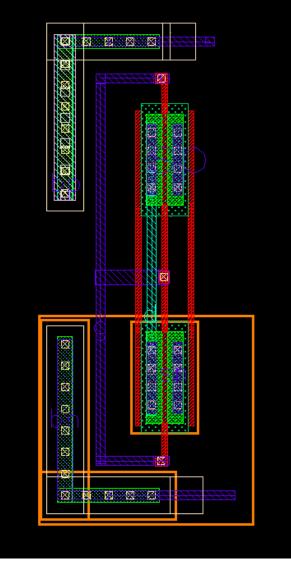

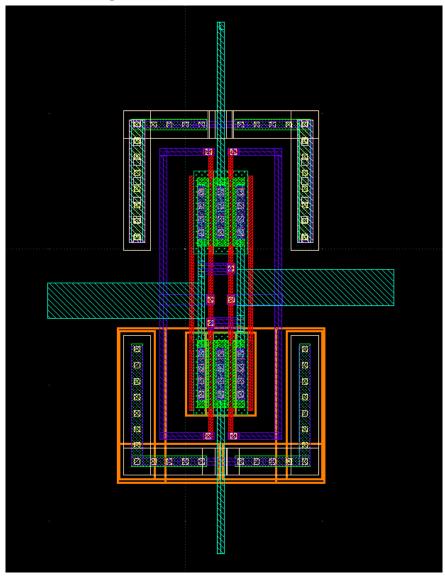

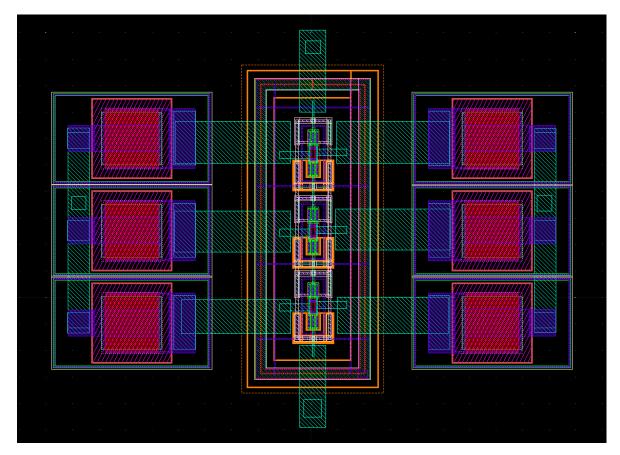

| Fig. 7.2: Left) Inverter Layout. Right) Cross-coupled inverter using a flipped copy of t     |      |

| initial inverter. Added lateral metal layers for connection to the capacitors                | . 83 |

| Fig. 7.3: Layout of a 3-stage CC-CP.                                                         | . 84 |

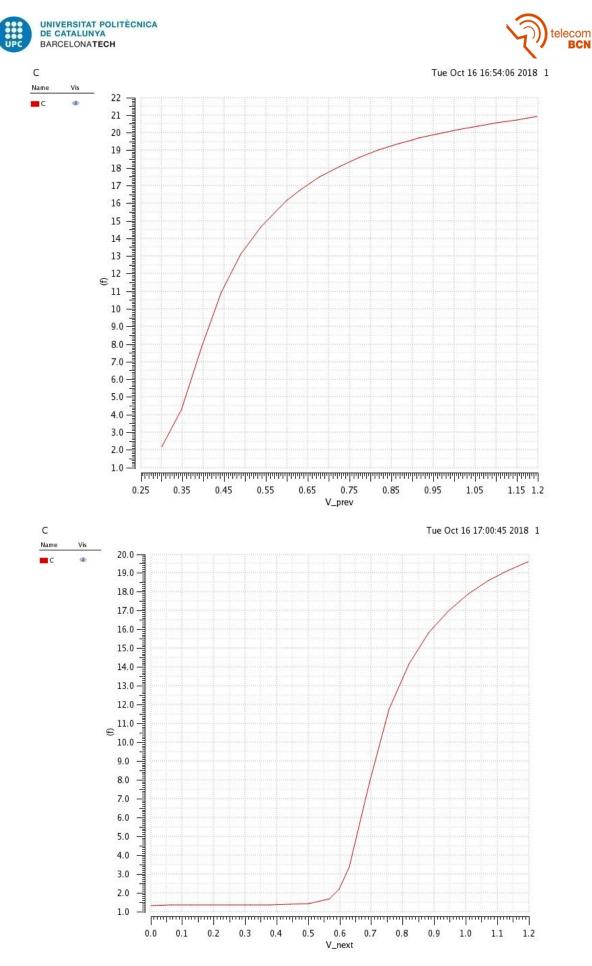

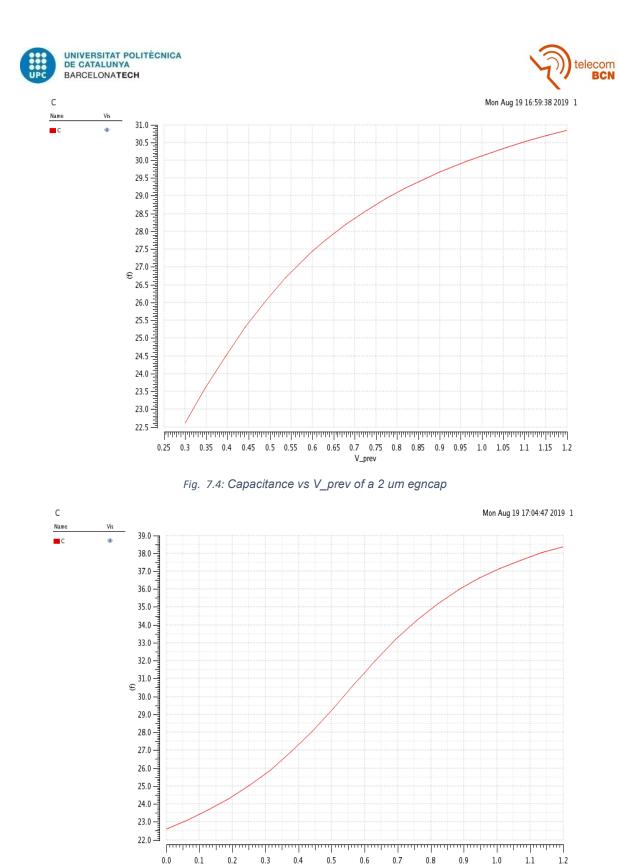

| Fig. 7.4: Capacitance vs V_prev of a 2 um egncap                                             | . 85 |

| Fig. 7.5: Capacitance vs V_next of a 2 um egncap                                             |      |

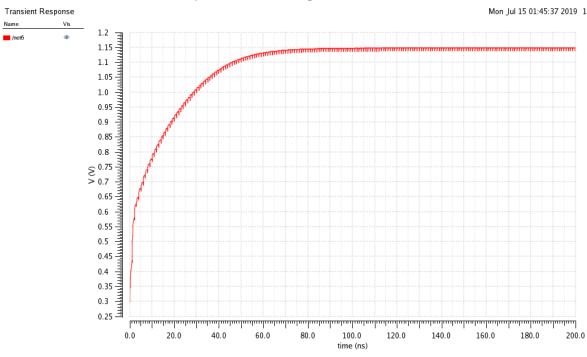

| Fig. 7.6: Transient simulation, open circuit, of the schematic. Overview                     | . 86 |

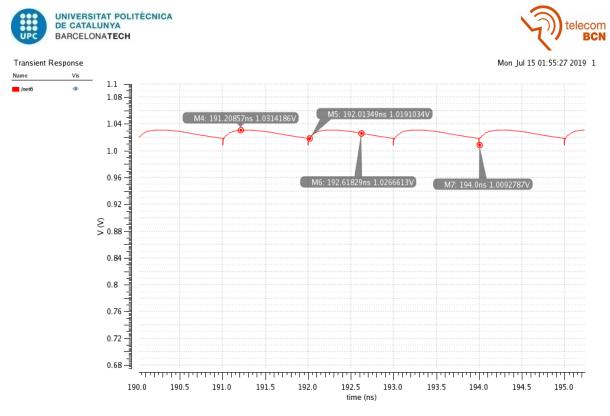

| Fig. 7.7: Transient Simulation, schematic, open circuit. Zoomed in steady-state              | . 87 |

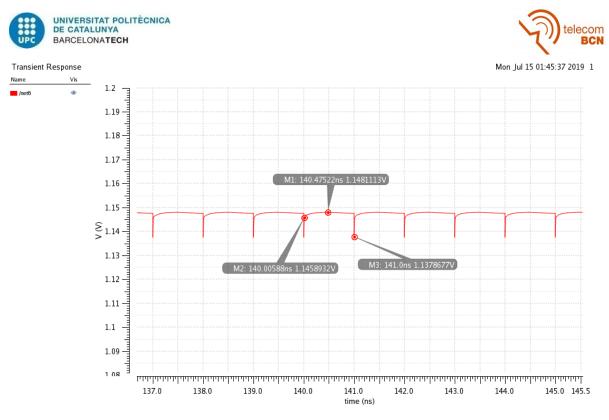

| Fig. 7.8: Transient Simulation, Schematic. Loaded. Overview                                  |      |

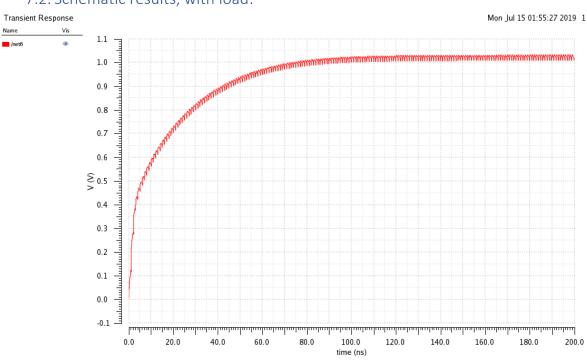

| Fig. 7.9: Transient Simulation, schematic. Loaded. Zoomed                                    | . 88 |

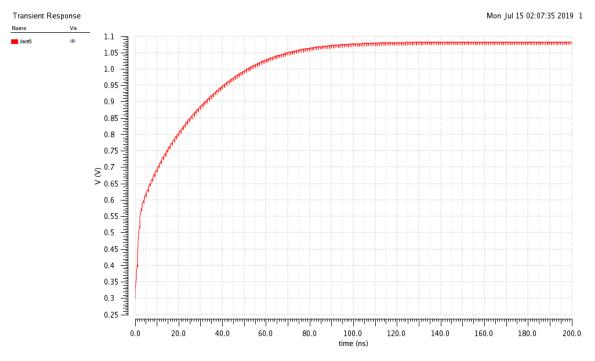

| Fig. 7.10: Transient simulation. Layout, open circuit. Overview                              | . 89 |

| Fig. 7.11: Transient Simulation. Layout, open circuit. Zoomed                                | . 90 |

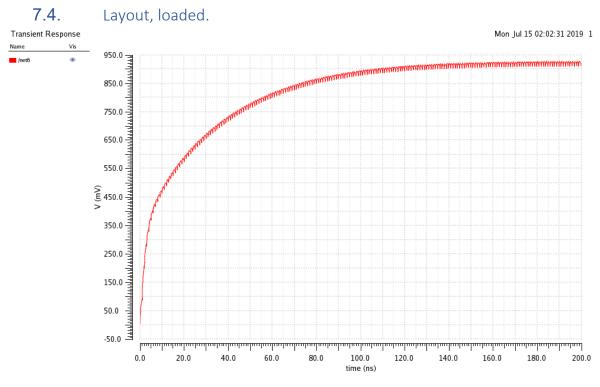

| Fig. 7.12: Transient Simulation. Layout, loaded. Overview                                    | . 90 |

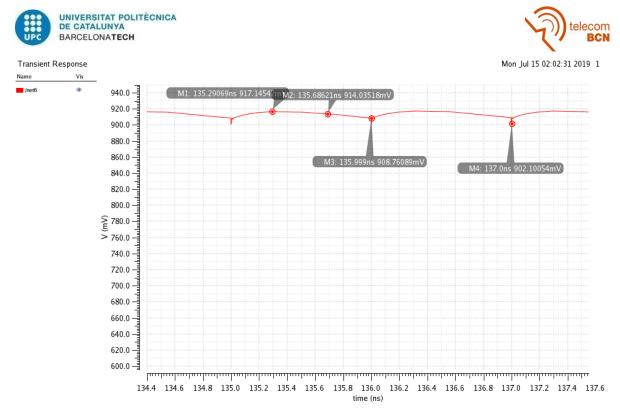

| Fig. 7.13: Transient Simulation. Layout, loaded. Zoomed                                      | . 91 |

## List of Tables

| TABLE I: Parameters used during the simulation of the Dynamic Model                           | 8 |

|-----------------------------------------------------------------------------------------------|---|

| TABLE II: Steady-State voltages achieved as a consequence of parasitics                       | 8 |

| TABLE III: Mean Voltage Values, Simulation Results       32                                   | 2 |

| TABLE IV: Mean Voltage Values, Equations Results       32                                     | 2 |

| TABLE V: Relative Error between simulation and equations                                      | 3 |

| TABLE VI : 3-stage CC-CP Equivalent Resistances Method Comparison (Charge                     |   |

| Multiplier Vector Method)                                                                     | 2 |

| TABLE VII: Parasitic capacitance effect summary4                                              | 5 |

| TABLE VIII: SPICE and equations result comparison of the Steady-Stage voltage under different | ; |

| current loads with RCMV4                                                                      | 7 |

| TABLE IX: SPICE and equations result comparison of the Steady-Stage voltage under different   |   |

| current loads with RThesis4                                                                   | 7 |

| TABLE X: Accuracy of distinct equivalent resistances in FSL operation                         | 8 |

| TABLE XI: SPICE and equations result comparison of the ripple under different current         |   |

| loads in SSL operation52                                                                      | 2 |

| TABLE XII: SPICE and equations result comparison of the ripple under different current        |   |

| loads in FSL operation52                                                                      | 2 |

| TABLE XIII: Transistors' width and resistances         79                                     | 9 |

| TABLE XIV: Schematic, open circuit results80                                                  |   |

| TABLE XV: Schematic, Loaded. Results88                                                        | 8 |

| TABLE XVI: Layout, open circuit. Results88                                                    |   |

| TABLE XVII: Layout. Loaded. Results                                                           | 1 |

## 1. Introduction

#### 1.1. Technological trends and FDSOI

Technological improvements, industrial trends and energy efficient management have always driven the direction of microelectronic design.

The reduction in size of microelectronic components, in an endeavor to achieve ever larger system complexity has merited, almost since its conception, a defined trend that became law (Moore's Law). In an effort to attain higher functioning speeds and ever decaying power consumption in digital circuits, billions of dollars are spent each year to reduce size, improve performance and reduce the cost of fabrication of transistors.

A reduction in transistor size is, however, accompanied by a myriad of challenges. Namely, a reduction in the channel length of MOS transistors leads to an increase of the electrical fields formed within the channel. As a consequence, the maximum voltage the device can withstand (breakdown voltage) is reduced with each technology reduction.

Also, as transistor size is reduced, more complex systems with a higher count of transistors can be implemented in the same die area. This leads to an overall increase of the power consumption, both dynamic and static.

Scaling the voltage supply then becomes a necessity both to allow functionality without surpassing the breakdown voltage and to reduce power consumption. In digital circuits, this reduction of the voltage supply produces a decreased Voltage overdrive (Vgs-Vth), which increases the equivalent switching resistance of transistors and limits the overall speed of the circuit.

To overcome these limitations, transistors must then be manufactured with lower Threshold voltages. But this presents other problems.

Both the reduction in channel length to sub-micron scales and the reduction of the Threshold voltage can significantly impact power losses due to leakage currents.

To overcome these limitations accompanied by size reduction, the last decades have seen the emergence of new technologies such as FIN-FETs and FDSOI transistors, with new "architectures" that provide solutions to the aforementioned problems.

FDSOI transistors in particular benefit from the addition of a fourth terminal that can be used to modify some of the properties of the transistors previously fixed during the manufacturing process.

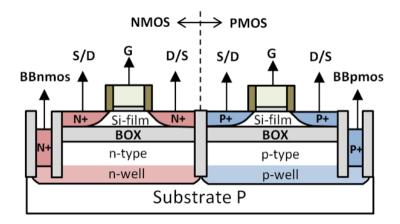

The addition of an insulating layer below the channel limits the width of the junctions' depletion layer and allows the use of an undoped channel (Fig. 1.1), significantly improving short-channel effects, leakage currents and variations of the Threshold voltage along the channel. The reduction of junctions' depletion layer width decreases junction capacitances as well, reducing dynamic power consumption. At the same time, the architecture of FDSOI transistors allows biasing through a fourth terminal. Controlling the voltage applied to this fourth terminal, the Threshold voltage can be modified outside the manufacturing process to a certain degree. This, in turn, can be used to alter the operational speed, current gain, leakage current and consumption in idle states in low voltage circuits or otherwise. [1][2][3]

Fig. 1.1: Flipwell FDSOI transistor structure. The flipwells allow the NMOS and PMOS transistors to be biased through the BBnmos and BBpmos terminals with positive and negative voltage values respectively (forward body biasing). [4]

#### 1.2. Ultra-Low Voltage and Energy Harvesting

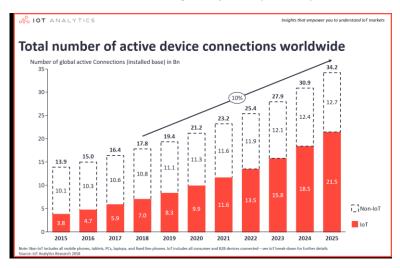

On the other hand, with various industrial sectors (automobile, medical, weather) benefiting from the technological trend emerging from the IoT, some estimations point to a doubling in IoT nodes in the following five years (Fig. 1.2).

Fig. 1.2: Prospective increase in IoT devices.[5]

The philosophy behind IoT nodes (either remote locations or minimum human intervention once installation is complete) goes hand by hand with minimum power consumption either by having low frequency of operation (the device is active only for short periods of time during long inactive periods), and/or by consuming the minimum possible power during operation, so as to maximize the available active life of the device.

This, in turn, leads to the potential application of energy-harvesting solutions that could be used to either completely power the device or extend its available active life before having to relay to human intervention to either change the battery or the device.

Energy harvesting, on the other hand, tends to produce low voltages, low power output, or both, which might not be readily suitable to power any active device, requiring the presence of intermediate power converters or voltage multipliers.

Power converters have been a key element of electronic design since its conception. However, their reliance on inductors has been and, in some ways, continues to be, a problem for microelectronic design, given their poor performance in integrated circuit. Instead, inductorless power converters (switched-capacitor converters) have become one of the most widely used devices for this purpose in IC design. Switched-capacitor converters have been proven to exhibit similar properties and behavior to inductive power converters.

#### 1.3. Motivation and outline of the thesis

The present study is part of research project funded by the MICINN ([Together] " DISPOSITIVOS, CIRCUITOS Y ARQUITECTURAS FIABLES Y DE BAJO CONSUMO PARA IOT", TEC2016-75151-C3-2-R (2016-2019)), where low voltage supply circuits are the focus of study, with implementation in FDSOI technology.

To improve or even allow the complete functionality of such circuits, a Back-biasing voltage higher to that of the supply voltage is needed, to be applied to the fourth terminal of the FDSOI transistors, thus decreasing the Threshold voltage of the transistors.

The objective of this study was to originally design a Cross-Coupled Charge Pump (CC-CP) [6] to perform this functionality. In the process of studying and analyzing the behavior of such circuits, a dynamical and steady-state models were derived to guide the design of such circuits in FDSOI technology (and otherwise).

As such, this thesis is a compendium of the models derived and the experiments followed to establish the validity of such models, presenting some design guidelines and a final design both with schematic and layout extraction.

This thesis is the culmination of a year-long project initiated during the first Semester of the academic year 2018-2019 through the Introduction to Research subject. Part of this work has been accepted for publishing as posters in two international conferences.[7][8]

## 2. Overview of the Cross-Coupled Charge Pump circuit

#### 2.1. Principles of Switched-Capacitor Converters

Power converters are ubiquitous components in most electronic systems, portable or otherwise, tailoring power management requirements between energy sources and circuits.

Traditionally, inductive power converters (IPC), in which the temporary energy storage between switching phases is carried out by inductors, have dominated the field of power electronics. Most courses on the subject of power electronics still focus solely on these types of converters.

DC-DC IPC have been extensively studied and modelled for the better part of the last century. They provide ideal power efficiencies of 100 %, step-up and step-down capabilities and can provide continuous Vout/Vin conversion ratios based on switching frequency.

However, as VLSI technologies continue to scale down, implementation of power converters with inductive components becomes challenging and expensive, given their complex scalability (reduced Q factor, parasitic components, bulk and adjacent vias coupling).

For this reason, and given the ease of implementation of capacitors in VLSI technologies, Switched-Capacitor converters can become the better alternative in power management of IC systems.

In Switched-Capacitor Converters (SCC), capacitors become the temporary energy storage components. Similarly to IPC, SCC use switches controlled by different clock phases to redirect the flow of energy between components at different phases of operation.

SCC also present step-up and step-down capabilities, but their conversion ratios are intrinsically tied to the topology of the circuit, and is presented in ratios of integer numbers (i.e. Vout/Vin $\rightarrow$  2/1, 3/1, 4/3, 5/8...)[9].

On the other hand, the intrinsic losses associated with the charging or discharging of capacitors limit even the ideal efficiency of these converters, although practical applications show their feasibility [10].

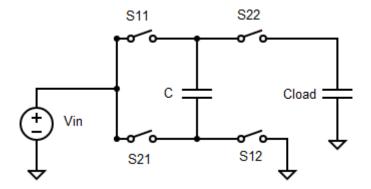

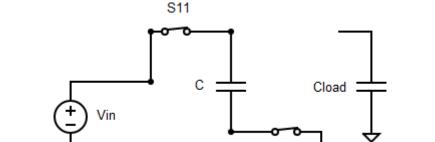

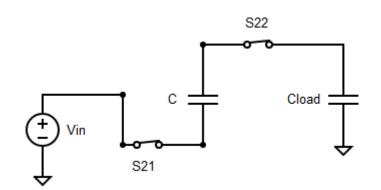

Fig. 2.1 shows a Switched Capacitor voltage doubler in the equivalent topology of a Dickson Charge Pump. During phase 1, the top plate of capacitor C is connected to the input voltage source, and receives some charge. During phase 2, the bottom plate of capacitor C is connected to the input voltage source. Cload receives some charge from capacitor C at a voltage that is the superposition of Vin and the voltage across the terminals of capacitor C. With enough cycles of operation, Cload is eventually charged to 2\*Vin.

S12

Fig. 2.1: 1-stage equivalent Dickson Pump (charge doubler). A) General Topology. b) Phase 1, C charging. C) Phase 2, C discharging with boosted voltage.

A Cross-Coupled Charge Pump (CC-CP) is a type of switched-capacitor converter, similar in operation to a Dickson Charge Pump. A CC-CP is an inductorless DC-DC boost converter that provides a voltage at the output N times higher than the voltage at the input, where N is an integer that depends on the topology (namely, on the number of stages of the circuit): The voltage at the output is boosted to n+1, where n is the number of stages of the circuit. It follows that:

$$N = \frac{V_{out}}{V_{in}} = n + 1 \tag{1}$$

The functionality of a CC-CP (Fig. 2.2) is based on transfers of charge of everincreasing voltage potentials between capacitors through a series of resistive paths governed by clock-controlled switches. These properties are more or less shared by all

switched-capacitor converters, and the analysis of the circuit follows the foundations of SC circuit analysis, with certain peculiarities.

Namely, the gate of the MOS transistors implemented as switches are directly tied to the top plate of the fly-capacitors. As subsequent analysis will show, this guarantees that the Vgs is constant across all transistors during circuit operation, meaning that the clock amplitude must not be tailored for stages where VD and VS are higher than the clock voltage.

#### 2.2. Operation of the CC-CP

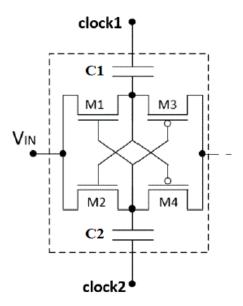

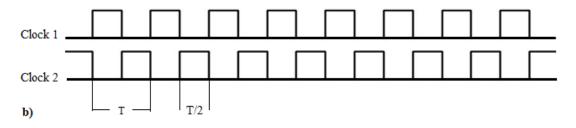

Fig. 2.2 depicts a 1-stage CC-CP. The circuit comprises 4 MOSFETs (2 NMOS and 2 PMOS) and 2 fly capacitors. Two non-overlapping clock signals are connected to the bottom plates of the fly capacitors. Each clock is active high during 50 % of the period of operation of the circuit. The clocks are operating at the same frequency, but with a 180 ° phase difference (Fig. 2.3).

The MOSFET transistors are implemented to operate as resistive switches. They present a large off resistance and a comparatively low on resistance. The switching is controlled by the aforementioned clock signals, by connecting the top plate of the capacitors to the gate of the transistors lying opposite to them.

Fig. 2.2: 1-Stage CC-CP

Fig. 2.3: Clock signals governing the behavior of CC-CP

When Clock 2 has a rising transition, the top plate of capacitor C2 will experience an initial voltage increase equal to the clock source amplitude, Vclk. This increase in voltage produces a decrease in the equivalent resistance of the NMOS transistor M1 lying opposite to C2 and, at the same time, increase the resistance of the PMOS transistor M3.

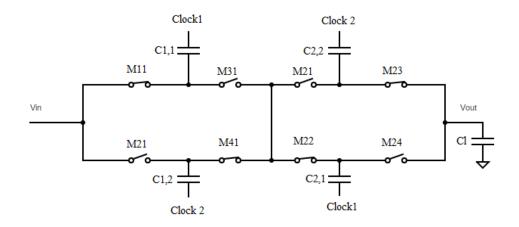

At the same time, as Clock1 has a falling transition, the top plate of capacitor C1 sees a decrease in voltage that produces the opposite effect on the NMOS transistor M2 (increasing its resistance) and on PMOS transistor M4 (producing a decrease in its resistance). This combined effect generates a series of high and low resistance paths that connect the capacitors to different nodes in the circuit, as depicted schematically in the form of open and closed switches in Fig. 2.4, depicting a 2-stage CC-CP.

Fig. 2.4: 2-Stage CC-CP schematic representation. Clock 2 is active high.

When a path of low resistance is created between two capacitors, the capacitor the bottom plate of which is connected to a clock which has experienced a rising transition will have, at the top plate, a voltage equal to the clock signal amplitude plus the voltage across the terminals of the capacitor. This allows the capacitor with its bottom plate connected to an inactive clock to be charged, in subsequent periods, to a higher voltage than the preceding capacitor. Thus, as previously stated, the circuit acts as a boost-converter.

Assuming that the impedances of the open switches are much higher than the impedances of the closed switches, from a current perspective, the circuit operates as a sequence of transfers of charge between capacitors. These charge transfers can be modeled as simple RC circuits once the pertaining topologies have been identified.

Observing Fig. 2.4, it is possible to identify different resistive paths between:

- The input voltage source and capacitor C1,1.

- Capacitor C1,2 and capacitor C2,1

- Capacitor C2,2 and the load capacitor.

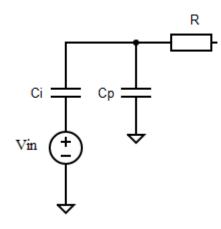

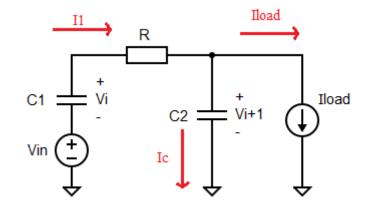

Careful consideration can lead to the observation that the last two resistive paths give rise to the same topology. Thus, a maximum of two different topologies arise during the circuit operation. These topologies are depicted in figure 5.

The first topology (Fig. 2.5.a) corresponds to the charging of the first fly capacitor by the input voltage source. In this topology, resistance R1 is comprises a single NMOS transistor. The second topology (Fig. 2.5.b) corresponds to the charging/discharging of any adjacent pair of capacitors. In this topology, resistance Ri comprises a series combination of 1 NMOS and 1 PMOS transistor. The final stage, where Ci+1 corresponds to the load capacitor Cload presents a resistance Ri formed by a single PMOS transistor (see Fig. 2.4)

*Fig. 2.5: a)* Charging topology of the first fly-capacitor. *B)* Discharging topology of fly-capacitor *i*, charging topology of fly-capacitor (*i*+1).

These topologies can be easily analyzed through Kirchoff Voltage Law (KVL) in the frequency domain to obtain equations that relate the changes in the fly capacitors voltage through charge transfer during one period of operation.

#### 2.3. Charge transfer equations:

In order to analyze the different topologies, various assumptions are taken with the aim of simplifying the procedure.

- The clocks are ideal and non-overlapping, with a period T and a duty cycle of 50 %.

- The clock signal amplitude (Vclk) is equal to the amplitude of the input voltage source (Vin).

- The MOSFETs are modeled as ideal switches in series with linear resistors.

- All fly-capacitors present the same capacitance. The load capacitor is also equal to the rest.

- There are no losses nor parasitic elements (These will be explored later).

These considerations lead to the ideal circuit depicted in Fig. 2.6, where the CC-CP has been simplified to depict a single path of current flow instead of the crossed, interwoven circuit with two parallel current paths.

*Fig. 2.6:* Schematic representation of one branch of a 3-stage CC-CP with resistive load.

With these considerations in mind and the topologies depicted in Fig. 2.5, reflecting the different sub-circuits in the Laplace domain, KVL can be applied. Focusing on the first topology we obtain:

$$-\frac{V_{in}}{s} + I_1 \left( R_1 + \frac{1}{Cs} \right) + \frac{V_1}{s} = 0$$

(2)

$$I_1(s) = \frac{V_{in} - V_1}{R_1} * \left(\frac{1}{s + \frac{1}{R_1 C}}\right)$$

(3)

$$i_1(t) = \frac{V_{in} - V_1}{R} * e^{-\frac{t}{R_1 C}}$$

(4)

Analyzing the second sub-circuit yields the following results:

$$-\frac{V_{in}}{s} - \frac{V_i}{s} + I_2 * \left(R_i + \frac{1}{Cs} + \frac{1}{Cs}\right) + \frac{V_{i+1}}{s} = 0$$

(5)

$$I_2(s) = \frac{V_{in} + V_i - V_{i+1}}{R_i} * \frac{1}{s + \frac{2}{R_i C}}$$

(6)

$$i_2(t) = \frac{V_{in} + v_i - v_{i+1}}{R_i} * e^{-\frac{2t}{R_i C}}$$

(7)

If we integrate both equations, knowing that each sub-circuit is operative for T/2:

$\Delta Q_1 =$

TAT POLITÉCNICA

NYA

ATECH

$$\int_{0}^{\frac{T}{2}} i_{1}(t) * dt = \int_{0}^{\frac{T}{2}} \frac{V_{in} - V_{1}}{R_{1}} * e^{-\frac{t}{R_{1}C}} * dt = C(V_{in} - v_{1}) \left(1 - e^{-\frac{T}{2R_{1}C}}\right)$$

(8)

$$\Delta Q_{i} = -\int_{0}^{\frac{T}{2}} i_{2}(t) * dt = -\int_{0}^{\frac{T}{2}} \frac{V_{in} + v_{i} - v_{i+1}}{R_{i}} * e^{-\frac{2t}{R_{i}C}} * dt = -\frac{C(V_{in} + v_{i} - v_{i+1})}{2} \left(1 - e^{-\frac{T}{R_{i}C}}\right)$$

(9)

These equations represent the amount of charge that is transferred into capacitor 1 and from capacitor i respectively.

Alternatively, the equations can be expressed as voltage variations:

$$\frac{\Delta Q_1}{C} = \Delta V_1 \tag{10}$$

$$\frac{\Delta Q_2}{C} = -\Delta V_i = \Delta V_{i+1} \tag{11}$$

$$\Delta V_1 = (V_{in} - v_1) \left( 1 - e^{-\frac{T}{2R_1 C}} \right)$$

(12)

$$\Delta V_{i+1} = -\Delta V_i = \frac{(V_{in} + v_i - v_{i+1})}{2} \left(1 - e^{-\frac{T}{R_i C}}\right)$$

(13)

These two equations represent the increase or decrease in voltage across the terminals of a capacitor after one semi-period of operation.

They depend on the clock/input voltage amplitude, the current voltage across the terminals of the capacitors involved and a constant involving an exponential that depends on circuit parameters.

This last constant parameter is not equal between equations (12) and (13). In intermediate topologies, the discharging and charging capacitors form a series association (equation 5). Under the assumption that all capacitors are equal, the equivalent capacitance of intermediate stages is reduced to C/2. It is of interest to have equal RC time constants for all topologies, so the exponential parameter can be simplified in subsequent analysis.

Thus, notice that by reducing the resistance of the first stage R1 to half the value of Ri (R1 = Ri/2), equation (12) becomes:

$$\Delta V_1 = (v_{in} - v_1) \left( 1 - e^{-\frac{T}{2\frac{R_i}{2}C}} \right) = (v_{in} - v_1) \left( 1 - e^{-\frac{T}{R_iC}} \right)$$

(14)

If we design the resistance of the first stage to be R1=Ri/2 we can ensure some mathematical simplifications that facilitate further analysis. At the same time, the equivalent resistance of the rest of stages must be the same. ( $R_i = R, \forall i \neq 1$ ).

That way, the parameter

$\left(1-e^{-\frac{T}{R_iC}}\right)$

is the same for both equations (13) and (14). Note that, given the periodic nature of the circuit, this term, equal for all topologies, becomes a constant that depends exclusively on design parameters. This constraint massively simplifies the developing of the following analysis.

Given that this term appears through most part of the analysis and that once the equivalent resistance is fixed, the term becomes constant (under the assumed constraints), the  $R_i$  notation will be dropped from now on, and will be substituted by simply R.

$$\left(1-e^{-\frac{T}{RC}}\right)$$

## 3. Discrete-Time State-Space Model

#### 3.1. Procedure to derive the Discrete-Time State-Space Model

If the values of the voltage across the different capacitors' terminals are known at a given period kT, the equations above derived allows us to determine the value at period (k+1)T. Each capacitor experiences a charging and a discharging during a period of operation of the circuit. For an arbitrary fly-capacitor *i* (see Fig. 2.5), we can write:

$$V_{Ci}((k+1)T) = V_{Ci}(kT) + \Delta V_{charging} - \Delta V_{discharging}$$

(15)

The charging and discharging terms correspond to equations (13) and/or (14) and, as above stated, depend exclusively on design parameters in the form of a constant term and, more importantly, on the current state of the circuit.

If the different capacitor voltages at a given time are treated as state-variables, given some initial conditions, these equations allow us to predict the evolution of the statevariables in time.

These state-variables present a continuous time evolution, but the discontinuities introduced by the switching nature of the circuit would severely impact the linearity of a continuous time model. It is, therefore, much simpler to conceive the state-variables evolving in discrete increments of time.

This leads to the foundations of a discrete-time state-space entity that can predict the dynamics of the circuit.

Consider a time-invariant system as represented by the generalized discrete-time state-space equations of the form:

$$\boldsymbol{X}[K+1] = A * \boldsymbol{X}[K] + B * \boldsymbol{U}[K]$$

$$\boldsymbol{Y}[K] = C * \boldsymbol{X}[K] + D * \boldsymbol{U}[K]$$

(16)

Where:

- X[·] is the state vector, in this case representing the fly- and load capacitor voltages. It is an (2\*n+1)\*1 vector, where n is the number of stages.

- Y[·] is the output vector. In this case, a scalar (1\*1 vector) representing the load capacitor (output) voltage.

- U[.] is the input vector. The inputs signals are those of the input voltage source and the clocks. Under the assumptions presented (the input voltage and clock amplitudes are equal) this is a 1\*1 vector, constant in time.

- A[·] is the state matrix, relating the current values of the state-variables to those of the next period. It is an N\*N matrix.

- B[·] is the input matrix, an N\*1 matrix relating the current value of the input vector to the state of the next period. Since U[·] is a constant scalar, B

comprises constant parameters. In fact, both A and B are constant, time-invariant matrixes.

- C[·] is the output matrix, a 1\*N matrix.

- D[·] is the feedthrough matrix. In this case it is a zero matrix.

We wish to derive such a compact expression so as to be able to better analyze the properties of this circuit. We analyze a single branch of a CC-CP (Fig. 2.6) to showcase the procedure.

In order to do so, we divide each period into two separate sub-periods with their respective sub-circuits as depicted in Fig. 3.1. The components of the state vector are here represented as Vc1, Vc2, Vc3 and Vout.

*Fig. 3.1: Circuit topologies during the first semi-period of operation. Bottom) Topologies during the second semi-period.*

We take as an example the voltage variations of capacitor C1 (Vc1) during the first semi-period of circuit operation (Fig. 3.1.top). It can be assumed that Capacitor C1 already has some charge stored, and that the circuit is at its *Kth* period after start-up. Capacitor C1, connected to the input voltage source, will gain some additional charge. After the first semi-period has been completed, the voltage across the terminals of C1 will be:

$$V_{C1}\left[K + \frac{1}{2}\right] = V_{C1}[K] + \Delta V_{C1}$$

(17)

As per equation (14):

$$V_{C1}\left[K + \frac{1}{2}\right] = V_{C1}[K] + (V_{in} - V_{C1}[K])\left(1 - e^{-\frac{T}{RC}}\right)$$

(18)

And, rearranging terms for ease of manipulation:

$$V_{C1}\left[K + \frac{1}{2}\right] = V_{C1}[K](1-a) + a * V_{in}$$

<sup>(19)</sup>

Where we have written  $a = (1 - e^{-\frac{T}{RC}})$

We now take the same approach for capacitor C1 during the second semi-period of operation. In this instance, C1 is connected to C2 and will relay some charge onto it. That is, C1 will partially discharge and its voltage will decrease.

$$V_{C1}[K+1] = V_{C1}\left[K + \frac{1}{2}\right] - \Delta V_{C1}$$

(20)

As per equation (13):

$$V_{C1}[K+1] = V_{C1}\left[K + \frac{1}{2}\right] - \frac{\left(V_{in} + V_{C1}\left[K + \frac{1}{2}\right] - V_{C2}\left[K + \frac{1}{2}\right]\right)}{2} \left(1 - e^{-\frac{T}{RC}}\right)$$

(21)

Rearranging terms:

$$V_{C1}[K+1] = V_{C1}\left[K + \frac{1}{2}\right]\left(1 - \frac{a}{2}\right) + V_{C2}\left[K + \frac{1}{2}\right] * \frac{a}{2} - V_{in} * \frac{a}{2}$$

(22)

Now we can substitute the term  $V_{C1}\left[K + \frac{1}{2}\right]$  by the expression derived in equation (19).

$$V_{C1}[K+1] = (V_{C1}[K](1-a) + a * V_{in})\left(1 - \frac{a}{2}\right) + V_{C2}\left[K + \frac{1}{2}\right] * \frac{a}{2} - V_{in} * \frac{a}{2}$$

(23)

The same procedure can be done for C2. That is, obtain an expression relating  $V_{C2}\left[K + \frac{1}{2}\right]$  to  $V_{C2}[K]$ , and substitute it in all the instances of equations of the type  $V_{Ci}[K + 1]$ . Thus, for each capacitor in a circuit with 2n+1 capacitors an expression is obtained of the form:

$$V_{Ci}[K+1] = ai1 * V_{C1}[K] + ai2 * V_{C2}[K] + \dots + aii * V_{Ci}[K] + \dots + aiN * V_{CN}[K] + bi * V_{in} (24)$$

Where the different *aij* coefficients are the constant components of the ith row of the state matrix and the *bi* coefficient is the constant component of the ith row of the input matrix.

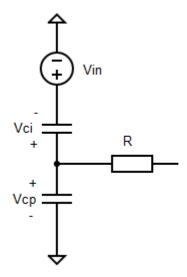

If we wish to represent the output of the state-space system as the voltage of the load capacitor, following equation (16), consider the following:

$$Y[K] = V_{CN}[K] = [c_1 \ c_2 \ \dots \ c_N] * \begin{bmatrix} V_1[K] \\ V_2[K] \\ \dots \\ V_N[K] \end{bmatrix}$$

(25)

telecom

It is readily observed that C is a vector where only the ith component of interest is 1, the rest being zero.

$$C = [0 \ 0 \dots 1]$$

#### 3.2. Parasitic capacitances effects on the dynamic model

Let's consider now the case in which the circuit presents some parasitic components; namely, parasitic capacitances along the main capacitors forming the charge pump.

Fig. 3.2 depicts a cross-section of capacitor implemented with VLSI technology, as well as the main parasitics that arise in such implementation. These are not to be taken as accurate representations of the parasitic capacitances arising in FDSOI technology, but as simple indications of the types of parasitics that can arise.

The following analysis ignores for the moment the bottom plate parasitic capacitances which, despite generally being the largest, an initial analysis and circuit simulation show little to no impact on either the dynamic or steady-state models. However, bottom plate parasitic capacitances do present effects that can alter real implementations. Namely, they introduce loading effects at the output of the clock drivers. This loading effect impacts both the power consumption of the drivers and the clock waveform, so they have to be taken into account when designing the drivers. These considerations are beyond the scope of this thesis, so they will not, at the moment, be taken into account.

Regarding top-plate parasitic capacitances, they can originate from various sources, such as top-plate to bulk couplings of the implemented capacitors (as seen in Fig. 3.2), the transistors (gate and junction capacitances), and nearby metal layers.

*Fig. 3.2: :* [From Baker et al.]: Cross-sectional view of a capacitor implemented with VLSI technology, including the various sources of parasitic capacitances.

#### 3.2.1. Parasitic capacitances impact on voltage gain:

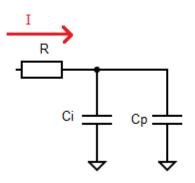

When an arbitrary capacitor  $C_i$  is charging (Fig. 3.3), its bottom plate is connected to ground (through the inverter), and so the capacitor  $C_i$  lies in parallel to the top plate parasitic capacitances ( $C_p$ ).

*Fig. 3.3:* Topology during a charging semi-period. The main capacitor lies in parallel with the equivalent parasitic capacitances.

At the end of a charging semi-period, both capacitors present the same voltage.

When the capacitor  $C_i$  is discharging (Fig. 3.4), its bottom plate is connected to the inverter (here depicted and analyzed as an ideal voltage source). The top plate parasitic capacitances are, however, still connected to ground at one end.

*Fig. 3.4:* Topology during a discharging semi-period. The parasitic capacitances are not directly affected by *the inverter.*

This generates a voltage difference between the top plates of both capacitors. This, in turn, initiates a charge redistribution between the two capacitors.

Assuming that the process of charge redistribution between capacitors takes place at a much higher rate than the discharge of capacitor  $C_i$  through the resistance R, the effect of the parasitic capacitances can be easily analyzed through the superposition principle and a capacitive voltage divider (Fig. 3.5).

Fig. 3.5: Parasitic Voltage Divider

Applying the superposition principle, the node connected to the R equivalent resistance experiences two sources of voltage:

- The voltage across the terminals of either capacitor  $(V_{C_i})$ .

- The voltage contributed by the clock driver  $(V_{in})$  in the form of a capacitive voltage divider.

The voltage at the node connected to R before initiating the discharge process becomes:

$$V_n = V_{C_i} + V_{in} * \frac{C_i}{C_i + C_p}$$

(26)

Ideally, the voltage gain of a stage of a CC-CP is  $V_{in}$ . This equation shows that the maximum voltage gain of a stage is reduced from the ideal to a fraction of this value, meaning that the maximum voltage attainable at the output once the steady-state has been reached is affected by the presence of top-plate parasitic capacitances. In later sections discussing the steady-state model a proof of the final impact of parasitics in the output voltage will be derived.

Regarding the dynamic model, this effect can be included in the discrete-time state space system. To that end equation (13) must be modified, becoming:

$$\Delta V_{i+1} = -\Delta V_i = \frac{\left(V_{in} * \frac{C_i}{C_i + C_p} + v_i - v_{i+1}\right)}{2} \left(1 - e^{-\frac{T}{RC}}\right)$$

(27)

However, there is another effect that must be taken into account before fully committing to the procedure derived in the previous section.

#### 3.2.2. Parasitic effects on topology dynamics:

Fig. 3.6: CC-CP topologies with top-plate parasitic capacitances.

Although the procedures derived in section 2.3 still hold, the inclusion of parasitic capacitances in the model requires the consideration that they modify the value of the equivalent capacitances in each topology. Again, for simplicity we can consider that all fly-capacitors present the same value and that all parasitic capacitances also present the same value, albeit distinct from the value of fly-capacitors. These assumptions are not so rigorous as they might have been in previous sections (given that the size of transistors may vary from stage to stage), but they allow us to showcase the effect of parasitics.

Namely, the equivalent capacitance of the first stage topology (Fig. 3.6.left) is now the parallel association of capacitance C1 and Cp.

$$C_{eq} = C_1 + C_p \tag{28}$$

The same is true for the capacitances of intermediate stages. Since all fly-capacitances are equal and all parasitic capacitances are equal, all the resulting equivalent capacitances are equal.

Equations (13) and (14) must now be further modified.

$$\Delta V_1 = (v_{in} - v_1) \left( 1 - e^{-\frac{T}{RC_{eq}}} \right)$$

(29)

$$\Delta V_{i+1} = -\Delta V_i = \frac{\left(v_{in} * \frac{C_i}{C_i + C_p} + v_i - v_{i+1}\right)}{2} \left(1 - e^{-\frac{T}{RC_{eq}}}\right)$$

(30)

#### 3.3. Dynamic Model Validation:

The validation of the above derived models and equations is done in two steps. Firstly, a matlab script describing the model is written and tested. Secondly, using a elecom

SPICE-based software (TINA-TI), an idealized version of the circuit is built and simulated, comparing the results obtained to the matlab results.

The matlab model has been created by generating a discrete-time state-space system. The transient response of such model has been simulated through the use of the Linear Simulation Tool, by applying a unit step function to the input.

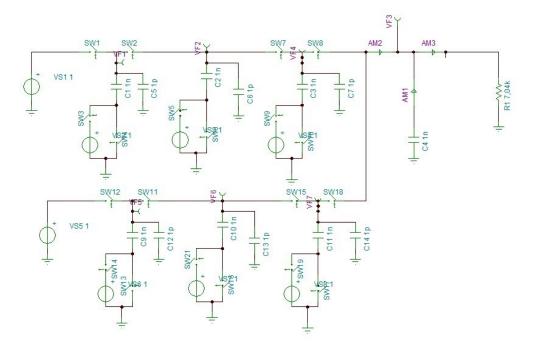

Following the creation of the idealized circuit and its mathematical model, various transient analyses have been performed. The ideal circuit used to compare the results was built using the SPICE-based software from Texas Industries, TINA-TI. The circuit can be seen in Fig. 3.7.

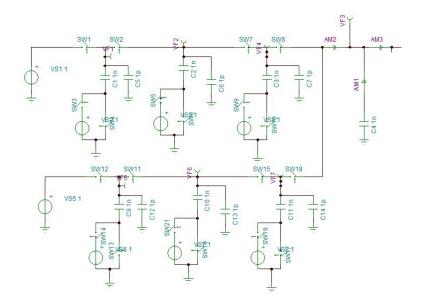

Fig. 3.7: Schematic form used for simulation of the CC-CP.

The model is simulated in a variety of cases. However, we present here only those with parameters shown in Table II, so as to simplify the presentation. The transient response of the output stage in those two cases, only differing in the presence of parasitic capacitances, is compared to a transient simulation of the circuit using the Texas Instruments SPICE-based software (TINA-TI).

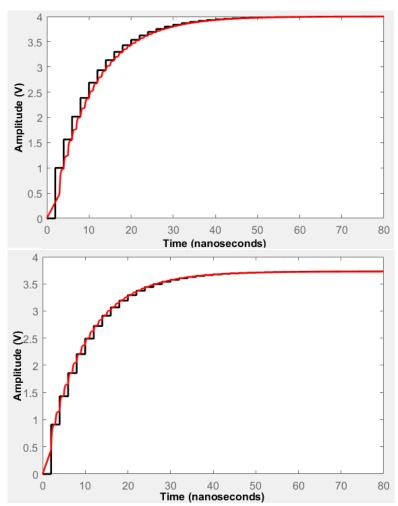

All fly-capacitors and load capacitance are equal in value. Fig. 3.8 shows the superposition of the matlab model (black line) and the transient simulation of the SPICE circuit (red line). Table III presents the comparison of the steady-stage voltages reached as a consequence of the presence or absence of parasitic capacitances, given an ideal output voltage of 4V. The third column depicts the relative error between the model and the SPICE simulation.

Fig. 3.8: Dynamic Model Simulation. Top) Case1. Bottom) Case 2. The black line corresponds to the Matlab script output. The red line, to the SPICE transient.

|        | С    | Ср     | R     | f       | Vin |

|--------|------|--------|-------|---------|-----|

| Case 1 | 6 fF | 0 F    | 50 kΩ | 500 MHz | 1 V |

| Case 2 | 6 fF | 0.6 fF | 50 kΩ | 500 MHz | 1 V |

| TABLE I: Parameters used durir | ng the simulation | of the Dynamic Model |

|--------------------------------|-------------------|----------------------|

|--------------------------------|-------------------|----------------------|

TABLE II: Steady-State voltages achieved as a consequence of parasitics

|        | Model (V) | SPICE (V) | %    |

|--------|-----------|-----------|------|

| Case 1 | 4         | 3.99      | 0.25 |

| Case 2 | 3.73      | 3.727     | 0.08 |

It can be seen that both the transient and the steady-state output voltage coincide fairly well in both cases.

The advantage of the presented discrete time model is in calculation time. For large values of capacitances, the transient simulation in the SPICE based software can take several minutes, in some extreme cases (with capacitors in the picofarad range) up to

10-15 minutes. However, the Matlab model was able to produce results within 1-2 seconds of run-time for a varied range of capacitor values.

## 4. Steady-State Analysis: mean voltage values.

In a switched-capacitor converter of any type, the condition of steady-state is reached when, after a whole period of operation, the state-space vector value remains the same as that of the previous period. That is, X[K + 1] = X[K]. What this means is that, for any capacitor:  $V_{Ci}[K + 1] = V_{Ci}[K]$ . As per equation (15), this implies:

$$\Delta V_{charging} = \Delta V_{discharging} \tag{31}$$

That is, the increase in voltage during the charging semi-period must be equal to the decrease in voltage during the discharging semi-period.

A simple way to see this relation that allows to come up with an analysis equation is to consider that the increase in voltage of capacitor  $C_i$  during its charging semi-period must be equal to the increase in voltage of capacitor  $C_{i+1}$  during its own charging semi-period. This is only true if both capacitors present the same capacitance.

$$\Delta V_{Ci_{charging}} = \Delta V_{Ci+1_{charging}} \tag{32}$$

Restricting ourselves to the constraints imposed at the beginning of the analysis, we can forgo for the moment a generalized view and continue considering that all capacitances are equal. In this instance, equation (32) holds and, as per equations (13) and (14):

$$\left(V_{in} - \hat{V}_1\right) = \frac{V_{in} + \hat{V}_1 - \hat{V}_2}{2} \tag{33}$$

$$\frac{V_{in} + \hat{V}_i - \hat{V}_{i+1}}{2} = \frac{V_{in} + \hat{V}_{i+1} - \hat{V}_{i+2}}{2}$$

(34)

The symbol  $\hat{}$  is indicative of the mean voltage value during steady-state. Here we work under the assumption that the ripple is superposed over a DC voltage value.

It is important to stress that the voltage values of the capacitors change during a semiperiod of operation (the system is inherently time-continuous), but one can assume that, during steady-state, the mean value remains the same.

Consider a CC-CP with 3 stages. The Steady-State condition equations are:

$$\left(V_{in} - \hat{V}_1\right) = \frac{V_{in} + \hat{V}_1 - \hat{V}_2}{2} \tag{35}$$

$$\frac{V_{in} + \hat{V}_1 - \hat{V}_2}{2} = \frac{V_{in} + \hat{V}_2 - \hat{V}_3}{2}$$

(36)

$$\frac{V_{in} + \hat{V}_2 - \hat{V}_3}{2} = \frac{V_{in} + \hat{V}_3 - \hat{V}_{out}}{2}$$

(37)

The first equation can be rearranged to isolate the mean value of V1:

$$\hat{V}_1 = \frac{V_{in} + \hat{V}_2}{3} \tag{38}$$

V1 can be substituted in the second equation, and V2 can be isolated:

$$\hat{V}_2 = \frac{3 * \hat{V}_3 + V_{in}}{5} \tag{39}$$

And, finally, we can substitute V2 in the third equation, isolating V3.

$$\hat{V}_3 = \frac{5 * \hat{V}_{out} + V_{in}}{7}$$

(40)

These equations relate the mean voltage value of each capacitor to the contiguous one. These equations serve two purposes:

• From an analytical standpoint, they can be used to derive the ideal ratio  $V_{out}/V_{in}$ . One must only consider that capacitor C1 is fully charged, the circuit is unloaded, and there is no ripple. Then,  $\hat{V}_1 = V_{in}$ . Substituting, one obtains:  $V_1 = V_{in}$

$$V_2 = 2V_{in}$$

$$V_3 = 3V_{in}$$

$$V_{out} = 4V_{in}$$

$$\frac{V_{out}}{V_{in}} = 4$$

Which is to be expected for a 3-stage CC-CP, partially validating equations (33) and (34)

From a synthesis perspective, these equations allow the prediction of mean voltage values of each capacitor under non-idealized conditions. That is, when the output voltage is lower than the one predicted by the ideal relation Vout/Vin, be it because of parasitic effects, the presence of a load or both, the mean voltage of the fly-capacitors can still be predicted. From a design perspective, knowing these mean voltage values allows the proper sizing of the transistors working under the circuit's operating point.

#### 4.1. Mean Voltage Value Validation

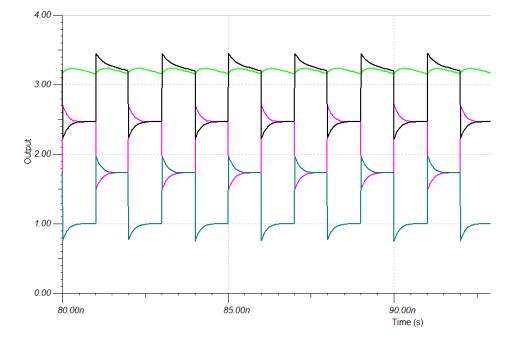

In order to determine the validity of equations (33) and (34), the circuit in Fig. 3.7 is loaded with different resistances. A transient simulation is then performed with circuit parameters equal to those of TABLE I, case 1, expect for the resistances' values. The mean voltage values of the output and each fly-capacitor is calculated grossly as  $\frac{(V_{min}+V_{max})}{2}$ during a charging semi-period for all capacitors and annotated (see Fig. 4.1). The results can be seen in TABLE III.

Fig. 4.1: Fly-capacitor waveforms in steady-state, Rload = 2MΩ. Green: output capacitor. Black: fly-capacitor 3. Purple: fly-capacitor 2. Blue: fly-capacitor 1. The mean value is extracted in their respective charging period.

| $\widehat{V}_1$ (V) | $\widehat{V_2}$ (V) | $\widehat{V_3}$ (V) | $\widehat{V}_4$ (V) | Vin (V) | Rload ( $\Omega$ ) |

|---------------------|---------------------|---------------------|---------------------|---------|--------------------|

| 1                   | 2                   | 3                   | 4                   | 1       | Open               |

| 0,93                | 1,72                | 2,5                 | 3,34                | 1       | 2,5 M              |

| 0,88                | 1,66                | 2,4                 | 3,22                | 1       | 2M                 |

| 0,871               | 1,55                | 2,19                | 3                   | 1       | 1,5M               |

| 0,803               | 1,37                | 1,93                | 2,67                | 1       | 1M                 |

TABLE III: Mean Voltage Values, Simulation Results

The values of V4 (Vout) are then introduced in equation (40) and the mean voltage value of each fly-capacitor is recursively calculated. TABLE IV presents the results obtained. TABLE V compares the results of both tables.

| Equations           |                     |                     |                     |         |  |

|---------------------|---------------------|---------------------|---------------------|---------|--|

| $\widehat{V}_1$ (V) | $\widehat{V_2}$ (V) | $\widehat{V_3}$ (V) | $\widehat{V}_4$ (V) | Vin (V) |  |

| 1                   | 2                   | 3                   | 4                   | 1       |  |

| 0,91                | 1,72                | 2,53                | 3,34                | 1       |  |

| 0,89                | 1,67                | 2,44                | 3,22                | 1       |  |

| 0,86                | 1,57                | 2,29                | 3                   | 1       |  |

| 0,81                | 1,43                | 2,05                | 2,67                | 1       |  |

TABLE IV: Mean Voltage Values, Equations Results

| Relative error (%)  |                     |       |  |  |

|---------------------|---------------------|-------|--|--|

| $\widehat{V}_1$ (V) | $\widehat{V_3}$ (V) |       |  |  |

| 0,000 0,000         |                     | 0,000 |  |  |

| -2,681              | -0,166              | 1,130 |  |  |

| 0,965 0,343         |                     | 1,754 |  |  |

| -1,617              | 1,364               | 4,188 |  |  |

| 0,864               | 4,196               | 5,854 |  |  |

TABLE V: Relative Error between simulation and equations

Note that the results are consistently under a 10% relative error. Also, it is important to note that as the value of the resistive load decreases, the ripple both at the output and each fly-capacitor increases. Given the exponential nature of ripple during a semiperiod, it can be hard to properly determine the mean value of the curves by inspection. These results are then to be taken as approximations.

However, they might be enough to consider them useful from a synthesis perspective. When transistors are to be sized appropriately to present a desired equivalent resistance, the mean values of the fly-capacitors correspond to the mean operating points of Vd, Vs and Vg. These considerations will be explored in detail in the FDSOI implementation section.

# 5. Steady-State Analysis: Thèvenin Model and Ripple approximation.

The previous section analyzed the mathematical conditions that arise during steadystate and how they affect the mean voltage of the different fly-capacitors. However, no model has been derived yet to predict the output voltage under loaded conditions.

There are three phenomena that affect the output voltage. Namely:

- Resistive loses

- Parasitic capacitances

- Voltage dependent capacitors

The effect of parasitic capacitances has been already explored in section 3.2, and will only be slightly extended to consider the effect on the output voltage as related to the number of stages of a CC-CP.

Voltage dependent capacitors introduce some challenging effects, but under idealized conditions of linear capacitors, their effect can be ignored. Therefore, they will not be considered in this section. However, their effect will be presented in the sections regarding FDSOI implementations of the circuit.

#### 5.1. Resistive losses – CC-CP equivalent resistance.

When a DC-DC converter is connected to a load, under steady-state conditions, a constant in average flow of current through the circuit will take place. If the converter can be modeled as a resistance under certain operation conditions, this flow of current will produce a voltage drop. This voltage drop will ultimately affect the voltage at the output of the converter. It is then necessary, in order to have a complete steady-state model, to model the equivalent resistance of the CC-CP.

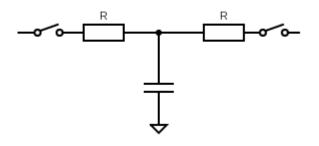

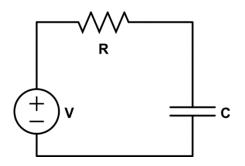

It is a well-known fact [11] that the equivalent resistance of a switched-capacitor (Fig. 5.1) can be expressed as:

$$R_{eq} = \frac{1}{fC} \tag{41}$$

Fig. 5.1: Switched-Capacitor circuit representation.

Where f is the switching frequency and C the capacitance.

An extensive derivation of the generalized equivalent power resistance of a switchedcapacitor circuit can be found in [11], presenting a more generalized equation applicable to a broader set of conditions.

$$R_{eq} = \frac{1}{fC} \coth\left(\frac{1}{2fR_{sw}C}\right) \tag{42}$$

Or, defining  $\beta_1 = \frac{1}{fR_{SW}C}$

$$R_{eq} = \frac{1}{fC} \coth\left(\frac{\beta_1}{2}\right) \tag{43}$$

#### 5.1.1. Fast vs Slow Switching limit

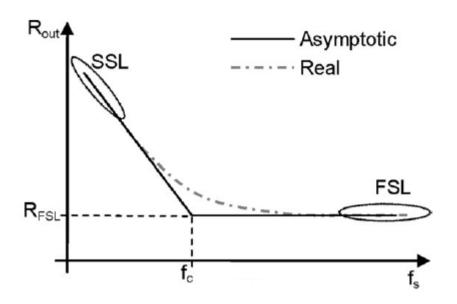

Equation (43) can take two limits (Fig. 5.2):

- $\circ$  When  $|β_1|$  → 0. This is called the Fast Switching Limit (FSL)

- $\circ$  When  $|β_1|$  → ∞. This is called the Slow Switching Limit (SSL)

Fig. 5.2: Asymptotic and Real representations of equation (42), including their limits (from [12])

In the limit when  $\beta_1$  tends to 0 (FSL), equation (43) can be simplified as follows:

$$R_{eq} \lim_{\beta_1 \to 0} = \frac{1}{fC} \left[ \frac{(1 + (1 - \beta_1))}{(1 - (1 - \beta_1))} \right]$$

(44)

$$R_{eq} \lim_{\beta_1 \to 0} = \frac{1}{fC} \left[ \frac{2}{\beta_1} \right] = \frac{1}{f_{SW}C} \left( \frac{2fR_{SW}C}{1} \right)$$

(45)

$$R_{FSL} = R_{eq} \lim_{\beta_1 \to 0} = 2R_{sw} \tag{46}$$

Where we have used the fact that the Maclaurin series expansion of the exponential function  $e^x$  is 1 + x in a first order approximation.

In the limit when  $\beta_1$  tends to  $\infty$  (SSL),  $\operatorname{coth}\left(\frac{\beta_1}{2}\right) \approx 1$  and:

$$R_{SSL} = R_{eq} \lim_{\beta_1 \to \infty} = \frac{1}{f_{sw}C}$$

(47)

Equation (46) tells us that when the frequency is sufficiently high, the equivalent resistance of a switched-capacitor is determined by the sum of the ON resistances of the switches at either side of the capacitor, while equation (47) tells us that if the switching frequency is low enough, the switch resistances bear no effect. These are, respectively, the fast and the slow switching limits (FSL and SSL).

Conventionally, the literature [12][13] considers the equivalent resistance of a switched-capacitor circuit can be approximated as:

$$R_{eq} = \sqrt{R_{SSL}^2 + R_{FSL}^2} \tag{48}$$

Where RssI and RfsI, described below, are the equivalent resistances of the whole circuit operating, respectively, at the aforementioned limits.

In the next section, we derive an expression for the equivalent resistance of a CC-CP as a simple linear combination of equation (43).

### 5.1.2. Equivalent resistance of a CC-CP of an arbitrary number of stages.

Equation (43) is based on a derivation based on the energy losses produced during the charging and/or discharging of a capacitor in a switched regime. Reference [14] offers a conceptual and physical insight into energy losses incurred during the operation of switched-capacitor circuits, remarking that it is the process of charging/discharging itself that is responsible for the equivalent power resistance.

That is, there are energy losses that can be modelled as resistances regardless of the presence of actual ohmnic resistors. This is notable enough to be stressed:

Switched-capacitor circuits with ideal switches presenting 0 ON resistances incur energy losses as a direct consequence of the process of charging/discharging of the capacitors.

Every time a capacitor is charged, there are energy losses. Every time a capacitor is discharged, there are energy losses.

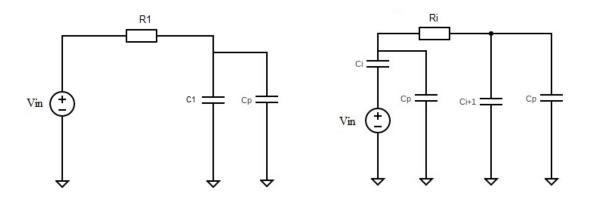

Let's consider a 3-stage CC-CP with 2N fly-capacitors and 1 load capacitor, where N=n+1, and **n** is the number of stages (equation 1). The equivalent circuit can be found in Fig. 5.3 in schematic form.

*Fig. 5.3:* Schematic representation of a 3-stage CC-CP with resistive load.

If we consider only one branch of the CC-CP, there are N fly-capacitors and 1 load capacitor. Each fly capacitor experiences charging and discharging, while the load capacitor experiences only a charging process through a switch.

Reference [15] introduces a methodology to derive the RssI and RfsI for SC circuits of arbitrary complexity. These RssI and RfsI are not to be confused with those of equations (46) and (47), as those refer to a single switched-capacitor. Reference [15] proposes a method to compute the overall RSSL and RFSL of the circuit as a whole.

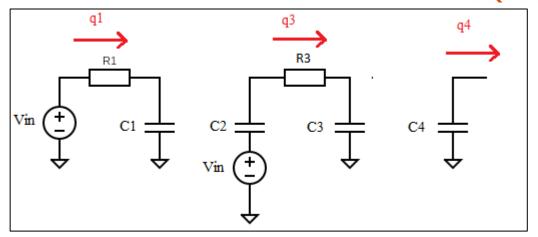

In order to obtain the RSSL and RFSL of the circuit in Fig. 5.3, consider Fig. 5.4 and Fig. 5.5, depicting, respectively, phase 1 and 2 of operation, during which a packet of charge is transferred among capacitors.

telecom

Fig. 5.4: Charge exchange during phase 1 of operation.

$\varphi_1$ :

$$q_1 = q_{in} \tag{49}$$

$$q3 = q2 \tag{50}$$

$$\frac{qout}{2} = q4 \tag{51}$$

$\varphi_2$ :

$$q2 = q1 \tag{52}$$

$$q3 = \frac{qout}{2} + q4 \tag{53}$$

Solving the system yields:

$$q1 = q2 = q3 = qout$$

(54)

$$q4 = \frac{qout}{2} \tag{55}$$

Fig. 5.5: Charge exchange during phase 2 of operation

UNIVERSITAT POLITÈCNICA DE CATALUNYA BARCELONATECH

These are the equivalent topologies formed during phase 1 and 2 respectively (see Fig. 3.1).

Following the nomenclature on [15], the Charge Multiplier Vector (CMV) has coefficients:

$$\vec{a}_c = \left[1\ 1\ 1\ \frac{1}{2}\right] \tag{56}$$

We can also define a capacitor vector:

$$\vec{C} = \left[\frac{1}{C_1} \frac{1}{C_2} \frac{1}{C_3} \frac{1}{C_{load}}\right]$$

(57)

And the equivalent RSSL resistance can be found as the vector product of the square of the CMV ( $\vec{a}_c$ ) and the capacitor vector ( $\vec{C}$ ), all divided by the switching frequency.

$$R_{SSL} = \frac{1}{f} \ \vec{a}_c^2 \cdot \vec{C}' \tag{58}$$

$$R_{SSL} = \frac{1}{f} * \left(\frac{1}{C_1} + \frac{1}{C_2} + \frac{1}{C_3} + \frac{1}{4} * \frac{1}{C_{load}}\right)$$

(59)

Since we are assuming that all capacitances are equal:

$$R_{SSL} \approx \frac{13}{4} \frac{1}{fC} \tag{60}$$

In order to determine the RFSL resistance, a similar procedure is followed regarding the charge flow through the switches. From the previous analysis, the charge flowing through each resistor is equal to Qout. Normalizing the vector.

$$\vec{a}r = [1\ 1\ 1\ 1] \tag{61}$$

We can now build a vector with the values of the switches' resistances.

$$\vec{R}_{sw} = [R_{sw1} R_{sw2} R_{sw3} R_{sw4}]$$

(62)

The RFSL resistance can be computed as 2 times the vector product of  $\vec{a}r$  squared and the  $\vec{R}_{sw}$  vector.

$$R_{FSL} = 2 * \left( \vec{a}_r^2 \cdot \vec{R}_{SW}' \right) \tag{63}$$

$$R_{FSL} = 2 * (R_{sw1} + R_{sw2} + R_{sw3} + R_{sw4})$$

(64)

Remember that, in order to keep all the sub-circuits with equal RC constants, switches 2, 3 and 4 have equal resistance Ron, while switch 1 has a resistance of Ron/2.

$$R_{FSL} = 2 * \left(\frac{R_{on}}{2} + 3 * R_{on}\right)$$

(65)

$$R_{FSL} = 2R_{on} * \left(\frac{7}{2}\right) \tag{66}$$

$R_{FSL} = 7R_{on}$

Therefore:

$$R_{tot} \approx \sqrt{\left(\frac{13}{4}\frac{1}{fC}\right)^2 + (7R_{on})^2}$$

(68)

However, a CC-CP presents a comparatively simple topology (two branches of switched-capacitors connected in series, those two branches connected in parallel). This allows us to derive a more general expression, a linear combination of equation (43).

Based on the conceptual and physical insight presented in [11] and [14], we theorize that the equivalent resistance of a single switched-capacitor can be linearly associated, similarly to ideal ohmnic resistors. That is, several concatenations of switched-capacitors can form equivalent resistive series associations and parallel associations.

In order to analyze these associations, we begin with the most generalized form of equation (43)

$$R_{eq} = \frac{1}{2fC} \operatorname{coth}\left(\frac{\beta_1}{2}\right) + \frac{1}{2fC} \operatorname{coth}\left(\frac{\beta_2}{2}\right)$$

(69)

Equation (69) states that the equivalent resistance of a switched-capacitor converter comprises the linear association (sum) of two equivalent resistances.

Remembering that it is the charging and discharging processes which produce the energy losses that can be modelled as resistances, we can identify each resistance of equation (69), one pertaining to the charging process and one pertaining to the discharging process (Fig. 5.1). If the charging and discharging time constants are equal ( $\beta_1 = \beta_2$ ), equation (69) reduces to equation (43).

This leads us to hypothesize that the indivisible unit of the equivalent resistance of switched-capacitor converter is:

$$R_{eq_{unit}} = \frac{1}{2fC} \coth\left(\frac{\beta}{2}\right) \tag{70}$$

This equation represents the instance of either a charging process or a discharging process.

In a single branch of a CC-CP (Fig. 2.6), the switched-capacitors lie in series. Working under the assumption that all capacitors have equal value and that the RC time constants of each topology are equal, we expect to be able to express the equivalent resistance as the sum of all the instances of equation (70).

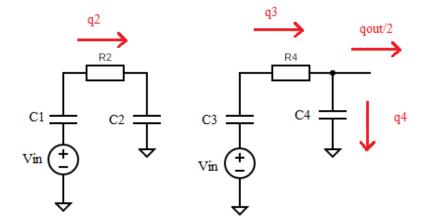

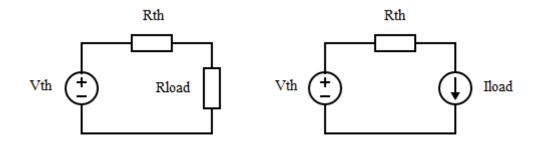

To illustrate this process, consider Fig. 5.6. We can readily observe a total of 7 charging and discharging processes (as illustrated by the black arrows) during a complete period of operation.

Fig. 5.6: Single Branch of a 3-Stage CC-CP. Top) Phase 1. Bottom) Phase 2. The black lines represent capacitive charging or discharging processes. We ignore discharging of Capacitor 4 (load capacitor) as it does not discharge in a switched manner.

Thus, we conclude that the equivalent resistance of a single branch of a 3-stage CC-CP is:

$$R_{eq} = 7 * \frac{1}{2fC} \coth\left(\frac{\beta}{2}\right) \tag{71}$$

We believe that this equation holds, generally, as long as all the topologies present an equal RC time constant and, if all capacitors have equal value, when R1=Ri/2.

Applying the limits above derived we can determine whether this expression coincides with the results of the CMV:

$$R_{SSL} = \lim_{\beta_1 \to \infty} \frac{7}{2} \frac{1}{fC} \coth\left(\frac{\beta_1}{2}\right) = \frac{7}{2} \frac{1}{fC}$$

(72)

$$R_{FSL} = \lim_{\beta_1 \to 0} \frac{7}{2} \frac{1}{fC} \operatorname{coth}\left(\frac{\beta_1}{2}\right) = 7 R_{on}$$

(73)

The results of the RSSL resistance are not exactly equal, but they may suffice depending on the mode of operation. The RFSL coincides exactly (see equation (68)).

So far, we have calculated the resistance of one branch of a 3-stage CC-CP. To calculate the full resistance of a CC-CP, we can consider that the above resistances are simply halved (both for the CMV and our proposed method), there being two equivalent resistances in parallel. In the case of the Charge Multiplier Vector method, we can also analyze the circuit as a whole.

Table I compares the different resistances of a full CC-CP using the CMV method, according to these two possibilities (considering a parallel association, or applying the CMV to the circuit as a whole).

| TABLE VIL 2 store CC CD Equivalent  | Desistances Mathed Comparing | n (Charge Multiplier Vester Method) |

|-------------------------------------|------------------------------|-------------------------------------|

| TABLE VI : 3-stage CC-CP Equivalent | Resistances Method Companso  | (Charge Multiplier vector Method)   |

|                  | Single Branch                | Parallel            | CMV Method                  |

|------------------|------------------------------|---------------------|-----------------------------|

|                  |                              | Equivalent          |                             |

| R <sub>SSL</sub> | 13 1                         | 13 1                | 31                          |

|                  | $\overline{4} \overline{fC}$ | 8 <i>fC</i>         | $\overline{2}\overline{fC}$ |

| R <sub>FSL</sub> | 7 <i>R</i> <sub>on</sub>     | $\frac{7}{2}R_{on}$ | $\frac{7}{2}R_{on}$         |

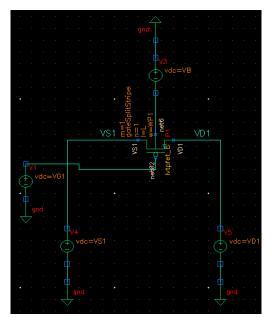

|                  |                              | 2 00                | 2 01                        |