Sede Amministrativa: Università Degli Studi di Padova

Dipartimento di Ingegneria dell'Informazione

CORSO DI DOTTORATO DI RICERCA IN: Ingegneria dell'Informazione

CURRICOLO: Scienza e Tecnologia dell'Informazione

CICLO XXXI

### Design and Development of a Multi-Purpose Input Output Controller Board for the SPES Control System

Tesi redatta con il contributo finanziario dell'Istutito Nazionale di Fisica Nucleare - Laboratori Nazionali di Legnaro

Coordinatore: Ch.mo Prof. Andrea Neviani Supervisore: Ch.mo Prof. Matteo Bertocco Co-Supervisore: Ch.mo Dr. Marco Bellato

Dottorando: Davide Pedretti

## Design and Development of a Multi-Purpose Input Output Controller Board for the SPES Control System.

#### In collaboration with:

#### National Institute for Nuclear Physics (INFN)

Legnaro National Laboratories (LNL)

SPES Project

Davide Pedretti

# Contents

| Sc           | omma  | ario                                                           | XVII |

|--------------|-------|----------------------------------------------------------------|------|

| $\mathbf{A}$ | bstra | $\operatorname{ct}$                                            | XXI  |

| 1            | The   | SPES Control System                                            | 1    |

|              | 1.1   | Introduction                                                   | . 1  |

|              |       | 1.1.1 Binding Energy and the Mass Defect                       | . 2  |

|              | 1.2   | The Production of Radioactive Ion Beams at LNL                 | . 4  |

|              | 1.3   | SPES Integration in the LNL Accelerators Complex               | . 4  |

|              | 1.4   | The SPES Control System Architecture                           | . 7  |

|              | 1.5   | The SPES Accelerator Technology                                | . 9  |

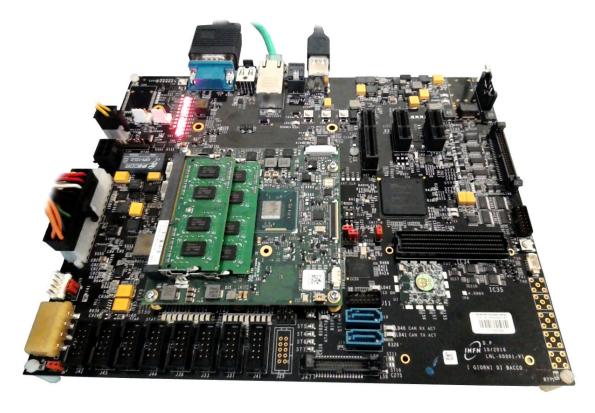

| 2            | The   | Multi-Purpose Input Output Controller                          | 13   |

|              | 2.1   | The IOC Board Precursor                                        | . 14 |

|              | 2.2   | IOC Board Design Guidelines                                    | . 15 |

|              | 2.3   | IOC Board Main Features                                        | . 17 |

|              |       | 2.3.1 $$ The COM Express Standard and General PC Peripherals . | . 19 |

|              |       | 2.3.2 Serial Interfaces                                        | . 20 |

|              |       | 2.3.3 IOC Board Boot Options                                   | . 21 |

|              |       | 2.3.4 FPGA and Application Specific Interfaces                 | . 22 |

|              |       | 2.3.5 $$ The JTAG Chain and FPGA Remote Configuration          | . 26 |

|              | 2.4   | Power Distribution                                             | . 27 |

|              |       | 2.4.1 ATX Power Control                                        | . 30 |

|              |       | 2.4.2 Power Over Ethernet                                      | . 31 |

| 3            | IOC   | Board Design Process                                           | 33   |

|              | 3.1   | Tools and Design Flow                                          | . 33 |

|              | 3.2   | PCB Stackup                                                    | . 36 |

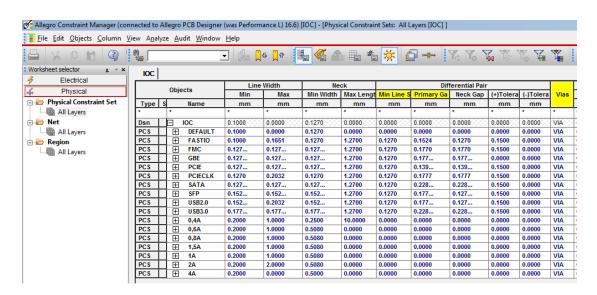

|              | 3.3   | Constraint Manager                                             | . 39 |

IV CONTENTS

|   |      | 3.3.1                   | Impedance Calculator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 40       |

|---|------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

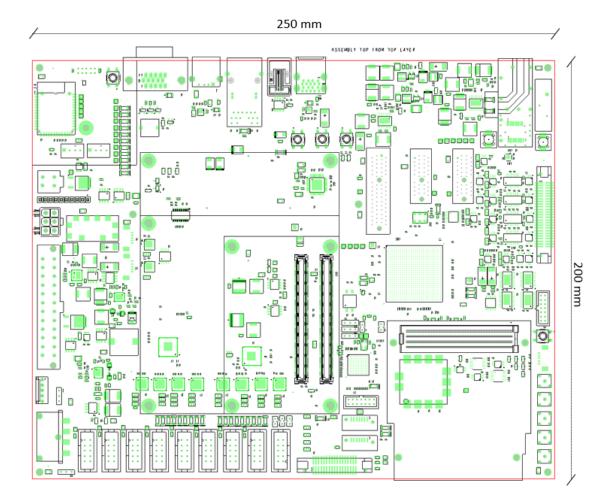

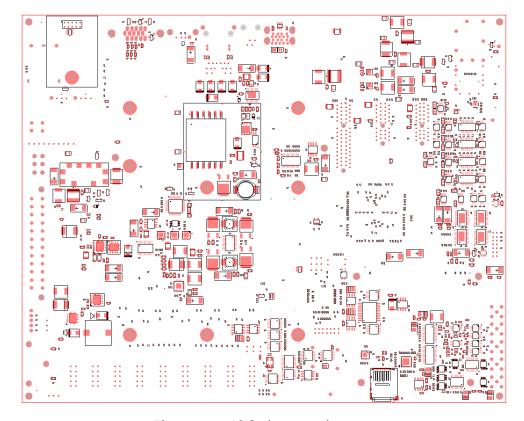

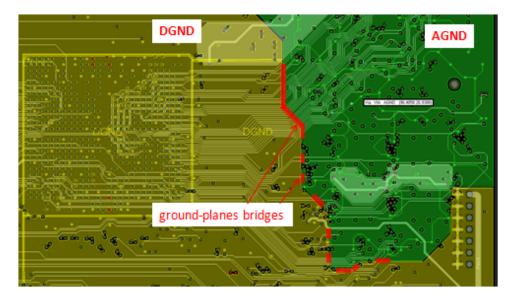

|   | 3.4  | Layou                   | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41       |

|   |      | 3.4.1                   | Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41       |

|   |      | 3.4.2                   | Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44       |

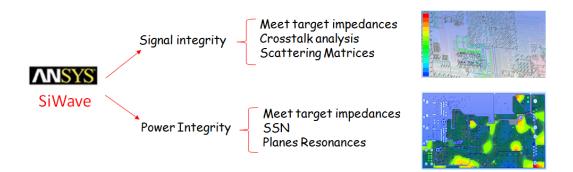

|   | 3.5  | Post I                  | Layout Signal and Power Integrity Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45       |

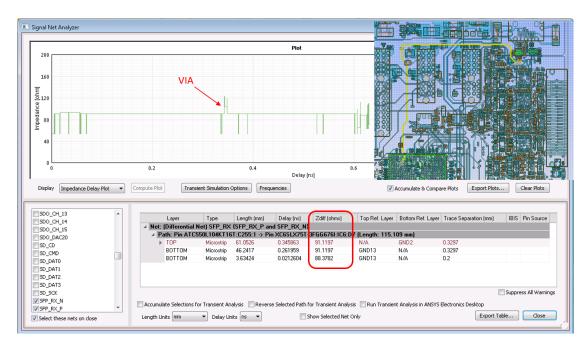

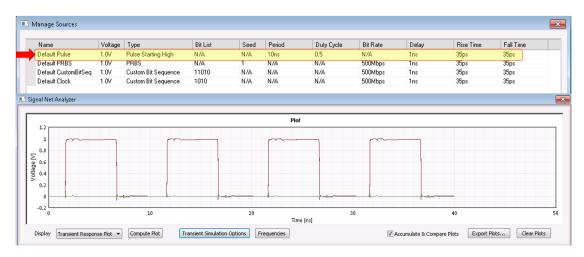

|   |      | 3.5.1                   | Signal Integrity Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46       |

|   |      | 3.5.2                   | Power Integrity Analysis: Computing Resonant Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49       |

| 4 | Firr | nware                   | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53       |

|   | 4.1  | Digita                  | l Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53       |

|   | 4.2  | RTL I                   | Design Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55       |

|   |      | 4.2.1                   | Digital Design Performances Boosting Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56       |

|   | 4.3  | Slow (                  | Control and Data Acquisition via COM Express                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58       |

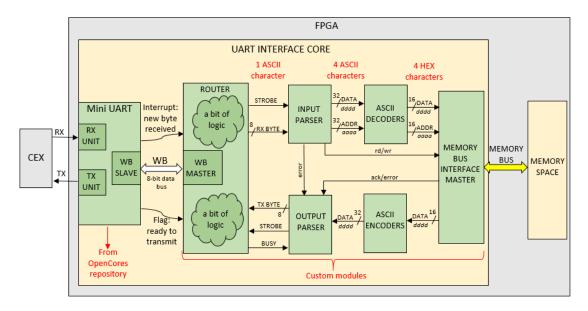

|   |      | 4.3.1                   | UART Interface Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58       |

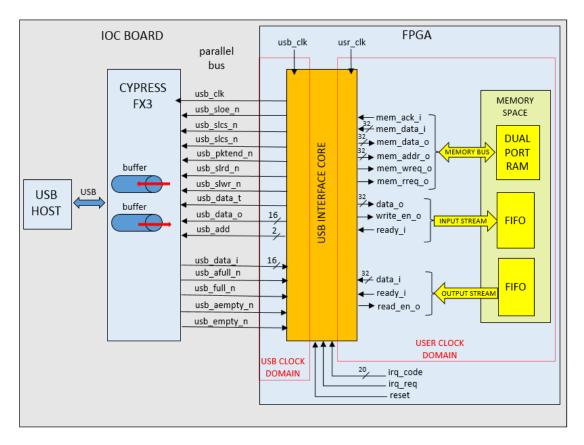

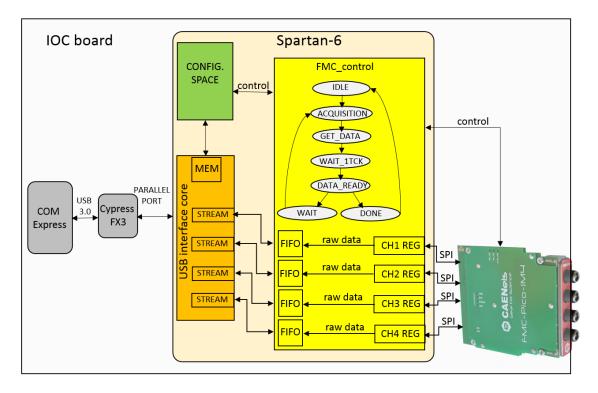

|   |      | 4.3.2                   | USB Interface Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60       |

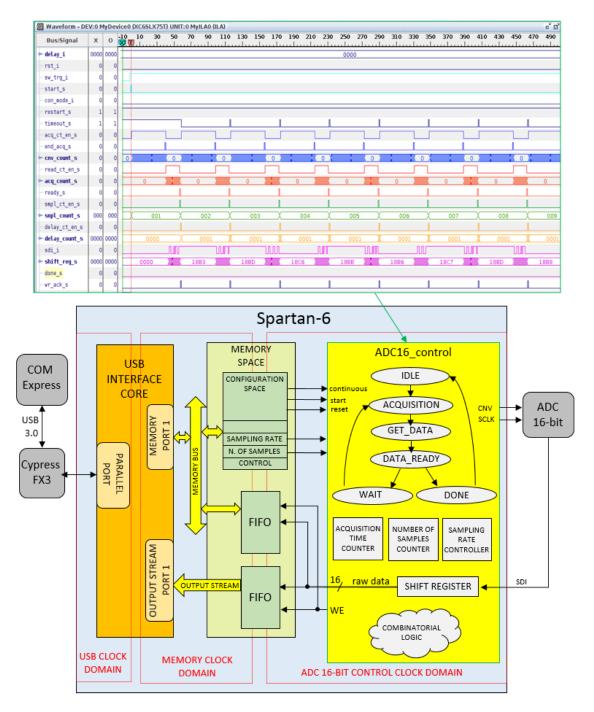

|   |      | 4.3.3                   | Example of Analog Input Data Acquisition and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62       |

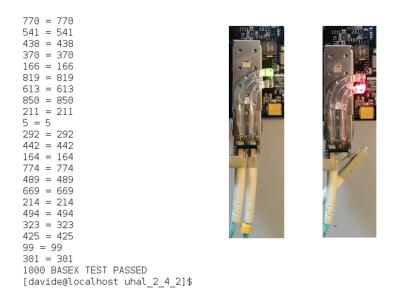

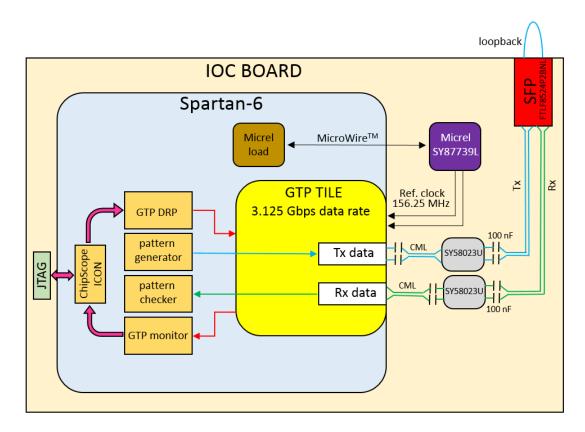

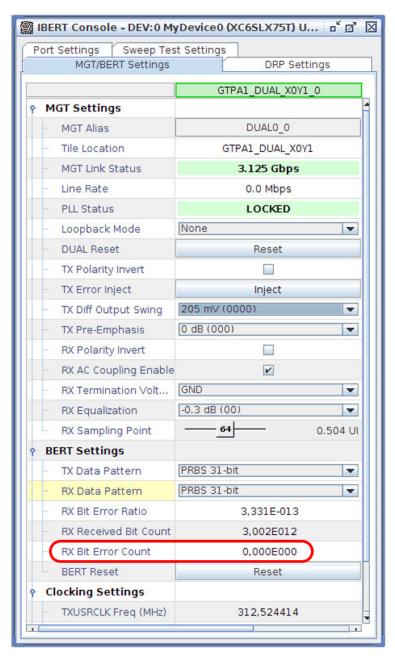

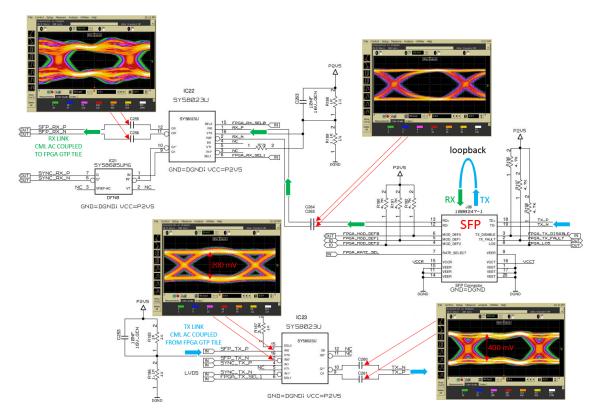

|   | 4.4  | Gigab                   | it Ethernet 1000BASE-X Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 62       |

| 5 | IOC  | Boar                    | d Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 67       |

|   | 5.1  | Power                   | Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67       |

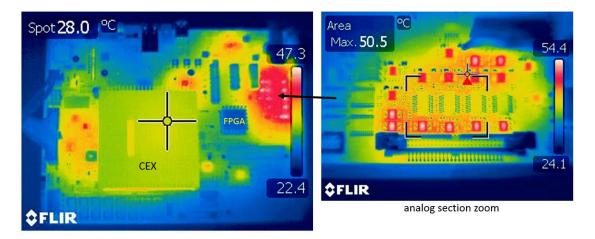

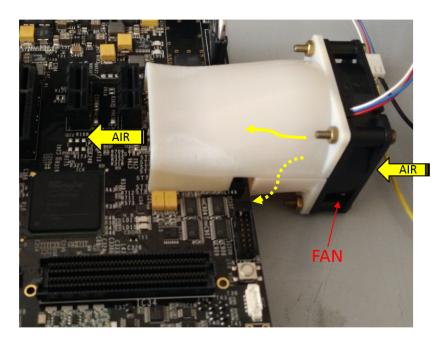

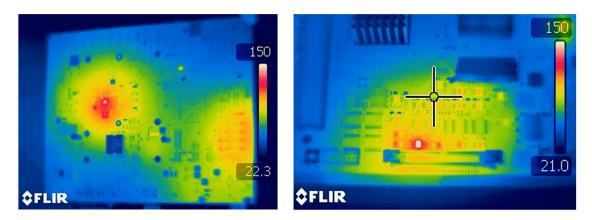

|   | 5.2  | Therm                   | nal Distribution Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68       |

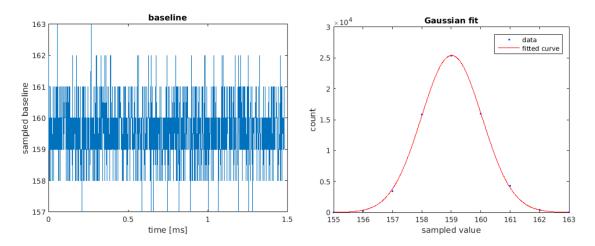

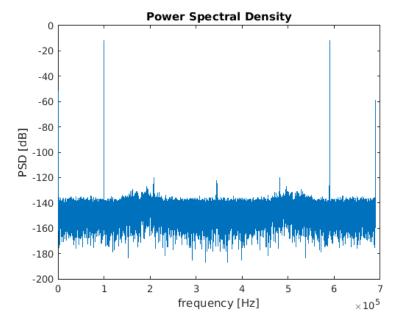

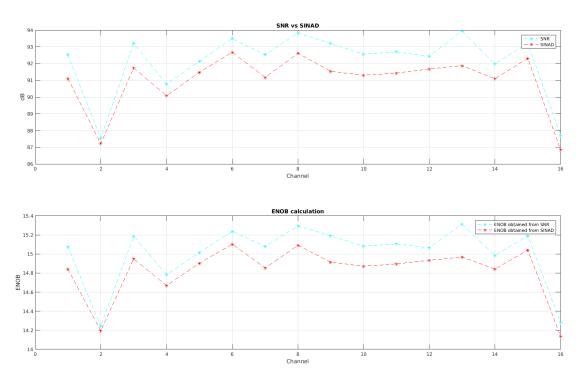

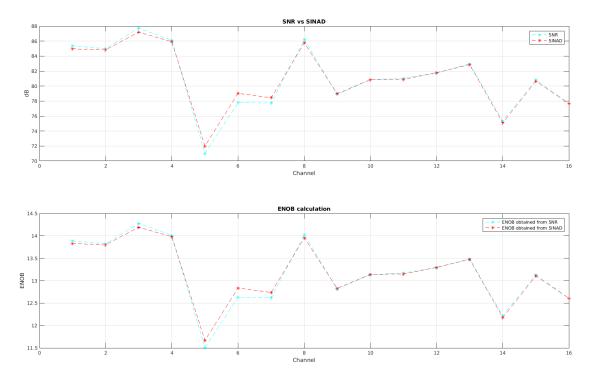

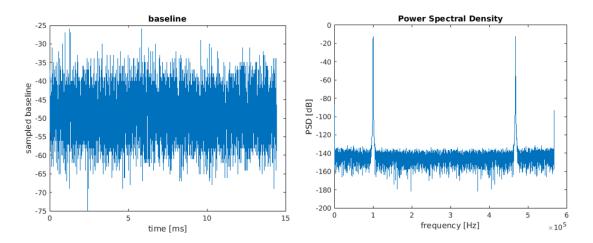

|   | 5.3  | Data I                  | Digitization Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70       |

|   |      | 5.3.1                   | ENOB Calculation From SNR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71       |

|   |      | 5.3.2                   | ENOB Calculation From SINAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72       |

|   |      | 5.3.3                   | IOC Board ADCs Performances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73       |

|   | 5.4  | ADC (                   | Offset and Gain Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75       |

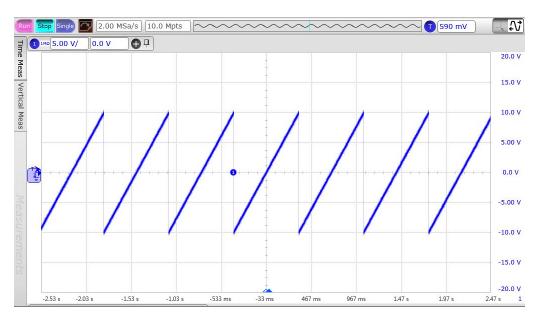

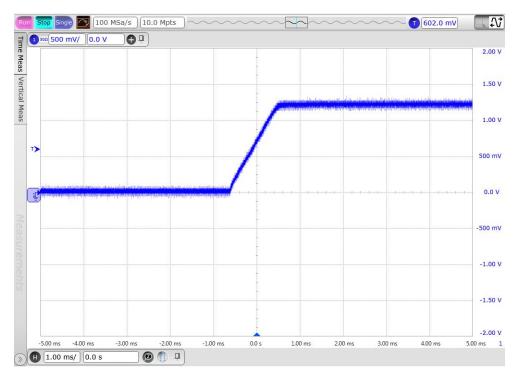

|   | 5.5  | DAC 2                   | 16-bit Functionality Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 77       |

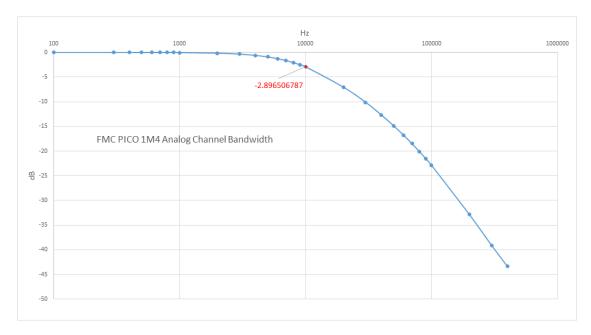

|   | 5.6  | FPGA                    | Mezzanine Card Interface Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 78       |

|   | 5.7  | Signal                  | and Power Integrity Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 81       |

|   |      | Digital                 | and rower integrity integration in the rest of the res |          |

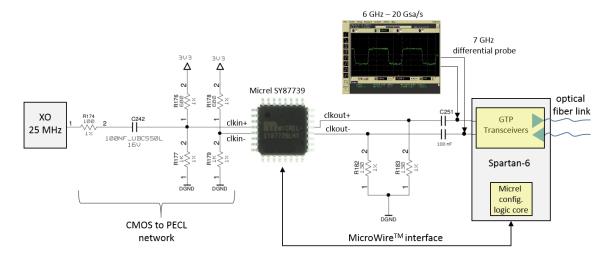

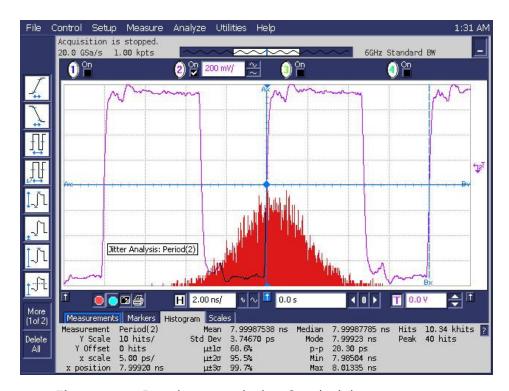

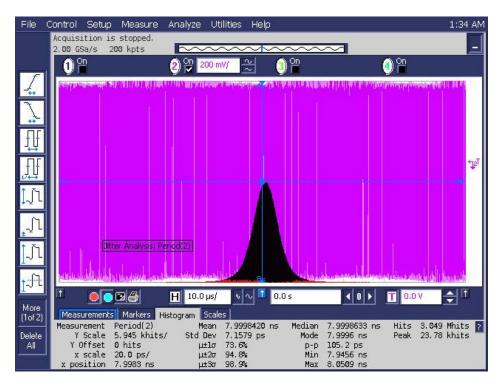

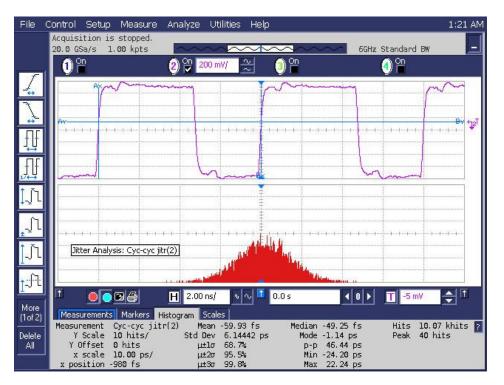

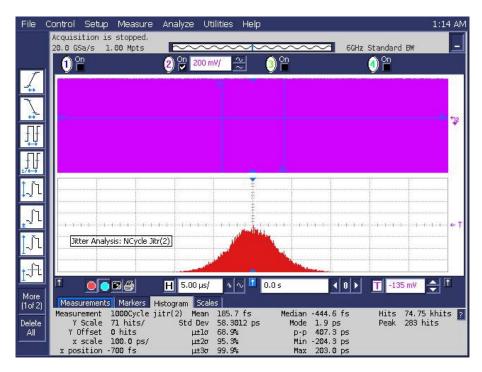

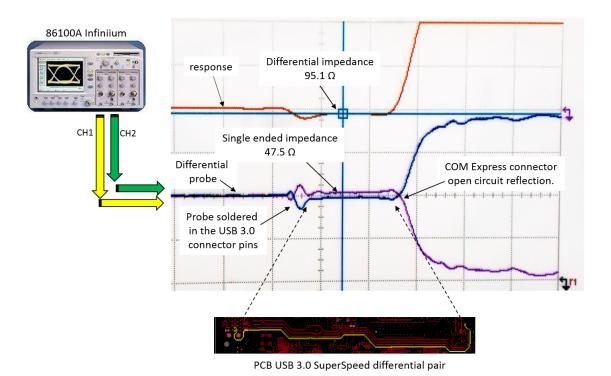

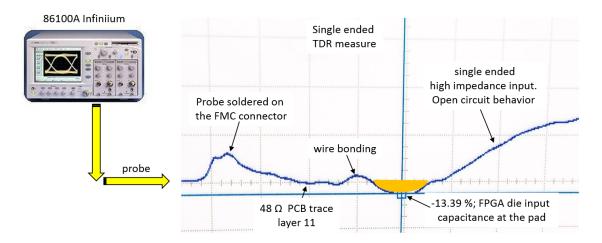

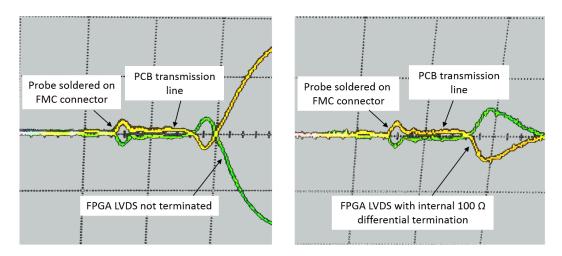

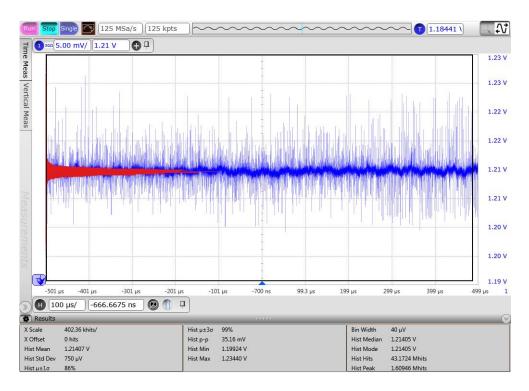

|   |      | 5.7.1                   | Clock Jitter Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 81       |

|   |      | _                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 81<br>87 |

|   |      | 5.7.1                   | Clock Jitter Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

|   | 5.8  | 5.7.1<br>5.7.2<br>5.7.3 | Clock Jitter Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 87       |

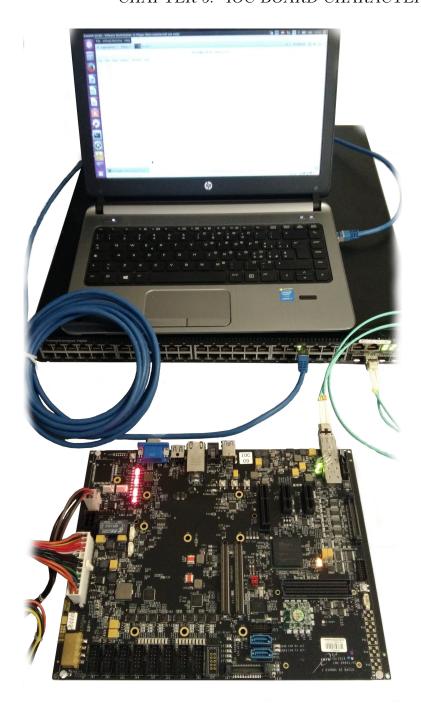

|   | 5.8  | 5.7.1<br>5.7.2<br>5.7.3 | Clock Jitter Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 87<br>90 |

CONTENTS

| 6                                    | Bea   | m Diagnostic Data Readout System                       | 105         |  |

|--------------------------------------|-------|--------------------------------------------------------|-------------|--|

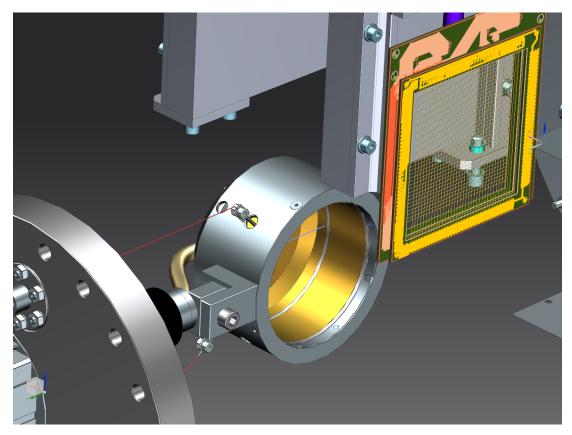

|                                      | 6.1   | Beam Diagnostic Instruments                            | 106         |  |

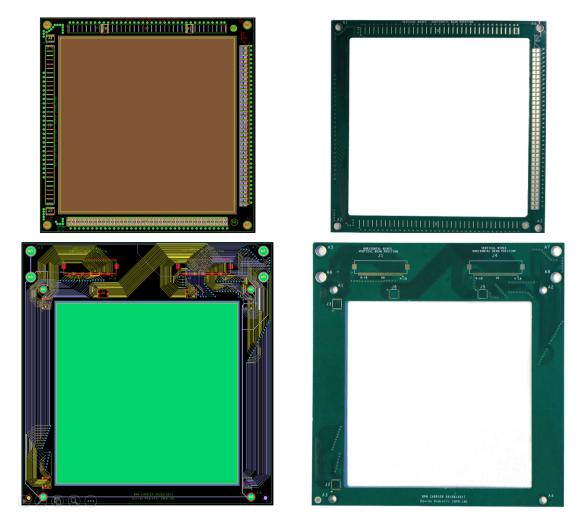

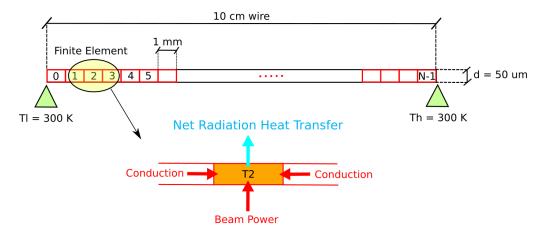

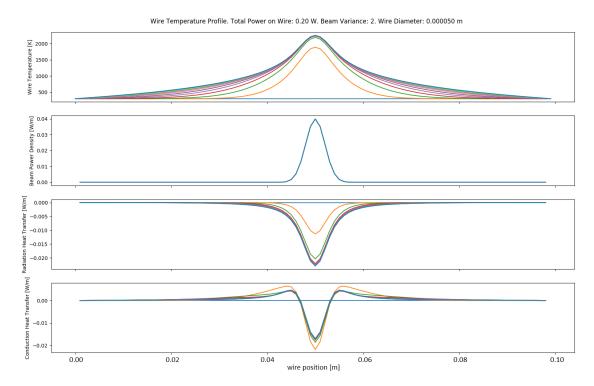

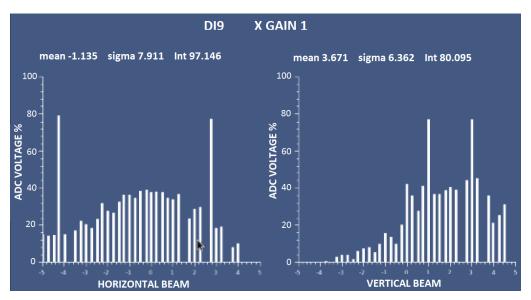

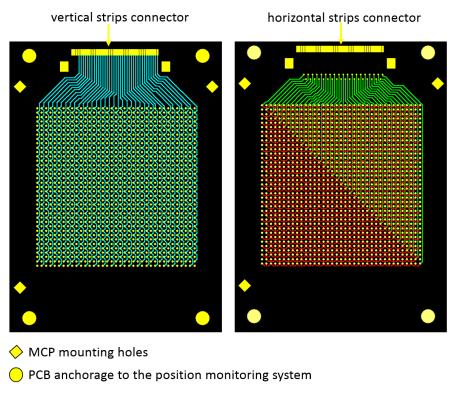

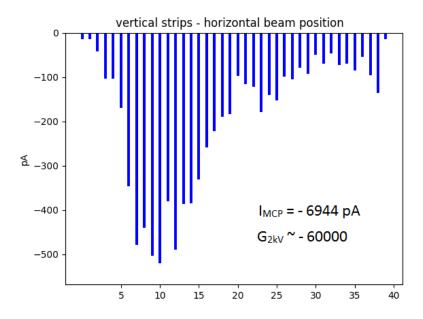

|                                      |       | 6.1.1 Beam Profile Monitor                             | 107         |  |

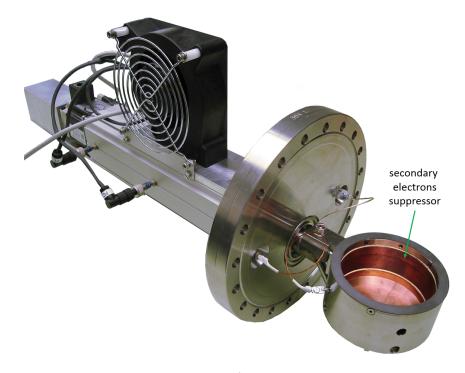

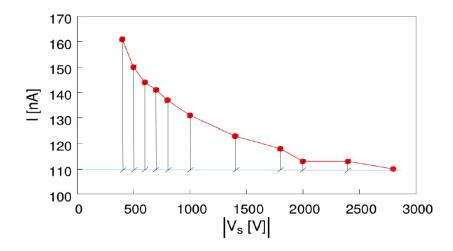

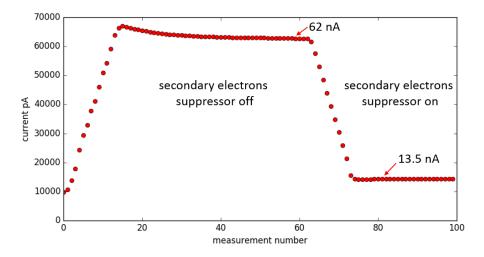

|                                      |       | 6.1.2 Faraday Cup                                      | 113         |  |

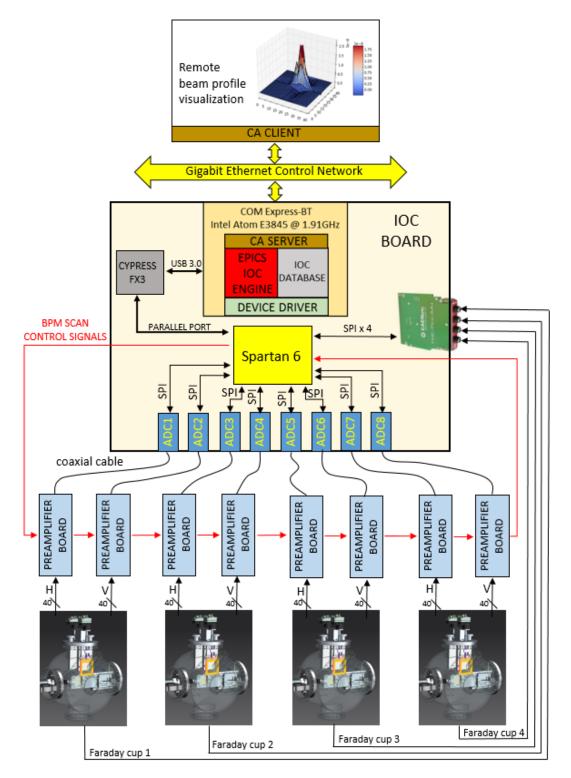

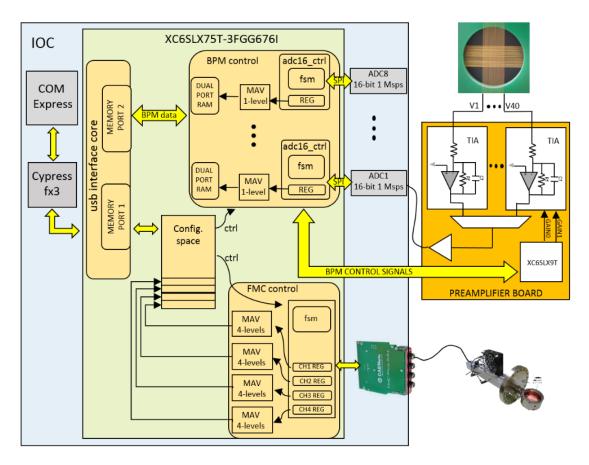

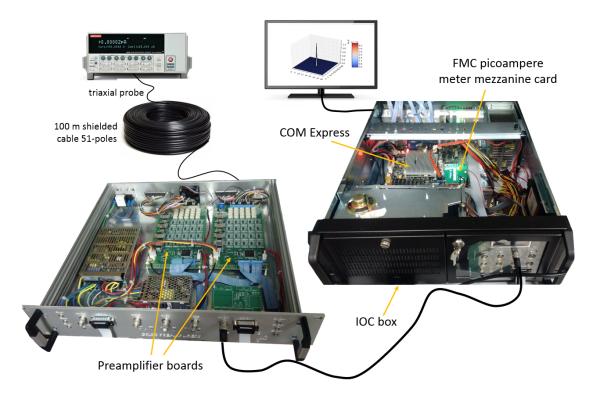

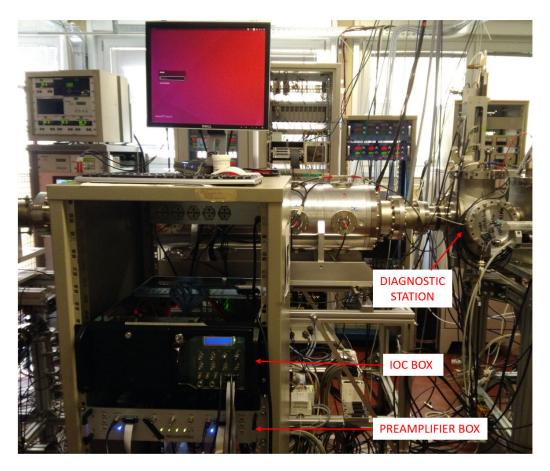

| 6.2 Diagnostics Readout Architecture |       |                                                        |             |  |

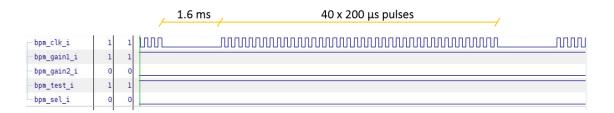

|                                      |       | 6.2.1 Diagnostic Data Digital Processing               | 117         |  |

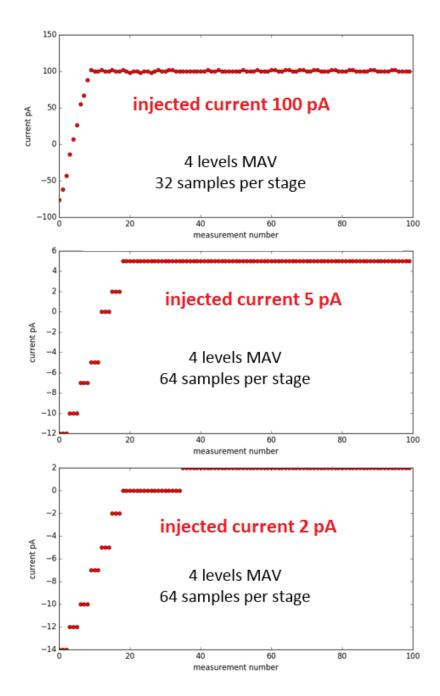

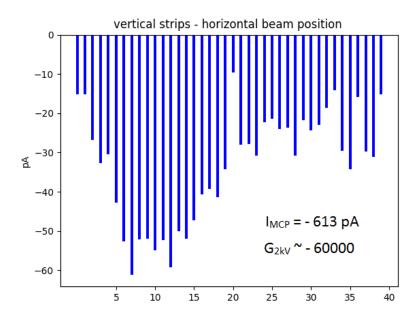

|                                      | 6.3   | Current Sensitivity Tests                              | 121         |  |

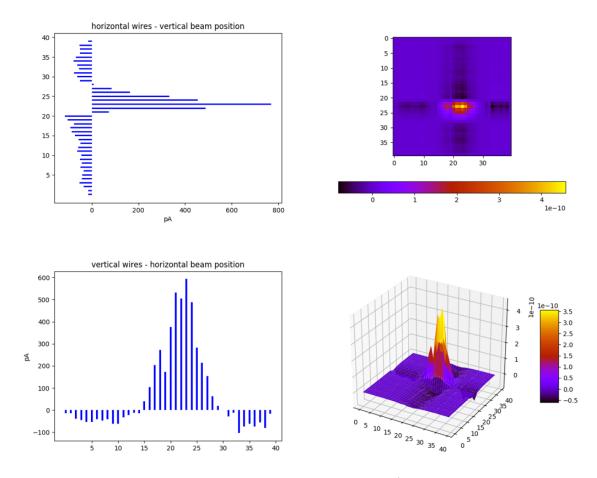

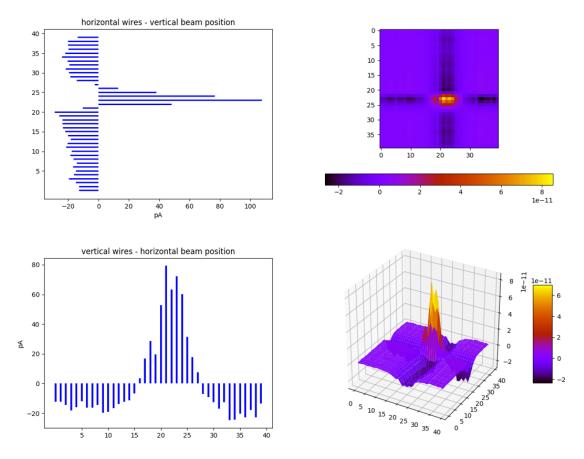

| 6.4 Real Beam Measurements           |       |                                                        |             |  |

|                                      |       | 6.4.1 Integration of the New Diagnostic System in ALPI | 128         |  |

|                                      |       | 6.4.2 Micro-Channel Plate Detectors                    | 130         |  |

| 7                                    | Cor   | nclusions                                              | 133         |  |

|                                      | 7.1   | PhD Project Outcome                                    | 133         |  |

|                                      | 7.2   | IOC Board Applications                                 | 136         |  |

| Bi                                   | bliog | graphy                                                 | 139         |  |

| $\mathbf{A}$                         | Pyt   | hon Code - Wire Temperature Profile                    | 147         |  |

| В                                    | Mat   | tlab Code - ENOB Calculation                           | <b>15</b> 1 |  |

VI CONTENTS

# List of Figures

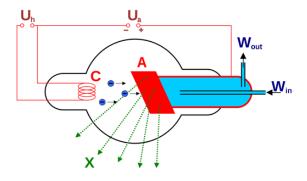

| 1.1  | X-Ray tube                                                               | 1  |

|------|--------------------------------------------------------------------------|----|

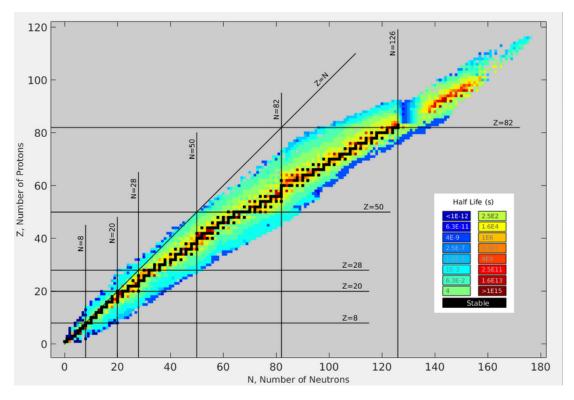

| 1.2  | Stability valley                                                         | 2  |

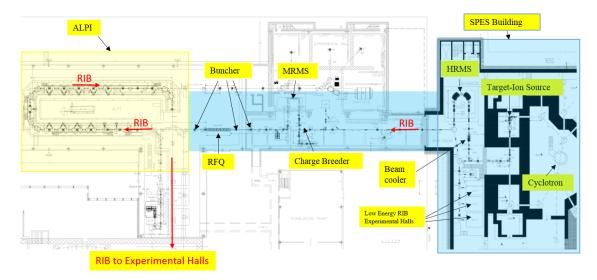

| 1.3  | The SPES facility layout                                                 | 5  |

| 1.4  | The 70 MeV cyclotron installed at LNL                                    | 6  |

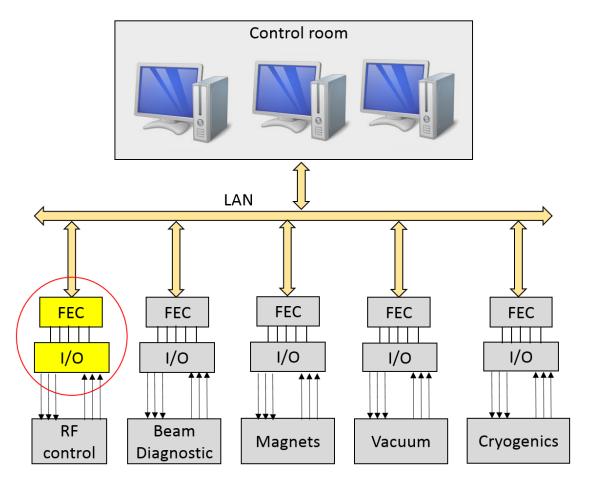

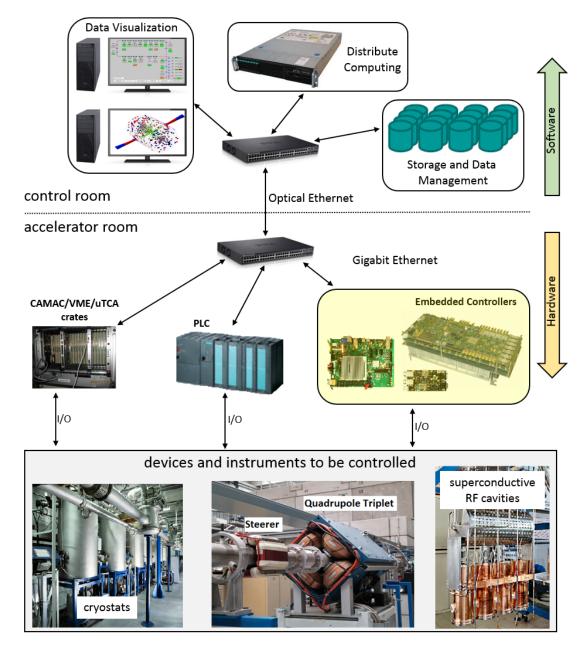

| 1.5  | The SPES control system architecture                                     | 8  |

| 1.6  | SPES control system technology                                           | 10 |

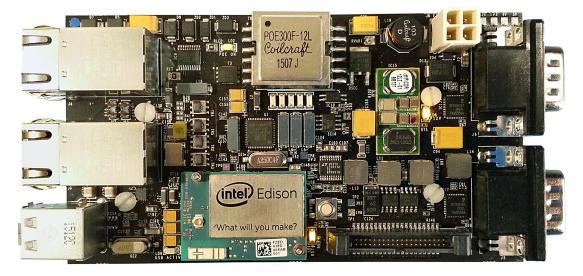

| 2.1  | Intel <sup>®</sup> Edison computing platform                             | 14 |

| 2.2  | Intel <sup>®</sup> Edison carrier board                                  | 15 |

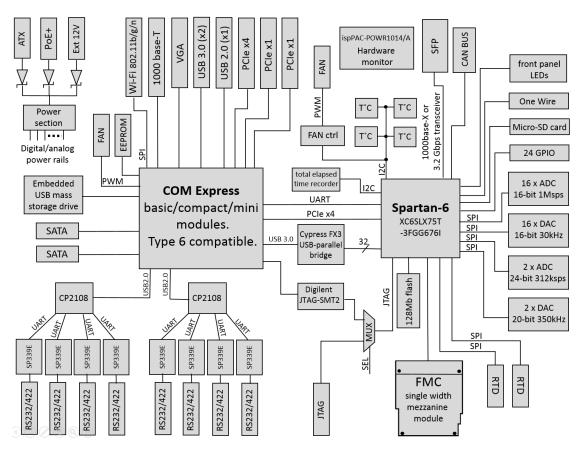

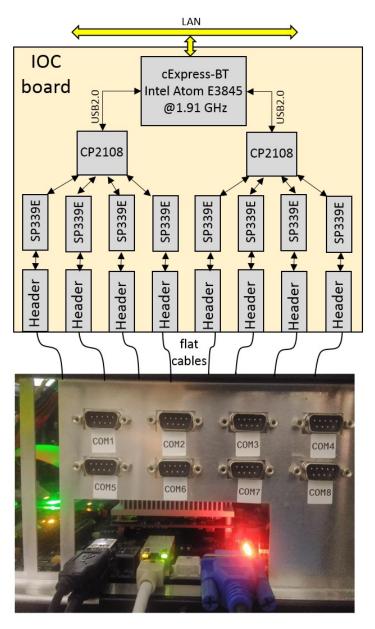

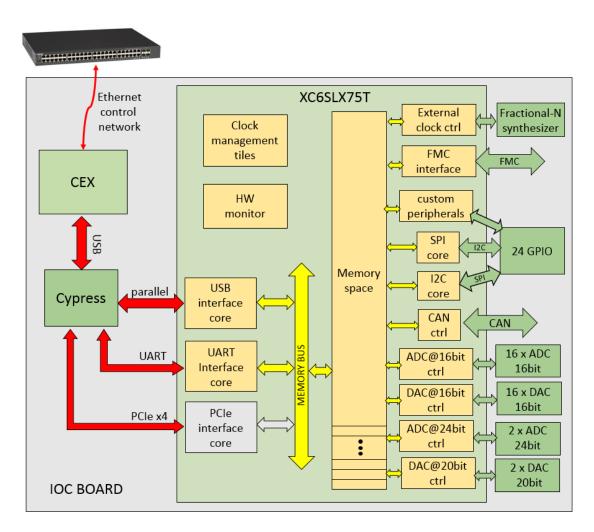

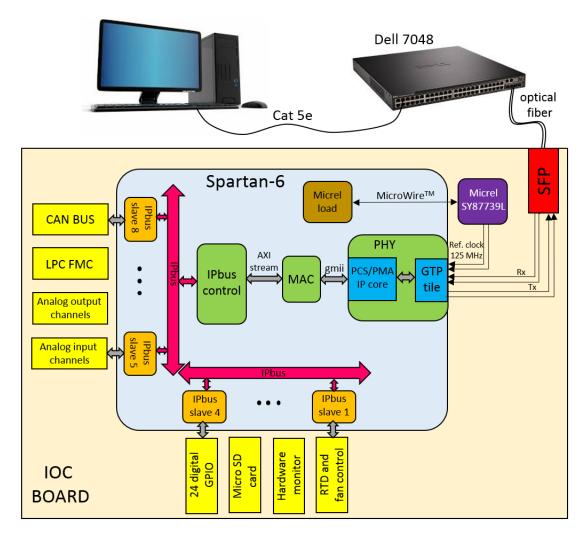

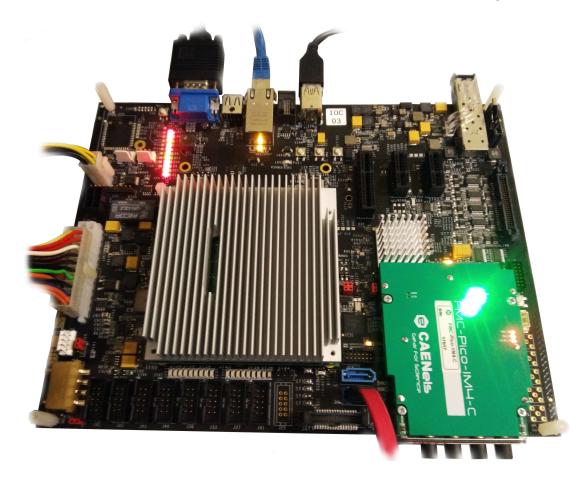

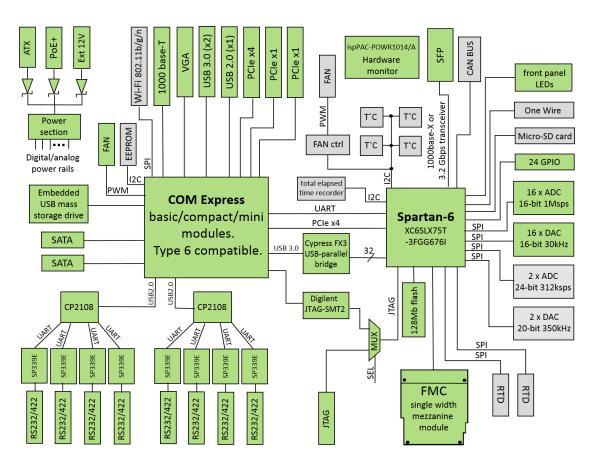

| 2.3  | IOC board block diagram                                                  | 17 |

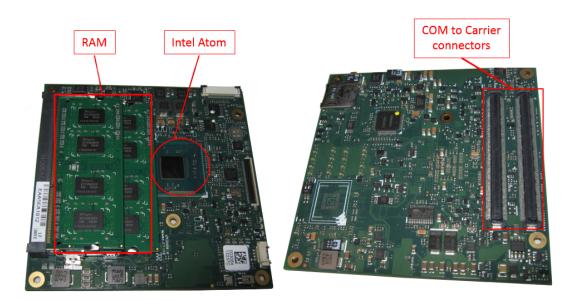

| 2.4  | COM Express cExpress-BT type 6 module. Top and bottom views.             | 19 |

| 2.5  | IOC box rear panel serial ports                                          | 21 |

| 2.6  | Embedded USB mass storage drive                                          | 22 |

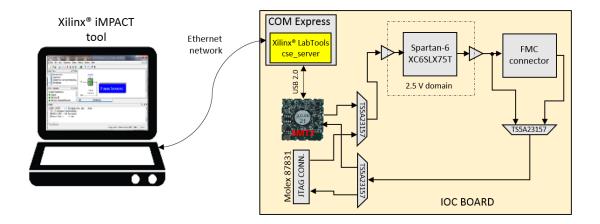

| 2.7  | JTAG chain and FPGA remote reconfiguration and debug tools               | 26 |

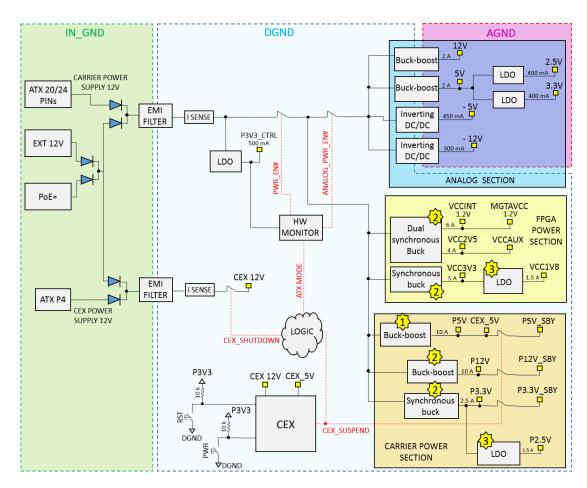

| 2.8  | IOC board power distribution network                                     | 28 |

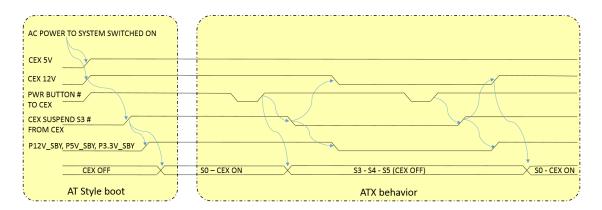

| 2.9  | AT style power-up boot and the ATX style emulation using the             |    |

|      | suspend S3 signal                                                        | 31 |

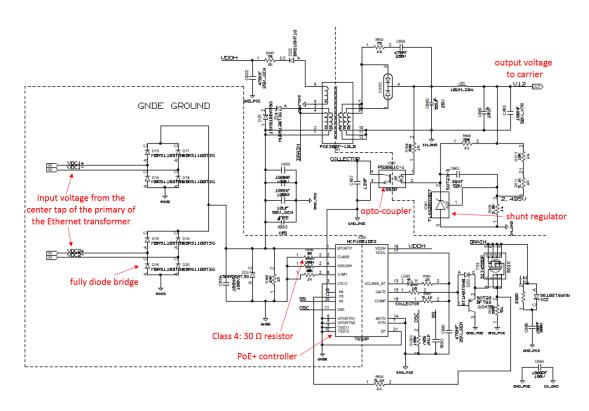

| 2.10 | $\mbox{PoE}+$ schematics. Isolated Fly-back converter with extra winding | 32 |

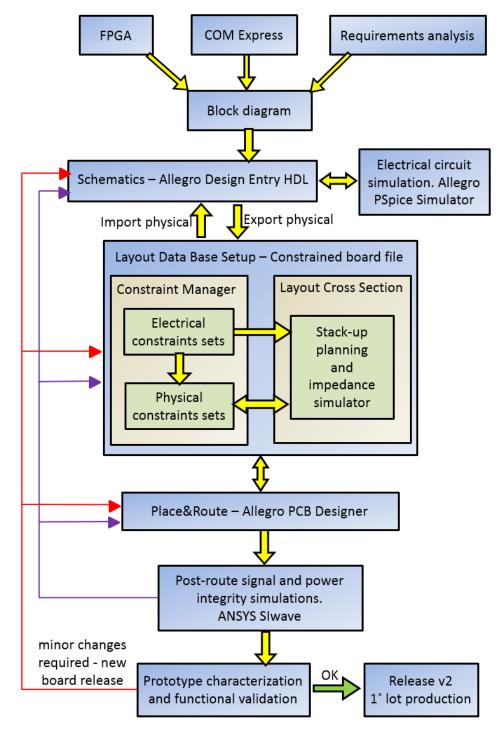

| 3.1  | IOC board workflow                                                       | 34 |

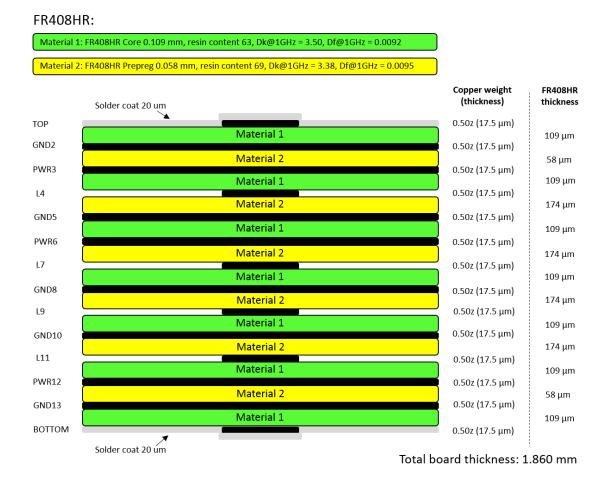

| 3.2  | IOC board stack-up                                                       | 37 |

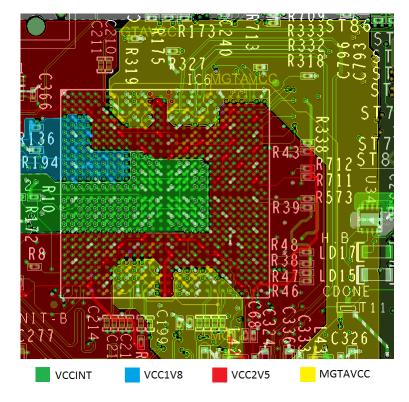

| 3.3  | PWR3 layer, FPGA power distribution                                      | 38 |

| 3.4  | Physical constraints mapping to the Allegro constraint manager           | 39 |

| 3.5  | IOC layout data base setup                                               | 40 |

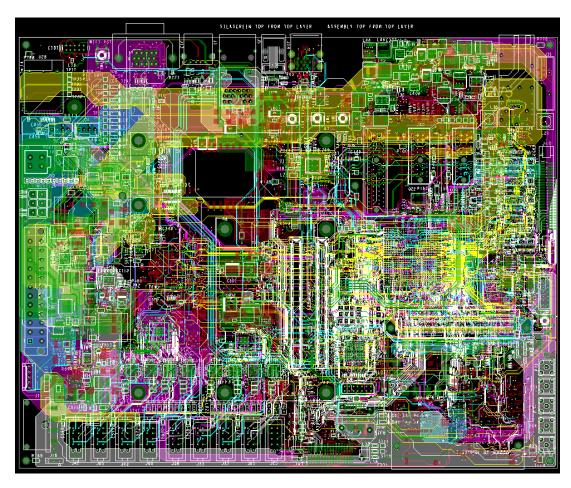

| 3.6  | IOC placement top                                                        | 42 |

| 3.7  | IOC placement bottom                                                     | 43 |

| 3.8  | Ground plane bridges for traces                                          | 43 |

| 3.9  | IOC board fully routed; layers top, bottom, L4, L7, L9 and L11 on.       | 44 |

VIII LIST OF FIGURES

| 3.10 | Simulation performed using SIwave                                    | 45 |

|------|----------------------------------------------------------------------|----|

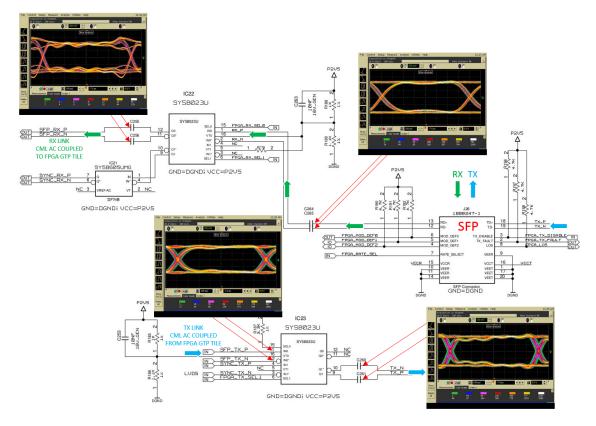

| 3.11 | Impedance delay plot of the SFP RX pair                              | 46 |

| 3.12 | Transient analysis of the SFP RX pair                                | 47 |

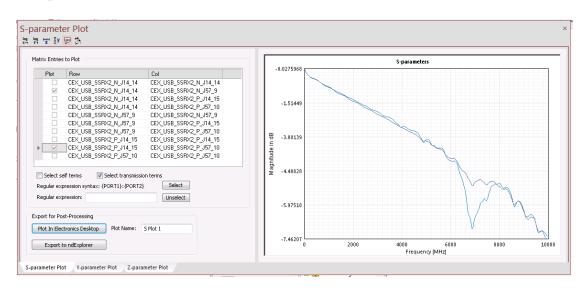

| 3.13 | Scattering parameters S21: forward transmission terms for the USB    |    |

|      | super speed RX pair two port networks                                | 48 |

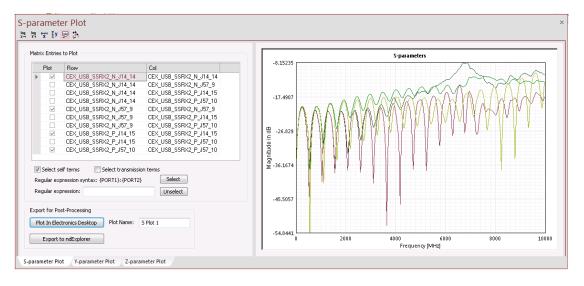

| 3.14 | USB super speed RX pair return terms                                 | 48 |

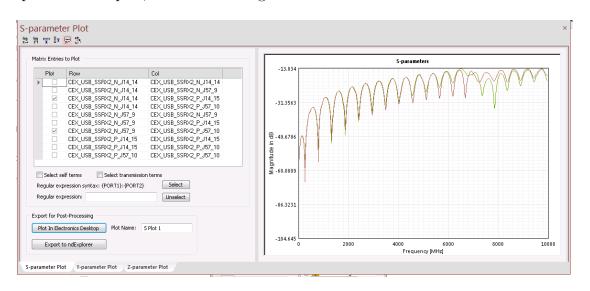

| 3.15 | USB super speed RX pair coupling terms                               | 49 |

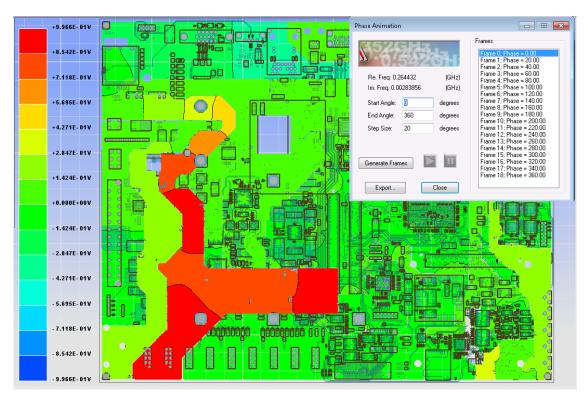

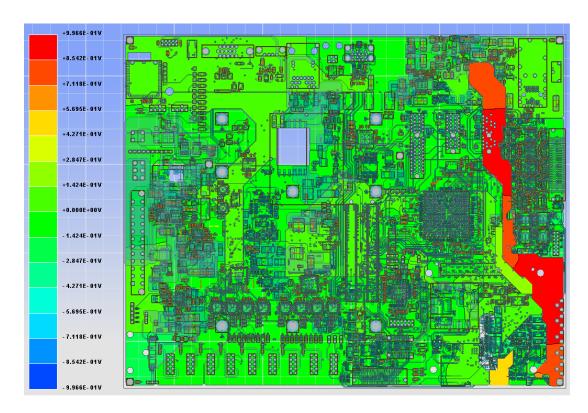

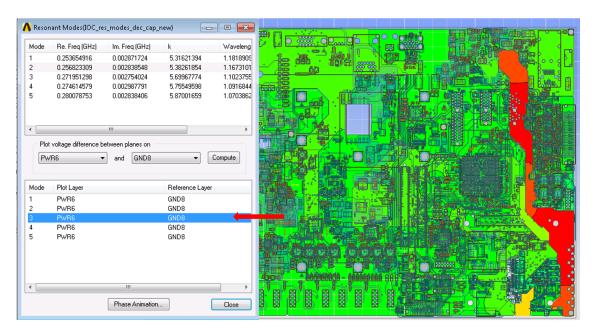

| 3.16 | Voltage distribution between PWR6 and GND8 induced by the res-       |    |

|      | onant mode 3 that occurs at 264 MHz                                  | 50 |

| 3.17 | Voltage distribution between PWR6 and GND8 induced by the res-       |    |

|      | onant mode 4 that occurs at 272 MHz                                  | 51 |

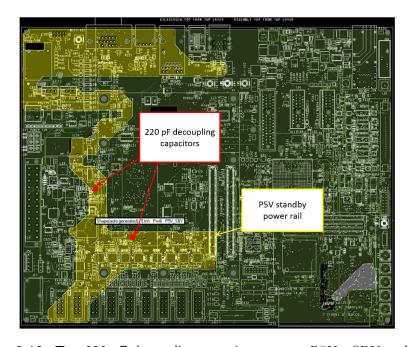

| 3.18 | Two 220 pF decoupling capacitors across $P5V\_SBY$ and GND           | 51 |

| 3.19 | New resonant modes with decoupling capacitors                        | 52 |

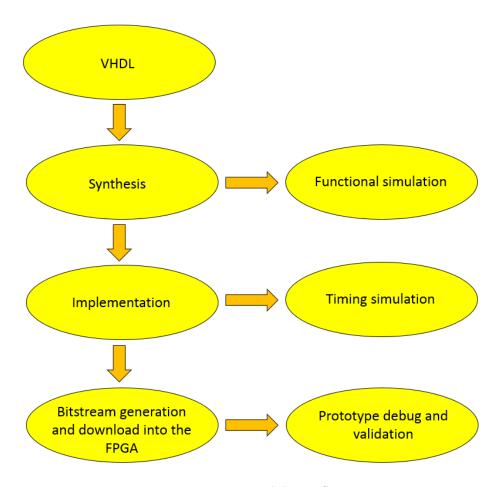

| 4.1  | Digital design flow                                                  | 54 |

| 4.2  | RTL design overview                                                  | 55 |

| 4.3  | UART interface core overview                                         | 59 |

| 4.4  | USB interface core. In this example we have only one memory port,    |    |

|      | one input stream port, and one output stream port. Multiple ports    |    |

|      | configurations are allowed                                           | 61 |

| 4.5  | ADC 16-bit control and data acquisition via the USB interface core.  | 63 |

| 4.6  | IOC board control via IPbus                                          | 64 |