# High Voltage Step-up Multi-output DC/DC Converters for Power Conversion Systems

By

Sen Song

Ph.D.

A thesis submitted in accordance with the requirements for the award of the degree of *Doctor of Philosophy* of the University of Liverpool

October 2019

I would like to dedicate this thesis to my loving girlfriend and my parents

#### Declaration

I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other University. This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration, except where specifically indicated in the text.

The copyright of this thesis rests with the author. Copies (by any means) either in full, or of extracts, may not be made without prior written consent from the author. Copyright © 2019 Sen Song, all rights reserved.

Song, Sen 2019

# Acknowledgements

First and foremost, I would like to express my deepest gratitude to my primary supervisor Dr. Hu Yihua, for granting me the precious opportunity to test myself at the highest level. He has encouraged and helped me to grow up from a fresh graduate student to a professional researcher. I learned so much from Dr. Hu both academically and personally. Thanks for the invaluable comments and advice on my research as well as my life and career. Secondly, I would also like to thank my second supervisor Dr. Jiang Lin, and Dr. Chen Guipeng, for the generous support and academic guidance they have provided to me. I will always treasure their support, encouragement and guidance.

I would also like to thank my parents, especially my mother. They have always supported me with no expectation of a reward. Their continuous help and understanding have made my life full of love, and I am grateful for everything they have done. I would also like to express my appreciation to my girlfriend Li Shuang. I would never have succeeded without her love, tolerance, support, encouragement and patience. This work is dedicated to her.

Special thanks are also paid to my brilliant and lovely colleagues and friends; in particular to Li Xinhua, Ni Kai, Zhang Yixuan, Wu Zuyu, Gong Chao, Xie Lujia, Zhao Zhiyi, Dr. Zhuang Yuan, Dr. Chen Anqi, Xu Chen, for many fruitful discussions and enjoyable moments.

Last but not least, the support from the Electrical Engineering and Electronics Department of the University of Liverpool is gratefully acknowledged.

# Abstract

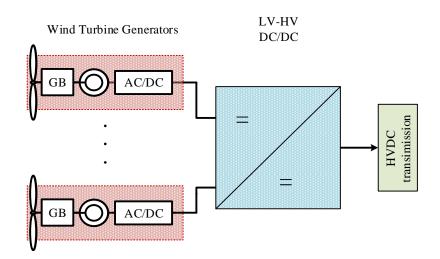

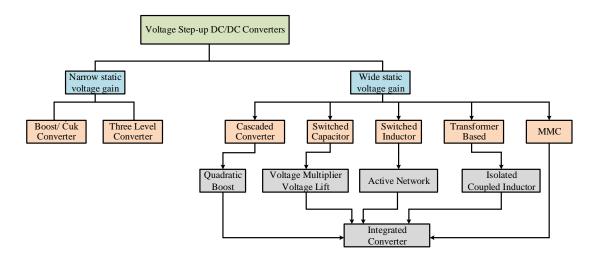

With the increasing development of semiconductor components, solid-state DC/DC converters become popular in power conversion systems. Applications powered by sources with relatively low voltage level such as PV panels, and batteries require high voltage conversation ratios to meet the voltage level of load systems. Additionally, high voltage gain converters are also critical in grid-tied applications such as high voltage direct current (HVDC) transmission systems. Thus, the relatively low voltage level generated from offshore wind turbines or PV panels could be boosted up to the ultra-high line voltage level of HVDC transmission. Although conventional boost converters could achieve high voltage gain theoretically, their switches operate with an excessive duty cycle that degrades the reliability of converters. This thesis proposes the derivation, analysis, and verification of advanced high voltage step-up DC/DC converters that could obtain an improved performance compared with current state-of-the-art topologies.

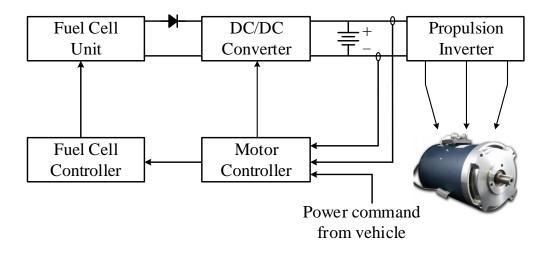

Four novel DC/DC converters that have high step-up voltage ratios are proposed for applications as HVDC transmission systems, light emitting diode (LED) lightings, and electric vehicles respectively as following.

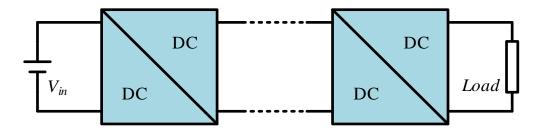

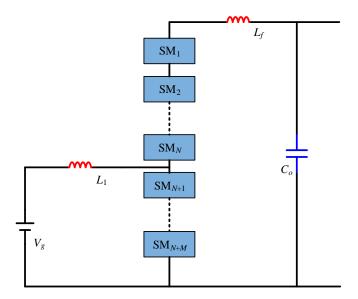

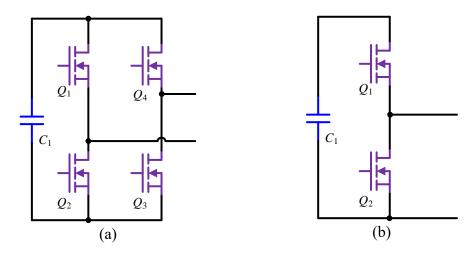

- The matrix configuration is proposed so that converters only suitable for low power applications could be scaled up to meet the requirements of HVDC transmission. Thanks to the matrix configuration, simultaneous ultra-high voltage step-up ratio as well as low voltage/current rating of components, and high reliability are obtained. Additionally, two topologies of submodules (SMs) are designed and installed in the matrix configuration to meet the specific requirements of HVDC transmission of offshore wind farms and large scale solar power plants. Moreover, owing to the design of SMs, the voltage step-up ratios of designed multi-module converters, *G*<sub>boost</sub>, is increased to the number of SMs in series, *N*, times the voltage conversion ratio of SMs, *G*<sub>SM</sub>, as *G*<sub>boost</sub>=*N*×*G*<sub>SM</sub>. Compared with modular multilevel converters (MMCs), the proposed multi-module converters can achieve a higher voltage gain ratio since the output voltage of SMs implemented in MMCs equals to the input voltage.

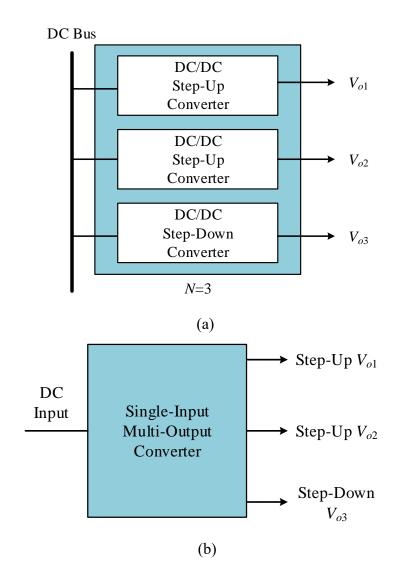

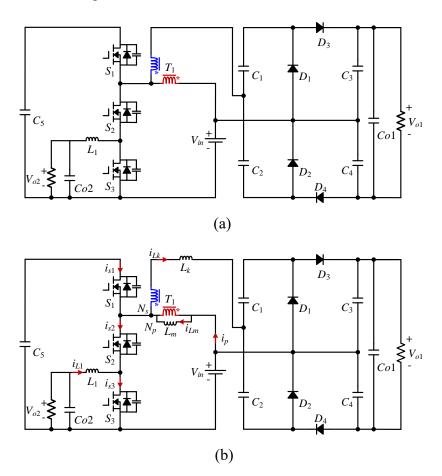

- A stacked multi-output isolated DC/DC converter is proposed for the LED driver. The installation of transformers and switched capacitors enlarge the voltage gain.

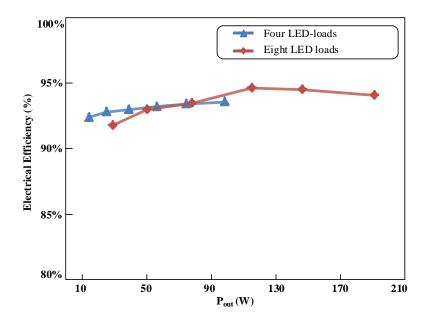

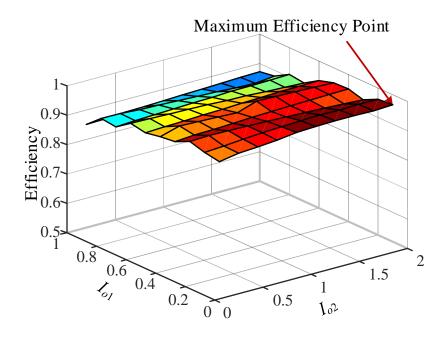

Additionally, compared with two conventional isolated converters, the proposed one could use one less active switch to achieve similar performance, so that the cost is reduced. Moreover, all switches could achieve soft-switching operation. According to the experiment results, the proposed converter can maintain the high power efficiency 92%~94.6% with the output power range from 12 W to 200 W, which exceeds the similar topologies whose active switches are hard-switching.

• Furthermore, a three-switch-based single-input dual-output (SIDO) converter is presented in this thesis. Due to the integration of two switches, the proposed SIDO converter can use one less switch, and the operation performance is similar to that of applying two conventional two single-input single-output converters. Hence, the cost is reduced. Moreover, thanks to the independent power flow and two control variables, the cross regulation performance is improved, and simultaneous buck as well as boost output voltages are realised. According to the experiment results, the voltage error ratio caused by cross regulation problems is reduced to 1.55%, and the maximum power efficiency reaches 96.6%, which shows a better performance than current state-of-the-art SIDO converters.

This thesis has successfully demonstrated several novel topologies for DC/DC power conversion systems. The most challenging issues such as increasing voltage conversion ratios, scale up power converters applied in low power applications for high power applications, and improving power efficiency while keep the low cost at the same time have been overcome by applying the proposed techniques.

Key words: DC/DC converters, high voltage step-up ratio, soft-switching, low cost.

# CONTENTS

| Abstractv                                                                                   |

|---------------------------------------------------------------------------------------------|

| Contentsvii                                                                                 |

| List of Figuresxii                                                                          |

| List of Tablesxvi                                                                           |

| Abbreviationxvii                                                                            |

| Chapter 1. Background1                                                                      |

| 1.1 High Step-up DC/DC Converter Applications                                               |

| 1.1.1 HVDC Transmission                                                                     |

| 1.1.2 LED Driver                                                                            |

| 1.1.3 EV                                                                                    |

| 1.2 Operating Characteristics of High Voltage Step-up Converters 5                          |

| 1.2.1 High Voltage Boost Ratio                                                              |

| 1.2.2 High Power Efficiency5                                                                |

| 1.2.3 Low Current/Voltage Ripple5                                                           |

| 1.2.4 Fast Response5                                                                        |

| 1.3 Aims and Objectives                                                                     |

| 1.4 Thesis Outline7                                                                         |

| Chapter 2. High Voltage Gain DC/DC Converters Techniques-A Literature                       |

| Review9                                                                                     |

| 2.1 Introduction                                                                            |

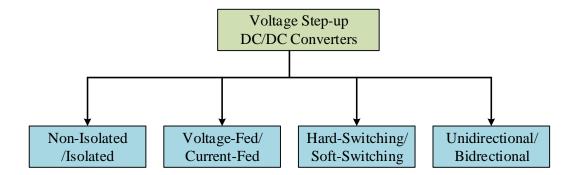

| 2.2 Categories of Voltage Boost DC/DC Converters                                            |

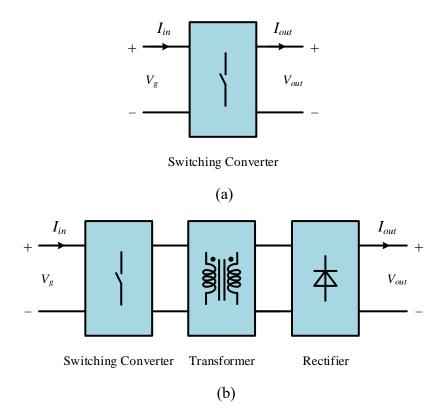

| 2.2.1 Isolated/Non-isolated Converters10                                                    |

| 2.2.2 Unidirectional/Bidirectional Converters                                               |

| <ul><li>2.3 Topology Review of Typical High Voltage Step-Up Converters</li><li>13</li></ul> |

| 2.3.1 Conventional Boost Converter                                                          |

| 2.3.2 Cascaded Converters                                                                   |

|                                                                                             |

| 2.3.3 Quadratic Boost Converter                                                            |

|--------------------------------------------------------------------------------------------|

| 2.3.4 Three Level Boost Converter                                                          |

| 2.3.5 Switched Capacitor Converters                                                        |

| 2.3.6 Voltage Multiplier Circuits                                                          |

| 2.3.7 Switched Inductor Converters                                                         |

| 2.3.8 Isolated Boost Converters                                                            |

| 2.3.9 Coupled Inductor Converters                                                          |

| 2.3.10 Modular Multilevel Converters                                                       |

| 2.3.11 Integrated Converters                                                               |

| 2.4 Classification of DC/DC converters by Voltage Gain                                     |

| 2.5 Converter Control Method                                                               |

| 2.5.1 Voltage Control                                                                      |

| 2.5.2 Current Control                                                                      |

| 2.6 Switching Strategy                                                                     |

| 2.6.1 Hard-switching                                                                       |

| 2.6.2 Soft-switching                                                                       |

| 2.7 Failure Mechanism                                                                      |

| 2.7.1 Failure Type                                                                         |

| 2.7.2 Diode Failure Indications                                                            |

| 2.7.3 Transistor Failure Indications                                                       |

| 2.8 Summary                                                                                |

| Chapter 3. Multi-port High Voltage Gain Modular Power Converter for<br>Offshore Wind Farms |

| 3.1 Introduction                                                                           |

| 3.2 Design of the Proposed Multi-module Converter                                          |

| 3.2.1 Design and Operation of the SM                                                       |

| 3.2.2 Design and Operation of the Matrix Configuration                                     |

|                    | 3.3 | An  | alysis of the Proposed Multi-module Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47 |

|--------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                    | 3.  | 3.1 | Scalable Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47 |

|                    | 3.  | 3.2 | High Voltage Step-up Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49 |

|                    | 3.  | 3.3 | Current Balance with Column Interleaved Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49 |

|                    | 3.  | 3.4 | Closed Loop Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50 |

|                    | 3.4 | Fa  | alt Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51 |

|                    | 3.4 | 4.1 | Fault Tolerance for WTGs with Different Output Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51 |

|                    | 3.4 | 4.2 | Redundancy Fault Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52 |

|                    | 3.4 | 4.3 | Fault Tolerance of Short-circuited Diodes and Failed SMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52 |

|                    | 3.4 | 4.4 | Fault Tolerance of Open-circuited Diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53 |

|                    | 3.5 | Sir | nulation Verification and Comparison Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54 |

|                    | 3.  | 5.1 | Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54 |

|                    | 3.  | 5.2 | Comparison Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59 |

|                    | 3.6 | Su  | mmary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60 |

| Chapter 4.<br>Inte |     |     | alar Multi-port Ultra-high Power Level Power Convertion to the term of ter |    |

|                    | 4.1 | Int | roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 61 |

|                    | 4.2 | An  | alysis of the Basic Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65 |

|                    | 4.  | 2.1 | Design of the Basic Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65 |

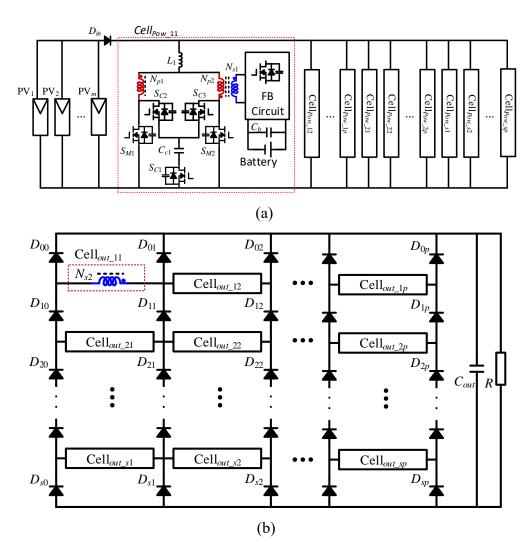

|                    | 4.  | 2.2 | Operation of the Basic cell with PV Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66 |

|                    | 4.  | 2.3 | Operation of the Basic Cell without PV Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 71 |

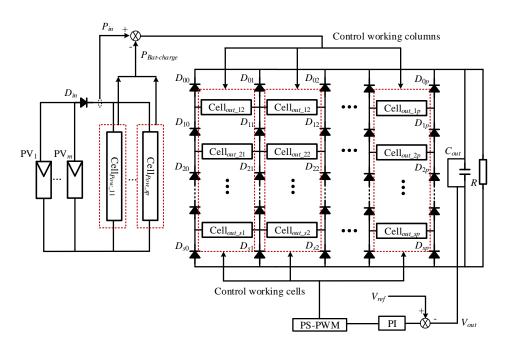

|                    | 4.3 | An  | alysis of the Proposed Multi-module Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75 |

|                    | 4.  | 3.1 | Voltage Gain of the Scalable Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76 |

|                    | 4.  | 3.2 | Voltage/Current Rating of Semiconductor Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77 |

|                    | 4.  | 3.3 | Control Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 78 |

|                    | 4.4 | Fa  | ult Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 78 |

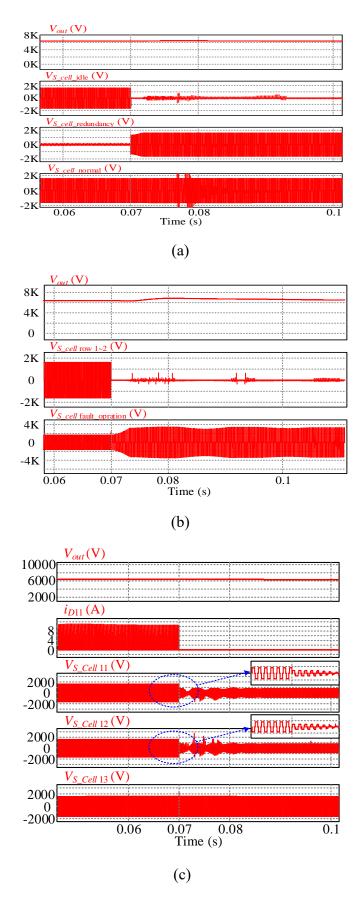

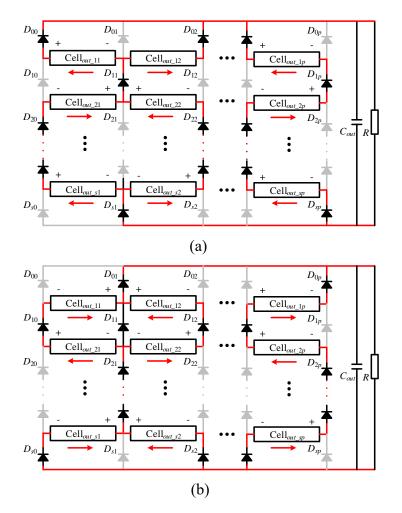

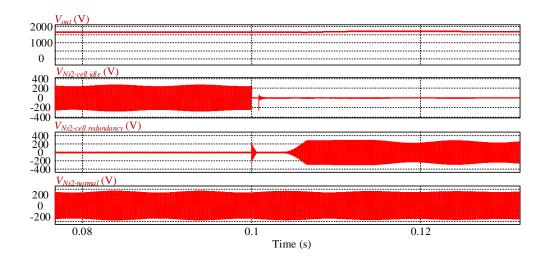

|                    | 4.  | 4.1 | Redundancy Fault Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 78 |

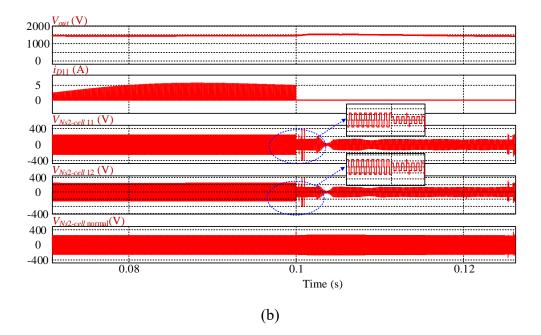

| 4.4.2 Fault Tolerance of Short-circuited Diodes and Failed SMs79        |

|-------------------------------------------------------------------------|

| 4.4.3 Fault Tolerance of Open-circuited Diodes                          |

| 4.4.4 DC Fault Tolerance                                                |

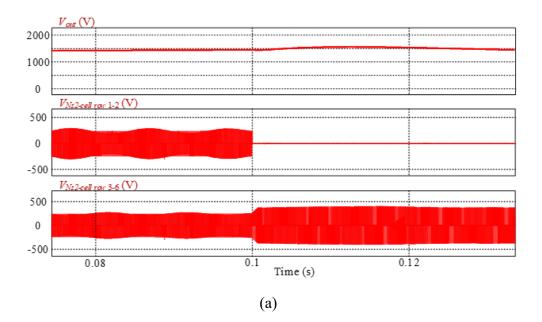

| 4.5 Simulation Verification and Discussion                              |

| 4.6 Summary                                                             |

| Chapter 5. Multi-output LED Driver Integrated with 3-Switch Converter & |

| Passive Current Balance for Portable Application                        |

| 5.1 Introduction                                                        |

| 5.2 Operation Mode Discussion                                           |

| 5.3 Topology Characteristics Analysis                                   |

| 5.3.1 Passive Current Balancing                                         |

| 5.3.2 Operation of Resonant Capacitors                                  |

| 5.3.3 Control System                                                    |

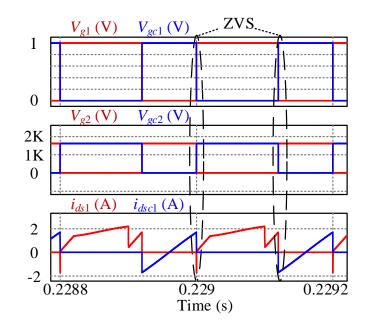

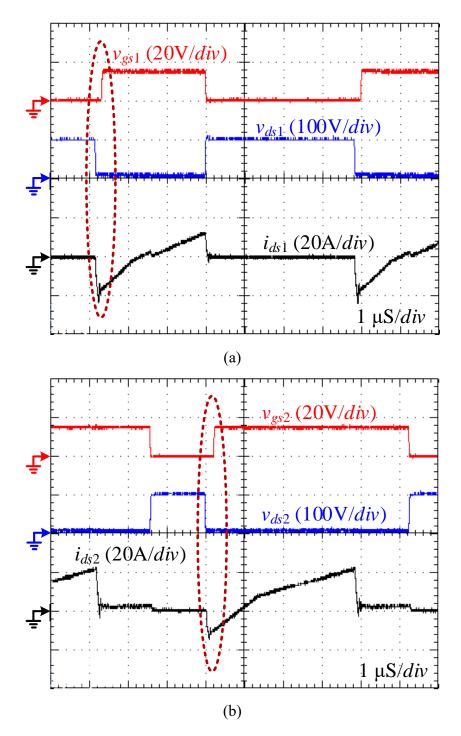

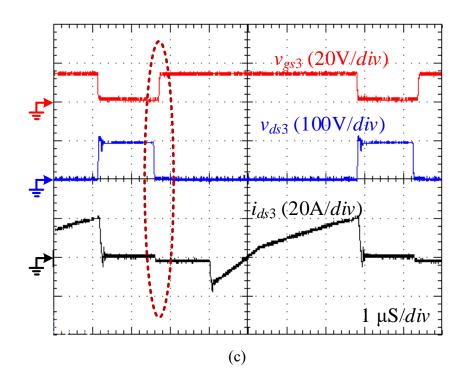

| 5.3.4 Soft-switching Analysis 100                                       |

| 5.3.5 Expandable Topology 101                                           |

| 5.4 Design Guide101                                                     |

| 5.4.1 Passive Current Balancing 102                                     |

| 5.4.2 Maximum Voltage and Current of Switches 103                       |

| 5.4.3 Voltage Variation of Resonant Capacitors                          |

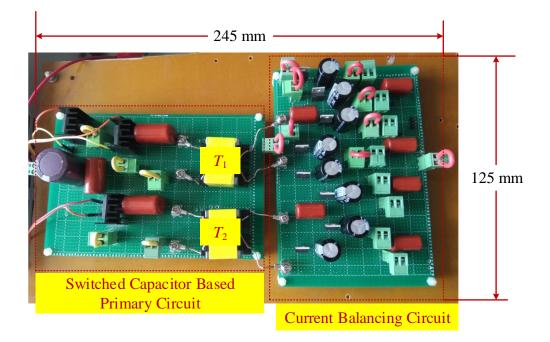

| 5.5 Experiment Verification and Comparison Results                      |

| 5.5.1 Hardware                                                          |

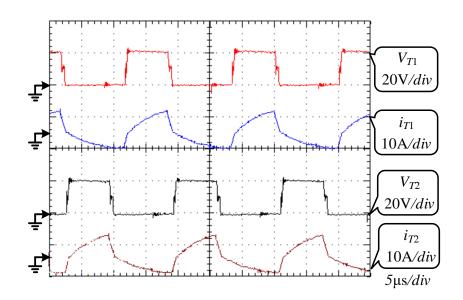

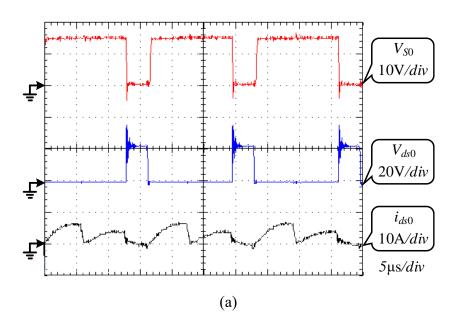

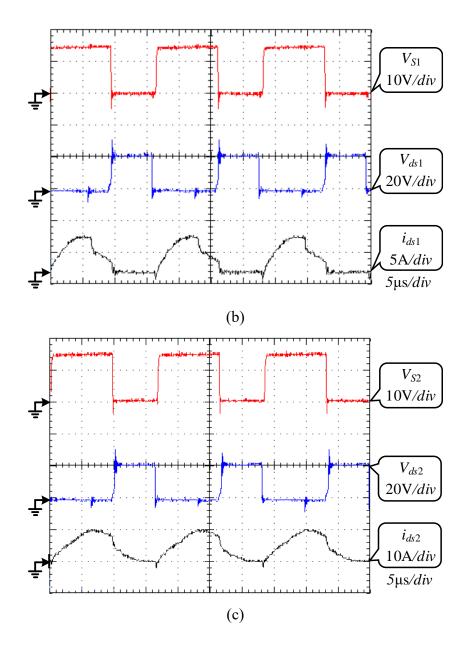

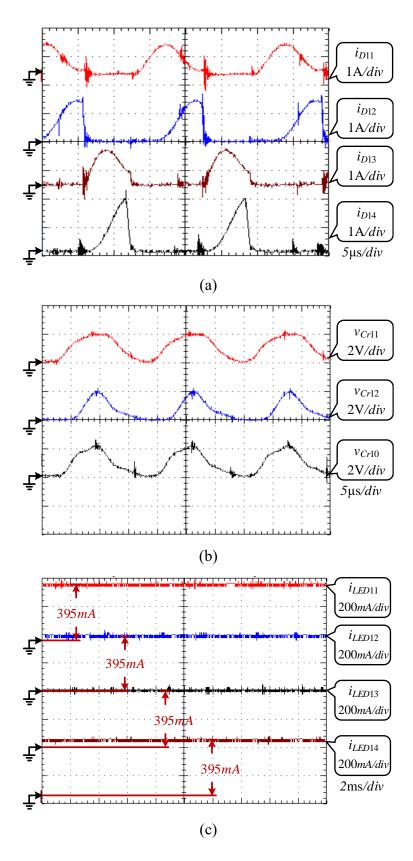

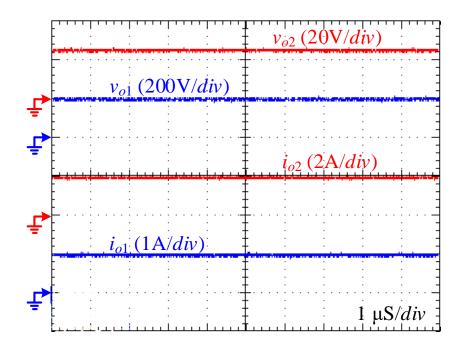

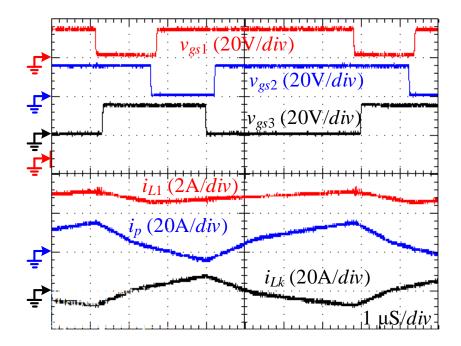

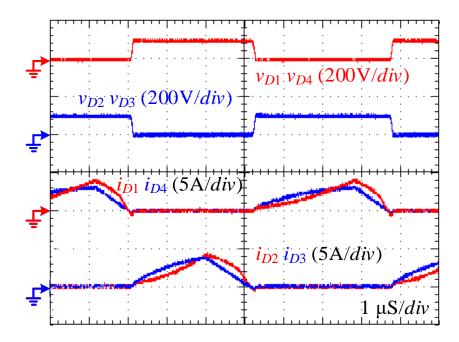

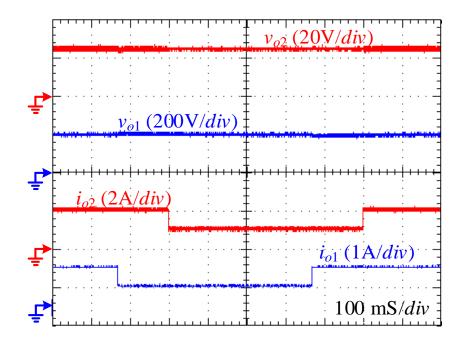

| 5.5.2 Experiment Results 105                                            |

| 5.5.3 Comparison Results 109                                            |

| 5.6 Summary 110                                                         |

| Chapter 6. A Three-Switch-Based Single-Input Dual-Output Converter with |

| Simultaneous Boost & Buck Voltage Conversion                            |

| 6.1 Introduction                                                        |

| 6.2 Operation Principles                                                |

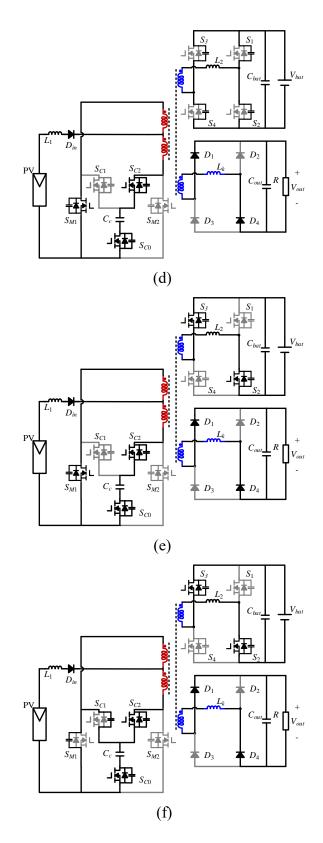

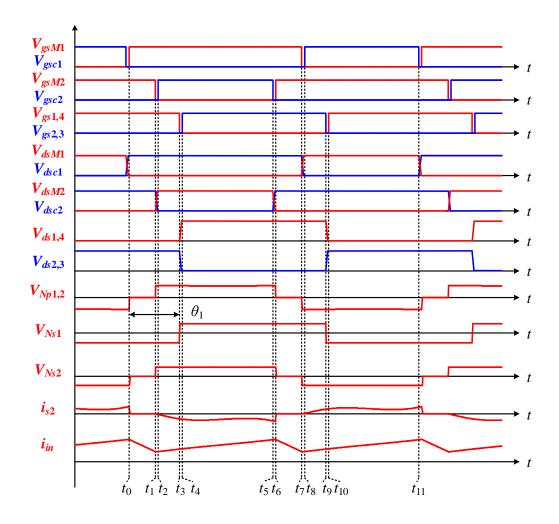

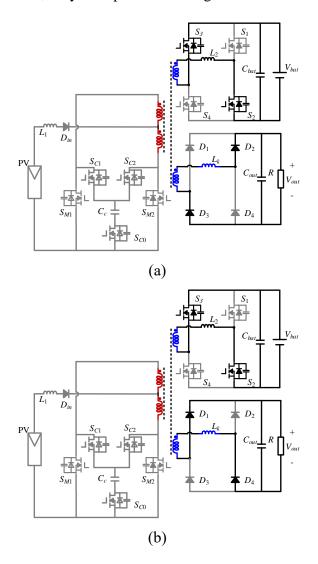

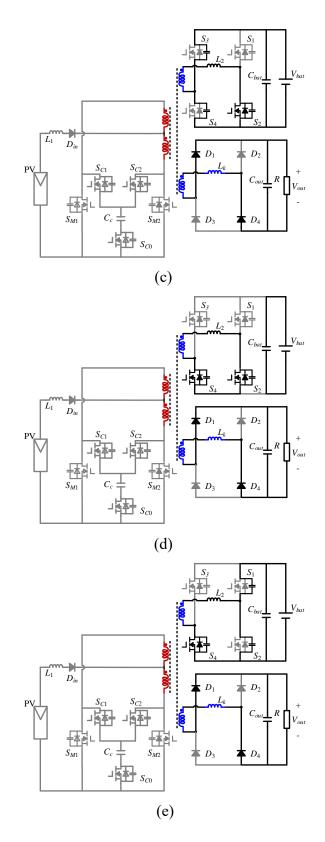

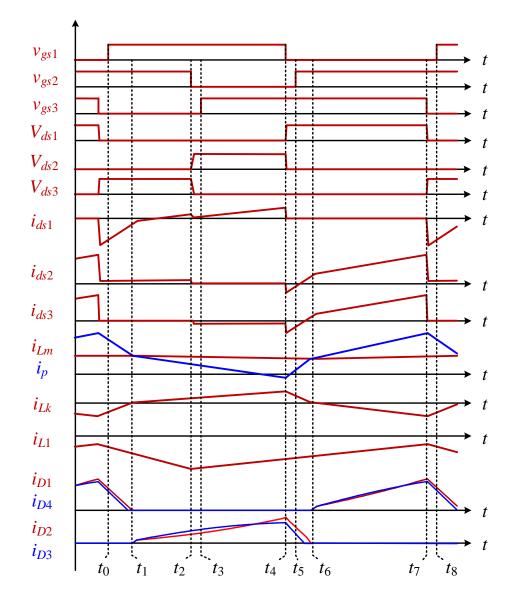

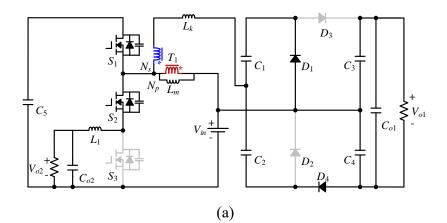

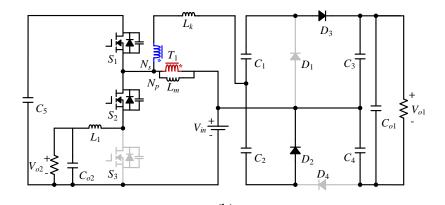

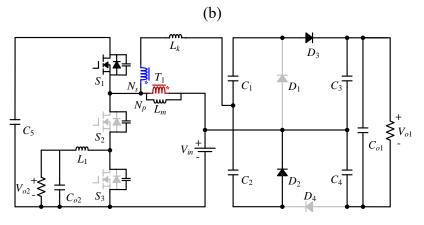

| 6            | .2.1  | Operation Modes Analysis                         |

|--------------|-------|--------------------------------------------------|

| 6            | .2.2  | Voltage Gain 120                                 |

| 6.3          | De    | sign Consideration and Analysis121               |

| 6            | .3.1  | Design Consideration 121                         |

| 6            | .3.2  | Reduced Switch Count                             |

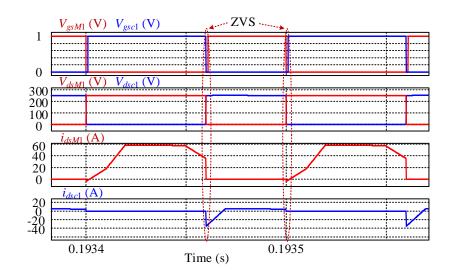

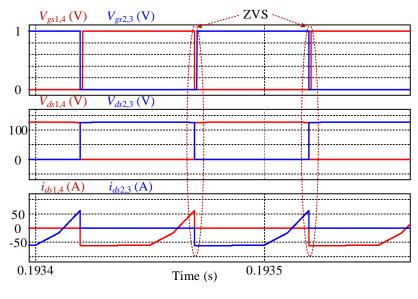

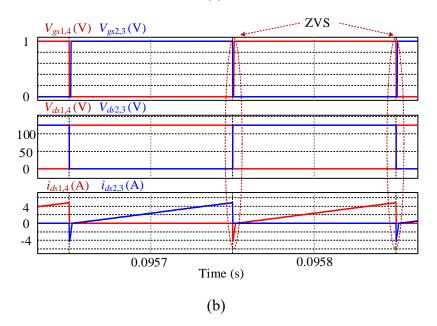

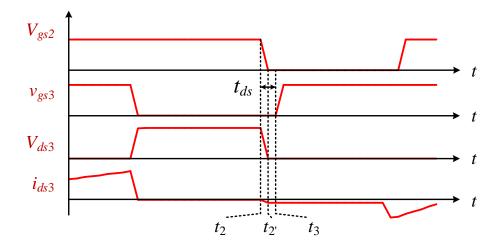

| 6            | .3.3  | ZVS Operation                                    |

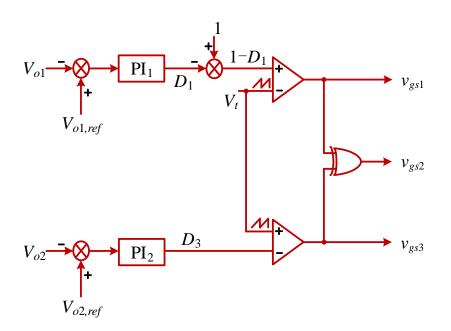

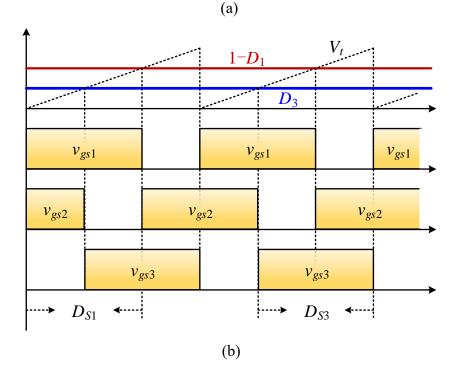

| 6            | .3.4  | Closed Loop Control                              |

| 6.4          | Ex    | periment Verification and Comparison Results 125 |

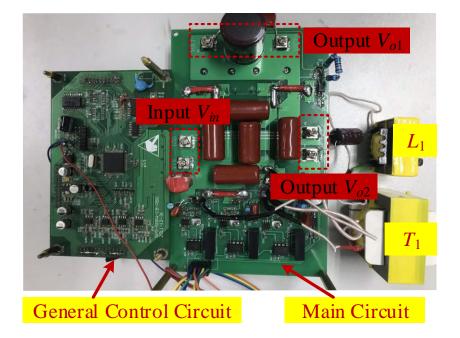

| 6            | .4.1  | Hardware                                         |

| 6            | .4.2  | Experiment Results 127                           |

| 6            | .4.3  | Comparison Results                               |

| 6.5          | Su    | mmary                                            |

| Chapter 7. C | Concl | lusion                                           |

| 7.1          | Su    | mmary                                            |

| 7.2          | Ke    | y Contributions138                               |

| 7.3          | Fu    | ture Work140                                     |

| 7.4          | Pu    | blications Arising from this Research141         |

| Reference    |       |                                                  |

# **LIST OF FIGURES**

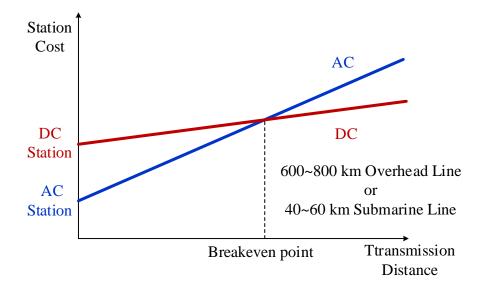

| Figure 1.1 Distance versus cost for HVAC and HVDC cables [8-10]                          |

|------------------------------------------------------------------------------------------|

| Figure 2.1 Categories of voltage boost DC/DC converters                                  |

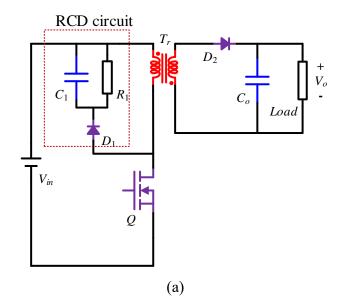

| Figure 2.2 Schematic of non-isolated and isolated converters: (a) non-isolated; (b)      |

| isolated                                                                                 |

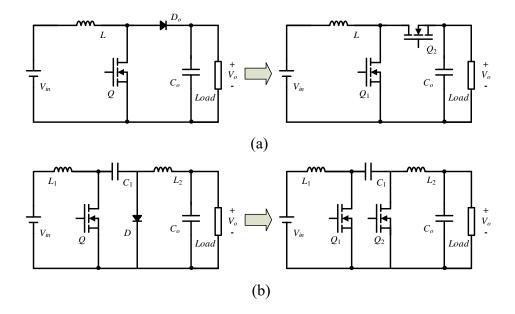

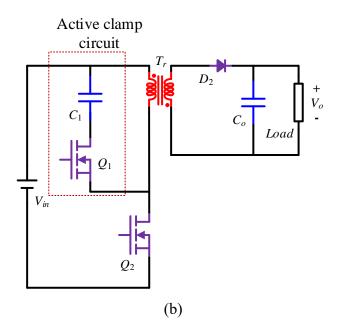

| Figure 2.3 Derivation of bidirectional converters: (a) boost converter; (b) Ćuk          |

| converter                                                                                |

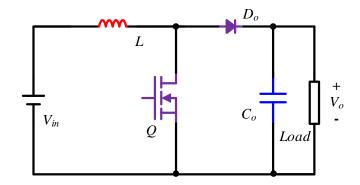

| Figure 2.4 Topology of the conventional non-isolated converter                           |

| Figure 2.5 Configuration of cascaded DC/DC converter                                     |

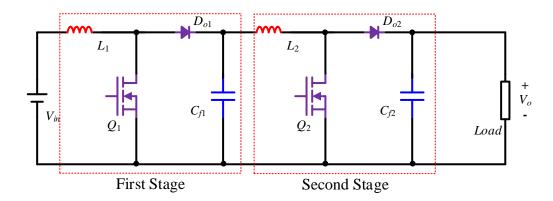

| Figure 2.6 Cascade converter with two stages boost converters15                          |

| Figure 2.7 Quadratic boost converter                                                     |

| Figure 2.8 Three level boost converter                                                   |

| Figure 2.9 Topology of switched capacitor converter                                      |

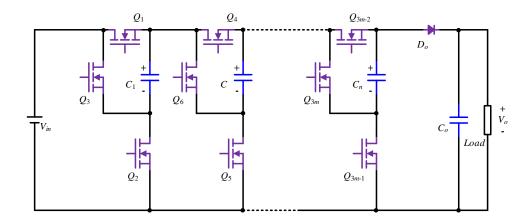

| Figure 2.10 Cascaded <i>m</i> stages switched capacitor converter                        |

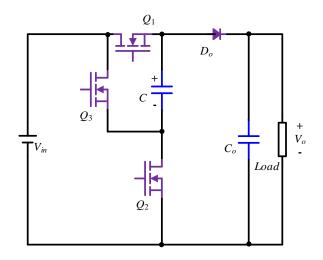

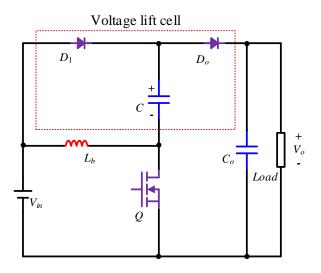

| Figure 2.11 Topology of the voltage lift circuit19                                       |

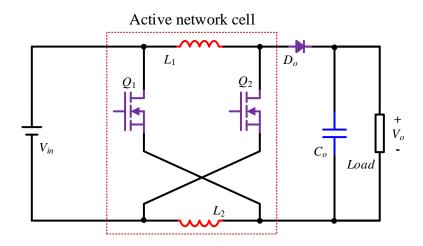

| Figure 2.12 Topologies of voltage multiplier: (a) half-wave voltage doubler; (b) full-   |

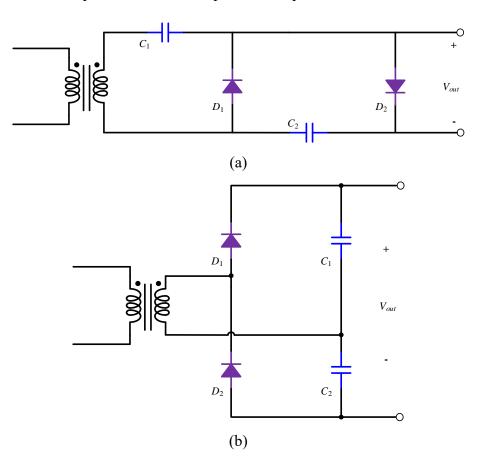

| wave voltage doubler; (c) half-wave voltage multiplier extendable topology20             |

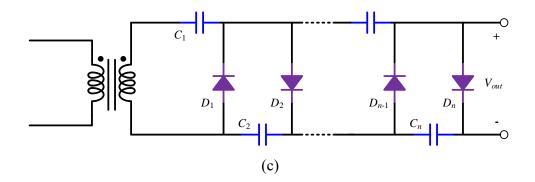

| Figure 2.13 Topology of the switched inductor converter                                  |

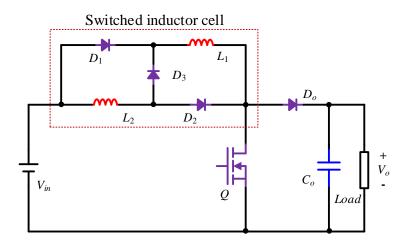

| Figure 2.14 Topology of the active network converter                                     |

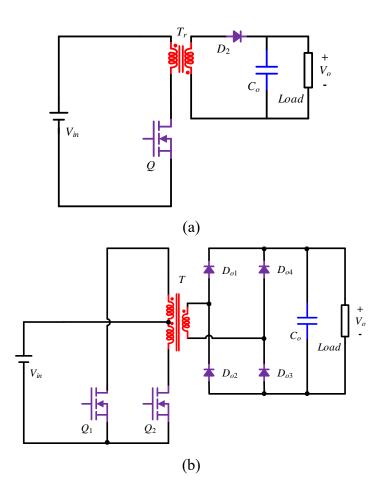

| Figure 2.15 Typical isolated boost converters: (a) fly-back converter; (b) push-pull     |

| converter; (c) FB converter; (d) HB converter                                            |

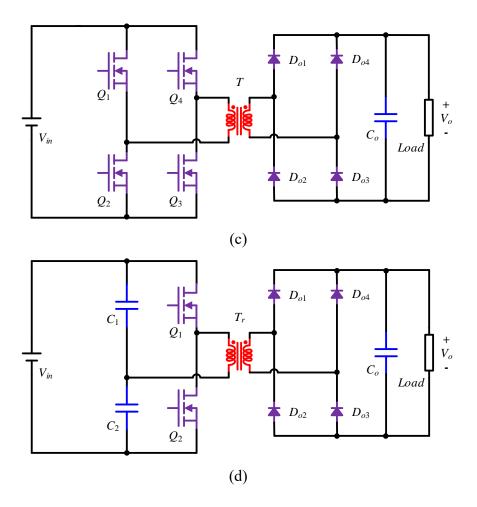

| Figure 2.16 Auxiliary circuits for isolated boost converter: (a) RCD circuit; (b) active |

| clamp circuit                                                                            |

| Figure 2.17 Topology of coupled inductor converter                                       |

| Figure 2.18 Topology of coupled inductor converter with two output capacitors26          |

| Figure 2.19 Configuration of MMCs                                                        |

| Figure 2.20 Topologies of SMs in MMCs: (a) FB circuit; (b) HB circuit27                  |

| Figure 2.21 Classification of boost converters by voltage conversion ratio29             |

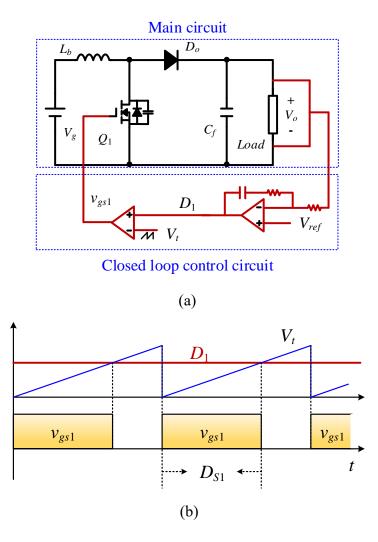

| Figure 2.22 Voltage control system: (a) voltage control circuit; (b) key waveforms.30    |

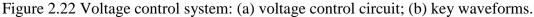

| Figure 2.23 Current control system: (a) current control circuit; (b) key waveforms. 31   |

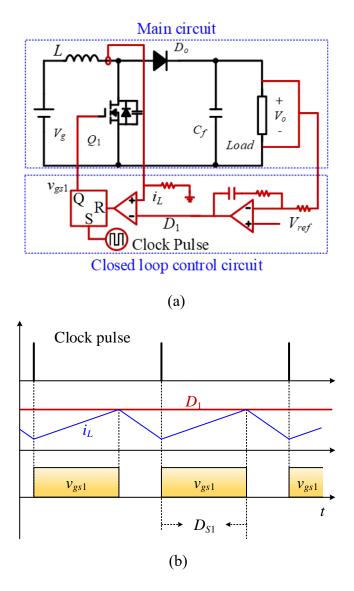

| Figure 2.24 Typical hard-switching voltage-current waveform of power switches 33         |

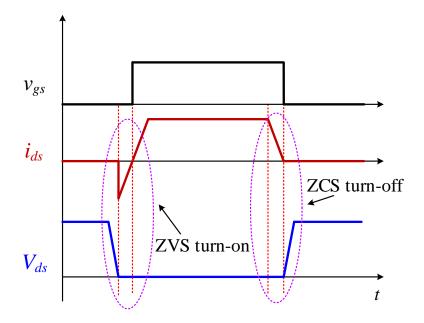

| Figure 2.25 Typical soft-switching voltage-current waveform of power switches 34               |  |  |  |

|------------------------------------------------------------------------------------------------|--|--|--|

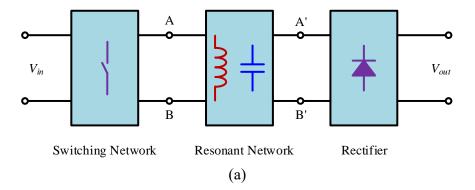

| Figure 2.26 ZVS structure: (a) resonant circuit configuration; (b) LC resonant tank; (c)       |  |  |  |

| LLC resonant tank; (D) LCC resonant tank; (E) CLLC resonant tank                               |  |  |  |

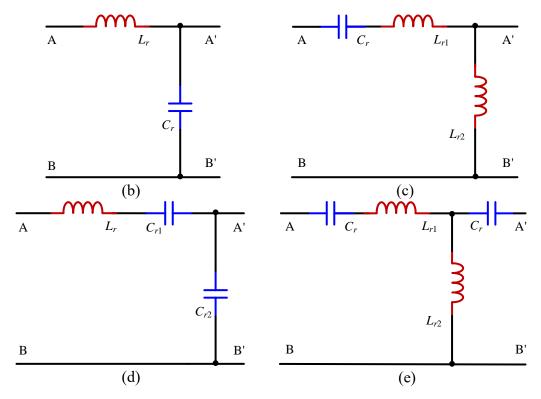

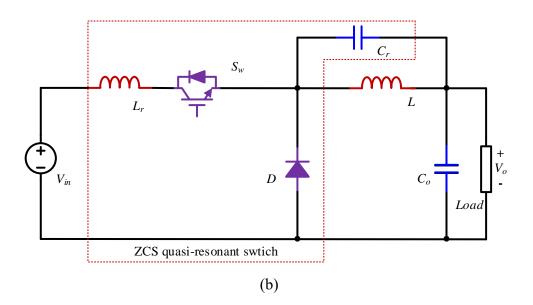

| Figure 2.27 Installation of the ZCS quasi-resonant cell: (a) connection to the DC output;      |  |  |  |

| (b) connection to the DC input                                                                 |  |  |  |

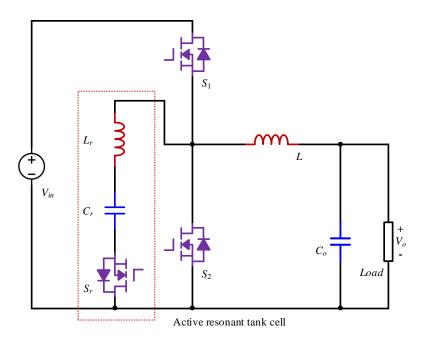

| Figure 2.28 Active resonant tank circuit                                                       |  |  |  |

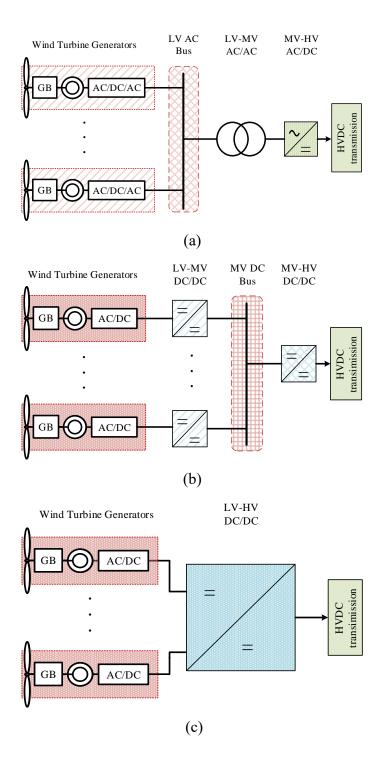

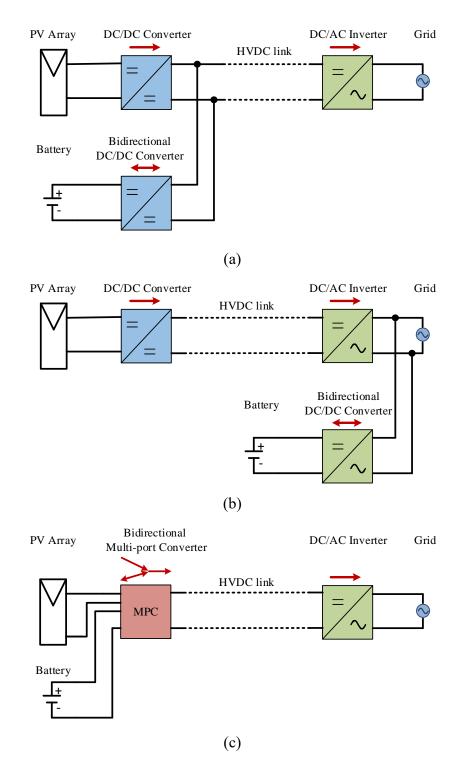

| Figure 3.1 HVDC configurations for wind power transmission: (a) DC-based                       |  |  |  |

| connection with two-stage hybrid conversion; (b) DC-based connection with two-stage            |  |  |  |

| DC/DC conversion; (c) DC-based connection with the proposed modular converter.                 |  |  |  |

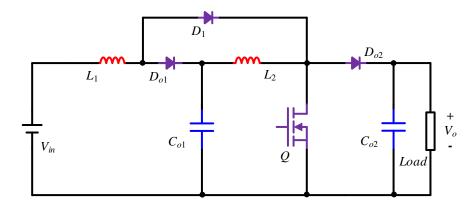

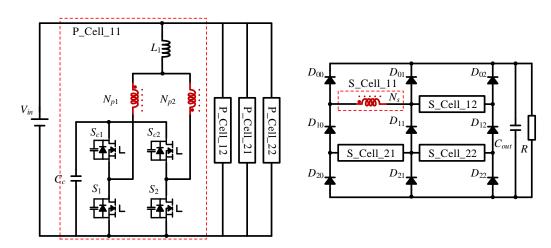

| Figure 3.2 Topology of the basic cell on CFPP converter                                        |  |  |  |

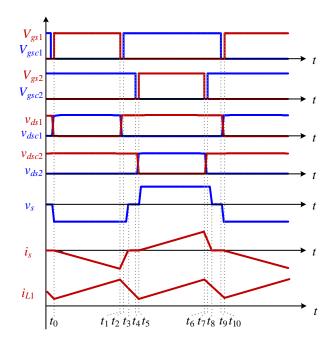

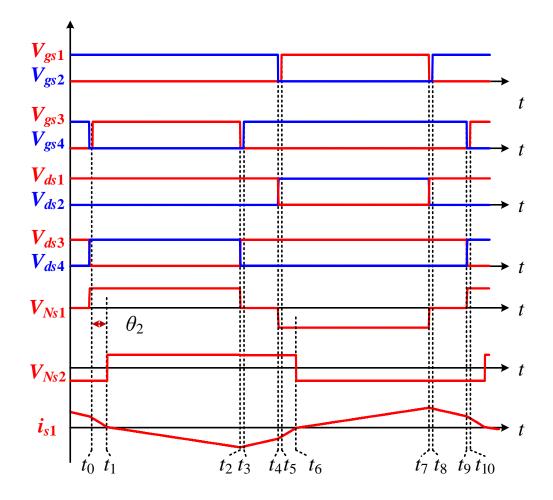

| Figure 3.3 Operating waveforms of the basic cell                                               |  |  |  |

| Figure 3.4 2×2 topology of the isolated high voltage gain DC/DC converter with basic cells     |  |  |  |

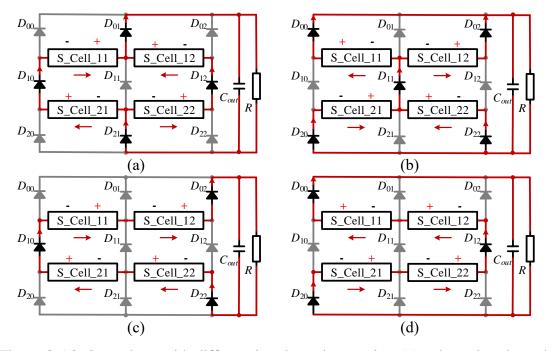

| Figure 3.5 $2 \times 2$ topology with different interleaved strategies: (a) column interleaved |  |  |  |

| mode 1; (b) column interleaved mode 2; (c) series interleaved mode 1; (d) series               |  |  |  |

| interleaved mode 2                                                                             |  |  |  |

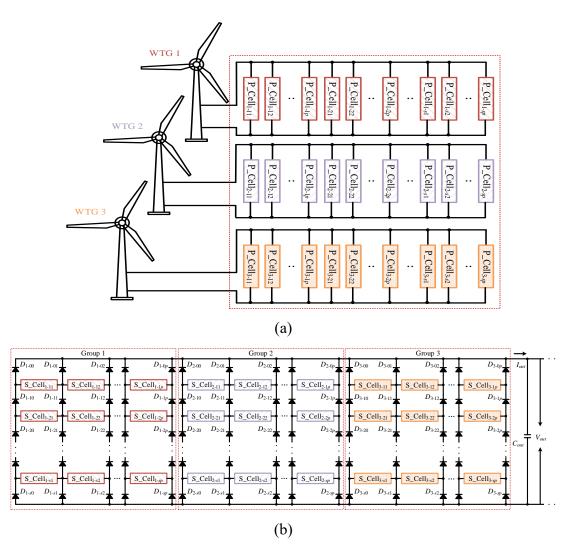

| Figure 3.6 Topology of the proposed converter with three input-ports: (a) primary              |  |  |  |

| circuits with three power sources; (b) secondary circuits collecting power and                 |  |  |  |

| delivering it to load                                                                          |  |  |  |

| Figure 3.7 Auto-balanced currents of cells in the same column with column interleaved          |  |  |  |

| working strategy: (a) column interleaved working mode 1; (b) column interleaved                |  |  |  |

| working mode 2                                                                                 |  |  |  |

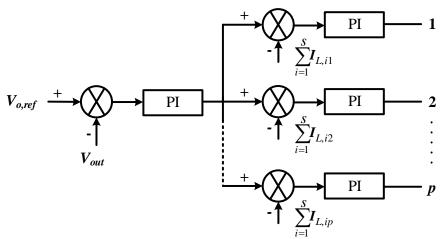

| Figure 3.8 Control scheme of the $s \times p$ topology                                         |  |  |  |

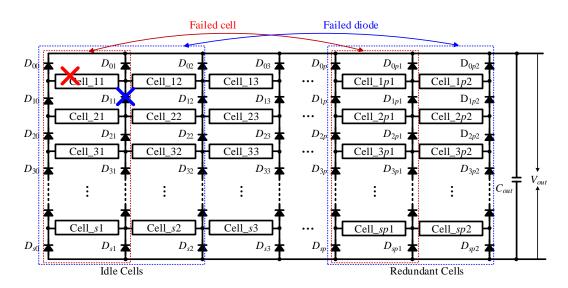

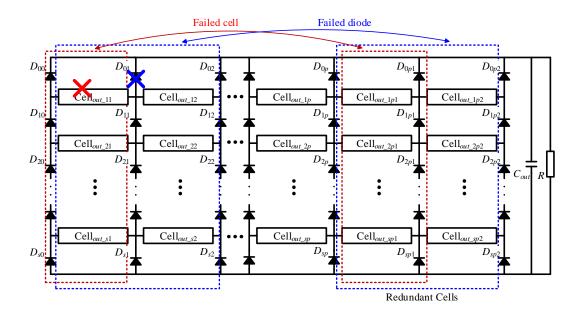

| Figure 3.9 Fault tolerance with redundancy                                                     |  |  |  |

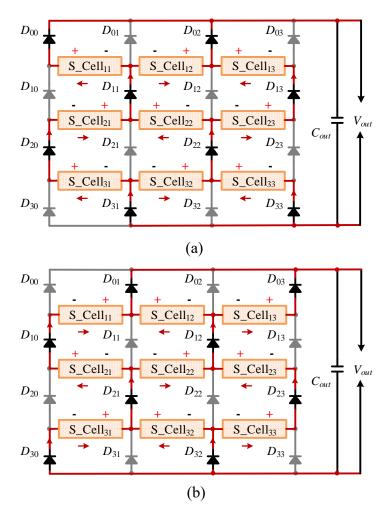

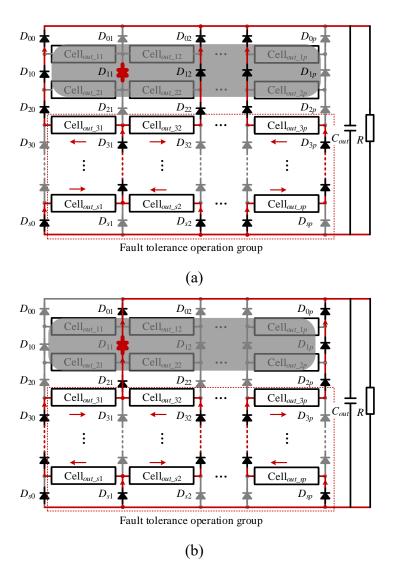

| Figure 3.10 Fault tolerance when diode $D_{11}$ is short-circuited: (a) working mode 1; (b)    |  |  |  |

| working mode 2                                                                                 |  |  |  |

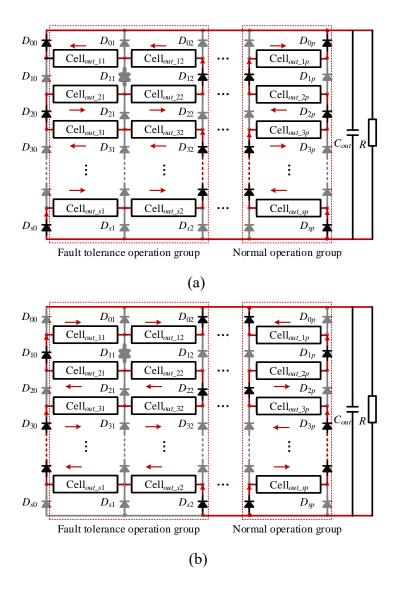

| Figure 3.11 Fault tolerance when diode $D_{11}$ is open-circuited: (a) working mode 1; (b)     |  |  |  |

| working mode 2                                                                                 |  |  |  |

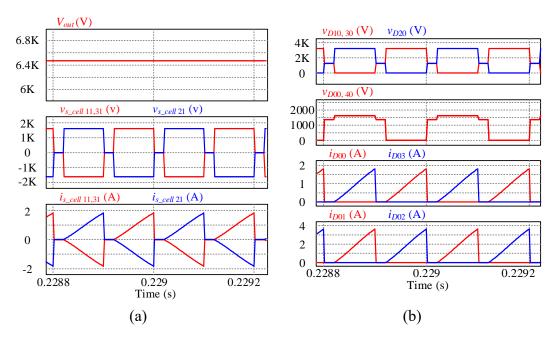

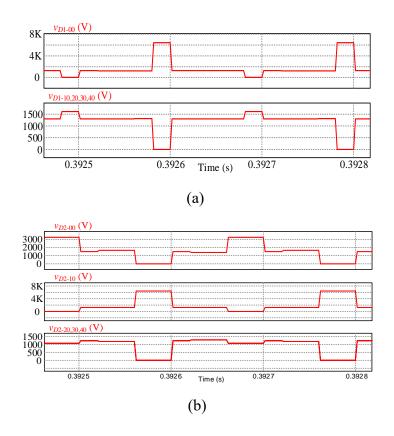

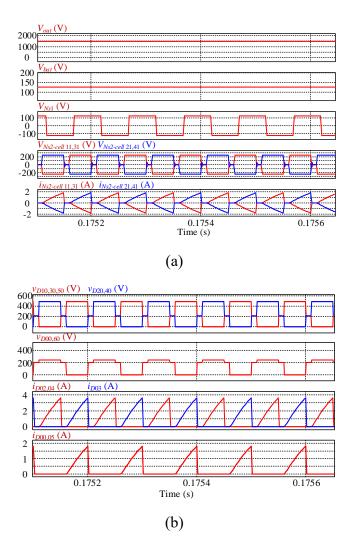

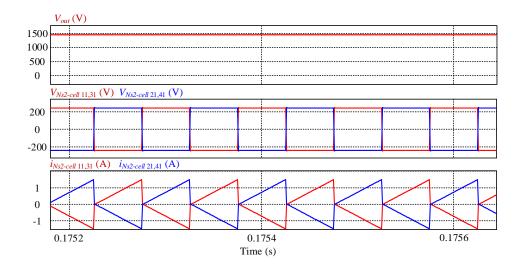

| Figure 3.12 Steady state waveforms for cells and diode: (a) voltage/current of basic           |  |  |  |

| cells; (b) voltage/current of diodes                                                           |  |  |  |

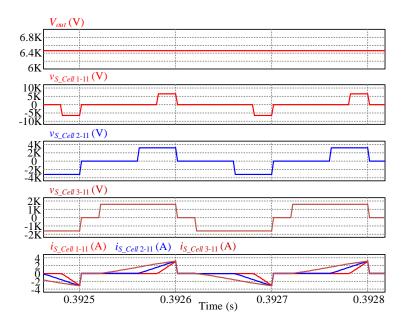

| Figure 3.13 Waveforms of cells when Groups 1~3 have different output power 56                  |  |  |  |

| Figure 3.14 Voltages of diodes in each Group when Groups 1~3 have different output             |  |  |  |

| power: (a) voltages of diodes in Group 1; (b) voltages of diodes in Group 2                    |  |  |  |

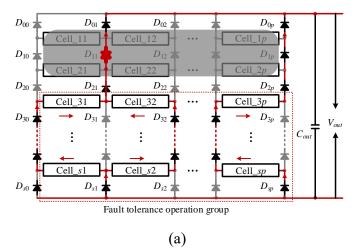

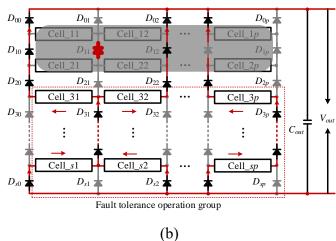

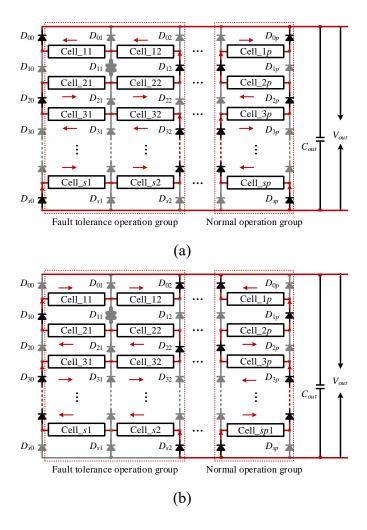

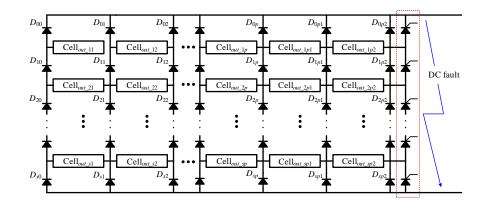

| Figure 4.19 Fault tolerance operation without redundancy; (a) without redundancy for                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $D_{11}$ short-circuit; (b) without redundancy for $D_{11}$ open-circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

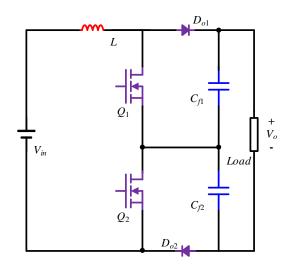

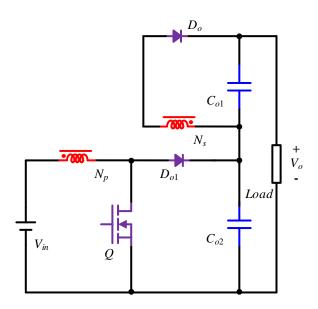

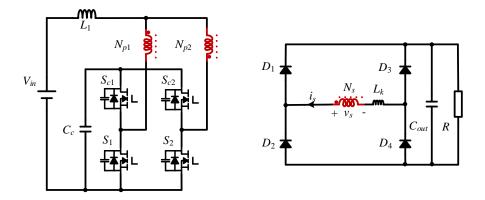

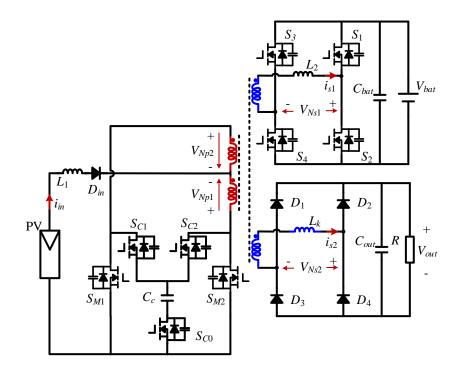

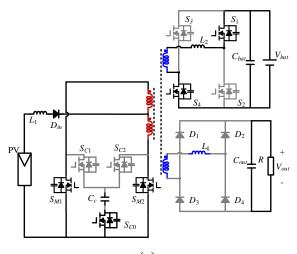

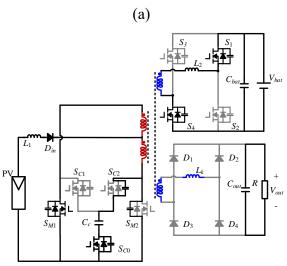

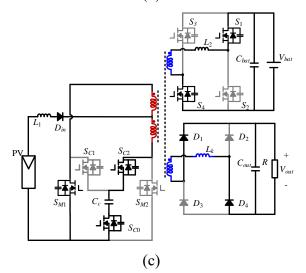

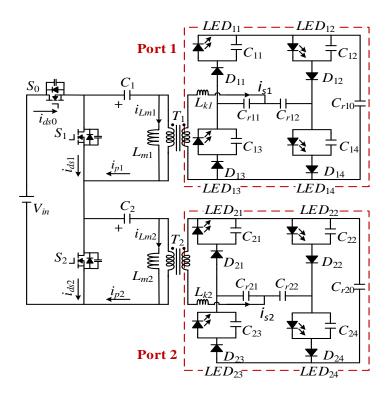

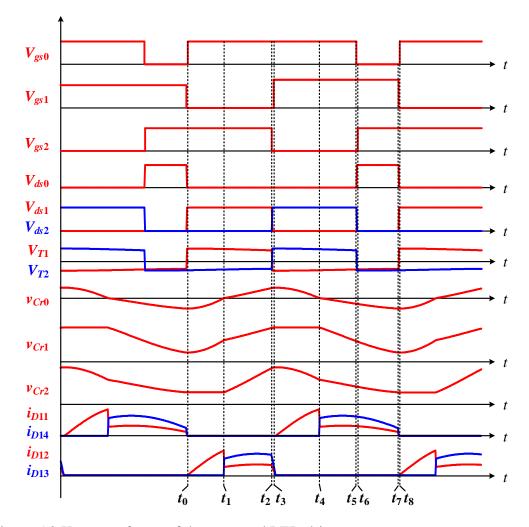

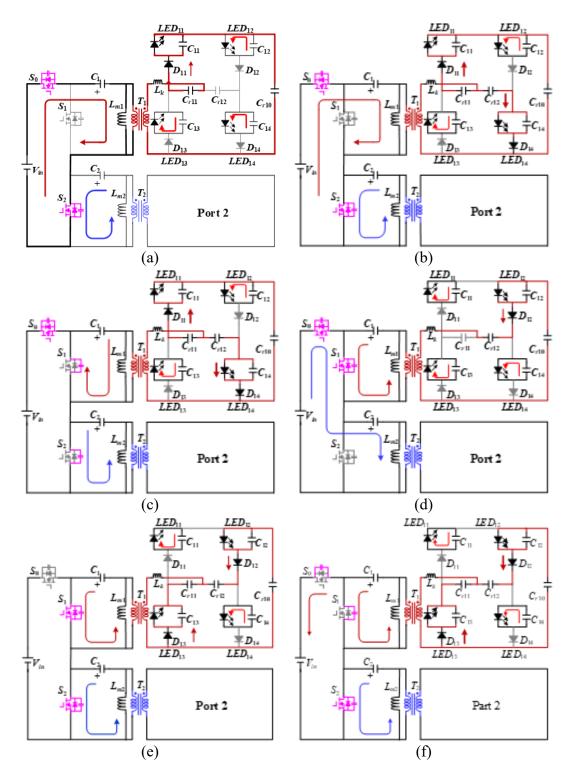

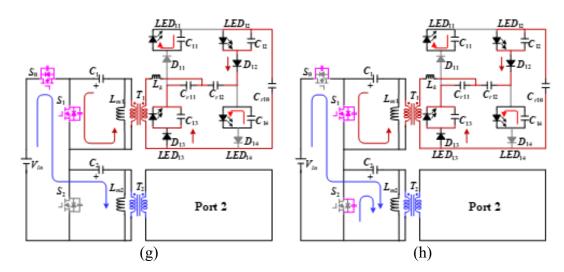

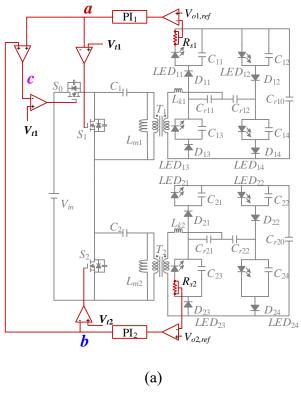

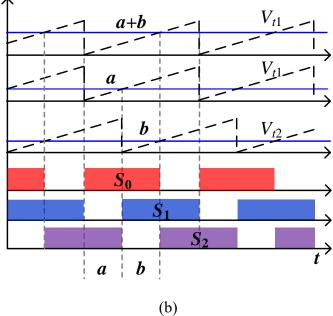

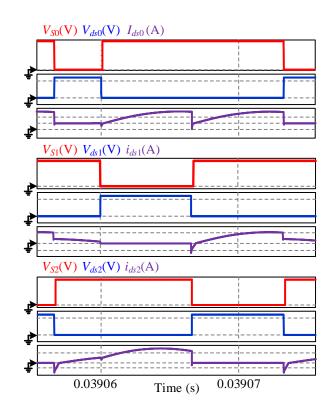

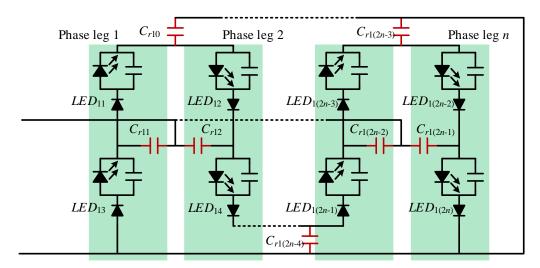

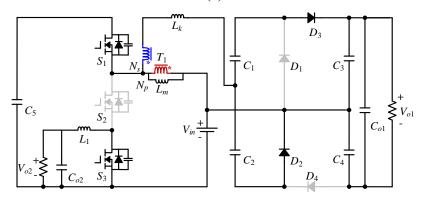

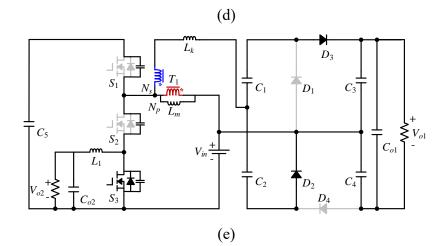

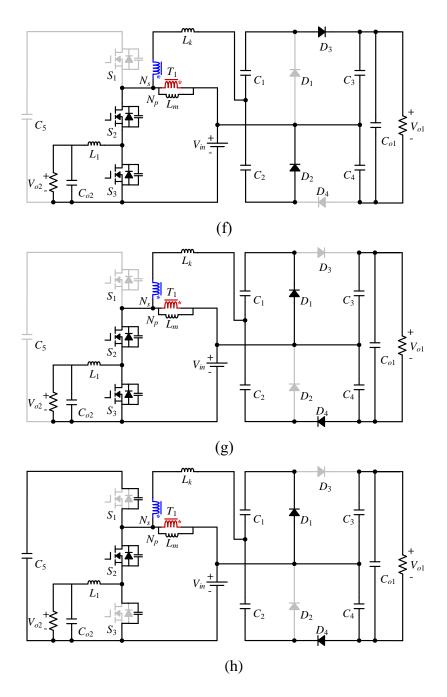

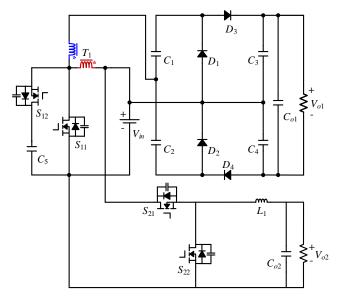

| Figure 5.1 Equivalent topology of the proposed LED driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |