WAIKATO Research Commons

## http://researchcommons.waikato.ac.nz/

### Research Commons at the University of Waikato

### **Copyright Statement:**

Te Whare Wānanga o Waikato

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

The thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognise the author's right to be identified as the author of the thesis, and due acknowledgement will be made to the author where appropriate.

- You will obtain the author's permission before publishing any material from the thesis.

# High Precision Timing in Passive Measurements of Data Networks

A thesis submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy at the University of Waikato by

## **Stephen F Donnelly**

Hamilton, New Zealand

June 12, 2002

© 2002 Stephen F Donnelly

All Rights Reserved

## Abstract

Understanding, predicting, and improving network behaviour under a wide range of conditions requires accurate models of protocols, network devices, and link properties. Accurate models of the component parts comprising complex networks allows the plausible simulation of networks in other configurations, or under different loads. These models must be constructed on a solid foundation of reliable and accurate data taken from measurements of relevant facets of actual network behaviour.

As network link speeds increase, it is argued that traditional network measurement techniques based primarily on software time-stamping and capture of packets will not scale to the required performance levels. Problems examined include the difficulty of gaining access to high speed network media to perform measurements, the insufficient resolution of time-stamping clocks for capturing fine detail in packet arrival times, the lack of synchronisation of clocks to global standards, the high and variable latency between packet arrival and time-stamping, and the occurrence of packet loss within the measurement system. A set of design requirements are developed to address these issues, especially in high-speed network measurement systems.

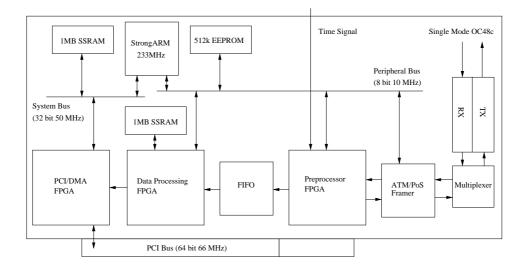

A group at the University of Waikato including myself has developed a series of hardware based passive network measurement systems called 'Dags'. Dags use re-programmable hardware and embedded processors to provide globally synchronised, low latency, reliable time-stamping of all packet arrivals on high-speed network links with sub-hundred nanosecond resolution. Packet loss within the measurement system is minimised by providing sufficient bandwidth throughout for worst case loads and buffering to allow for contention over shared resources. Any occurrence of packet loss despite these measures is reported, allowing the invalidation of portions of the dataset if necessary. I was responsible for writing both the interactive monitor and network measurement code executed by the Dag's embedded processor, developing a Linux device driver including the software part of the 'DUCK' clock synchronisation system, and other ancillary software.

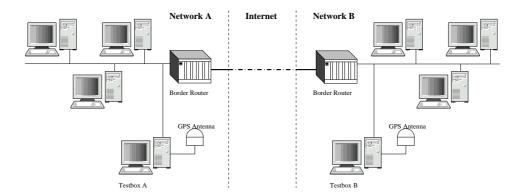

It is shown that the accuracy and reliability of the Dag measurement system allows confidence that rare, unusual or unexpected features found in its measurements are genuine and do not simply reflect artifacts of the measurement equipment. With the use of a global clock reference such as the Global Positioning System, synchronised multi-point passive measurements can be made over large geographical distances. Both of these features are exploited to perform calibration measurements of RIPE NCC's Test Traffic Measurement System for One-way-Delay over the Internet between New Zealand and the Netherlands. Accurate single point passive measurement is used to determine error distributions in Round Trip Times as measured by NLANR's AMP project.

The high resolution afforded by the Dag measurement system also allows the examination of the forwarding behaviour of individual network devices such as routers and firewalls at fine time-scales. The effects of load, queueing parameters, and pauses in packet forwarding can be measured, along with the impact on the network traffic itself. This facility is demonstrated by instrumenting routing equipment and a firewall which provide Internet connectivity to the University of Auckland, providing passive measurements of forwarding delay through the equipment.

## Acknowledgements

I would like to thank Ian Graham, my chief supervisor for his support, encouragement and patience. Thanks go to John Cleary and Murray Pearson, members of my supervisory board for their assistance and suggestions over the course of my work and in the preparation of this thesis. Discussions on statistics with IIze Ziedins were very useful, whom also kindly proof-read early drafts of this thesis providing much needed feedback. Jed Martens designed and debugged the Dag hardware and FPGA images, making much of this work possible. Thanks go to Jörg Micheel and Klaus Mochalski for lengthy discussions on the analysis of various datasets and their help with Dag software maintenance and tools. Henk Uijterwaal and René Wilhelm provided access to RIPE NCC's TTM system and measurements, assisted in instrumenting the Amsterdam node and in analysing the results. Access to and assistance with the collection of data from the NLANR AMP system was provided by Tony McGregor, Matthew Luckie, and Jamie Curtis.

This work was partially supported by a University of Waikato Postgraduate Scholarship. The manuscript was typeset using LATEX.

# Contents

| Al | bstrac  | t                                               | iii  |

|----|---------|-------------------------------------------------|------|

| A  | cknow   | vledgements                                     | v    |

| Li | st of l | Figures                                         | xiii |

| Li | st of [ | Fables                                          | xv   |

| Li | st of A | Abbreviations and Units x                       | vii  |

| 1  | Intr    | oduction                                        | 1    |

| 2  | An      | Overview of IP Network Measurement and Analysis | 5    |

|    | 2.1     | Passive Measurement                             | 5    |

|    | 2.2     | Network Traffic Statistics Collection           | 6    |

|    | 2.3     | Packet Capture                                  | 7    |

|    |         | 2.3.1 Routers                                   | 8    |

|    |         | 2.3.2 Workstations                              | 8    |

|    |         | 2.3.3 Dedicated Measurement Equipment           | 11   |

|    | 2.4     | Flow Based Measurement                          | 12   |

| 3  | Soft    | ware Based Measurement                          | 15   |

|    | 3.1     | Passive Measurement                             | 15   |

|    |         | 3.1.1 Interface Buffering and Queueing          | 17   |

|    |         | 3.1.2 Interrupt Latency                         | 18   |

|    | 3.2     | Active Measurement                              | 22   |

|    |         | 3.2.1 Single-point Active Measurement           | 22   |

|    |         | 3.2.2 Multi-point Active Measurement            | 23   |

|   | 3.3                                                       | Passive Assisted Active Measurements                                                                                                                     | 24                                                                                                                                 |

|---|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.4                                                       | Clock Synchronisation                                                                                                                                    | 25                                                                                                                                 |

| 4 | Desi                                                      | gn Requirements for Accurate Passive Measurement                                                                                                         | 31                                                                                                                                 |

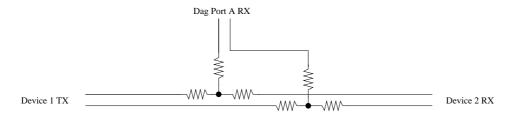

|   | 4.1                                                       | Media Access                                                                                                                                             | 31                                                                                                                                 |

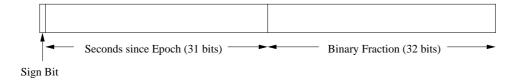

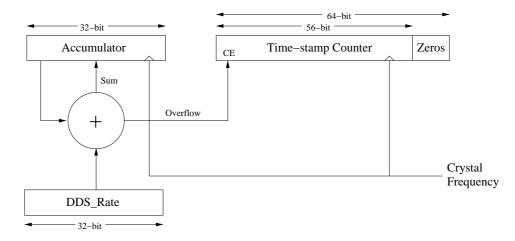

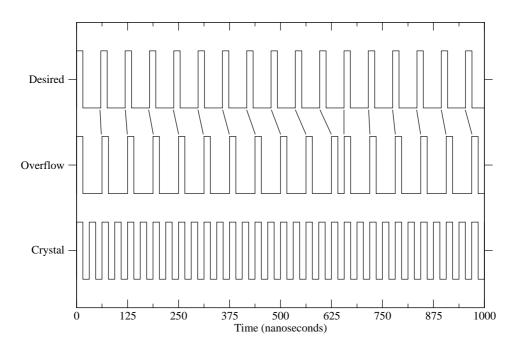

|   | 4.2                                                       | Time-stamping                                                                                                                                            | 33                                                                                                                                 |

|   |                                                           | 4.2.1 Resolution                                                                                                                                         | 34                                                                                                                                 |

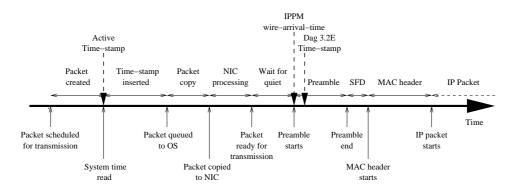

|   |                                                           | 4.2.2 Latency                                                                                                                                            | 35                                                                                                                                 |

|   |                                                           | 4.2.3 Wire Arrival and Exit Times                                                                                                                        | 35                                                                                                                                 |

|   | 4.3                                                       | Clock Synchronisation                                                                                                                                    | 41                                                                                                                                 |

|   | 4.4                                                       | Packet Processing                                                                                                                                        | 43                                                                                                                                 |

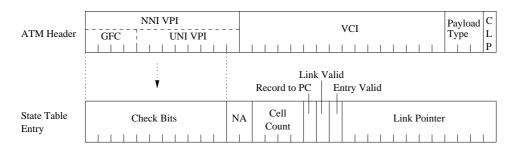

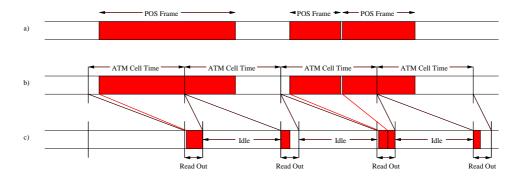

|   |                                                           | 4.4.1 ATM: Segmentation and Re-assembly                                                                                                                  | 44                                                                                                                                 |

|   |                                                           | 4.4.2 Filtering                                                                                                                                          | 45                                                                                                                                 |

|   |                                                           | 4.4.3 CRCs: Integrity and Signatures                                                                                                                     | 47                                                                                                                                 |

|   |                                                           | 4.4.4 Data Reduction                                                                                                                                     | 49                                                                                                                                 |

|   | 4.5                                                       | System Integration                                                                                                                                       | 53                                                                                                                                 |

| 5 | The                                                       | Dag: A Hardware Based Measurement System                                                                                                                 | 57                                                                                                                                 |

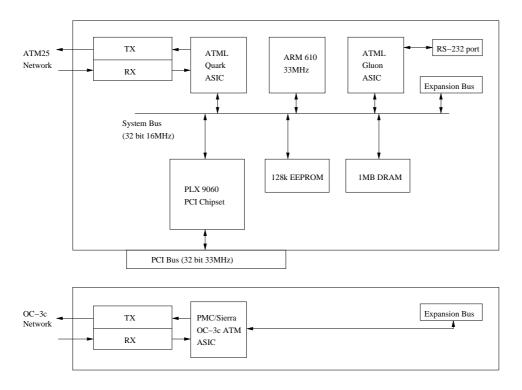

|   | 5.1                                                       | ATM-25 NIC                                                                                                                                               | 58                                                                                                                                 |

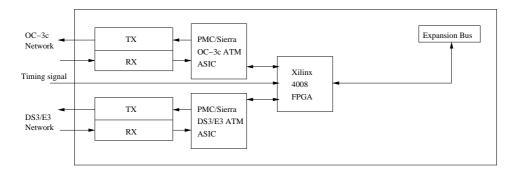

|   | 5.2                                                       | OC-3c ATM NIC                                                                                                                                            | 59                                                                                                                                 |

|   | <i>-</i> 2                                                |                                                                                                                                                          |                                                                                                                                    |

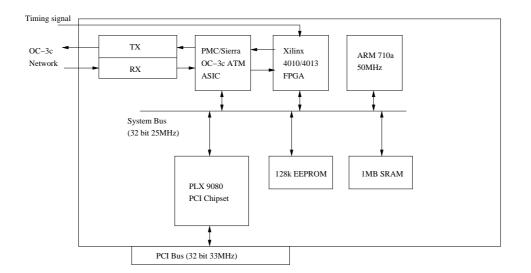

|   | 5.3                                                       | The Dag                                                                                                                                                  | 61                                                                                                                                 |

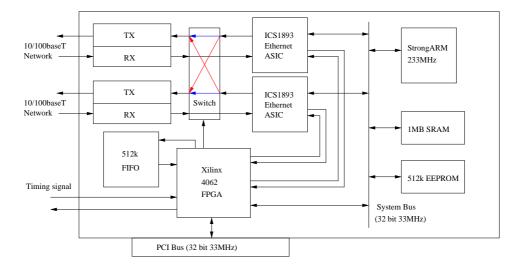

|   | 5.3<br>5.4                                                | The Dag 2       The Dag 2                                                                                                                                | 61<br>63                                                                                                                           |

|   |                                                           | The Dag 2                                                                                                                                                |                                                                                                                                    |

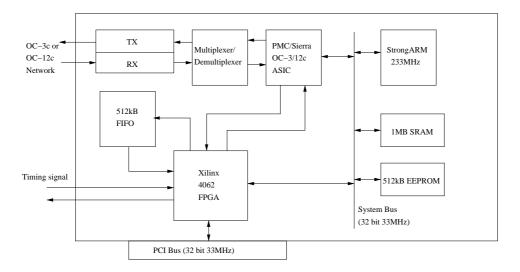

|   | 5.4                                                       | The Dag 2                                                                                                                                                | 63                                                                                                                                 |

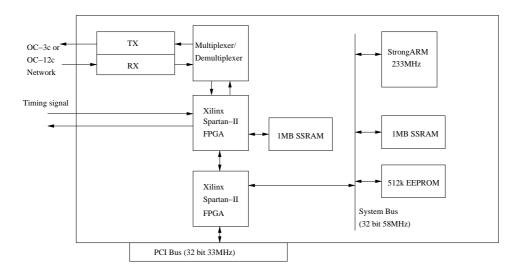

|   | 5.4                                                       | The Dag 2          The Dag 3                                                                                                                             | 63<br>66                                                                                                                           |

|   | 5.4                                                       | The Dag 2                                                                                                                                                | 63<br>66<br>67                                                                                                                     |

|   | 5.4                                                       | The Dag 2                                                                                                                                                | 63<br>66<br>67<br>69                                                                                                               |

|   | 5.4                                                       | The Dag 2                                                                                                                                                | 63<br>66<br>67<br>69<br>71                                                                                                         |

|   | 5.4                                                       | The Dag 2                                                                                                                                                | <ul> <li>63</li> <li>66</li> <li>67</li> <li>69</li> <li>71</li> <li>82</li> </ul>                                                 |

|   | 5.4                                                       | The Dag 2The Dag 35.5.1Buffering5.5.2IP Header Capture on ATM5.5.3Time Formatting and Synchronisation5.5.4Packet over SONET5.5.5Ethernet                 | <ul> <li>63</li> <li>66</li> <li>67</li> <li>69</li> <li>71</li> <li>82</li> <li>86</li> </ul>                                     |

|   | 5.4                                                       | The Dag 2The Dag 35.5.1Buffering5.5.2IP Header Capture on ATM5.5.3Time Formatting and Synchronisation5.5.4Packet over SONET5.5.5Ethernet5.5.6The Dag 3.5 | <ul> <li>63</li> <li>66</li> <li>67</li> <li>69</li> <li>71</li> <li>82</li> <li>86</li> <li>89</li> </ul>                         |

|   | 5.4                                                       | The Dag 2                                                                                                                                                | <ul> <li>63</li> <li>66</li> <li>67</li> <li>69</li> <li>71</li> <li>82</li> <li>86</li> <li>89</li> <li>91</li> </ul>             |

| 6 | <ul><li>5.4</li><li>5.5</li><li>5.6</li><li>5.7</li></ul> | The Dag 2                                                                                                                                                | <ul> <li>63</li> <li>66</li> <li>67</li> <li>69</li> <li>71</li> <li>82</li> <li>86</li> <li>89</li> <li>91</li> <li>92</li> </ul> |

|   | 6.2      | Test Tr | raffic Measurement System    99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |          | 6.2.1   | Calibration Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

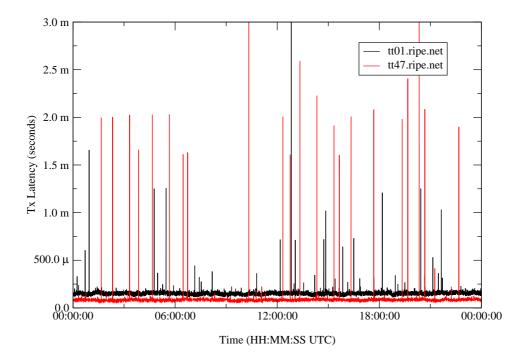

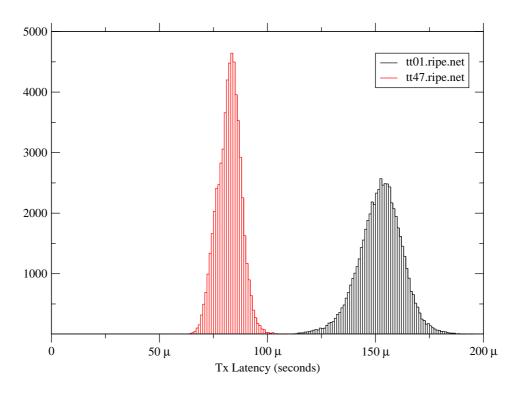

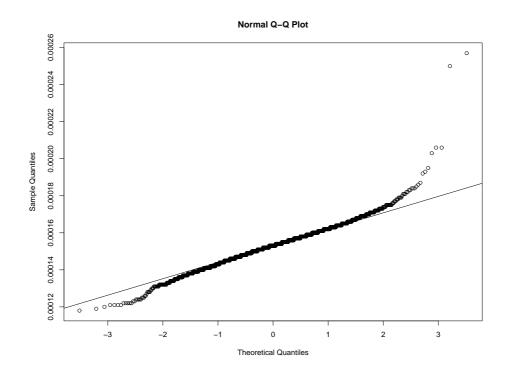

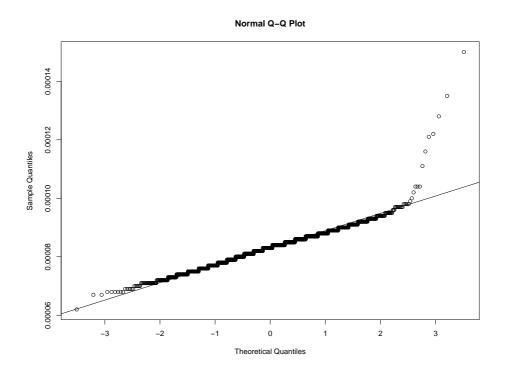

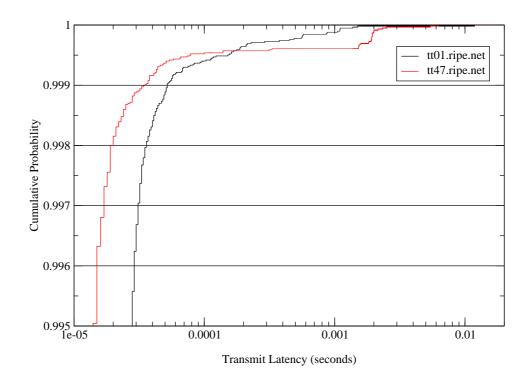

|   |          | 6.2.2   | Transmission Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |          | 6.2.3   | Transmission scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |          | 6.2.4   | Reception Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |          | 6.2.5   | End to End Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

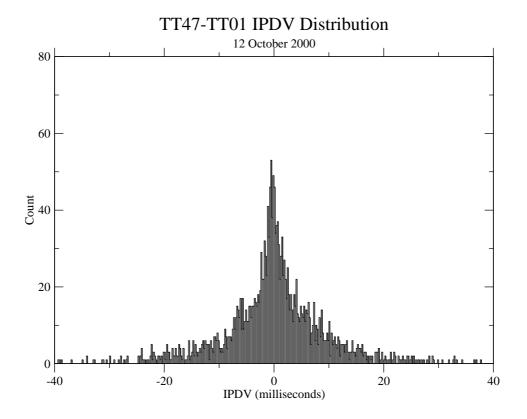

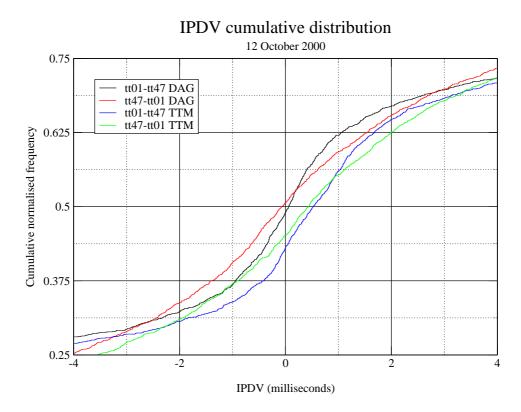

|   | 6.3      | Instant | aneous Packet Delay Variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 6.4      | Round   | Trip Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

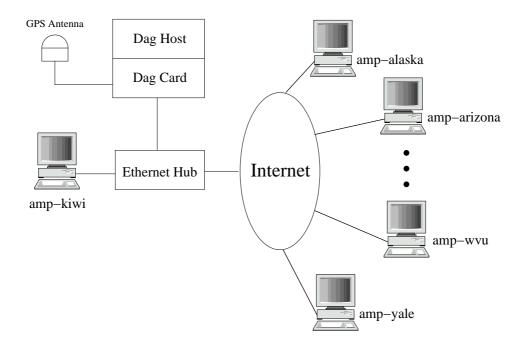

|   | 6.5      | AMP:    | The Active Measurement Project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

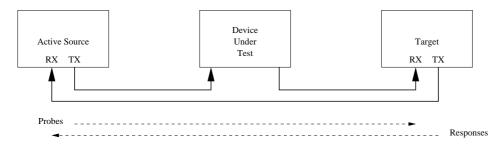

|   |          | 6.5.1   | Calibration Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

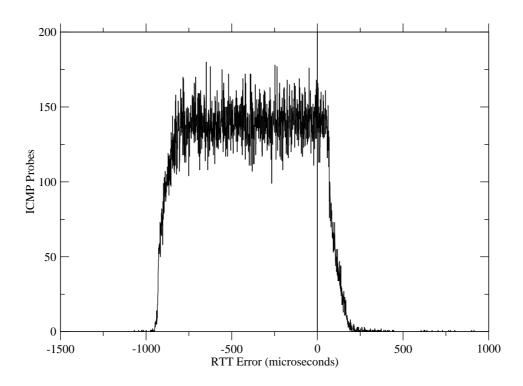

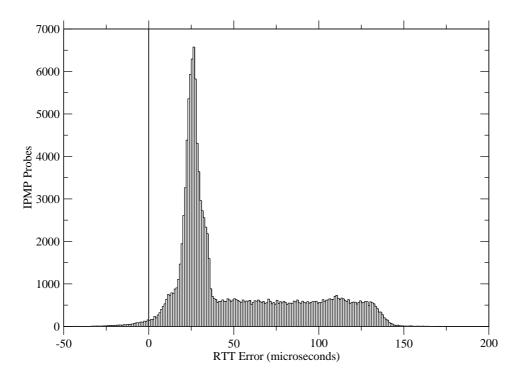

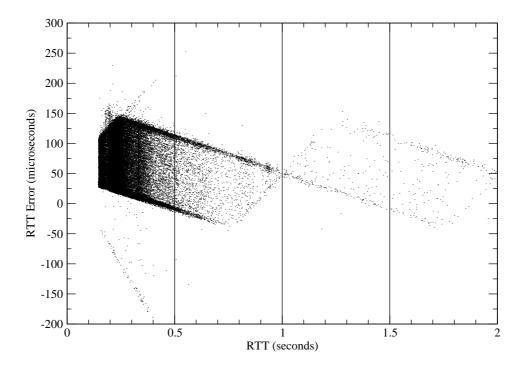

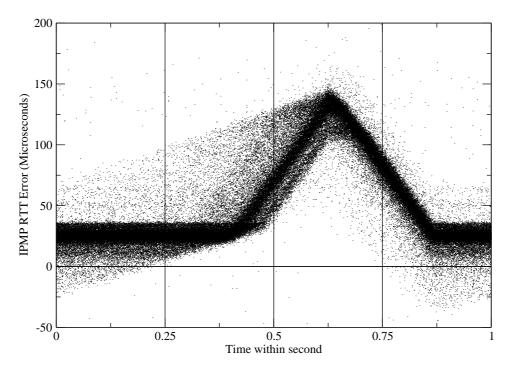

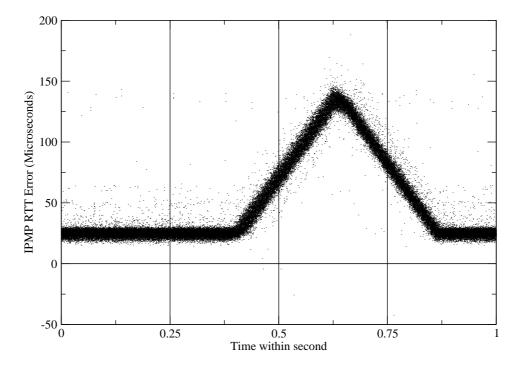

|   |          | 6.5.2   | RTT Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |          | 6.5.3   | Target Response Time    130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 6.6      | Conclu  | sions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| - | <b>D</b> |         | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7 |          |         | racterisation of Network Equipment 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 7.1      |         | 135 Internet in the second sec |

|   | 7.2      |         | Characterisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |          | 7.2.1   | Active Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |          | 7.2.2   | Passive Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |          | 7.2.3   | Traffic Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |          | 7.2.4   | Measurement System Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |          | 7.2.5   | Packet Delay and Loss Derivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |          |         | Packet Recognition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |          | 7.2.7   | IP Id as sequence number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |          | 7.2.8   | Revised Passive Delay Derivation Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 7.3      | The U   | niversity of Auckland Passive Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |          | 7.3.1   | Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

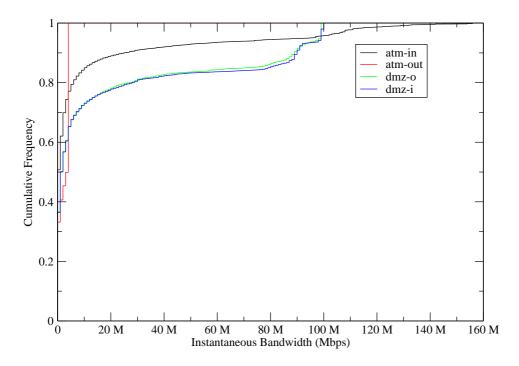

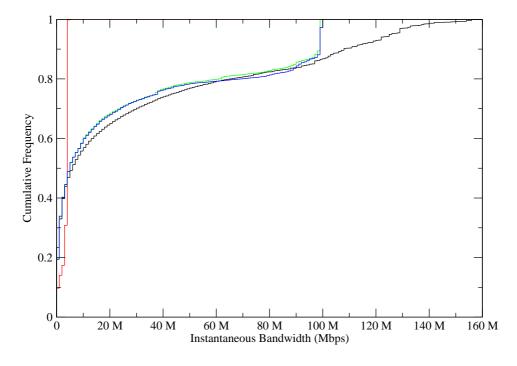

|   |          | 7.3.2   | Link Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

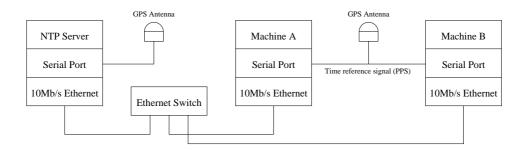

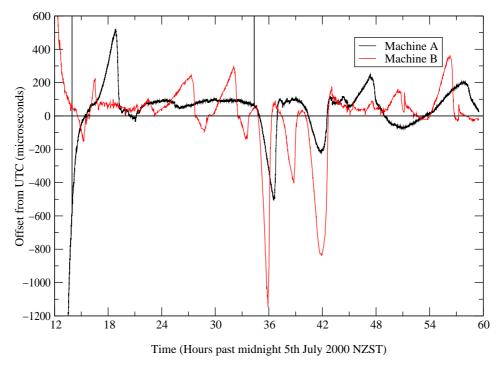

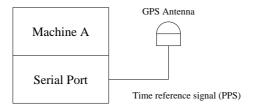

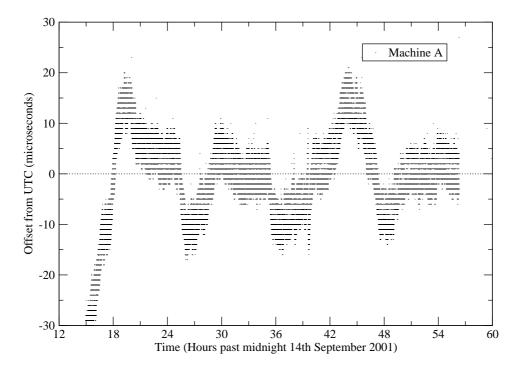

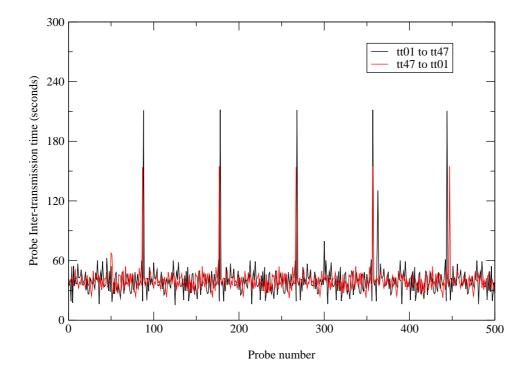

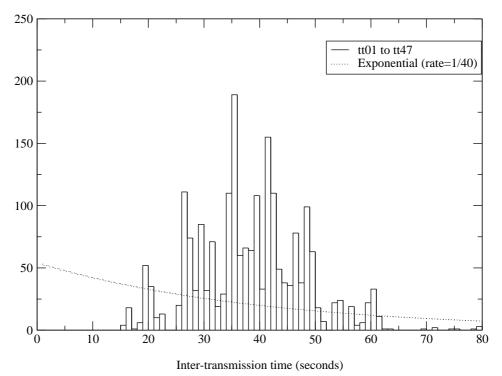

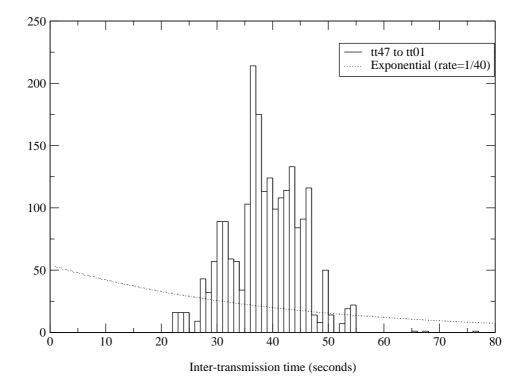

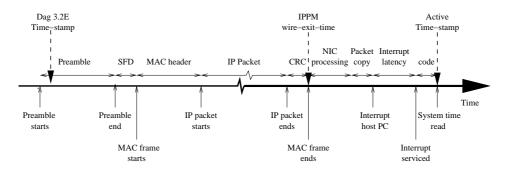

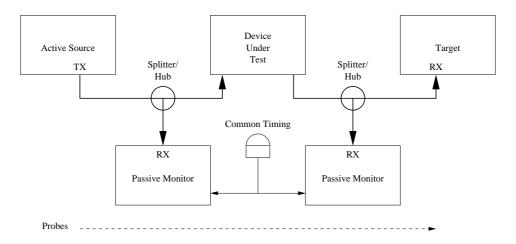

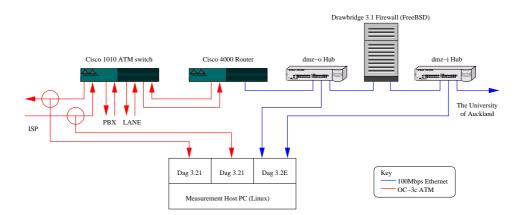

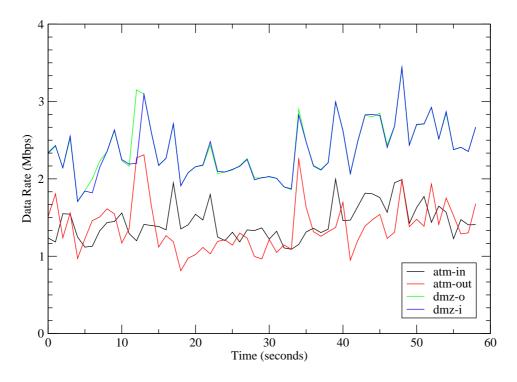

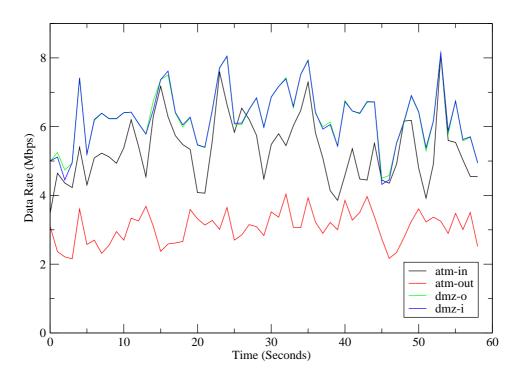

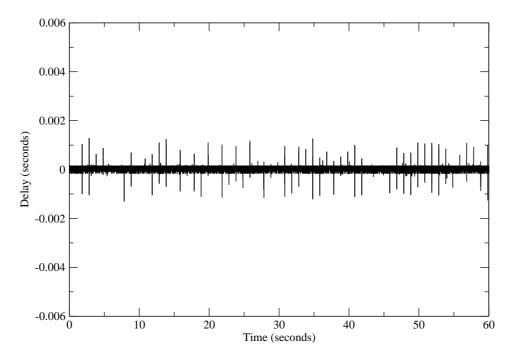

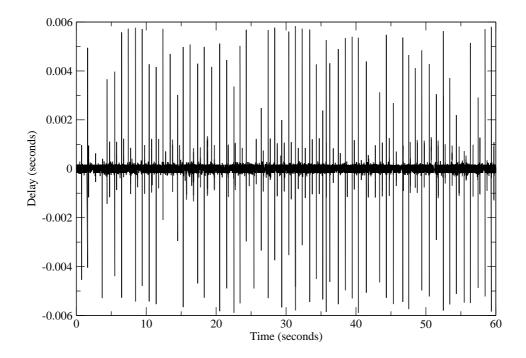

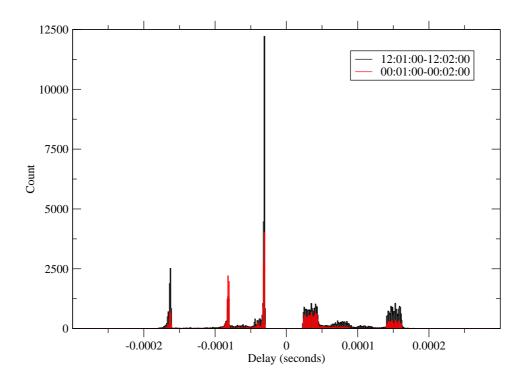

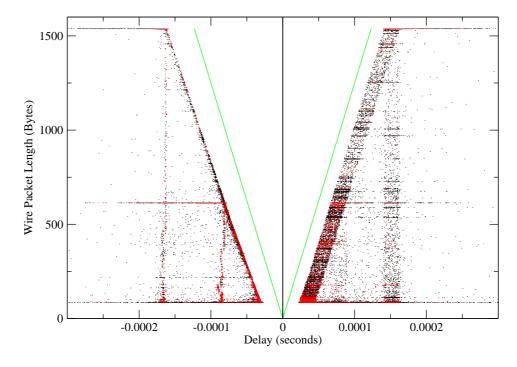

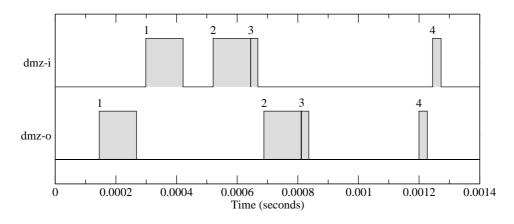

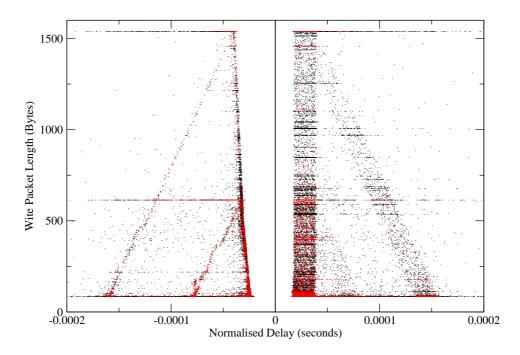

|   |          | 7.3.3   | Delay Datasets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |