#### University of Massachusetts Amherst

## ScholarWorks@UMass Amherst

**Doctoral Dissertations**

**Dissertations and Theses**

October 2019

# TIME-DIFFERENCE CIRCUITS: METHODOLOGY, DESIGN, AND DIGITAL REALIZATION

Shuo Li

Follow this and additional works at: https://scholarworks.umass.edu/dissertations\_2

Part of the Digital Circuits Commons, Electrical and Electronics Commons, Hardware Systems Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Li, Shuo, "TIME-DIFFERENCE CIRCUITS: METHODOLOGY, DESIGN, AND DIGITAL REALIZATION" (2019). *Doctoral Dissertations*. 1751.

https://scholarworks.umass.edu/dissertations\_2/1751

This Open Access Dissertation is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

## TIME-DIFFERENCE CIRCUITS: METHODOLOGY, DESIGN, AND DIGITAL REALIZATION

A Dissertation Presented

by

SHUO LI

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

September 2019

Electrical and Computer Engineering

© Copyright by Shuo Li 2019 All Rights Reserved

## TIME-DIFFERENCE CIRCUITS: METHODOLOGY, DESIGN, AND DIGITAL REALIZATION

A Dissertation Presented by SHUO LI

| Approved as to style and content by |                                                                               |

|-------------------------------------|-------------------------------------------------------------------------------|

|                                     |                                                                               |

| Wayne P. Burleson, Chair            |                                                                               |

|                                     |                                                                               |

| Russell Tessier, Member             |                                                                               |

|                                     |                                                                               |

| Emily Kumpel, Member                |                                                                               |

|                                     |                                                                               |

|                                     | Christopher V. Hollot, Department Head<br>Electrical and Computer Engineering |

## **DEDICATION**

To Elaine and Xiaolin

#### ACKNOWLEDGMENTS

There are so many people I want to thanks to help me, encourage me, support me to finish my PHD dissertation. First of all, I mush express my gratitude to my two advisors during the whole PHD study: Professor Wayne Burleson, I can say without him, I cannot approach here. He pulled me out from dilemma and gave me the chance to continue pursuing my goal; he has always shown his kindness, knowledge, patience, and understanding to help me and support me, which is very important for me and my family, thus we can stay together after my babys born. Working with him has simply become a pleasure since he gave me freedom to work on the project, and provided lots of updated experience from industry to lead the advancing and practical topics in my thesis.

Also I am thankful to Dr. Christopher Salthouse, who led me into this area, getting in touch with integrated circuits design from the beginning. He gave me a very precious opportunity to finish a tape-out independently when I was still a fresh master student right after joining the lab. He was using his knowledge and experience to guide me whenever I needed. My first understanding and training of research are all from him. Working in BEL lays good foundation of IC design, which I think will benefits for long term career and future life.

I gratefully acknowledge the financial support provided by BEL and the department of Electronic and Computer Engineering. In particular, I want to thank Prof. Christopher V. Hollot, Prof. Robert Jackson, Prof. Paul Siqueira, and Prof. Russell Tessier, who generously gave me advices and help; encourage me to complete my thesis when I encountered difficulties. Also my friends and colleagues at UMASS provided great company, feedback, and wonderful friendship during the past years.

They made the beautiful town Amherst my first family in US. And all these memories have become invaluable reward of my PH. D degree.

It has been 9 years I left home to come aboard to pursuit my dreams. My parents provided all physical, mental and financial support through these years. Whenever I felt upset either from study or life, they can immediately comfort me and make me relaxed. They are the foundation and freedom to undertake many adventures. I hope I can have more time to company with my family in return.

Finally, I should express my special gratitude to my beloved husband, my best friend, Dr. Xiaolin Xu. His faithfulness to me and my family becomes the best support for me to continue finishing the work. I appreciated everything we experienced together over the past 10 years. The best thing we work together is raising our lovely daughter Elaine. Elaine has kept me focused on the important priorities; she reminds me each day of small joys that would otherwise go unnoticed. She taught us from her joy of learning and explorations.

There are many others to thank as well, too many to list here. So to my extended family and friends who have supported me financially, spiritually, and emotionally, I want to sincerely say thank you.

#### ABSTRACT

## TIME-DIFFERENCE CIRCUITS: METHODOLOGY, DESIGN, AND DIGITAL REALIZATION

#### SEPTEMBER 2019

#### SHUO LI

B.E., UNIVERSITY OF ELECTRONIC SCIENCE & TECHNOLOGY OF CHINA

M.S., UNIVERSITY OF MASSACHUSETTS AMHERST

Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Wayne P. Burleson

This thesis presents innovations for a special class of circuits called Time Difference (TD) circuits. We introduce a signal processing methodology with TD signals that alters the target signal from a magnitude perspective to time interval between two time events and systematically organizes the primary TD functions abstracted from existing TD circuits and systems. The TD circuits draw attention from a broad range of application fields. In addition, highly evolved complementary metal-oxide-semiconductor (CMOS) technology suffers from various problems related to voltage and current amplitude signal processing methods. Compared to traditional analog and digital circuits, TD circuits bring several compelling features: high-resolution, high-throughput, and low-design complexity with digital integration capability. Further, the fabrication technology is advancing into the nanometer regime; the reduction in

voltage headroom limits the performance of traditional analog/mixed-signal designs. All-digital design of time-difference circuit needs to be stressed to adapt to the low-cost, low-power, and high-portability applications.

We focus on Time-to-Digital Converters (TDC), one of the crucial building blocks in TD circuits. A novel algorithmic architecture is proposed based on a binary search algorithm and validated with both simulation and fabricated silicon. An all-digital structure Time-difference Amplifier (TDA) is designed and implemented to make FPGA and other all-digital implementations for TDC and related TD circuits feasible. Besides, we propose an all-digital timing measurement circuit based on the process variation from CMOS fabrication: PVTMC, which achieves a high measurement resolution: < 0.5ps. Moreover, our experimental results demonstrate that the PVTMC is fully compatible with the CMOS technology nodes from 180nm to 7nm with enhanced performance in more advance nodes. The design of PVTMC is realized on two FPGAs: Spartan-6 (45nm) and Artix-7 (28nm) and also obtained a high resolution of < 1ps.

## TABLE OF CONTENTS

|              |            |                                                    | P                                                                                                                                                                                                                                    | age                          |

|--------------|------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| $\mathbf{A}$ | CKN        | OWLI                                               | EDGMENTS                                                                                                                                                                                                                             | . <b>v</b>                   |

| $\mathbf{A}$ | BST        | RACT                                               |                                                                                                                                                                                                                                      | vii                          |

| LI           | ST (       | OF TA                                              | BLES                                                                                                                                                                                                                                 | xiii                         |

| LI           | ST (       | OF FIC                                             | GURES                                                                                                                                                                                                                                | xiv                          |

| <b>C</b> :   | HAP        | TER                                                |                                                                                                                                                                                                                                      |                              |

| 1.           | BA         | CKGR                                               | OUND AND MOTIVATION                                                                                                                                                                                                                  | 1                            |

|              | 1.1<br>1.2 |                                                    | fication of circuits                                                                                                                                                                                                                 |                              |

|              |            | 1.2.1<br>1.2.2                                     | Application of time difference circuits in LiDAR Application of time difference circuits in fluorescence lifetime                                                                                                                    |                              |

|              |            | 1.2.3                                              | imaging                                                                                                                                                                                                                              |                              |

|              | 1.3        | Thesis                                             | Outline                                                                                                                                                                                                                              | . 11                         |

| 2.           | ME         | THOE                                               | OOLOGY                                                                                                                                                                                                                               | 13                           |

|              | 2.1        | Signal                                             | processing in time-mode                                                                                                                                                                                                              | . 13                         |

|              |            | 2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6 | Time-mode vs. voltage-mode signal processing  Time-mode vs. current-mode signal processing  Time-mode signal processing strengths and challenges  TD circuits operation functions  TD Sample and Hold (S/H)  TD arithmetic operation | . 15<br>. 15<br>. 16<br>. 17 |

|              |            |                                                    | 2.1.6.1 TD adding/subtracting                                                                                                                                                                                                        | . 18                         |

|    |            |                | 2.1.6.2 TD integration                                    | . 20 |

|----|------------|----------------|-----------------------------------------------------------|------|

|    |            | 2.1.7<br>2.1.8 | TD comparison or quantization                             |      |

| 3. | TIN        | <b>1Е-ТО</b>   | -DIGITAL CONVERTER ARCHITECTURES                          | 32   |

|    | 3.1        |                | TDC                                                       |      |

|    | 3.2<br>3.3 |                | e-fine interpolation TDC<br>ΓDC                           |      |

|    | 3.4        |                | sed Compact Algorithmic TDC                               |      |

|    |            | 3.4.1          | CATDC: architecture and implementation                    |      |

|    |            | 3.4.2<br>3.4.3 | Simulations results and analysis                          |      |

| 4. |            | ATDC           | : A CONFIGURABLE COMPACT ALGORITHMIC TO-DIGITAL CONVERTER |      |

|    |            |                |                                                           |      |

|    | 4.1        |                | uction                                                    |      |

|    | 4.2<br>4.3 |                | ed Workrsion Error Analysis                               |      |

|    | 1.0        | COIIVO         | v                                                         |      |

|    |            | 4.3.1<br>4.3.2 | Scheme of CATDC                                           |      |

|    |            | 4.0.2          | ·                                                         |      |

|    |            |                | 4.3.2.1 Gain Error                                        |      |

|    |            |                | 4.3.2.2 Time Reference                                    |      |

|    |            |                | 4.5.2.9 I focess variations and fransient Noise           | . 55 |

|    | 4.4        | Propos         | sed Methodologies                                         | . 54 |

|    |            | 4.4.1          | Gain Compensation                                         | . 54 |

|    |            | 4.4.2          | Adjustable Delay-line                                     |      |

|    |            | 4.4.3<br>4.4.4 | Delay Chain Configuration with Machine Learning           |      |

|    | 4.5        | Impler         | mentation and Performance                                 | . 59 |

|    | 4.6        | -              | usion and Future Work                                     |      |

| 5. | DES        | SIGN (         | OF PVT-RESISTANT ALL-DIGITAL                              |      |

|    |            |                | DOMAIN AMPLIFIER WITH VARIABLE GAIN                       | 00   |

|    | A          | AND V          | WIDE OPERATION RANGE                                      | 62   |

|    | 5.1        |                | uction                                                    |      |

|    | i) /       | певате         | ed Work                                                   | -04  |

|    | 5.3        | All-Di                           | gital Time-Domain Amplifier                                                                        | 66       |

|----|------------|----------------------------------|----------------------------------------------------------------------------------------------------|----------|

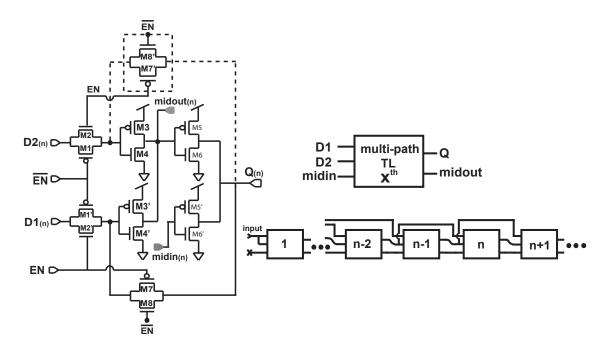

|    |            | 5.3.1<br>5.3.2<br>5.3.3<br>5.3.4 | Pulse extraction.  Pulse duplication.  Pulse summation.  The multi-path high resolution time-latch | 67<br>69 |

|    | 5.4<br>5.5 |                                  | ion and Performance Evaluation                                                                     |          |

| 6. | ľ          | MEAS                             | DIGITAL PVT-RESISTANT TIMING UREMENT CIRCUIT WITH RESOLUTION OF CICOSECOND                         | . 77     |

|    | 6.1<br>6.2 |                                  | luction                                                                                            |          |

|    |            |                                  | 6.2.0.1 The process variations from CMOS fabrication                                               |          |

|    |            |                                  | procedure                                                                                          |          |

|    | 6.3        | Introd                           | luction of PVTMC                                                                                   | 83       |

|    |            | 6.3.1<br>6.3.2                   | Schematic of PVTMC                                                                                 |          |

|    |            |                                  | 6.3.2.1 Simulation setup:                                                                          | 84       |

|    | 6.4        | Algori                           | thms Used in PVTMC Measurements                                                                    | 86       |

|    |            | 6.4.1<br>6.4.2<br>6.4.3          | Principles of PVTMC                                                                                | 89       |

|    |            |                                  | 6.4.3.1 Using machine learning to model PVTMC                                                      | 92       |

|    | 6.5        | Perfor                           | emance Evaluation with HSPICE Simulation                                                           |          |

|    |            | 6.5.1                            | Timing Measurements                                                                                | 97       |

|    |            | 6.5.2                            | Performance evaluation under different environmental conditions                                    |          |

|    |            | 6.5.3                            | Impact of circuit length                                                                           |          |

|    |            | 654                              | Compatibility with different CMOS technology models                                                | 100      |

|    | 6.6 | Valida | ation with FPGA Implementations              | 100   |

|----|-----|--------|----------------------------------------------|-------|

|    |     | 6.6.1  | Implementation of PVTMC circuit on FPGA      | 101   |

|    |     | 6.6.2  | $t_{in}$ generation within FPGA              | 103   |

|    |     | 6.6.3  | Experimental results of FPGA validation      | 104   |

|    |     |        | 6.6.3.1 Binary search-based measurement      | 105   |

|    | 6.7 | Concl  | lusion                                       | 106   |

|    | 6.8 | Cumu   | ulative probability distribution of $t_{in}$ | 106   |

| 7. | CO  | NCLU   | JSIONS AND FUTURE WORK                       | . 110 |

| BI | BLI | OGR.A  | APHY                                         | . 113 |

## LIST OF TABLES

| <b>T</b> able | Page                                                                                   |

|---------------|----------------------------------------------------------------------------------------|

| 4.1           | Overhead and energy comparison between different TDC structures 60                     |

| 5.1           | ADTDA performance using different CMOS technologies (with gain=2)                      |

| 7.1           | Comparison between our work and the state-of-the-art ASIC and FPGA TDC implementations |

## LIST OF FIGURES

| Figure | Page                                                                                                                                                                                                                                                                  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1    | Traditional analog variables represent circuits                                                                                                                                                                                                                       |

| 1.2    | Definition of TD variable. The rising edges of two pulses determine the time difference                                                                                                                                                                               |

| 1.3    | Classification of circuit types in time-value plane                                                                                                                                                                                                                   |

| 1.4    | Discrete-time continuous-value signal sampled with clock cycle T 4                                                                                                                                                                                                    |

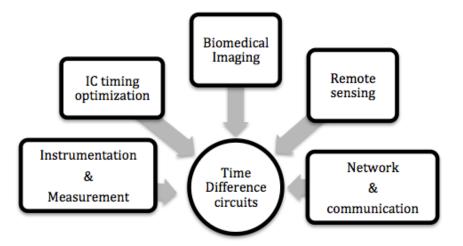

| 1.5    | Applications of time-difference circuits                                                                                                                                                                                                                              |

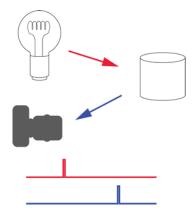

| 1.6    | An example schematic of LiDAR system. The distance between the object and sensor is measured by time interval between two pulses                                                                                                                                      |

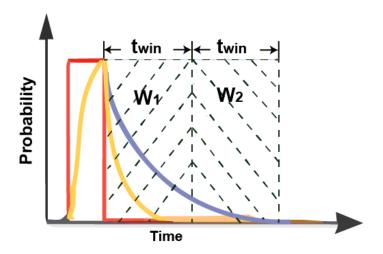

| 1.7    | RLD method for fluorescence lifetime measurements. When a pulse excites the sample, the intensity falls off exponentially after the pulse. The fluorescence lifetime can be calculated using RLD method with the fluorescence intensity in two time windows W1 and W2 |

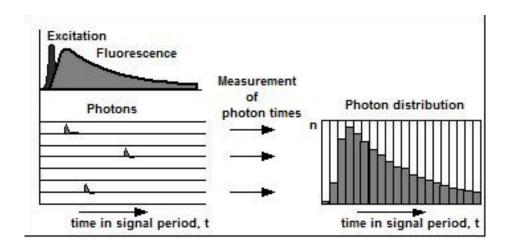

| 1.8    | Operation principle of time-correlated single photon counting (TCSPC) measurements. The sample is excited by a pulsed laser source with a high repetition rate. By counting many events a histogram of the photon distribution over time is built up                  |

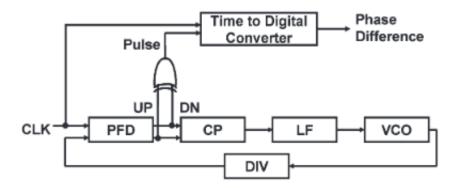

| 1.9    | Build-in timing measurement circuits using TD circuits (Time-to-Digital Converter) for real-time digitizing and characterizing the phase error for PLL/DLL                                                                                                            |

| 1.10   | Jitter description in a clock signal                                                                                                                                                                                                                                  |

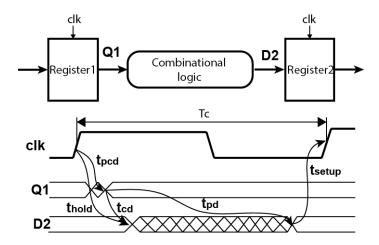

| 1.11   | Time constraints of data setup/hold time for sequential circuits                                                                                                                                                                                                      |

| 2.1    | Function block and timing diagram of time-difference memory. The time-difference information is stored in the repeated events                                                                                                                                         |

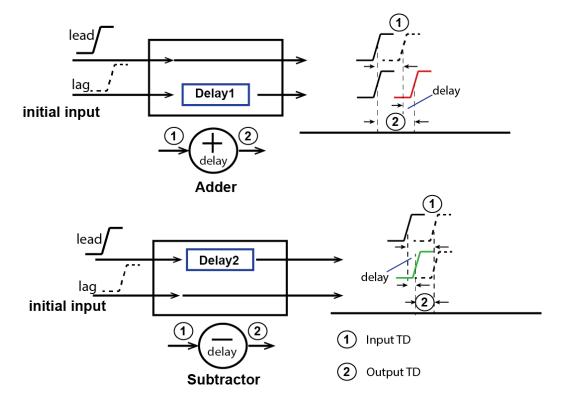

| 2.2  | The symbol and basic function of a time-difference adder. TD (1) labels the input TD value and (2) labels the output TD value.  Delay1 and Delay2 are two constant delay values                                                                                                                        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

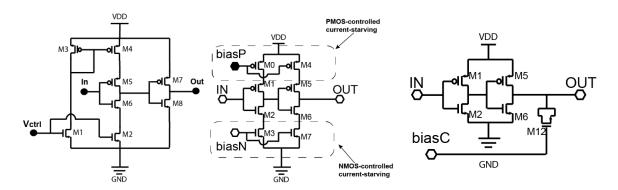

| 2.3  | Alternative Designs of adjustable delay elements by controlling current, voltage and load capacitance                                                                                                                                                                                                  |

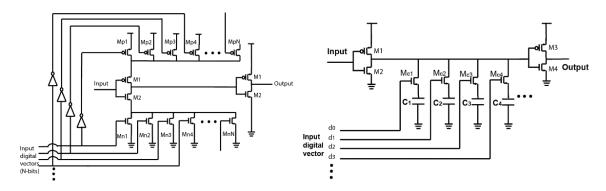

| 2.4  | Alternative Designs of digital-controlled delay elements                                                                                                                                                                                                                                               |

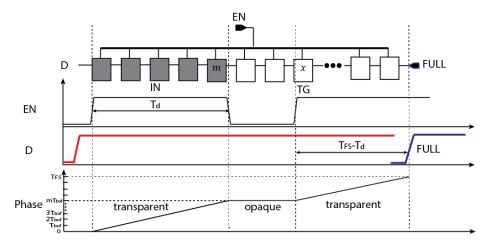

| 2.5  | Time-latch function diagram, signal D propagates in transparent mode, and is held during the opaque mode                                                                                                                                                                                               |

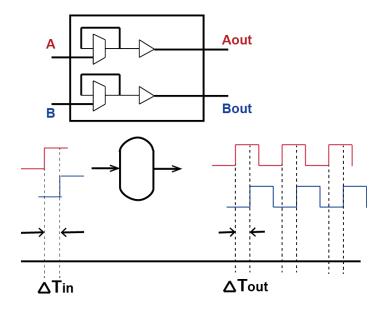

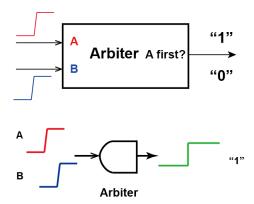

| 2.6  | Symbol and function block of two-input TD arbiter                                                                                                                                                                                                                                                      |

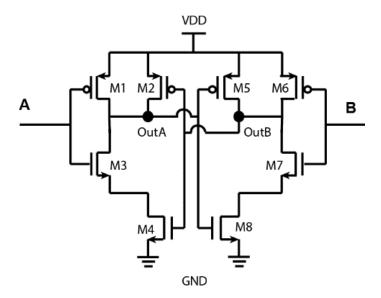

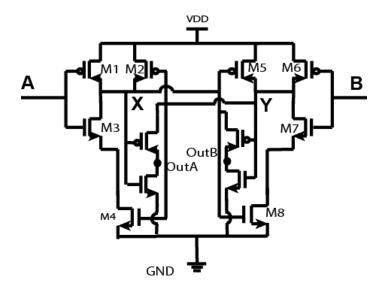

| 2.7  | Schematic of SR-latch-based arbiter with two input events                                                                                                                                                                                                                                              |

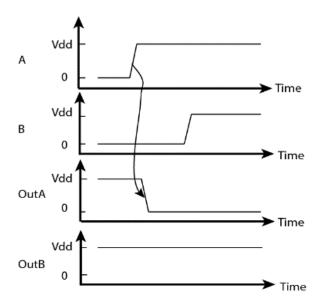

| 2.8  | Arbiter function diagram. Two signals asynchronously arrive at the arbiter. The lead signal In1 is selected to be output by the arbiter, Out1 respond to transmit from Vdd to 0                                                                                                                        |

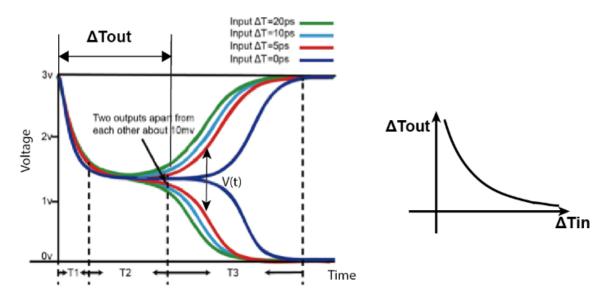

| 2.9  | Output transient waveforms for different input time difference. $\Delta T_{out}$ exponentially increases with reduced $\Delta T_{in}$                                                                                                                                                                  |

| 2.10 | Schematic of MUTEX-based arbiter                                                                                                                                                                                                                                                                       |

| 2.11 | Timing diagram of MUTEX-based arbiter. SR latch enters metastable state due to the small time interval between two rising edges of In1 and In2. X leads Y during metal stable state, and the filter helps Out1 win the arbitration when the voltage difference between X and Y is larger than $V_{th}$ |

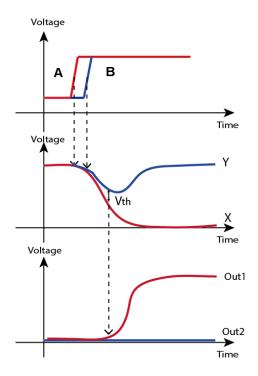

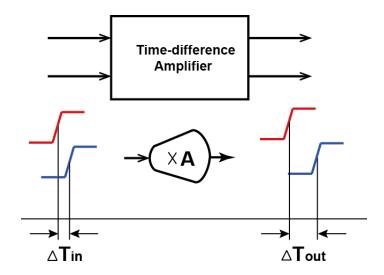

| 2.12 | Function diagram of time-difference amplifier. The output of TD is multiplied by a constant value A of input TD                                                                                                                                                                                        |

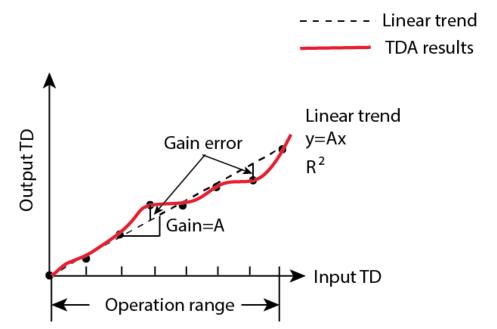

| 2.13 | TDA works with specifications. The amplification gain is A. The operation range is determined by the maximum input TD. The variation between real TDA data and linear trend is the gain error                                                                                                          |

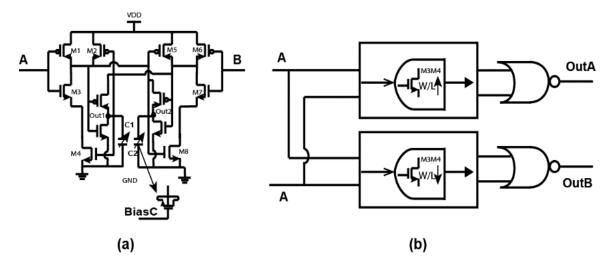

| 2.14 | Schematic of developed arbiter-based TDA presents that the gain can be adjusted by BiasC. (a) schematic of arbiter with voltage-controlled MOScap as load capacitors of the NAND gate. (b)TDA schematic based on the arbiter design in (a) with different scaled size of transistor in NAND gates      |

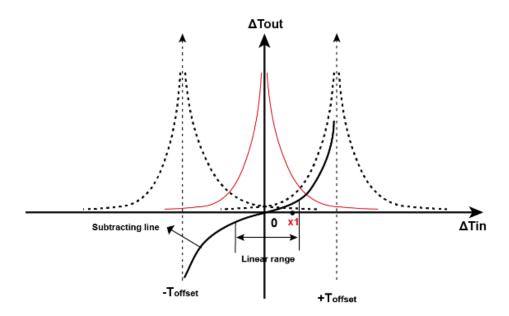

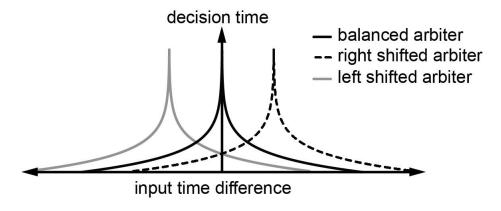

| 2.15 | Two shifted version of exponential relationship of input and output time difference                                                                                                                                                                                                                                            |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

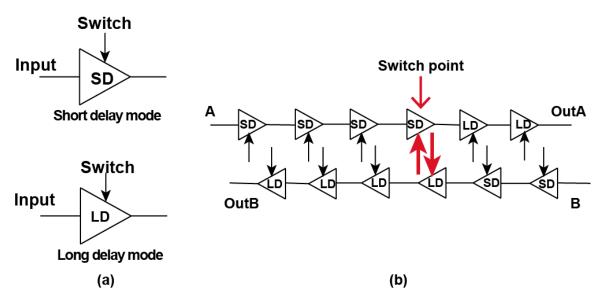

| 2.16 | Implementation of TDA based on switched-delay element. (a) The delay element can be switched with two delay modes. (b) Delay line configuration                                                                                                                                                                                |

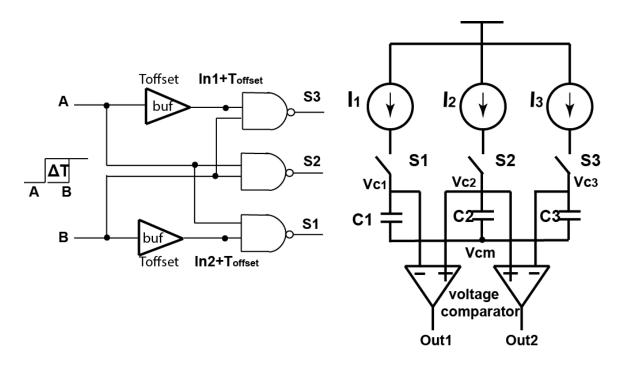

| 2.17 | Implementation of pulse-stretched TDA                                                                                                                                                                                                                                                                                          |

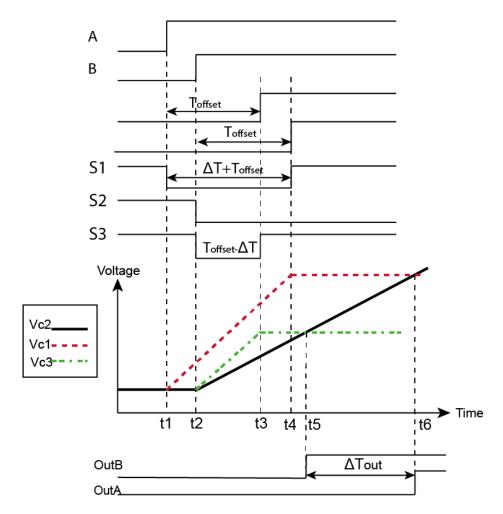

| 2.18 | Timing diagram of pulse-stretched TDA. The input TD $\Delta T$ is amplified to $\Delta T_{out}$                                                                                                                                                                                                                                |

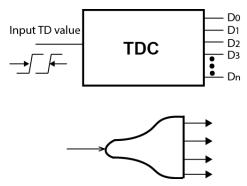

| 3.1  | TDC is presented in the traditional schematic symbol, in which each wire is drawn as a line or as a time difference symbols. Digital symbols are drawn with filled arrow heads and a TD signal is drawn as a an arrow with narrow arrowhead                                                                                    |

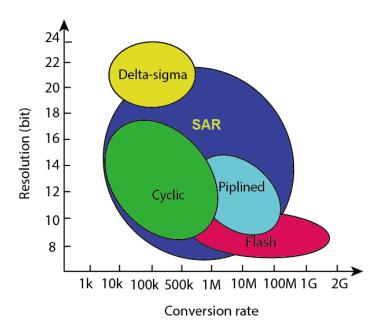

| 3.2  | Tradeoffs of different ADC architectures in resolution and conversion rate. (ADC-survey from [1])                                                                                                                                                                                                                              |

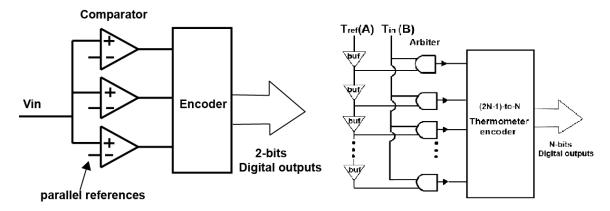

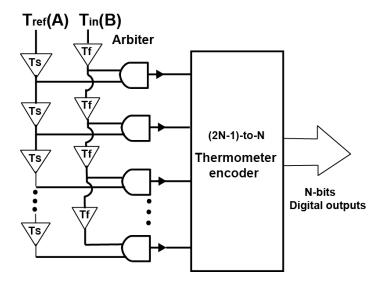

| 3.3  | Diagram of flash converter. Left: A general 2-bits flash analog to digital converter is consisted of 3 comparators and voltage references, encoding the compared results by a thermometer encoder to 4 digital outputs. Right: N-bits flash TDC function similar with flash ADC replacing the voltage comparator to TD arbiter |

| 3.4  | N-bit Vernier flash TDC is implemented with two delay lines with short single delay time $T_f$ and long delay time $T_s$                                                                                                                                                                                                       |

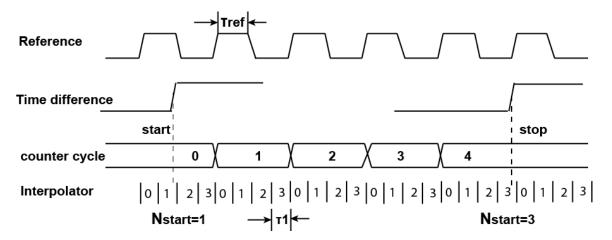

| 3.5  | TDC function diagram with a counter and interpolation                                                                                                                                                                                                                                                                          |

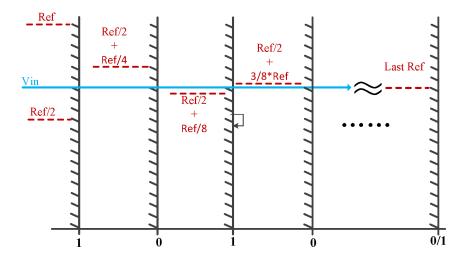

| 3.6  | 3-bit successive approximation conversion diagrams. The input signal value is compared to the reference dependent on the previous conversion results                                                                                                                                                                           |

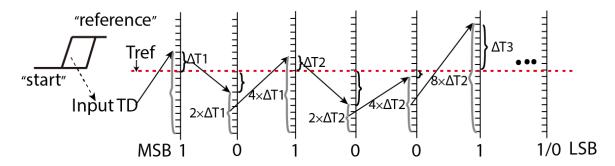

| 3.7  | Multi-bit function diagram of proposed CATDC with a fixed reference value; for each comparison the time residue is further processed for the next loop                                                                                                                                                                         |

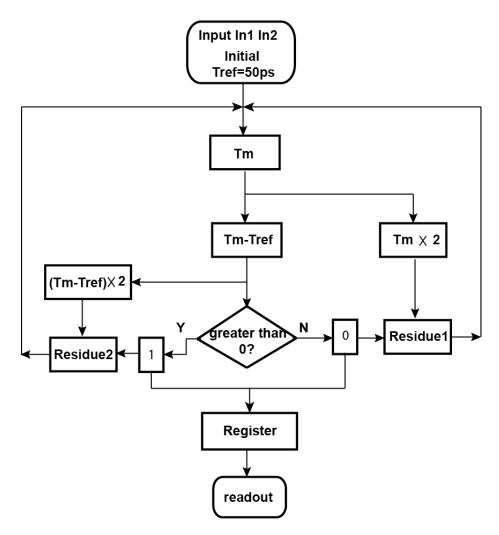

| 3.8  | The algorithm needs to be revised for time-mode conversion by splitting the amplification into two parallel paths. The algorithmic TDC conversion flow diagram is shown here                                                                                                                                                   |

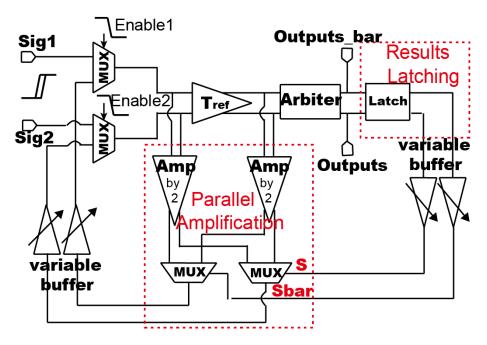

| 3.9  | The full implementation of proposed CATDC. The variable buffers are applied for compensating the variation along the delay paths due to PVT                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

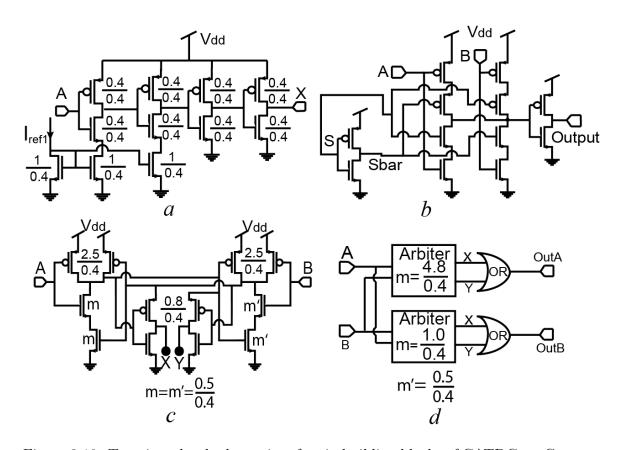

| 3.10 | Transistor level schematics of main building blocks of CATDC. a. Current-starved variable delay buffers. b. Multiplexer (MUX). c. Arbiter-based Time-Difference Amplifier. d. Balanced MUTEX-based Arbiter                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.11 | TDA function diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

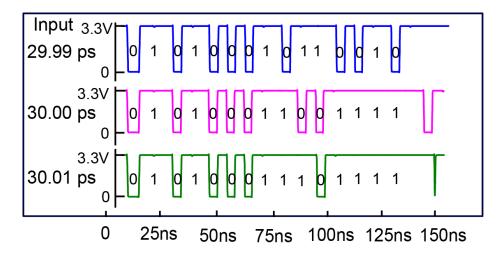

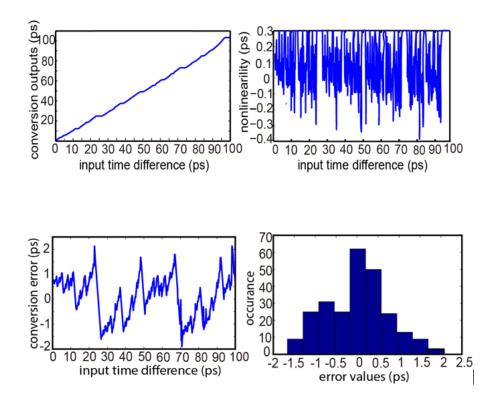

| 3.12 | CATDC transient simulation results with 0.01ps resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.13 | CATDC simulation results and analysis. a. Input time difference sweep from 0 to 100ps. b. Differential non-linearity presented in picosecond. c. Integral non-linearity, conversion error presented in picosecond. d. Error distribution                                                                                                                                                                                                                                                                                                                                                          |

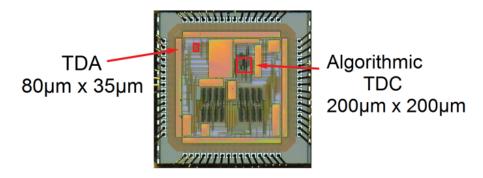

| 3.14 | The die photo of test chip, in which the overhead of CATDC and TDA are labeled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

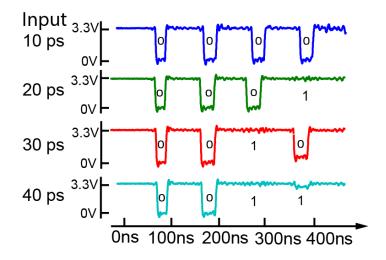

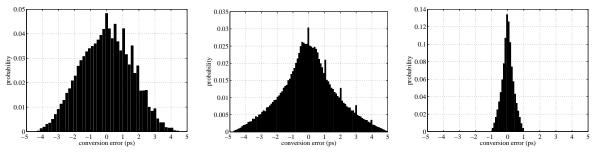

| 3.15 | Experimental test results of CATDC for 10ps, 20ps, 30ps, and 40ps input time differences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

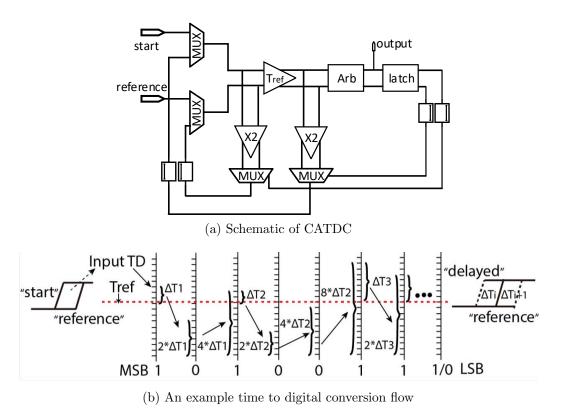

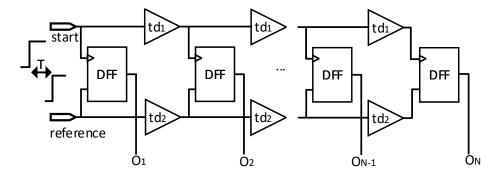

| 4.1  | Schematic of a time-to-digital converter design in [2]. $T_{ref}$ stands for the reference signal, the time difference TD between "start" and "reference" signals are iteratively compared with $T_{ref}$ to get each conversion bit. If the TD is larger than $T_{ref}$ , then the output is 1, otherwise the output is 0 and TD will be amplified by 2 for next comparison. The time can be rebuilt with the binary output as $\sum_{0}^{n-1} o_i \times \frac{T_{ref}}{2^i} \dots \dots$ |

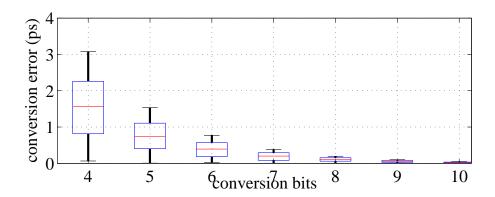

| 4.2  | The simulated conversion error caused by different factors; it can be seen that the inaccurate amplification and time reference block introduce more conversion error than process variations. This is because, in CATDC, the primary conversion procedure is accomplished by $T_{ref}$ and amplification module. While the effect of process variations between different transistors is canceled out along the delay chain, thus incurring less error. Due to the self-oscillation mechanism of CATDC, the impact of transient noise is automatically averaged                                  |

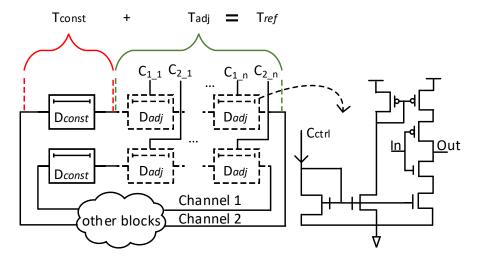

| 4.3  | Schematic of the proposed configurable delay element, which is composed of two blocks, $D_{const}$ and $D_{adj}$ . There are many possible implementations of the adjustable delay element, in this figure a current-controlled delay element is shown as an example56                                                 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

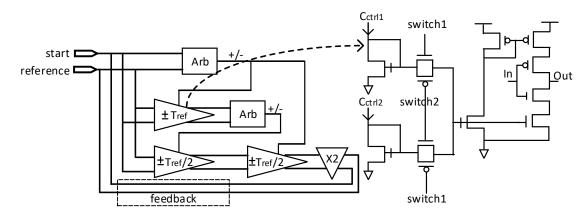

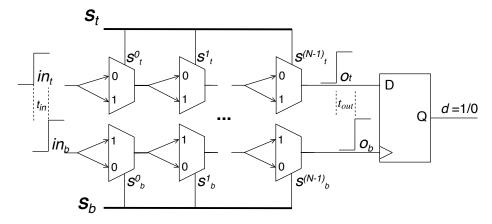

| 4.4  | Schematic of bidirectional CCATDC. Two Arbiter circuit is employed, the outputs of them are used to switch the effect of delay-line. The switch signal is used to determine which channel is delayed more than the other. Note that for brevity, some auxiliary blocks like latch circuit are not shown in this figure |

| 4.5  | Time conversion results of different input time differences (10-100ps), the designed CCATDC has an ideal reference time $T_{ref} = 50ps$ , and an ideal gain=2. It can be found that while more conversion rounds are utilized, the error become smaller 60                                                            |

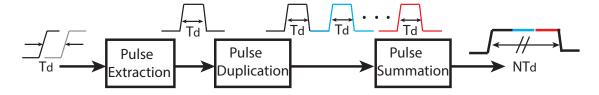

| 5.1  | Proposed Digital-Time-Difference-Amplifier block diagram 66                                                                                                                                                                                                                                                            |

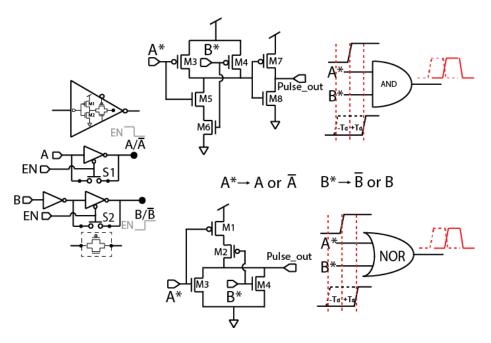

| 5.2  | Phase extraction based on two alternative designs of positive-edge phase detector. Inputs A and B are always opposite polarity 67                                                                                                                                                                                      |

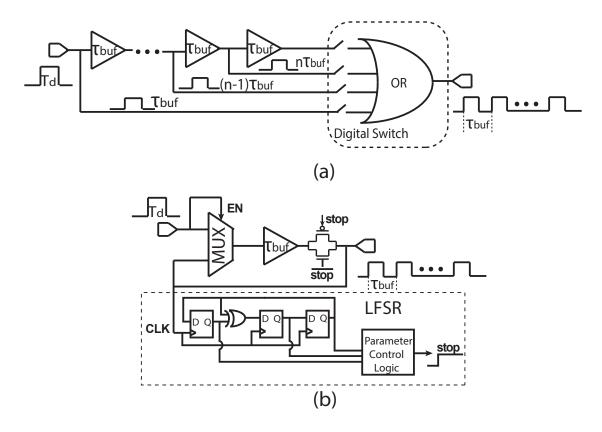

| 5.3  | Replicating pulses in parallel (a) and series (b)                                                                                                                                                                                                                                                                      |

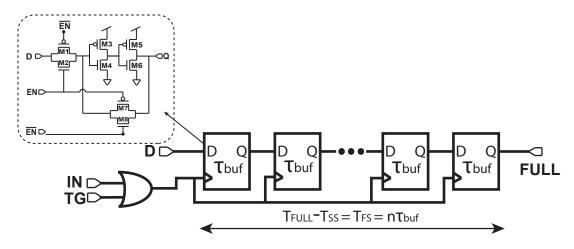

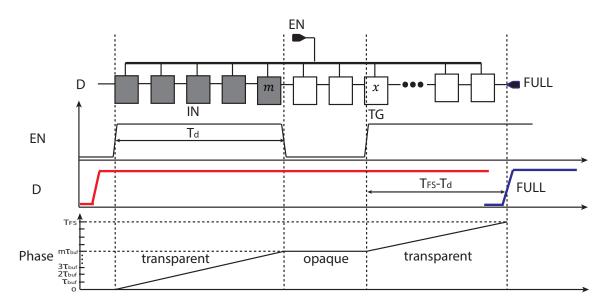

| 5.4  | Time-Latch implementation diagram using a chain of D-latch 69                                                                                                                                                                                                                                                          |

| 5.5  | Time-Latch function diagram with two modes: propagating and holding                                                                                                                                                                                                                                                    |

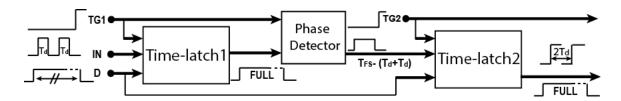

| 5.6  | Pulse summation by cascading two time-latches                                                                                                                                                                                                                                                                          |

| 5.7  | Implementation of multi-path time-latch to improve the time resolution of ADTDA                                                                                                                                                                                                                                        |

| 5.8  | The gain is tunable with integer multiplier                                                                                                                                                                                                                                                                            |

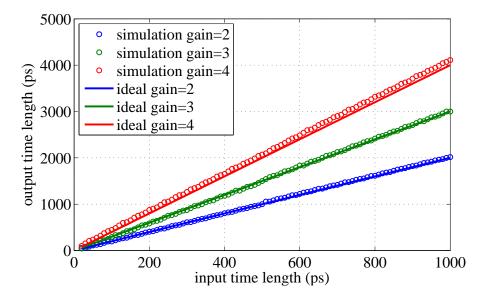

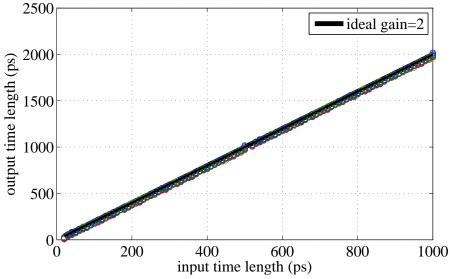

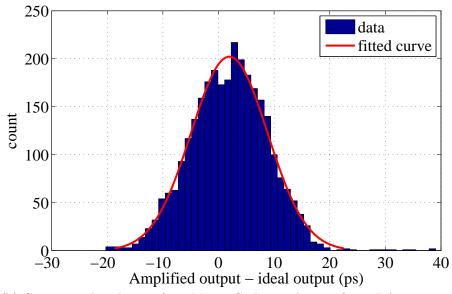

| 5.9  | Monte Carlo simulation results for 30 TDA instances. It can be observed that the gain of the proposed TDA architecture is reliable against process variations                                                                                                                                                          |

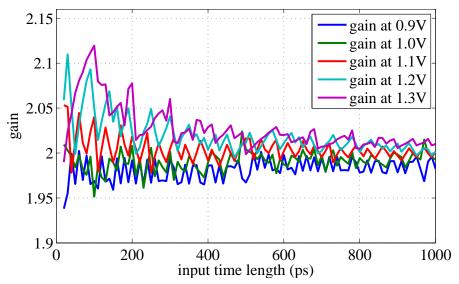

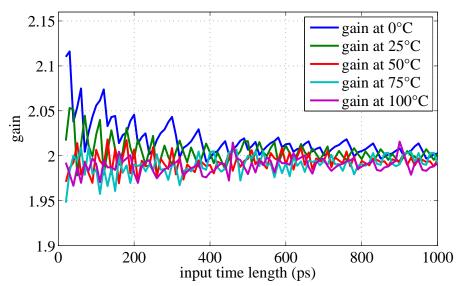

| 5.10 | The gain of proposed TDA architecture under different environmental conditions                                                                                                                                                                                                                                         |

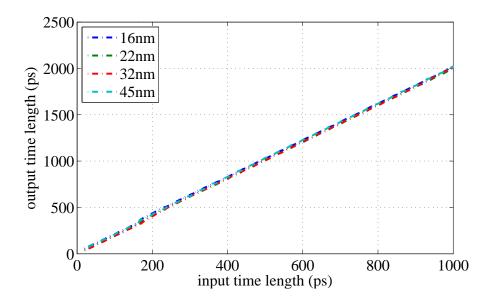

| 5.11 | The implementation of all-digital TDA is portable in other advanced CMOS technologies                                                                                                                                                                                                                                  |

| 6.1  | Schematic of a vernier TDC                                                                                                                                                                                                                                                                                                                                                                          |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2  | Schematic of PVTMC                                                                                                                                                                                                                                                                                                                                                                                  |

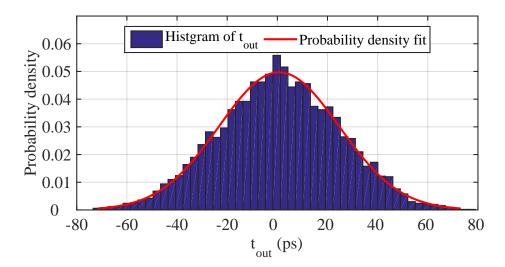

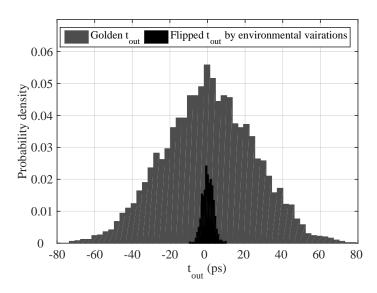

| 6.3  | The $t_{out}$ values follow approximately Gaussian distribution                                                                                                                                                                                                                                                                                                                                     |

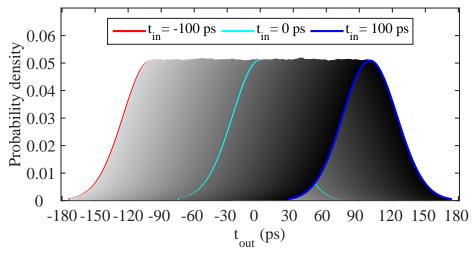

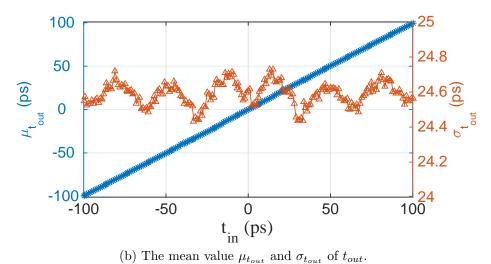

| 6.4  | Simulation results showing the distribution of $t_{out}$ . (a) plots the fitted distribution of $t_{out}$ values for different $t_{in}$ from $-100~ps$ to $100~ps$ . (b) plots the mean value $\mu_{t_{out}}$ and the standard variance for each fitted curve in (a)                                                                                                                                |

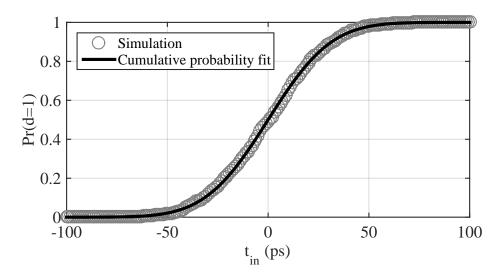

| 6.5  | The probability of generating $d=1$ by PVTMC circuit for different $t_{in}$ input values is in agreement with the CDF of Gaussian distribution $t_{in} \sim \mathcal{N}(0, \sigma_{t_{out}})$ . Thus, for a given $t_{in}$ , its value can be measured with the probability $P(d=1)$                                                                                                                |

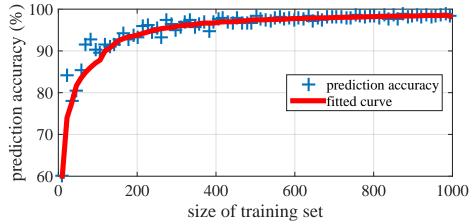

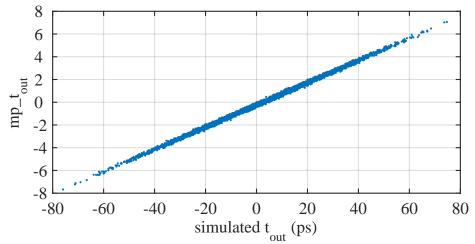

| 6.6  | (a) shows that while more training samples are used, the prediction rate of $\mathbf{P}_{model}$ becomes higher, and 1000 training samples achieves around 100% prediction rate. (b) presents simulated $t_{out}$ by HSPICE and model predicted $t_{out}$ by $\mathbf{P}_{model}$ . It can be found that there exist a linear relationship between these two parameters93                           |

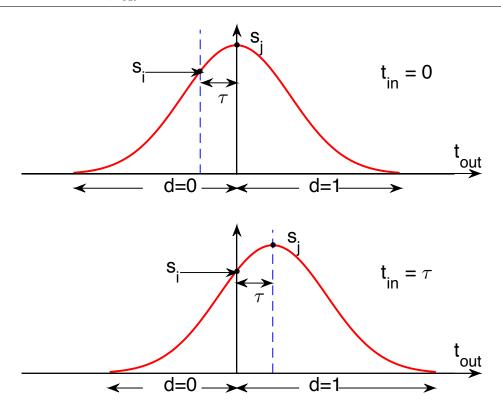

| 6.7  | Visualization of the PDF curve shift caused by $t_{in}$ . It can be found that, while $t_{in}$ changes, the boundary of $d = 1$ and $d = 0$ will shift correspondingly                                                                                                                                                                                                                              |

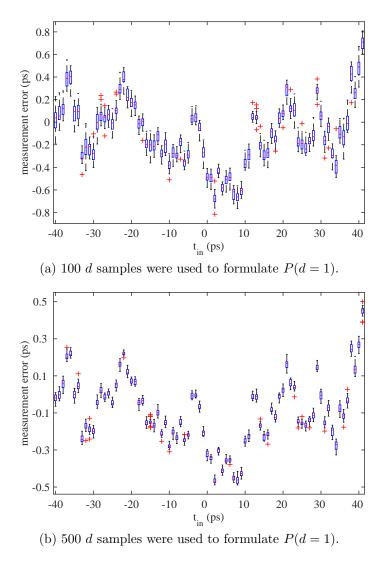

| 6.8  | Plot shows the timing measurement errors of random search. 1,000 iterations were analyzed for each $t_{in}$ . (a) In each iteration, 100 $d$ values were collected to formulate $P(d=1)$ , (b) In each iteration, 500 $d$ values were collected to formulate $P(d=1)$                                                                                                                               |

| 6.9  | Simulation results of $t_{out}$ at standard environmental condition $(25^{\circ}C, 1.1\ V)$ and a set of changed conditions                                                                                                                                                                                                                                                                         |

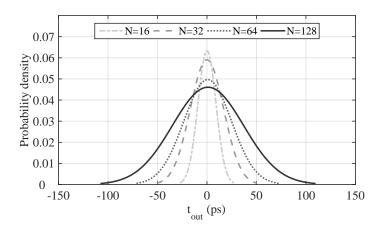

| 6.10 | Plot shows that a PVTMC circuit with more MUXs can coverage a larger measurable time range                                                                                                                                                                                                                                                                                                          |

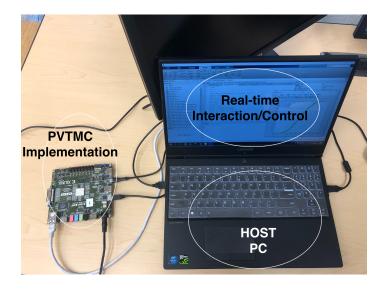

| 6.11 | The experimental setup for PVTMC circuit implemented on FPGA.  The HOST PC is used for programming and controlling the FPGA chip, i.e., sending and receiving data. In the HOST PC, a  Matlab-based framework is built, which can visualize and analyze the measurement data in real-time. Note that the real-time control is an important component to realize the binary search-based measurement |

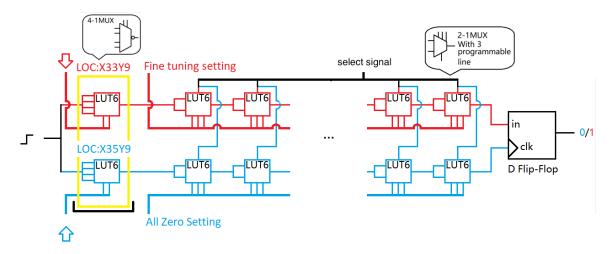

| 6.12 | Schematic of PVTMC implementation on FPGA                                                                                                                                                                                                | 102 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

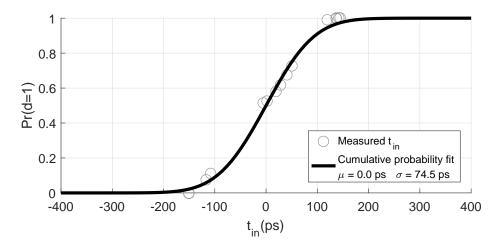

| 6.13 | 16 measured $t_{in}$ values and the corresponding fitted CDF curve. It can be found that the values of $\mu_{t_{out}}$ and $\sigma_{t_{out}}$ formulated from this curve are $0ps$ and $74.5ps$ , respectively                           | 105 |

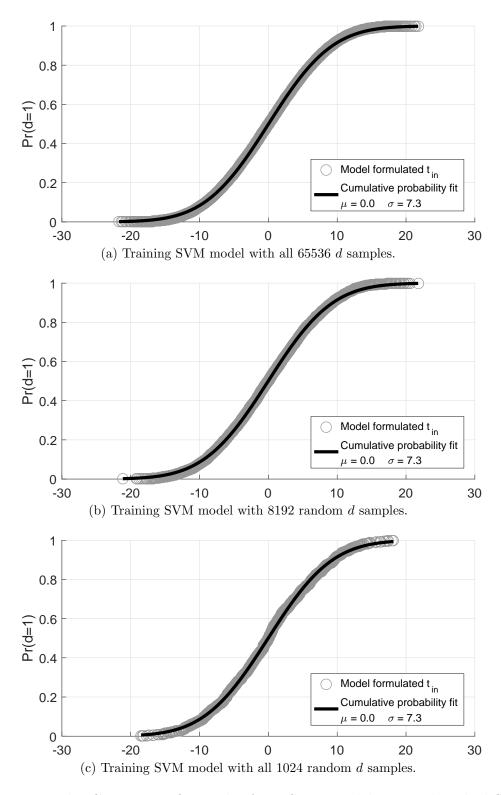

| 6.14 | The CDF curve fit results from SVM models trained with different number of training samples. It can be found that is the training samples are randomly selected, using fewer number of training samples does not degrade the performance | 108 |

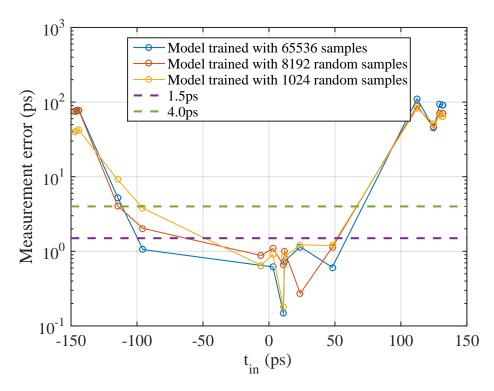

| 6.15 | The timing measurement results with PVTMC model trained with different amount of samples. It can be found that using fewer number of training samples does not degrade the measurement accuracy.                                         | 109 |

#### CHAPTER 1

#### BACKGROUND AND MOTIVATION

The characteristics that are commonly used to describe electronics circuits include voltages, currents, or digital bits. This thesis focuses on the investigation of a different variable: Time Difference (TD), which is essential for a wide variety of both on-chip and off-chip applications. Examples include measuring clock skew and jitter [3][4], building LIDAR remote sensing systems [5], synthesizing and optimizing digital systems. The main contributions of this thesis are 1) a design methodology that systematically organizes the TD circuits, 2) several novel and practical time-to-digital converter (TDC) designs, and 3) a new approach to an All-Digital design of a Time-Difference Amplifier, which forms the foundation of the TD circuits digital realization.

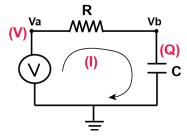

Voltage, current, and charge are three commonly used parameters in the description of analog circuits. These three parameters are closed related with each other: voltage is defined between each node and ground, current is defined through each element, and charge is stored on capacitors, as shown in Fig. 1.1.

Figure 1.1: Traditional analog variables represent circuits.

Though these parameters are closely related, different parameter-based circuits have unique strengths and weaknesses. For example, voltage-mode circuits are the

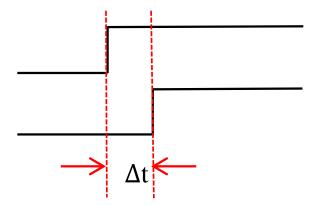

Figure 1.2: Definition of TD variable. The rising edges of two pulses determine the time difference.

most commonly used because voltage can be easily distributed and nondestructively measured with high input impedance instruments, such as voltmeters and oscilloscopes [6]. The weakness of voltage-signal is that its value is usually limited within the range of the supply voltage. As the CMOS feature size shrinks down below 100-nanometers (nm), the transistor gate oxide thickness forces the supply voltage to decrease below 1 volt. Correspondingly, the signal headroom becomes too small to design circuits with sufficient dynamic range [7]. Although the current-mode circuits take advantage of easy and accurate scaling and addition [8]. They have unique weaknesses that measuring current usually means high power consumption for large signal values and the need to make copies of currents with current mirrors to distribute a signal.

Time Difference (TD) circuits are becoming attractive for two types of applications:

1) where the physical signal being processed is inherently a time difference between two events; and 2) the processing of analog signals should be at very low supply voltage [9]. Specifically, the Time Difference (TD) in this thesis is defined as the time interval between two pulse edges, shown in Fig. 1.2, which is obtained by differentiating two pulsing edges. The advantage of TD variable that is independent with power supply makes it an ideal parameter for analog signal processing with requirement for higher resolution and lower power consumption than traditional analog signal processing [10].

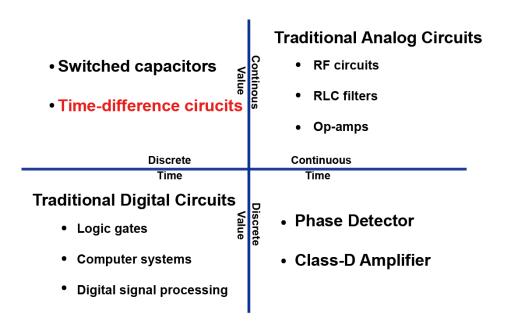

Figure 1.3: Classification of circuit types in time-value plane.

#### 1.1 Classification of circuits

All types of circuits can be classified according to the time-value quadrants plane. The TD circuits presented in this thesis operate on continuous electronic parameters like voltage and current, which is different from circuits that work in discrete time points. The circuits belong to the class are known as the discrete-time continuous-value circuit, as shown in Fig. 1.3, which shows that the sampled value at discrete time point can be any real number within a range, but it can only change at discrete times. TD circuits can be compared to analog circuits in the time-value plane where signals vary continuously in a range. In comparison, traditional digital circuits quantize both time and voltage, so the signal only switches at the clock frequency between two stable logic voltages "0" and "1".

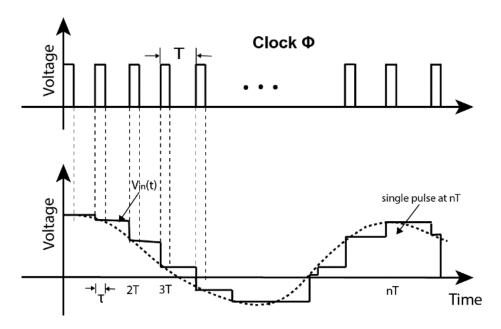

The less common quadrants of the time-value plane are Continuous-Time Discrete-Value (CTDV) and Continuous-Value Discrete-Time (CVDT). The most common CTDV circuit is digital phase detector, while the most commonly used DTCV circuit is switched-capacitor circuit [11] [12]. Switched-capacitor circuits hold an analog signal

Figure 1.4: Discrete-time continuous-value signal sampled with clock cycle T.

as the charge on a capacitor, which is only get charged during clock edges, as shown in Fig. 1.4. Switched-capacitor circuits are good for discrete-time signal processing because the transfer function is governed by capacitance matching, not transistor parameters [13]. The TD circuits studied in this thesis are also DTCV circuits, but unlike switched-capacitor circuits whose value is invalid between changes, it is only valid during a single event.

### 1.2 Applications of time-difference circuits

Time-difference circuits can be employed in various fields [14] [15] [16] [17] [18] [19], a few of them are summarized in Fig. 1.5. This chapter highlights three applications: LiDAR [5], biomedical imaging, timing characterization for integrated circuit.

#### 1.2.1 Application of time difference circuits in LiDAR

Light Detection and Ranging (LiDAR), like RADAR (Radio Wave Detection and Ranging), obtains the distance information by measuring the time difference between sending an excitation pulse and receiving a reflected pulse from a target object [20].

Figure 1.5: Applications of time-difference circuits.

Figure 1.6: An example schematic of LiDAR system. The distance between the object and sensor is measured by time interval between two pulses.

$$|D| = \frac{1}{2}(v_{light} * t_{bounce}) \tag{1.1}$$

LiDAR and RADAR differ in the wavelength of the electromagnetic pulse. The shorter wavelength of light used in the LiDAR system compared to radio waves used in RADAR creates a more focused beam [20]. The narrower beam means that LiDAR can image smaller objects [15] [5]. LiDAR systems consist of three major components: a light source (laser), a scanner, and a sensor (photo-detector), as shown in Fig. 1.6.

A light source emits a pulse that bounces off the objects. The receiver contains high-speed photo-detectors that can sense the reflected laser pulse. Time-difference circuits are then used to measure the time interval between these two pulses. Since the speed of light is 299, 792, 458 meters per second, the measurement resolution of picosecond to nanosecond timescale are required to achieve excellent accuracy for measuring small objects such as forestry layer measurements [21], atmospheric aerosol measurements [22], and chemical particle detections.

Because LiDAR uses light wave, it applies a similar basis with the time-of-flight (TOF) camera [23], which can be used to capture 3D images. The TOF camera measures the distance from objects to its every pixel, requiring high-resolution detector and TD circuits to obtain the small range accurately. Real-time motion imaging systems require a short time-difference measurement circuit with a high-speed operation that can be integrated within each pixel in the imaging sensor.

## 1.2.2 Application of time difference circuits in fluorescence lifetime imaging

The time difference between excitation of a light pulse and recording of a photon is also of interest for fluorescence lifetime imaging [24]. Fluorescence imaging is widely used in biology because of the ease of labeling biological molecules, the availability of multiple colors and high signal-to-background ratio. Fluorescent labeling of proteins is an important technique for understanding protein structure, protein folding, and chromosome formation [25] [26] [27]. RNA and DNA labeling are important techniques for disease diagnosis [28].

Fluorescence imaging is performed by illuminating a sample with filtered light by an excitation filter and imaging the sample through an emission filter [24]. The fluorescence lifetime is the time constant of exponential energy decay, as shown in Eq. 1.2 [24] [29]. Fluorescent lifetime is used to measure the chemical environment in solutions of pH or calcium ion concentration [30] [31].

$$p(t) = \alpha e^{-\frac{t}{\tau}} \tag{1.2}$$

TD circuits are significantly used in two techniques for CMOS fluorescence lifetime sensors: direct integration/digitization and time-correlated single photon counting (TCSPC), both techniques can be used in high-throughput biomedical imaging [24]. The usage of the pixel topology determines the choice of the sensors and the corresponding timing control circuits. Direct integration and digitization use a high-speed detector to record the exponential decay in a single excitation pulse [32]. This is a conventional technique with which the fluorescence lifetime can be measured directly by exciting the fluorophore with an impulse of light and measuring the fluorescence with a high-speed detector [24]. Rapid lifetime determination (RLD) calculates the fluorescence lifetime using images from two time windows [33], as shown in Fig. 1.7. The ratio of the signals from the two windows is then used to calculate the fluorescence lifetime using Eq. 1.3.

$$\tau_{RLD} = \frac{-\tau_{win}}{\ln(\frac{w_2}{w_1})} = \tau \tag{1.3}$$

Optimum width of the time windows,  $\tau_{win}$ , for creating a low noise measurement, is equal to the expected fluorescence lifetime [24]. Since fluorescent lifetime floats between a hundred picoseconds and hundreds of nanoseconds, TD circuit is required to precisely set the adjustable integration time windows with wide time range for optimum signal-to-noise sensing of fluorescence lifetime [34].

Unlike integrating pixels that convert the number of photons hitting the photodiode into a voltage, TCSPC applies single-photon avalanche diodes (SPADs) to generate the signal as soon as the first individual photon is detected [35][32]. The sample is excited periodically with a pulse source, each time a photon is detected,

Figure 1.7: RLD method for fluorescence lifetime measurements. When a pulse excites the sample, the intensity falls off exponentially after the pulse. The fluorescence lifetime can be calculated using RLD method with the fluorescence intensity in two time windows W1 and W2.

Figure 1.8: Operation principle of time-correlated single photon counting (TCSPC) measurements. The sample is excited by a pulsed laser source with a high repetition rate. By counting many events a histogram of the photon distribution over time is built up.

time difference circuits measure the time interval between corresponding detection and excitation pulses. The photon is counted as "1" at the location that is proportional to the detection time in the memory. After collecting a group of photons, a histogram of detection time reconstructs the optical decay waveform, as presented in Fig. 1.8.

Because at very low light levels every photon that hits a photo-diode is collected and its arrival time is precisely measured, the sensor arrays built with SPAD pixels are more sensitive to low fluorescence signal levels than sensor arrays built with integrating pixels. In this case, a time-to-digital converter (TDC) is an essential component in SPAD pixel-based fluorescence sensor and requires compact structure, high resolution and throughput [35].

## 1.2.3 Application of time difference circuits in timing characterizing and IC optimization

As transistor characteristics are shrinking down to sub-ten nanometers in CMOS fabrication process, minimum gate delay decreases to dozens of picoseconds or even sub-ten picoseconds. In such a fine time scale, the supply voltage is reduced below one volt, which makes the manipulation of analog parameters more challenging. To overcome these issues, TD circuits are proposed to offer an alternative signal processing approach for conventional A/D converter and Phase-Locked Loop (PLL) that can avoid the limitations on voltage headroom, but without degrading the voltage resolution. Meanwhile, digital-friendly mixed-signal circuits such as all-digital phase-lock loop (PLL)/delay-lock loop (DLL) are highly developed as the interface that can help better leverage digital circuits to improve analog processing capability, as shown in Fig. 1.9. In these circuits, the digital representation of the phase difference and time mismatch is an essential function for the digital-controlled synchronization and calibration [36][10][37]. In both scenarios, the TD circuits plan an essential role for the mixed-signal circuits to maintain high-quality performance.

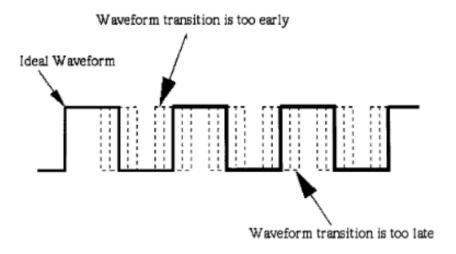

The time jitters and clock skew in critical paths, or high-speed interconnections can directly impact the timing characteristics of the electronic systems, which may even cause function failure [3][4]. Jitter is the timing variations of a set of signal edges from their ideal values, which in clock signals are typically caused by noise or other

Figure 1.9: Build-in timing measurement circuits using TD circuits (Time-to-Digital Converter) for real-time digitizing and characterizing the phase error for PLL/DLL.

Figure 1.10: Jitter description in a clock signal.

disturbances in the system, as demonstrated in Fig. 1.10. The composition of jitter includes thermal noise, power supply variations, loading conditions, device noise, and interference coupled from nearby circuits [4]. Consider a microprocessor-based system in Fig. 1.11, in which the processor requires data setup time before clock rise, if the clock encounters negative period jitter, then the rising edge of the clock could occur before the data is valid [38][39]. Similarly, the hold time may be violated if positive jitter happens. Hence the microprocessor will be presented with incorrect data.

Figure 1.11: Time constraints of data setup/hold time for sequential circuits.

In summary, the demanding for a robust and efficient testing block of the jitter, phase, and distributed clock skew measurements have rapidly risen in recent years. In both scenarios, TD circuits, especially Time-to-Digital Converters (TDCs) are playing an essential role in timing measurement. TDCs realize the non-invasive measurement of timing/phase characteristics by precisely digitizing the time interval between two events, usually two rising edges. On-chip integration with the DUT blocks fully reduces the effects of the external loads and noise in the off-chip testing system [20]. The state-of-art performance of integrated systems requires that TDC must provide high resolution within a very small area in order to be distributed around the die.

#### 1.3 Thesis Outline

This chapter mainly describes the background of time difference circuits, a class of circuits that measure the time interval between two events. Chapter 2 presents the methodology of signal processing based on the time-difference circuits and provides a new organization of TD function blocks that are used to build comprehensive time-difference circuits. Chapters 3 introduces the different types of TDCs by comparing their topologies, performance, and cost. And a novel compact TDC architecture is proposed and fabricated. Chapter 4 solves practical and industrial problems in

proposed algorithmic TDC; the design is improved to increase the digitizing throughput and save more power. In Chapter 5, we come up with an all-digital time-difference amplifier with only standard digital blocks, the implementation of which can be successfully transferred to difference advanced CMOS technologies, which lays the foundation of the digital realization for the time difference circuits. Chapter 6 presents a novel timing measurement circuit: PVTMC that constructively leverages the process variations from circuit fabrication to measure timing signals, which achieve high resolution as of < 0.5ps. Chapter 7 concludes this thesis.

#### CHAPTER 2

#### METHODOLOGY

The concept and classification of time difference (TD) circuits are introduced in Chapter 1. In this chapter, we discuss the TD signal processing methodology in details and provide a systematic organization of the TD function modules. In TD circuits, the most interesting information is the time difference between between two pulses, rather than the nodal voltages or branch currents of electric networks. Therefore, TD circuits offer a new and promising way for mixed-mode systems to deal with the challenges of conventional voltage/current-mode designs.

TD signal, which two time instants occur at specified timing points, will disappear at any timing point in the future. Since the original events are gone, so does the TD information stored in the signals. Therefore, the first difficulty of measuring TD signal is to storage and re-usage it with considering the discrete-time and continuous-value feature. In this chapter, we systemically study the fundamental of TD circuits, new methodology for TD signal processing definition and circuits expression are also included.

### 2.1 Signal processing in time-mode

Time-mode circuits depict an analog signal using the difference between the timing points at which two timing events take place. Ideally, the amount of time difference is linearly proportional to the amplitude of the analog signal. A time variable is a pulse-width-modulated signal with its pulse width directly proportional to the magnitude of the signal that it represents. A time variable possesses a unique duality characteristic;

specifically, it is an analog signal as the continuous amplitude is represented by the duration of the pulse. However, we can also deem it as a digital signal since it only has two largely distinct values. The duality of time variables enables them to conduct analog signal processing in a digital environment. This unique characteristic is possessed by neither analog nor digital variables.

Time-mode signal processing deals with addition, multiplication, amplification, integration, and comparison, etc., of time variables. Information to be processed by time-mode circuits is represented by the time difference between digital signals, for example, pulses. These circuits are necessarily digital systems that perform analog and mixed analog-digital signal processing without using power-greedy and speed-limited digital signal processors.

#### 2.1.1 Time-mode vs. voltage-mode signal processing

Nowadays, the typical requirements of advancing CMOS technology is the capability of integration with high-performance digital systems. As a result, CMOS analog circuits are losing the flexibility to adapt specific and process-controlled components critical to the performance of these circuits [40]. Also, the voltage headroom, that is, the difference between the given supply voltage of a circuit and the minimum supply voltage of the circuitry required for MOS transistors to operate in saturation is continuously reducing and approaching to the performance constraints [7][40] [41]. The shrinking voltage headroom not only limits the maximum achievable signal-to-noise ratio (SNR), it also enlarges the effect of the non-linear characteristics of MOS devices which subsequently reduces the dynamic range of voltage-mode circuits [42]. As a result, the accuracy of voltage-mode circuits, or the minimum detectable voltage, typically degrades with technology development [40].

#### 2.1.2 Time-mode vs. current-mode signal processing

Current-mode circuits apply current branches of circuit networks to represent the signal processing, compensating for the dropping of the voltage headroom. These circuits achieve a low voltage swing by lowering the impedance of nodes. The existence of low-impedance nodes throughout current-mode circuits, however, gives rise to large branch currents, typically consuming more power as compared with their voltage-mode counterparts. Lowering the power consumption of current-mode circuits while meeting other design constraints at the same time is rather difficult. The characteristics of the low-impedance nodes of current-mode circuits, on the other hand, offer an inherent advantage of a low time constant at every node of the circuits. As a result, current-mode circuits are suitable for applications where speed is more critical than power consumption. Since voltage and current are inherently related to each other via impedance or conductance, the characteristics of voltage-mode circuits and current-mode circuits do not fundamentally differ with each other. As a result, the performance of both circuits does not scale well with CMOS technology development.

#### 2.1.3 Time-mode signal processing strengths and challenges

As the intrinsic gate delay of digital circuits accommodates most from technology scaling, time-mode circuits become a promising applicant of rapid signal processing. For example, the oscillation frequency of ring oscillators implemented in state-of-the-art CMOS technologies has reached tens of GHz, providing a large oversampling ratio while consuming a small amount of power [40]. It is showing that time-based signal processing has many desirable characteristics such as excellent scalability with the advancement of CMOS technology, such as reconfigurability, ease of portability, low-power consumption, and high-speed operation, which are competitive to mixed analog-to-digital signal processing outperform voltage and current driven circuits.

Although time-based signal processing possesses many critical advantages, challenges also need to be considered. The intrinsic gate delay of digital circuits benefits the most from technology scaling and device mismatch. To minimize the effect of device mismatch, minimum-sized delay cells are usually used, which can cause the impact on the speed and subsequently on other specifications of time-mode circuits. For time-mode circuits, to against of process, supply voltage, and temperature (PVT) variation is the other inevitable challenges [40]. Usually, corresponding calibration techniques and assisted circuits are applied to minimize the PVT effects on the performance of TD circuits [36].

Withholding or storing a time variable is rather difficult due to the irretrievable nature of time, which rises unique challenges to operate circuits using conventional function blocks [40]. To overcome the obstacles, we introduce a new methodology to organize and describe the TD circuits function in the next section, with which we can solve different problems with specified targets. The practical examples are demonstrated in the following chapters.

#### 2.1.4 TD circuits operation functions

TD circuits are a new class in the circuits family branches where the particular circuits feature drives the unique understanding of the circuits expression. However, due to the relatively less study on it, the systematic organization of the function blocks is rare to see. In this section, we study all types of TD circuits from wide-spread application fields and give a summary of TD circuits function analogous to the conventional voltage-mode circuits, four primary functions are standardized as a sample and hold, the arithmetic unit, comparison, and amplification, to build comprehensive TD systems.

Figure 2.1: Function block and timing diagram of time-difference memory. The time-difference information is stored in the repeated events.

## 2.1.5 TD Sample and Hold (S/H)

As TD signal is transient, discrete time signal, the conventional sample and hold function is not applicable here. In order to realize multiple operations on the same TD at different time, the signal must be stored or rerouted around the circuit. A design is shown in Fig 2.1(top), in which the multiplexing paths let TD signal propagate through with delay buffers, this operation is more likely sampling the TD signal and holding it for the later use. Instead of recording the time difference between two events directly, TD S/H can be realized by repeating the timing events as well, as shown in Fig 2.1(bottom). With the repeated events, the TD value can be reused in each repeating period. Time-difference storage can be achieved with a feedback-loop multiplexer that is used to select feedback signal after the original input TD event finishes, this feedback-loop can also block interference signal from input. Delay buffers can be used to adjust the repeating period.

#### 2.1.6 TD arithmetic operation

TD arithmetic operation such as TD adding/subtracting and TD integration is critically needed in time-based signal processing. The accumulation of a variable in the voltage or current mode can be realized by representing the variable as current and integrating the current onto a capacitor or inductor. However, the arithmetic operation in TD circuits is different.

#### 2.1.6.1 TD adding/subtracting

The mechanism to add or subtract a certain amount of time from the target TD between two signals is making either of the signals delayed by a fixed delay element. If the 'start' signal is delayed, the subtraction is archived; while opposite operation realizes adding. A fixed amount of delay time generated by a delay buffer or delay-line plays the role of an adder or a subtractor. The sign of the operand can be easily switched by moving the delay time between two input nodes.

The delay element shown in Fig 2.2 can be implemented with a simple CMOS inverter. The propagation delay  $t_{pd}$  of an inverter is a fixed value for a given CMOS process. The CMOS inverter-based delay element and its transient waveform are shown in Fig 2.3, in which the inverter delay element produces an inverting propagation delay. The transition time of the basic inverter is determined by the charging time of a load capacitor,  $C_{load}$ , with drain current  $I_D$ , as shown in equation 2.1.

$$t_{pd} = C_L \int \frac{dV_{out}}{|I_D|} \tag{2.1}$$

There are alternative ways of varying the propagation delay of delay-elements by adjusting either load capacitance or drive resistance. In Fig 2.4, we illustrate all these options using a control voltage, a control current, or a digital control value. The driven-resistance adjustable delay elements are also called a current-starved inverter. However, the tunable range of these methods are relatively smaller.

Figure 2.2: The symbol and basic function of a time-difference adder. TD ① labels the input TD value and ② labels the output TD value. Delay1 and Delay2 are two constant delay values

Figure 2.3: Alternative Designs of adjustable delay elements by controlling current, voltage and load capacitance.

The digital-controlled delay-element can also achieve similar performance of adjusting the delay time with small step. A useful feature of these designs stands out for directly interfacing with the digital system and microprocessors.

Figure 2.4: Alternative Designs of digital-controlled delay elements.

A digital-to-time converter (DTC) is the compound version of the digital-controlled delay element [43][44]. DTCs convert the digital input strings into precise TD value and are functioned as a programmable TD generator [34], which can configure a wide range of desired TD value as a reference of a clock or time windows for TD systems.

#### 2.1.6.2 TD integration