## Journal of Physics D: Applied Physics

#### **ACCEPTED MANUSCRIPT**

# Diamond power devices: State of the art, modelling and figures of merit

To cite this article before publication: Nazareno Donato et al 2019 J. Phys. D: Appl. Phys. in press https://doi.org/10.1088/1361-6463/ab4eab

## Manuscript version: Accepted Manuscript

Accepted Manuscript is "the version of the article accepted for publication including all changes made as a result of the peer review process, and which may also include the addition to the article by IOP Publishing of a header, an article ID, a cover sheet and/or an 'Accepted Manuscript' watermark, but excluding any other editing, typesetting or other changes made by IOP Publishing and/or its licensors"

This Accepted Manuscript is © 2019 IOP Publishing Ltd.

During the embargo period (the 12 month period from the publication of the Version of Record of this article), the Accepted Manuscript is fully protected by copyright and cannot be reused or reposted elsewhere.

As the Version of Record of this article is going to be / has been published on a subscription basis, this Accepted Manuscript is available for reuse under a CC BY-NC-ND 3.0 licence after the 12 month embargo period.

After the embargo period, everyone is permitted to use copy and redistribute this article for non-commercial purposes only, provided that they adhere to all the terms of the licence <a href="https://creativecommons.org/licences/by-nc-nd/3.0">https://creativecommons.org/licences/by-nc-nd/3.0</a>

Although reasonable endeavours have been taken to obtain all necessary permissions from third parties to include their copyrighted content within this article, their full citation and copyright line may not be present in this Accepted Manuscript version. Before using any content from this article, please refer to the Version of Record on IOPscience once published for full citation and copyright details, as permissions will likely be required. All third party content is fully copyright protected, unless specifically stated otherwise in the figure caption in the Version of Record.

View the article online for updates and enhancements.

# **Title**

Diamond Power Devices: State of the Art, Modelling, Figures of Merit and Future perspective

## **Authors**

N.Donato<sup>1</sup>, N.Rouger<sup>2</sup>, J.Pernot<sup>3,4,5</sup>, G.Longobardi<sup>1</sup>, F.Udrea<sup>1</sup>

- <sup>1</sup> Engineering Department, Cambridge University, Cambridge, U.K.,

- <sup>2</sup> LAPLACE, Université de Toulouse, CNRS, F-31071 Toulouse, France

- <sup>3</sup> University Grenoble Alpes, F-38042 Grenoble, France

- <sup>4</sup> CNRS, Inst. NEEL, F-38042 Grenoble, France

- <sup>5</sup> Institut Universitaire de France, 103 Boulevard Saint Michel, 75005 Paris, France

# **Table of Contents**

| Keywords                         |                                  |                   |         |      |

|----------------------------------|----------------------------------|-------------------|---------|------|

| List of symbols and acronyms     |                                  |                   |         | •••• |

| Abstract                         |                                  |                   |         |      |

|                                  |                                  |                   |         |      |

| 1. Introduction                  |                                  |                   |         | •••• |

| 2. Material requirements and     | d modelling                      |                   |         |      |

|                                  |                                  |                   |         |      |

| 2.2. Doping and defects          |                                  |                   |         |      |

| 2.3. Device surface termination  | on                               | •••••             |         |      |

| 2.3.1. Oxvgen termi              | nation                           |                   |         |      |

|                                  | nination                         |                   |         |      |

|                                  | mond                             |                   |         |      |

|                                  |                                  |                   |         |      |

| 2.5. Bulk and surface mobility   |                                  |                   |         | •••• |

| 3. Figure of merits: definition  | and discussion                   |                   |         |      |

| 3.1 Limits of existing figures o | f merits and their application t | o diamond power ( | devices |      |

| 3.2 Device surface and current   | t rating                         |                   |         |      |

| 3.3 Breakdown voltage            |                                  | •••••             |         |      |

| 3.4. Switching losses            |                                  |                   |         |      |

|                                  |                                  |                   |         |      |

| 3.5. Other criteria and figures  | of merit                         | •••••             |         | •••• |

| 4. Diamond devices for power     | er converters                    |                   |         |      |

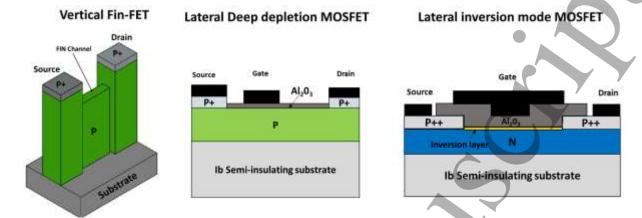

| 4.1 Overview of diamond de       | vice architectures               |                   |         |      |

| 4.1.1. Diodes                    |                                  |                   |         |      |

| 4.1.2. Metal-Oxide               | -Semiconductor devices           |                   |         |      |

| 4.1.2.1. Deep depletion MOSFETs                          |          |

|----------------------------------------------------------|----------|

| 4.1.2.2. Inversion MOSFETs                               |          |

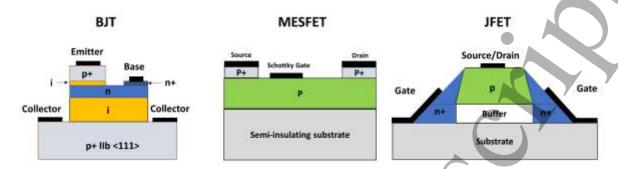

| 4.1.4. JFETs, MESFETs and Bipolar Transistors            |          |

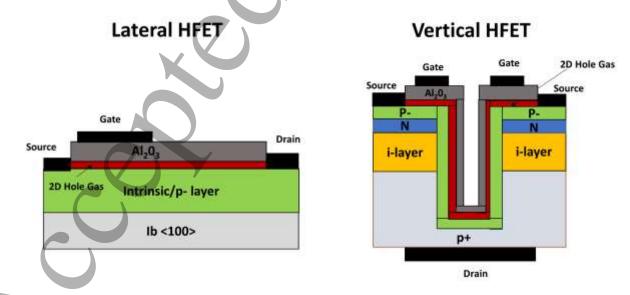

| 4.1.5. 2DHG FETs                                         |          |

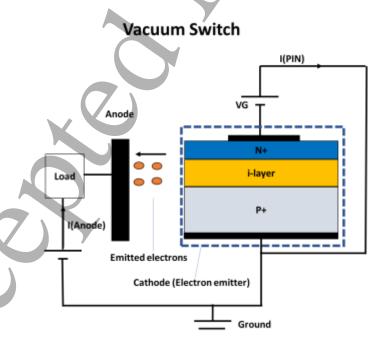

| 4.1.6. Vacuum switches                                   |          |

| 4.2. Comparison of 2DHG and bulk transistors             |          |

| 4.3 Leakage current in diamond devices                   |          |

| 4.4. Diamond devices with field relief designs           |          |

| 4.5. Packaging, thermal management and reliability       |          |

| 5. Benchmark of diamond power devices                    |          |

| 5.1. System level benefits and challenges                |          |

| 5.2. Power converters with diamond devices               |          |

|                                                          |          |

| 5.4. Benchmarking of diamond FETs against 4H-SiC and GaN |          |

| 5.4.1. 10kV range                                        |          |

|                                                          |          |

| 6.1. The roadmap of diamond                              | <b>X</b> |

| 6.2. Conclusions                                         | <b></b>  |

|                                                          |          |

## Keywords

Diamond, power devices, wide bandgap semiconductors, figures of merit, power converters, packaging, modelling, diamond roadmap.

# List of symbols and acronyms

(B)FOM, (BALIGA) figure of merit

(N)PT, (non) punch-through design

2DHG (2DEG), two-dimensional hole (electron) gas

A\*, Richardson constant,

BJT, bipolar junction transistor

BV, breakdown voltage

$C_{T(BV)}$ , transition capacitance

Coss, output capacitance

CVD, chemical vapor deposition

d, region thickness

dV/dt (di/dt), time derivative of voltage (current)

Ec, critical electric field

E<sub>co(va)</sub>, conduction/valence band minimum/maximum

E<sub>G</sub>, bandgap

E<sub>on</sub> (E<sub>off</sub>), energies loss densities by the diode during the turn ON (turn OFF) transient of the diode

EMI, electromagnetic interference

f, the switching frequency

FET, Field effect transistor

FLP, Fermi Level Pinning

HEMT, High electron mobility transistor

HPHT, High pressure high temperature

IGBT, Insulated Gate bipolar transistor

$J_F(J_R)$ , forward (reverse) current density

JFET, junction FET

k, Boltzmann constant

L, region length

MESFET, Metal-semiconductor FET

MOS, Metal oxide semiconductor

MOSFET, MOS field effect transistor

n, p, electron/hole concentration

$N_{A,D,}$  active acceptor/donor concentration

$N_{\text{AO},\text{DO}}$  total acceptor/donor concentration

NEA(PEA), negative (positive) electron affinity

Nsheet<sub>2DHG</sub>, charge sheet concentration of the 2DHG

NTC(PTC), negative (positive) temperature coefficient

Nv(Nc), valence (conduction) density of states

P, total power dissipation

$P_{\mbox{\scriptsize disp}}$  , power dissipations due to displacement current

P<sub>static</sub> (P<sub>dynamic</sub>), static (dynamic) power density components for a power diode

P<sub>sw.on</sub>, turn ON power losses

q, electron charge

Qg, gate charge

Qgd, gate-drain charge

Qoss, output charge

Qs, charge density stored in the PIN diode

R<sub>ON</sub>, ON state resistance

R<sub>ON spec</sub>, specific ON state resistance

$R_{\mbox{\scriptsize P}}\mbox{, specific on state resistance of the p-type region of the diode$

Rs, sheet resistance

Rth, thermal resistance

S, active area

T, absolute temperature (K)

Tj, junction temperature

V<sub>bi</sub>, built-in voltage

$V_{\text{bn}}$ , barrier height between the p-type semiconductor and the Schottky metal

$V_{\mbox{\scriptsize bn}}$ , barrier height between the p-type semiconductor and the Schottky metal

V<sub>F</sub> (V<sub>R</sub>), forward (reverse) voltage

WBG, wide bandgap

$\delta$ , duty cycle

$\varepsilon$  , permittivity

$\epsilon_0$  , vacuum permittivity

$\epsilon_r$  , relative permittivity

η, ideality factor of the diode

$\mu_{n,p}$ , electron/hole mobility

ρ, region resistivity

$\tau$ , ambipolar lifetime

## **ABSTRACT**

With its remarkable electro-thermal properties such as the highest known thermal conductivity (~22W/cm· K at room temperature) of any material, high hole mobility (> 2000cm²/V·s), high critical electric field (>10MV/cm), and large bandgap (5.47eV), diamond has overwhelming advantages over

silicon and other wide bandgap semiconductors (WBG) for ultra-high- voltage and high temperature applications (>3kV and >450 K, respectively). However, despite their tremendous potential, fabricated devices based on this material have not delivered yet the expected high-performance. The main reason behind this is the absence of shallow donor and acceptor species. The second reason is the lack of consistent physical models and design approaches specific to diamond-based devices that could significantly accelerate their development. The third reason is that the best performances of diamond devices are expected only when the highest electric field in reverse bias can be achieved, something that has not been widely obtained yet. In this context, high temperature operation and unique device structures based on the 2DHG formation represent two alternatives which could alleviate the issue of the incomplete ionization of dopant species. Nevertheless, ultra-high temperature operations and device parallelization could result in severe thermal management issues and affect the overall stability and long-term reliability. Additionally, problems connected to the reproducibility and the long-term stability of 2DHG based-devices still need to be resolved.

This review paper aims at addressing these issues by providing the power device research community with a detailed set of physical models, device designs and challenges associated to all the aspects of the diamond power device value chain, from the definition of figures of merits, the material growth and processing conditions, to packaging solutions and targeted applications. Finally, the paper will conclude with suggestions on how to design power converters with diamond devices and will provide the roadmap of diamond devices development for power electronics.

#### 1. Introduction

The increasing demand for a low carbon and energy efficient society has raised the need for new technologies for power electronics applications. In this context, wide bandgap (WBG) and ultra-wide bandgap (UWBG) semiconductors have been researched to quantify their advantages in terms of efficiency, current density, thermal performance, radiation hardness, switching frequency, and form factor of the overall power system compared to Si devices and systems [1-3]. The mature technology and the best trade-off between performance and cost have been so far the key to success of Silicon-based power devices and circuits. Nevertheless, there exists a huge variety of applications in the medium- to high- power (e.g. automotive sector, satellite communications, high speed trains, mobile terminals) where Si-based devices reach their limit in terms of efficiency due to ON state and switching losses and poor thermal dissipation management. While GaN and 4H-SiC devices have been successfully commercialized and also demonstrated to outperform their Si-based counterparts [4, 5], diamond and other UWBG semiconductors still face a number of challenges which are hindering the full exploitation of their superior physical properties (see table 1).

Despite its challenges, diamond has distinctive advantages when compared to other UWG semiconductors, due to its high hole-electron mobility, critical electric field, the highest known thermal conductivity and the widest bandgap [6, 7]. It has also peculiar features such as electron emission from hydrogen terminated surfaces, hopping conduction and surface transfer doping on hydrogen terminated surfaces. Recent breakthroughs have demonstrated efficient chemical vapor deposition (CVD) doping techniques for both p-type and n-type dopant species and relatively large area high pressure high temperature (HPHT) and CVD substrates [8]. Nevertheless, substrates are still limited in terms of cost and availability, and the resistivity of diamond layers is affected by the partial ionization of the dopants. More specifically, the lack of shallow dopant species is the main reason behind the poor room temperature performance of bulk diamond devices (see fig.1). In spite of this, several devices with high ON state current (up to 10A [9]), fast switching performance [10] and high breakdown voltage (>2kV) without any field relief structure [11] have been manufactured. Although the future commercialization of such devices seems to be limited only to niche applications (mainly

high power, frequency and temperature), future optimization of substrate growth techniques and device fabrication steps could enable the use of diamond devices in a wider range of applications.

This topical review is organised as follows. Section 2 focuses on the specific techniques to improve the doping efficiency and control, the unique properties arising from surface termination, the heterojunction structures and the carrier mobility for diamond. Section 3 presents a thorough investigation of the figures of merit applied to the specific scenario of diamond power devices and introduces a more global approach which allows to compare different diamond FETs. Section 4 deals with a systematic review of the applications and current state-of-the-art of diamond. It also highlights the issues that still need to be addressed prior to commercialization. In sections 5, the system level benefits of diamond diodes and FETs and their potential use in power converters are addressed. Finally, a suggested roadmap to a market-ready diamond power technology concludes this paper in section 6.

Table 1. Material properties of silicon, WBG and UWBG semiconductors for power applications.

| Material   Silicon   4H-SiC   GaN   Ga <sub>2</sub> O <sub>3</sub>   Diamond   AlN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                       | LINDS LINDS |                |          |                 |        |           |            |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------|----------------|----------|-----------------|--------|-----------|------------|---------------|

| Bandgap (eV)         1.1         3.3         3.4         4.9         5.5         6.1           Critical Electric Field(MV/cm)*         0.3         2.8         3.5         8         7.7-20         10           RT Field(MV/cm)*         electron Private Pri |                                                       |             |                |          |                 |        |           |            |               |

| Critical Electric Field(MV/cm)*         0.3         2.8         3.5         8         7.7-20         10           RT Field(MV/cm)*         electron         1500         1000         2000   >1000         300         1060         300           Mobility (cm²/vs)*         hole         480         120         <100   <200   <200   <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4H-SiC GaN Ga <sub>2</sub> O <sub>3</sub> Diamond AIN | Ģ           | GaN            |          | 1-SiC           | 4H-    | Silicon   | rial       | Mate          |

| Field(MV/cm)*           RT         electron         1500         1000         2000 (2DEG)         1000 (bulk)         300         1060         300           Mobility (cm²/vs)*         hole         480         120         <100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.3 3.4 4.9 5.5 6.1                                   | A           | 3.4            |          | 3.3             | 3.     | 1.1       | <b>'</b> ) | Bandgap (e)   |

| RT Mobility (cm²/Vs)*         electron         1500         1000         2000 (2DEG)         >1000         300         1060         300           Thermal Conductivity(W/mK)         150         370         100(on si) (bulk)         11-27         2200 - 2400         253-31           Relative permittivity (a.u.)         11.8         9.8         9         9.9         5.5         8.5           Substrate         8-17.7         8         8         4         <1         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.8 3.5 8 7.7-20 10                                   |             | 3.5            |          | 2.8             | 2.     | 0.3       | tric       | Critical Elec |

| Mobility (cm²/vs)*         hole         480         120         <100 (2DHG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |             |                |          |                 |        |           | *          | Field(MV/cm   |

| (cm²/Vs)*         hole         480         120         <100 (2DHG) (bulk)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                       |             | -              |          | .000            | 100    | 1500      | electron   |               |

| Conductivity(W/mK)   11.8   9.8   9   9.9   5.5   8.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                       |             |                | · · ·    | 120             | 13     | 400       |            |               |

| Conductivity(w/mK)         165(on Shappire) 253 (on GaN)           Relative permittivity (a.u.)         11.8         9.8         9         9.9         5.5         8.5           Substrate         8-17.7         8         8         4         <1         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |             | // /           |          | 120             | 12     | 480       | nole       | (cm²/Vs)*     |

| Relative permittivity   11.8   9.8   9   9.9   5.5   8.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                       |             |                |          | 370             | 37     | 150       |            | Thermal       |

| (a.u.) Substrate 8-17.7 8 8 4 <1 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                       | e)          |                |          |                 |        |           | y(W/mK)    | Conductivit   |

| Substrate         8-17.7         8         8         4         <1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9.8 9.9 9.9 5.5 8.5                                   |             | 9/             |          | 9.8             | 9.     | 11.8      | mittivity  | Relative pe   |

| ourse and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                       |             |                |          |                 |        |           |            | (a.u.)        |

| diameter(inch)**                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8 8 4 <1 2                                            |             | 8              |          | 8               | 8      | 8-17.7    |            |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |             |                | <u> </u> |                 |        |           |            |               |

| Substrate <10 10 <sup>2</sup> 10 <sup>4</sup> 10 <sup>4</sup> 10 <sup>4</sup> 10 <sup>4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $10^2$ $10^4$ $10^4$ $10^4$ $10^4$                    |             | ) <sup>4</sup> | 1        | 10 <sup>2</sup> | 10     | <10       |            |               |

| Dislocations (per cm <sup>-2</sup> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |             |                |          |                 |        |           |            |               |

| Saturatio         electro         1         1.9         2.5         2         2.5         1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.9 2.5 2 2.5 1.4                                     |             | .5             | 2        | 1.9             | 1.     | 1         | electro    |               |

| n velocity n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |             |                |          |                 |        |           |            | •             |

| (x10 <sup>7</sup> cm/s) hole 0.8 1.2 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.2 1.4                                               |             |                |          | 1.2             | 1.     | 0.8       | hole       | (x10' cm/s)   |

| Built-in Voltage   0.6   2.8   2.9     4.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.8 2.9 4.9                                           |             | 9              | 2        | 2.8             | 2.     | 0.6       | age        |               |

| (V)***                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                       |             |                |          |                 | )      |           |            | ` '           |

| type departe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |             | available      |          |                 |        |           |            |               |

| p-type dopants available available available Not Available poor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |             | available      |          | ailable         | availa | available | nts        | p-type dopa   |

| Commercially MOSFETs Diodes HEMTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       |             | HEMTs          |          |                 |        |           |            |               |

| available devices IGBTs BJTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |             |                |          |                 |        |           | vices      | available de  |

| Diodes MOSFETs Thyristors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MUSEIS                                                |             |                |          | JSFEIS          | IVIOSI |           |            |               |

| BJTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |             |                |          |                 |        |           |            |               |

<sup>\*</sup> Critical electric field and mobility are assumed to be doping independent.

<sup>\*\*</sup> Typical size

<sup>\*\*\*</sup> Calculation assumed constant doping for both sides of the junction (10x<sup>15</sup>cm<sup>-3</sup>), room temperature conditions and bandgap values which can be found in the table.

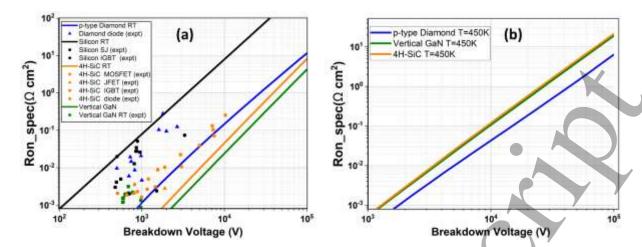

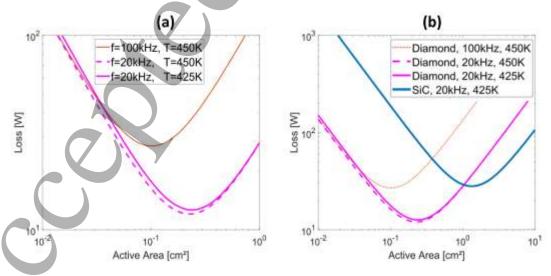

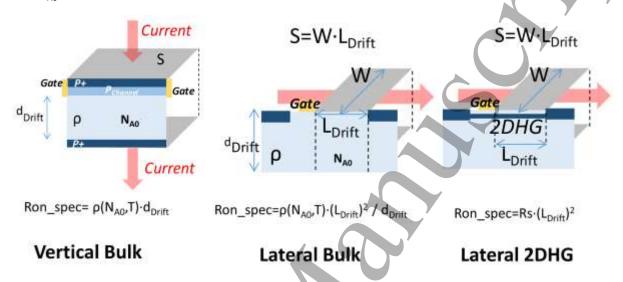

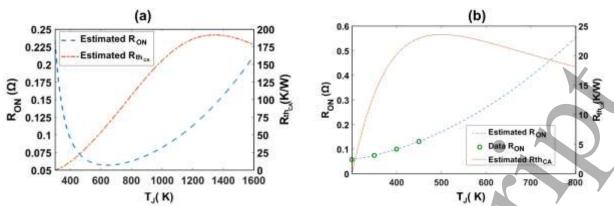

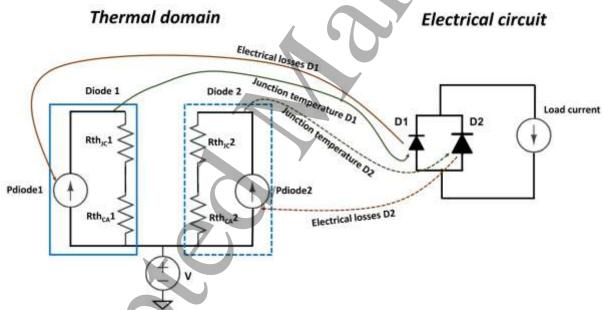

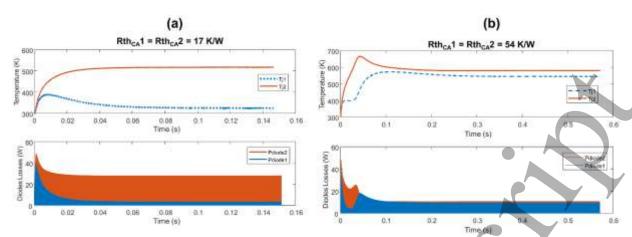

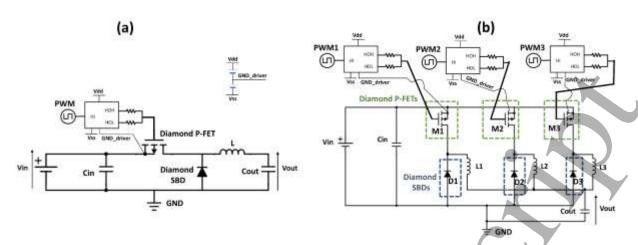

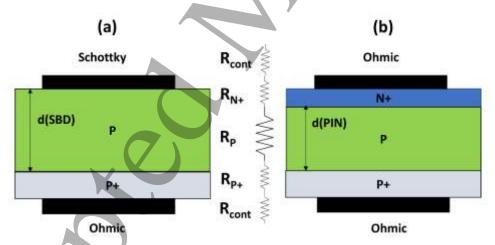

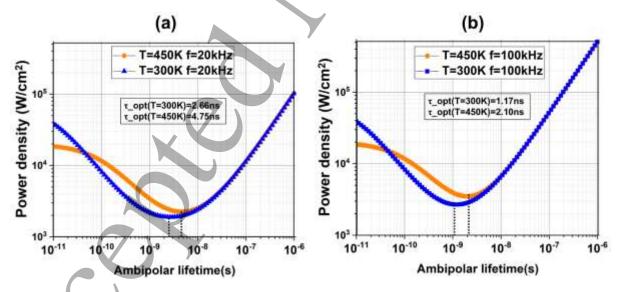

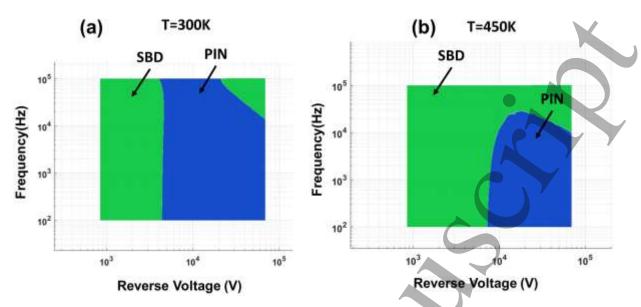

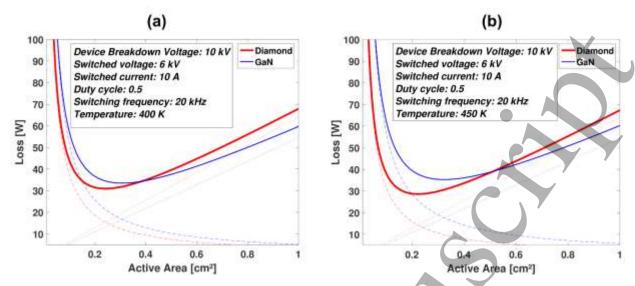

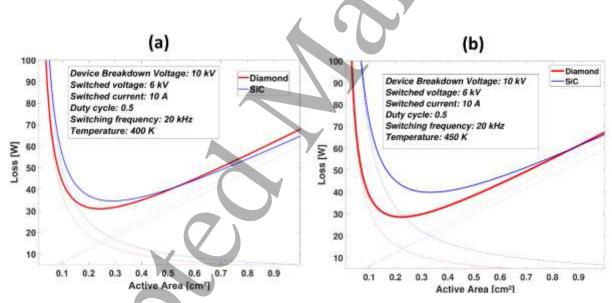

Figure 1, Vertical Ron\_spec vs BV unipolar limit for semiconductors and comparison with experimental results at room temperature (T=300K) (a) and for high operating temperature (T=450K) (b). The calculated limit is the result of an optimization procedure which assumes PT profile for the electric field, mobility function of temperature and doping, temperature dependent breakdown field for 4H-SiC (calculated by means of the ionization integral) and the incomplete ionization in the case of p-type diamond. Silicon RT is used as reference considering a constant critical electric field (table 1). As it can be noted, boron doped diamond (p-type diamond) shows a better trade-off only for high temperature (b). Data taken from [11-21] and references therein.

#### 2. Material requirements and modelling

#### 2.1. Substrates and growth

Diamond crystals are usually classified on the basis of the type of impurities concentration (nitrogen and boron) and their arrangement in the crystalline structure. An accurate classification of diamond crystals can be found in table 2 and it applies to both natural and synthetic diamonds (HPHT or CVD).

Table 2. Classification of Diamond crystals based on the type and amount of impurities.

| Diamond Substrates                                                                                                                           |                                                                                                                                                                            |                                                                                                                                                                                        |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Type I It has enough nitrogen concentration (0.3%-0.5%) which can be measured with Infrared (IR) spectrometry.                               | Type Ia Nitrogen (N) atoms replace carbon (C) atoms in the lattice (N atoms are in substitutional lattice sites) and they then                                             | Type IaA A specific type of Ia with N atoms pairs which occupy neighboring lattice site.  Type IaB Cluster of 4 substitutional N atoms symmetrically surround a vacancy in the lattice |  |  |  |

|                                                                                                                                              | Type Ib N atoms replace C atoms in A great part of HPHT diamor                                                                                                             | the lattice, but they are isolated from each other.  and substrates is type lb.                                                                                                        |  |  |  |

| Type II  It is characterized by a low nitrogen concentration which cannot be detected with IR. (usually <10 <sup>17</sup> cm <sup>-3</sup> ) | Type IIa  Very low boron and nitrogen concentration which makes this form one of the purest diamond crystals available. Diamond gemstone can be included in this category. |                                                                                                                                                                                        |  |  |  |

|                                                                                                                                              | Type IIb  Boron concentration is higher properties.                                                                                                                        | er than nitrogen. It has p-type semiconducting                                                                                                                                         |  |  |  |

The HPHT technique for the realization of synthetic diamond substrates allows to achieve high purity with a low defect density but the total size (between 2x2mm² up to 10x10mm² for IIa) is restricted due to intrinsic limitations of this method. HPHT substrates used for electronic devices are usually type Ib due to their relatively low cost and low dislocations density of about 10<sup>5</sup>cm<sup>-2</sup>, but type IIa substrates can achieve even lower dislocations density (<10<sup>3</sup>cm<sup>-2</sup>) with drawbacks in terms of complex fabrication process and cost. CVD growth has less limitations on the size of the substrate (up to 0.5 inch) despite the fact that CVD does not allow to achieve the same crystalline quality of HPHT technique. Over 2

inches CVD substrates can be found in a mosaic configuration but the bonding boundaries between the wafers can limit the electrical performance of the devices and increase strain and defects in the structure [22]. An alternative technique to homoepitaxial growth is the heteroepitaxial growth of diamond on Iridium (Ir) and other similar substrates [23, 24]. This process allows to reach over 3 inches substrates but with a high dislocation density (between 10<sup>7</sup>-10<sup>9</sup>cm<sup>-2</sup>).

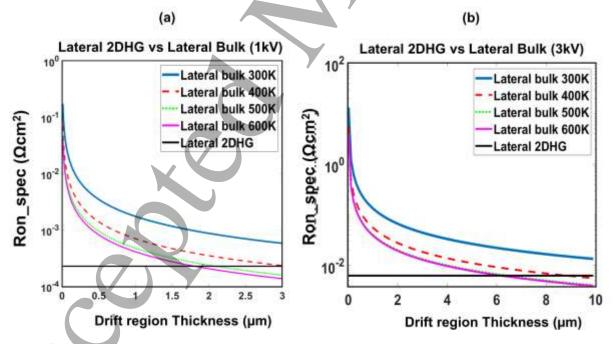

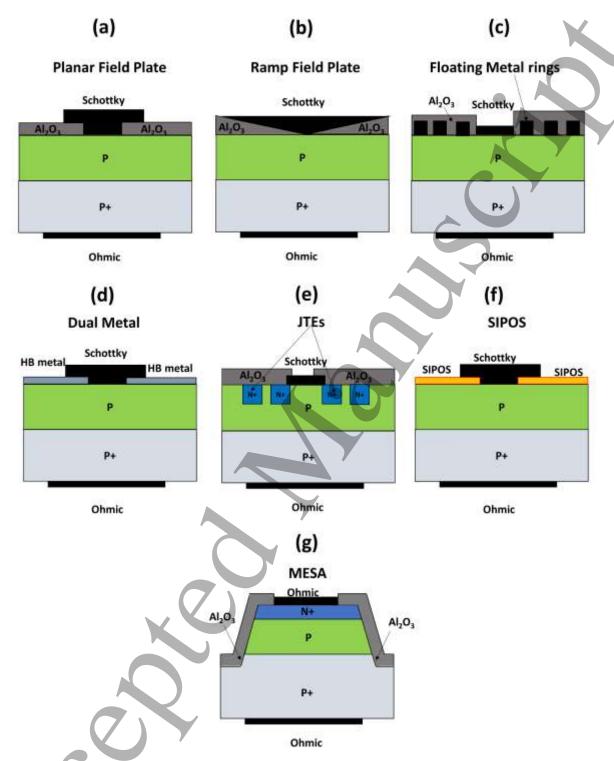

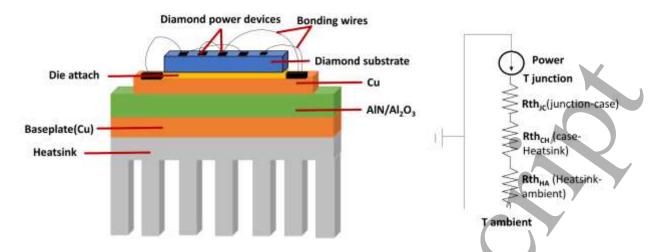

### 2.2. Doping and defects