# CIRCUITS AND SYSTEMS FOR INTELLIGENT HEARING AIDS

Thesis submitted in accordance with the requirements of the University of Liverpool for the degree of Doctor of Philosophy

by

Ian Daniel Hasler

June 2009

## **ABSTRACT**

This thesis presents research and development of electronic circuits and systems that will be used for a new generation of hearing aids. The next generation of hearing aid devices will implement a high level of adaptive signal processing enabling the hearing aids to have excellent performance and flexibility. The thesis brings together research on the natural human auditory system and hearing impairment together with research into developing a hearing aid that uses the human auditory system as a system model for the design of a hearing aid circuits and systems. This thesis then focuses on the implementation of the required signal processing with the criteria of low power; low distortion; flexibility and small scale. The work concluded that a hybrid mixed analogue/digital signal processing approach is most efficient. Hybrid signal processing uses the very low power consumption advantages from each of analogue and digital signal processing to achieve a system which operates in a very similar way to the highly power efficient human biological signal processing systems. The use of a hybrid mixed signal approach leads to the development of silicon on insulator (SOI) technology to implement hearing aid circuits because of its performance with a mixed signal system and possibilities for silicon micro-machined (MEM) microphones to provide a complete system on chip. The thesis identifies the well known Lyon & Mead, cochlea model as a highly effective and power efficient hybrid frequency feature extraction hearing aid system that uses a cascade of analogue filters. The thesis then presents, in depth, SOI as the technology for these analogue The work focuses on modelling analogue circuits in SOI and operating SOI devices in weak inversion. The thesis highlights the importance of the dynamic range and its dependence on noise and linearity of the component operational transconductance amplifiers (OTA). There is therefore an identification of the noise performance of SOI and a SOI OTA with a 10 fold improvement in linear input range is presented. The thesis presents a comparison of fully-depleted SOI versus traditional Si bulk CMOS for implementing analogue hearing aid filters. Finally in this thesis a DSP adaptive filter hearing aid noise cancellation system is investigated and the results show good noise cancellation for a wide range of SNRs whilst the DSP can be simply and power efficiently implemented.

# **CONTENTS**

| C  | CHAPTER 1 1 |                                                |      |  |  |

|----|-------------|------------------------------------------------|------|--|--|

| 1  | INTI        | RODUCTION                                      | 1    |  |  |

|    | 1.1         | MOTIVATION                                     | 1    |  |  |

|    | 1.2         | RESEARCH AIMS                                  |      |  |  |

|    | 1.3         | CONTRIBUTION OF THIS WORK                      |      |  |  |

|    | 1.4         | ORGANISATION OF THESIS                         |      |  |  |

| C  | НАРТЕ       | R 2                                            | 5    |  |  |

| 2  | THE         | HUMAN AUDITORY SYSTEM                          | 5    |  |  |

|    | 2.1         | HUMAN AUDITORY SYSTEM                          | 5    |  |  |

|    | 2.2         | ANATOMY AND PHYSIOLOGY OF THE AUDITORY SYSTEM  |      |  |  |

|    | 2.3         | HUMAN SPEECH                                   |      |  |  |

|    | 2.4         | NOISE                                          |      |  |  |

|    | 2.5         | CONCLUSION                                     |      |  |  |

| ~  |             |                                                |      |  |  |

|    |             | 3                                              |      |  |  |

| 3  | HEA         | RING IMPAIRMENT & HEARING AID TECHNOLOGY       | 17   |  |  |

|    | 3.1         | TYPES OF HEARING IMPAIRMENT                    |      |  |  |

|    | 3.1.1       | Conductive hearing impairment                  |      |  |  |

|    | 3.1.2       | Senorineural hearing impairment                | 17   |  |  |

|    | 3.2         | IMPORTANCE OF TESTING HEARING IMPAIRMENT       | 19   |  |  |

|    | 3.3         | THE PERCEIVED CATEGORIES OF HEARING IMPAIRMENT | 19   |  |  |

|    | 3.3.1       | Attenuation Loss                               | 20   |  |  |

|    | 3.3.2       | Compression Loss                               | 21   |  |  |

|    | 3.3.3       | Perceptual Loss                                |      |  |  |

|    | 3.3.4       | Bi-aural Loss                                  | 24   |  |  |

|    | 3.4 Co      | ONCLUSION                                      |      |  |  |

| C  | HAPTER      | R 4                                            | 27   |  |  |

| 4  | HEA         | RING AID DESIGN AND SPECIFICATION              | 27   |  |  |

|    | 4.1         | REVIEW OF HEARING AID TECHNOLOGY               | 27   |  |  |

|    | 4.1.1       | Conventional Hearing Aids                      |      |  |  |

|    | 4.1.2       | Bone Conduction Hearing Aid                    |      |  |  |

|    | 4.1.3       | Middle Ear Implants                            |      |  |  |

|    | 4.1.4       | Cochlear Implants                              |      |  |  |

|    | 4.1.5       | Cochlea Implant coding strategies              | . 31 |  |  |

|    | 4.1.6       | Auditory Brainstem Implants                    | . 33 |  |  |

|    | 4.2         | DEVELOPING HEARING AID TECHNOLOGY              |      |  |  |

|    | 4.3         | HEARING AID DESIGN SPECIFICATION               | . 34 |  |  |

|    | 4.3.1       | Challenges for HA development                  |      |  |  |

|    | 4.4         | CONCLUSION                                     |      |  |  |

| Cl | CHAPTER 540 |                                                |      |  |  |

| 5  | HEA         | RING AID HARDWARE IMPLEMENTATION               | . 40 |  |  |

|    | 5.1         | THE LYON & MEAD AUDITORY MODEL                 | 40   |  |  |

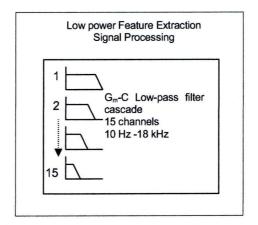

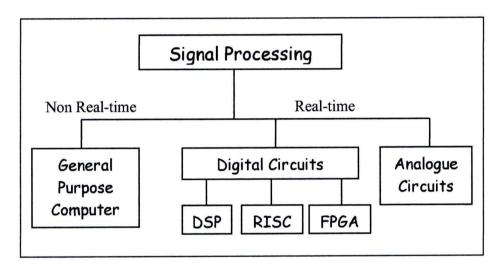

|   | 5.2            | SIGNAL PROCESSING HARDWARE ALTERNATIVES                | . 42 |

|---|----------------|--------------------------------------------------------|------|

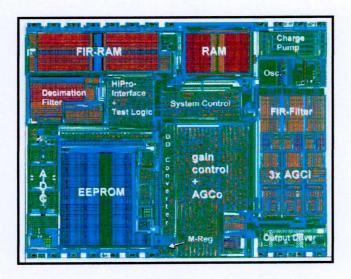

|   | 5.2.1          | Current Hearing Aid design: DSP and Microcontroller    | . 43 |

|   | 5.2.2          | A fresh approach: Digital vs analogue?                 | . 44 |

|   | 5.3            | DIGITAL VS. ANALOGUE FOR VLSI CIRCUITS                 |      |

|   | 5.4            | CONCLUSION                                             | 47   |

| C | НАРТЕН         | R 6                                                    | . 50 |

| 6 | SOI            | CMOS FOR ANALOGUE HEARING AID CIRCUITS                 | . 50 |

|   | 6.1            | INTRODUCTION                                           | 51   |

|   | 6.1.1          | Frequency Feature Extraction System                    |      |

|   | 6.1.2          | CMOS VLSI technology                                   |      |

|   | 6.2            | Low Power Analogue CMOS                                | . 52 |

|   | 6.2.1          | Fundamental limit of Power in Analogue CMOS            | . 52 |

|   | 6.2.2          | Practical limits of Power Consumption in Analogue CMOS | . 54 |

|   | 6.2.3          | Other Obstacles to Low power analogue CMOS design      | . 55 |

|   | 6.2.4          | Supply voltage reduction                               |      |

|   | 6.3            | THE MOSFET TRANSISTOR IN STRONG INVERSION              |      |

|   | 6.3.1          | Large Signal Analysis                                  | . 56 |

|   | 6.3.2          | Small Signal Analysis                                  |      |

|   | 6.3.3          | Channel length modulation                              | . 58 |

|   | 6.4            | THE MOS TRANSISTOR IN WEAK INVERSION                   | . 59 |

|   | 6.4.1          | Transconductance in weak inversion                     |      |

|   | 6.5            | NOISE IN ANALOGUE CIRCUITS                             |      |

|   | 6.5.1          | Shot Noise [6.11]                                      |      |

|   | 6.5.2          | Thermal Noise[6.12]                                    |      |

|   | 6.5.3          | Flicker Noise                                          |      |

|   | 6.6            | SOI                                                    |      |

|   | 6.6.1          | Overview of the state of SOI technology in electronics |      |

|   | 6.6.2          | SOI advantages                                         |      |

|   | 6.6.3          | SOI Disadvantages                                      |      |

|   | 6.6.4          | Manufacturing SOI                                      |      |

|   | 6.6.5          | Modelling SOI                                          |      |

|   | 6.6.6          | $g_m/I_D$ design process                               |      |

|   | 6.6.7          | $g_m/I_D$ comparison for FD-SOI and Si bulk<br>EKV     |      |

|   | 6.6.8<br>6.6.9 | EKV noise                                              |      |

|   | 6.7            | CONCLUSION                                             |      |

|   |                |                                                        |      |

| C | HAPTEF         |                                                        | . 88 |

| 7 | ANA            | LOGUE FILTER IMPLEMENTATION IN CMOS                    | . 88 |

|   | 7.1            | INTRODUCTION                                           |      |

|   | 7.2            | OPERATIONAL TRANSCONDUCTANCE AMPLIFIER                 |      |

|   | 7.3            | LARGE SIGNAL ANALYSIS                                  |      |

|   | 7.3.1          | Common mode range and minimum supply voltage           |      |

|   | 7.4            | SMALL SIGNAL ANALYSIS                                  |      |

|   | 7.5            | FD SOI / SI BULK OTA DESIGN, FABRICATION AND TESTING   |      |

|   | 7.6            | NOISE EQUIVALENT CIRCUIT FOR AN OTA                    |      |

|   | 7.7            | LINEARITY                                              |      |

|   | 7.8            | OTA IN ANALOGUE FILTERS                                |      |

|   | 7.8.1          | First Order structure                                  |      |

|   | 7.8.2<br>7.8.3 | Second order filter structure                          |      |

|   | 7.8.3<br>7.8.4 | Linearity                                              |      |

|   | 1.0.4          | Linear ny                                              | 101  |

|   | 7.8.5  | Linearized FD SOI tuneable OTA                     | 113      |

|---|--------|----------------------------------------------------|----------|

|   | 7.9    | DYNAMIC RANGE OF G <sub>M</sub> -C FILTER          | 119      |

|   | 7.10   | CONCLUSION                                         | 121      |

| C | HAPTEF | 88                                                 | 124      |

| 8 | ADA    | PTIVE FILTERS IMPLEMENTED AS A DSP CORE PROC       | CESS 124 |

|   | 8.1    | ADAPTIVE FILTERS FOR NOISE CANCELLATION            | 125      |

|   | 8.1.1  | Noise                                              | 125      |

|   | 8.1.2  | Adaptive Filters                                   | 126      |

|   | 8.1.3  | Adaptive Filter Structure                          | 126      |

|   | 8.2    | ADAPTIVE FILTER ALGORITHMS                         |          |

|   | 8.2.1  | The LMS (Least Mean Squares) Algorithm             | 127      |

|   | 8.2.2  | Recursive Least Squares (RLS) Algorithm            | 128      |

|   | 8.2.3  | Evolutionary Filters Using Genetic Algorithms      | 128      |

|   | 8.2.4  | Adaptive Algorithm Conclusion                      | 129      |

|   | 8.3    | THE LMS ALGORITHM                                  | 129      |

|   | 8.3.1  | Step-size Parameter                                | 129      |

|   | 8.3.2  | Stability of LMS Algorithm                         | 130      |

|   | 8.3.3  | Analysis of the LMS algorithm                      | 130      |

|   | 8.3.4  | Time invariant unitary input                       | 131      |

|   | 8.3.5  | Number of filter coefficients (Filter Length, 1)   |          |

|   | 8.3.6  | Step-size Parameter, $\mu_{ssp}$                   | 135      |

|   | 8.3.7  | Normalised LMS Algorithm                           |          |

|   | 8.4    | SYSTEMS USING ADAPTIVE FILTERS FOR NOISE REDUCTION | 138      |

|   | 8.4.1  | Short Term Invariant Noise                         |          |

|   | 8.4.2  | Adaptive Noise Cancellation                        |          |

|   | 8.4.3  | Feedback Cancellation                              | 140      |

|   | 8.5    | DUAL MICROPHONE ADAPTIVE NOISE CANCELLATION        |          |

|   | 8.5.1  | Method                                             |          |

|   | 8.5.2  | Misalignment                                       |          |

|   | 8.5.3  | Misadjustment                                      |          |

|   | 8.6    | CONCLUSION                                         | 147      |

| C | HAPTER | 19                                                 | 151      |

| 9 | SUM    | MARY AND CONCLUSIONS                               | 151      |

# LIST OF FIGURES

| Number                                                                                                   | Page |

|----------------------------------------------------------------------------------------------------------|------|

| Figure 2.1, The Human Ear (taken from [2.4])                                                             | 7    |

| Figure 2.2, Three-dimensional representation of the travelling wave on the basilar                       |      |

| membrane in the uncoiled cochlea, (taken from [2.4])                                                     |      |

| Figure 2.3, Cross section of the uncoiled cochlea, showing the three tubes and the hearing               | ıg   |

| organ, the organ of Corti. Hair cells sit on the basilar membrane and the auditory                       |      |

| nerve, (taken from [2.8]).                                                                               | 11   |

| Figure 2.4, Auditory System Process Model.                                                               | 13   |

| Figure 3.1, Auditory System Process Model.                                                               | 20   |

| Figure 3.2, Illustration of Dynamic Range Compression                                                    | 22   |

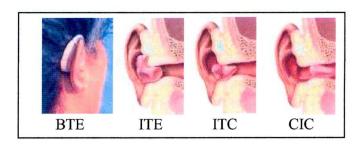

| Figure 4.1, Fitting styles for Conventional Hearing Aids, (taken from [4.1])                             | 29   |

| Figure 4.2, Trade off in the design of a Hearing Aid.                                                    | 36   |

| Figure 5.1, Lyon & Mead model of the fluid dynamics of the cochlea as a cascade of                       |      |

| filters.                                                                                                 | 41   |

| Figure 5.2, Signal Processing Hardware Alternatives                                                      | 42   |

| Figure 5.3, TÜRK+TÜRK ELECTRONIC GMBH Digital Hearing Aid Die Layout (tak                                | en   |

| from [5.6])                                                                                              | 43   |

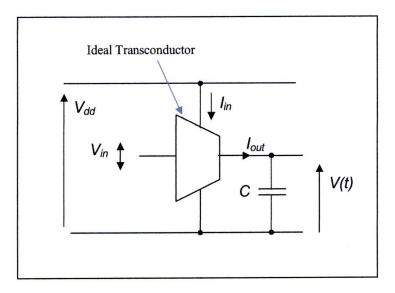

| Figure 6.1, Basic integrator circuit, assuming the transconductor is 100% efficient                      | 53   |

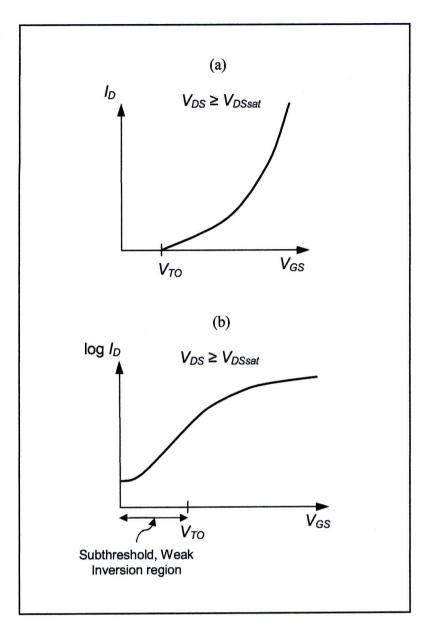

| Figure 6.2, a) Strong inversion model for $I_D$ versus $V_{GS}$ for a device operating in saturation     | on   |

| $(V_{DS} \ge V_{DSsat})$ , showing no drain current below $V_{TO}$ ; b) Drain current below $V_{TO}$ for | •    |

| subthreshold/weak inversion for $I_D$ versus $V_{GS}$ for a device operating in saturation               |      |

| $(V_{DS} \ge V_{DSsat})$ .                                                                               |      |

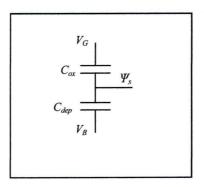

| Figure 6.3, The body effect coefficient Si bulk MOSFET                                                   | 62   |

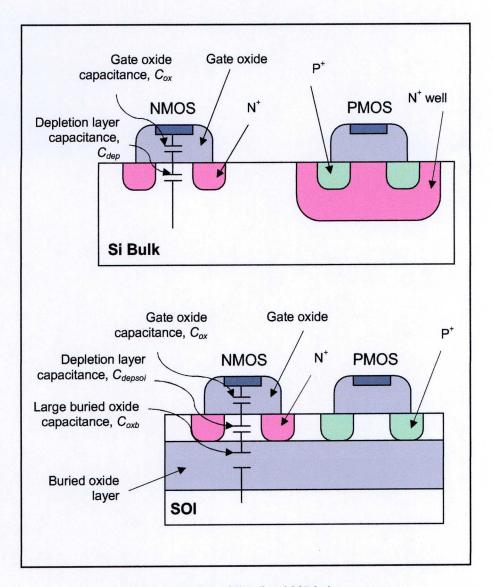

| Figure 6.4, Comparison of Si Bulk and SOI device structures.                                             | 70   |

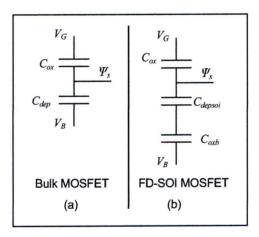

| Figure 6.5, The body effect coefficient for, (a), Si bulk and (b) FD SOI CMOS                            | 71   |

| Figure 6.6, Drain current $I_D$ versus $V_{DS}$ for a SOI MOSFET device, showing the "kink               |      |

| effect"                                                                                                  | 74   |

| Figure 6.7, Simple CMOS gain circuit.                                                                    | 77   |

| Figure 6.8, $g_m/I_D$ vs $I_D/(W/L)$ curves for Bulk PMOS, NMOS and SOI PMOS, NMOS                       |      |

| using EKV model [6.29]                                                                                   |      |

| Figure 6.9, EKV model of drain current versus gate voltage for an Si bulk NMOS, $V_{TO}$ =               |      |

| $0.6 \text{ V}, L = 6  \mu\text{m}, W = 35  \mu\text{m}.$                                                |      |

| Figure 7.1, OTA (a) Symbol, (b) Ideal Small Signal Equivalent Circuit                                    |      |

| Figure 7.2, Tuneable Transconductance Amplifier CMOS circuit                                             |      |

| Figure 7.3, Simulation results for voltage to current compression controlled by bias curre               |      |

| $I_b$                                                                                                    |      |

| Figure 7.4, Parasitic Capacitances of OTA with differential input signal, (see (7.4))                    |      |

| Figure 7.5, Small Signal equivalent circuit for an OTA                                                   |      |

| Figure 7.6, Small Signal equivalent circuit for an OTA including capacitances (see (7.4))                | ).   |

|                                                                                                          |      |

| Figure 7.7, Cadence® design created for a typical Si bulk transistor technology OTA                       |

|-----------------------------------------------------------------------------------------------------------|

| circuit95                                                                                                 |

| Figure 7.8, Basic copy of a 2 µm FD SOI technology OTA circuit fabricated at UCL,                         |

| Catholic University in Leuven-la-Neuve, Belgium, based on the circuit shown in fig.                       |

| 7.2 and parameter given in table 7.2                                                                      |

| Figure 7.9, Simulated and experimental characteristics of the FD SOI OTA described in                     |

| fig. 7.2 and table 7-1                                                                                    |

| Figure 7.10, Comparison of bandwidth versus bias current, (as a measure of power                          |

| dissipation), for an Si bulk and FD SOI basic OTA                                                         |

| Figure 7.11, (a) Noise model of OTA with equivalent noise sources for each transistor. (b)                |

| Overall Equivalent noise model for OTA                                                                    |

| Figure 7.12, First-order low-pass filter, or follower integrator circuit using a single OTA.              |

| The bias current controls the cut-off frequency of the filter                                             |

| Figure 7.13, Second order G <sub>m</sub> -C filter using two OTAs                                         |

| Figure 7.14, Second order low pass filter structure with controllable Q                                   |

| Figure 7.15, Gain magnitude response for second order low pass filter, with controllable                  |

| $Q$ , figure 7.14, for various values of $\alpha_t$                                                       |

| Figure 7.16, Asymmetric differential pairs with common ratio $m:1$ , for the linearization of             |

| an OTA                                                                                                    |

| Figure 7.17, Differential pair and four different source degradation techniques for the                   |

| linearization of an OTA; a) Single resistor diffuser; b) single transistor diffuser; c)                   |

| symmetric transistor diffusers; d) diode connected series transistors                                     |

| Figure 7.18, Linearized FD SOI tuneable OTA                                                               |

| Figure 7.19, Voltage-to-current characteristics and transconductance of a Si bulk OTA                     |

| with no linearization; Source degradation linearization and Source degradation and                        |

| Bump Linearization                                                                                        |

| Figure 7.20, Voltage-to-current characteristics and transconductance of the basic and                     |

| linearized OTA in Si bulk and FD SOI                                                                      |

| Figure 7.21, Normalized tranconductance for Si bulk and FD SOI OTA circuits 116                           |

| Figure 7.22, Transconductance bandwidth for basic and linearized OTA; using Si Bulk                       |

| and FD SOI devices; at different bias currents                                                            |

| Figure 7.23, Dependence of transconductance, at $V_{id} = 0$ V, on circuit temperature for Si             |

| bulk and FD SOI MOSFETS in a basic and linearized OTA circuit, $I_b = 25$ nA 118                          |

| Figure 7.24, Equivalent input voltage noise for a first order G <sub>m</sub> -C filter with a Si bulk and |

| FD SOI MOSFETS basic and linearized OTA                                                                   |

| Figure 8.1, Adaptive Filter Structure                                                                     |

| Figure 8.2, Set-up of a simple Adaptive Noise Canceller                                                   |

| Figure 8.3, Predicted output signal intensity of LMS Noise Cancellation Simulation for                    |

| Unitary Input with varying Filter Lengths, $l$ , with $\mu_{ssp} = 0.01$                                  |

| Figure 8.4, Mean predicted output signal intensity of 1000 independent trials of LMS                      |

| Noise Cancellation Simulation for Unitary Input with varying Filter Lengths, $l$ , with                   |

| $\mu_{ssp} = 0.01.$ 132                                                                                   |

| Figure 8.5, MSE for 1000 independent trials of LMS Noise Cancellation Simulation for                      |

| Unitary Input with varying Filter Lengths, $l$ , with $\mu_{ssp} = 0.01$                                  |

| Figure 8.6, Settled MSE against Filter Length, <i>l</i> , for a LMS Noise Cancellation with    |

|------------------------------------------------------------------------------------------------|

| Unitary Input, $\mu = 0.01$                                                                    |

| Figure 8.7, MSE Learning Curve against Filter Length, <i>l</i> , for a LMS Noise Cancellation  |

| with Unitary Input Input, $\mu = 0.01$                                                         |

| Figure 8.8, Predicted output signal intensity of LMS Noise Cancellation Simulation for         |

| Unitary Input with varying $\mu_{ssp}$ and filter length $l = 10$                              |

| Figure 8.9, Mean predicted output signal intensity of 1000 independent trials of LMS           |

| Noise Cancellation Simulation for Unitary Input with varying $\mu_{ssp}$ and filter length $l$ |

| = 10                                                                                           |

| Figure 8.10, MSE for 1000 independent trials of LMS Noise Cancellation Simulation for          |

| Unitary Input with varying $\mu_{ssp}$ and filter length $l = 10$                              |

| Figure 8.11, Adaptive Filter Noise Reduction Structures, a) A simple short term invariant      |

| noise canceller using speech detection and an adaptive filter, b) A dual microphone            |

| noise canceller with two adaptive filters, c) feedback noise cancellation with a               |

| delayed adaptive filter                                                                        |

| Figure 8.12, Simple Two-microphone adaptive noise cancellation beamformer schematic.           |

|                                                                                                |

| Figure 8.13, Simulation results for Simple Two-microphone Adaptive Noise Canceller             |

| (from top to bottom: a) Target Speech, (Male speaker), b) Noise Signal,(Inside a               |

| car), c) Input Signal, (0 dB SNR), d) Output Signal)142                                        |

| Figure 8.14, Energy improvement for Simple Two-microphone Adaptive Noise Canceller             |

| for in-car noise with speech                                                                   |

| Figure 8.15, Energy improvement for Simple Two-microphone Adaptive Noise Canceller             |

| for in-car noise with misaligned speech                                                        |

| Figure 8.16, Two-microphone adaptive noise cancellation beamformer schematic with              |

| speech detection to eliminate misalignment                                                     |

| Figure 8.17, Energy improvement for Two-microphone Adaptive Noise Canceller with               |

| Speech Detection for in-car noise with misaligned speech                                       |

| Figure 8.18, Simulation results for Two-microphone Adaptive Noise Canceller with               |

| Speech Detection for in-car noise with misaligned speech, (from top to bottom: a)              |

| Target Speech, (Male speaker), b) Noise Signal, (Inside a car), c) Input Signal, (0 dB         |

| SNR), d) Output Signal)                                                                        |

| Figure 8.19, Energy improvement for Two-microphone Adaptive Noise Canceller with               |

| Variable Convergence Parameter for in-car noise with speech                                    |

### **ACKNOWLEDGMENTS**

The author wishes to thank Doctor Octavian Buiu for his supervision and guidance both academically and personally. The author would like to thank Professor S. Hall for this advice and comments to this thesis. The author would like to acknowledge his gratitude to the members of UCL, Microelectronics Laboratory, Louvain-la-Neuve, Belgium for their expert help and assistance, in particular the author could like to acknowledge the help of Bertrand Rue and Professer D. Flandre. The author also wishes to acknowledge ARM UK, EUROSOI and EPSRC for their financial assistance.

This thesis is dedicated to my wife, parents and Christopher, Karl and Samuel for their endless support and encouragement. They are very special people.

## **PUBLICATIONS**

- I. Hasler, O. Buiu, "Design of a noise cancellation system for intelligent hearing aids", Proc. of Int. CAS 2004 Proceedings, pp. 479-482, no. 2, 4-6 Oct. 2004, Sinaia, Romania.

- I. Hasler, O. Buiu, B. Rue, D. Flandre, S. Hall, "Design of a low voltage low power highly linear fully depleted SOI OTA for hearing aid applications", Proc. of EUROSOI 2006, pp. 27-28, March 2006, Grenoble.

- I. Hasler, O. Buiu, B. Rue, D. Flandre, S. Hall, "Noise in Fully depleted and Linearized SOI OTAs based G<sub>m</sub>-C filters", Proc. of EUROSOI 2007, pp.76-77, Jan. 2007, Louvain.

## **GLOSSARY**

DIBL

bandwidth  $\Delta f$  $\Delta I$ differential current 1/fflicker noise **ABI** auditory brainstem implant advanced combination encoder cochlea implant coding **ACE** strategy **ACM** device simulation model **ADC** analogue to digital converter AFprocess empirical parameter automatic gain control **AGC** ANC adaptive noise canceller **ASIC** application specific integrated circuit open loop gain  $A_{\nu \alpha}$ transconductance bandwidth proportionality constant B**BAHA** bone anchored hearing aid BOX buried oxide layer BTE behind the ear hearing aid fitting distance along the channel cCcapacitor  $C'_{ox}$ device gate oxide capacitance per unit area CA compressed analogue cochlear implant coding strategy  $Ca^+$ calcium ion  $C_{dbi}$ device 'j' drain bulk capacitance device depletion layer capacitance  $C_{dep}$ device depletion layer capacitance of the FD SOI layer  $C_{depsoi}$  $C_{gdj}$ device 'j' gate drain capacitance  $C_{gsj}$ device 'j' gate source capacitance CI cochlea implant CIC complete in canal hearing aid fitting CIS continuous interleaved sampling cochlea implant coding strategy  $C_L$ load capacitance C-level maximum power threshold for hearing loud sounds at a particular frequency Complementary metal-oxide-semiconductor **CMOS**  $C_{ox}$ device gate oxide capacitance device buried oxide layer capacitance  $C_{oxb}$ d(i)desired signal digital to analogue converter DAC  $D_e$ diffusion coefficient for electrons

drain-induced barrier lowering

DSP digital signal processing DRC dynamic range compression error signal e(i)Expected signal j  $E\{j\}$ **EEPROM** electrically erasable programmable read-only memory equivalent input noise potential  $e_{eq}$ **EKV** EPFL device simulation model device 'j' equivalent noise  $e_{ni}$ thermal noise potential  $e_{th}$ frequency F1, F2, F3 first, second, third format of speech FD SOI fully depleted silicon on insulator wafer technology transconductance bandwidth frequency  $f_{gm}$ finite impulse response **FIR FPGA** field programmable gate array transition frequency  $f_t$ effective transconductance  $g'_m$ **GBW** gain bandwidth product device transconductance  $g_m$  $G_m$ -Ctransconductance-capacitor filter device 'j' transconductance  $g_{mi}$ OTA transconductance  $g_{mOTA}$ transconductance of OTA that controls quality in filter  $g_Q$ transconductance of OTA that controls transition frequency  $g_t$ transconductance proportionality constant h flicker noise current  $i_{1/f}$ OTA bias current  $I_b$ bias current to control of OTA that controls quality in filter  $I_{bO}$ inversion coefficient ICcarrier number fluctuation theory noise  $i_{cnf}$ device drain current  $I_D$ device 'j' drain current  $I_{di}$ **IHC** inner hair cells input current  $I_{in}$  $I_n$ noise current mobility fluctuation theory noise current  $i_{mf}$ device process dependant constant for weak inversion  $I_o$ output current  $i_{out}$ shot noise current  $i_{sn}$ **ITC** in the canal hearing aid fitting ITE in the ear hearing aid fitting thermal noise current  $i_{th}$ total output noise current  $i_{to}$

Boltzman constant

k

K supply voltage reduction constant

$K^+$  potassium ion  $K_F$  empirical constant

KF process empirical parameter

l filter length

L device length dimension

LMS least mean squared algorithm for adaptive filters

LVLP low voltage, low power

m width-to-length ratio M1 & M2

MEI middle ear implant

MEM micro electro mechanical system

$M_i$  device 'j'

MPS hybrid of CA and CIS cochlea coding strategy

MSE mean squared error body effect coefficient

$Na^+$  sodium ion  $N_a$  substrate doping

$n_e$  effective body effect coefficient

NLMS normalised least mean squared algorithm for adaptive filters

$n_o$  body effect coefficient for the technology

$N_{ot}$  effective number of traps

$N_T(E_{fn})$  number of taps at quasi – Fermi level

OHC outer hair cells

OTA operational transconductance amplifier

P power

PD SOI partial depleted silicon on insulator

$p_i$  OTA pole 'j'

PNPN P-type to N-type to P-type to N-type semiconductors

iunctions

PPS hybrid of CA and CIS cochlea coding strategy

$egin{array}{ll} q & & ext{electron charge} \ Q & & ext{filter quality factor} \end{array}$

$Q_B$  device depletion layer charge  $Q_I$  device inversion layer charge

$Q_{I0}$  device inversion charge at the source  $Q_{IL}$  device inversion charge at the drain RISC reduced instruction set computer

RLS recursive least square algorithm for adaptive filters

rms root mean squared  $r_o$  device output resistance  $R_{out}$  OTA output resistance

$R_{SD}$  source degradation device resistance

$R_{th}$  equivalent resistor in which the thermal noise occurs

$R_{xx}$  autocorrelation matrix s.i. strong inversion

SD source degradation SF NLMS stability factor

Si bulk silicon bulk wafer technology

SIMOX separation by implanted oxygen FD SOI wafer production

process

SNR signal to noise ratio SoC system on chip

SOI silicon on insulator wafer technology

SPEAK example of a maximum spectral peak extraction cochlea

implant coding strategy

SRT speech reception threshold

T temperature

THD total harmonic distortion  $t_{ox}$  gate oxide thickness

T-level minimum power threshold for hearing quiet sounds at a

particular frequency

UNIBOND FD SOI wafer production process

$U_T$  thermal voltage

$vd_e$  volume density of electrons

$vd_{eo}$  equilibrium number of electrons in the substrate

$V_A$  device early voltage  $V_B$  device bulk voltage

V<sub>b</sub> OTA bias current setup voltage

$V_{dd}$  positive supply voltage  $V_{DS}$  device drain – source voltage

$V_{dssat}$  device drain source saturation voltage

$V_G$  device gate voltage

$V_{GS}$  device gate – source voltage  $V_{GSi}$  device 'j' gate – source voltage

$V_{ic}$  common input voltage  $V_{id}$  differential input voltage VLSI very large scale integration

$V_{out}$  output voltage  $V_{pp}$  peak to peak voltage

$V_{sat}$  saturation or pinch-off voltage

$V_{ss}$  negative supply voltage  $V_{TO}$  device threshold voltage W device width dimension

w.i.weak inversion $w_i$ filter weightsx(i)input signaly(i)output signalzOTA zero $Z^I$ delayed process $\alpha'$ scattering coefficient

| ~                           | Haaga'a aanstant                                     |

|-----------------------------|------------------------------------------------------|

| $\alpha_H$                  | Hooge's constant                                     |

| $\alpha_t$                  | $g_{Q}/(2g_{t})$                                     |

| $\beta$                     | $\mu C_{ox}W/L$                                      |

| $\Gamma_{rch}$              | effective channel resistance coefficient             |

| γ'                          | attenuation coefficient of electron waves into oxide |

| $\mathcal{E}_{o}$           | permittivity of free space                           |

| $\varepsilon_{ox}$          | permittivity of oxide layer                          |

| $\varepsilon_r$             | relative permittivity                                |

| $\mathcal{E}_{\mathcal{S}}$ | permittivity of silicon layer                        |

| $\lambda_{max}$             | maximum eigenvalue                                   |

| $\mu$                       | device effective mobility                            |

| $\mu_c$                     | device surface mobility                              |

| $\mu_{e\!f\!f}$             | effective mobility                                   |

| $\mu_l$                     | mobility if only lattice scattering were present     |

| $\mu_o$                     | mobility                                             |

| $\mu_{ssp}$                 | set size parameter                                   |

| $\xi(i)$                    | mean squared error                                   |

| $\xi_{ox}$                  | electric field in oxide layer                        |

| $\xi_s$                     | electric field in silicon layer                      |

| τ                           | time constant                                        |

| $\psi_s$                    | device surface potential                             |

| $\omega_o$                  | cut-off frequency                                    |

| $ abla_* $                  | gradient operator                                    |

|                             | transposed matrix operator                           |

| Н                           | complex conjugate transposed matrix operator         |

|                             | 1 3 3 5 F                                            |

# Chapter 1

#### 1 INTRODUCTION

### 1.1 Motivation

The starting point for this thesis is the natural human auditory system. We must study the natural human auditory system as a biological engineered system so that we can develop hearing aids that can compliment the biological system with an electronic auditory system. The electronic auditory system or hearing aid can therefore be used to overcome an individual's biological auditory system's deficiencies. Unfortunately statistics show only approximately 25% of people who could benefit from a hearing aid have one and of these as few as 53% are satisfied with their hearing instrument. Therefore there is plenty of potential to provide more satisfactory and more effective hearing aid circuits and systems. The ideal specification for hearing aid technology requires them to be unobtrusive (small scale), power efficient and easy to use. Hearings aids must also be highly adaptive systems to operate effectively with different types of hearing loss and in all types of noise environments. The motivation for this thesis is therefore to develop circuits and systems for hearing aids that can most effectively use technology to meet this specification.

#### 1.2 Research Aims

The objective of this research is to develop hearing aid circuits and systems to best implement an electronic auditory system to overcome an individual's auditory deficiencies. The approach used in this research will enable innovation in the development of circuits and systems for hearing aids and their implementation in hardware.

The thesis will take the human auditory system as an inspiration and model for developing a hearing aid. The research will identify how the natural human auditory system operates as a system and studies current auditory models and hearing aid technologies. This study focuses on assessing their characteristics and limitations. This will enable the fundamental requirements for effective hearing aid circuits and systems to be identified. This knowledge will them be used to develop technology for implementing these circuits and systems within hearing aids.

## 1.3 Contribution of this Work

The project involved researching the electronic circuits and systems that would be required for a new generation of hearing aids.

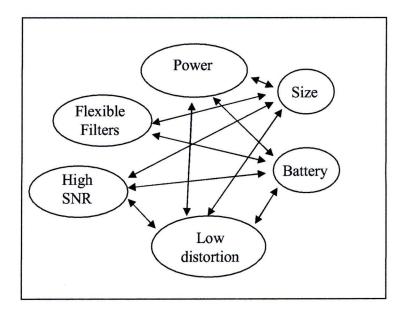

This thesis shows how the natural human auditory system can be used as a model and basis for developing hearing aid circuits and systems. It shows how previously developed electronic auditory models can be integrated into the core of a hearing aid device. The research identifies the specification for the implementation of hearing aid circuits and systems in terms of efficient power consumption, price, performance and flexibility. The specification provides no clear choice in terms of analogue versus digital implementations. This leads to the conclusion that a hybrid mixed signal implementation would provide the best solution for this application. The mixed signal approach means specific attention is required in terms of the technology platform for the hardware implementation, i.e. Silicon on insulator, SOI, technology. SOI technology provides good integration of the DSP and analogue circuits with MEM microphones or arrays of microphones, to produce a truly complete system on chip, SoC, solution.

The thesis shows how fully depleted, FD, SOI technology performs when it is used to implement analogue filter circuits as part of a hybrid system for frequency feature extraction within a hearing aid. The traditional view of SOI technology for this kind of analogue circuit would conclude that there is a detrimental effect on performance compared to a traditional silicon bulk, Si bulk, technology [1.1]. This reduction in performance results from the reduction in transconductance associated with SOI transistor structures. This thesis however shows that it is important to study other factors which enhance the performance of SOI circuit

compared to Si bulk. As a result overall it is possible to achieve comparable performance for an SOI and Si bulk circuit.

The thesis also identifies how adaptive filters can be used with a hearing aid system to remove noise and promote the recognition and understanding of speech. The thesis develops an adaptive noise cancellation system for a hearing aid application.

## 1.4 Organisation of Thesis

The thesis begins by looking at the natural human auditory system studying how it functions and operates as a biologically engineered system. As part of the investigation into the human auditory system it is necessary to have an understanding of characteristics of the main input signals, i.e. speech and noise. The natural human auditory system is translated into a system model of various functional blocks. This model is then used as the inspiration for a hearing aid systems model. The model can then be used to create an electronic device which can overcome deficiencies and malfunctions in the natural auditory system whilst still being able to fit and interact with the existing natural auditory system.

Following the creation of the hearing aid system model the thesis discusses the circuits and systems required to implement stages within the model. Taking the fact that the overall model is based on the natural auditory system the thesis looks at previous work on creating electronic versions of the human ear. An electronic auditory model can then be adapted and developed to form part of a hearing aid.

Based on the individual's requirement and current hearing aid technology a specification for implementing circuits and systems within a hearing aid is discussed. From this it becomes clear there is no clear justification for using either exclusively analogue or exclusively digital circuits and a biologically inspired hybrid approach is most efficient. Therefore a technology platform for a hybrid mixed signal approach is required. A

SOI technology platform can offer performance advantages for these kinds of mixed signal circuits and systems.

Less is known about the performance of SOI technology for analogue circuits than for digital circuits. Therefore the thesis specifically compares the implementation of transconductance–capacitance,  $G_mC$ , analogue filter circuits in FD, SOI MOSFET with traditional Si, bulk MOSFETS. These filter circuits form part of a "frequency feature extraction" stage within the hearing aid model. The performance is specifically compared in terms of dynamic input range, noise tolerance, and supply voltage.

This thesis also looks at adaptive filtering for a noise cancellation system within the hearing aid model. An investigation of how adaptive filters operate with this kind of application is presented. This includes a discussion of the algorithm used to adapt the filters within the system. An adaptive noise cancellation system is developed for the hearing aid application.

## References

[1.1] Flandre, D., Vanhoenacker, D., "Thin-film fully-depleted SOI CMOS technology, devices and circuits for LVLP analogue/digital/microwave applications", Proc. of Semiconductor Conf., CAS '98, vol. 1, pp. 115-124, 1998.

# Chapter 2

#### 2 THE HUMAN AUDITORY SYSTEM

This chapter presents an anatomical and physiological overview of the human auditory system. Hearing is discussed from an analytical point of view highlighting, in particular, those features and characteristics which are relevant to the functioning of hearing aids. This discussion is important for the following chapters. This is because the natural auditory system will provide the inspiration for the design of hearing aid circuits and systems. Also the discussion enables the understanding of when and where hearing impairment manifests within the auditory system and how and where a hearing aid must interface with the natural human auditory system. This chapter discusses and defines speech and noise from a processing viewpoint. This is important because speech and noise are the inputs to the auditory system.

# 2.1 Human Auditory System

The starting point for considering the hearing aid circuits and systems is the normal functional and operation of the human auditory system. Firstly there must be an understanding of exactly where and within which context a hearing aid must operate and interact with the wearer. Secondly the normally functioning human auditory system is used as a model for an artificial electronic auditory system which will interface with the natural auditory system and therefore operate as a hearing aid. There are obvious reasons for choosing the human auditory system as a template for the hearing aid system, since the hearing aid will be replacing or working alongside, as well as directly interacting with, a human auditory system. However there are also good reasons from an engineering point of view for using the human auditory system as a template for a hearing aid system. The human auditory system has evolved over millions of years to be an

excellent signal processing system in terms of power consumption, sensitivity, dynamic range and noise tolerance.

Normal human hearing is a very sensitive, active and a highly nonlinear processing system which is not yet fully understood. Humans can hear sounds ranging in frequency from approximately 10 Hz to 20 kHz. At the same time, the hearing system can operate as an excellent frequency analyser, differentiating tones whose frequencies vary by less than one percent [2.1]. We can tolerate a wide dynamic range with a 12 times order of magnitude from the faintest audible whisper to the loudest comfortable listening level, and within this range we can discriminate approximately 100 loudness levels [2.2].

Human hearing is primarily a system for the recognition of human speech, to historically aid communication, social understanding and aid learning. We are also able to understand and filter speech from a wide range of sources and in a range of different noise environments. These environments could range from road noise to the babble of a large number of people talking together, for example, in a bar or restaurant. A secondary function of the human auditory system involves the location of the source of sound. We can accurately discern the direction and position of a variety of acoustic sources in various environments [2.3].

# 2.2 Anatomy and Physiology of the Auditory System

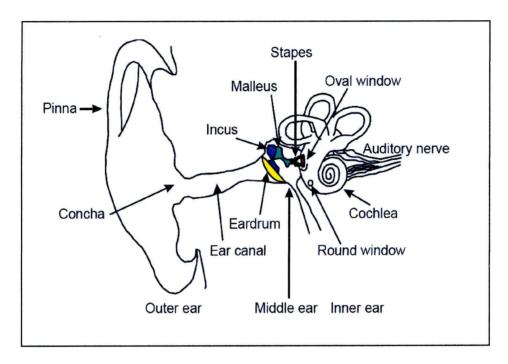

Physiologically the ear is basically a system which translates acoustic energy into electrical nerve energy which is then passed to the brain. Figure 2.1 shows that the anatomy of the ear is split into three parts; the outer; middle and inner ear. The outer ear is comprised of the ear flap made up of the pinna and concha, and the ear canal. It has the function of focusing the acoustic pressure wave energy towards the ear drum. The middle ear contains the ear drum, or tympanic membrane, and three small bones called the Incus, Malleus and Stapes; these are collectively called the ossicles and they are more commonly known as the hammer, anvil and stirrup because of their appearance. The middle ear transforms the

acoustic energy into mechanical vibrations within the inner ear. The inner ear contains the fluid filled snail shaped cochlea and the auditory or cochlea nerve. The basic function of the inner ear is to convert the mechanical energy into processed electrical nerve energy for communication with the central nervous system and transmission of information to the brain. Whilst performing this energy translation the inner ear carries out a number of more complex functions.

Figure 2.1, The Human Ear (taken from [2.4])

As described later a considerable amount of research has been carried out to understand and model the sophisticated functionality of the cochlea. Despite this research there is still not a complete understanding of how the auditory system within the cochlea precisely operates.

The basic function of the cochlear is firstly as a frequency analyser and feature exactor so that different auditory nerves are stimulated at varying stimulation rates by the frequency components and amplitude features of the acoustic input. The cochlea, and in particular the outer hair cells, OHC, are also believed to have active characteristics. It can control the gain of certain frequency bands resulting in an ability to mask or amplify certain extracted features. This can help mask some speech from noise and

operate as an automatic gain control. Secker-Walker and Searle [2.5] presented this conclusion by showing the perception of vowel forming format frequencies is enhanced by the non-linear filtering of the inner ear.

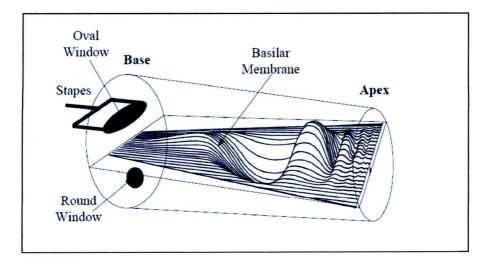

Figures 2.2 and 2.3 show the basilar membrane which runs the length of the cochlea. This divides the cochlea into two canals, the vestibular and tympanic canals. The membrane is a flexible membrane which is displaced by pressure variations in the fluid within the cochlea [2.6]. The change in width and hence the change in the stiffness of the membrane along its length causes it to act as a frequency analyser. (The membrane is stiff at the base and floppy at the apex). As a result, low frequency energy propagates a long way through the cochlear and causes a peak disturbance of the basilar membrane towards the apex of the cochlea. However high frequency energy only propagates a short way along the cochlear and peaks near the base of the cochlear. In all cases, once the energy has caused a peak disturbance in the basilar membrane, the displacement is quickly damped due to the mechanical properties of the membrane and does not travel further along the membrane. This removes these frequency components from future signal analysis along the membrane, resulting in the basilar membrane being frequency selective in the position at which maximum displacement occurs followed by no displacement further along the membrane.

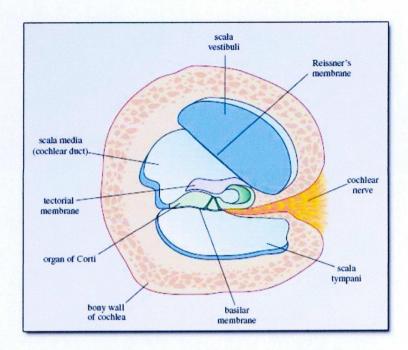

Situated upon the basilar membrane is the Organ of Corti. This contains two sets of hair cells: the inner hairs cells, IHC, and the outer hair cells, OHC. Taking a cross-section of the Organ of Corti, as shown in figure 2.3, there are three rows of OHC and one row of IHC. The IHC are primary elements which cause electrical stimulation of the auditory nerve fibres with 95% of the fibres interacting with IHC and only 5% interacting with the OHC. Each IHC interacts with approximately 20 auditory nerve fibres. The hair cells possess a tapered bundle of specialised tiny finger-like projections from the surface of the cells called stereocilla. The tips of the stereocilla are mechanically linked by tip elements which are thought, under changing tension, to act as mechanical gate controls which allow

ions to pass into the hair cells via channels in the stereocilla. The stereocilla are also in intimate contact with the tectorial membrane so that displacement of the basilar membrane causes a shear force to be set up between the tectorial membranes resulting in the bending of the bundle of stereocillia. The endolymph fluid in the cochlear surrounding the hair cell tips has a high concentration of potassium  $K^+$  ions and hence has a potential of approximately 90 mV. Therefore as the bundle is bent in one direction the transduction channel gates are opened allowing the influx of  $K^+$  ions into the hair cells causing the cell to become depolarized. This initial depolarization by  $K^+$  ions, allows other channels to open in the body of the cells which allow further depolarization as calcium  $Ca^{2+}$  ions enter the cell.

At this stage the major difference between the IHC and OHC will be presented. Studying the IHC first, depolarization causes a channel at the base of the cell to open which releases the transmitter substance called Glutamate from the IHC. This substance is collected in the synaptic cleft between the base of the cells and the end of the auditory nerve fibres. The transmitter substance causes sodium ions Na<sup>+</sup> channels to open in the fibre ends and hence the Na<sup>+</sup> rich Perilymph fluid surrounding the nerve fibre ends enters and potentials within the fibres are created. This stimulation is then sent to the brain via the 30,000 fibres of the auditory nerve [2.6]. It should also be noted that bending of the stereocillia in the opposite direction causes the K<sup>+</sup> channels to be firmly closed and the IHC become hyperpolarized resulting in a reduction of release of transmitter fluid and a reduction in the stimulation of the auditory nerve fibres. The change of polarization within OHC has a very different effect. The outer hair cell exhibits "motility" or movement.

The polarization causes the shape of the OHC to change, either lengthening or shortening as a result of changes in the internal pressure of the cell. This motility of the OHC creates an active component of the auditory system and adds or subtracts from the mechanical energy passed to the inner hair cell. Thus the auditory system can be viewed as having a

gain control system, through the motility of the OHC and its ability to add or subtract from the polarization which occurs in the IHC.

Figure 2.2, Three-dimensional representation of the travelling wave on the basilar membrane in the uncoiled cochlea, (taken from [2.4]).

We currently only have a limited understanding of the complete physiological system of hearing within the brain. However the processing area of the brain responsible for hearing, the auditory cortex, has been identified. It is known that information from the ears goes to both sides of the brain. Physiologically the auditory system is specifically designed for adaptive filtering of speech from noise. As previously discussed it is also believed that the physiology of the inner ear has some functionality for speech perception in noise. The fact we have two ears, one on each side of the head, is also important. Bi-aural hearing is also used to reduce noise by using the different noise references from each ear to filter out the background noise. Bi-aural hearing enables the physiology of the auditory system to localize sound and noise by analysing the time delay between each of the two ears picking up a sound. Localization and noise reduction is achieved by interpreting the differences in the attenuation of the sound signal resulting from each ear caused by sound shadowing of the head [2.7].

Figure 2.3, Cross section of the uncoiled cochlea, showing the three tubes and the hearing organ, the organ of Corti. Hair cells sit on the basilar membrane and the auditory nerve, (taken from [2.8]).

# 2.3 Human Speech

The fundamental aim of human hearing is to enable the understanding human speech to enhance and aid communication. Therefore it is important when discussing the human auditory system to have an understanding of speech from a signal processing point of view.

Speech is broken down into a group of sounds associated with each language. These are called phonemes. Each phoneme is created by the repetitive opening and closing of the vocal cords along with differing positioning of the tongue and lips. Voicing is the name given to a set of fundamental frequencies or formants that are a relatively long-lasting phenomenon in speech. These formants vary from person to person and depend on age and sex. Within a particular phoneme there is a signature combination of large concentrations of energy at particular formats. During voicing the spectral or frequency characteristics of a formant change and evolve as phonemes superseded one another. However the frequency of the formants remains relatively unchanged over time. The strong stable formants are easy to distinguish in a spectral analysis. These

are the first three formants called F1, F2 and F3. The fact that these formants remain relatively constant means that from a signal processing point of view, once they have been identified, they can be used to define speech and also define a particular speaker.

#### 2.4 Noise

In almost every real life situation an auditory system, be it the normal human auditory system or a hearing aid, will not just have speech on its own as an input signal. If we define the speech that is to processed and ultimately understood as the "target" signal, then we can define any other input signal as noise. From this definition of noise it can be noted that noise could be other speech signals from people speaking at the same time as the target speaker. When this type of noise from other speaker's effects someone's ability to understand a target speaker it is commonly known as the "cocktail party effect".

As well as other people speaking, noise can be classified into three main categories; "broad-band", "narrow-band" and "transients".

The broad-band noise consists of random noise with energy spread across a wide range of frequencies and is in general representative of the higher frequencies, for example noise experienced within a car, road noise and general noise.

Narrow-band noise comes from the various structural resonances, for example those heard in a car from the engine and gearbox. The spectral analysis is dominated by particularly well defined peaks associated with the mechanical natural frequencies. They are easily identified as not being formant frequency peaks because of their long term, almost stationary, highly focused nature.

Transient noise covers more intermittent noise. It does have a particular regularity, for example car noise due to running over road markings, direction indicator noise and windscreen wiper transients. This noise has a

very regular spectral analysis as it changes in time which can help identify it as not being speech.

It is rare that in any real situation, noise would consist of a single type. In general auditory environments, many types of noise occur simultaneously. These combine to cause a broad-band noise signal where, overall, the noise frequencies are slow changing. This is as opposed to speech signals which have more focused, but still changing frequency components. Also speech can be defined from noise as having overall fast changing frequencies as different phonemes are formed.

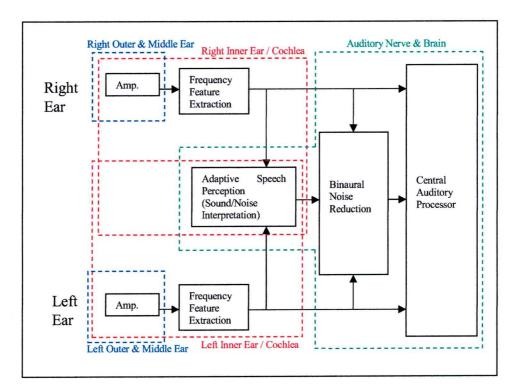

Figure 2.4, Auditory System Process Model.

## 2.5 Conclusion

The neuro-mechanical process of the human ear is not fully understood. The mechanics of sound entering the outer ear and being mechanically transferred to the inner ear is fairly straight forward. Within the inner ear the mechanical properties of the basilar membrane and fluid mechanics of the sound wave travelling through the cochlea structure acts to analyse the sound wave into its frequency components. This "frequency feature

extraction" is detected by localised stimulation of hair cells along the cochlea and the hair cells in turn stimulate neurons at their bases.

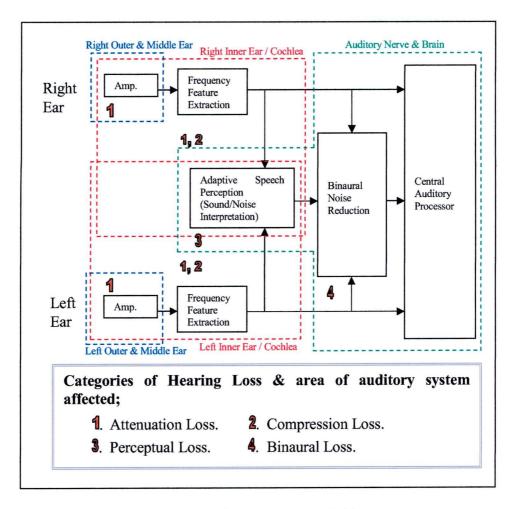

Figure 2.4 is a model of the human auditory system broken down into a series of processing blocks. The figure identifies the location of each processing block within the auditory system as they have been discussed in this chapter.

The outer and middle structures of each ear act to amplify and focus the sound for the inner ear stage. The inner ear, consisting of the cochlear structure, acts as a frequency feature extraction system. The frequency component information is passed via neurons to the brain. Before the brain concludes the processing and understanding of the information there are various processes of noise interpretation and localization which occur partly in the cochlear and partly in the brain itself. These are adaptive intelligent processes which enhance areas of target input sound whilst suppressing other noise input sound. The bi—aural nature of the human auditory system also acts to locate and localize target sound and thereby reduce non—target noise.

This chapter has particularly identified the importance of the frequency feature extraction within the auditory system. Frequency feature extraction is the analysis of an input signal into its frequency components and the analysis of the magnitude of each of these components. The importance of frequency feature extraction for communication can be seen when speech is analysed. Speech can be summarised as a pattern of changing frequency components which are called formats. The exact frequencies of the formats are particular to each individual; however the relationship between formats and the patterns they form are recognised as speech.

The area of the human auditory system that is less well understood is the ability to actively cope with noise. To begin with, it is known that it is very important for an individual to localise sound [2.3] and hence the auditory system is able to target a particular source and to some extent ignore others. This is partly achieved by the shape of the outer ear to focus

incoming sound and more importantly by the functioning of the brain. With regards to hearing aids this has important implications for the position where the devices should be worn and how the microphones should pickup sound, i.e. close to the normal ear position or within the ear canal. On a second level it is recognised that the human auditory system also has an active mechanical process whereby the outer hair cells, controlled by neurons, act to dampen certain frequency components within sound waves. This occurs along with the process of frequency feature extraction within the cochlear and carried out by the inner hair cells. From a signal processing point of view it would make sense for this active mechanical process, within the auditory system, to be working as a noise reduction process. To explain this further, we can think of it as a feedback process whereby the brain is using prior knowledge to recognise frequency components that constitute noise. These frequency components are then dampened or reduced to allow other non-noise, or target frequency components, to stand out and be more significantly recognised. It is easy to conceive that the human brain at a subconscious level would be able to identify noise using the frequency feature extraction process that occurs within the auditory system. The identification of noise would then be used for a feedback noise reduction process based on the different frequency characteristics and slow changing nature of noise compared to speech or another target.

Now that the processing blocks within the human auditory system have been identified the next chapter can discuss the manifestation and details of hearing impairment that a hearing aid device must be designed to overcome.

#### References

[2.1] Givelberg, E., Bunn, J., "A Comprehensive Three-Dimensional model of the Cochlea", J. Comput. Phys., vol. 191, pp. 377–391, 2003.

- [2.2] Nelson, D. A., Schmitz, J. L., Donaldson, G. S., Viemeister, N. F., Javel, E., "Intensity discrimination as a function of stimulus level with electric stimulation", Journal of the Acoustical Society of America, vol. 100, no. 4, pp. 2393-2414, Oct. 1996

- [2.3] Hartmann, W. M., "Localization of sound in rooms", Journal of the Acoustical Society of America, vol. 74, no. 5, pp. 1380-1391, Nov. 1983.

- [2.4] Van Schaik, A., "Analogue VLSI building blocks for an Electronic auditory pathway", PhD Thesis, Dept. Electronics, Federal Polytechnic of Lausanne, 1997.

- [2.5] Secker-Walker, H. E., Searle, C. L., "Time-domain analysis of auditory-nerve-fiber firing rates", Journal of the Acoustical Society of America, vol. 88, no. 3, pp.1427-1436, Nov. 1983.

- [2.6] Loizou, P. C., "Introduction to cochlear implants", IEEE Eng. in Med. and Bio. Mag., vol. 18, pp.32-42, 1999.

- [2.7] Krahe, R., Larsen, O. N., Ronacher, B., "Directional hearing is only weakly dependent on the rise time of acoustic stimuli", Journal of the Acoustical Society of America, vol. 107, no. 2, pp.1067-1070, Feb. 2000.

- [2.8] http://medic.med.uth.tmc.edu/Lecture/Main/ear.htm

# Chapter 3

# 3 HEARING IMPAIRMENT & HEARING AID TECHNOLOGY

Following the discussion of how the human auditory system operates and functions this chapter looks at the sources and manifestations of hearing impairment. The chapter also discusses how hearing impairment is categorised for an individual and the types of circuits and systems that are required within a hearing aid to overcome the sources of hearing impairment. Following the discussion of hearing impairment we are then able to understand relevance and requirements for hearing aids and similar devices.

## 3.1 Types of Hearing Impairment

There are two separate types of hearing impairment that can occur; Conductive hearing impairment; and Senorineural hearing impairment.

#### 3.1.1 Conductive hearing impairment

Conductive hearing impairment is caused by a disability in the outer or middle ear that causes acoustic energy not to be properly transferred to the inner ear. This can be a defect in the development of the outer and middle ear which means they have not properly formed, or damage to the ear drum and/or ossicles caused by disease or trauma within the middle ear. Generally conductive hearing impairment causes attenuation of input sound and requires a simple amplification hearing aid. However for more serious conductive hearing damage the outer and middle ear can to be bypassed and a hearing aid can be used as an alternative route for the transfer of energy to the inner ear.

#### 3.1.2 Senorineural hearing impairment

Senorineural hearing impairment is the most common type of hearing impairment and is most commonly caused by prolonged exposure to high

volume levels, bacterial and viral infections, fluid build-up, sudden trauma to the ear, as well as through the normal aging process. This type of hearing impairment manifests in the inner ear. There are different ways this impairment occurs.

Impaired inner hair cells can cause loss of sensitivity to acoustic stimulation resulting in a reduction of the acoustic energy level which is passed to the brain. Impairment of the inner hair cells can result in a reduction of the dynamic range that can be perceived, as well as a reduction of the sensitivity to variations in frequency and to overall acoustic energy levels. Hence inner hair cell damage will generate both attenuation and distortion. Hair cell damage is very common, for example, in the USA it accounts for most of the 250,000 people with profound deafness, [3.1].

Within the inner ear, the damage or the simple aging of the basilar membrane can alter its mechanical properties making it stiffer and less elastic. This will again reduce the sensitivity of hearing and reduce the frequency sensitivity and selectivity of the ear, at the frequency feature extraction stage.

To overcome these types of senorineural hearing impairment, a hearing aid is used to compensate for the deficiencies of the inner ear and adjust the acoustic signal so that audibility and perception of the sound is greatly increased.

Within the category of senorineural hearing impairment there can be hearing impairment caused by damage to the brain or the auditory nerve connecting the ear and brain. This type of hearing loss can be caused by trauma or a tumour and can cause severe distortion to hearing and an inability to interpret binaural hearing. This type of hearing impairment is associated with damage to the neuron system and its ability to transfer information. Current technology makes it difficult to design hearing aids that could compensate and take over the role of the neuron system.

## 3.2 Importance of testing hearing impairment

The exact nature of hearing impairment is very particular to the individual, therefore there are methods of characterising and testing an individual's hearing loss. Understanding how hearing loss can be characterised is important so that hearing aids can be designed to have the flexibility when they are fitted to the characterised individual's hearing loss. It would be no use to have a hearing aid that can be fitted to hearing characteristics that cannot be tested.

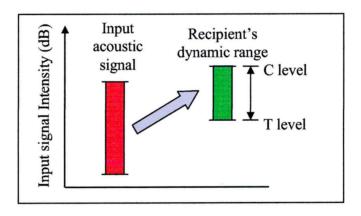

There are a number of different tests which are used to characterise the different types of hearing loss. The most important test uses an audiogram. An audiogram uses pure tone signals, (with particular frequencies across the audible range) to determine hearing characteristics at each particular frequency. Within the test the intensity or amplitude of each pure tone signal can be varied. From this the audiogram defines, for each frequency, the threshold for hearing quiet sounds, called the T-level and the threshold of maximum comfortable listening of loud sounds, called the C-level. The audiogram can also be used to categorise the perceived intensity of signals at each particular frequency.

## 3.3 The Perceived Categories of Hearing Impairment

The discussion about hearing impairment can be simplified (and better organised) if it is categorised into four types of hearing loss: Attenuation, Compression, Perceptual, and Bi-aural.

Taking the model of the hearing aid system presented in chapter 2, figure 2.4, we can use this model to indicate the area of the auditory system that is associated with each category of hearing loss, figure 3.1.

Figure 3.1, Auditory System Process Model.

#### 3.3.1 Attenuation Loss

Attenuation loss can be caused by either conductive impairment within the outer and middle ear or by senorineural impairment within the inner ear. This is when a certain frequency or range of frequencies is attenuated in amplitude resulting in certain sounds and parts of speech being perceived as being quieter.

Attenuation loss is measured using an audiogram. The audiogram determines how well the subject can hear at different frequencies, hence the louder the tone must be in order to be heard, the greater the degree of hearing loss.

To compensate for attenuation loss a hearing aid requires signal processing to amplify the input sound and counteract the attenuation. The simplest technique is "linear amplification", which means the gain is constant across all sound levels and frequencies. Because of limited dynamic range, linear amplification hearing aids usually include some peak clipping or compression limiting to limit the maximum energy output [3.2]. The disadvantage of the linear amplification is the lack of ability to adapt to different listening environments. Non-linear amplification using Automatic Gain Control, (AGC) improves the ability to interpret soft speech by varying the gain across the frequency range, hence amplifying the weak signals more than the strong ones. This results in the compression of the input dynamic range into a smaller dynamic range at the output [3.2-3.4].

## 3.3.2 Compression Loss

Compression loss is caused by senorineural hearing impairment within the inner ear, where the subject's ear has an inability to hear the full dynamic range of sounds. This results in the subject's threshold of hearing for quieter sounds (T-level) being higher and can also mean their maximum threshold for comfortable listening of loud sounds (C-level) is changed. Compression hearing loss means the subject has a reduced dynamic range of hearing. With a smaller dynamic range, the number of loudness steps that can be differentiated is also reduced.

Using the audiogram setup, compression loss is measured using the socalled 'Categorical Loudness Scaling' which involves the subject being tested with a range of stimuli consisting of different intensity levels spaced equally over the dynamic auditory range. The subjects are then asked to associate each level of intensity to one of a given set of loudness categories. The hearing impairment will be highlighted by a lack of correlation between the signals intensity and the perceived intensity. This test also enables the C-level or threshold of maximum comfortable listening to be defined.

Dynamic Range Compression, (DRC) is the principal hearing aid signal processing that compensates for the loss of range perception by

compressing the full input dynamic range into the limits of the patients dynamic range. Figure 3.2 shows a schematic example of DRC where the input acoustic signal range is translated into a dynamic range that is perceivable by the hearing aid wearer. The upper limit for the compression is the C-level (the maximum intensity for comfortable listening), and the lower limit is the T-level (the threshold of perceivable sound) [3.5]. "Multiband compression" involves separate compression being applied to two or more frequency bands; here the compression is frequency specific and requires the haring aid to have a frequency feature extraction stage. Multiband compression, as opposed to wideband compression, can reduce the masking effect of noise without affecting the audible range of speech at frequencies away from the noise [3.2].

Figure 3.2, Illustration of Dynamic Range Compression.

### 3.3.3 Perceptual Loss

Perceptual loss is caused by senorineural impairment. Background noise reduces the intelligibility of speech in all cases since the noise will mask fundamental elements of sound that make it intelligible. At high signal to noise ratios, SNR, the noise masking only affects a small amount of the speech and hence the other parts of the speech are sufficient for the auditory system to make the speech intelligible. Conversely as the signal to noise ratio reduces, more of the speech is masked and it becomes less intelligible. Because of the inabilities in the auditory system, a hearing impaired subject suffers a more significant degradation of intelligibility

from noise masking. Hence perceptual loss means subjects have greater difficulty understanding speech in noise.

This category of hearing loss is characterised by measuring a subject's 'Speech Reception Threshold', SRT. In practice this is done by exposing the subject to a set of words which are masked by various signal to noise ratios. The subject is then asked to repeat the word back as it was heard. The result is then a percentage score of the number of correctly perceived words. The words used for this test can take a variety of forms, but the words fall into two types: pure vowel sound (low frequencies), and pure consonant sounds (high frequencies). Single syllable words and sentences can also be tested; also, nonsense-syllables can be used [3.6]. percentage of correct responses in each case can be used on its own to measure hearing loss. Alternatively, the SRT can be taken as a given percentage point below which it is determined that a subject is unable to perceive the speech at that SNR; this is generally taken to be 50%. The SRT test can also be varied, for example, by using different speakers for the sound, e.g. male voice, female voice or children. Varying speech to noise ratios with varying noise types can be implemented to determine a subject's ability to hear in varying noise environments.

Perceptual loss requires hearing aid circuits and systems that can help distinguish a particular target signal from a noise signal or act to localise and identify a target signal. This requires signal processing that can focus and enhance particular frequencies within the overall input signal. These particular frequencies would belong to the target source whilst other frequencies which contribute to the noise can be suppressed. This kind of signal processing must be adaptive so that it can enhance different targets at different times and in a variety of noise environments. There is also the requirement for the signal processing to identify the target and feedback the knowledge to enable the perception of the target to be enhanced.

The signal processing for perceptual loss often requires adaptive filters as discussed later in this thesis extensively in chapter 8.

#### 3.3.4 Bi-aural Loss

Bi-aural loss is caused by senorineural impairment. This results from impairment in analysing the simultaneous information from both ears. It can again reduce the patient's ability to interpret speech from noise and can cause an inability to localise sound sources.

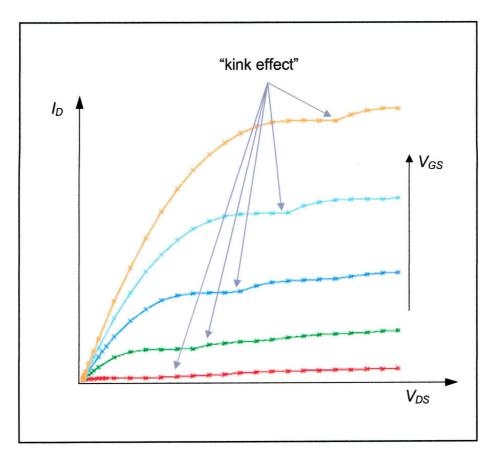

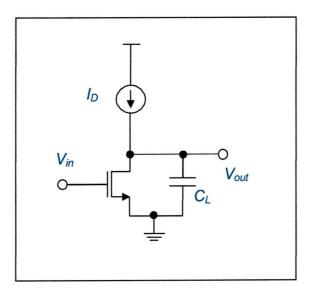

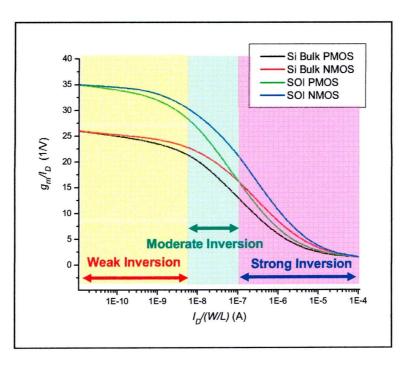

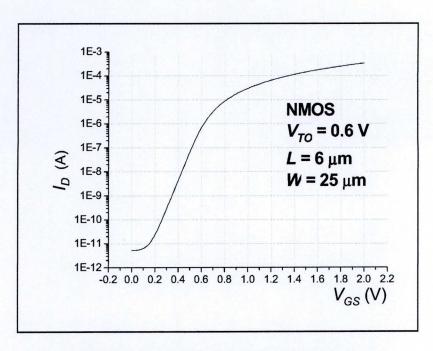

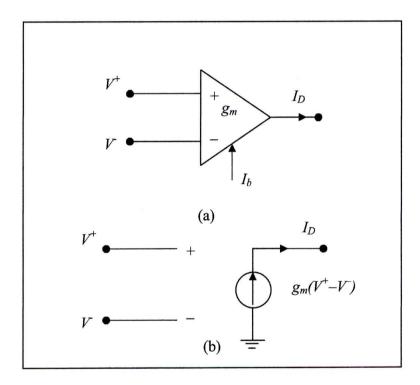

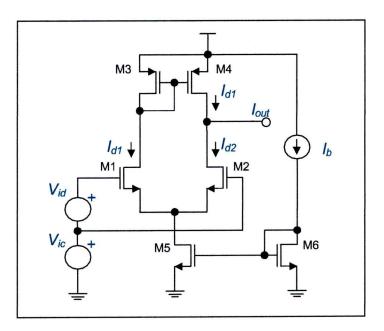

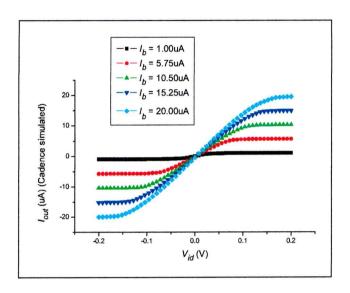

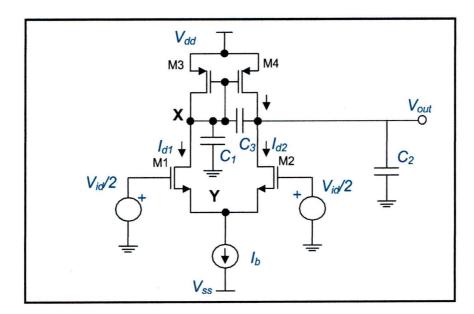

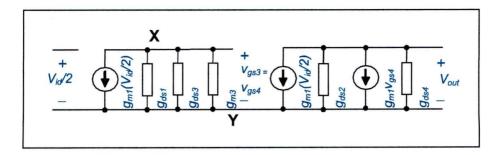

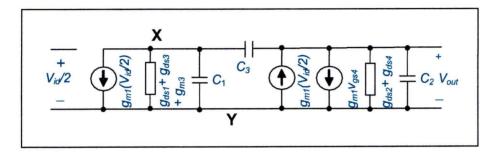

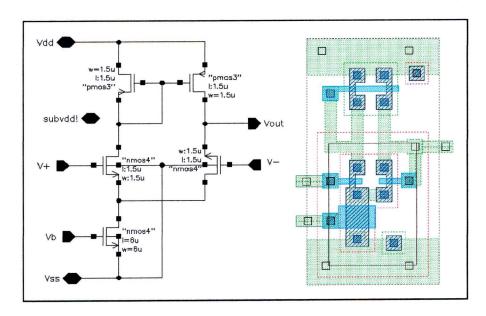

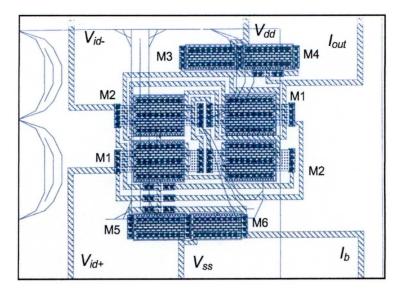

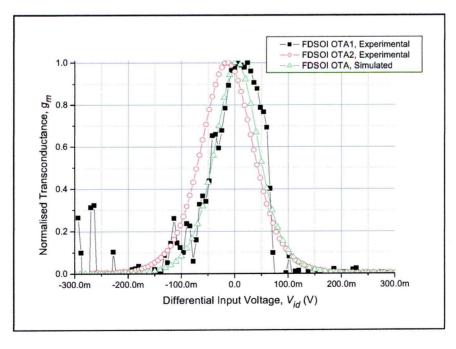

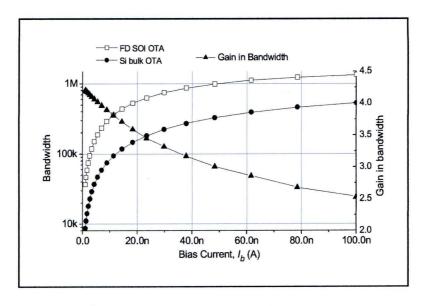

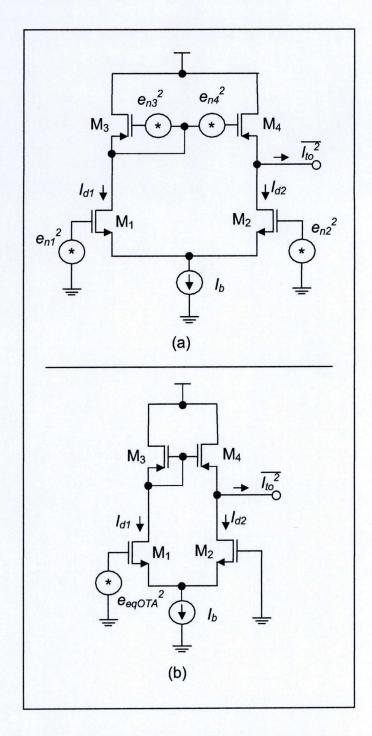

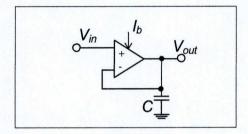

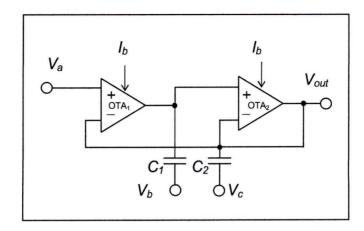

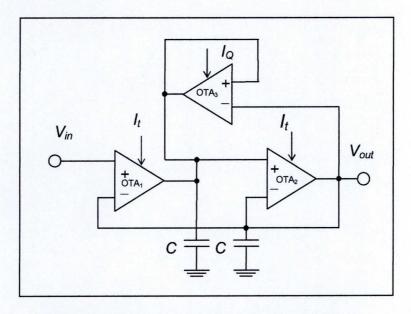

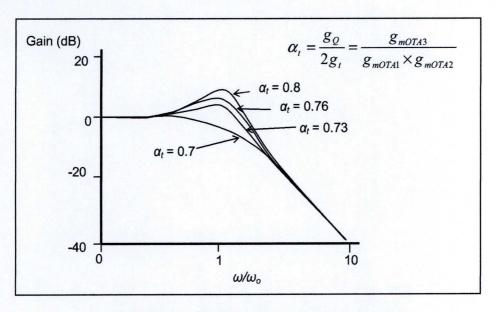

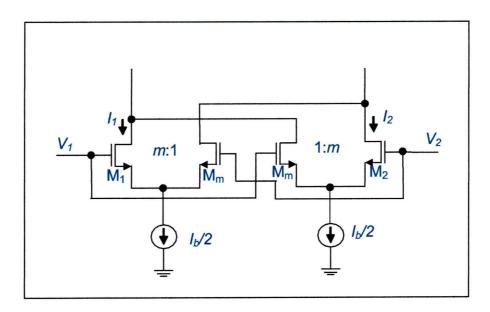

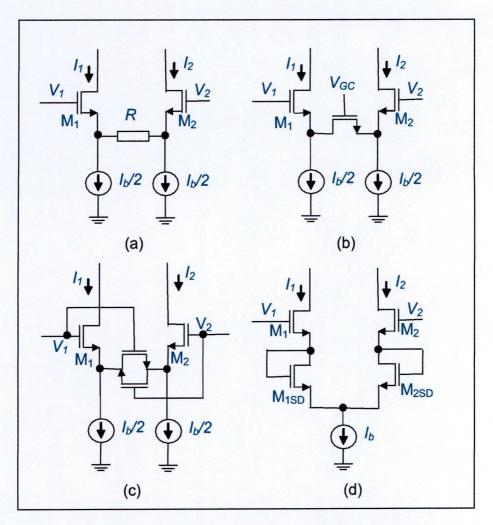

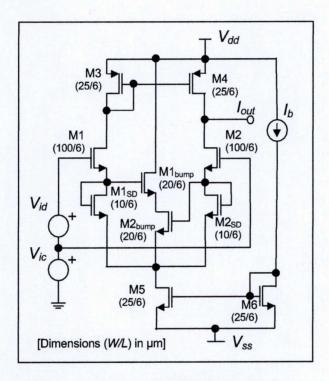

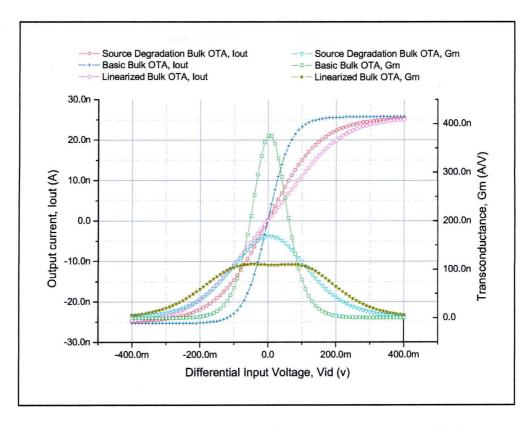

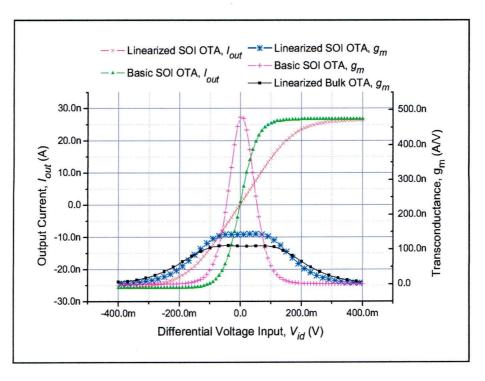

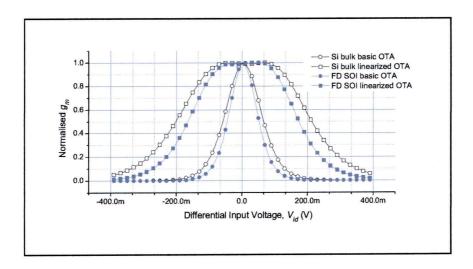

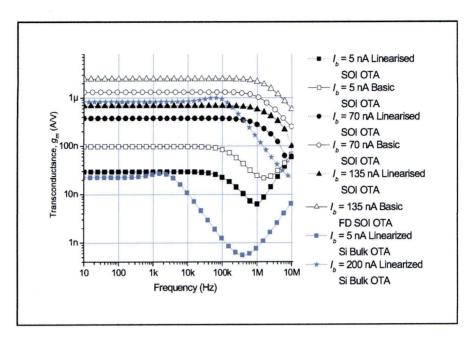

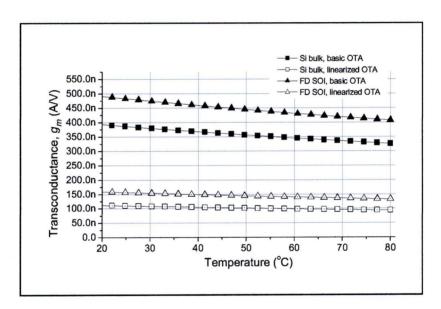

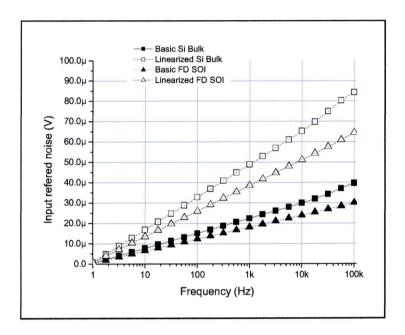

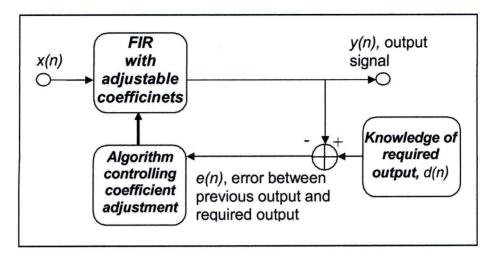

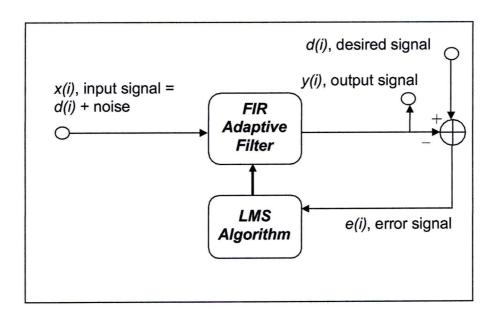

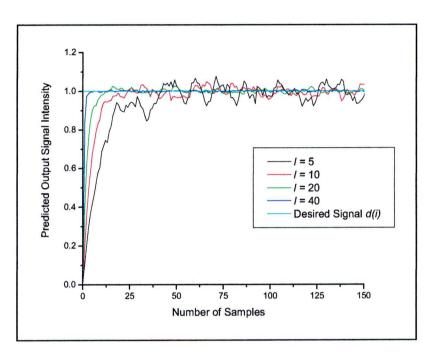

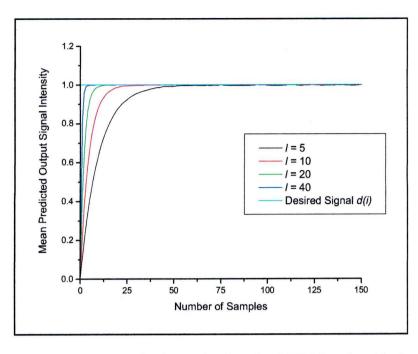

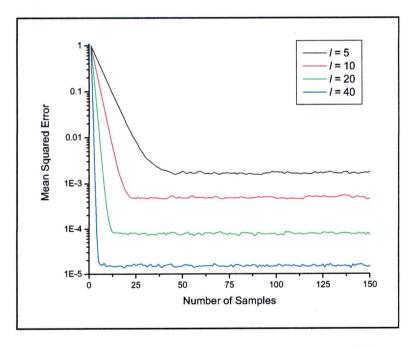

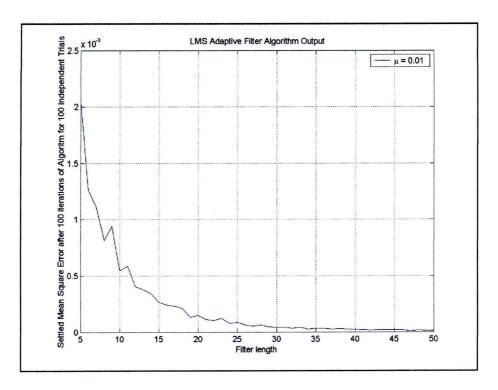

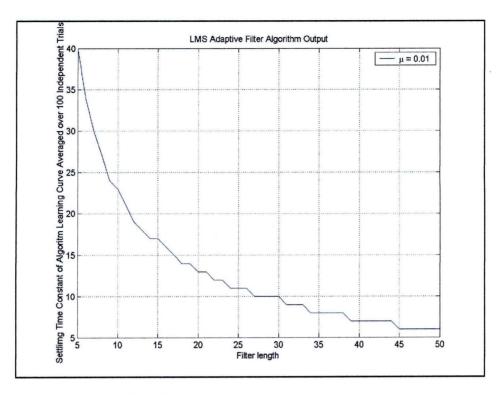

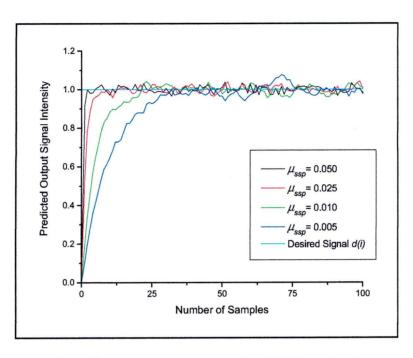

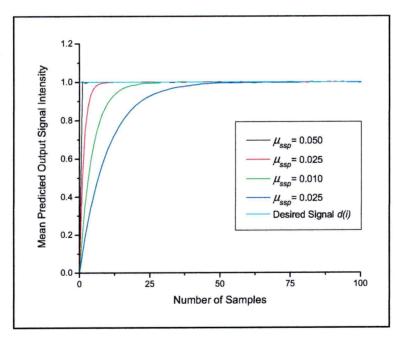

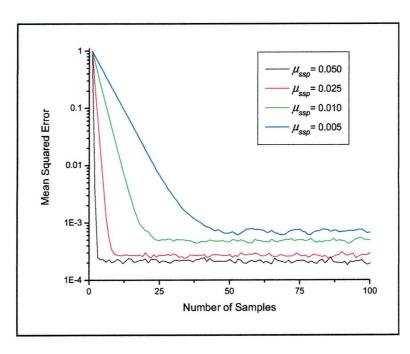

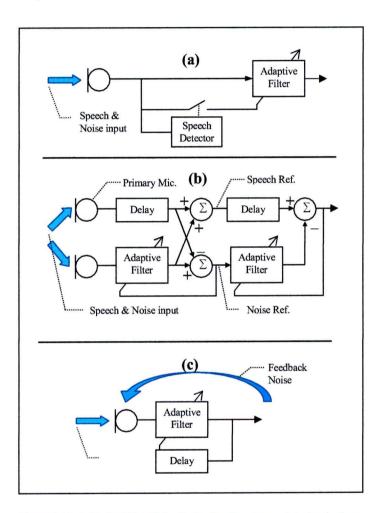

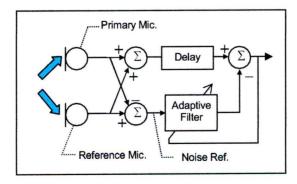

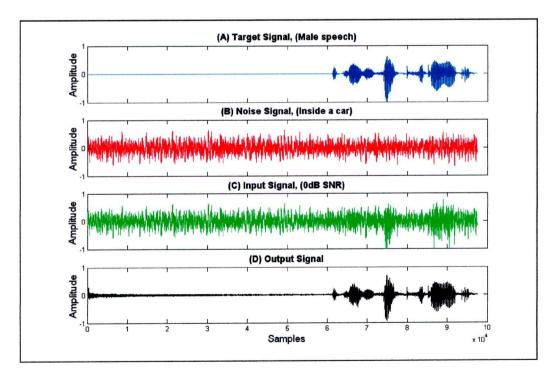

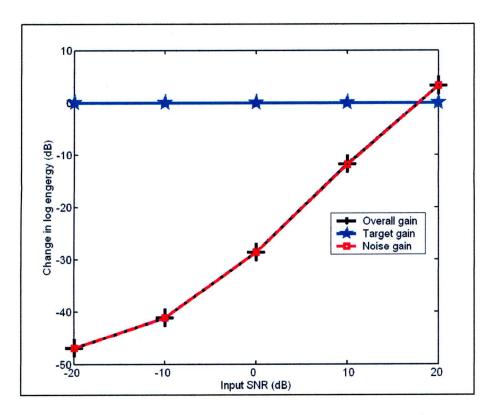

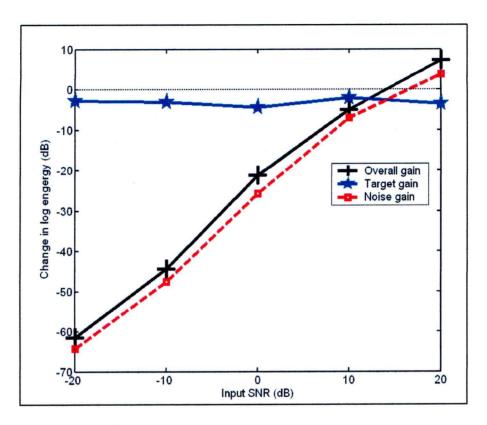

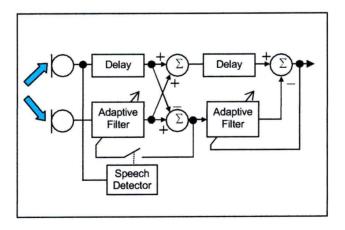

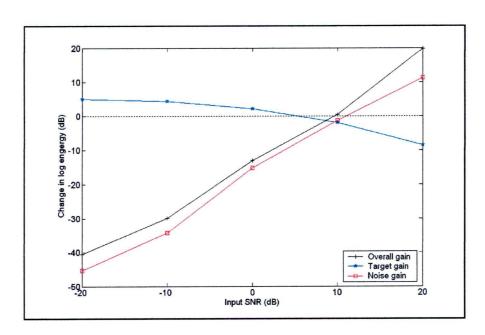

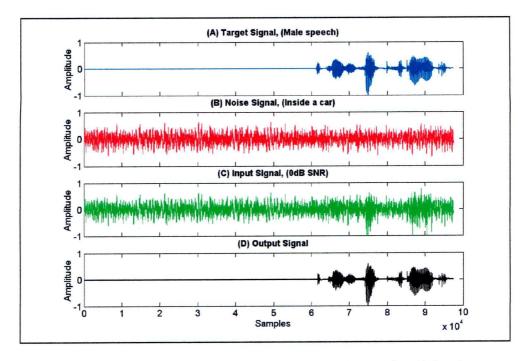

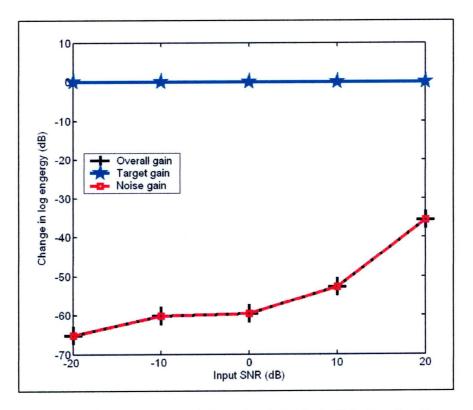

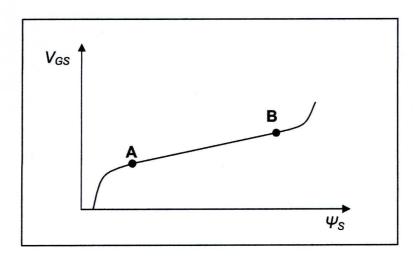

This is again tested using the SRT test, but this time varying the location of the sound source to determine the directionality of a subject's hearing ability.